The University of Manchester

# Thermal and Small-Signal Characterisation of AlGaAs/InGaAs pHEMTs in 3D Multilayer CPW MMIC

A thesis submitted to The University of Manchester for the degree of

Doctor of Philosophy

in the Faculty of Engineering and Physical Sciences

2010

Jimmy P. H. Tan

School of Electrical and Electronic Engineering

## **Contents**

| Contents                                                                | 2  |

|-------------------------------------------------------------------------|----|

| List of Figures                                                         | 4  |

| List of Tables                                                          | 9  |

| ABSTRACT                                                                | 10 |

| DECLARATION                                                             | 11 |

| Copyright Statement                                                     | 12 |

| Acknowledgement                                                         | 13 |

| List of Publications From This Work                                     | 15 |

| Chapter 1 Introduction                                                  | 16 |

| 1.1 Introduction                                                        | 16 |

| 1.2 Key Objectives                                                      | 18 |

| 1.3 Overview of The Thesis                                              | 19 |

| Chapter 2 Background Review                                             | 22 |

| 2.1 MMIC Technology                                                     | 22 |

| 2.1.1 History of GaAs MMIC Technology                                   | 22 |

| 2.1.2 Advantages and Disadvantages of MMICs                             | 25 |

| 2.1.3 Multilayer Technology and Coplanar Waveguide                      | 27 |

| 2.1.4 Polyimide as Dielectric in Multilayer Structure                   | 29 |

| 2.1.5 Fabrication Process                                               | 30 |

| 2.2 III – V Transistors                                                 | 37 |

| 2.2.1 Introduction                                                      | 37 |

| 2.2.2 Unipolar and Bipolar Transistors                                  | 38 |

| 2.2.3 Microwave Applications                                            | 39 |

| 2.3 Principle of pHEMT                                                  | 39 |

| 2.3.1 Introduction                                                      | 39 |

| 2.3.2 Small-Signal Analysis                                             | 47 |

| 2.4 Temperature Characterisation                                        | 49 |

| Chapter 3 Experimental Details                                          | 52 |

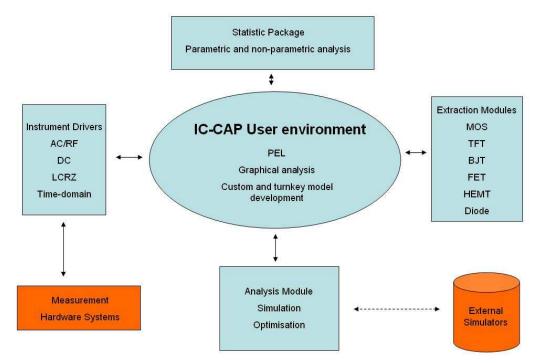

| 3.1 CAD Software                                                        | 52 |

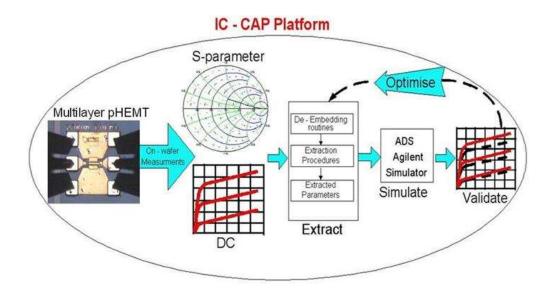

| 3.1.1 Integrated Circuit Characterization and Analysis Program (IC-CAP) | 52 |

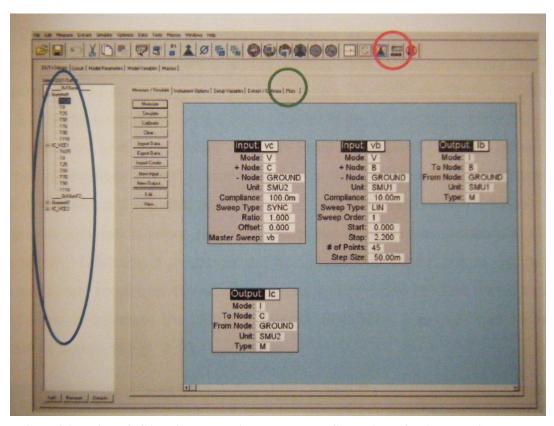

| 3.1.2 Parameter Extraction in IC-CAP                                    | 53 |

| 3.1.3      | Device Modelling Tool                                        | 56     |

|------------|--------------------------------------------------------------|--------|

| 3.2 C      | On-Wafer RF and DC Measurements                              | 58     |

| 3.2.1      | Calibration Technique                                        | 60     |

| 3.2.2      | Temperature Control Tool                                     | 62     |

| 3.3 S      | S-Parameters                                                 | 63     |

| Chapter 4  | Results and Discussion                                       | 66     |

| 4.1 D      | Device Structure                                             | 66     |

| 4.2 U      | Uniformity of pHEMTs                                         | 67     |

| 4.2.1      | Uniformity of the Virgin pHEMTs                              | 68     |

| 4.2.2      | Uniformity of the Multilayer pHEMTs                          | 72     |

| 4.3 N      | Multilayer pHEMTs Modelling                                  | 76     |

| 4.3.1      | DC Characterisation and Results                              | 77     |

| 4.3.2      | RF Parameter Extraction.                                     | 78     |

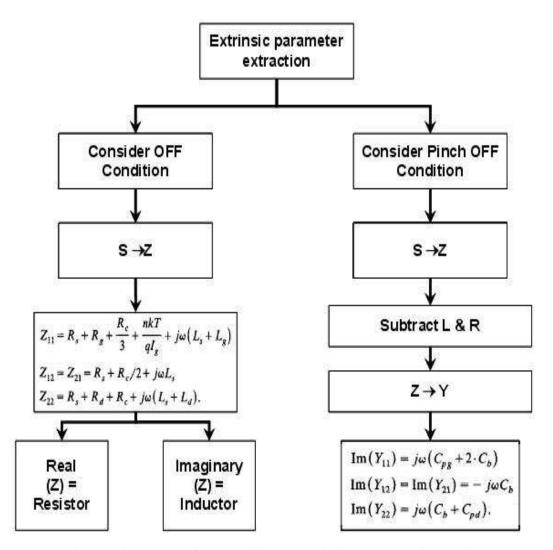

| 4.3.       | 2.1 Cold Bias Extraction                                     | 80     |

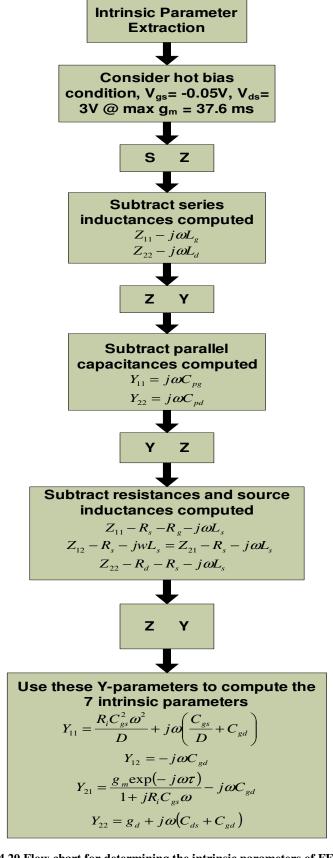

| 4.3.       | 2.2 Hot Bias Extraction                                      | 84     |

| 4.3.3      | RF Small-Signal Characterisation                             | 87     |

| 4.3.       | 3.1 Small-Signal Model of Virgin pHEMTs                      | 89     |

| 4.3.       | 3.2 Small-Signal Model of Multilayer pHEMTs                  | 94     |

| 4.4 D      | OC Temperature Dependent Multilayer pHEMTs Modelling         | 99     |

| 4.4.1      | Thermal Effects                                              | 99     |

| 4.4.2      | Results and Discussion                                       | 101    |

| 4.5 S      | Small-Signal Temperature Dependent Multilayer pHEMTs Modelli | ng 107 |

| 4.5.1      | Extrinsic Parameters Analysis                                | 108    |

| 4.5.2      | Intrinsic Parameters Analysis                                | 111    |

| Chapter 5  | Conclusions and Future Works                                 | 122    |

| 5.1 C      | Conclusions                                                  | 122    |

| 5.2 F      | Future Works                                                 | 126    |

| References |                                                              | 127    |

# **List of Figures**

| Figure 1.1 Illustration of the multilayer processing [12]                               | 17             |

|-----------------------------------------------------------------------------------------|----------------|

| Figure 2.1 Micrograph of the analogue FET switch based on Silicon MMIC technology       | ,              |

| [22]                                                                                    | 22             |

| Figure 2.2 Micrograph of the schottky barrier diode for use in 94GHz mixer circuit [27] | ].             |

| 2                                                                                       | 22             |

| Figure 2.3 Micrograph of the first monolithic amplifier [28]                            | 23             |

| Figure 2.4 Micrograph of a planar CPW amplifier using MMIC technology [16] 2            | 27             |

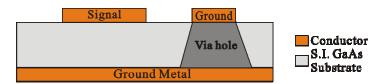

| Figure 2.5 Cross-sectional view of a Microstrip type MMIC with via holes                | 27             |

| Figure 2.6 Cross-sectional view of a typical CPW MMIC structure.                        | 28             |

| Figure 2.7 Basic structure of a multilayer MMIC [49]                                    | 29             |

| Figure 2.8 Illustration of the 3D CPW MMIC fabrication steps                            | 31             |

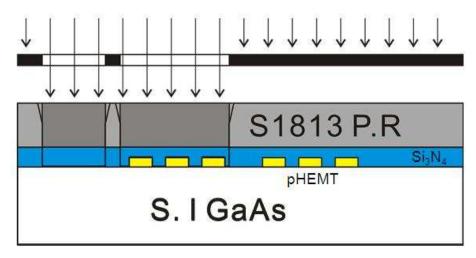

| Figure 2.9 Step 1: Opening Si <sub>3</sub> N <sub>4</sub> windows.                      | 32             |

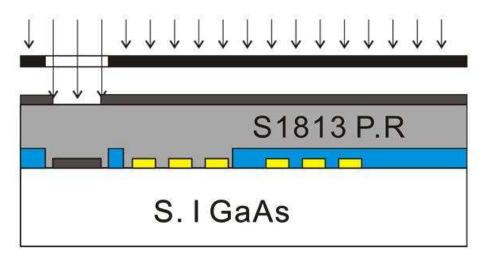

| Figure 2.10 Step 2: Making thin film NiCr resistors.                                    | 32             |

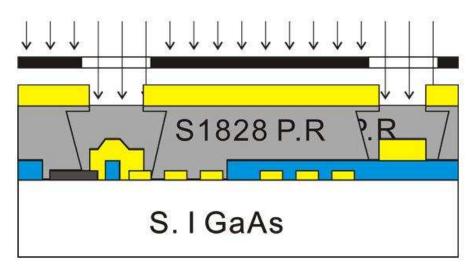

| Figure 2.11 Step 3: Evaporating Au/Ti metal layer 1                                     | 33             |

| Figure 2.12 Step 4: Applying Polyimide layer 1                                          | 34             |

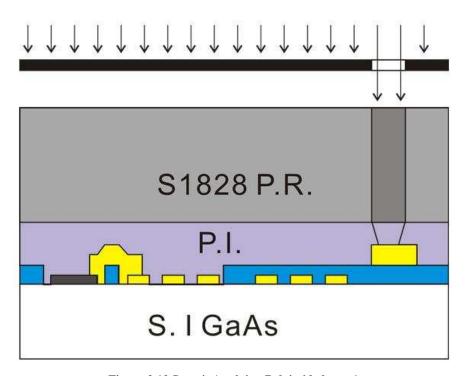

| Figure 2.13 Step 5: Evaporating Au/Ti metal layer 2                                     | 35             |

| Figure 2.14 Step 6: Applying Polyimide layer 2                                          | 35             |

| Figure 2.15 Step 7: Evaporating Au/Ti metal layer 3                                     | 36             |

| Figure 2.16 Mask set design (a single unit cell).                                       | 37             |

| Figure 2.17 Structures of three types of FETs: (a)MESFET, (b)HEMT and (c)pHEMT.         |                |

|                                                                                         | <del>1</del> 0 |

| Figure 2.18 Band structure of AlGaAs/GaAs heterojunction: (a)before and (b)after        |                |

| connecting.                                                                             | 43             |

| Figure 2.19 Cross-sectional view of a GaAs MESFET under common source                   |                |

| configuration                                                                           | 14             |

| Figure 2.20 The output characteristics of a pHEMT.                                      | 16             |

| Figure 2.21 The transfer characteristics of a pHEMT.                                    | <del>1</del> 6 |

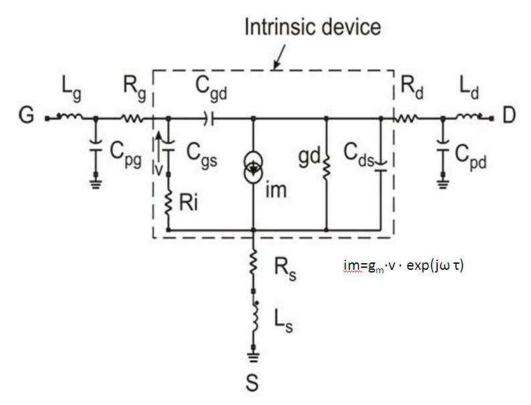

| Figure 2.22 Small-Signal equivalent circuit of a FET.                                   | 17             |

| Figure 3.1 A pictorial view of IC-CAP environment [71]                                  | 53             |

| Figure 3.2 Typical IC-CAP window showing the DUT and Setups (Blue Oval) and the         |                |

| instrument server option (Red Oval).                                                    | 54             |

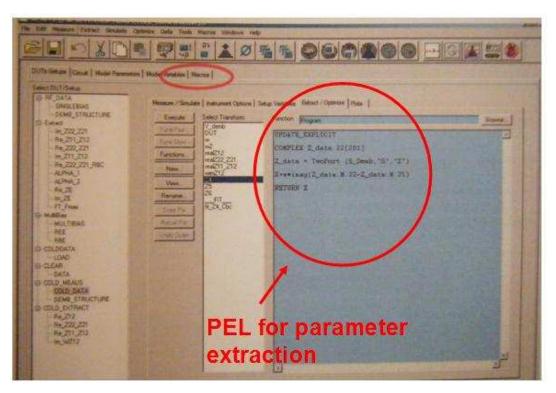

| Figure 3.3 A pictorial view of parameter extraction using IC-CAP                        | 54                  |

|-----------------------------------------------------------------------------------------|---------------------|

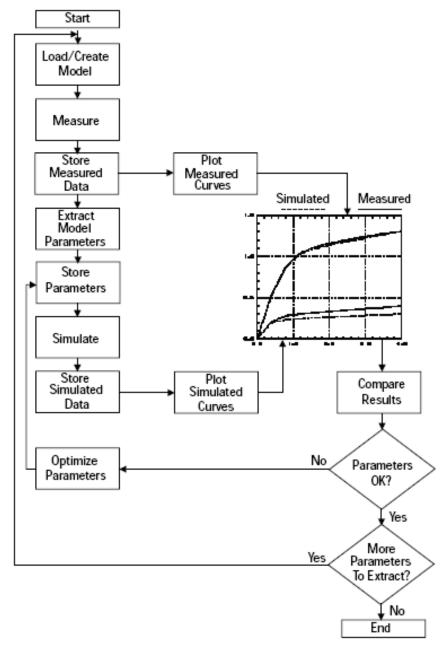

| Figure 3.4 Parameter extraction using PEL in IC-CAP.                                    | 55                  |

| Figure 3.5 Work flowchart of IC-CAP during parameter extraction [71]                    | 56                  |

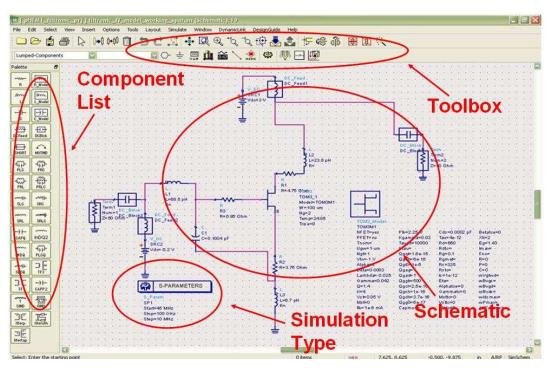

| Figure 3.6 ADS Schematic simulator user interface.                                      | 58                  |

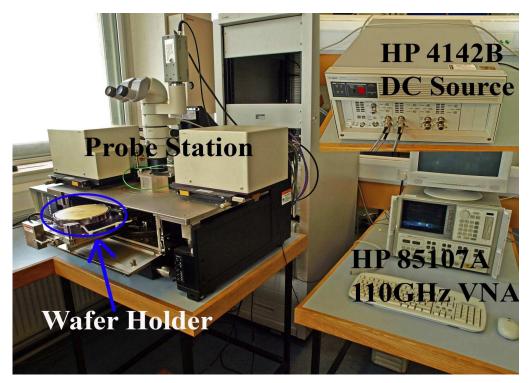

| Figure 3.7 On-wafer measurement setup showing the HP 85107A VNA, HP 4142B               | DC                  |

| source, probe station and wafer holder.                                                 | 59                  |

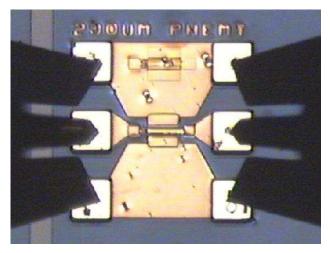

| Figure 3.8 Micrograph of a multilayer pHEMT under on-wafer probing                      | 60                  |

| Figure 3.9 Micrograph of an empty pad of the multilayer pHEMT                           | 60                  |

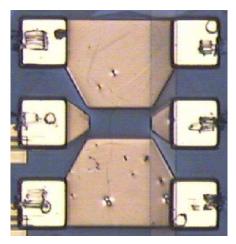

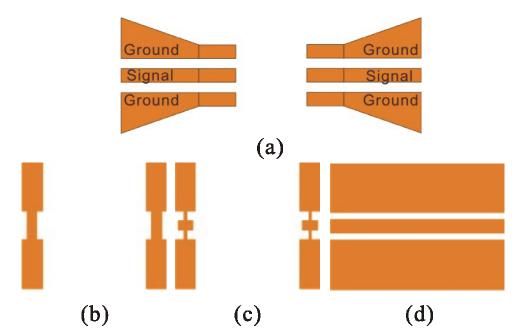

| Figure 3.10 GSG probes and calibration standards for LRRM method: (a) GSG prob          | bes,                |

| (b) short standard, (c) load standard and (d) through standard                          | 61                  |

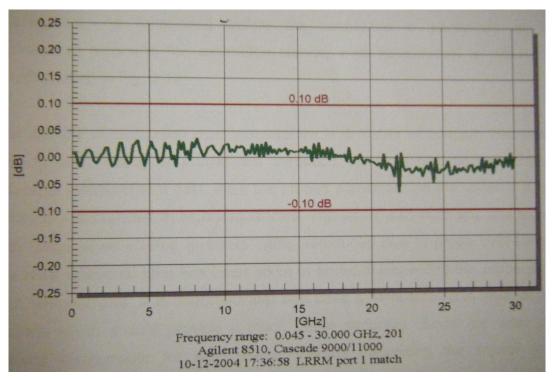

| Figure 3.11 Magnitude of S11 versus frequency showing a good calibration of S-          |                     |

| parameter measurements (±0.05 dB of error).                                             | 62                  |

| Figure 3.12 The temperature control equipment: (a) temperature controlled wafer ch      | nuck                |

| and (b) Temptronic TP03200A temperature controller.                                     | 63                  |

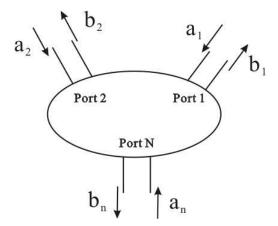

| Figure 3.13 An N-port microwave network.                                                | 64                  |

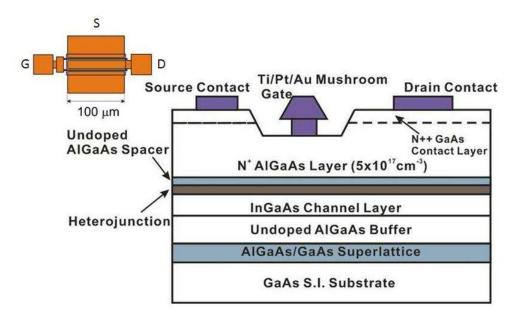

| Figure 4.1 Top and cross-sectional view of the AlGaAs/InGaAs pHEMT                      | 66                  |

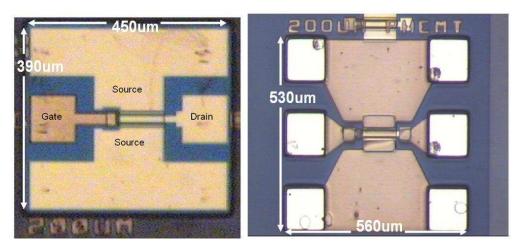

| Figure 4.2 Micrographs of the fabricated pre- (virgin) and post-multilayer-processed    | d                   |

| multilayer pHEMTs.                                                                      | 67                  |

| Figure 4.3 Illustration of the multilayer fabrication process technology [12]           | 67                  |

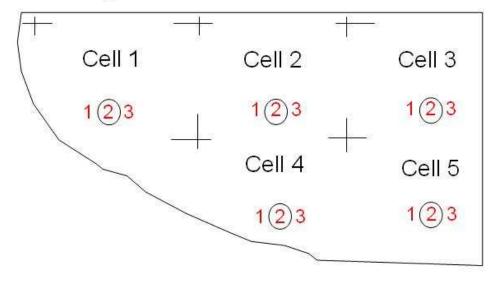

| Figure 4.4 Sketch showing the locations of the chosen five (circled) virgin pHEMTs      | s on                |

| Sample 3                                                                                | 68                  |

| Figure 4.5 Measured transfer characteristics of the five virgin pHEMTs (0.5x200 µm      | m <sup>2</sup> ) at |

| room temperature                                                                        | 69                  |

| Figure 4.6 Measured output characteristics of the five virgin pHEMTs ( $0.5x200\ \mu m$ | <sup>2</sup> ). 70  |

| Figure 4.7 S11, S21 and S22 of the five virgin pHEMTs $(0.5x200  \mu m^2)$              | 71                  |

| Figure 4.8 S12 of the five virgin pHEMTs (0.5x200 µm²)                                  | 71                  |

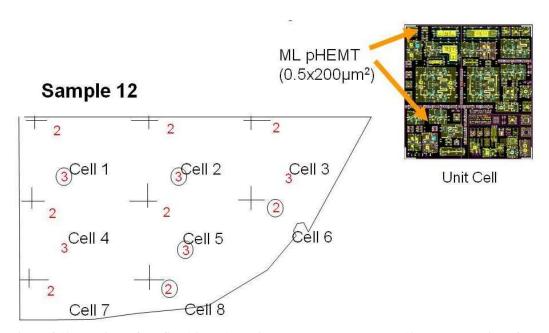

| Figure 4.9 Current and power gains of the five virgin pHEMTs $(0.5x200 \ \mu m^2)$      | 72                  |

| Figure 4.10 Locations of the five (circled) multilayer pHEMTs on sample 12 and th       | e top               |

| view of the unit cell.                                                                  | 73                  |

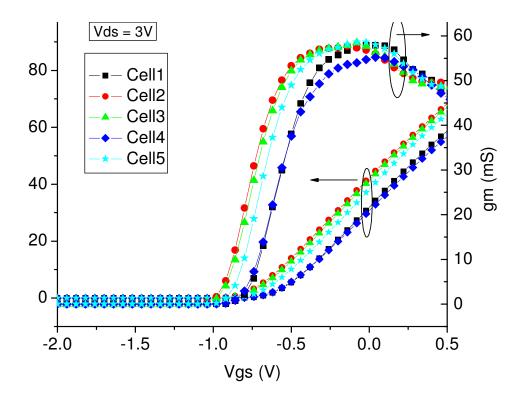

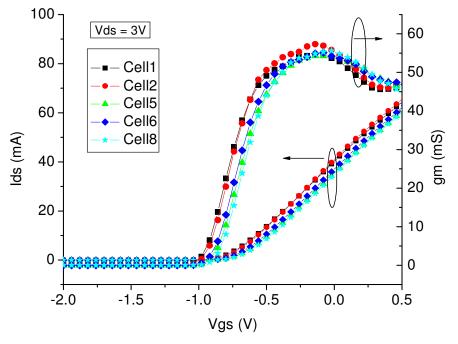

| Figure 4.11 Measured transfer characteristics of the five multilayer pHEMTs (0.5x2      | 200                 |

| μm <sup>2</sup> ) on Sample 12.                                                         | 73                  |

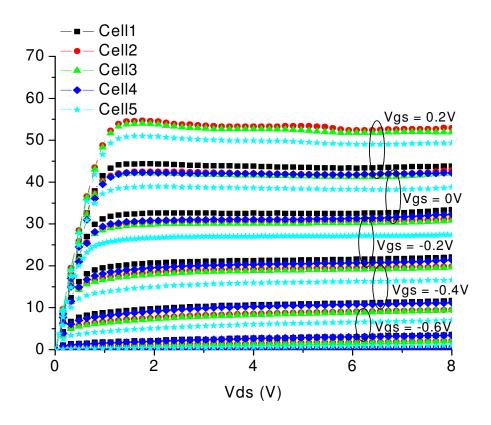

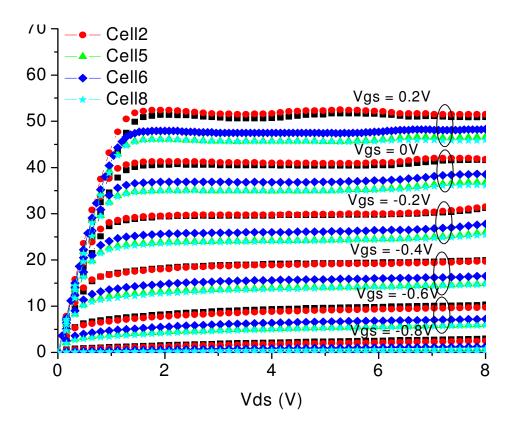

| Figure 4.12 Measured output characteristics of the five multilayer pHEMTs (0.5x20       | )()                 |

| μm <sup>2</sup> ) on Sample 12.                                                         | 74                  |

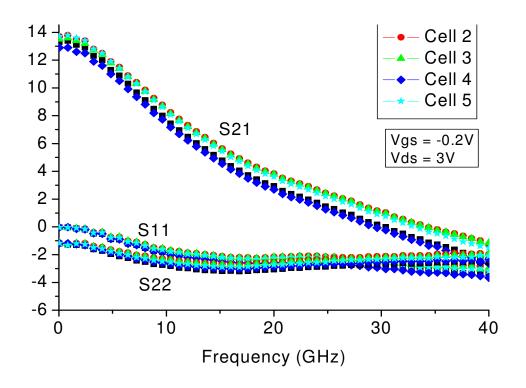

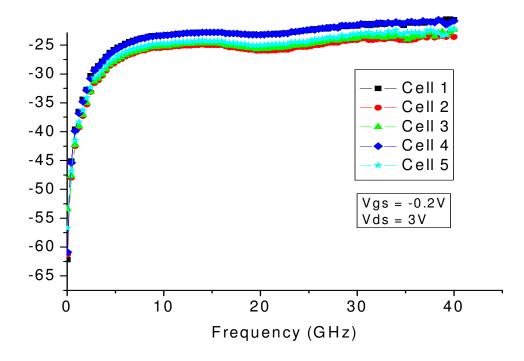

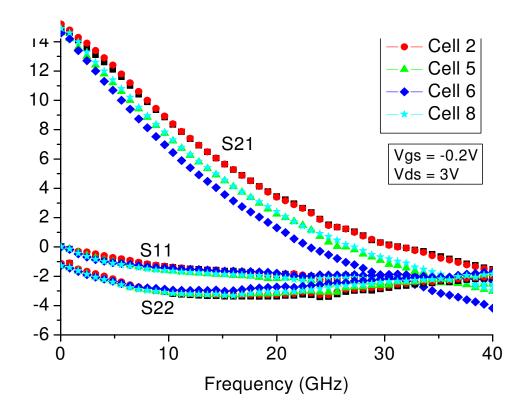

| Figure 4.13 S11, S21 and S22 of the five multilayer pHEMTs $(0.5x200\ \mu m^2)$ on Sample   |

|---------------------------------------------------------------------------------------------|

| 12                                                                                          |

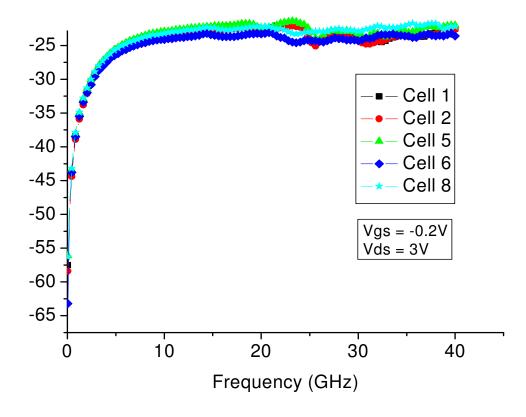

| Figure 4.14 S12 of the five multilayer pHEMTs (0.5x200 µm²) on Sample 1275                  |

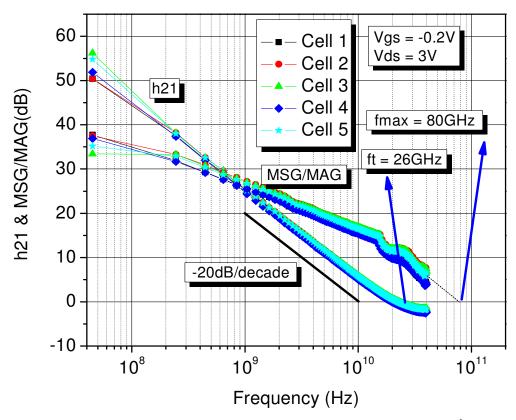

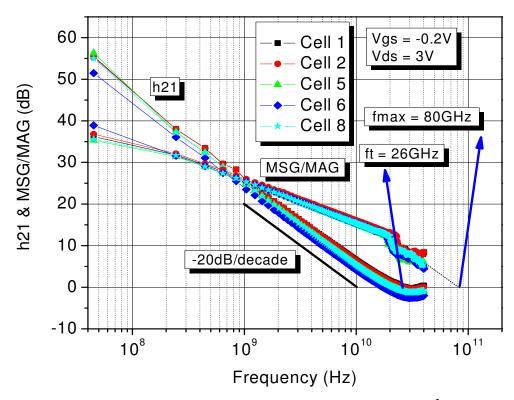

| Figure 4.15 Current and power gains of the five multilayer pHEMTs (0.5x200 μm²) on          |

| Sample 12                                                                                   |

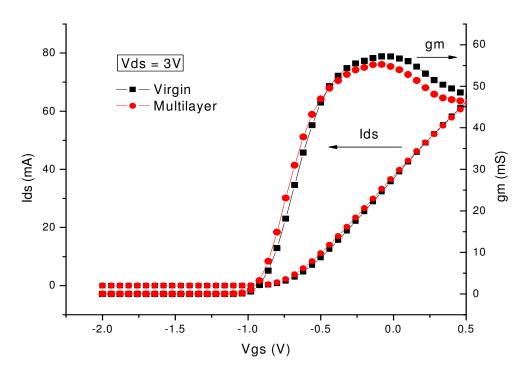

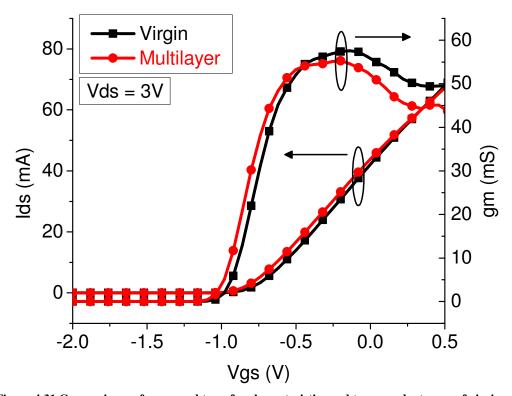

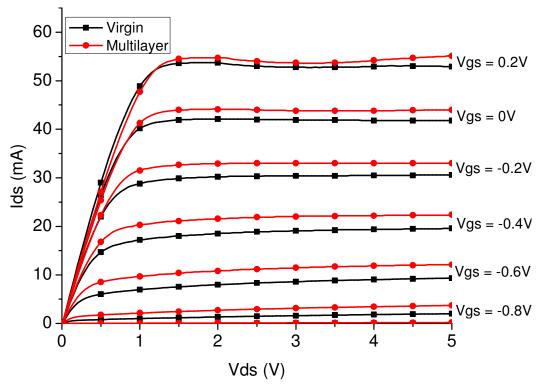

| Figure 4.16 Comparison of measured Ids and gm characteristics between virgin and            |

| multilayer 0.5x200 µm² pHEMTs77                                                             |

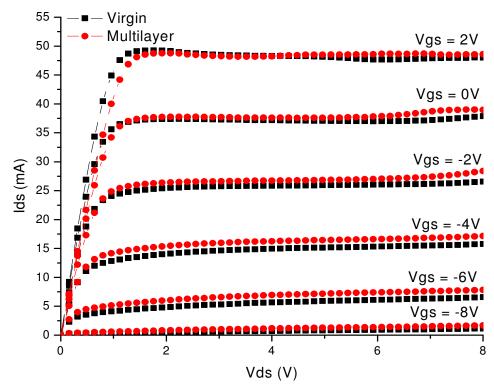

| Figure 4.17 Comparison of output characteristics between virgin and multilayer 0.5x200      |

| μm <sup>2</sup> pHEMTs                                                                      |

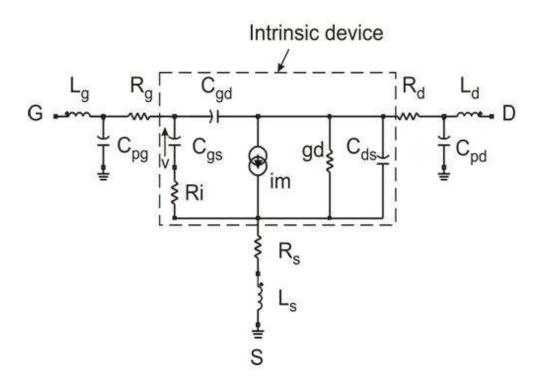

| Figure 4.18 $\Pi$ small-signal equivalent circuit model for pHEMT in common source          |

| configuration [60]80                                                                        |

| Figure 4.19 Flow chart for determining the extrinsic parameters of FETs[60]81               |

| Figure 4.20 Flow chart for determining the intrinsic parameters of FETs [60]85              |

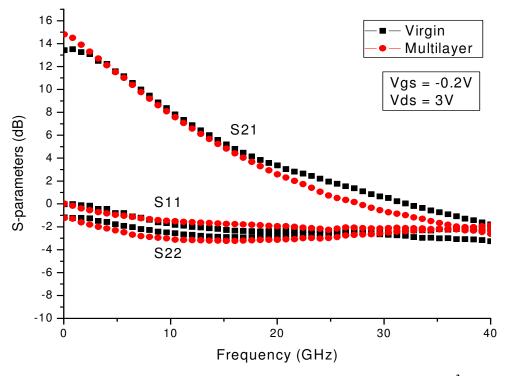

| Figure 4.21 Comparison of S11, S21 and S22 between virgin and multilayer 0.5x200            |

| μm <sup>2</sup> pHEMTs87                                                                    |

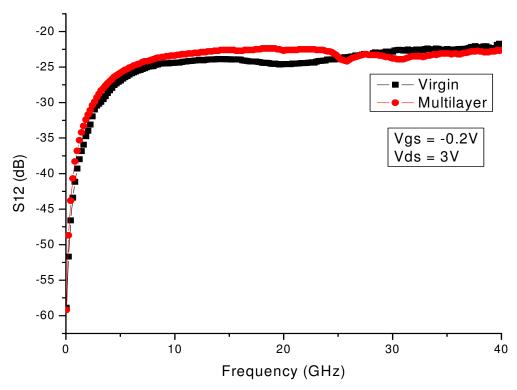

| Figure 4.22 Comparison of S12 between virgin and multilayer 0.5x200 µm <sup>2</sup> pHEMTs. |

|                                                                                             |

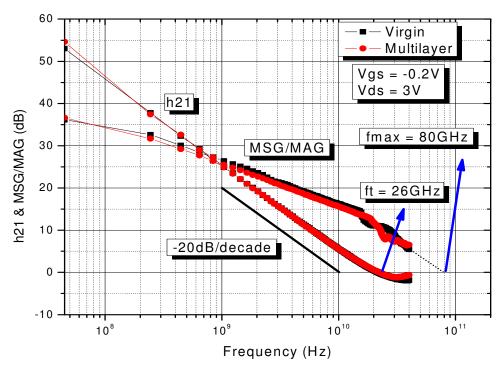

| Figure 4.23 Comparison of current and power gains between virgin and multilayer             |

| 0.5x200 μm <sup>2</sup> pHEMTs88                                                            |

| Figure 4.24 Comparison of measured and modelled S11, S21 and S22 (virgin 0.5x200            |

| μm <sup>2</sup> pHEMT)91                                                                    |

| Figure 4.25 Comparison of measured and modelled S12 (virgin 0.5x200 μm² pHEMT).             |

| 91                                                                                          |

| Figure 4.26 Comparisons of measured and modelled current and power gains (virgin            |

| 0.5x200 μm <sup>2</sup> pHEMT)92                                                            |

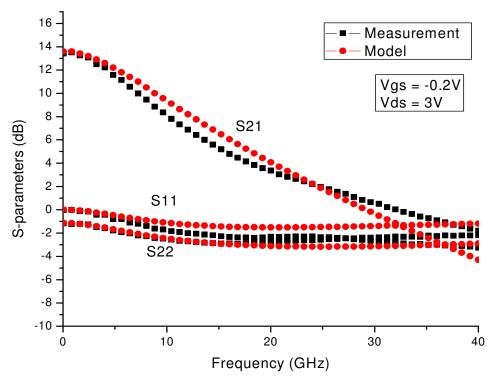

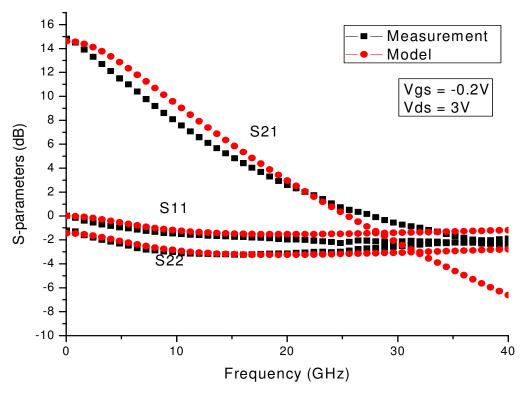

| Figure 4.27 Comparison of measured and modelled S11, S21 and S22 (multilayer                |

| 0.5x200 μm <sup>2</sup> pHEMT)96                                                            |

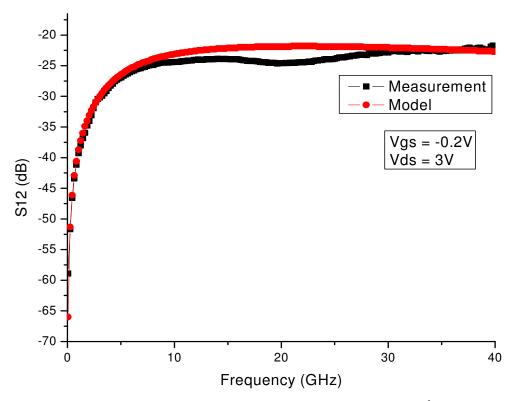

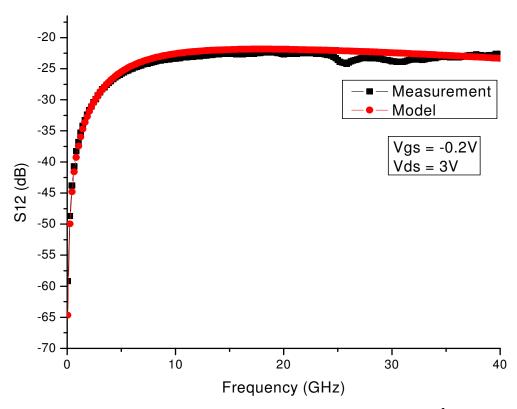

| Figure 4.28 Comparison measured and modelled of S12 (multilayer 0.5x200 μm <sup>2</sup>     |

| pHEMT)96                                                                                    |

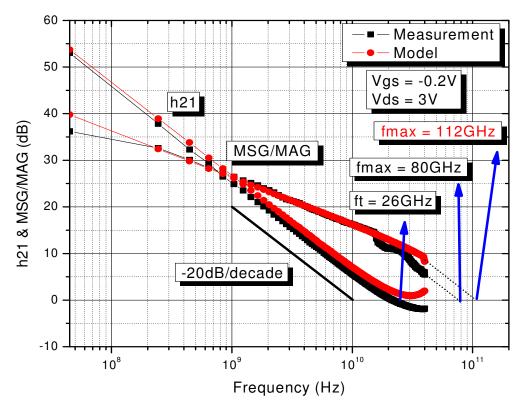

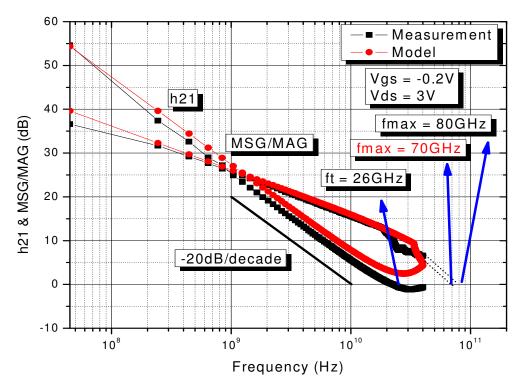

| Figure 4.29 Comparisons of measured and modelled current and power gains (multilayer        |

| 0.5x200 μm <sup>2</sup> pHEMT)97                                                            |

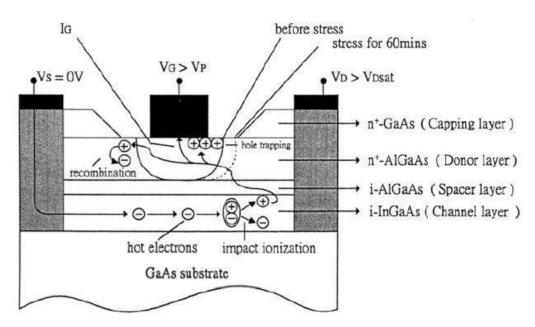

| Figure 4.30 Hot electrons and impact ionization effects [78]                                |

| Figure 4.31 Comparisons of measured transfer characteristics and transconductances of       |

| virgin and multilayer pHEMTs at room temperature101                                         |

| Figure 4.32 Comparisons of measured output characteristics of virgin and mult                                        | ilayer                |

|----------------------------------------------------------------------------------------------------------------------|-----------------------|

| 0.5x200 µm <sup>2</sup> pHEMTs at room temperature                                                                   | 102                   |

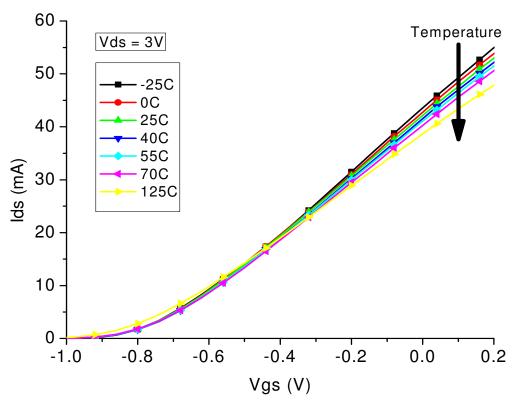

| Figure 4.33 Temperature dependent transfer characteristics of the virgin 0.5x20                                      | $00  \mu \text{m}^2$  |

| pHEMTs ( $V_{ds} = 3V$ ).                                                                                            | 103                   |

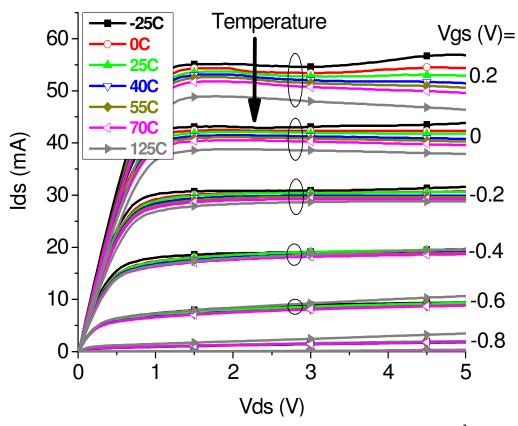

| Figure 4.34 Temperature dependent of output characteristics of the virgin 0.5x2                                      | $200  \mu \text{m}^2$ |

| pHEMTs                                                                                                               | 104                   |

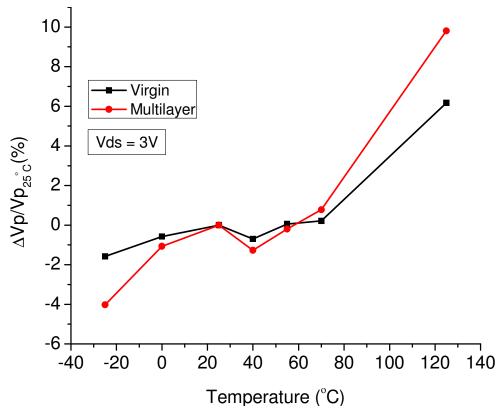

| Figure 4.35 Comparison of pinch-off voltage shift with respect to the temperate                                      | ure                   |

| between virgin and multilayer 0.5x200 $\mu m^2$ pHEMTs ( $V_{ds} = 3V$ )                                             | 105                   |

| Figure 4.36 Comparison of degradation of transconductance with respect to the                                        | <b>;</b>              |

| temperature between virgin and multilayer $0.5x200 \mu m^2$ pHEMTs ( $V_{ds} = 3V$ ; $V_{ds} = 3V$ )                 | $V_{\rm gs} = -$      |

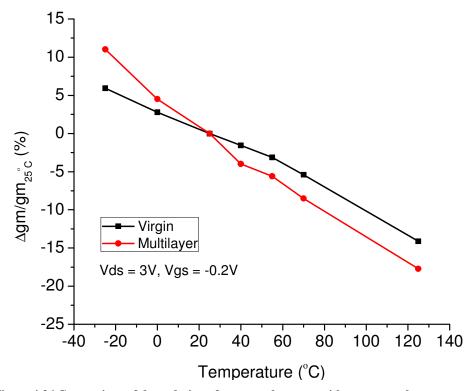

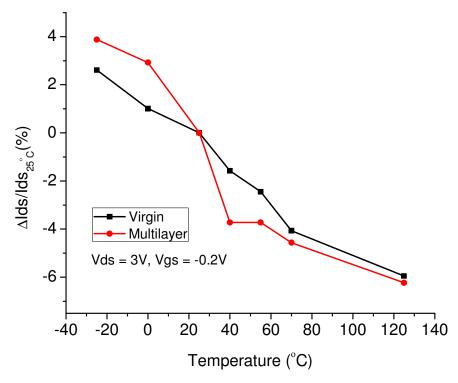

| 0.2V)                                                                                                                | 106                   |

| Figure 4.37 Comparison of degradation of output current with respect to the ter                                      | mperature             |

| between virgin and multilayer $0.5x200 \mu m^2$ pHEMTs (Vds = 3V; Vgs = -0.2V)                                       | ) 107                 |

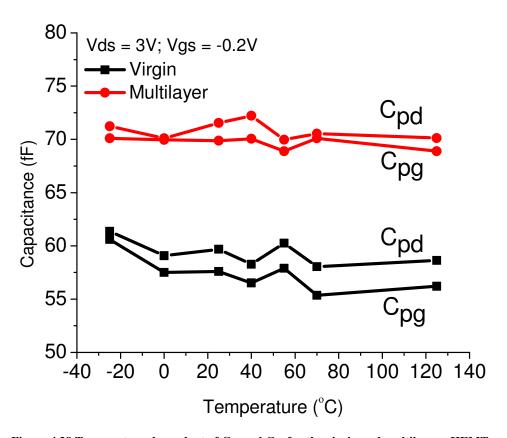

| Figure 4.38 Temperature dependent of $C_{pg}$ and $C_{pd}$ for the virgin and multilaye                              | r                     |

| pHEMTs                                                                                                               | 109                   |

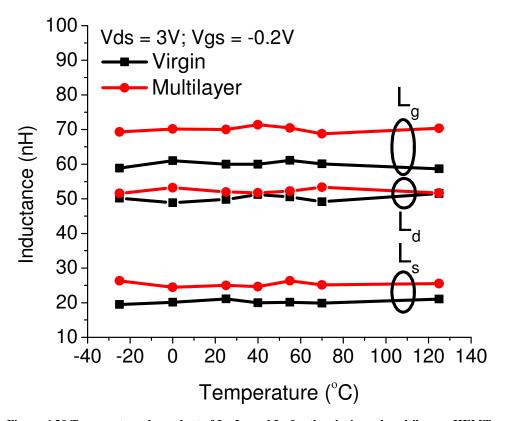

| Figure 4.39 Temperature dependent of $L_s$ , $L_d$ and $L_g$ for the virgin and multilay                             | er                    |

| pHEMTs                                                                                                               | 110                   |

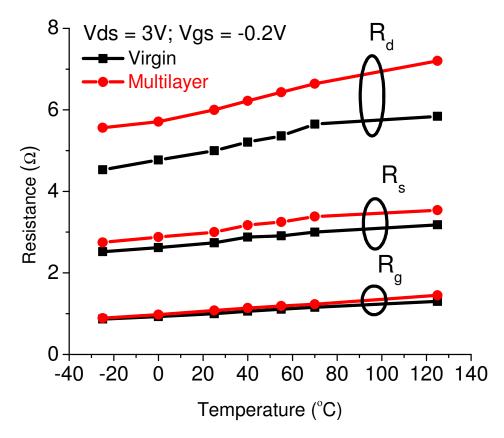

| Figure 4.40 Temperature dependent of R <sub>s</sub> , R <sub>d</sub> and R <sub>g</sub> for the virgin and multilage | yer                   |

| pHEMTs                                                                                                               | 111                   |

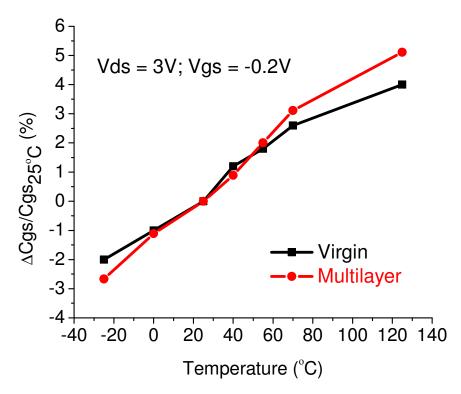

| Figure 4.41 Temperature dependent of C <sub>gs</sub> of the virgin and multilayer pHEMT                              | Ts .                  |

| (normalised to 25°C)                                                                                                 | 112                   |

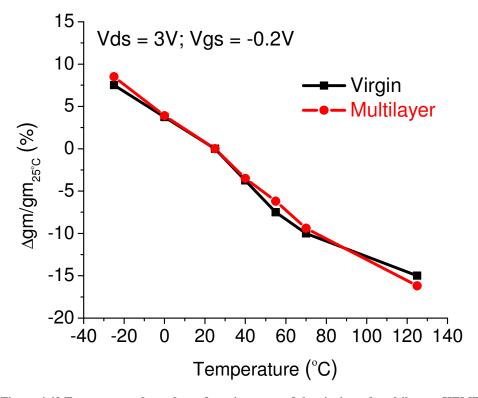

| Figure 4.42 Temperature dependent of maximum g <sub>m</sub> of the virgin and multilayer                             | er                    |

| pHEMTs (normalised to 25°C)                                                                                          | 112                   |

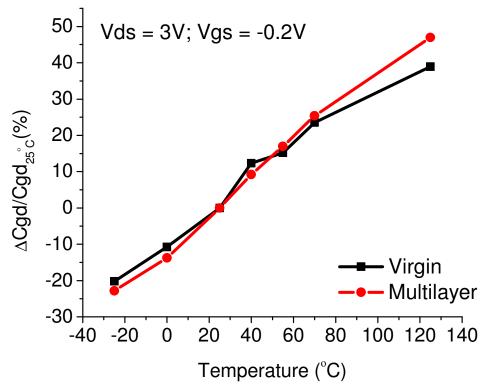

| Figure 4.43 Temperature dependent of $C_{\rm gd}$ of the virgin and multilayer pHEM7                                 | Γs                    |

| (normalised to 25°C)                                                                                                 | 113                   |

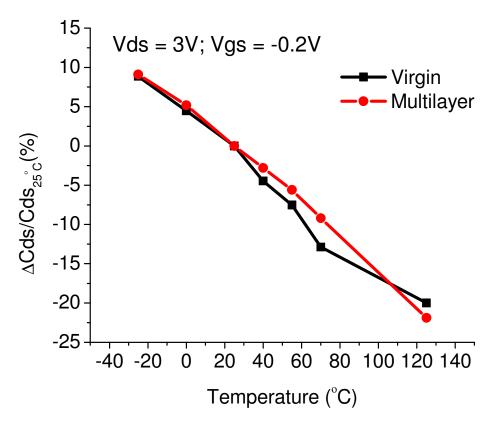

| Figure 4.44 Temperature dependent of $C_{ds}$ of the virgin and multilayer pHEMT                                     | ?s                    |

| (normalised to 25°C)                                                                                                 | 114                   |

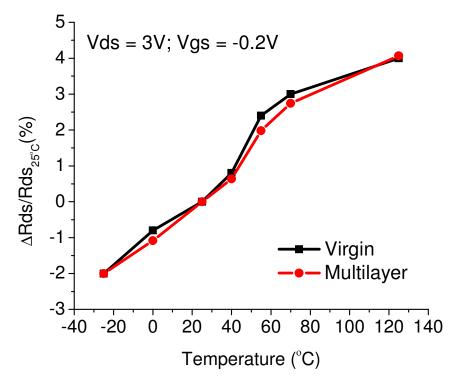

| Figure 4.45 Temperature dependent of $R_{ds}$ of the virgin and multilayer pHEMT                                     | ¬s                    |

| (normalised to 25°C)                                                                                                 | 115                   |

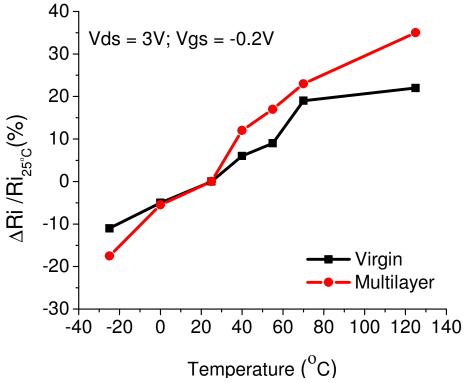

| Figure 4.46 Temperature dependent of R <sub>i</sub> of the virgin and multilayer pHEMTs                              | 3                     |

| (normalised to 25°C).                                                                                                | 115                   |

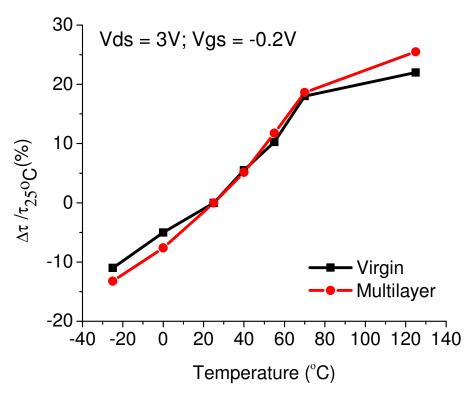

| Figure 4.47 Temperature dependent of $\boldsymbol{\tau}$ of the virgin and multilayer pHEMTs                         |                       |

| (normalised to 25°C).                                                                                                | 116                   |

|                                                                                                                      |                       |

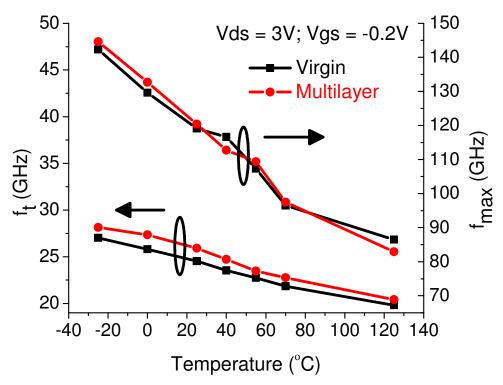

| Figure 4.48 Temperature dependent of $f_t$ and $f_{max}$ of the virgin and multilay | er pHEMTs.   |

|-------------------------------------------------------------------------------------|--------------|

|                                                                                     | 117          |

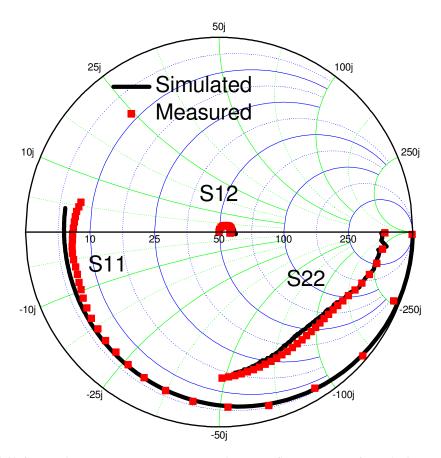

| Figure 4.49 Comparisons between measured and simulated S-parameters o               | f the virgin |

| pHEMT at $125^{\circ}$ C (bias: $V_{gs}$ =-0.2V; $V_{ds}$ =3V)                      | 120          |

## **List of Tables**

| Table 2.1 Electronic and physical properties of GaAs and Silicon [30-32]                | . 24             |

|-----------------------------------------------------------------------------------------|------------------|

| Table 2.2 Advantages and disadvantages of MMIC and hybrid MIC [1]                       | . 26             |

| Table 2.3 Effect of chip size on fabrication cost in 1995 [1]                           | . 26             |

| Table 2.4 Relationships of small-signal parameters to the physical properties of FET    |                  |

| [53]                                                                                    | . 49             |

| Table 3.1 Descriptions of ADS simulation types [72]                                     | . 57             |

| Table 4.1 Extracted small-signal parameter for the virgin 0.5x200 μm <sup>2</sup> pHEMT | . 90             |

| Table 4.2 Extracted small-signal parameters for the multilayer 0.5x200 μm² pHEMT        | . 95             |

| Table 4.3 Temperature coefficients (TCs) for equivalent circuit parameters (ECPs) and   | d f <sub>t</sub> |

| and $f_{max}$ with reference temperature at 0 °C ( $V_{gs} = -0.2V$ ; $V_{ds} = 3V$ )   | 119              |

#### **ABSTRACT**

Rapid advancement in wireless communications over the years has been the driving force for many novel technologies providing compact and low cost solutions. Recent development of multilayer coplanar waveguide (CPW) MMIC technology promises realization of 3D MMIC in which large area-occupying passive components are translated from horizontal into vertical configuration resulting compact structure. The other main advantages of this technology are elimination of via-holes and wafer-thinning giving alternative performance solution, if not better, from the traditional MMIC. In this thesis, thermal and small-signal characteristics of prefabricated AlGaAs/InGaAs pseudomorphic high electron mobility transistors (pHEMTs) on semi-insulating (S.I.) GaAs substrate incorporated in the 3D MMIC technology have been analysed and modelled for the first time. A comprehensive small-signal parameter extraction procedure has been successfully developed which automatically determines the device small-signal parameters directly from the measured S-parameters.

The developed procedure is unique since it provides a great deal of data on measured devices over a wide bias, temperature and frequency range for future incorporation of different active devices for the 3D MMIC technology and provides a first hand knowledge of how the multilayer structure will affect the performance of pre-fabricated pHEMTs. The extracted small-signal models of both pre- and post- multilayer processed pHEMTs have been compared and validated to the RF S-parameters measurements. The main focus was drawn upon the temperature dependent model parameters and how the underlying physics of the transistors behave in response to the change of temperature. These novel insights are especially valuable for devices designed specifically for high power applications like power amplifiers where tremendous heat could be generated. The data can also be interpreted as a way to optimise the multilayer structure, for example, alternative material with different properties can be implemented. The governing physics affecting device performance are also modelled and discussed empirically in details through extracted device parameters. These investigations would assist in the development of reliable, efficient and low cost production of future compact 3D multilayer CPW MMICs.

## **DECLARATION**

I declare that no portion of the work referred to in the thesis has been submitted in support of an application for another degree or qualification of this or any other university or other institute of learning.

### **Copyright Statement**

- i. The author of this thesis (including any appendices and/or schedules to this thesis) owns certain copyright or related rights in it (the "Copyright") and s/he has given The University of Manchester certain rights to use such Copyright, including for administrative purposes.

- ii. Copies of this thesis, either in full or in extracts and whether in hard or electronic copy, may be made **only** in accordance with the Copyright, Designs and Patents Act 1988 (as amended) and regulations issued under it or, where appropriate, in accordance with licensing agreements which the University has from time to time. This page must form part of any such copies made.

- iii. The ownership of certain Copyright, patents, designs, trade marks and other intellectual property (the "Intellectual Property") and any reproductions of copyright works in the thesis, for example graphs and tables ("Reproductions"), which may be described in this thesis, may not be owned by the author and may be owned by third parties. Such Intellectual Property and Reproductions cannot and must not be made available for use without the prior written permission of the owner(s) of the relevant Intellectual Property and/or Reproductions.

- iv. Further information on the conditions under which disclosure, publication and commercialisation of this thesis, the Copyright and any Intellectual Property and/or Reproductions described in it may take place is available in the ΙP University Policy (see http://www.campus.manchester.ac.uk/medialibrary/policies/intellectualproperty.pdf), in any relevant Thesis restriction declarations deposited in the The University Library, University Library's regulations (see http://www.manchester.ac.uk/library/aboutus/regulations) and in The University's policy on presentation of Theses.

## Acknowledgement

I would like to express my greatest appreciation to my supervisor, Professor Ali A. Rezazadeh. He has given me tremendous help and guidance in the course of this work. He is very supportive and has been a great mentor to me.

I am grateful for the help and guidance provided by Prof. Andrew Gibson, Dr. Tuyen Vo and Dr. Suba Subramaniam, their ever helpfulness always warm me. I also deeply appreciate the help and companionship provided by my fellow colleague, Dr. Sun Qing, Dr. Yuan Junyi, Dr. Hasan Khan and soon to be Dr. Lu Jiaping throughout the years. Special thanks go to Dr. Yuan, who is always there providing tremendous help and insightful advice.

I would like to thank my lovely family. I am thankful to my parents, Mr. Michael Tan Kee Yow and Ms. See Siew Kean, my brother, David and my sister, Janice, for their constant support and love without any reservation. I would like to thank my brother and sister especially for taking care of our parents when I have been not readily available, being overseas. I am also grateful to my parents-in-law, Mr. See Ching Oo and Ms. Chuah Saw Hoon. Thanks to Dr. Lee Chern Yang, his wife Dr. Low and my mentor, Dr. Mihai Rotaru. Last but not least, my greatest thanks go to my wife, Yea Huey. I cannot stress enough how lovely and supportive she has been and always will be. She has always been there when I was down. Without her, this project would not have been possible.

This work is dedicated to my lovely wife

See Yea Huey

#### **List of Publications From This Work**

- [1] **Jimmy P. H. Tan**, J. Yuan, A. A. Rezazadeh, and Q. Sun, "Temperature Dependent Small-Signal Model Parameters Analysis of AlGaAs/InGaAs pHEMTs in Mulitlayer 3D MMIC Technology," Proceedings of European Microwave Integrated Circuit (EuMIC) Conference, Paris, September 2010, pp. 378-381.

- [2] Q. Sun, V. T. Vo, R. A. Davies, A. A. Rezazadeh and Jimmy P. H. Tan, "Miniaturized Multilayer CPW pHEMT Amplifiers," Proceedings of European Microwave Integrated Circuit (EuMIC) Conference, Amsterdam, September 2008, pp. 44-47.

- [3] **Jimmy P. H. Tan** and Ali A. Rezazadeh, "Small-Signal Characterization of pHEMTs in Multilayer CPW MMIC Technology using IC-CAP," UK Semiconductors 2008, Sheffield, June 2008.

- [4] **Jimmy P. H. Tan**, J. Yuan, A. Rezazadeh and Q. Sun, "Thermal Effects on AlGaAs/InGaAs pHEMTs in Multilayer 3D MMIC Technology," to be submitted for journal publication.

## **Chapter 1** Introduction

#### 1.1 Introduction

In contrast to hybrid microwave integrated circuits (MICs), monolithic microwave integrated circuits (MMICs) technology has the advantages of small size, high reliability, low cost and the capability of large volume production. MMIC is an integrated circuit that incorporates all the circuit components such as resistors, inductors, capacitors, transistors, diodes on a single semiconductor chip [1].

MMIC technology has seen much progress and has been maturing for the past few decades. Recent development of multilayer coplanar waveguide (CPW) MMIC has shown promising features of being capable of eliminating the needs of via-holes and substrate-thinning allowing lower production cost to be achieved [2]. Unlike the microstrip design, in the CPW, the substrate does not need to be thinned down which is the most disadvantage of making the chip fragile [2-4]. In addition, realization of 3D MMIC is possible in the CPW-based MMICs using multilayer technology which consists of thin layer of dielectric and metal conductors. In this way, large area occupying passive components are translated from horizontal to vertical configuration resulting compact designs with reduced cost of manufacturing [5-7].

There have been several reports in the building up of the components library for this multilayer CPW MMIC technology [8-16]. But accurate characterisations of various components are necessary in order to produce a reliable library for future 3D MMIC designs. The research group at Manchester has been successful in demonstrating CPW based 3D MMICs incorporating AlGaAs/InGaAs pseudomorphic high electron mobility transistors (pHEMT), fabricated on thick GaAs substrate, and a multilayer technology consisting of thin polyimide as dielectric layers and Ti/Au as metal layers. Although the initial work has been realised and produced some good results, a great deal of research were required to characterise accurately the pHEMTs used in the multilayer technology. In this work, small-signal characterisation and modelling of pHEMTs in this multilayer CPW MMIC environment have been carried out. Another important issue is that the

thermal charachterisation of pHEMTs used in the multilayer technology needs to be carefully assessed. This is because in the 3D MMICs, thick GaAs substrates (~0.6mm) has been used and since thermal conductivity of GaAs is rather poor (~45W/m°C) as compared to Si (~150W/m°C), transistors can experience a great deal of heat and therefore it is essential to investigate their thermal characterisations.

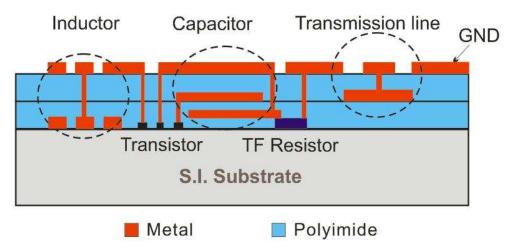

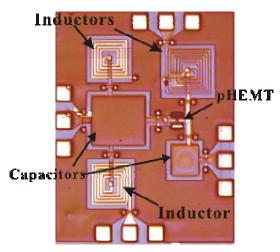

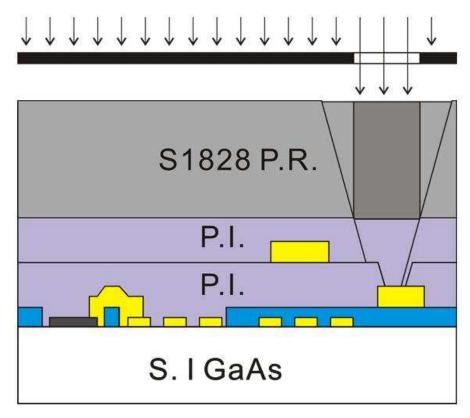

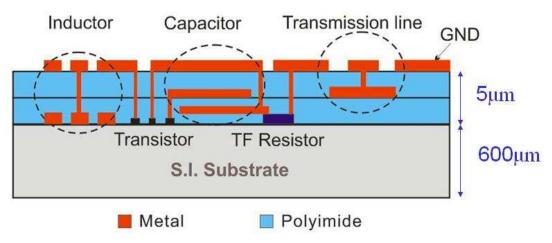

The multilayer CPW MMIC under investigation has been developed by The Electromagnetics Centre at The University of Manchester with the active devices, AlGaAs/InGaAs pHEMTs, provided by the foundry, Filtronic Compound Semiconductors. A conceptual drawing of this technology can be seen in Figure 1.1. Three metal layers are stacked in between of two dielectric layers, various circuit components are then carefully designed realising 3D MMIC.

Figure 1.1 Illustration of the multilayer processing [12].

Device modelling work has always been an ongoing project, with many state-of-the-art novel devices being designed every now and then. The establishment of an empirical equivalent circuit model forms an integral part of characterising of a device. It not only provides insights to the underlying physics of the device with the corresponding circuit parameters, but also offers a predictable performance which circuit designers can optimise when incorporating the device in designing amplifiers, switches, oscillators and other useful circuits. Analyses and optimisations such as gain, noise and stability can also be carried out with the aid of a circuit model.

In this work, a small-signal pHEMT model has been developed. Traditionally, small-signal field effect transistor (FET) models and their circuit parameters values were determined by optimization of fit to measured scattering parameters (S-parameters). However, this technique suffers from the disadvantages such as time consuming, less accurate and lack of physical significance. As a solution, direct parameter extraction method, which is fast and accurate, was introduced and is therefore demonstrated in this thesis. The procedure has also been made semi-automated using Agilent's IC-CAP.

Once the equivalent circuit parameters (ECPs) are accounted for, insights of the underlying physics of the device could be achieved by careful analyses. In order to investigate the effect of the multilayer processing, pre- and post-multilayer-processed AlGaAs/InGaAs pHEMTs are compared with their corresponding ECPs.

Thermal effects, being one of the major issues for power-related applications, are one of the key research areas in this work. This is because the AlGaAs/InGaAs pHEMTs that are multilayer-processed in this work are suitable to be designed as power amplifiers. Enormous heat could be generated during the operation and hence to know how the change of temperature would affect the characteristics and performance of the AlGaAs/InGaAs pHEMTs is of the major concern.

### 1.2 Key Objectives

The main aims of this research work are:

- To carry out a review of published theoretical and experimental reports on device modeling, placing special emphasis on AlGaAs/InGaAs pHEMTs.

- To investigate the uniformity of pre- and post-multilayer-processed AlGaAs/InGaAs pHEMTs in 3D MMIC environment.

- To establish suitable physics based compact expressions for the transport of the electrons in a pHEMT which in turn forms the circuit parameters of a physically intuitive pi-model.

- To develop a small-signal model parameter extraction algorithm. Direct parameter extraction is to be used, where the extraction is made directly from the measured DC and RF data without requirement of iterations or optimisations.

- To extend the small-signal model development to both pre- and post-multilayerprocessed AlGaAs/InGaAs pHEMTs and validate the models to the on wafer Sparameters measurements.

- To develop temperature dependent small-signal models for the pre- and postmultilayer-processed AlGaAs/InGaAs pHEMTs.

- To establish linear temperature dependent expressions for each of the equivalent circuit model parameters and observe the temperature coefficients between preand post-multilayer-processed AlGaAs/InGaAs pHEMTs.

- To analyse and attain knowledge of the underlying physics governing the electrons transport in various temperature and explore ways of optimising the performance.

#### 1.3 Overview of The Thesis

This thesis is divided into the following chapters:

In Chapter 1, general overview of the research work is presented with introduction of the 3D MMIC technology. Motivation and key objectives are highlighted. An outline of the thesis is also given.

Chapter 2 provides background reviews on the MMIC technology, advantages and disadvantages are discussed. III-V semiconductors are reviewed next, with various designs and technologies presented including applications. Following, principles of pHEMT are reviewed placing emphasis on the development of small-signal model. Lastly, thermal effects are discussed with its implications on the performance explained.

The experimental set-up is presented in Chapter 3. Software tools that are used during the course of this work are introduced. Procedures and how to apply them in order to achieve good results are discussed and explained. On-wafer DC and RF measurements are shown and temperature control set-up is given.

Chapter 4 is the main results chapters providing analyses and discussions of the obtained data.

The device structure is first presented in Section 4.1. The top and cross-sectional views of the AlGaAs/InGaAs pHEMTs provide information of fundamental specifications. Layouts of the pre- and post-multilayer-processed pHEMTs are shown. Incorporations of the AlGaAs/InGaAs pHEMTs to the 3D MMIC are presented showing interconnects realising various circuit components.

Following that, Section 4.2 investigates the uniformity of both the pre- (virgin) and post-multialyer-processed (multilayer) pHEMTs and observations are shown. Section 4.3 of Chapter 4 is about the modelling of pHEMTs. It first shows the DC characteristics of the multilayer AlGaAs/InGaAs pHEMTs. After that, direct on-wafer RF S-parameters measurements are shown. Equivalent circuit model for the pHEMTs is adopted and procedure of the extractions for each of the circuit parameters are presented and carried out. The procedure can be roughly divided into cold and hot bias measurements with careful bias points selected and measured. In the last part of Section 4.3, the developed small-signal models for both the virgin and multilayer AlGaAs/InGaAs pHEMTs are validated and compared to the measurements.

Section 4.4 of Chapter 4 moves on to explore the DC temperature dependent modelling of the pHEMTs, the change of DC characteristics of the pHEMTs to the change of temperature is observed and explained with the thermal effect on the electron transport physics. In Section 4.5, the concept of the development of small-signal model is extended to temperature dependent small-signal model for both virgin and multilayer pHEMTs. Circuit parameters are divided into two categories, extrinsic and intrinsic, and analysed. Each of the circuit parameters is expressed in a linear temperature-dependent equation giving a temperature coefficient. The implications of the temperature

coefficients are discussed and both virgin and multilayer AlGaAs/InGaAs pHEMTs are compared.

And finally, Chapter 5 presents the conclusion and the future works. Key observations and results are highlighted. Potential future works are suggested and discussed.

## **Chapter 2 Background Review**

#### 2.1 MMIC Technology

#### 2.1.1 History of GaAs MMIC Technology

In 1959, first concept of integrated circuit (IC) was brought forward by Kilby of Texas Instruments [17]. Rapid development was started in early 1960s by Moll following several publications on the integrated circuit applications [18-21]. In 1964, first Silicon based monolithic microwave integrated circuit (MMIC) was invented by Ruegg [22]. It was an analogue FET switch as presented in Figure 2.1. However, like all pioneering inventions, it suffered from poor switching speed due to the low mobility of Silicon. MMIC proceeded to further improvement and in 1960s, with maturing development of microstrip lines reported by Wheeler [23-25], two publications were made [26-27] and widely recognised as the first original realisation of Gallium Arsenide (GaAs) based MMIC technology. Figure 2.2 shows the Schottky diode circuit reported in the papers.

Figure 2.1 Micrograph of the analogue FET switch based on Silicon MMIC technology [22].

Figure 2.2 Micrograph of the schottky barrier diode for use in 94GHz mixer circuit [27].

In 1976, Pengelly and Turner, who were widely acknowledged as the inventor of MMICs, reported a GaAs FET amplifier [28]. This is thus known as the first practical MMIC. This single-stage amplifier was capable of 5dB gain at X-band with 1µm optically-written gates. Figure 2.3 shows the picture of this amplifier. No DC block was used and the lumped element matching network was designed using computer optimisation. This invention spurred a new interest in MMIC and many great developments and associated technologies were achieved. MMIC with better performance and higher operating frequency is sought after ever since.

Figure 2.3 Micrograph of the first monolithic amplifier [28].

For realisation of active devices, Silicon is one of the most mature and popular semiconductor materials. It has gone through intensive research for several decades and achieved great maturity in terms of fabrication technology. The main attraction of Silicon as the building block of integrated circuits is its low processing cost. However, limitations of Silicon based active devices started to shown at high operation frequency, especially after X-band. The key issue is to do with the low electron mobility of the material property.

There is where GaAs was first proposed in late 1970s as an alternative material to make up for the tasks for high frequency applications [29]. GaAs was introduced with some superior electronic properties that Silicon is lacking. A comparison of the physical and electronic properties of GaAs and Silicon can be seen in Table 2.1. GaAs has an intrinsic electron mobility of 8500 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> at 300K, five time greater than the 1500 of Silicon. On the other hand, the saturation velocity of GaAs is much higher than that of Silicon. The result is that GaAs based circuit can be operated with a lower voltage and perform faster than the Silicon counterpart. Also, it means with the same doping density, GaAs

based devices will have lower resistivity. Low resistivity is especially important for low noise applications as noise is normally created as thermal noise in the channel resistance and the gate, drain and source contact resistance. Therefore, a lower resistivity found in GaAs material compared to Silicon will generate a lower power level of noise. This is also why GaAs is attractive to be designed as low noise amplifier at microwave frequency. Furthermore, as a substrate, as can be seen in the Table 2.1, GaAs exhibits resistivity of  $10^9 \,\Omega$ ·cm while Silicon has merely  $10^3 \,\Omega$ ·cm. It makes GaAs a much better substrate which introduces lower substrate associated losses [30].

Table 2.1 Electronic and physical properties of GaAs and Silicon [30-32]

| Properties                                                                           | Si         | GaAs         |

|--------------------------------------------------------------------------------------|------------|--------------|

| Intrinsic Electron Mobility at 300K, cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> | 1500       | 8500         |

| Electron Saturation velocity, cms <sup>-1</sup>                                      | $9x10^{6}$ | $1.3x10^{7}$ |

| Intrinsic Hole Mobility at 300K, cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup>     | 450        | 400          |

| Thermal conductivity at 300K, Wcm <sup>-1</sup> K <sup>-1</sup>                      | 1.5        | 0.46         |

| Dielectric constant                                                                  | 11.9       | 12.9         |

| Substrate (intrinsic) resistivity at 300K, Ω·cm                                      | $10^{3}$   | $3.7x10^8$   |

| Band gap at 300K, eV                                                                 | 1.12       | 1.424        |

Unfortunately, one of the shortcomings of GaAs is that it has a lower thermal conductivity, 0.46 Wcm<sup>-1</sup>K<sup>-1</sup>, compared to Silicon's 1.5 Wcm<sup>-1</sup>K<sup>-1</sup>. It means that GaAs has poorer heat handling capability and more susceptible to adverse heat effects [32]. That is why thinning process is introduced for GaAs based devices to reduce the thermal resistance. This thinning process however introduces additional processing cost and time and results in a fragile wafer. In contrast, Silicon, the second most abundant element within the Earth's crust, is a very low cost material. It is therefore, GaAs based active devices are almost always more expensive compared to Silicon.

Hole mobility of GaAs is much lower than its electron mobility, compared to Silicon. In Silicon, the hole and electron mobilities are comparable and that is why complementary metal-oxide-semiconductor (CMOS) is possible. Therefore, there is yet a feasible CMOS equivalent technology in GaAs material due to the fact that p-type GaAs devices will perform much slower than n-type GaAs devices [32].

#### 2.1.2 Advantages and Disadvantages of MMICs

Traditional microwave hybrid integrated circuit (MIC) consists of wire bonding and other surface mounted discrete components. Soldering and conductive epoxy could also be found to bond on-chip and off-chip components on a single substrate. In contrast, monolithic microwave integrated circuit (MMIC) is a microwave circuit where all active and passive components are fabricated together during the process on a single semiconductor substrate [1].

Many unwanted losses could be introduced in MIC, such as the parasitics associated with the wiring and solders. During the assembly, use of various interconnects could result in many undesirable coupling or interference that could seriously affect the target performance of the circuit.

This is where MMIC technology is more superior than hybrid MIC for there is no need for any kind of wire bonding, soldering and gluing. Parasitics are kept at the minimum, unwanted losses would then be minimised. Better performance at high frequency can thus be achieved. A table comparing the advantages and disadvantages of both MMIC and MIC is presented in Table 2.2.

Table 2.2 Advantages and disadvantages of MMIC and hybrid MIC [1].

|                                                   | MMIC                                                                                                       | Hybrid MIC                                                                                 |

|---------------------------------------------------|------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|

| Cost                                              | Cheap in large quantities<br>Cheap for complicated circuits with<br>large number of components             | Cheap for simple circuits and with automated assembly                                      |

| Choice of components                              | Limited choice of components                                                                               | Vast selection of components                                                               |

| Parasitic                                         | Less unwanted parasitic Can be controlled                                                                  | More unwanted parasitic from bond pads/bond wires Cannot be controlled                     |

| Performance                                       | Good broadband performance                                                                                 | Limited bandwidth performance                                                              |

| Frequency of operation                            | Good performances to well over 100 GHz                                                                     | Very hard to realise above 30 GHz                                                          |

| Assembly work                                     | Minimal                                                                                                    | Can be difficult and time-<br>consuming to assemble                                        |

| Reproducibility                                   | Very good                                                                                                  | Poor                                                                                       |

| Reliability                                       | Very good                                                                                                  | Adequate                                                                                   |

| Size, weight and layout area                      | Very small and light in general Must miniaturise area as much as possible to stay commercially competitive | Larger and heavier than MMICs Less pressure to miniaturise layout as substrate is low cost |

| Turnaround and post-<br>fabrication modifications | Typically 3-6 months Cannot make any changes to the design after fabrication                               | Typically a few days Possible to tune after fabrication                                    |

| Investment required                               | Very expensive to start up                                                                                 | Little investment required to start up                                                     |

The main attractiveness of MMIC lies in the fact of their excellent reproductivity at large quantity in a relatively cheaper cost. A table showing the approximated chip fabrication cost in 1995 with respect to chip size is shown in Table 2.3. It was a high yield MESFET process using ion implantation. As can be seen in the table, smaller chip size is attractive due to a more compact structure and at the same time lower production cost. An example of a single stage MMIC amplifier is shown in Figure 2.4.

Table 2.3 Effect of chip size on fabrication cost in 1995 [1].

| Chip size(mm <sup>2</sup> ) | Yields (%) | working circuits per 3 inch wafer | Cost of single chip<br>at \$4000 per<br>wafer(\$) |

|-----------------------------|------------|-----------------------------------|---------------------------------------------------|

| 1 X 1                       | 80         | 3600                              | 1.1                                               |

| 2 X 2                       | 70         | 800                               | 5                                                 |

| 5 X 5                       | 45         | 80                                | 50                                                |

| 7 X 7                       | 30         | 25                                | 160                                               |

| 10 X 10                     | 20         | 9                                 | 440                                               |

Figure 2.4 Micrograph of a planar CPW amplifier using MMIC technology [16].

#### 2.1.3 Multilayer Technology and Coplanar Waveguide

Microstrip has been the most popular configuration found in MMIC technology for the past few decades. In microstrip technology, a conductive ground plane is needed at the bottom of the substrate. Therefore, vias are needed to be constructed. An illustration of this can be seen in Figure 2.5. As vias can introduce unwanted losses to the circuit, in order to keep these to the minimum, substrate thinning is required. Unfortunately, this would introduce additional cost during the fabrication process. A thinned down wafer also suffers from the fragility and is difficult to handle.

Figure 2.5 Cross-sectional view of a Microstrip type MMIC with via holes.

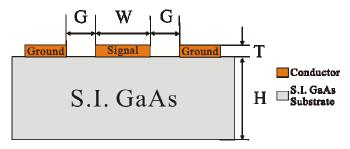

Therefore, alternative configuration is sought after and coplanar waveguide (CPW) technology has arisen as the possible solution. CPW is first invented by Wen [2]. A cross sectional view of a typical CPW structure is presented in Figure 2.6, where G is the gap width between the signal and ground conductors, W is the signal trace width and T and H are the metal and substrate thickness respectively. No via is needed as can be seen and thus parasitics associated with the vias are eliminated. Production cost can also be driven down as no vias construction and wafer thinning process are required.

Figure 2.6 Cross-sectional view of a typical CPW MMIC structure.

For a conventional MMIC like the one found in Figure 2.4, the most area-occupying components are the passives. Spiral inductors and capacitors are both huge in size compared to the active devices. As the cost for a given size wafer is more or less fixed, much of the cost will be on the large size passives. A 3D multilayer CPW MMIC technology is thus proposed and developed. In this technology, minimised cost could be achieved as the passives are constructed in layers, translating the planar components into 3D structure. A much more compact size of the wafer could then be obtained. Many miniatured components and circuits have been reported since late 1980s [33-48].

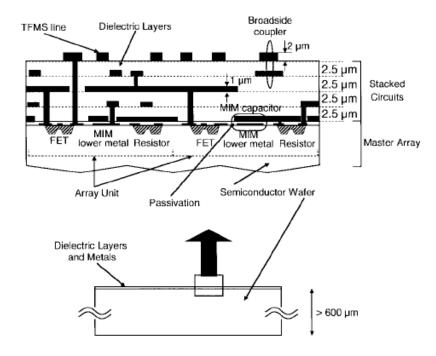

An illustration of the 3D multilayer CPW MMIC is presented in Figure 2.7. As can be observed, the passive components, such as resistors, capacitors and inductors are moved from their conventional planar to vertical plane with respect to the wafer. Layers of dielectrics and metal conductors are fabricated in the multilayer process as well realising required functions. Interconnects are made in the form of via holes.

3D multilayer CPW MMIC has the advantages of compact size, minimised coupling and a great flexibility in layout designs. Compactness is achieved as mentioned before most of the are-occupying components are now translated into vertical direction. Unwanted coupling between nearby components found in conventional CPW MMIC can be made minimum after a much further separations made possible in 3D multilayer CPW MMIC. Also, compared to MMIC in microstrip configuration, CPW MMIC with the ground on the same plane as the signal traces, separating adjacent components, unwanted crosstalks could be minimised.

Figure 2.7 Basic structure of a multilayer MMIC [49].

There is however a potential disadvantage of 3D multilayer CPW structure. All this layers stacking could make the generated heat during the operation difficult to be dissipated. The thick substrate would make the problem harder and reduce the heat dissipation efficiency. This is especially noteworthy as GaAs has much worse thermal conductivity compared to Silicon. Hence, a comprehensive thermal characterisation in this technology is required.

#### 2.1.4 Polyimide as Dielectric in Multilayer Structure

Polyimide has been chosen to be used as the dielectric in the multilayer structure. It can serve firstly for the purpose of supporting and insulating layers of conductors in the 3D MMIC designs and also secondly of planarising and passivating the surface of MMICs.

Careful designing process has been carried out investigating the thickness effect of the polyimide in 3D MMIC. It has been built with 2 layers of about 2.5 microns during the fabrication. This thickness was chosen to ensure most of the electric flux would be fallen within the polyimide. With a much lower dielectric constant of about 3.7 in comparison to GaAs of about 12.9, various passive components and transmission lines could be

designed. This is especially the case for lower values of MIM capacitors. Also, in order to design high impedance transmission lines, according to the fundamental definition of characteristic impedance of CPW transmission lines, the ratio of inductance to capacitance has to be kept as high as possible. It is therefore, when a lower dielectric constant polyimide is placed underneath the CPW transmission lines in compared to GaAs substrate, higher impedance could be achieved. Dissipation loss of the transmission lines could also be minimised with a material of lower dielectric constant. The accessibility and controllability of polyimide in the clean room are also the other major considerations in selecting it as the dielectric.

#### 2.1.5 Fabrication Process

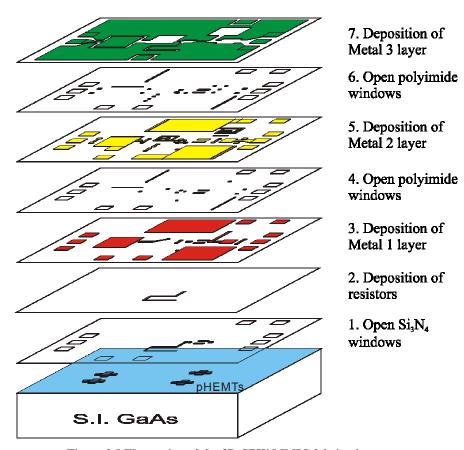

3D CPW MMIC fabrication is carried out in the clean room of the School of Electrical and Electronic Engineering, University of Manchester. An illustration of the fabrication process can be seen in Figure 2.8. It could be mainly divided into 7 steps with 3 conductors layers separated and insulated by the 2 dielectric layers, which in this case polyimide is used. Plasma etching technique is used to etch dielectric windows in order to build the interconnects.

Figure 2.8 Illustration of the 3D CPW MMIC fabrication steps.

One of the very first steps of the fabrication process is to open windows of the  $Si_3N_4$  passivation supplied by the semiconductor foundry. Photoresist were used during the process of lithography. Figure 2.9 shows the step 1 or etching the  $Si_3N_4$ , care should be taken as residue of  $Si_3N_4$  results in poor metal contact. First, dehydration bake was done at 110 °C for 10 minutes. Next, photoresist S1813 was spin thin at 5200 rpm for 30 seconds. Softbaking was done at 90 °C for 30 minutes, after that, the back of the sample was checked to make sure there was any residue of photoresist. Exposure was next done for 45 seconds with the mask design. 1 Microdev to 2 D.I. water was mixed to develop photoresist for 50 seconds followed by postbake at 110 °C for 30 minutes. Bufferal HF was used to remove  $Si_3N_4$  for 120 to 140 seconds. No  $Si_3N_4$  was to be found in the holes. Lastly, acetone was used to remove the remaining photoresist and the sample was then rinsed in D.I. water.

Figure 2.9 Step 1: Opening Si<sub>3</sub>N<sub>4</sub> windows.

The second step is making the thin film resistor, evaporating the NiCr. The sheet resistance of the thin film resistors depends on the ratio of Ni and Cr. First, the sample was dried at 110 °C for 10 minutes. Photoresist was spin into at 5200 rpm for 30 seconds followed by softbaking at 70 °C for 30 minutes. Again, back of the sample needed to be checked to ensure there was no photoresist residue. After that, the sample was under exposure for 45 seconds. The development was done using 1 Microdev to 2 D.I. water for 50 seconds. Next, sample was cleaned using HCL (10%) to remove metal oxide for 15 seconds. Evaporating speed was controlled at 0.1 nm/sec. Lastly, unwanted metal was lifted off by removing photoresist using acetone. The step is presented in Figure 2.10.

Figure 2.10 Step 2: Making thin film NiCr resistors.

The third step is to do with evaporating the Ti/Au metal layer 1. This step involves developing hardened photoresist by applying chlorobenzene treatment to achieve overhanging profile. Plasma etching was used to remove photoresist residue. During the evaporation of metal, clean Ti was required to obtain good metal adhesion. Like what previously done, the sample was cleaned first and dried at 110 °C for 10 minutes. Photoresist was spin at 5200 rpm for 30 seconds and softbaked at 70 °C for 30 minutes, residue was to be checked. Exposure was later done for 210 seconds. Chlorobenzene was used to harden the photoresist for 1 minute. Postbaking was followed at 70 °C for 10 minutes. 1 Microdev to 2 D.I. water was mixed in for 50 seconds and undercuts was checked using microscope. Redevelopment could be done if required. Next, plasma etching was used to remove photoresist residue for 30 seconds. HCL (10%) was applied to remove metal oxide for 15 seconds. The sample was then rinsed using D.I. water and dried to be ready for the evaporation of metal. Before opening the shutter, Ti was evaporated with dirty and the evaporation was carried out at 0.1 nm/sec to prevent photoresist from overheating. The Au evaporating speed was adjusted to 1 nm/sec and was stopped for 10 minutes for every 150 nm of Au to avoid photoresist overheating. Finally, metal was lifted off using NMP (photoresist stripper 1165). The illustration of the third step is shown in Figure 2.11.

Figure 2.11 Step 3: Evaporating Au/Ti metal layer 1.

The forth step is about applying the polyimide layer 1. After the usual steps of cleaning and drying the sample, polyimide was pre-baked at 110 °C for 10 minutes. The

polyimide (PI 6210) was then spin at 2200 rpm for 40 seconds. Next, it was soft cured at 110 °C for 30 minutes in the oven. After curing, residue of polyimide was removed from the backside using microposit developer. The final cure was done at 200 °C for 4 hours in vacuum oven. Following that, photoresist was applied. It was spin at 3000 rpm for 30 seconds, softbaked at 90 °C for 30 minutes. The photoresist residue was checked to avoid poor metal contact. Exposure was then done for 250 seconds. The development process involved using 1 microdev to 2 D.I. water to develop for 50 seconds. The postbaking was then carried out at 110 °C for 30 minutes. The polyimide was then etched using plasma etching technique at 50scm O2, 140W, 100mTorr for 13 to 14 minutes. Residue was checked. Photoresist was then removed in NMP. 1 minute of plasma etching was added at 50W to improve metal adhesion. Finally, it was rinsed in microposit developer to remove residue of polyimide. It was rinsed again lastly in D.I. water. An illustration of this step is shown in Figure 2.12.

Figure 2.12 Step 4: Applying Polyimide layer 1.

Step 5 is about evaporating metal layer 2. Almost the identical processing steps in Step 3 were carried out again. After that, Step 6 is applying the second layer of polyimide layer (Polyimide layer 2), again, the same steps elaborated in Step 4 were taken. The final step of Step 7 is evaporating the final metal layer 3. Once again, identical steps undertaken in

Step 3 and Step 5 were carried out to apply the conductor layer. Illustrations of the final three steps are presented in Figure 2.13 to 2.15.

Figure 2.13 Step 5: Evaporating Au/Ti metal layer 2.

Figure 2.14 Step 6: Applying Polyimide layer 2.

Figure 2.15 Step 7: Evaporating Au/Ti metal layer 3.

Due to the nature of the multilayer MMIC, each conductor and dielectric layers has to be provided with a mask design. Alignment among them was achieved with the help of alignment marks. Due to the nature of the polyimide, it is difficult to deposit gold conductor layers on it. That is why an alloy of Ti/Au was chosen in order to ensure the contact.

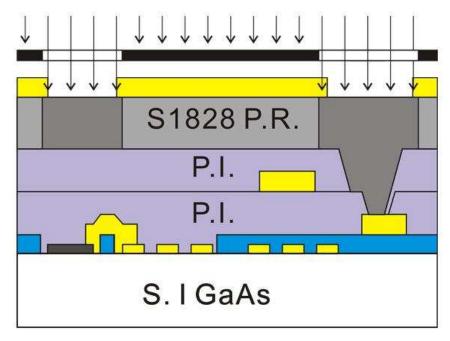

Figure 2.16 shows the mask set design of the 3D MMIC under investigation in this work. As can be seen, multilayer transmission lines with different geometries realising various impedances, couplers, inductors and capacitors with different designs and geometries together with demonstrations of integration of the pHEMTs with passive components realising a 2GHz CPW amplifier can all be found in this mask set. There is also a bandpass filter designed using multilayer passive components in this mask set.

Figure 2.16 Mask set design (a single unit cell).

Although MMIC is a highly repeatable technology for industrial fabrication process, there are some limitations of the facilities available in the clean room of the University of Manchester. That is why uniformity study is vital and needs to be carefully investigated for parameter variations in this work.

# 2.2 III – V Transistors

#### 2.2.1 Introduction

Driven by the advancement of lithography technology, transistor dimensions have continuously shrunk for the last few decades as predicted by Moore's Law [50]. As the dimension pushes into the sub-micron regime, it becomes more and more challenging to realise CMOS transistors with good and acceptable performance at microwave frequency. Both fundamental physics and practical considerations contribute to the limitation of Silicon technology scaling into sub-micron dimensions. As the gate length goes shorter and shorter coupled with the scaled down oxide, the off-state leakage current becomes a prominent issue. Other than that, as parasitic resistance and capacitance become comparable to the channel resistance and capacitance, a practical

limit as how small the scaling can go has been set. There are also considerations like how small the lithography can go and if single molecular transistor is possible.

In order to overcome the limitations of Silicon material, researchers around the world have been trying to find alternative semiconductor technology, among them compound III-V semiconductors are found. The fundamental physics of them having light effective masses means higher electron mobilities and larger output currents. All these make them attractive candidates for microwave applications.

# 2.2.2 Unipolar and Bipolar Transistors

Solid-state transistors can be generally categorised into two families, ie. unipolar and bipolar transistors. Unipolar transistors, also called field-effect transistors, deploy only one type of carriers, either electron or hole, to perform the transistor functions. Whereas, bipolar transistors are using both hole and electron carriers to perform the tasks. JFET (Junction Field-Effect Transistor), MOSFET (Metal-Oxide Semiconductor Field-Effect Transistor), MESFET (Metal Semiconductor Field-Effect Transistor), HEMT (High Electron Mobility Transistor) and pHEMT (pseudomorphic High Electron Mobility Transistor) are all unipolar transistors. On the other hand, BJT (Bipolar Junction Transistor) and HBT (Heterojunction Bipolar Transistor) are bipolar transistors. Another main difference between a unipolar and bipolar transistor is that unipolar transistor has higher input impedance than the bipolar counterpart [51].

Both unipolar and bipolar transistors have their own merits in terms of suitability for a specific application. Being unipolar or bipolar is not the sole reason for a particular device to be chosen for a given task. It also involves the semiconductor material used to construct the device. Silicon, Germanium, compound III-V semiconductors (GaAs, InP etc.) have all their special material property to make them especially suited for a certain job.

#### 2.2.3 Microwave Applications

Amplifier and switch are the two major device applications at microwave frequency. High power outputs are the imperative task required for a power amplifier. The best power amplifiers are those who have high voltage, high current density, high power density and low thermal impedance. In order to minimise the losses due to impedance matching, the power amplifier should possess a very high input impedance. Of course, the gain of the device used must be the most important parameter to be judged as the suitability for power amplifier design. On the other hand, low noise and linear amplifiers require the device to be inherently low noise and highly linear.

Switch demands a different requirement from the device. As switching function does not require any gain from the device, gate resistance is not as important. Not only that, instead of matching the gate input impedance to the matching network, the gate of the switch uses the highest impedance to stop the RF energy from leaking to the biasing network. In MMIC technology, the most popular choice of switch is the FET. It is very compatible to and flexible to be integrated to the MMIC. The ON- and OFF-state of the FET switch are achieved by opening or shutting down the conducting channel. The main challenge of FET switch compared to PIN diode switch is that the OFF-state capacitance of FET switch is significantly higher than PIN diode switch, in other words, isolation is relatively poorer [52].

# 2.3 Principle of pHEMT

#### 2.3.1 Introduction

As discussed above, field effect transistors (FET) can be fabricated using Silicon or Gallium Arsenide (GaAs). GaAs based active devices, due to its material property, can generally perform much faster than Silicon based devices. It is also why they are more suitable to be used for microwave and milimeter wave applications.

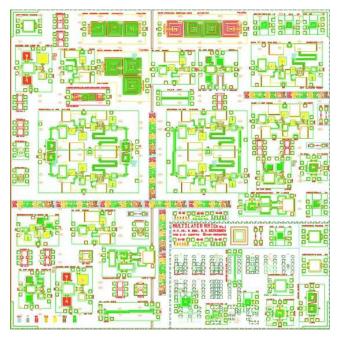

The differences between MESFET (Metal Semiconductor Field-Effect Transistor), HEMT (High Electron Mobility Transistor) and pHEMT (pseudomorphic High Electron

Mobility Transistor) are illustrated in Figure 2.17. In the figure, they are all n-type field-effect transistors, and HEMT and pHEMT have heterojunction formed in their structure to improve the performance achieving high electron mobility in the devices.

Figure 2.17 Structures of three types of FETs: (a)MESFET, (b)HEMT and (c)pHEMT.

Among them, MESFET has the simplest structure where a homogeneous material is used throughout the structure. For a device to perform good conductivity, high doping of impurities to generate the majority carriers is needed. However, for a structure like MESFET, high doping of the impurities would also introduce unwanted scattering effect hindering the electrons moving path in the channel. In other words, a higher channel resistance is observed [53].

That is why heterojunction is introduced [54-55]. Heterojunction is created when two material having two different energy bandgaps are joint together. Fundamental physics require the Fermi Levels of the two materials to be aligned, with that, at the interface, a quantum well is created with the bands bending in order to be joined together. The existence of the quantum well makes a good confinement for the electrons to travel in a certain path, the channel. The electrons are so well-confined in this path and hence it almost makes the electrons travel in 2 dimensions. Therefore, the electrons in this case are called 2DEG, 2 dimensional electron gas.

As shown in Figure 2.17, in HEMT, a ternary material AlGaAs is added on top of the GaAs. AlGaAs has a wider bandgap than GaAs, a heterojunction is thus formed at the interface of these two materials. AlGaAs can be taken as the supply layer, where high doping is done to generate n-type electron carriers. Before the interface of AlGaAs and GaAs, which is where the 2DEG is located, an undoped AlGaAs region is created. This

is sometimes called a spacer layer. Due to the fact that it is undoped, it creates a barrier for the 2DEG to escape from the quantum well, therefore a better confinement. As the doping is done in the AlGaAs supply layer, there is no need for doping done in the 2DEG GaAs channel layer. In other words, no impurities found in the channel layer which would further improve the mobility [53].

The latest improvement is seen in the pHEMT in Figure 2.17. Not any two materials could be joined and create the heterojunction. A lattice constant matched is a prerequisite for a heterojunction to be formed. However, it was found in 1990s that a lattice constant mismatched pair of materials could still be joined together to form heterojunction [56-58]. The requirement is that there is a limit on the thickness of the top material, it is called the critical thickness. As can be observed in Figure 2.17, a very thin layer of InGaAs is placed on top of the GaAs. InGaAs compared to GaAs can further improve the performance of the transistor because it can be made to have a very narrow bandgap and a much better confinement is made possible due to the bigger bandgap mismatch of AlGaAs and InGaAs.

One of the most important driver for compound semiconductor development is the advancement of growth techniques such as the Metal Organic Chemical Vapour Deposition (MOCVD) and Molecular Beam Epitaxy (MBE). For InGaAs and AlGaAs, the addition of Indium and Aluminium will alter the bandgap of the semiconductor according to (at 300K):

$$Al_{1-x}Ga_{1-x}As: E_g = 1.423 + 1.247x$$

(2.1)

$$In_{1-x}Ga_{1-x}As: E_{\sigma} = 1.423 - 1.53x$$

(2.2)

Bandgap of the GaAs would increase with addition of Aluminium component but decrease with Indium. Bandgap engineering could thus be achieved and new transistor designs could be created and made possible. Stacking difference layers of material with varying bandgap (discontinuities of valence band and conductor band) could create heterojunctions which in turn would create quantum wells making the 2DEG possible. Not only accumulation of the carriers could be achieved, the heterojunctions could also introduce some migration barriers for the carriers which both would contribute to a high mobility transistor. This bandgap engineering could also be implemented in bipolar

transistors family, where both majority and minority carriers could be accumulated and confined in the respective mismatchs of valence or conduction bands. However, in the case of the unipolar transistors family such as pHEMT, only one type of carrier would be affected.

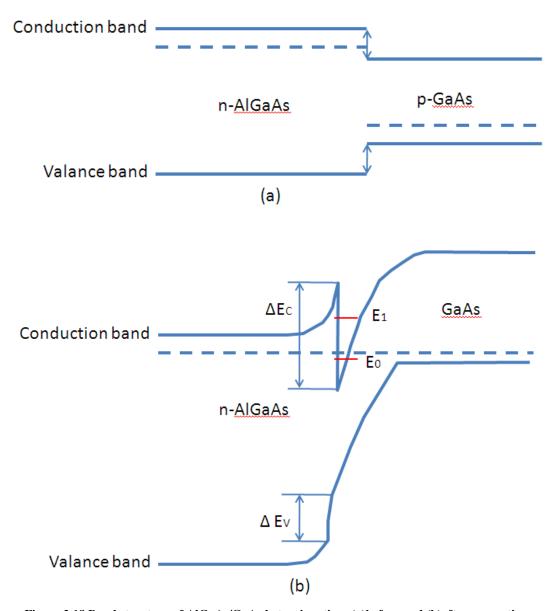

Figure 2.18 shows how the band diagrams would look like before and after the creation of heterojunction of AlGaAs and GaAs. Fermi level indicates the energy level that the probability of finding an electron is half. The spacing between conduction band and the Fermi level is defined as the relative electron density. As can be seen in Figure 2.18(b), along the conduction band, there is a "quantum well" area (falling below the Fermi level) where accumulation and confinement of electrons could be achieved. The differences in conduction band and valence band are represented by  $\Delta E_C$  and  $\Delta E_V$  respectively. Ideally, the difference in conduction band should simply be the difference in the electron affinities,  $X_1$  and  $X_2$  of the two materials:

$$\Delta E_c = X_1 + X_2 \tag{2.3}$$

And

$$E_{g2} = E_{g1} + \Delta E_c + \Delta E_v \tag{2.4}$$

Rearranging (2.4):

$$\Delta E_c + \Delta E_v = E_{g2} - E_{g1} = E_g \tag{2.5}$$

where  $X_1$  = electron affinity in AlGaAs,  $X_2$  = electron affinity in GaAs,  $Eg_1$  = bandgap of AlGaAs ad  $Eg_2$  = bandgap of GaAs.

Figure 2.18 Band structure of AlGaAs/GaAs heterojunction: (a)before and (b)after connecting.

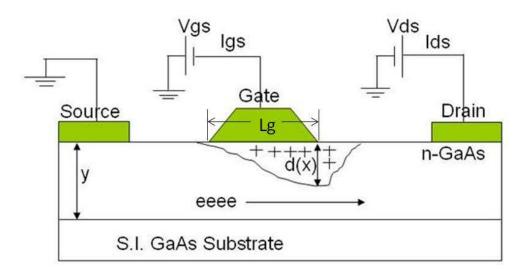

The operation of a pHEMT, or HEMT in this manner, is very similar to the operation of a MESFET. Figure 2.19 shows the operation of an n-type depletion-mode MESFET under common source configuration. The gate is used as the input and is reverse bias and the drain is used as the output and forward bias. A depletion region under the gate-semiconductor Schottky barrier is formed, due to reverse bias. This depletion region will have a rectifying effect on the electron transport along the channel which flows from the source to the drain end. It is clear that, if the gate voltage is fixed, as the drain voltage increases, more current will flow through. That is why, initially, for small drain voltage, the MESFET behaves like a resistor. However, as the potential at the drain end is

increased, the depletion width closer to the drain end will become larger, a point will be reached when the channel could accommodate the maximum velocity of the electrons. As this happens, the current starts to saturate.

Figure 2.19 Cross-sectional view of a GaAs MESFET under common source configuration

For long channel (gate length  $L_g >> y$ ), based on constant low field mobility and gradual channel approximation, the current  $I_{ds}$  is given as [59]:

$$I_{ds} = Z[Y - d(x)]qN_d \mu \cdot \frac{dV}{dx}$$

(2.6)

where Z is the gate width, Y is the channel depth, d(x) is the depletion width and  $N_d$  is the doping concentration.

d(x), the depletion width, is given by [59]:

$$d(x) = \left\{ \frac{2\varepsilon_{s}[V(x) + V_{bi} - V_{gs}]}{qN_{d}} \right\}^{1/2}$$

(2.7)

where  $\varepsilon_s$ =  $\varepsilon_0$   $\varepsilon_r$  is the semiconductor dielectric constant,  $V_{bi}$  the built-in potential.

Substituting equation (2.7) into equation (2.6):

$$I_{ds} = G_0 \left\{ V_{ds} - \frac{2[(V_{ds} + V_{bi} - V_{gs})^{3/2} - (V_{bi} - V_{gs})^{3/2}}{3V_p^{1/2}} \right\}$$

(2.8)

where  $G_0$ , the channel conductance and is given by [59]:

$$G_0 = \frac{q\mu N_d ZY}{L} \tag{2.9}$$

and  $V_p$ , the pinch-off voltage when the depletion width d(x) equals the channel depth Y, is [59]:

$$V_p = \frac{qN_d Y^2}{2\varepsilon_s} \tag{2.10}$$

On the other hand, for short channel MESFET (small Lg/Y ratio), the  $I_{ds(sat)}$  can be approximated as [59]:

$$I_{ds(sat)} = Z[Y - d]qN_d v_{sat}$$

(2.11)

where  $v_{sat}$  is the saturation velocity and the intrinsic transconductance,  $g_m$ , can be given by [59]:

$$g_m = \frac{\varepsilon_s Z v_{sat}}{d} \tag{2.12}$$

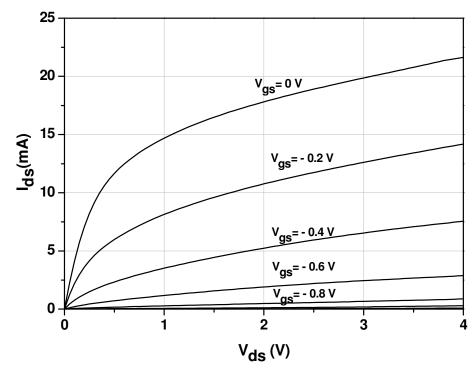

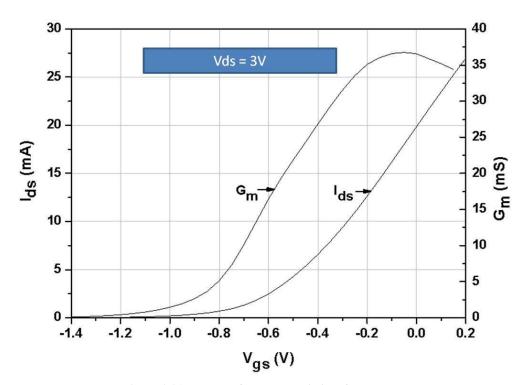

A typical DC characteristics of a pHEMT can be seen in Figure 2.20 and 2.21.

Figure 2.20 The output characteristics of a pHEMT.

Figure 2.21 The transfer characteristics of a pHEMT.

#### 2.3.2 Small-Signal Analysis