### Wright State University

## **CORE Scholar**

Browse all Theses and Dissertations

Theses and Dissertations

2006

# FPGA Frequency Domain Based Gps Coarse Acquisition **Processor using FFT**

Cyprian D. Sajabi Wright State University

Follow this and additional works at: https://corescholar.libraries.wright.edu/etd\_all

Part of the Electrical and Computer Engineering Commons

#### **Repository Citation**

Sajabi, Cyprian D., "FPGA Frequency Domain Based Gps Coarse Acquisition Processor using FFT" (2006). Browse all Theses and Dissertations. 27.

https://corescholar.libraries.wright.edu/etd\_all/27

This Thesis is brought to you for free and open access by the Theses and Dissertations at CORE Scholar. It has been accepted for inclusion in Browse all Theses and Dissertations by an authorized administrator of CORE Scholar. For more information, please contact library-corescholar@wright.edu.

# FPGA FREQUENCY DOMAIN BASED GPS COARSE ACQUISITION PROCESSOR USING FFT

A thesis submitted in partial fulfillment of the requirements for the degree of

Master of Science in Engineering

Ву

CYPRIAN D. SAJABI

B.A. BIOLOGY, Earlham College, 1995

2006

Wright State University

# WRIGHT STATE UNIVERSITY SCHOOL OF GRADUATE STUDIES

June 8, 2006

I HEREBY RECOMMEND THAT THE THESIS PREPARED UNDER MY SUPERVISION BY Cyprian Sajabi ENTITLED Design and Implementation Of an FPGA Frequency Domain Based GPS Coarse Acquisition Processor Using FFT BE ACCEPTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF Master of Science in Engineering

|                                  | Chien-In Henry Chen, Ph.D. Thesis Director |

|----------------------------------|--------------------------------------------|

|                                  | Fred Garber, Ph.D. Department Chair        |

| Committee on Final Examination   |                                            |

| Chien-In Henry Chen, Ph.D.       |                                            |

| Raymond Siferd, Ph.D.            |                                            |

| Marty Emmert, Ph.D.              |                                            |

| Dr. Joseph F. Thomas, Jr., Ph.D. |                                            |

Dean, School of Graduate Studies

### **Abstract**

Sajabi, David, Cyprian, M.S.E.E., Department of Electrical Engineering, Wright State University, 2006.

FPGA Frequency Domain Based GPS Coarse Acquisition Processor Using FFT.

The Global Positioning System or GPS is a satellite based technology that has gained widespread use worldwide in civilian and military applications. Direct Sequence Spread spectrum (DSSS) is the method whereby the data transmitted by the satellite and received by user is kept secure, low power and relatively noise-immune. The first step required in the GPS operation is to perform a lock on the incoming signal, both with respect to time synchronization and frequency resolution. Because of the need for reduced time to lock and also reduced hardware, algorithms based in the frequency domain have been developed. These algorithms take advantage of the time to frequency matrix operation known as the fast Fourier transform or FFT. For this thesis, a Direct Sequence Spread Spectrum Coarse Acquisition code processor based on the FFT was implemented in VHDL and targeted to a Xilinx Virtex –II Pro Field Programmable Gate Array (FPGA). The use of the FFT allows simultaneous lock on coarse acquisition (C/A) code and carrier frequency. Because of hardware limitations, a novel technique of sub-sampling is used in this system to obtain data block sizes that match hardware limitations. In addition, design challenges related to scheduling and timing were addressed, allowing a system with 19 pipeline stages to be built. The system, which fits on a Xilinx Virtex-II pro XC2VP70 FPGA, uses 10 ms of data to perform the lock with 5.5 ms of processing time at 100 MHz and theoretically can operate on signals 20 db below the noise floor.

# TABLE OF CONTENTS

| 1          | INTRO      | DUCTION 1                                                               |                |

|------------|------------|-------------------------------------------------------------------------|----------------|

| 1.1        | GPS        | Background                                                              | 1              |

| 1.2        | Motiv      | vation                                                                  | 2              |

| 1.3        | Sprea      | d Spectrum Basics                                                       | 2              |

| 1.4        |            | ast Fourier Transform                                                   |                |

| 1          | .4.1 Dire  | ct Computation of the DFT                                               | 8              |

| 1          | .4.2 Divid | le-and-Conquer Approach                                                 |                |

| 1          | .4.3       | DECIMATION-IN-TIME APPROACH TO COMPUTING                                | G THE          |

|            |            | DFT                                                                     | 12             |

| 1.5        | Radix      | z-2 FFT Algorithms                                                      | 1.2            |

| 1.5        | Hard       | ware Implications of FFT                                                | 14             |

| 2          | STATE      | MENT OF NEED 17                                                         |                |

| 2.1        | The Field  | l Programmable Gate Array (FPGA)                                        | 17             |

| 2.2        |            | Locking in on GPS Coarse Acquisition Code                               | 17             |

| 2          | .2.1       | Spreading Data with C/A Code                                            | 18             |

| 2          | .2.2       | Despreading at the Receiver                                             |                |

|            | .2.3       | Frequency Steps In Acquisition                                          |                |

| 2          | .2.4       | C/A Code Multiplication and The FFT                                     |                |

| 3          | 25         | JENCY DOMAIN BASED APPROACHES TO ACQUISIT  -Domain Circular Correlation | <b>ION.</b> 25 |

| 3.2        | _          | ving range and Doppler uncertainties                                    | 26             |

| 3.2<br>3.3 |            | isition By FFT Based Circular Correlation                               | 30             |

| 3.4        | _          | shold Values                                                            | 33             |

|            |            |                                                                         |                |

| 4          |            | TECTURE AND DESIGN CONSIDERATIONS 34                                    |                |

| 4.1        | _          | n Choices                                                               | 34             |

|            | .1.1       | Buffering                                                               |                |

|            | .1.2       | Sample Rate Conversion                                                  |                |

|            | .1.3       | Mapping 5,000 Point DFT To Hardware                                     |                |

| 4          | .1.4       | Direct Digital Synthesizer (DDS) Challenges                             | 38             |

| 5          | GLOBA      | AL VIEW OF DATAFLOW THROUGH THE SYSTEM                                  | 39             |

| 5.1        | Data       | Capture Domain.                                                         | 39             |

| 5          | .1.1       | <b>Details of Datapaths In The Data Capture Domain</b>                  | 40             |

|            | 5.1.1.1    | The Dual Port RAMs                                                      | 40             |

|            | 5.1.1.2    | Counters                                                                | 41             |

|            | 5.1.1.3    | The Direct Digital Synthesizer (DDS)                                    | 42             |

|            | 5.1.1.4    | The C/A Code Generator (CCG)                                            | 43             |

|            | 5.1.1.4    | The Complex Multiplier                                                  | 43             |

|            | 5.1.1.5    | Complex Multiplexor (CM)                                                | 44             |

| 5.1.2           | Controllers in the Data Capture Domain.                           | . 44     |

|-----------------|-------------------------------------------------------------------|----------|

| 5.1.2.1         | Front_dual_port_control (FDPC)                                    | 44       |

| 5.1.2.2         | DDS / Data Controller (DDC)                                       | 45       |

| 5.1.2.3         | Supplementary Control for Subsampling (SCS)                       | 46       |

| 5.1.2.4         | Pre FFT Control (PFC)                                             | 47       |

| 5.1.2.5         | C/A Code Control (CCC)                                            | 47       |

| 5.1.2.6         | Some Observations and Notes on Synchronization:                   | 48       |

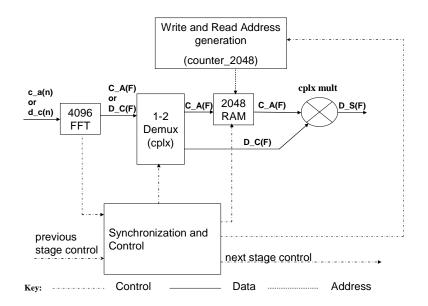

| 5.2 FFT 4       | 1,096 Domain                                                      | 49       |

| 5.2.1           | Overview of Operations in the FFT 4,096 Domain.                   | . 49     |

| 5.2.2           | Datapath And Control Operations In The FFT 4,096 Domain           |          |

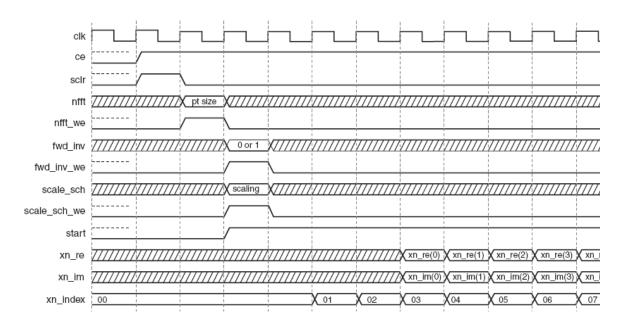

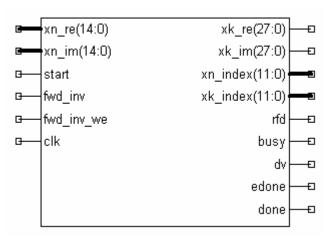

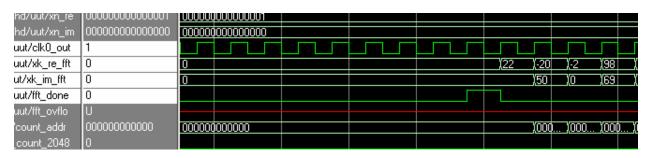

| 5.2.2.1         | FFT_4096                                                          | 52       |

| 5.2.2.2         | Counter_2048                                                      | 55       |

| 5.2.2.3         | RAM_2048                                                          | 55       |

| 5.2.2.4         | Cplx_mult_1                                                       | 55       |

| 5.2.2.5         | Demultiplexer_2 (DEMUX 1_2)                                       | 56       |

| 5.2.3           | Controllers in the FFT_4096 Domain                                | . 56     |

| 5.2.3.1         | IFFT_Cont (IC)                                                    | 56       |

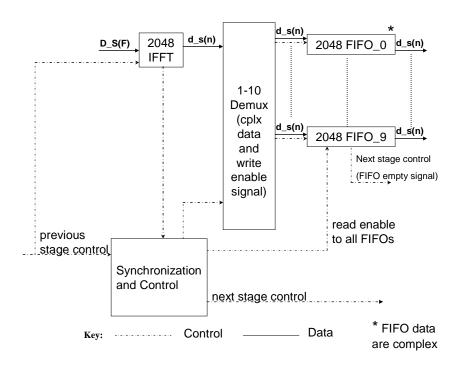

| <b>5.3</b> IFFT | _2048 Domain.                                                     | 58       |

| 5.3.1           | Overview of Operations the IFFT_2048 Domain                       | . 59     |

| 5.3.2           | Details of Datapaths in the IFFT_2048 Domain                      |          |

| 5.3.2.1         | IFFT_2048                                                         | 59       |

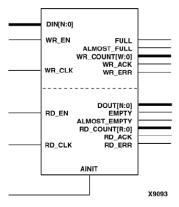

| 5.3.2.2         | FIFO_2048                                                         | 60       |

| 5.3.2.3         | DEMUX 1_10                                                        | 61       |

| 5.3.3           | Controllers in the IFFT_2048 Domain                               | . 62     |

| 5.3.3.1         | IFFT_OP_CONT (IOC)                                                | 62       |

| 5.3.4           | Timing Issues Post IFFT_2048                                      | . 62     |

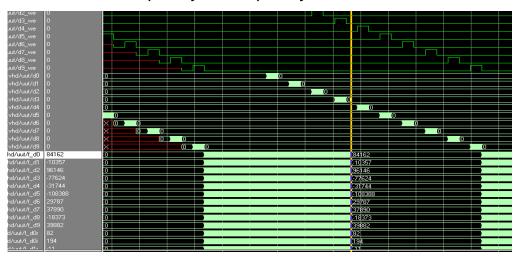

| 5.4 The 1       | 0 Point DFT/ Sorting Domain                                       | 63       |

| 5.4.1           | Overview of Operations in the 10 Point DFT/ Sorting Domain        | . 64     |

| 5.4.2           | Details of Datapaths in The 10-Point DFT/Sorting Domain           | . 64     |

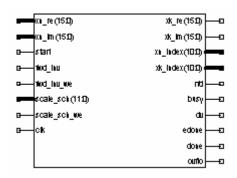

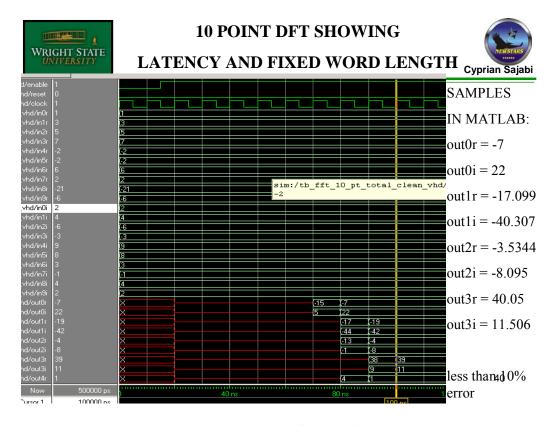

| 5.4.2.1         | DFT_10                                                            | 64       |

| 5.4.2.2         | Max_find_0                                                        | 66       |

| 5.4.2.3         | Max_find_1                                                        | 67       |

| 5.4.2.4         | Max_find_2                                                        | 68       |

| 5.4.2.5         | Final Calculation Circuitry                                       | 68       |

| 5.4.2.          | 5.2 FDM_0                                                         | 69       |

| 5.4.2.          | 5.2 FDM_1                                                         | 69       |

| 5.4.3           | Controllers in the DFT_10/Sorting Domain                          | . 70     |

| 5.4.3.1         | Max_find_1 Control                                                | 70       |

| 5.4.3.1.2       | Max_find_2_control                                                | 71       |

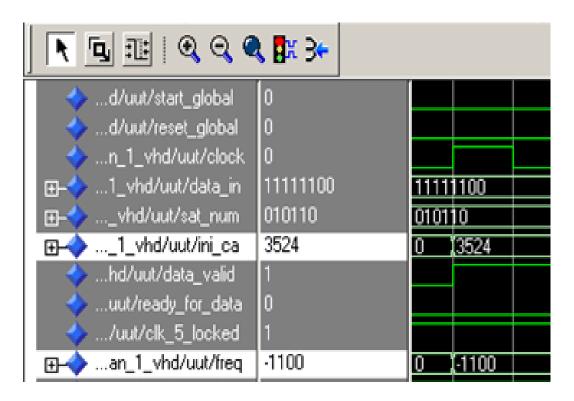

| 5.5 Simul       | ation results of the Processor                                    | 71       |

| 6 Finite W      | Vord-length Considerations. 73                                    |          |

|                 | th of the Bits in the Datapath Due to Addition and Multiplication | 73       |

|                 | ts of Truncation on the Datapath.                                 | 73<br>74 |

|                 | ing without changing value.                                       | 74<br>76 |

|                 | cation and resizing schedule for C/A processor                    | 76       |

| vot iluliv      |                                                                   | / U      |

| 7            | HARD  | WARE REQUIREMENTS FROM XILINX REPORTS 79 | 9  |

|--------------|-------|------------------------------------------|----|

| 8.           | COMP  | ARISONS WITH CURRENT DESIGNS 81          |    |

| 9.           | CONCI | LUSIONS AND FUTURE WORK 83               |    |

| 9.1          | Conc  | elusions                                 | 83 |

| 9.2          | Futu  | re Work                                  | 83 |

| AP           | PENDI | <b>X</b> 85                              |    |

| <b>A.1</b>   | MAT   | TLAB CODE FOR C/A PROCESSOR BLOCKS       | 85 |

| $\mathbf{A}$ | .1.1  | C/A Code Generation                      | 85 |

| $\mathbf{A}$ | .1.2  | C/A Code Sampling                        | 86 |

| $\mathbf{A}$ | .1.3  | Generation of real-world data.           | 87 |

| $\mathbf{A}$ | .1.4  | C/A code acquisition function.           | 88 |

| $\mathbf{A}$ | .1.5  | Subsampling Matlab Function.             | 90 |

| RE           | FEREN | ICES 91                                  |    |

# **List of Figures**

| Figure                                                                               | Page |

|--------------------------------------------------------------------------------------|------|

| Figure 1.1 Direct Sequence code spreading of data                                    | 6    |

| Figure 1.2 DS- Concept, before and after despreading <sup>a</sup>                    | 6    |

| Figure 1.3 Basic Butterfly Computation in the FFT Algorithm                          | 13   |

| Figure 1.4 Three stages in the computation of an $N = 8$ -point DFT (Proakis P. 459) | 13   |

| Figure 2.1 Autocorrelation of 1,023 C/A code chips                                   | 21   |

| Figure 2.2 AutoCorrelation 5,000 C/A code chips.                                     | 21   |

| Figure 2.3 C/A coded input signal multiplied by C/A code                             | 24   |

| Figure 3.1 The Ambiguity Function Concept                                            | 27   |

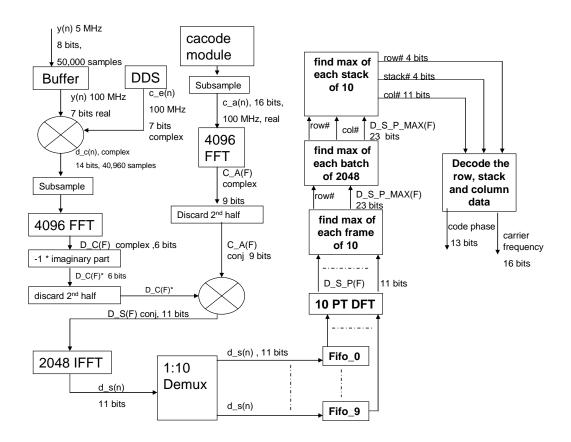

| Figure 3.1 A block diagram of the proposed C/A code acquisition process              | 32   |

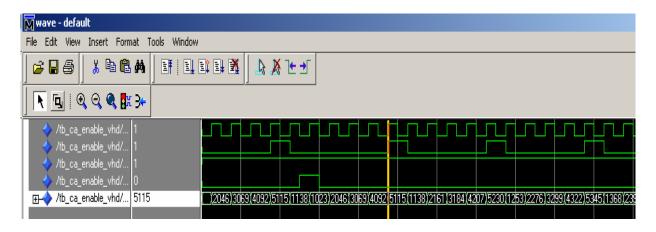

| Figure 4.1. Count sequence of LFSR_enable module showing enable signal               | 36   |

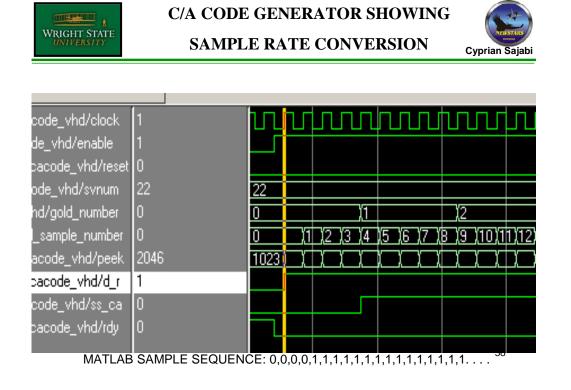

| Figure 4.2. C/A code generator showing sample rate conversion                        | 36   |

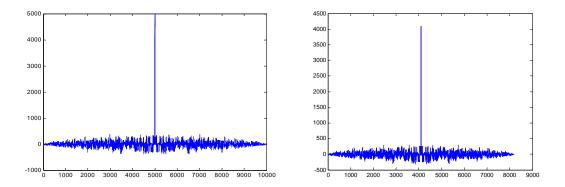

| Figure 4.3 Autocorrelation properties of C/A code before and after "subsampling."    | 37   |

| Figure 5.1. The Data Capture Domain                                                  | 39   |

| Figure 5.2 Dual Port RAM used in Data Capture Domain                                 | 41   |

| Figure 5.3 Schematic symbol of the Direct Digital Synthesizer                        | 42   |

| Figure 5.4 Schematic Symbol of C/A code Generator                                    | 43   |

| Figure. 5.5. Block diagram of 4,096 FFT domain                                       | 51   |

| Figure 5.6: Synchronization of Beginning of Data Frame with index for FFT            | 53   |

| Figure 5.7 FFT_4096 symbol (overflow not shown)                                      | 54   |

| Figure 5.8, Unloading results after <i>fft_done</i> has pulsed                       | 54   |

| Figure 5.9 Complex multiplier Schematic                                              | 56   |

| Figure 5.10 The IFFT 2048 Domain                                                     | 58   |

| Figure 5.11 Schematic of IFFT_2048 module                                     | 60 |

|-------------------------------------------------------------------------------|----|

| Figure 5.12 FIFO 2,048 IP Core                                                | 61 |

| Figure 5.13 Simulation showing that FIFO collisions are avoided.              | 63 |

| Figure 5.14 Block Diagram of 10 Point DFT/Sorting Domain                      | 63 |

| Figure 5.15 DFT_10 Module Sample Simulation                                   | 66 |

| Figure 5.16 Behavioral simulation showing successful emulation of MATLAB code | 72 |

| Figure 6.1 Action of std_resize to smaller size                               | 76 |

# **List of Tables**

| Table                                                                     | Page |

|---------------------------------------------------------------------------|------|

| Table 1.1 Complexity of Direct Computation of the DFT vs FFT Algorithm    | 14   |

| Table 5.1 Synthesis Results of FFT_10 showing FPGA resources utilized     | 65   |

| Table 6.1 Examples of Truncation Error for positive and negative numbers  | 75   |

| Table 6.2 Theoretical versus implemented truncation and resizing schedule | 77   |

| Table 7.1 Overall Virtex-II Pro 70 FPGA Resource Usage of Processor       | 79   |

| Table 7.2 Analysis of Individual Synthesis Results of Major Components    | 80   |

| Table 8.1 Comparisons with some Current GPS Receivers                     | 82   |

### Acknowledgements

This work was supported in part by the program of Receiver and Processing Concepts Evaluation (RAPCEval), Department of Defense, Air Force Research Lab, USA.

I especially thank my wife, Nacim Sajabi and my whole family both locally and overseas for their patience, support and strong encouragement throughout this thesis. I know it has not been easy, thanks for hanging in there and helping keep up my spirits.

I would like to heartily thank my advisor, Dr. Henry Chen for his invaluable insights unflagging energy, and facilitation of my thesis work over the last year and a half. It has been a great learning and growth journey for me. Thank you ever so much Dr. Chen.

The members of my thesis defence committee have my heartfelt thanks for taking the time out of their busy schedules to read my thesis and advise me in big and small ways throughout the circuit design process.

To all the folks in the VLSI lab, it has been great spending time with you, debating EE and life topics and sharing all our various experiences on our respective thesis paths. It is always easier to go through these experiences together rather than singly.

I would also like to thank numerous individuals from the Wright Patterson Air force Base who gave me pointers on tips on how to make the design simpler and practical. The list includes, but is not limited to David Lin, Dr. James Tsui, James Stephens, Ted Vandewerker, George Gonczy, Ed Huling, and Cliff Bullmaster.

To Vicky Slone, and Jenny and Barry Woods and Marie Donohue, thank you ever so much for helping me fill in all the big and small details that would otherwise go unfilled in all my haste and myopic focus on the all consuming "circuit".

# **DEDICATION**

I dedicate this thesis to the memory of my beloved parents, Lorna Hope Forbes Sajabi and Samuel Sembuze Sajabi, who always encouraged their children, natural or adopted, to excel in all that they do.

#### 1 INTRODUCTION

## 1.1 GPS Background

The Global Positioning System, usually called **GPS** is referred to by the United States Military as **NAVSTAR GPS** - **Navigation Signal Timing and Ranging Global Positioning System.** GPS has a number of applications such as ranging and targeting of ammunition, civilian navigation, and tracking of goods, personnel, and vehicles, just to name a few [1].

The rapid development in Very Large Scale Integration (VLSI) means that GPS units can now be purchased for less than \$100.00 or integrated into Cell phones, PDAs and vehicle navigation systems. There is almost no limit the range of applications for GPS and it promises to become as fundamental as the telephone in modern society. GPS is based on 24 orbiting satellites in **Intermediate circular orbit (ICO)** orbiting at around 11,000 nautical miles in such a manner that there will always be at least four satellites visible from anywhere on earth [2]. The precise position and velocity of each satellite is known and is used as a reference point for the GPS calculations. Each satellite is generating and continuously transmitting a **Pseudorandom Noise (PN)** sequence of ones and zeroes that can be used to identify it uniquely. This sequence is combined with a very low frequency signal that is used in further data processing for the GPS process. The GPS receiver unit can generate the same PN sequences as the satellites and uses the similarity or **correlation** between these and the received sequence to identify which satellite or satellites are visible at a given time. [2] This step of identifying the satellites is part of an overall process known as **acquisition**. Acquisition is only the first step in the GPS process and is required for the next phases of GPS to proceed. This thesis will

focus on initial acquisition, as the other phases of the GPS are beyond the scope of this project.

#### 1.2 Motivation

This thesis is based on a proven model of a GPS acquisition system on MATLAB. The use of powerful mathematical software such as MATLAB to model systems is very important because it allows design and prototyping to take place at a high level of abstraction. In this way proof-of-concept can be demonstrated efficiently and if needed, rapid modifications can be made to a model under study. The acquisition system model for this thesis is based in a frequency-domain approach, which, although using more hardware than a time-domain approach, is considerably faster [3]. The need for rapid algorithms to carry out GPS acquisition is critical, and in most cases is worth the hardware cost. A rapidly moving system such as an airplane or rocket cannot afford large delays when determining its relative position and velocity.

#### 1.3 Spread Spectrum Basics

Now, a few words about Spread Spectrum technology are in order. A spread-spectrum communication system is one that uses much more bandwidth than would ordinarily be needed simply for information transmission. Sometimes the transmitted bandwidth is as much as 10<sup>5</sup> times the information bandwidth. Spread Spectrum technology was first used developed by the US Navy in the 1950 and was conceived by Hedy Lamar, a Hollywood actress, during WWII [4]. DSSS techniques are ubiquitous in wireless devices such as cell phones, Wireless Ethernet standard 802.11, and of course

GPS units. DSSS technology allows multiple users access to the same frequency band at the same time, leading an efficient use of spectrum. DSSS is designed to operate in low signal to noise ratio environments, and this allows transmitters to use low power signals, major factor to consider when designing a GPS system. Another benefit of DSSS is that it is resistant to jamming (intentional or otherwise) by narrowband signals, making it ideal for military applications and critical civilian applications. In a Spread Spectrum system, the bandwidth of the transmitted signal is much greater than minimum bandwidth needed to transmit it. For example a typical GPS satellite data signal bandwidth is about 50 Hz, so 100 Hz is the minimum bandwidth needed to transmit this signal. The spread spectrum bandwidth is over 2 MHz - a 20,000 fold increase in the needed bandwidth to transmit the signal if double sideband transmission is used. This spreading of the spectrum is accomplished by modulating or multiplying the information with a wideband encoding signal. There are three types of techniques that are generally thought of as spread spectrum. They are direct sequence, frequency hopping, and "chirp" modulation. This thesis is focused on the direct sequence method, so the details will only be given on this method. In direct sequence, there is modulation of a carrier by a digital code sequence whose "chip" rate is much higher than the information signal bandwidth.

The basis of spread spectrum technology is expressed by Claude Shannon in the form of channel capacity:

$$C = W \log_2 \left( 1 + \frac{S}{N} \right) \tag{1.1}$$

C = capacity in bits per second, W = bandwidth in Hz

N = noise power, S = signal power

This equation shows that the higher the signal to noise ratio and the higher the bandwidth, the more information we can transmit though a channel.

If we change to natural logarithms and rearrange the equation, we get the following expression:

$$\frac{C}{W} = 1.44 \log_e \left( 1 + \frac{S}{N} \right), \tag{1.2}$$

and for small S/N of less than 0.1 (which is the case in a GPS system),

$$\frac{C}{W} \approx 1.44 \left(\frac{S}{N}\right) \tag{1.3}$$

Further rearranging to make W the subject of the equation gives

$$W \approx \left(\frac{NC}{S * 1.44}\right) \tag{1.4}$$

From this equation we can see that if we have a fixed channel capacity and fixed signal strength, then in the presence of a large amount of noise, we need to increase the transmitting bandwidth to counteract the effects of the noise. This is the price that needs to be paid to ensure secure and error free transmission in a noisy environment. There are various methods of embedding the information onto the spread spectrum signal. One common method is to add the information to the spectrum spreading code before a carrier wave is added. Alternately, one may modulate the information and then apply the spreading code. Each approach has pros and cons which need to be weighed before proceeding. There are numerous reasons for using spread spectrum technology. Below are just a few:

- 1. Selective addressing capability

- 2. Code division multiplexing is possible for multiple access (CDMA).

- 3. Low density spectra for signal hiding

- 4. Message screening from eavesdroppers

- 5. High resolution ranging

- 6. Interference rejection. (High Jamming Margin)

The major figure of merit for a spread spectrum system is the **jamming margin.** It is closely related to another property of the system known as **process gain.** The process gain is simply the ratio of the spread bandwidth to the minimum bandwidth needed to transmit a signal. In a spread spectrum signal process gain is given by:

$$G_P = \left(\frac{BW_{RF}}{R_{\inf o}}\right),\tag{1.5}$$

where RF bandwidth (BW<sub>RF</sub>) is the bandwidth of the transmitted spread spectrum signal and the information rate ( $R_{info}$ ) is the data rate in the information base-band channel.

Processing Gain is inherent in the transmission of the system and is an upper bound on the quality of the system. No real system achieves its potential process gain. A more realistic figure of merit is the jamming margin. To understand jamming margin, we need to discuss how the spectrum is "de-spread" at the receiver end. Basically, what happens at the receiver is as follows: First carrier needs to be wiped off, base banding the incoming signal. Then and the incoming signal is correlated with a local reference code identical to the code that was used to spread the spectrum. If there is a match between the local code and the signal, the spectrum collapses back to its original bandwidth before spreading. Any uncorrelated signal, such as a jamming signal or noise, is spread by the local code to the local reference bandwidth. A filter is then used to reject all but the desired narrowband signal of interest. One thing to note is that the spreading codes tend to be periodic. They are generated by a device known as a Linear Feedback Shift

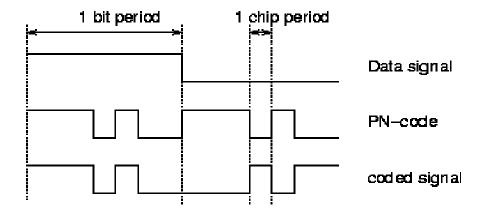

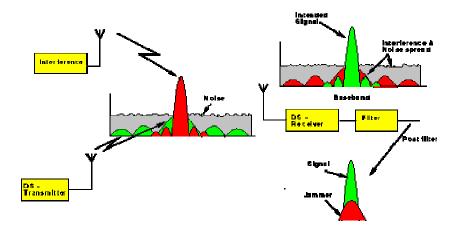

Register or LFSR. This periodicity is important in the synchronization of the incoming signal with the locally generated version of the code. Figures 1.1 and 1.2 give an overview of the spectrum changes occurring in a spread spectrum system.<sup>a</sup>

Figure 1.1 Direct Sequence code spreading of data

Figure 1.2 DS- Concept, before and after despreading<sup>a</sup>

This process results in enhancement of the desired signal and attenuation of the spurious signals. The difference in output and input signal to noise ratios is defined as the process gain. Ideally this should also be equal to the jamming margin. In reality the jamming margin is less than the process gain. Jamming margin takes into account internal

-

<sup>&</sup>lt;sup>a</sup> Source: http://cas.et.tudelft.nl/~glas/ssc/techn/techniques.html

losses and the minimum SNR needed to decode the received information. Jamming margin in dB is expressed as:

$$M_{j} = G_{P} - \left[L_{sys} + \left(\frac{S}{N}\right)_{out}\right], \tag{1.6}$$

Where  $L_{sys}$  = system implementation losses, and  $(S/N)_{out}$  = SNR at the information output.

A sample calculation with a system that has a 30-dB process gain,  $minimum (S/N)_{out} \ of \ 10 \ dB \ and \ L_{sys} \ of \ 2dB \ would \ have \ an \ 18-dB \ jamming \ margin \ (Mj).$  Therefore, if the jamming signal is more than 18-dB above the signal of interest, the system would not operate properly [5].

#### 1.4 The Fast Fourier Transform

The fast Fourier transform (FFT) is based on the discrete Fourier transform (DFT), an algorithm that performs a frequency analysis on a discrete sampled signal. The DFT transforms a sequence of N complex numbers  $\{xn_1, xn_2... xn_{N-1}\}$  in the time domain to a sequence of N complex numbers  $\{XK_1, XK_2 ... XK_{N-1}\}$  in the frequency domain. The formula is as follows:

$$X_k = \sum_{n=0}^{N-1} x_n e^{-\frac{2\pi i}{N}kn} \qquad k = 0, \dots, N-1$$

(1.7)

The DFT gives a representation of the signal in the frequency domain and is useful for understanding where in the frequency domain most of the energy or information in a signal is concentrated.

The inverse DFT or IDFT translates data from the frequency domain to the time domain and the formula is as follows

$$x_n = \frac{1}{N} \sum_{k=0}^{N-1} X_k e^{\frac{2\pi i}{N}kn} \qquad n = 0, \dots, N-1.$$

(1.8)

The DFT and IDFT are used extensively in digital signal processing algorithms such as linear filtering, correlation analysis and spectrum analysis. [6]

#### 1.4.1 Direct Computation of the DFT

"For a complex valued sequence x(n) of N points, the DFT may be expressed as

$$X_{R}(k) = \sum_{n=0}^{N-1} \left[ x_{R}(n) \cos \frac{2\pi kn}{N} + x_{I}(n) \sin \frac{2\pi kn}{N} \right]$$

(1.9)

$$X_{I}(k) = -\sum_{n=0}^{N-1} \left[ x_{R}(n) \sin \frac{2\pi kn}{N} - x_{I}(n) \cos \frac{2\pi kn}{N} \right]$$

(1.10)

The direct computation of (1.9) and (1.10) requires:

- 1.  $2N^2$  evaluations of trigonometric functions.

- 2.  $4N^2$  real multiplications.

- 3. 4N (N-1) real additions.

- 4. A number of indexing and addressing operations.

These operations are typical of DFT computational algorithms. The operations in items 2 and 3 result in the DFT values  $X_R(k)$  and  $X_I(k)$ . The indexing and addressing operations are necessary to fetch the data x(n),  $0 \le n \le N-1$ , and the phase factors  $(W_N)$  and to store the results."[7]

The DFT and IDFT are very computation-intensive, and for large blocks of data are not very practical in real-time systems. Efficient computation of the DFT is carried using what are termed Fast Fourier Transforms or FFTs. The two kinds of FFTs used in this thesis are the divide-and-conquer approach and the decimation-in-time approach.

# 1.4.2 Divide-and-Conquer Approach

If we adopt a divide-and-conquer approach, the DFT can be carried out in a fairly efficient manner. By prime factoring, the N point DFT is broken into successively smaller DFTs, whose results are then used to compute the final DFT.

The algorithm below is one of many that can be used to accelerate the calculation of the DFT:

# Algorithm to Directly Calculate the DFT of any sequence using the Divide and Conquer Approach.

- 1. Factor N into the product of two prime integers; N = LM;

- 2. We can zero pad if needed to ensure factorization

- 3. Store the signal column-wise in L rows and M columns.

- 4. Compute the M-point DFT of each row.

- 5. Multiply the resulting array by the phase factors

- 6. Compute the L-point DFT of each column

- 7. Read the resulting array row-wise

Here is an example to illustrate the algorithm. Consider the computation of an N = 10 DFT. The following summary information is given.

- $a = [a0 \ a1 \ a2 \ a3 \ a4 \ a5 \ a6 \ a7 \ a8 \ a9]$ ; a is assumed to be complex.

- b = fft(a); b = [A0 A1 A2 A3 A4 A5 A6 A7 A8 A9]; b is complex.

- The number 10 can be factored into 2 \* 5. We select L = 5 and M = 2.

Step 1: Store the 10-point sequence column-wise in 2 columns. (M = 2)

| row1  | a(0,0) = a0 | a(0,1) = a5 |

|-------|-------------|-------------|

| row2  | a(1,0) = a1 | a(1,1) = a6 |

| row3  | a(2,0) = a2 | a(2,1) = a7 |

| row 4 | a(3,0) = a3 | a(3,1) = a8 |

| row5  | a(4,0)= a4  | a(4,1) = a9 |

**Step 2: Compute the 2-point DFT on each row**

| f(0,0) = a0 + a5 = f0 | f(0,1) = a0 - a5 = f5 |

|-----------------------|-----------------------|

| f(1,0) = a1 + a6 = f1 | f(1,1) = a1 - a6 = f6 |

| f(2,0) = a2 + a7 = f2 | f(2,1) = a2 - a7 = f7 |

| f(3,0) = a3 + a8 = f3 | f(3,1) = a3 - a8 = f8 |

| f(4,0)= a4 + a9 = f4  | f(4,1) = a4 - a9 = f9 |

Step 3: Multiply each of the terms f(l,q) by the phase factors  $W_{l0}^{l,q}$

|                                   | T                                                    |

|-----------------------------------|------------------------------------------------------|

| $f(0,0)^* W_{10}^{0.0} = f0^*1$   | $  f(0,1)^* W_{10}^{0.1} = f5^*1$                    |

| =g(0,0)=g0                        | =g(0,1)=g5                                           |

| $f(1,0)^* W_{10}^{1.0} = f1^*1$   | $f(1,1)^* W_{10}^{1.1} = f6^* (0.8090 - 0.5878i)$    |

| =g(1,0)=g1                        | =g(0,2)=g6                                           |

| $f(2,0)^* W_{10}^{2.0} = f2^*1$   | $f(2,1)^* W_{10}^{2.1} = f7^* (0.3090 - 0.9511i)$    |

| =g(2,0)=g2                        | =g(0,3)=g7                                           |

| $f(3,0)^* W_{10}^{3.0} = f3^*1$   | $f(3,1)^* W_{10}^{3.1} = f8^* (-0.3090 - 0.9511i)$   |

| =g(3,0)=g3                        | =g(0,4)=g8                                           |

| $f(4,0)^*$ $W_{10}^{4.0} = f4^*1$ | $f(4,1)^*$ $W_{10}^{4.1} = f9^*$ (-0.8090 - 0.5878i) |

| =g(4,0)=g4                        | =g(0,5)=g9                                           |

|                                   |                                                      |

# Step 4: Compute the 5-point DFT of each column. A(k) = DFT(g(n))

Step 5: Read the resulting array row-wise

| A(0,0) = A0 | A(0,1) = A1 |

|-------------|-------------|

| A(1,0) = A2 | A(0,2) = A3 |

| A(2,0) = A4 | A(0,3) = A5 |

| A(3,0) = A6 | A(0,4) = A7 |

| A(4,0) = A8 | A(0,5) = A9 |

#### 1.4.3 DECIMATION-IN-TIME APPROACH TO COMPUTING THE DFT

One of the most efficient forms of the FFT is the decimation in time FFT. It is derived as follows:

If we perform the substitution:  $e^{-j2\pi/N} = W_{N.}$ , where  $W_N$  is known as the phase factor, then the DFT then becomes:

$$X(k) = \sum_{n=0}^{N-1} x(n) W_N^{kn} . {(1.11)}$$

Similarly, the IDFT becomes:

$$x(n) = \frac{1}{N} \sum_{n=0}^{N-1} X(k) W_N^{-kn} . {(1.12)}$$

Using the properties of complex exponentials, we discover two interesting characteristics in the phase factors that allow us to simplify the DFT and IDFT computations. These two characteristics are:

Symmetry Property:

$$-W_N^k = W_N^{k+N/2}$$

(1.13)

Periodicity Property:

$$W_N^k = W_N^{k+N}$$

(1.14)

All the computationally efficient FFT algorithms exploit these two basic characteristics of the phase factor.

#### 1.5 Radix-2 FFT Algorithms

By far the most widely used FFT algorithm is the radix-2 FFT algorithm. If N is a power of 2, then the dataset lends itself to a radix-2 FFT algorithm. The mathematical details of

implementation of the radix-2 FFT algorithm are beyond the scope of this thesis, but a brief description here will suffice.

- 1 The data set is successively divided (or decimated by 2) into odd and even sequences until resulting sequences are reduced to one-point sequences.

- 2 These one point sequences are then operated on and successively combined to produce the final results.

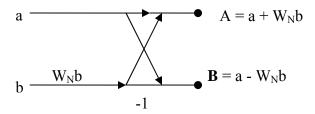

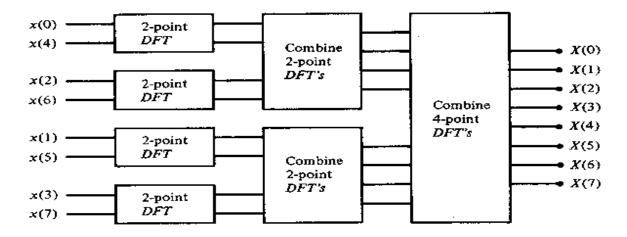

The basic operation at each stage, as illustrated in figure 1.3 is know as a butterfly. In this operation, take two complex numbers (a,b) multiply b by the appropriate phase factor and then add and subtract the product from a to form two new complex numbers (A,B). The combination of the results of each butterfly is shown in figure 1.4. [8]

Figure 1.3 Basic Butterfly Computation in the FFT Algorithm

Figure 1.4 Three stages in the computation of an N = 8-point DFT (Proakis P. 459)

An analysis of the reduction in computations in a radix-2 FFT versus a straight DFT is shown below in table 1.1

Table 1.1 Complexity of Direct Computation of the DFT vs FFT Algorithm

| Number of | Complex                   | Complex                  | Speed       |

|-----------|---------------------------|--------------------------|-------------|

| Points    | Multiplications in        | Multiplications in       | Improvement |

| N         | <b>Direct Computation</b> | FFT algorithm            | Factor      |

|           | $N^2$                     | (N/2) log <sub>2</sub> N |             |

| 4         | 16                        | 4                        | 4.0         |

| 8         | 64                        | 12                       | 5.3         |

| 16        | 256                       | 32                       | 8.0         |

| 32        | 1,024                     | 80                       | 12.8        |

| 64        | 4,096                     | 192                      | 21.3        |

| 128       | 16,384                    | 448                      | 36.6        |

| 256       | 65,536                    | 1,024                    | 64.0        |

| 512       | 262,144                   | 2,304                    | 113.8       |

| 1,024     | 1,048,576                 | 5,120                    | 204.8       |

|           |                           |                          |             |

There are a number of other kinds of FFTs such as Radix-4 and split Radix, which are also commonly used.

## 1.5 Hardware Implications of FFT

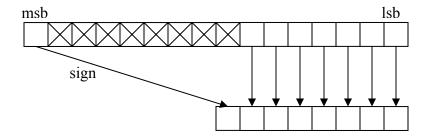

There are numerous multiplications at each butterfly stage of the FFT, which potentially leads to bit growth. The following excerpt from the Xilinx fast Fourier

transform Datasheet gives a summary of the considerations surrounding this bit growth: "For a radix-4 Decimation in Time FFT (4,096 is a radix-4 number), the values computed in a butterfly stage (except the second) can experience a growth to  $4\sqrt{2}\approx 5.657$ . For radix-2 (2,048 is a radix-2 number), the growth can be up to  $1+\sqrt{2}\approx 2.414$ . Various approaches are used to deal with this dynamic range expansion. There are three

Various approaches are used to deal with this dynamic range expansion. There are three main approaches:

- Performing the calculations with no scaling and carrying all significant integer bits to the end of the computation.

- Scaling at each stage using a fixed-scaling schedule

- Scaling automatically using block-floating point

All significant integer bits are retained when doing full-precision unscaled arithmetic. The width of the data path increases to accommodate the bit growth through the butterfly. The growth of the fractional bits created from the multiplication are truncated (or rounded) after the multiplication. The width of the output will be the (input width + number of stages + 1). This will accommodate the worst case scenario for bit growth. For example, a 1024-pt transform with an input of 16 bits consisting of 1 integer bit and 15 fractional bits, will have an output of 27 bits with 12 integer bits and 15 fractional bits.

When using scaling, a scaling schedule is used to scale by a factor of 1, 2, 4, or 8 in each stage. If scaling is insufficient, a butterfly output may grow beyond the dynamic range and cause an overflow. As a result of the scaling applied in the FFT implementation, the transform computed is a scaled transform.... If a radix-4 algorithm uses a scaling schedule of all 2's, the factor of 1/s will be equal to the factor of 1/N in the

inverse FFT equation. For radix-2, a scaling schedule of all 1's provides the factor of *1/N*. Otherwise, additional scaling is necessary."

With block floating point, each data point in a frame is scaled by the same amount, and the scaling is tracked by a block exponent. Scaling is performed only when necessary (to prevent data overflow), which is detected by the core. As with unscaled arithmetic, for scaled and block floating point arithmetic, the core does not have a specific location for the binary point. The location of the binary point in the output data is inherited from the input data and then shifted by the scaling applied. [9]

#### 2 STATEMENT OF NEED

#### 2.1 The Field Programmable Gate Array (FPGA)

The Field Programmable Gate Array or FPGA is an attractive hardware platform for implementation of signal processing algorithms. It provides a compromise between flexibility of a general purpose processor (GPP) and the speed of a dedicated Application Specific Integrated Circuit (ASIC). The development of an algorithm on an FPGA is not as rapid as a software approach for a GPP, but is considerably more rapid than a full custom design. In addition, the FPGA is easily reprogrammable and carries out many more effective operations per clock cycle than a GPP [10].

## 2.2 GPS Locking in on GPS Coarse Acquisition Code

The "lock" on a GPS signal is accomplished initially via the coarse acquisition or "C/A" code. Subsequent to this, the system will proceed to lock onto another code known as the P code using information gathered from the data embedded in the C/A code.

Under normal conditions GPS signal strength is about 130 dBm in a bandwidth of about 2 MHz where the thermal noise at R<sup>0</sup> is about -111 dBm [11]. In this case, 1 ms of data is adequate to acquire the signal. However, in many cases, such as indoors or in cloudy or forested areas, the GPS signal is 20 dB below the noise floor (-131 dBm), so instead of the usual 1 ms of data usually required, a receiver may have to process 10 ms of data to acquire the signal [12]. This provides special challenges for extracting the phase and carrier information from the received signal. The computational and time requirements are quite large, and if the acquisition is attempted in the time domain,

something on the order of 4\*N² multiplications and additions are required [13], where N represents the number of data samples. These computational demands discourage the performing acquisition in the time domain, especially in a weak signal environment where repeated locks may be required. A number of approaches, based in the frequency domain, have been developed to deal with this challenge. One way to speed up the acquisition process is to move the intermediate operations from the time domain to the frequency domain. This results in reduced time and power requirements for the complete operation. The FFT-and-multiply implementation of circular correlation is a very popular and standard method of transferring the correlation operation to the frequency domain. This is followed by an IFFT, which transfers the finished results back to the time domain [13, 14]. If a fast Fourier Transform (FFT) is used, the number of calculations is reduced to (2\*log<sub>2\*</sub>2N+l) \* 2N additions and half of the number of multiplications as before. Compared with the time domain approach the overall efficiency of the system improves exponentially as the number of data points increases.

There have been numerous software approaches to GPS acquisition because of their relative flexibility, but if real-time processing is wanted for long blocks of data, a hardware approach remains the most attractive because of speed of operation [15, 16, 17]. The following sections will cover the GPS C/A/ lock Algorithm in more detail.

#### 2.2.1 Spreading Data with C/A Code

Each of the 24 GPS satellite generates a number of unique PN sequences know as coarse acquisition code (C/A code), and precision code (P-code). This analysis will focus on the C/A code acquisition because this is the fundamental step in the GPS process.

Within each satellite, the C/A code is generated by a specialized class of PN code generators known as Gold Code generators, which are beyond the scope of this thesis. The C/A code is generated at a rate of 1.023 MHz and sampled at 5 MHz. The 50 Hz GPS navigation data that is needed for performing lock on the P code is also sampled at 5 MHz and multiplied by the C/A code samples. The product of this multiplication is now termed the C/A GPS signal. We now have a 2.046 MHz spread spectrum signal that is ready for transmission. The following step is the mixing of the spread spectrum signal up to 1575.42 MHz using Binary Phase shift keying or BPSK. In BPSK, the phase  $\phi$  of the carrier is  $\pm \pi$ , depending on whether the signal is a '1' or a '0'. The satellite then transmits the GPS C/A signal at a center frequency of 1575.42 MHz (L1). The transmitted signal can be written as:

$$S_{L1} = A_c C(t) D(t) \cos(2\pi f_1 t \phi) \tag{2.1}$$

Where  $S_{L1}$  is the signal at L1 frequency,  $A_c$  is the amplitude of the C/A code, C (t) =  $\pm 1$  represents the C/A code, D (t) =  $\pm 1$  is the navigation data code, f1 is the L1 frequency in Hz, and  $\phi$  is the initial phase of the carrier. [18]

# 2.2.2 Despreading at the Receiver

At the receiver side, in order to obtain the navigation data,  $S_{L1}$  has to be down converted back to base band and C(t) has to then be stripped from the signal yield D(t). Base-banding involves multiplying  $S_{L1}$  by  $cos(2\pi f_1 t \phi)$ . This is a very simplified approach to basebanding, and in reality a multi-stage approach is used. C(t) then has to be stripped from the resulting signal. This is achieved by a point multiplication with a

locally generated copy of C (t). The process of stripping the C (t) from a spread spectrum signal is often called "despreading" because the resulting spectrum is collapsed back to its original bandwidth-in our case 100 MHz. If the despreading is successful, the navigation data, D (t) is available and can be used to perform lock on the P code. If the despreading is not successful, the process of point multiplying the two signals needs to be repeated for different delays of the locally generated code. This process basically amounts to an autocorrelation function, which generally has its maximum when the two sequences are aligned. The mathematical representation of the correlation function, a(n) between two discrete time signals, a(n) and a(n) and is given as:

$$a(n) = \sum_{m=0}^{N} x(n)h(n+m), \qquad (2.2)$$

where N is the number of sample points in either discrete time signal.

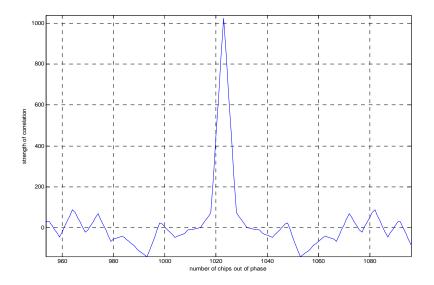

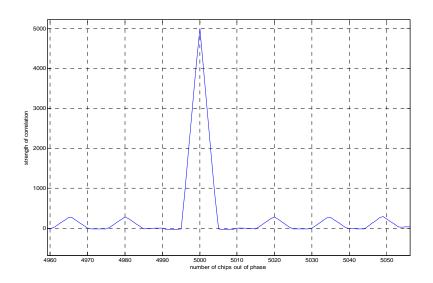

The figures below show the autocorrelation properties of 5,000 samples of C/A code and 1,023 samples of C/A code. It is apparent that the incoming signal and the locally generated code need to be very closely aligned to give a strong correlation peak needed for lock. If the two are not properly aligned, the spectrum remains spread and acquisition cannot follow. Another point to note is that the magnitude of the correlation peak is equal to the number of samples of data. Therefore if there is a very weak signal, a longer data record is needed for acquisition.

Figure 2.1 Autocorrelation of 1,023 C/A code chips

Figure 2.2 AutoCorrelation 5,000 C/A code chips.

The acquisition process in complicated by the fact that the receiver is moving relative to the satellite. This relative movement introduces a Doppler shift in frequency into the received signal. This Doppler shift must be accounted for otherwise acquisition is bound to fail. For a low speed vehicle, the Doppler shift is in the range of  $\pm 5$  KHz. For a high speed aircraft, the shift is in the range of  $\pm 10$  KHz [19]. Because of the unknown Doppler shift, the receiver must attempt a number of down conversion multiplications and select the one that gives an output that is closest to base band.

A successful acquisition therefore gives two important parameters about the received C/A code, namely the code phase and the Doppler shift. It is clear then that C/A code acquisition is a two-dimensional search among a number of C/A code phases and Doppler shifts. These two parameters are continually used to keep a lock on the incoming navigation data, which are needed to lock onto the P code.

One can perform C/A "acquisition" on two consecutive 10 ms of data. Between two consecutive sets of 10 ms of data there is at most one navigation data bit phase transition because the navigation data frequency is 50 Hz. Therefore, one set of these data will have no data bit transition and can result in successful acquisition. [20]

#### 2.2.3 Frequency Steps In Acquisition

It is necessary to determine the down conversion frequency steps needed in acquisition. Let us assume a  $\pm 10 KHz$  Doppler range. The frequency step is closely related to the length of data used. One chip difference between locally generated C/A code and the input signal will result in almost zero correlation. If the signals are out of step by half a chip, then there is partial correlation between them. Therefore the

maximum allowable frequency separation between the two signals is  $\pm 0.5$  cycles. If the data length is 1 ms, then a1 KHz signal will toggle once in 1 ms. The maximum frequency offset allowable from baseband is  $\pm 0.5$  of a cycle or  $\pm 0.5$  Hz/ ms. For a 1 ms dataset, this maximum frequency step is 1KHz in order to allow for partial correlation. This arrangement will center the input signal in between baseband and 1 KHz in the worst case. If the 10 ms of data are taken, then a 100 Hz frequency step is needed. This fits with conventional FFT results in which the frequency resolution is inversely proportional to the number of points in the FFT [21]. The number of FFT bins increases by a factor of 10 and the memory needed to hold the data record increases by the factor of 10. The above discussion brings home the point of using as short a data record as possible for acquisition. The hardware requirements and operations increase by a factor of about 100 for a 10 fold increase in the data record.

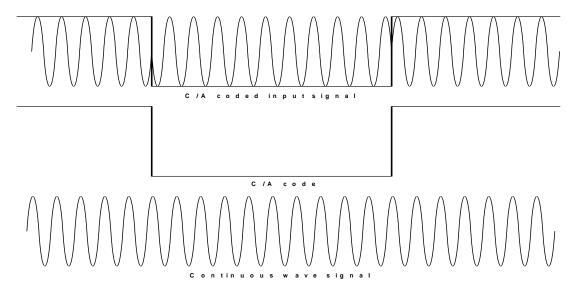

# 2.2.4 C/A Code Multiplication and The FFT

Acquisition has as its objective the dispreading of the input signal and obtaining the carrier frequency. Assuming the reference C/A code has the same phase as the C/A code in the transmitted GPS signal, then the input signal will be despread and become a narrowband signal continuous wave (cw) signal as shown in the figure 2.3. The top plot is an RF signal carrying the C/A code. The second plot is the locally generated reference C/A code, and the bottom plot is the result of multiplying the two top signals, assuming they are phase aligned with respect to the C/A code. The FFT of the bottom signal would reveal the Doppler shift and then the carrier could be stripped off the cw signal to reveal

the navigation data. The order of operations is matter of preference and in some implementations the carrier is stripped off before the spectrum is despread. If 1 ms of data sampled at 5 MHz were used, then the record would consist of 5,000 samples. The DFT of this signal would have a frequency resolution of  $\frac{5\times10^6}{5\times10^3}$  or 1 KHz. A 5,000 point DFT generates 5,000 frequency components, but the first 2,500 contain the majority of the energy relative to last 2,500 points. If the frequency range of interest is  $\pm10$ KHz,

Figure 2.3 C/A coded input signal multiplied by C/A code Source: Tsui, Fundamentals of GPS Receivers P 137

then in some implementations, only 21 frequency components need to be calculated if speed is an issue.

# 3 FREQUENCY DOMAIN BASED APPROACHES TO ACQUISITION.

#### 3.1 Time-Domain Circular Correlation

In order to complete the necessary acquisition operations in real-time, a number of approaches have been used. They range from the combination of time and frequency domain discussed above to more rapid frequency domain based approaches.

Since this thesis is focusing in a frequency domain approach, the discussion will be limited to this area.

Before going into details about frequency domain acquisition, a mathematical exploration of the circular correlation is in order. If a signal passes through a linear time invariant (LTI) system, the output of that system can be found by either convolution in the time domain or through the Fourier Transform in the frequency domain. We will limit our discussion to discrete LTI systems because of the digital nature of today's computers. If the impulse response of a discrete LTI system is given as h(n), then an input signal x(n) will produce an output y(n) through convolution as follows:

$$y(n) = \sum_{m=0}^{N-1} x(m)h(n-m)$$

(3.1)

Note the similarity to the correlation function expressed earlier. The exception is the negative sign in the second term. Convolution in the time domain is equivalent to multiplication in the frequency domain, hence the above expression transforms to:

$$Y(k) = H(k) \sum_{m=0}^{N-1} x(m) e^{(-j2\pi mk)/N} = X(k)H(k)$$

(3.2)

where Y(k), X(k) and H(k) are the DFTs of y(n), x(n) and h(n). These convolution expressions are often termed **circular convolution** because the results are periodic due the periodic nature of the DFT.

The acquisition algorithm uses correlation and not convolution, but the two processes are very similar, with a simple flip of sign on one of the operands. In the time domain circular correlation is given by:

$$a(n) = \sum_{m=0}^{N-1} x(m)h(n+m);$$

(3.3)

in the frequency domain the function is given by the formula:

$$|A(k)| = |X^*(k)H(k)| = |X(k)H^*(k)|,$$

(3.4)

where  $X^*(k)$  and  $H^*(k)$  are the complex conjugates of X(k) and H(k).

As mentioned earlier, this formula represents the circular correlation of the signal x(n) and h(n), which is the required operation for acquisition.

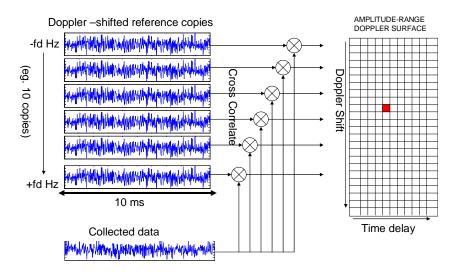

## 3.2 Resolving range and Doppler uncertainties

The GPS signals that are collected have two uncertainties associated with them. These are in the realm of velocity (which gives rise to a Doppler ambiguity) and distance (which gives rise to a range ambiguity). This combination of uncertainties means that there are a large number of range-Doppler estimations that must be carried out in a fairly short period of time. For example, if there are 10 possible Doppler shifts and 5,000 possible time delays, then there are a total of 50,000 combinations of range-Doppler

uncertainties to consider. This concept is illustrated in Figure 3.1. This algorithm operates on a10-ms block of data and generates Doppler shifted copies of the input signal and correlates them with the baseband reference code. This result is sometimes referred to as **the ambiguity function** of a signal and is often used in RADAR processing. [22] The algorithm will give a global maximum that corresponds to the best Doppler and delay match for the input data. In discrete-time notation, the ambiguity function is written as:

$$|\Psi(\tau,\nu)| = \left| \sum_{n=0}^{N-1} x(n)h * (n-\tau)e^{j2\pi \nu n/N} \right|$$

(3.5)

Figure 3.1 The Ambiguity Function Concept

If each block of 10-ms input data were used for correlation with 10-ms of the reference C/A code, the number of calculations would be prohibitive. A modified algorithm is used in which the input signal is broken up into 10 blocks of 1-ms and processed in parallel.

## 3.3 Noise and Amplification Considerations

The GPS signal is typically about -130 dBm at the antenna [23]. The maximum processing gain of a typical GPS system is given by:

$10 \log (\text{chip rate /data rate}) = 10 \log (1.023 \text{ MHz/} 50 \text{ Hz}) = 43 \text{ dB for this system.}$

The formula for available noise power N<sub>i</sub>, in watts, at the input of the receiver is:

$$N_i = kTB$$

watts, (3.5)

where k is Boltzman's constant (1.38 X  $10^{-23}$  J/K), T is the absolute temperature of a 50  $\Omega$  resistor R, and B is the bandwidth of the receiver in Hz. Over a sampled null-to-null bandwidth of 2.046 MHz, the integrated thermal noise power (T = 290 K) expressed in dBm (dB relative to a milliwatt) is given as follows:

Ni =  $1.38 \times 10^{-23} \times 290 \times 2.046 \times 10^6 =$ **8.1881 x 10^{-15} W** over a 2.046 MHz bandwidth. If we take this power relative to a milliwatt and find the power per Hz, then we get:

Ni =

$$\frac{8.1881 \times 10^{-15}}{10^{-3} \times 2.046 \times 10^{6}} = 4 \times 10^{-18}$$

(3.6)

We can then take log to base 10 and multiply by 10.

So now  $N_i(dBm) = 10*log10(4 x 10^{-18}) = -174 dBm/Hz$ .

This works out to approximately -111 dBm, for a 2.046 MHz bandwidth [24]. In this arrangement, the GPS signal is 19 dB below the noise floor at the input to the receiver. One common approach is to amplify the signal so that the noise floor at right at the maximum range of the ADC. A typical ADC will have a 100 mV dynamic range. The corresponding power is:

$$P = \frac{V^2}{2R} = \frac{(0.1)^2}{2 \times 50} = 0.1 \text{ mW} = -10 \text{ dBm}.$$

(3.7)

Since the noise floor is -111 dBm, then 101 dB of amplification would be adequate to get it to this range. In the RF chain there are insertion losses caused by mixers, filters and cables and these must also be compensated for when calculating the required net gain of the system. We want to avoid saturation of the ADC and also wastage of the quantization levels.

Assuming a base band processor requires a Bit Error Rate (BER) of  $10^{-5}$ , the corresponding post correlator  $E_b/N_0$  for the BPSK modulation used is no less than 9.5 dB (assuming additive white Gaussian noise).  $E_b/N_0$  is defined as the ratio of energy per bit to the spectral noise density [25]. Subtracting 43 dB of theoretical processing gain from the required 9.5 dB post correlator  $E_b/N_0$ , the minimum SNR at the correlator input is - 33.5 dB. Assuming implementation losses of 3.3 dB for software GPS, the SNR required at the quantizer input is – 30 dB. Assuming insertion losses of about 10 dB for amplifiers and filters, the GPS signal can theoretically be 23.5 dB below the noise floor and still be acquired. Using results of experimental work by Tsui et.al, very low energy signals of - 20 dB relative to the noise floor can be acquired. A block size of 10 ms input data is found to be adequate for C/A code acquisition at these low signal levels. The longer the data record used, the weaker the signals that can be acquired.

This value for block size yields a searching frequency resolution of 100 Hz.

This operation is suitable for a block of data. The data are sampled at 5 MHz and stored in memory for use as needed by the C/A system.

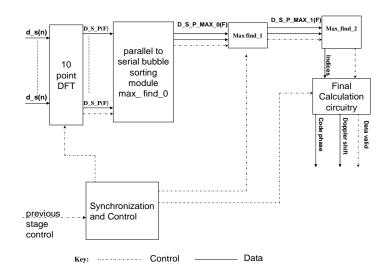

## 3.3 Acquisition By FFT Based Circular Correlation

Van Nee and Coenen have devised a technique to perform the two dimensional search for code phase and Doppler shift in a parallel manner [26]. The algorithm used in this paper is based largely on this technique with some modifications for handing a longer data record. Assuming we know the satellite were are trying to acquire, following steps, as shown in Figure 3.1, are taken to perform acquisition on the input data:

- Downconvert the input data y (n) to 10 slightly different frequencies close to baseband by multiplication with a 10 different complex RF signals f<sub>i</sub> separated by 1 KHz. The resulting complex signals are now called d c(n)[i] where i = 1 to 10.

- For each i, perform the DFT on the 10 ms of d\_c (n) in 1ms blocks, and convert the input into the frequency domain as D\_C (k) where n = k = 0 to 4999 for each 1 ms block. This will result in 10 different frames of D\_C (k) each of length 5,000.

- 3. Take the complex conjugate of each frame of  $D_C(k)$  and the outputs become  $D_C(k)^*$ .

- 4. Discard the second half of the D\_C(k)\* sequence, we only lose a small amount of energy from this step. There are now 10 frames of D\_C(k) of length 2,500.

- 5. Generate one local reference C/A code c\_a (n) of length 1 ms for the given satellite. The local code must be sampled at 5 MHz to generate 5,000 samples.

- 6. Perform DFT on c\_a(n) to transform it to the frequency domain as C\_A(k).

- 7. Discard the second half of the C\_A(k) sequence. 2,500 samples remain.

- 8. Multiply C\_A(k) and each frame of D\_C(k) point by point and call the result D\_S(k). There are 10 frames of D\_S(k), each of length 2,500.

- 9. Take the inverse DFT of each frame of D\_S(k) to transform the result into the time domain as d\_s(n). There are now 10 frames of d\_s(n).

- 10. Store the frames in parallel in a 10 \* 2,500 matrix.

- 11. Access the matrix one column at a time and perform a 10 point DFT on each column and repeat until all columns have been transformed. The result is a 10\*2,500 matrix in called D\_S\_P(k).

- 12. Sort through the matrix to locate the maximum of the | D\_S\_P(k)|. Store the row and column index of this maximum.

- 13. Repeat steps 2 through 12 for all i to generate 10 maxima and their associated row and column indices.

- 14. Sort through these maxima to generate a global maximum with an associated row, column and i index.

- 15. Via some simple arithmetic shown in the following equations, decode these three indices to infer the C/A code phase and carrier Doppler shift.

The complex RF signal is represented by the equation:

$$e^{j\omega t} = \cos(\omega t) + \sin(\omega t) \tag{3.8}$$

Figure 3.1 A block diagram of the proposed C/A code acquisition process. The equations for decoding the code phase are shown below. Let us define the inputs as

$i\_c$  is the column index,  $m\_c$  is the stack index, and  $m\_f$  is the row index.

The code phase in samples,  $c_p$  is therefore calculated as:

follows:

$$c_p = (2500 - i_c) * 2$$

(3.9)

Multiplication by 2 is as a result of the dropping of the second half of the DFT results in steps 4 and 7. The result needs to be mapped back from a data set of 2,500 to a data set of 5,000. The code phase time resolution is accurate to 200 ns in this approach. Since the code chips are about 977 ns long, this is well within the half-chip resolution needed by the system.

The calculation for Doppler frequency, dopp is a little more involved and depends on the value of the row index  $m_f$ . If  $m_f$  is less than or equal to 5, then the following calculation is used:

$$dopp = (m_c - 10/2)*1000 + (m_f - 1)*100$$

(3.10)

If  $m_f$  is greater than 5, then the following calculation is used:

$$dopp = (m_c - 10/2)*1000 + (m_f - 11)*100$$

(3.11)

This acquisition process repeats every 10 ms, with a fresh block of data in order to keep a lock on the C/A code for a given satellite.

#### 3.4 Threshold Values

In the above discussion, no mention of threshold has been made, but this is a very important consideration. Depending on the environment where this GPS receiver is operating, a threshold is set to determine if the maximum is a valid or spurious maximum. So not only does the maximum have to be determined, it then has to be compared to a threshold to determine its validity. The discussion and calculation of threshold is beyond the scope of this paper, but it is important to be aware that generating a maximum is not sufficient for determining if acquisition is successful.

#### 4 ARCHITECTURE AND DESIGN CONSIDERATIONS

The FFT based C/A code lock algorithm chapter was written in first in MATLAB to demonstrate proof of concept and then was implemented in VHDL code targeted to a Xilinx Virtex II-Pro FPGA. There are numerous choices an engineer must make when translating from high level code such as MATLAB, to more hardware-faithful code such as VHDL. This section highlights some of the design choices that were made to implement the design efficiently in digital FPGA hardware.

### 4.1 Design Choices

## 4.1.1 Buffering

An effective architecture will require that while the first 10 ms of data are being processed; the second 10 ms worth of data is being buffered. The 10 ms worth of data is equal to 50,000 samples. This leads to a decision of designing a 2-port RAM of depth 100,000 to read from and write to the buffer at the same time. The designed 2-port RAM is more effective than the FIFO generated by the Xilinx core generator for two reasons:

- Xilinx Intellectual Property (IP) cores only generate FIFOs with memory size of radix-2, so the closest size to 100,000 is around 131,072 leading to a waste of resources.

- 2. The FIFO has a "quirk" called first-word-fall-through after reset, which would cause errors and requires extra hardware for the control logic.

## **4.1.2** Sample Rate Conversion

Another design challenge was the generation of the C/A code samples. The code samples correspond to the code that is generated at 1.023 MHz and sampled at 5 MHz. One could generate a 1.023 MHz clock for a LFSR that generates the code, and then use a separate 5 MHz clock for the sampling circuit. This however would lead to a synchronization issue between the two clock domains. Both clocks would have to be rising at exactly the same time to ensure alignment of the code samples with the originally generated code. Even if this issue could be overcome, there is yet another challenge to design FPGA circuits that can produce a 1.023 MHz clock from the existing crystal-generated on-chip clock. The ratio of 5 to 1.023 is not a rational number and hence cannot be used as an input to the delay locked loop (DLL) that is used to generate the clocks of desired frequency.

The solution that was arrived at (with assistance from some Air Force Engineers) is as shown in figure 4.1: A counter is set to increment by multiples of 1,023, and 5,000 is subtracted from the count every time the count exceeds 5,000. So basically we are dividing 5,000 by 1,023 and only keeping the remainder. This cycle repeats indefinitely. An output is enabled for one clock every time the count exceeds 5,000. This signal enables the shift logic of the code generator, advancing it by one state. To the outside world it then appears that the 1.023 MHz code is being sampled at 5 MHz.

A check with the MATLAB generated and sampled C/A code reveals identical sequences.

Figure 4.1. Count sequence of LFSR\_enable module showing enable signal

Figure 4.2. C/A code generator showing sample rate conversion

## 4.1.3 Mapping 5,000 Point DFT To Hardware

The major obstacle to be overcome with this design was the mapping of a 5,000 point DFT from the MATLAB onto the hardware. In the MATLAB model, the input

data is processed in frames of 5,000. A 5,000 point DFT is straightforward in MATLAB because of the use of floating point calculations. In fixed-point hardware, this is a challenge. All hardware implemented DFTs are radix-2 or radix-4 FFTs because they need to be completed in real-time. The closest hardware implementation of a 5,000-point DFT is a 4,096 point FFT. Therefore, there needs to be a way to convert the 5,000 samples to 4,096 samples. One choice explored was the averaging correlation technique [27]. In this technique, the 5,000 samples would be averaged to 4,096 samples prior to application of the FFT. Although there has been success using the averaging correlation method [27, 28], it is relatively hardware and time-intensive. It seems to work well for a 1 ms acquisition, but for a 10 ms acquisition, it would prove too cumbersome. In the interest of hardware simplicity a pseudo-random sampling technique is proposed instead. If a pseudo-random scheme is used, then the data set retains most of its autocorrelation properties as shown in Figure 4.2. These autocorrelation properties are important for direct sequence spread spectrum acquisition [29].

Figure 4.3 Autocorrelation properties of C/A code before and after "subsampling." After experimenting with a few "sub-sampling" algorithms, an effective algorithm was proposed by D. Lin of WPAB, which proves to give the desired results. The algorithm is described below:

- 1) Out of every 11 samples, the 5<sup>th</sup> and 11<sup>th</sup> samples are dropped. This procedure is repeated 90 times. We would have now processed 900 input samples and stored 810 samples and dropped 90 samples.

- 2) For the 91<sup>st</sup> set of 11, only the 5<sup>th</sup> sample is dropped. We have now processed 1,000 samples and having stored 819 samples and discarded 181 samples.

- 3) Steps 1 and 2 are repeated 5 times for each set of 1,000 input samples to yield 4,095 stored samples. The 4,096<sup>th</sup> stored sample is always a zero. Now there are a total of 4,096 samples for further possessing. This "sub-sampling" technique is applied to both the C/A code and the downconverted data preserve the relative sample position of the code to the incoming data.

## 4.1.4 Direct Digital Synthesizer (DDS) Challenges

Another challenge was the generation of the complex RF sinusoids used for downconversion. In MATLAB, one can generate any arbitrary frequency and sample it at any other arbitrary frequency as long as the Nyquist criterion is met, i.e. the sampling frequency must be at least twice the bandwidth of the signal being sampled. In hardware, the RF signal is generated by a Direct Digital Synthesizer or DDS. The frequencies generated by the DDS are constrained by the input clock frequency. The DDS is required to generate the equivalent of complex sinusoids ranging in frequency from (1.25MHz - 4 KHz) to (1.25 MHz + 5 KHz), and sampled at 5 MHz. However, the rest of the system is configured to run at 100 MHz, so the DDS must be configured to produce frequencies 20 times (100/5) the actual value stated. For example a 25 MHz RF signal sampled at 100 MHz would generate the same sample set as 1.25 MHz sampled at 5 MHz.

#### 5 GLOBAL VIEW OF DATAFLOW THROUGH THE SYSTEM

The dataflow is partitioned into 4 functional domains: 1) Data Capture Domain; 2) 4,096 FFT domain; 3) 2,048 IFFT domain; and 4) 10 point DFT / Sorting Domain. Considering these breakdowns, each functional domain will discussed as follows.

### 5.1 Data Capture Domain.

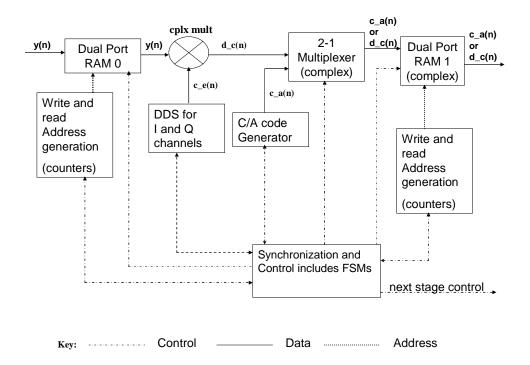

This domain functions to capture the data that is streaming in at 5 MHz, downconvert it to baseband, "subsample" it, and stream it to the 4,096 FFT at 100 MHz. It also regulates the generation and storage of the C/A code. The Data Capture Domain consists of two dual-port RAMs, a Direct Digital Synthesizer, the C/A code generator, a complex multiplier, counters, and some multiplexing ability to allow reuse of hardware. The block diagram is shown in figure 5.1.

Figure 5.1. The Data Capture Domain

#### 5.1.1 Details of Datapaths In The Data Capture Domain

#### **5.1.1.1** The Dual Port RAMs

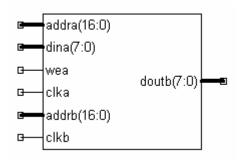

Each dual-port RAM has two address ports, one read port and one write port, and allows data to be written to it from one port, while data is being read from it via a different port. The ports can operate on different clock domains.

As shown in Figure 5.1 the **Dual Port RAM 0** is of width 8 bits and depth of 100,000, and is configured as a circular buffer that continuously reads in the data at 5 MHz. **Dual Port RAM 0** buffers the incoming 5 MHz data streams. When this RAM is about 39,000 full, or 89,000 full, we start to read from it at 100 MHz for further There is **control** so that when we finish reading the first 50,000 samples, we wait until the buffer is 89,000 samples full again before we read from it again. This is done continuously as long as the system is running. Once **Dual Port RAM 0** is almost full (39,000 or 89,000), the buffered data is then complex multiplied at 100 MHz. The 50,000 block of data is read from Dual Port RAM using two counters; a 0 to 50,000 and a 50,000 to 100,000 counter each running at 100MHz. The counters are enabled as needed. The **Dual Port RAM 1** is actually two dual port RAMs, each of depth 40,960 and width 16 bits. They store the real and imaginary "subsampled" downconverted data for streaming to the FFT module. When the system is initialized for given satellite, the **Dual Port RAM 1** stores the "subsampled" C/A code (which is all real) hence the need for a multiplexer. This C/A code is streamed to the 4,096 FFT for further processing before the primary data is written to **Dual Port RAM 1**. This initialization process occurs very early on in the cycle and is complete within about 95 µs of asserting global start.

Figure 5.2 Dual Port RAM used in Data Capture Domain

#### **5.1.1.2** Counters

- 1. Counter\_99999 is configured to count to 99,999 and asserts two terminal count signals, tc\_0 when its count reaches 48,000 and tc\_1 when the count reaches 98,000. When the count reaches 99,999, it rolls over to 0 and restarts its count. This counter resets to 0 and needs an enable signal to increment. This counter generates the write address to the Dual Port RAM 0 to collect the streaming 5 MHz input.

- 2. Counter\_50000 asserts its terminal count, tc\_0 signal when it reaches 50,000. This counter generates the read address for read operations from the bottom half of the Dual Port RAM 0.

- 3. Counter 50000\_100000 counts from 50,000 to 100,000 and asserts its terminal count signal when it reaches 100,000. This counter generates the read address for read operations from the top half of Dual Port RAM 0.

- 4. There are two instances of **Counter\_40960**, which has a terminal count of 40,960. It asserts  $tc\_0$  when the count reaches 31,000 and  $tc\_1$  when the count reaches 40,960. These counters are used to control the write and read address respectively of the Dual -port RAM 1. The one that controls the write address is designated as **Counter\_40960\_w**, and the one that controls the read as **Counter\_40960\_r**.

- 5. Counter\_4096 asserts its terminal count signal, tc\_0 at its terminal count of 4,096.

This count is used to control the asserting of the start signal for the FFT module every 4,096 clocks.

- 6. There are also two counters with a terminal count of 4 and 5 respectively. These counters are used to control which data points are "dropped" during "subsampling" via the manipulation of the write signal to Dual Port RAM 1.

#### **5.1.1.3** The Direct Digital Synthesizer (DDS)

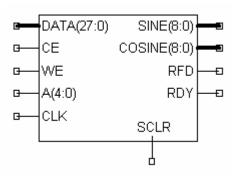

The **DDS** is responsible for generation of the complex RF signal. It is generated by the Xilinx Logicore IP generator. The DDS has a large number of active high inputs. The relevant ones are as follows: 28 bit *data* for programming new frequencies, *write\_enable* for clocking in the new frequency, and *clock\_enable* for enabling the generation of outputs. When programming in a new frequency, the *clock\_enable* is deasserted while the *write\_enable* is asserted for one clock.

The relevant outputs from the **DDS** are the 9-bit *sine* and *cosine* outputs, which are out of phase by  $\pi/2$ , and the active high  $data\_ready$  output, which indicates when the outputs samples are available and valid. Figure 5.3 shows the DDS schematic symbol.

Figure 5.3 Schematic symbol of the Direct Digital Synthesizer

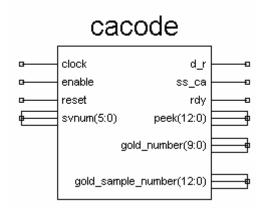

#### **5.1.1.4** The C/A Code Generator (CCG)

The C/A code generator, **cacode** is a Gold code generation module, which consists of a pair of Linear Feedback Shift Registers, a controller that schedules loading and shifting the code generator, a ROM for the initial fills, and a clock division circuit for controlling the generation of a sampled version of the code. This module, although clocked at 100 MHz, generates the equivalent of 5 MHz C/A code samples. The inputs to this, which are self-explanatory are: *enable*, *reset*, *and svnum*, the satellite number. The *enable* input needs to remain asserted for the code to be continuously generated. The relevant outputs are the *ss\_ca*, the code samples and *data\_ready*, indicating the data output data are valid. This module has to be reset before programming in a new satellite.

There are also a number of other output busses named *peek*, *gold\_number*,and *gold\_sample\_number*,which are used for synchronization and debugging.

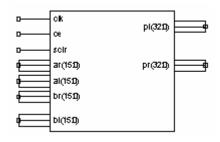

Figure 5.4 Schematic Symbol of C/A code Generator

#### **5.1.1.4** The Complex Multiplier