## Modelling and Control of Power Inverters in Microgrids

Thesis submitted in accordance with the requirements of the University of Liverpool for the degree of Doctor in Philosophy by X. Zhang

June 2012

## Abstract

Power electronic converter systems play an important role in the interconnection of renewable energy sources in microgrids and utility grid. The interface between energy sources and microgrids is usually implemented by digitally controlled power inverters. This thesis provides a discrete modelling and design method for the digitally controlled inverters in microgrids.

The fundamentals and background of digital control of power inverters are introduced. The small-signal models for digital pulse-width-modulations (PWMs) with delay effects are derived. Based on the models, the controllers can be designed using several methods according to the block diagrams. The simulation software and experimental environment for the digitally controlled inverters are described.

For inverters operating in parallel, a linear voltage control scheme with dutyratio feedforward is proposed. The control parameters are chosen according to the stable operating condition derived in z-domain. The closed-loop transfer function and output impedance for both the classical controller and the proposed controller are derived theoretically. A comparison reveals the advantages of the proposed control scheme: a unity closed-loop gain, no phase shift, good current sharing and low total harmonic distortion (THD) of the output voltage. The theoretical results are verified by the experimental setup of a system with two digitally controlled inverters connected in parallel.

For digitally controlled grid-connected inverters with LCL filters, new smallsignal z-domain models are deduced. The proposed methods model the inverters including different delay effects under most possible circumstances, which allows a direct design for controllers in z-domain. The stability boundaries obtained from the root loci of the classic models and the proposed models are compared to the simulation results, showing that the proposed z-domain models are more accurate in predicting instabilities. Experimental results are presented, showing the proposed models are also capable of predicting the values of control variables at the true sampling instants.

The phase-shifted modulated multisampled multilevel inverter is studied. The filter current ripple frequency of the multilevel inverters is increased by the phase-shifted PWM. The small-signal z-domain model is derived. Compared to the bipolar switched inverter, the multisampled multilevel inverter is characterized by the capability of achieving higher feedback control gains, which improves the control performance. An experimental prototype based on a 10 kHz switching frequency, 80 kHz sampling frequency five-level single-phase H bridge inverter is tested to demonstrate the validity of the analysis.

# Contents

| A             | bstra | $\mathbf{ct}$ |                                                                                         | i            |

|---------------|-------|---------------|-----------------------------------------------------------------------------------------|--------------|

| C             | onter | nts           |                                                                                         | $\mathbf{v}$ |

| $\mathbf{Li}$ | st of | Figur         | es                                                                                      | xiii         |

| $\mathbf{Li}$ | st of | Table         | s                                                                                       | xiv          |

| A             | cknov | wledge        | ement                                                                                   | xv           |

| 1             | Intr  | oduct         | ion                                                                                     | 1            |

|               | 1.1   | Power         | electronics in microgrids                                                               | 1            |

|               | 1.2   | Digita        | al control of power inverters                                                           | 2            |

|               | 1.3   | Proble        | ems in digitally controlled power inverters                                             | 3            |

|               |       | 1.3.1         | System stability                                                                        | 3            |

|               |       | 1.3.2         | Controller design                                                                       | 4            |

|               |       | 1.3.3         | Performance of controller                                                               | 4            |

|               |       | 1.3.4         | Power quality requirements                                                              | 5            |

|               | 1.4   | Overv         | view of the thesis                                                                      | 5            |

| <b>2</b>      | Bac   | kgrou         | nd                                                                                      | 8            |

|               | 2.1   | Introd        | luction                                                                                 | 8            |

|               | 2.2   | Funda         | amentals of digital control in power electronics                                        | 9            |

|               |       | 2.2.1         | Ideal sampler and ZOH                                                                   | 10           |

|               |       | 2.2.2         | z-Transform                                                                             | 11           |

|               |       | 2.2.3         | Discretization of controller                                                            | 12           |

|               | 2.3   | State         | of the art of modelling techniques for digitally controlled                             |              |

|               |       | switch        | ning converters                                                                         | 13           |

|               |       | 2.3.1         | Classic average model                                                                   | 13           |

|               |       | 2.3.2         | Small-signal $s$ -domain model                                                          | 13           |

|               |       | 2.3.3         | Classic z-domain model $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 14           |

|               |       | 2.3.4         | Small-signal z-domain model                                                             | 14           |

|   | 2.4 | State of  | the art of digital control techniques for power inverters .          | 15 |

|---|-----|-----------|----------------------------------------------------------------------|----|

|   |     | 2.4.1 C   | Classic controllers                                                  | 15 |

|   |     | 2.4.2 F   | Repetitive-based controllers                                         | 16 |

|   |     | 2.4.3 I   | Deadbeat controllers                                                 | 17 |

|   |     | 2.4.4 L   | linear controllers                                                   | 17 |

| 3 | Dig | itally Co | ontrolled Switching Converters with Synchronously                    |    |

|   | San | pled Pa   | use-Width-Modulators                                                 | 18 |

|   | 3.1 | Introduc  | etion                                                                | 18 |

|   | 3.2 | Small-sig | gnal modelling of uniformly-sampled digital PWMs with                |    |

|   |     | delay eff | ects                                                                 | 19 |

|   |     | 3.2.1 I   | Digital PWM models in shadow mode                                    | 19 |

|   |     | 3.2.2 I   | Digital PWM models in immediate mode                                 | 22 |

|   | 3.3 | Modellin  | ng H bridges with synchronously sampled PWMs                         | 26 |

|   |     | 3.3.1 E   | Bipolar switched H bridges                                           | 27 |

|   |     | 3.3.2 U   | Jnipolar switched H bridges                                          | 29 |

|   | 3.4 | Block di  | agrams of digitally controlled switching converters                  | 31 |

|   |     | 3.4.1 E   | Block diagram of a single control loop in $s$ -domain $\ldots$       | 31 |

|   |     | 3.4.2 E   | Block diagram of a single control loop in small-signal $z$ -         |    |

|   |     | d         | lomain                                                               | 32 |

|   |     | 3.4.3 E   | Block diagram of cascaded control loops in $s$ -domain $\ldots$      | 33 |

|   |     | 3.4.4 E   | Block diagram of cascaded control loops in small-signal $z$ -        |    |

|   |     | d         | lomain                                                               | 34 |

|   | 3.5 | Design o  | of digital controllers                                               | 35 |

|   |     | 3.5.1 I   | Design by simulation                                                 | 36 |

|   |     | 3.5.2 I   | Design by root locus                                                 | 37 |

|   |     | 3.5.3 I   | Design by frequency response                                         | 39 |

|   | 3.6 | Simulati  | on and experimental preparations                                     | 40 |

|   |     | 3.6.1 S   | Simulation environment                                               | 40 |

|   |     | 3.6.2 E   | Experimental setup                                                   | 40 |

|   | 3.7 | Conclusi  | ons                                                                  | 43 |

| 4 | Des | ign of D  | igitally Controlled Parallel Inverters                               | 44 |

|   | 4.1 | Introduc  | tion                                                                 | 44 |

|   | 4.2 | Small-sig | gnal $z$ -domain analysis of digitally controlled inverters $\ldots$ | 46 |

|   | 4.3 | Controll  | er design for power sharing                                          | 52 |

|   |     | 4.3.1 F   | Proportional plus resonant feedback control                          | 54 |

|   |     | 4.3.2 L   | inear voltage feedback scheme using duty-ratio feedforward           | 55 |

|   |     | 4.3.3 S   | Sensitivities                                                        | 59 |

|   | 4.4 | Simulati  | on results                                                           | 60 |

|                  | 4.5      | Experimental results                                                 | 63         |

|------------------|----------|----------------------------------------------------------------------|------------|

|                  | 4.6      | Conclusion                                                           | 69         |

| <b>5</b>         | Mo       | delling of Digitally Controlled Grid-Connected Inverters with        | 1          |

| 0                |          | L Filters                                                            | 73         |

|                  | 5.1      | Introduction                                                         | 73         |

|                  | 5.2      | Classic average models for grid-connected inverters                  | . s<br>75  |

|                  | 5.3      | Small-signal z-domain models for digitally controlled grid-connected |            |

|                  |          | inverters                                                            | 80         |

|                  |          | 5.3.1 Discrete models for grid-connected inverters                   | 81         |

|                  |          | 5.3.2 Stability analysis for internal current loop                   | 84         |

|                  |          | 5.3.3 Discrete root loci design                                      | 86         |

|                  | 5.4      | Simulation Results                                                   | 87         |

|                  | 5.5      | Experimental Results                                                 | 93         |

|                  |          | 5.5.1 Steady-state responses                                         | 94         |

|                  |          | 5.5.2 Transient responses                                            | 96         |

|                  | 5.6      | Conclusion                                                           | 99         |

| 0                | <b>.</b> |                                                                      |            |

| 6                |          | delling of Multisampled Multilevel Inverters with Improved           |            |

|                  |          |                                                                      | 101        |

|                  | 6.1      | Introduction                                                         | 101        |

|                  | 6.2      |                                                                      | 102        |

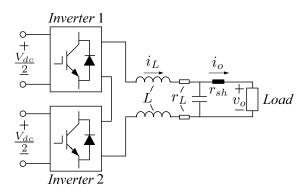

|                  | 6.3      | Multisampled multilevel inverters                                    | 106<br>107 |

|                  |          | <ul><li>6.3.1 System configuration</li></ul>                         | 107        |

|                  |          | 6.3.3 Current ripple reduction                                       | 107        |

|                  |          | 6.3.4 Small-signal <i>z</i> -domain modelling for switching function |            |

|                  |          | 6.3.5 Modulation error                                               |            |

|                  | 6.4      | Simulation results                                                   |            |

|                  | 6.5      | Experimental results                                                 |            |

|                  | 6.6      | Conclusion                                                           |            |

|                  | 0.0      |                                                                      |            |

| 7                | Coi      |                                                                      | 124        |

|                  | 7.1      | Conclusions                                                          | 124        |

|                  | 7.2      | Future work                                                          | 127        |

| R                | efere    | ences                                                                | 128        |

| $\mathbf{A}_{j}$ | ppen     | dix A z-Transforms for Stand-Alone Inverters                         | 140        |

| A                | ppen     | ndix B z-Transforms for Grid-Connected Inverters                     | 143        |

# List of Figures

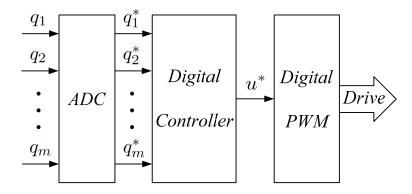

| 2.1  | The schematic of a typical digital controller                                                                                                                       | 9   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2  | Block diagrams of the transfer functions. (a) Continuous-time sys-                                                                                                  |     |

|      | tem. (b) Discrete-time system                                                                                                                                       | 11  |

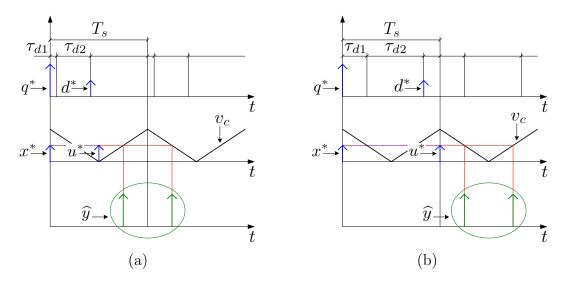

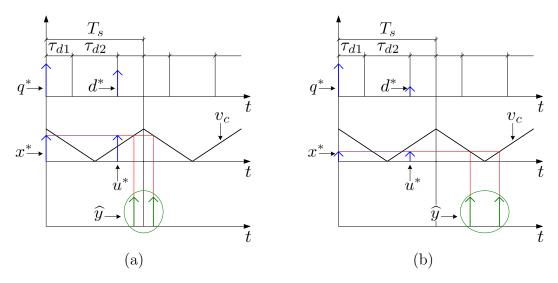

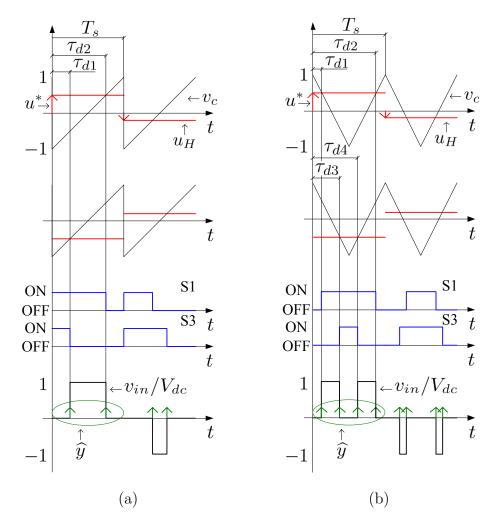

| 3.1  | Key waveforms of the sawtooth PWM in shadow mode. (a) Begin-                                                                                                        |     |

|      | of-on-time modulator. (b) End-of-on-time modulator                                                                                                                  | 20  |

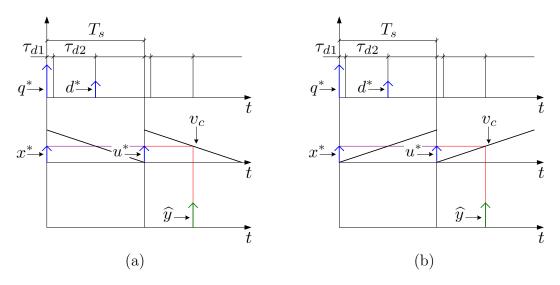

| 3.2  | Key waveforms of the symmetric-on-time PWM in shadow mode                                                                                                           |     |

|      | with duty-ratio updated when counter reaches zero value. (a) $\tau_{d1}$ +                                                                                          | ~ 1 |

|      | $\tau_{d2} < \frac{T_s}{2}.$ (b) $\frac{T_s}{2} < \tau_{d1} + \tau_{d2} < T_s.$                                                                                     | 21  |

| 3.3  | Key waveforms of the symmetric-on-time PWM in shadow mode                                                                                                           |     |

|      | with duty-ratio updated when counter reaches period value. (a)                                                                                                      |     |

|      | $\tau_{d1} + \tau_{d2} < \frac{T_s}{2}$ . (b) $\frac{T_s}{2} < \tau_{d1} + \tau_{d2} < T_s$                                                                         | 21  |

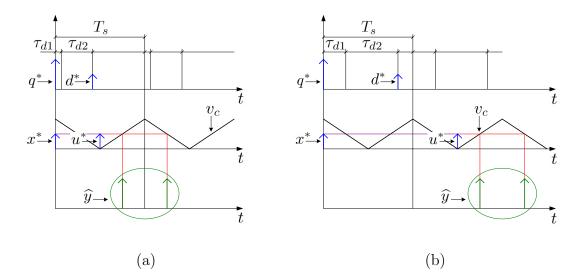

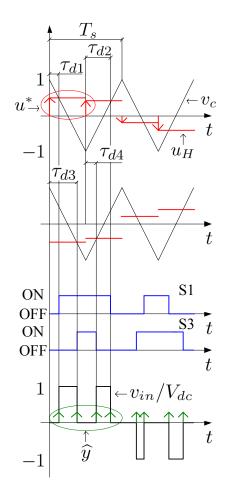

| 3.4  | Key waveforms of the symmetric-on-time PWM in shadow mode                                                                                                           |     |

|      | with double update. (a) $\tau_{d1} + \tau_{d2} < \frac{T_s}{2}$ . (b) $\frac{T_s}{2} < \tau_{d1} + \tau_{d2} < T_s$ .                                               | 23  |

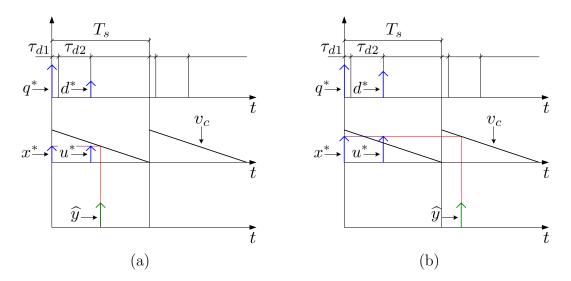

| 3.5  | Key waveforms of the begin-of-on-time PWM in immediate mode.                                                                                                        |     |

|      | (a) $\tau_{d1} + \tau_{d2} < (1 - D)T_s$ . (b) $(1 - D)T_s < \tau_{d1} + \tau_{d2} < T_s$                                                                           | 23  |

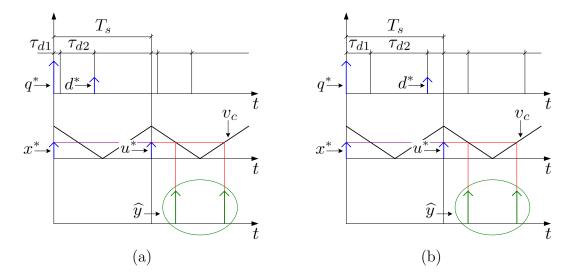

| 3.6  | Key waveforms of the end-of-on-time PWM in immediate mode.                                                                                                          |     |

|      | (a) $\tau_{d1} + \tau_{d2} < DT_s$ . (b) $DT_s < \tau_{d1} + \tau_{d2} < T_s$                                                                                       | 24  |

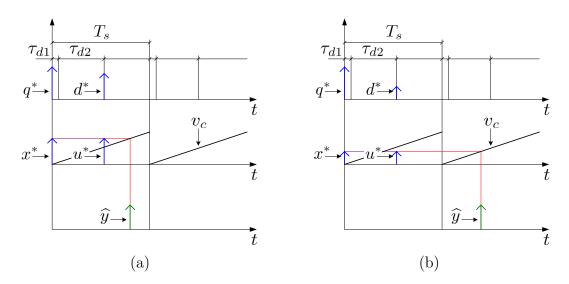

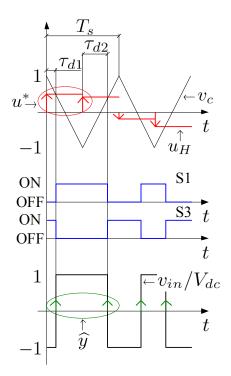

| 3.7  | Key waveforms of the symmetric-on-time $\operatorname{PWM}$ in immediate mode                                                                                       |     |

|      | with a fast processor. (a) $\tau_{d1} + \tau_{d2} < \frac{(1-D)T_s}{2}$ . (b) $\frac{(1-D)T_s}{2} <$                                                                |     |

|      | $\tau_{d1} + \tau_{d2} < \frac{T_s}{2} \dots \dots$           | 25  |

| 3.8  | Key waveforms of the symmetric-on-time PWM in immediate mode                                                                                                        |     |

|      | with a slow processor. (a) $\frac{T_s}{2} < \tau_{d1} + \tau_{d2} < \frac{(1+D)T_s}{2}$ . (b) $\frac{(1+D)T_s}{2} <$                                                |     |

|      | $\tau_{d1} + \tau_{d2} < T_s. \ldots \ldots$ | 26  |

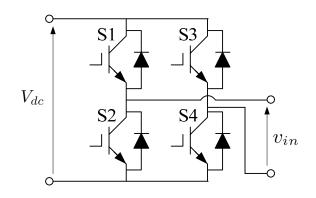

| 3.9  | A typical H bridge circuit.                                                                                                                                         | 26  |

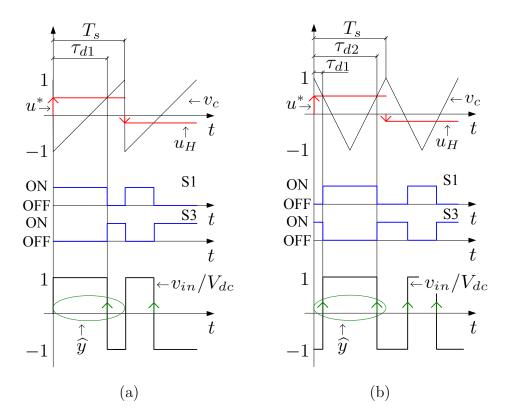

| 3.10 | Key waveforms of single-update-mode uniformly-sampled bipolar                                                                                                       |     |

|      | switched H bridge. (a) End-of-on-time modulator. (b) Symmetric-                                                                                                     |     |

|      | on-time modulator.                                                                                                                                                  | 27  |

| 3.11 | Key waveforms of double-update-mode uniformly-sampled bipolar                                                                                                       |     |

|      | switched H bridge.                                                                                                                                                  | 28  |

|      |                                                                                                                                                                     |     |

| 3.12 | Key waveforms of uniformly-sampled single-update-mode unipolar                |    |

|------|-------------------------------------------------------------------------------|----|

|      | switched H bridge. (a) End-of-on-time modulator. (b) Symmetric-               |    |

|      | on-time modulator                                                             | 29 |

| 3.13 | Key waveforms of uniformly-sampled unipolar switched H bridge                 |    |

|      | with double-update-mode.                                                      | 30 |

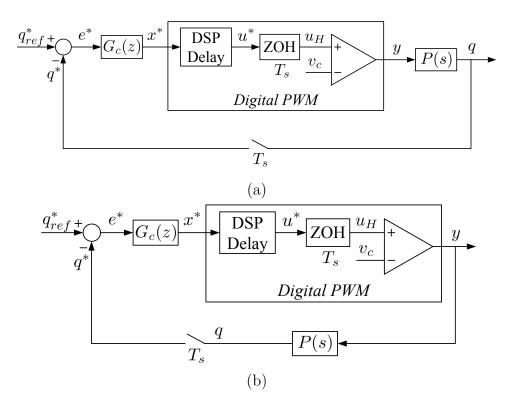

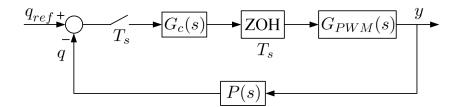

| 3.14 | Block diagram of a single loop digitally controlled switching con-            |    |

|      | verter. (a) Original block diagram. (b) Rearranged block diagram.             | 32 |

| 3.15 | Block diagram of the single control loop in large signal <i>s</i> -domain.    | 32 |

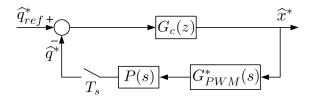

| 3.16 | Block diagram of the single control loop in small-signal z-domain.            | 33 |

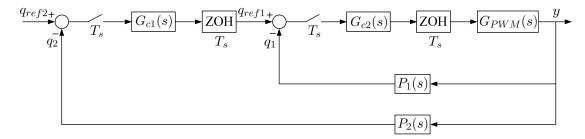

| 3.17 | Block diagram of digitally controlled switching converter with cas-           |    |

|      | caded loops                                                                   | 34 |

| 3.18 | Block diagram of the cascaded control loops in large signal <i>s</i> -domain. | 34 |

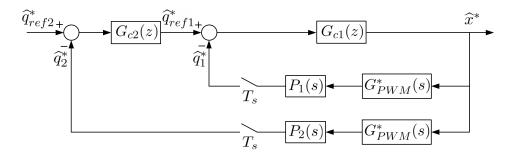

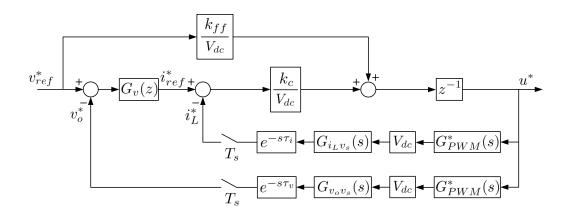

|      | Block diagram of the cascaded control loops in small-signal z-domain.         | 34 |

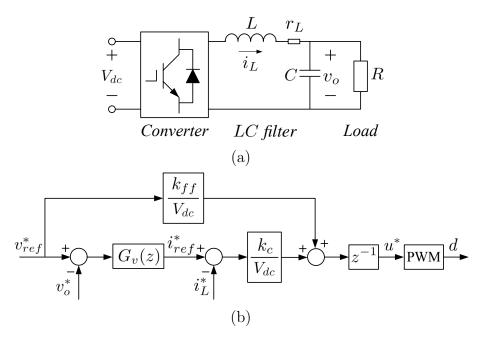

|      | The digitally controlled buck inverter. (a) Power circuit. (b) Volt-          |    |

|      | age and current controller                                                    | 35 |

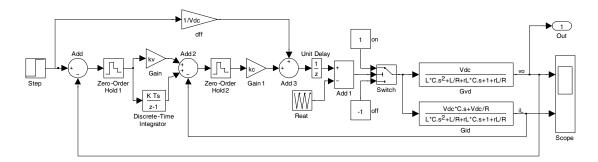

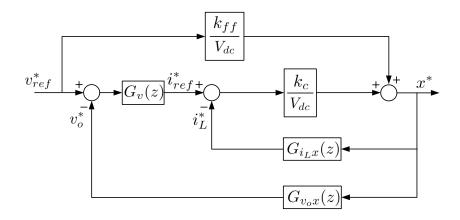

| 3.21 | Simulink block diagram of digitally controlled buck inverter                  | 36 |

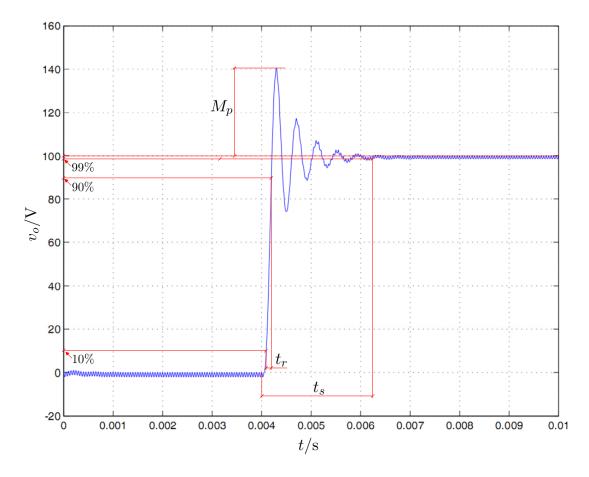

|      | Simulation retrieved voltage waveform of the digitally controlled             |    |

|      | buck inverter.                                                                | 37 |

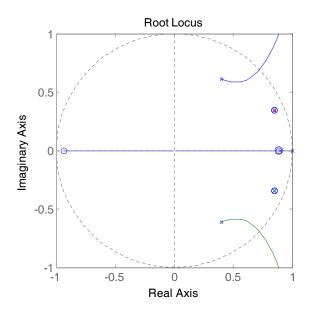

| 3.23 | z-domain model of digitally controlled buck inverter.                         | 38 |

|      | Root locus of digitally controlled buck inverter.                             | 39 |

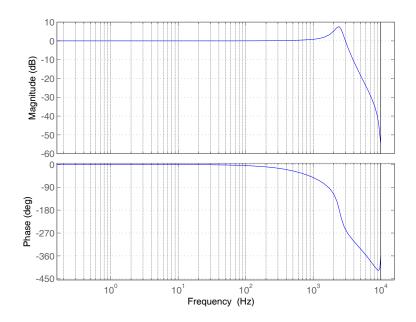

|      | Bode diagram of closed-loop transfer function of the buck inverter.           | 40 |

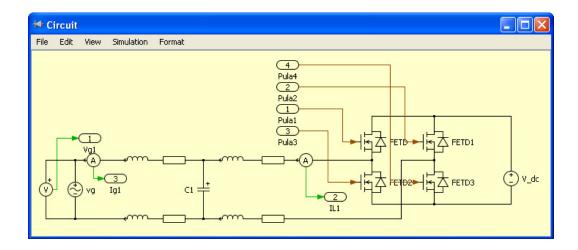

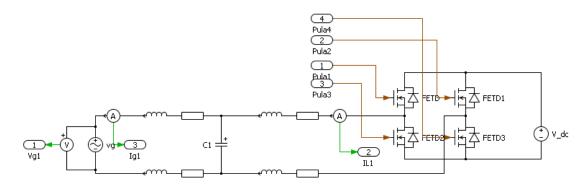

|      | A grid-connected inverter power circuit composed by PLECS ele-                |    |

|      | ments.                                                                        | 41 |

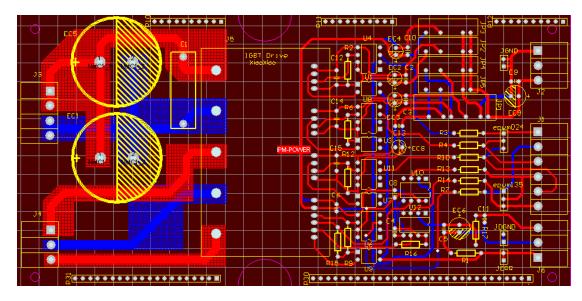

| 3.27 | The PCB layout of a power inverter and drive circuit                          | 41 |

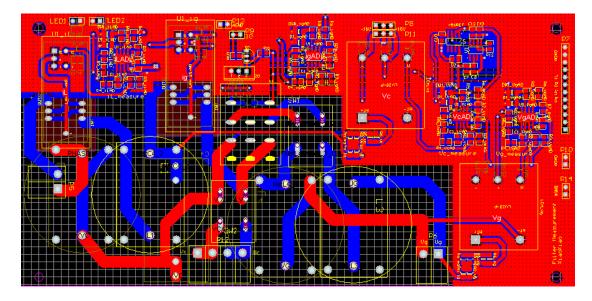

| 3.28 | The PCB layout of a filter and measurement circuit                            | 42 |

|      | The picture of the controller board                                           | 42 |

|      |                                                                               |    |

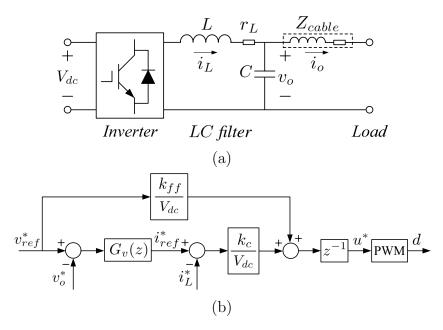

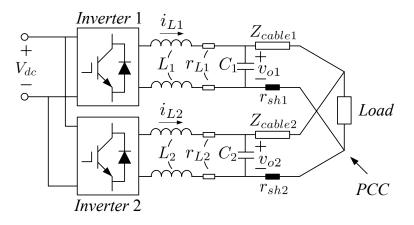

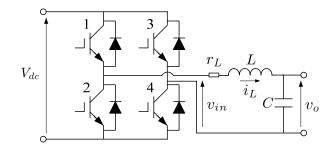

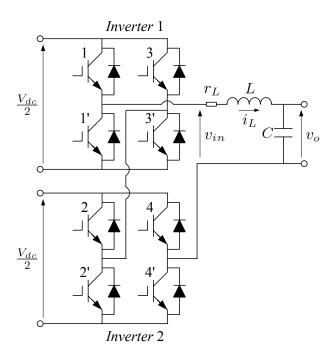

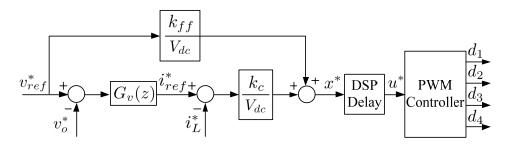

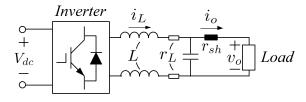

| 4.1  | The single phase digitally controlled inverter. (a) The power cir-            |    |

|      | cuit. (b) The controller                                                      | 46 |

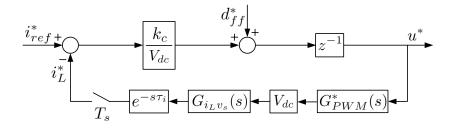

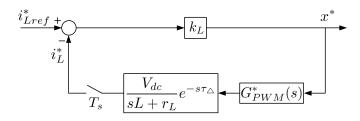

| 4.2  | Model for the current control loop of the digitally controlled inverter.      | 47 |

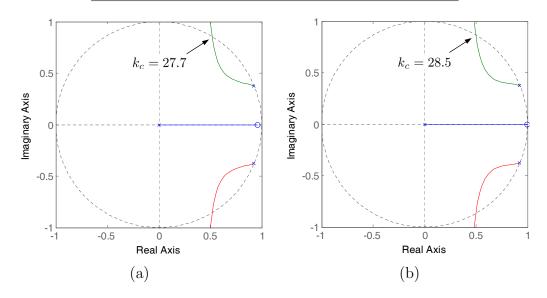

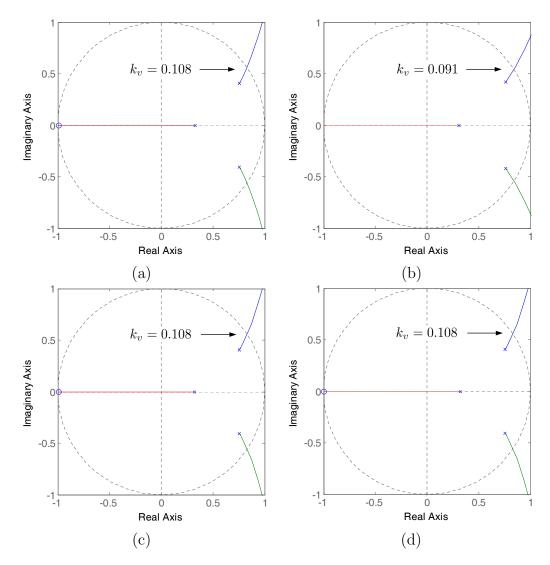

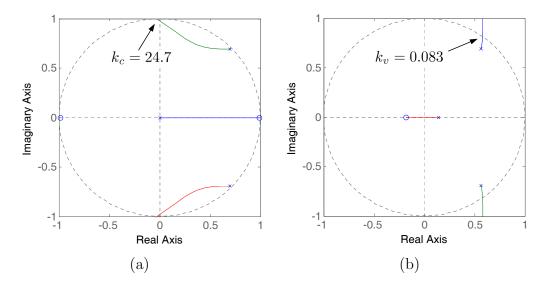

| 4.3  | Root loci of the internal current loop. (a) End-of-on-time modula-            |    |

|      | tor with $D = 0.75$ . (b) Symmetric-on-time modulator with $D = 0.5$ .        | 49 |

| 4.4  | Model for the cascaded control loops of the digitally controlled              |    |

|      | inverter                                                                      | 50 |

| 4.5  | Root loci of the external voltage loop. (a) End-of-on-time modu-              |    |

|      | lator with $D = 0.5$ . (b) End-of-on-time modulator with $D = 0.75$ .         |    |

|      | (c) Symmetric-on-time modulator with $D = 0.5$ . (d) Symmetric-               |    |

|      | on-time modulator with $D = 0.75$                                             | 51 |

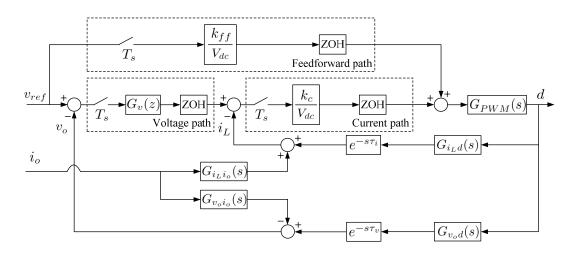

| 4.6  | Model of the digitally controlled inverter                                    | 53 |

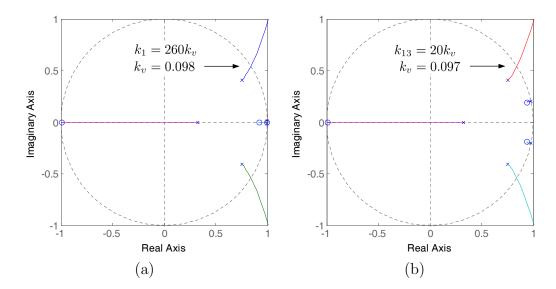

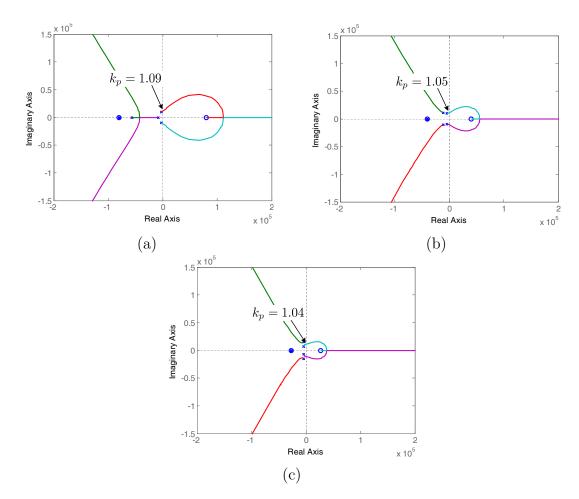

| 4.7   | Root loci of the external voltage loop when resonant compensators                                                                             |     |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|

|       | are used. (a) Proportional compensator plus fundamental fre-                                                                                  |     |

|       | quency resonant compensator. (b) Proportional compensator plus                                                                                |     |

|       | thirteenth harmonic frequency resonant compensator                                                                                            | 57  |

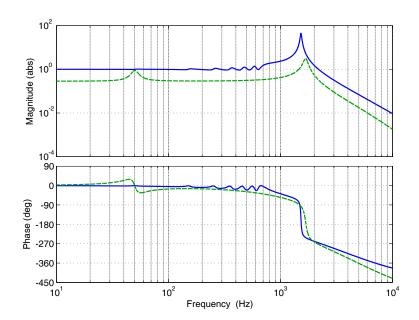

| 4.8   | Bode diagram of closed-loop transfer function (full line: linear                                                                              |     |

|       | voltage control scheme with duty-ratio feedforward; dashed line:                                                                              |     |

|       | classic PR control scheme)                                                                                                                    | 58  |

| 4.9   | Bode diagram of output impedance (full line: linear voltage con-                                                                              |     |

| -     | trol scheme with duty-ratio feedforward; dashed line: classic PR                                                                              |     |

|       | control scheme)                                                                                                                               | 59  |

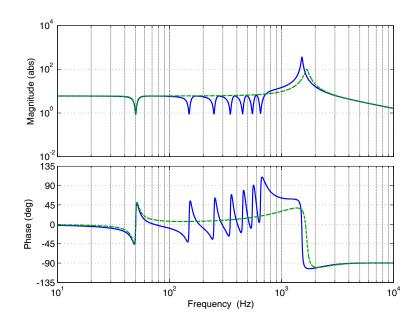

| 4.10  |                                                                                                                                               | 00  |

| 1.10  | rameters (full line: case 1; dashed line: case 2)                                                                                             | 61  |

| 4 11  | Sensitivities of the output impedance versus filter parameters (full                                                                          | 01  |

| 1.11  | line: case 1; dashed line: case 2).                                                                                                           | 61  |

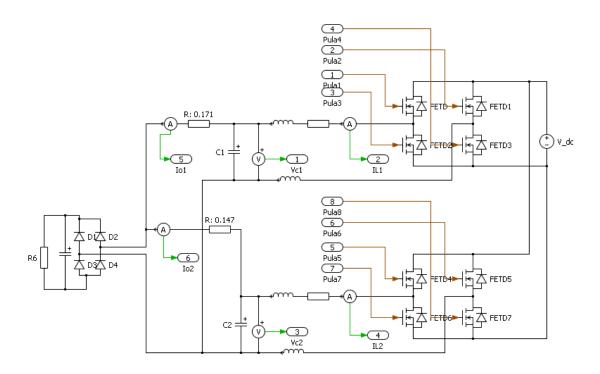

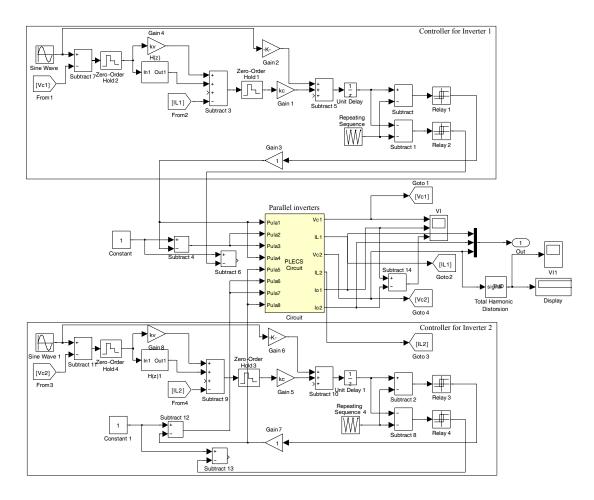

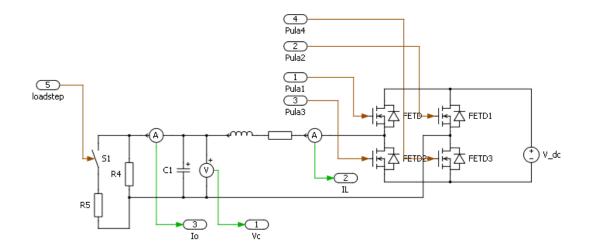

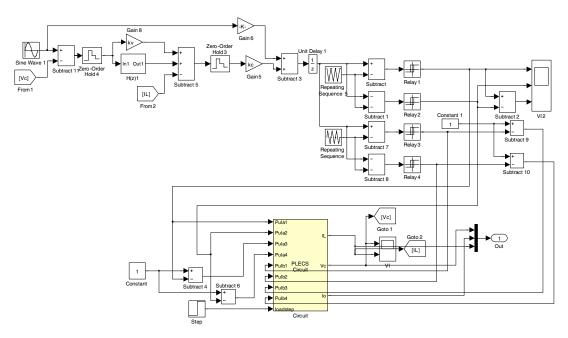

| 1 19  | Simulink block diagram of the power circuit of two parallel inverters.                                                                        | 62  |

|       | Simulink block diagram of two digitally controlled inverters in par-                                                                          | 02  |

| 4.10  |                                                                                                                                               | 63  |

| 111   |                                                                                                                                               | 05  |

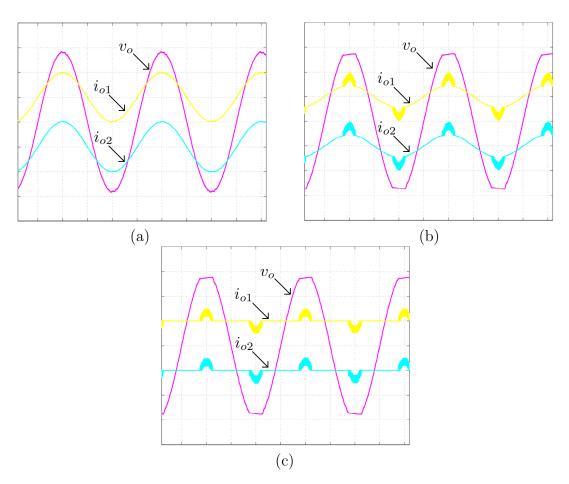

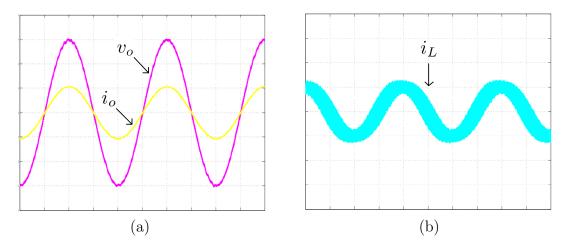

| 4.14  | Simulated output voltage and currents of the two parallel inverters                                                                           |     |

|       | with the PR and droop controller (X-axis: Time, 5 ms/div; Y-                                                                                  |     |

|       | axis: Magnitude of output currents and voltage; output currents,<br>$5 \wedge (dim output maltage 50 \vee (dim))$ (a) Lincon loads (b) Lincon |     |

|       | 5 A/div; output voltage, 50 V/div). (a) Linear loads. (b) Linear                                                                              | C A |

| 4 1 5 | load and nonlinear load. (c) Nonlinear load                                                                                                   | 64  |

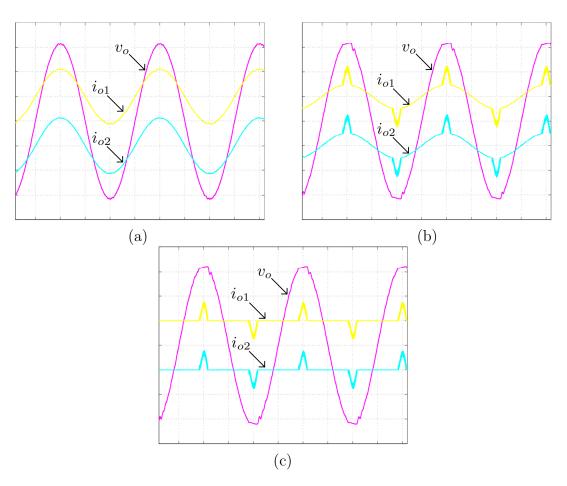

| 4.15  | Simulated output voltage and currents of the two parallel invert-                                                                             |     |

|       | ers with the proposed controller (X-axis: Time, 5 ms/div; Y-axis:                                                                             |     |

|       | Magnitude of output currents and voltage; output currents, 5 A/-                                                                              |     |

|       | div; output voltage, 50 V/div). (a) Linear loads. (b) Linear load                                                                             |     |

|       | and nonlinear load. (c) Nonlinear load                                                                                                        | 65  |

|       | Schematic of the experimental setup of the parallel inverters system.                                                                         | 65  |

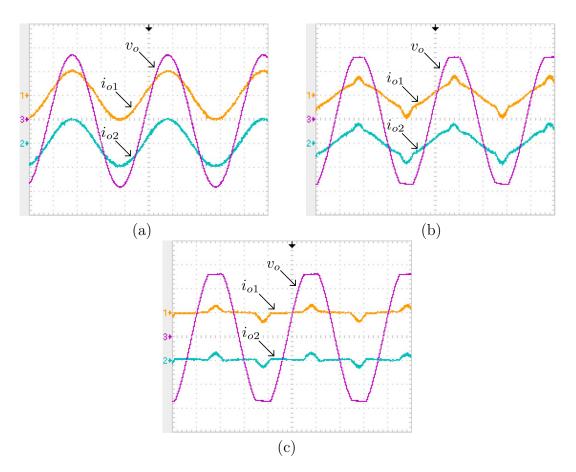

| 4.17  | Experimental output voltage and currents of the two parallel in-                                                                              |     |

|       | verters with the PR and droop controller (X–axis: Time, 5 ms/-                                                                                |     |

|       | div; Y–axis: Magnitude of output currents and voltage; Channel 1:                                                                             |     |

|       | output current of Inverter 1, 5 A/div; Channel 2: output current                                                                              |     |

|       | of Inverter 2, 5 A/div; Channel 3: output voltage, 50 V/div). (a)                                                                             |     |

|       | Linear loads. (b) Linear load and nonlinear load. (c) Nonlinear load.                                                                         | 69  |

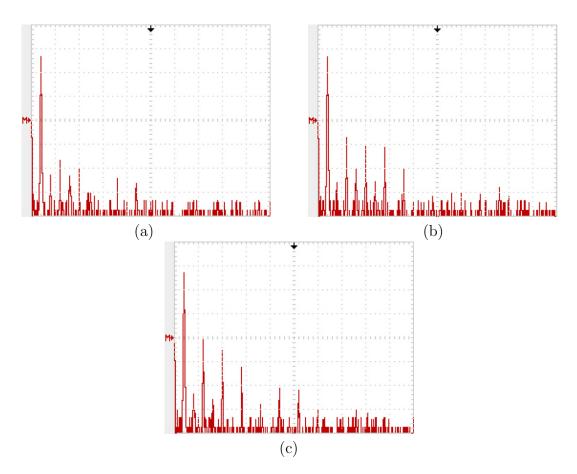

| 4.18  | Experimental output voltage FFT results of the two parallel in-                                                                               |     |

|       | verters with the PR and droop controller (X–axis: Frequency, 125                                                                              |     |

|       | Hz/div; Y-axis: Magnitude, 10 dB/div; Window: Flattop). (a)                                                                                   |     |

|       | Linear loads. (b) Linear load and nonlinear load. (c) Nonlinear                                                                               |     |

|       | load                                                                                                                                          | 70  |

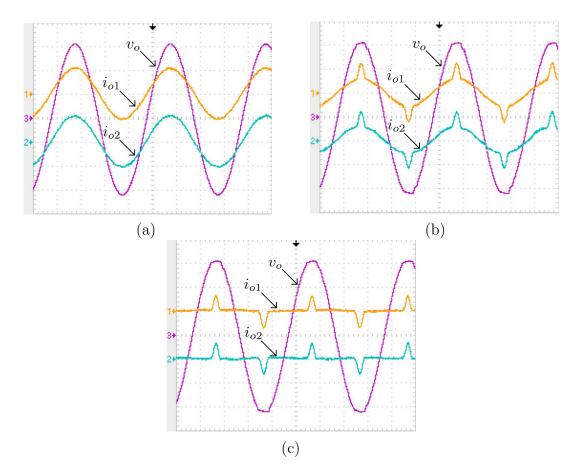

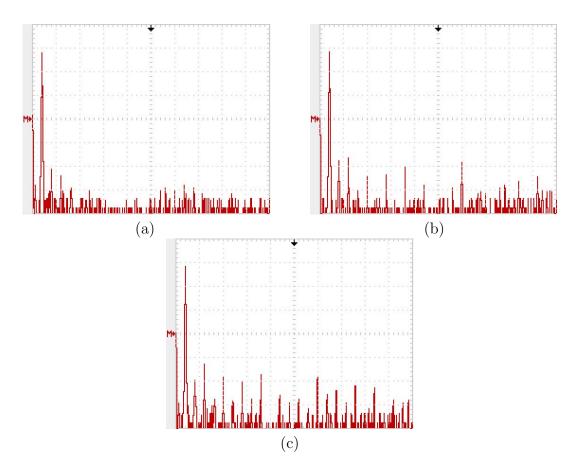

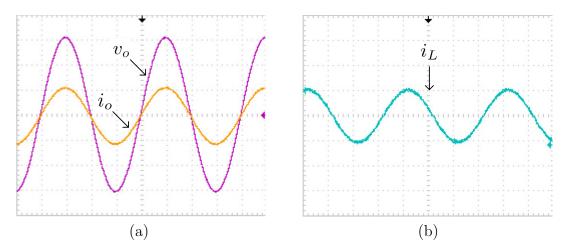

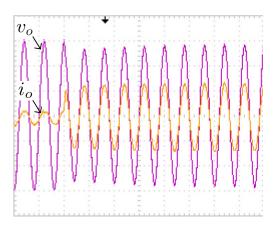

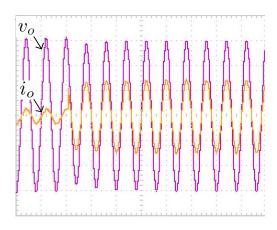

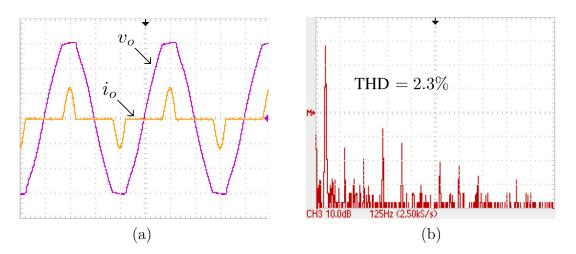

|              | Experimental output voltage and currents of the two parallel inverters with the proposed controller (X-axis: Time, 5 ms/div; Y-axis: Magnitude of output currents and voltage; Channel 1: output current of Inverter 1, 5 A/div; Channel 2: output current of Inverter 2, 5 A/div; Channel 3: output voltage, 50 V/div). (a) Linear loads. (b) Linear load and nonlinear load. (c) Nonlinear load. Experimental output voltage FFT results of the two parallel inverters with the proposed controller (X-axis: Frequency, 125 Hz/div; Y-axis: Magnitude, 10 dB/div; Window: Flattop). (a) Linear loads. (b) Linear load and nonlinear load. (c) Nonlinear load | 71<br>72 |

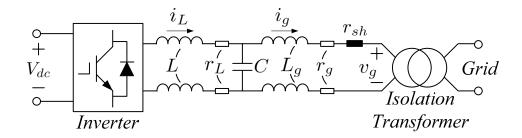

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

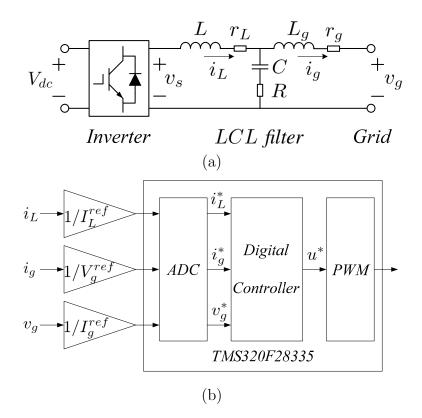

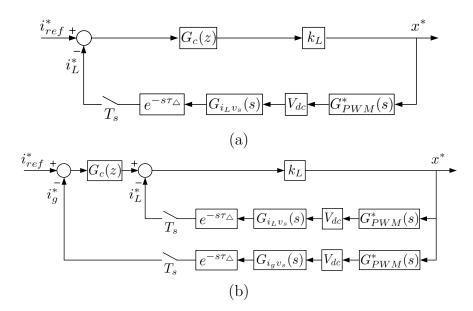

| $5.1 \\ 5.2$ | Single phase inverter. (a) Power circuit. (b) Control circuit<br>The <i>s</i> -domain block diagrams of grid-connected inverters. (a) Converter current feedback scheme. (b) Converter current plus grid                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 74       |

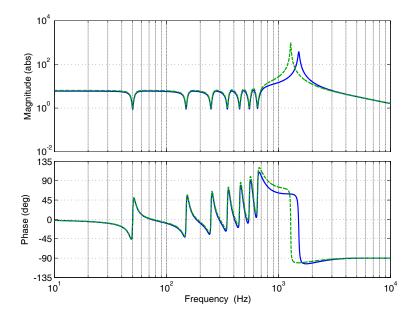

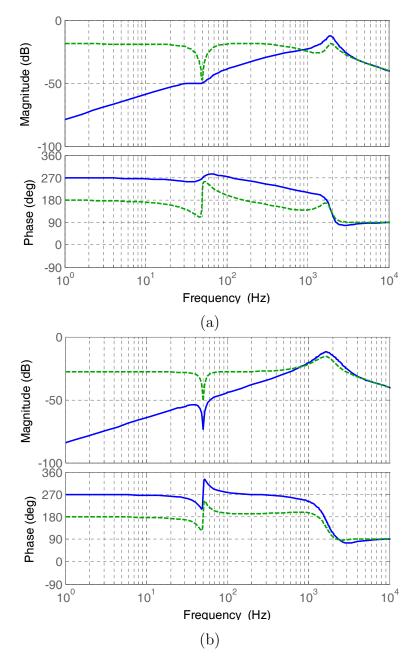

| 5.3          | current feedback scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 76       |

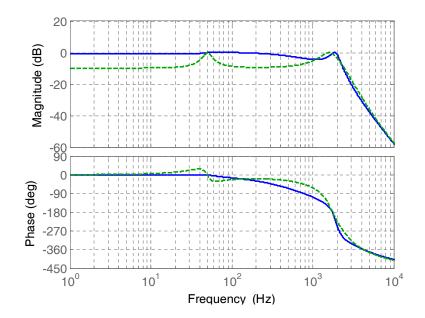

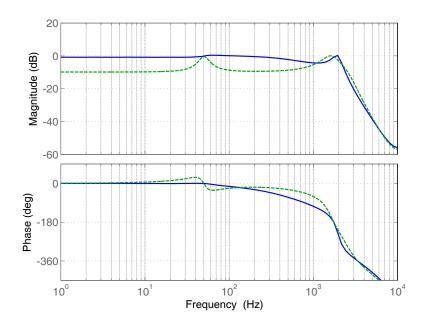

| 5.4          | converter current plus grid current control scheme) Bode diagrams of the grid voltage to grid current transfer functions (full line: with duty-ratio feedforward; dashed line: without duty-ratio feedforward). (a) Converter current feedback control scheme.                                                                                                                                                                                                                                                                                                                                                                                                 | 78       |

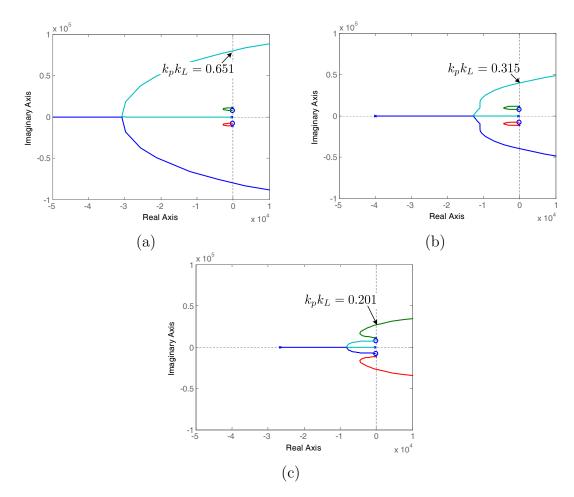

| 5.5          | (b) Converter current plus grid current feedback control scheme<br>Root loci of the converter current feedback controlled grid-connected<br>inverters in <i>s</i> -plane . (a) Minimum delay. (b) Medium delay. (c)                                                                                                                                                                                                                                                                                                                                                                                                                                            | 79       |

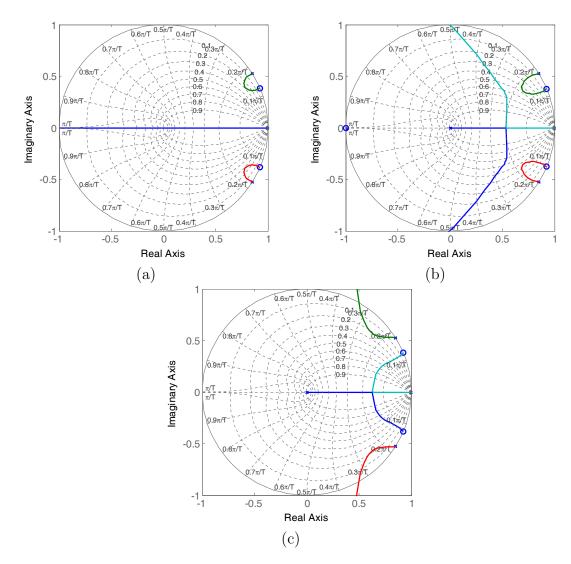

| 5.6          | Maximum delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80       |

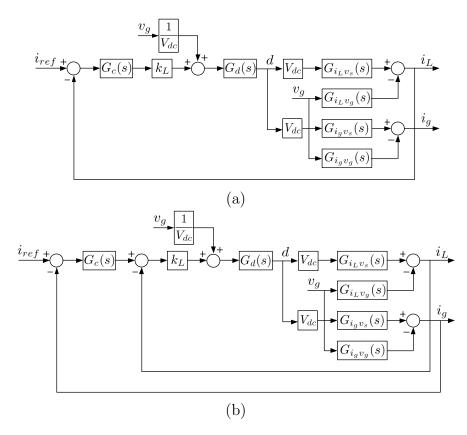

| 5.7          | Minimum delay. (b) Medium delay. (c) Maximum delay Block diagrams of grid-connected inverters. (a) Converter current feedback scheme. (b) Converter current plus grid current feedback                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81       |

| 5.8          | scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 82       |

| 5.9          | scheme; dashed line: converter current plus grid current controlscheme).Block diagram for the simplified converter current control loop of                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 85       |

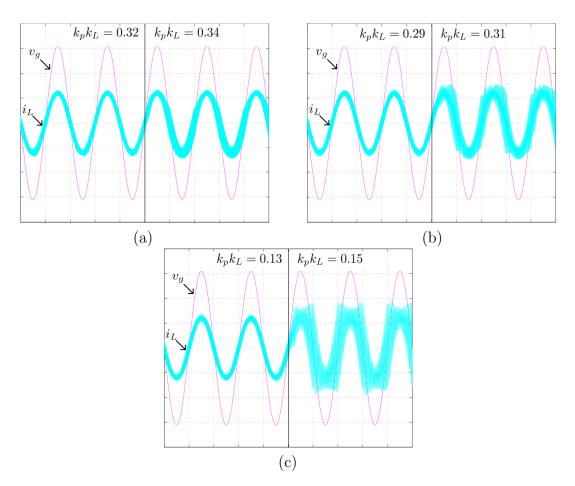

| 5.10         | a grid-connected inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85       |

|              | Maximum delay                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 88       |

| 1 | 5.11 | Root loci of the converter current plus grid current feedback con-                                            |    |

|---|------|---------------------------------------------------------------------------------------------------------------|----|

|   |      | trolled grid-connected inverters in z-plane with $k_L = 0.08$ . (a)                                           |    |

|   |      | Minimum delay. (b) Medium delay. (c) Maximum delay                                                            | 89 |

|   | 5.12 | Simulink block diagram of the power circuit of the grid-connected                                             |    |

|   |      | inverter                                                                                                      | 89 |

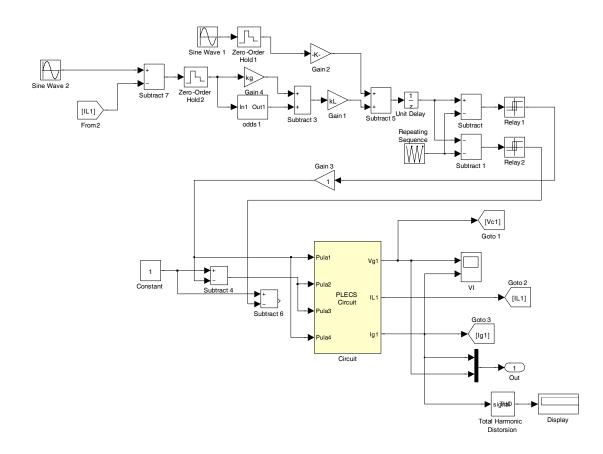

| , | 5.13 | Simulink block diagram of the converter current controlled grid-                                              |    |

|   |      | connected inverter. $\ldots$ | 90 |

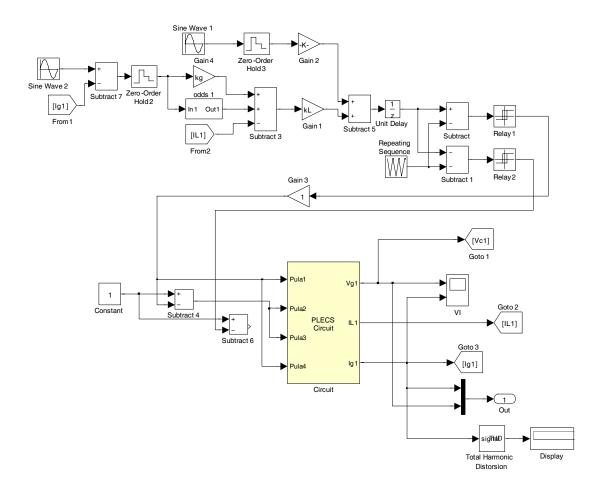

|   | 5.14 | Simulink block diagram of the converter current plus grid current                                             |    |

|   |      | controlled grid-connected inverter                                                                            | 91 |

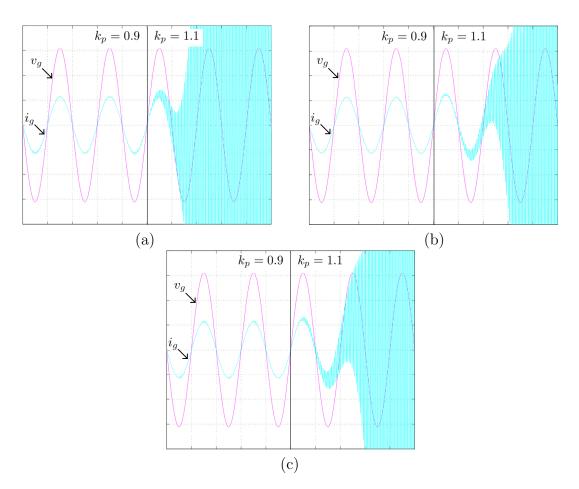

| , | 5.15 | Simulated waveforms of the converter current controlled grid-connected                                        | ł  |

|   |      | inverter (X–axis: Time, 5 ms/div; Y–axis: Magnitude of converter                                              |    |

|   |      | current: 5 A/div; and grid voltage: 50 V/div). (a) Minimum delay.                                             |    |

|   |      | (b) Medium delay. (c) Maximum delay                                                                           | 92 |

| , | 5.16 | Simulated waveforms of the converter current plus grid current                                                |    |

|   |      | controlled grid-connected inverter (X–axis: Time, 5 ms/div; Y– $$                                             |    |

|   |      | axis: Magnitude of grid current: 5 A/div; and grid voltage: 50 $$                                             |    |

|   |      | V/div). (a) Minimum delay. (b) Medium delay. (c) Maximum delay.                                               | 93 |

|   | 5.17 | Experimental grid connected inverter                                                                          | 94 |

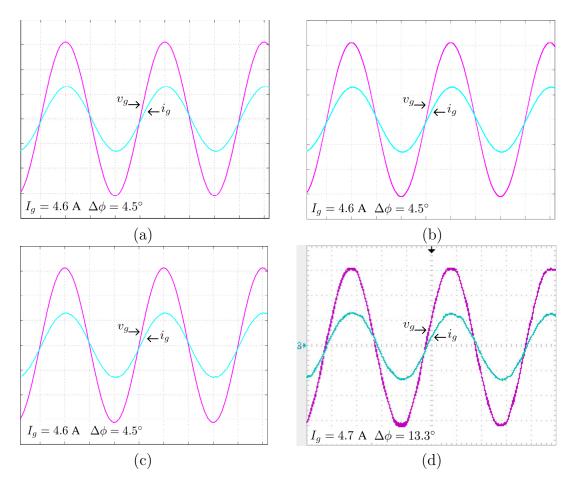

|   | 5.18 | Steady-state response of the converter current controlled grid-connecte                                       | d  |

|   |      | inverter (X–axis: Time, 5 ms/div; Y–axis: Magnitude of grid cur-                                              |    |

|   |      | rent: 5 A/div; and grid voltage: 50 V/div). (a) Average model $$                                              |    |

|   |      | prediction. (b) z-domain model prediction. (c) Simulation result                                              |    |

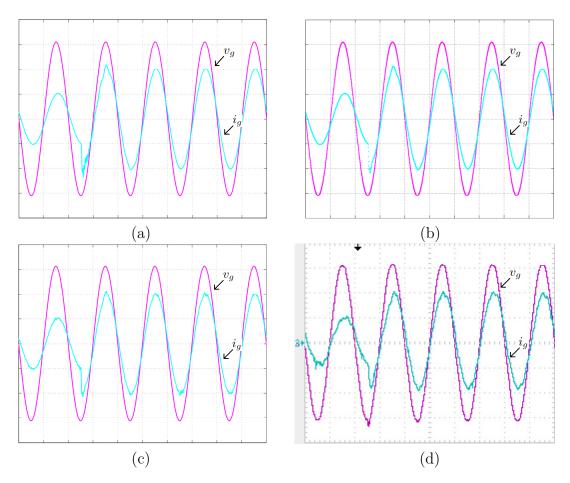

|   |      | (d) Experimental result.                                                                                      | 95 |

| , | 5.19 | Steady-state response of the converter current plus grid current                                              |    |

|   |      | controlled grid-connected inverter (X–axis: Time, 5 ms/div; Y–                                                |    |

|   |      | axis: Magnitude of grid current: $5 \text{ A/div}$ ; and grid voltage: $50$                                   |    |

|   |      | V/div). (a) Average model prediction. (b) $z$ -domain model pre-                                              |    |

|   |      | diction. (c) Simulation result (d) Experimental result                                                        | 96 |

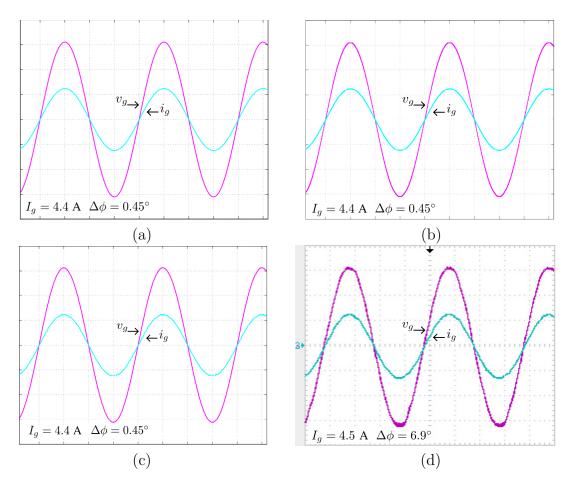

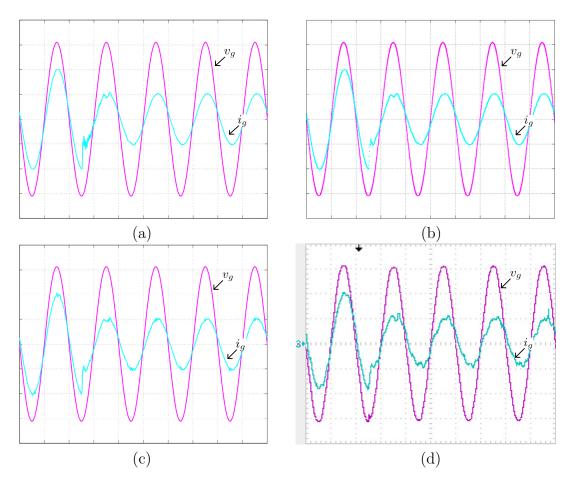

| , | 5.20 | Transient response of the converter current controlled grid-connected                                         |    |

|   |      | inverter with a step in the commanded current peak value from 2 A                                             |    |

|   |      | to 4 A (X–axis: Time, 5 ms/div; Y–axis: Magnitude of grid current                                             |    |

|   |      | and grid voltage; Channel 2: grid current, 2 A/div; Channel 3: grid                                           |    |

|   |      | voltage, 50 V/div). (a) Average model prediction. (b) z-domain                                                |    |

|   |      | model prediction. (c) Simulation result (d) Experimental result                                               | 97 |

|   |      |                                                                                                               |    |

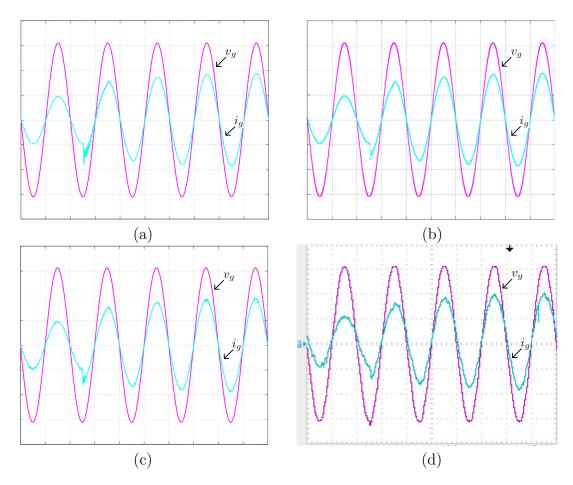

| 5.21 Transient response of the converter current controlled grid-connected     |    |

|--------------------------------------------------------------------------------|----|

| inverter with a step in the commanded current peak value from 4 A              |    |

| to 2 A (X–axis: Time, $5 \text{ ms/div}$ ; Y–axis: Magnitude of grid current   |    |

| and grid voltage; Channel 2: grid current, $2 \text{ A/div}$ ; Channel 3: grid |    |

| voltage, 50 V/div). (a) Average model prediction. (b) z-domain                 |    |

| model prediction. (c) Simulation result (d) Experimental result.               | 98 |

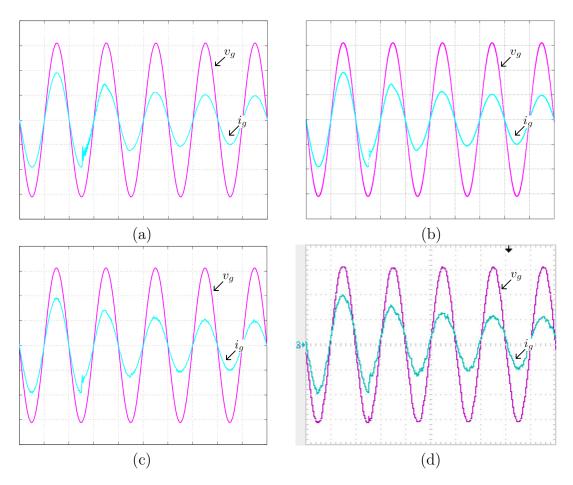

5.22 Transient response of the converter current plus grid current controlled grid-connected inverter with a step in the commanded current peak value from 2 A to 4 A (X-axis: Time, 5 ms/div; Y-axis: Magnitude of grid current and grid voltage; Channel 2: grid current, 2 A/div; Channel 3: grid voltage, 50 V/div). (a) Average model prediction. (b) z-domain model prediction. (c) Simulation result (d) Experimental result.

99

####

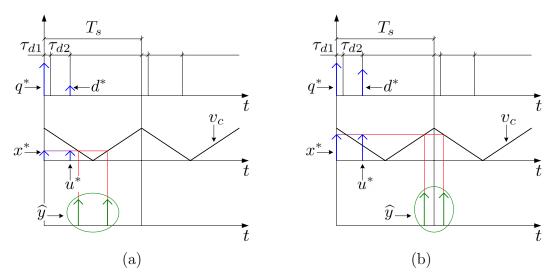

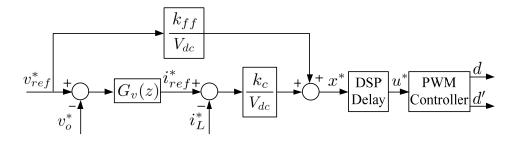

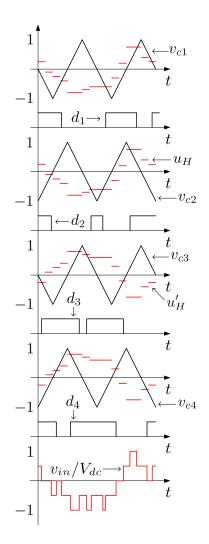

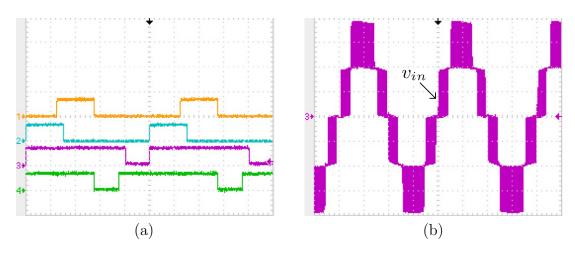

| 6.3 | Waveforms of drive signals and filter input voltage of a bipolar         |

|-----|--------------------------------------------------------------------------|

|     | switched inverter. (a) Drive signals for IGBT 1, 2, 3 and 4 (X– $$       |

|     | axis: Time, 10 $\mu$ s/div; Y–axis: Magnitude, 5 V/div). (b) Filter      |

|     | input voltage $v_{in}$ (X-axis: Time, 5 ms/div; Y-axis: Magnitude,       |

|     | 50  V/div)                                                               |

| 6.4 | Key waveforms of the bipolar switched inverter                           |

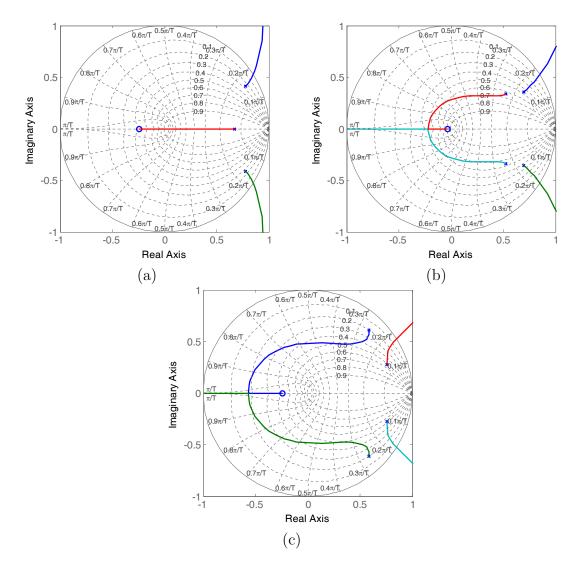

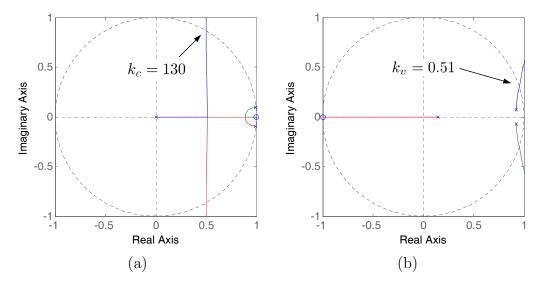

| 6.5 | Root loci of the control loops. (a) Internal current loop. (b) Ex-       |

|     | ternal voltage loop with $k_c = 4$                                       |

| 6.6 | The five-level H bridge inverters                                        |

| 6.7 | Digital controller of the five-level H bridge inverters                  |

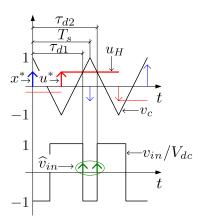

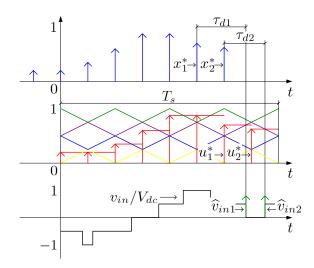

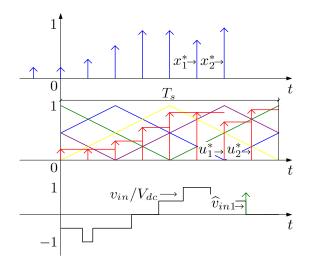

| 6.8 | Time-domain waveforms of the phase-shifted PWM 109                       |

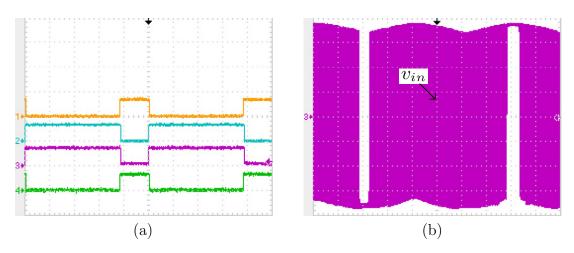

| 6.9 | Waveforms of drive signals and filter input voltage of five-level        |

|     | phase-shifted PWM multilevel inverters. (a) Drive signals for IGBT       |

|     | 1, 2, 3 and 4 (X–axis: Time, 10 $\mu$ s/div; Y–axis: Magnitude, 5 V/-    |

|     | div). (b) Filter input voltage $v_{in}$ (X-axis: Time, 5 ms/div; Y-axis: |

Magnitude, 50 V/div).  $\ldots$  110

| 6.10 | Time-domain enlarged view of the equivalent waveforms in phase-      |     |

|------|----------------------------------------------------------------------|-----|

|      | shifted PWM multilevel inverters                                     | 111 |

| 6.11 | Root loci of the control loops. (a) Internal current loop. (b) Ex-   |     |

|      | ternal voltage loop with $k_c = 16$                                  | 111 |

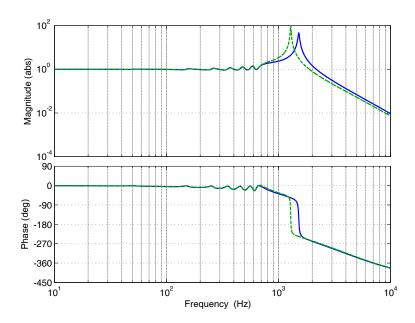

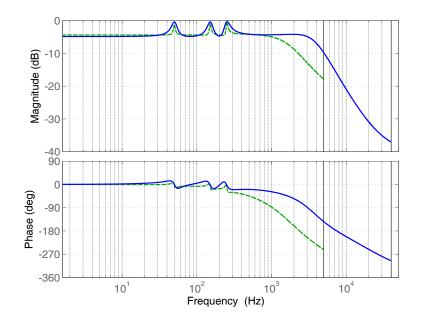

| 6.12 | Bode diagrams of closed-loop transfer functions (dashed line: bipo-  |     |

|      | lar switched inverter; full line: multisampled multilevel inverter). | 113 |

| 6.13 | Key waveforms of phase-shifted PWM multilevel inverter when          |     |

|      | vertical crossing occurs                                             | 114 |

| 6.14 | Simulink block diagram of the power circuit of the bipolar switched  |     |

|      | inverter.                                                            | 115 |

| 6.15 | Simulink block diagram of the digitally controlled bipolar switched  |     |

|      | inverter.                                                            | 115 |

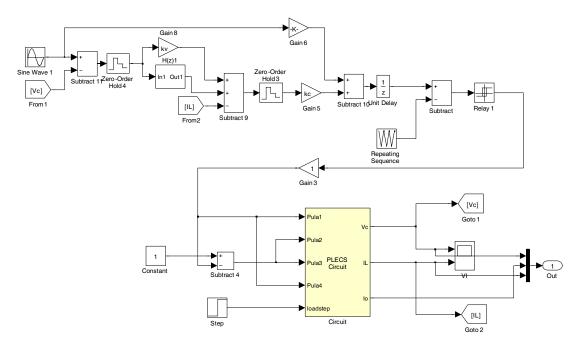

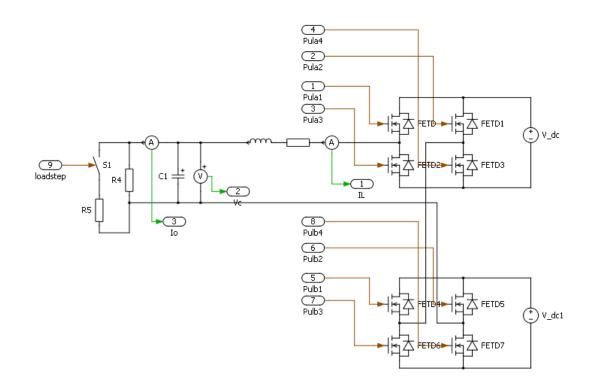

| 6.16 | Simulink block diagram of the power circuit of the multisampled      |     |

|      | multilevel inverter.                                                 | 116 |

| 6.17 | Simulink block diagram of the digitally controlled multisampled      |     |

|      | multilevel inverter.                                                 | 116 |

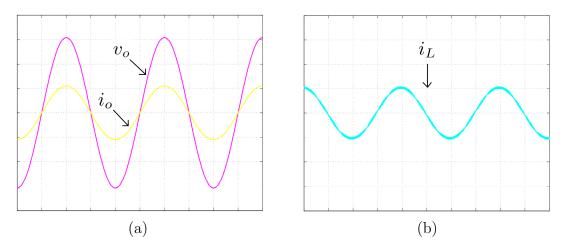

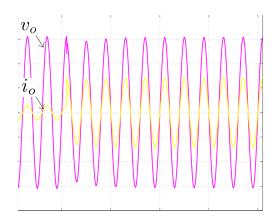

| 6.18 | Simulation retrieved waveforms of the conventional bipolar switched  |     |

|      | inverter with a resistive load. (a) Output voltage and output cur-   |     |

|      | rent (X–axis: Time, 5 ms/div; Y–axis: Magnitude, 50 V/div, 5 A/-     |     |

|      | div). (b) Inductor current (X–axis: Time, 5 ms/div; Y–axis: Mag-     |     |

|      | nitude, 5.33 A/div)                                                  | 117 |

| 6.19 | Simulation retrieved waveforms of the multisampled multilevel in-    |     |

|      | verter with a resistive load. (a) Output voltage and output current  |     |

|      | (X–axis: Time, 5 ms/div; Y–axis: Magnitude, 50 V/div, 5 A/div).      |     |

|      | (b) Inductor current (X–axis: Time, 5 ms/div; Y–axis: Magnitude,     |     |

|      | 5.33 A/div)                                                          | 117 |

| 6.20 | Simulation results of dynamic response of the conventional bipolar   |     |

|      | switched inverter when the load steps (X–axis: Time, 5 ms/div;       |     |

|      | Y-axis: Magnitude, 50 V/div, 5 A/div).                               | 118 |

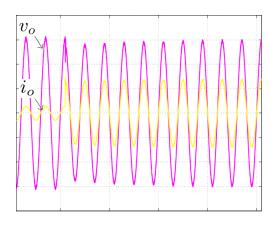

| 6.21 | Simulation results of dynamic response of the multisampled multi-    |     |

|      | level inverter when the load steps (X–axis: time, 5 ms/div; Y–axis:  |     |

|      | magnitude of output voltage, 50 V/div; magnitude of output cur-      |     |

|      | rent, 5 A/div). $\ldots$                                             |     |

| 6.22 | Experimental setup of the uniformly-sampled bipolar switched stand-  |     |

|      | alone inverter                                                       | 119 |

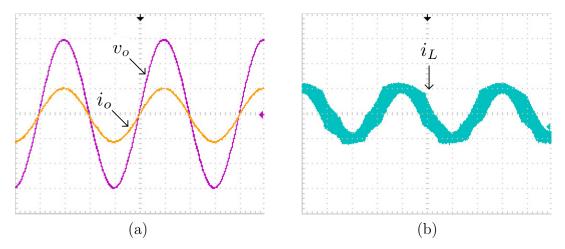

| 6.23 | Experimentally retrieved waveforms of the conventional bipolar        |     |

|------|-----------------------------------------------------------------------|-----|

|      | switched inverter with a resistive load. (a) Output voltage and out-  |     |

|      | put current (X–axis: Time, 5 ms/div; Y–axis: Magnitude, 50 V/-        |     |

|      | div, 5 A/div). (b) Inductor current (X–axis: Time, 5 ms/div;          |     |

|      | Y–axis: Magnitude, 5.33 A/div). $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 119 |

| 6.24 | Experimental setup of the multisampled multilevel inverter            | 120 |

| 6.25 | Experimentally retrieved waveforms of the multisampled multi-         |     |

|      | level inverter with a resistive load. (a) Output voltage and output   |     |

|      | current (X–axis: Time, 5 ms/div; Y–axis: Magnitude, 50 V/div,         |     |

|      | 5 A/div). (b) Inductor current (X–axis: Time, 5 ms/div; Y–axis:       |     |

|      | Magnitude, 5.33 A/div).                                               | 120 |

| 6.26 | eq:experimental dynamic response of the conventional bipolar switched |     |

|      | inverter when the load steps (X–axis: Time, 5 ms/div; Y–axis:         |     |

|      | Magnitude, 50 V/div, 5 A/div).                                        | 121 |

| 6.27 | Experimental dynamic response of the multisampled multilevel in-      |     |

|      | verter when the load steps (X–axis: time, 5 ms/div; Y–axis: mag-      |     |

|      | nitude of output voltage, 50 V/div; magnitude of output current,      |     |

|      | 5  A/div).                                                            | 121 |

| 6.28 | Experimental results of the multisampled multilevel inverter with     |     |

|      | a nonlinear load. (a) Output voltage and output current (X–axis:      |     |

|      | Time, 5 ms/div; Y–axis: Magnitude, 50 V/div, 5 A/div;). (b)           |     |

|      | Output voltage FFT result.                                            | 122 |

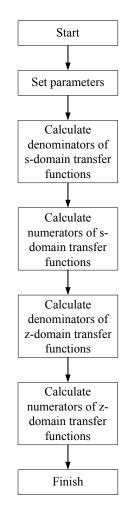

| A.1  | The flow chart of the program                                         | 140 |

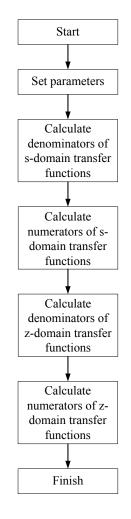

| B.1  | The flow chart of the program                                         | 143 |

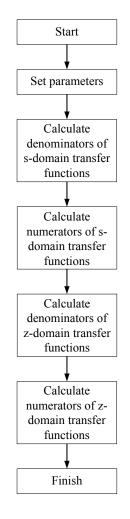

| C.1  | The flow chart of the program                                         | 147 |

# List of Tables

| 2.1 | Transfer functions of the PWM model                            | 15  |

|-----|----------------------------------------------------------------|-----|

| 3.1 | Parameters of the Inverter                                     | 36  |

| 4.1 | Parameters of the Islanding Inverters                          | 49  |

| 4.2 | Parameters of the Controller                                   | 56  |

| 4.3 | Simulated Output Performance Comparison of the Classic Con-    |     |

|     | troller and the Proposed Controller                            | 66  |

| 4.4 | Measured Data for Calibration of Inverter 1                    | 66  |

| 4.5 | Measured Data for Calibration of Inverter 2                    | 67  |

| 4.6 | Coefficients of Calibration for Inverter 1                     | 67  |

| 4.7 | Coefficients of Calibration for Inverter 2                     | 67  |

| 4.8 | Experimental output Performance Comparison of the Classic Con- |     |

|     | troller and the Proposed Controller                            | 71  |

| 5.1 | Parameters of the Grid-Connected Inverters                     | 77  |

| 5.2 | Predicted Maximum Proportional Gains                           | 90  |

| 6.1 | Parameters of the Bipolar Switched Inverter                    | 106 |

# Acknowledgement

I want to thank my supervisor Professor Joseph W. Spencer first. Not only did he give me the chance to continue my study, but he also gave me motivation and support on my experimental work. I also want to thank him for his comments and questions on my writing. His suggestions have significantly increased the quality of my papers and thesis. His contribution to this work is therefore important.

I would like to thank my best and brilliant friend, Dr. David Van de Sype who shares his broad knowledge with me. I thank him for the interesting technical discussions, especially for the critical comments on my research work. I also want to thank Professor Josep M. Guerrero for his encouragement on my research and comments on my writing work.

All colleagues in the University of Liverpool, I want to thank you for the help you have given to me. I also want to give my thanks to the colleagues who have already left. My previous mentors, teachers and colleagues in Xi'an Jiaotong University have given me support and help as well. I would like to thank them all.

The China Scholarship Council and University of Liverpool have given me financial support on my study. I want to thank the relevant officials working for this.

Finally, I want to thank especially my fiance Jing and my parents for their support. The last special thanks goes to my family members.

# Chapter 1 Introduction

#### **1.1** Power electronics in microgrids

The concept of distributed generation (DG) becomes promising when more and more renewable energy sources such as solar energy, wind energy and hydroenergy are available in reality. This is becoming important due to environmental, social and political interests. Energy from these resources can be transmitted via power electronics systems to local electric power networks. The local low-voltage electric power systems, including power generation, energy storage and loads, are connected to the conventional centralized grid and can also be disconnected from the grid. These local electric power systems are known as microgrids [1, 2, 3, 4, 5]. In such systems, dc-ac inverters (or ac-ac converters) are connected to local common bus. Due to the long distances between each inverter, these inverters are operating without intercommunications to provide power for local loads or remote loads in the grid.

For dc-ac inverters providing power to local loads without connecting to the grid, the inverters are operating in islanding mode. However, if the inverters provide power to remote loads in the grid, the inverters are operating in grid-connected mode. The islanding operation and the grid-connected operation are the main operation modes of microgrids. For the islanding operation, the inverters are disconnected from the grid and supply energy to their common loads in parallel, where a system of parallel inverters is a good paradigm. These parallel inverters provide energy only for local loads and are designed to share the power demanded by their loads. Moreover, if one unit fails to operate properly, it can quit the system of parallel inverters without causing instabilities. At the same time, the power required by the local loads will be retrieved from the other units. If the parallel inverters are not capable of maintaining the voltage level on the loads, more inverters can be connected to the point of common coupling (PCC). Consequently, such a system exhibits flexibility, reliability and redundancy while

supplying energy to the local loads.

However, when there are more energy generated than the demands from local loads, the inverters in microgrids can provide energy to the remote loads in the grid. In that case, each unit can be considered as an independent grid-connected inverter, as long as the grid voltage is not affected by the inverters in a microgrid. The grid-connected inverter usually injects a current according to the commanded current in phase with the grid voltage. In order to achieve a high power factor, phase locked loops (PLLs) are used for synchronization between the current reference and the grid. Therefore, each grid-connected inverter behaves as a grid voltage controlled current source. The voltage of grid-connected inverters follows the voltage on the PCC.

Generally, inverters with the two main functions mentioned above form a microgrid. Although there are many complicated topologies and structures, this thesis focuses on topics around the two classic operation modes (islanding and grid-connected) of H bridge inverters. Advanced topologies operating in a particular mode are also studied. Modelling methods and design regulations will be presented from the control point of view. Moreover, the main ideas in this thesis can also be extended to other applications in the control of power electronics.

#### **1.2** Digital control of power inverters

Either the islanding operation mode or the grid-connected operation mode requires proper control techniques. As the controllers of the inverters usually have complicated functions to ensure reliability, implementing a controller using analog devices is difficult. Moreover, the flexibility is also limited if analog circuits are mainly used. Under such conditions, the analog controllers are usually used in low power applications to reduce the cost. On the other hand, as the performance/price ratio of digital signal processors (DSPs) is increasing rapidly, nowadays most switching converters are controlled by digital controllers. Digital controllers for medium and high power inverters have the advantages such as lower sensitivity to variation of control parameters, immunity to switching noises, high flexibility and complexity in control algorithms, programmability of controllers and reduction of hardware components.

Due to the advantages of digital controllers, the control algorithms for islanding inverters and/or grid-connected inverters are usually implemented in DSPs. In most cases, a controller for a power inverter can be implemented using a single DSP (e.g., TMS320F28xx, ADSP2199x, etc.). The digital controllers are designed according to the models of the inverters. If higher switching frequency is used to reduce the electromagnetic interference (EMI), the sampling frequency can also be increased. In that case, high speed controllers are required and field programmable gate arrays (FPGAs) are usually combined with DSPs to implement the high sampling frequency.

For some practical limitations of switching devices, the switching frequency cannot be easily increased. However, the filter input voltage frequency can be increased by the structure of multilevel inverters. This achieves more or less the same filter input voltage frequency as that of the single H bridge inverter with higher switching frequencies. The EMI of the inverters can be reduced dramatically and higher sampling frequency can also be applied according to the level of the inverters. As a result, using the structure of multilevel inverters for islanding operation and grid-connected operation attracts great interests. Plenty of research work focuses on multilevel inverters controlled by one DSP plus one FPGA, with the phase-shifted carriers generated by the FPGA. This hardware arrangement provides sufficient feasibility of implementing complex digital control algorithms for multilevel inverters. The modelling of digitally controlled multilevel inverters are required for controller design.

## 1.3 Problems in digitally controlled power inverters

Unlike analog controlled power inverters, the knowledge of digitally controlled power inverters is still developing. A digital controller has significant influence on the dynamic behaviour of the control system. As a result, digitally controlled inverters have quite different dynamic behaviours from that of the analog controlled inverters. Accurate models are required for response predictions, since the classic averaged models for analog controlled inverters cannot be simply applied to digitally controlled inverters. The discrete-time models are applicable to digitally controlled systems, but these models cannot be obtained from the continuous-time models by using direct z-transform. More accurate modelling methods are needed for engineers when designing power inverters with the following practical considerations [6, 7, 8].

#### 1.3.1 System stability

Classic average models have been used to evaluate the stability of switching converters [9] and are capable of predicting slow-scale oscillations. However, the fast-scale instabilities such as period-n bifurcation can not be predicted by using the average models [10].

For a digitally controlled system, the stability analysis cannot be performed

using the average model. The main reason is that the sample and hold effect in digital controllers cannot be properly modelled by average models. Moreover, the delay effect differs when different pulse-width-modulation (PWM) strategies are used. Therefore, stability analysis for digitally controlled power inverters should be performed based on z-domain models. Compared to s-domain analysis, z-domain analysis also brings convenience for modelling delay effect and sample and hold effect.

#### 1.3.2 Controller design

Classic average models enables a direct design for controllers in analog controlled power inverters. Based on average models, the controllers can be obtained in *s*-domain and the control performance can be evaluated by using *s*-domain analysis. The average models are widely used to evaluate the low frequency control performances of digitally controlled power inverters. However, as the average models cannot predict instabilities in digitally controlled systems, the design of digital controllers based on *s*-domain analysis may not be able to guarantee an accurate gain margin. Therefore, the *z*-domain analysis is essential for design of digital controllers.

Based on the z-domain models, the design of digital controllers can be implemented using two strategies. One method is to design the controller directly in z-domain, which requires knowledge of the z-domain model of the inverter. This method allows to implement discrete control schemes such as deadbeat control scheme and repetitive-based control schemes. The other one is the indirect design strategy, which converts the well known classic analog controllers into z-domain. This method requires z-transform of s-domain transfer functions, where bilinear transform is usually used to obtain the z-domain expressions of controllers.

#### **1.3.3** Performance of controller

Steady-state performance and transient performance are important factors for evaluating a controller. The steady-state performance of a digitally controlled system can be evaluated using average models with good accuracy, as long as the interested performance is in low-frequency range. However, the transient response contains signals in a wide frequency range. Using average models may reduce the accuracy in predicting high frequency components. In contrast, zdomain models can be used to evaluated both the steady-state performance and transient performance. z-domain analysis can precisely predict the rise time, settling time and overshot in the transient response.

Robustness is another specification of a controller. Usually a robust digital

controller should have a gain margin of two. Only using a z-domain model the gain margin of a controller can be obtained from the z-plane root locus.

#### **1.3.4** Power quality requirements

Inverters should be designed to meet the power quality requirements. The normal voltage variation of islanding inverters should be within plus and minus 10% of the rated RMS value. The grid-connected inverters do not regulate the voltage, but they inject currents to the grid. Therefore, grid-connected inverters should have protection functions when the grid voltage is out of the normal operating range. The normal frequency range required for a inverter depends on the power level, which can be found in [11]. The standard [11] also provides regulations for the total harmonic distortion (THD) and individual harmonic current levels. These requirements applies to both islanding inverters and grid-connected inverters. The digitally control inverters described in this thesis are designed according to these requirements.

For grid-connected inverters, power factor is specified to be higher than 0.85 when output exceeds 10% of the power rating [12]. However, most grid-connected inverters are able to achieve a power factor close to unity. Another important requirement is that the injected dc current should be smaller than 0.5% of the rated output current [11, 12]. There are some techniques to minimize the dc current. For transformerless inverters, high resolution dc current sensor or auto-calibration [13] can be used to reduce the dc current injection. In our cases, isolation transformers are used to block the dc current injection into the grid. The grid-connected inverters in this thesis are designed according to the power quality requirements.

There are also functions and specifications on the interconnection of the electrical system, such as detection of islanding operation, automatic synchronization and grounding of the system. Moreover, voltage flicker is a subjective problem and has been discussed in IEEE Standard 519-1992, where the maximum borderline of the flicker has been defined. These requirements have to be taken into account in practice but are not included in the modelling of this thesis.

#### **1.4** Overview of the thesis

This thesis focuses on the modelling and control of digitally controlled power inverters in microgrids. These inverters may operate in islanding mode or in grid-connected mode. For islanding operations, stand-alone inverters are used to provide energy in parallel. The stand-alone inverters are controlled as voltage sources. These controllers are always implemented by cascaded control loops with an internal current control loop [2, 14]. Therefore, an accurate model for cascaded digital control loops has been proposed in this thesis. Based on the model, the controller design and analysis can be performed.

When inverters operate in grid-connected mode, they should behave as current sources. Inductive filters and LCL filters are usually used for grid-connected inverters. The controller of an inverter with inductive filter is easy to design, but for inverters with LCL filter, the design needs to be carefully considered. Moreover, the delay effects significantly affect the dynamic behaviour of the system. The LCL resonance in the high frequency range may lead to instabilities when the controller is not well designed. Hence, a new modelling method for grid-connected LCL inverters with accurately modelled delay effect is proposed in the thesis.

More stand-alone and grid-connected inverters tend to use the multilevel structure to lower the EMI. Many modulation techniques have been proposed for multilevel inverters, but the modelling of the phase-shifted PWM is still not available. Therefore, a general method of modelling digitally controlled multilevel inverters is presented in the thesis, which is also extendible to other modulation technologies.

The thesis is organized as follows. In Chapter 1, a brief introduction about digitally controlled power inverters in microgrids and the problems in this topic are given. Chapter 2 illustrates background and state of the art of the modelling and control for digitally controlled power inverters. Based on Chapter 1 and 2, Chapter 3 first provides the details of discrete modelling, with delay effects taken into account. Then, the block diagrams are derived for single switched switching converters. The model is also extended to H bridge inverters. To demonstrate the feasibility of the proposed model, a design example is provided. Furthermore, preparations for simulation and experimental work are presented.

An example of controller design for stand-alone inverters is shown in Chapter 4. The inverters are designed for parallel operation. The controllers are designed in z-domain, based on the proposed model. The aim of the design is to achieve good current sharing between inverters and to guarantee good power quality. To demonstrate the advantage of the proposed controller, the performance of the proposed controller has been compared to that of the conventional controller.

Chapter 5 gives an example of z-domain modelling for inverter with a thirdorder filter, i.e., grid-connected inverter with an LCL filter. Inverters with two typical control schemes have been modelled in the z-domain. Compared to the conventional s-domain models, the proposed models accurately predict the stability boundaries of control gains. Moreover, comparison between predictions of models, simulation and experimental results is provided to verify the capability of the models in predicting stabilities and retrieving time-domain waveforms.

Chapter 6 models the multilevel inverter, which is sampled with a frequency multiple of the switching frequency. These multilevel inverters become quite interesting in many microgrids' applications to increase power rating or to reduce the EMI. However, due to the complexity of the PWM, exact models for multilevel inverters are still not available. Therefore, the modelling method for the multisampled multilevel inverter is proposed. The chapter gives a concise way of modelling and proves that multisampled multilevel inverters can achieve better control performance compared to uniformly-sampled inverters.

Finally, conclusions are made in Chapter 7, which also highlights possible future work that would combine with this research.

# Chapter 2 Background

#### 2.1 Introduction

Conventional switching converters are controlled by analog controllers. For modelling and analysis of the switching converters, averaged switching characteristics are usually used [9]. The average modelling method has been widely applied to determine the control performance at low frequency range. However, even for analog controlled switching converters, average models fail to predict rapid dynamics [15]. Therefore, discrete-time maps have been developed as a more accurate modelling strategy [16, 17]. These methods successfully predict the nonlinear behaviour of naturally-sampled switching converters, but usually require solving transcendental equations every cycle to find the switching instants. As a result, approximated discrete-time models are proposed to reduce the computation load involved.

As analysis of digitally controlled switching converters has attracted wide interests in the last decade, the discrete-time mapping has also been applied to this topic [18, 19, 20, 21]. Moreover, for digitally controlled switching converters with sample and hold effect, it is easier to find the switching instants. Bilinear discretetime mapping has been proposed to show the capability of accurate prediction of instabilities such as bifurcation, strange attractor and chaos [22]. However, for practical controller design and performance analysis, it is more convenient to implement design and analysis in the Laplace domain.

The quantization effect of digitally controlled switching converters has been first studied in [23], where conditions of the limit cycle has been given. Based on these results, a describing function method has been proposed to model the quantization effect [24]. As the performance of DSPs improves and the resolution of analog-to-digital (AD) converters and digital pulse-width-modulators (DPWMs) becomes much greater than before, quantization effects can be neglected from the dynamic point of view [25]. Then, a more accurate model, i.e., small-signal z-domain model has been derived for DPWMs. This model enables the controller to be directly designed in the z-domain, and provides an evaluation of the controller in Laplace domain [25, 26]. Based on this accurate model, the classic design and analysis methods [27] for digitally controlled switching converters become applicable.

This chapter introduces the fundamentals of digital control for power electronics. Basic principles of sample and hold and z-transform are illustrated. The modelling methods and controller design techniques in the Laplace domain are reviewed. Most commonly used models regardless of quantization effects are provided. Based on the z-domain models, typical digital control strategies are presented.

## 2.2 Fundamentals of digital control in power electronics

A typical digital controller for a single switched converter is shown in Figure 2.1. The quantities of  $q_1, ..., q_m$  represent the analog variables which are required to be measured. Through an analog-to-digital converter (ADC), these quantities are converted to digital signals by ideal samplers, which are represented by  $q_1^*, ..., q_m^*$ . The digital controller implemented by using a cluster of difference equations, is equivalent to a control block comprised of z-domain transfer functions. The ratio of the switch on time duration to the switching period is defined as the duty-ratio. When a digital duty-ratio is calculated and updated in the PWM compare register as  $u^*$ , the zero-order-hold (ZOH) is used to convert  $u^*$  into a continuous modulation signal which compares with the carrier to generate the switch drive signals. Hence, the digital PWM is described by a pulse-to-continuous transfer function with a digital input but with an analog output. The fundamental of the

Figure 2.1: The schematic of a typical digital controller.

digital control of switching converters is introduced in the following subsections.

#### 2.2.1 Ideal sampler and ZOH

This subsection explains the conversions and transfer functions between continuous to discrete signals. The principle of sampling and hold in digital controllers can be found in [27]. To convert an analog signal into a digital signal, an ideal sampler is used. The conversion from digital signals to analog signals requires a ZOH. In the digitally controlled system [27], the ideal sampling process is to multiply the analog signal by a Dirac comb constructed from a series of Dirac delta functions, which is written as

$$\delta_T(t) = \sum_{k=-\infty}^{\infty} \delta(t - kT_s)$$

(2.1)

with t the time,  $T_s$  the sampling period and k the integers. Assuming  $e^*$  is the ideally sampled digital signal in respect to the analog error signal e, it can be represented as

$$e^*(t) = e(t)\delta_T(t). \tag{2.2}$$

On the other hand, the Dirac comb is a periodic function, whose Fourier series can be derived as

$$\delta_T(t) = \frac{1}{T_s} \sum_{k=-\infty}^{\infty} e^{jk\frac{2\pi}{T_s}t}.$$

(2.3)

In order to describe the function of the ideal sampler, Laplace-domain analysis is used. Substituting (2.3) into (2.2), the Laplace transform of  $e^*(t)$  becomes

$$e^*(s) = \frac{1}{T_s} \sum_{k=-\infty}^{\infty} e(s+jk\frac{2\pi}{T_s}).$$

(2.4)

If an input signal contains frequency lower than  $\frac{1}{2T_s}$  (the Nyquist frequency), it can be approximated from (2.4) that the transfer function of the ideal sampler is equivalent to a gain of  $\frac{1}{T_s}$ .

In contrast, the ZOH keeps an impulse for one sampling period with the amplitude equivalent to the area of the impulse, which is a pulse-to-continuous transfer function known as

$$G_{ZOH}^*(s) = \frac{1 - e^{-sT_s}}{s}.$$

(2.5)

Therefore, an ideal sampler cascaded by a ZOH with the same frequencies is represented by a continuous-to-continuous transfer function, whose Laplace-domain transfer function is written as

$$G_{ZOH}(s) = \frac{1 - e^{-sT_s}}{sT_s}.$$

(2.6)

It is interesting to mention that, in the digital controller with a fixed frequency, a ZOH followed by an ideal sampler behaves as a unity gain. From the transfer function point of view, the pulse transfer function in z-domain describing the ZOH followed by the ideal sampler is derived as

$$\mathcal{Z}\{G_{ZOH}^*(s)\} = \frac{z}{z-1} - \frac{1}{z-1} = 1.$$

(2.7)

The principle of z-transform is illustrated in the following subsection.

#### 2.2.2 *z*-Transform

In a continuous-time system, the impulse response is used to obtain the *s*-domain transfer function. The Laplace transform of the impulse response is the transfer function. In the discrete-time system, if a block is cascaded by a sampler, *z*-transform is used to describe the transfer function [27].

$$\underbrace{\begin{array}{c} \delta(t) \\ H(s) \end{array}}^{h(t)} h(t) \\ (a) \\ (b) \\ \end{array} \underbrace{\begin{array}{c} \delta(t) \\ H(s) \end{array}}^{h(t)} h(t) \\ T_s \\ \end{array} \\ \underbrace{\begin{array}{c} h^*(t) \\ T_s \end{array}}^{h^*(t)} \\ (b) \\ \end{array}$$

Figure 2.2: Block diagrams of the transfer functions. (a) Continuous-time system. (b) Discrete-time system.