# CMOS integrated Circuits for RF-powered Wireless Temperature Sensor

**Shailesh Singh Chouhan**

## Aalto University publication series **DOCTORAL DISSERTATIONS** 201/2015

## CMOS Integrated Circuits for RFpowered Wireless Temperature Sensor

**Shailesh Singh Chouhan**

A doctoral dissertation completed for the degree of Doctor of Science (Technology) to be defended, with the permission of the Aalto University School of Electrical Engineering, at a public examination held at the lecture hall S1 of the school on 4 December 2015 at 12.

Aalto University School of Electrical Engineering Department of Micro- and Nanosciences

### Supervising professor

Prof. Kari Halonen

### **Preliminary examiners**

Prof. Timo Erkki Rahkonen, University of Oulu, Finland Prof. Hervé Barthélemy, Université Sud Toulon Var, France

### Opponent

Prof. Catherine Dehollain, École Polytechnique Fédérale De Lausanne, Switzerland

## Aalto University publication series **DOCTORAL DISSERTATIONS** 201/2015

© Shailesh Singh Chouhan

ISBN 978-952-60-6545-8 (printed)

ISBN 978-952-60-6546-5 (pdf)

ISSN-L 1799-4934

ISSN 1799-4934 (printed)

ISSN 1799-4942 (pdf)

http://urn.fi/URN:ISBN:978-952-60-6546-5

Unigrafia Oy Helsinki 2015

Finland

□ Article dissertation (summary + original articles)

#### Author

Shailesh Singh Chouhan

### Name of the doctoral dissertation CMOS Integrated Circuits for RF-powered Wireless Temperature Sensor **Publisher** School of Electrical Engineering Unit Department of Micro- and Nanosciences Series Aalto University publication series DOCTORAL DISSERTATIONS 201/2015 Field of research Electronic circuit design Manuscript submitted 19 August 2015 Date of the defence 4 December 2015 Permission to publish granted (date) 8 October 2015 Language English

#### **Abstract**

Monograph

This dissertation presents original research contributions in the form of twelve scientific publications that represent advances related to RF-to-DC converters, reference circuits (voltage, current and frequency) and temperature sensors. The primary focus of this research was to design efficient and low power CMOS-based circuit components, which are useful in various blocks of an RF-powered wireless sensor node.

The RF-to-DC converter or rectifier converts RF energy into DC energy, which is utilized by the sensor node. In the implementation of a CMOS-based RF-to-DC converter, the threshold voltage of MOS transistors mainly affects the conversion efficiency. Hence, for the first part of this research, different threshold voltage compensation schemes were developed for the rectifiers. These schemes were divided into two parts; first, the use of the MOSFET body terminal biasing technique and second, the use of an auxiliary circuit to obtain threshold voltage compensation. In addition to these schemes, the use of an alternate signaling scheme for voltage multiplier configuration of differential input RF-harvesters has also been investigated.

A known absolute value of voltage or current is the most useful for an integrated circuit. Thus, the circuit which generates the absolute value of voltage or current is cited as the voltage or current reference circuit respectively. Hence, in the second part of the research, simple, low power and moderately accurate, voltage and current reference circuits were developed for the power management unit of the sensor node. Besides voltage and current reference circuits, a frequency reference circuit was also designed. The use of the frequency reference circuit is in the digital processing and timing functions of the sensor node.

In the final part of the research, temperature sensing was selected as an application for the sensor node. Here, voltage and current based sensor cores were developed to sense the temperature. A smart temperature sensor was designed by using the voltage cores to obtain temperature information in terms of the duty-cycle. Similarly, the temperature equivalent current was converted into the frequency to obtain a temperature equivalent output signal.

All these implementations were done by using two integrated circuits which were fabricated during the year 2013-14.

Keywords CMOS circuit, RF-to-DC converters, voltage reference circuit, current reference circuit, frequency reference circuit, temperature sensors

| ISBN (printed) 978-952-60-6545- | -8 <b>ISBN (pdf)</b> 978-952- | 60-6546-5            |

|---------------------------------|-------------------------------|----------------------|

| ISSN-L 1799-4934                | ISSN (printed) 1799-4934      | ISSN (pdf) 1799-4942 |

| Location of publisher Helsinki  | Location of printing Helsinki | Year 2015            |

| Pages 241                       | urn http://urn.fi/URN:ISBN:97 | 8-952-60-6546-5      |

### **Preface**

This dissertation is based on the work done at the Electronic Circuit Design Laboratory of Aalto University. This work is accomplished in the project, which is funded by the AUTOVOLT of the Academy of Finland and EFFINANO of the Aalto University, Finland. I have been supported financially by the Erasmus Mundus External Cooperation Window India4EU project (Lot 13c) scholarship, to which I express my sincere gratitude. I sincerely appreciate the financial support provided by the scholarship received from the Nokia Foundation during my research.

First and foremost, I thank my PhD supervisor Prof. Kari Halonen for his continual encouragement, strong support, inestimable guidance, and boundless enthusiasm throughout my doctoral studies. His inspiration and sharp advice on technical matters helped me in honing my technical skills and building a strong publication record for myself. He has been instrumental in bringing out my talent and has played a foundational role in my journey of becoming an independent researcher.

I extend my sincere gratitude to Prof. Timo Erkki Rahkonen from the University of Oulu, Finland and Prof. Hervé Barthélemy from Université Sud Toulon-Var, France for performing a thorough review of the thesis and providing insightful comments that helped to improve the quality of this thesis. I am also sincerely thankful to Prof. S.V. Tokekar, IET-DAVV, India without which I would not have landed in this beautiful country to pursue my PhD.

Many thanks to my colleagues at the Department of Micro- and Nanosciences, with whom I have worked on projects. I appreciate the patience shown by them during my weird technical discussions and making the lab a great place to work for me. Especially, I would like to thank Mr. Jakub Gronicz, Mr. Jarno Salomaa, Mr. Mika Pulkkinen and Mr. Tuomas Haapala. I am also thankful to Mr. Ali Vahdati, Mr. Matthew Turnqvist, Mr. Karthik

Upadhya and Ms. Heli Virtanen for many interesting discussions on technical and non-technical issues during tea time. In addition, many thanks to Ms.Lea Söderman for her constant support and friendly attitude.

I could not be the person that I am without endless love and invaluable support of my family and friends throughout my life. With their confidence in me and by their great expectations, I am climbing up the stairs of a successful life. I thank my father, Mr. B. N. Chouhan for always believing in me in whatever I do and for always encouraging me to explore new horizons. I am indebted to my loving mother, Mrs. Pushpa Chouhan for being the greatest 'Mom' that one can wish for, and for always being there when I needed someone to talk to. Most importantly, my mother is the reason that I arrive at the lab early in the morning since it is difficult to make excuses to her for a late arrival. A special acknowledgment to my younger brother Nilesh Singh Chouhan 'The time traveler' for being a critical thinker and the challenging reviewer for me. I want to express my gratitude and deepest appreciation to my lovely sweet daughter, Manaswie, for her great patience, understanding and valuable prayers to complete this work.

I am thankful to my guardian family members in Finland Mrs. Katarina Dimic-Misic and Mr. Stefan Misic, their children Viktor, Filip and Marko and mothers, Ms. Dragica Dimic and Ms. Tuula Jaale, for being my mentors. I appreciate that they have shared everything about life, politics, music, culture and most of all food. I feel honored that they have accepted me as a part of their family and make my life easier in Finland.

A Special thanks to my lifelong friends Sachin Chaudhari and Shekhar Nethi who are 'The game changers' in my research career.

And finally, last but certainly not least, I wish to thank my beloved wife Barkha for her affection, absolute love and precious support. She is my teacher who taught me how to be a fighter in the toughest period of the life. If it wasn't for her continuous love and support, I wouldn't even imagine achieving my goals in doctoral studies. She is the chosen one whom made my difficult times bearable and my good times more special. I am very fortunate to have her as my soulmate.

Espoo, November 13, 2015 Shailesh Singh Chouhan

## **Contents**

| Pı | refac | e       |                                                       |   | ì    |

|----|-------|---------|-------------------------------------------------------|---|------|

| Co | ontei | nts     |                                                       |   | iii  |

| Li | st of | Publi   | cations                                               |   | v    |

| Αι | atho  | r's Cor | ntribution                                            |   | vii  |

| Li | st of | Abbre   | eviations                                             |   | x    |

| Li | st of | Symb    | ools                                                  |   | xiii |

| Li | st of | Figur   | res                                                   | 7 | xvii |

| Li | st of | Table   | $\mathbf{s}$                                          |   | xxi  |

| 1. | Inti  | roduct  | ion                                                   |   | 1    |

|    | 1.1   | Motiv   | ration                                                |   | 1    |

|    | 1.2   | Resea   | arch objectives                                       |   | 3    |

|    | 1.3   | Conte   | ent and thesis organization                           |   | 3    |

|    | 1.4   | Main    | scientific contributions                              |   | 4    |

| 2. | Rac   | lio Fre | equency Energy Harvesting                             |   | 7    |

|    | 2.1   | Overv   | riew                                                  |   | 7    |

|    | 2.2   | Perfor  | rmance affecting design parameters                    |   | 7    |

|    |       | 2.2.1   | CMOS implementation                                   |   | 8    |

|    |       | 2.2.2   | Transistor sizing and operating frequency             |   | 11   |

|    |       | 2.2.3   | Sizing of load, fly capacitors and number of stages . |   | 14   |

|    |       | 2.2.4   | Matching network                                      |   | 21   |

|    |       | 2.2.5   | Figure of merits                                      |   | 25   |

|    | 2.3   | Propo   | sed RF-to-DC converters                               |   | 25   |

|    |       | 2.3.1   | Design based on controlling body voltage              |   | 26   |

|    |       | 2.3.2  | Designs with additional circuits                        | 47  |

|----|-------|--------|---------------------------------------------------------|-----|

|    |       | 2.3.3  | Design using signaling scheme for voltage multiplier    | 52  |

|    | 2.4   | Sumn   | nary                                                    | 54  |

| 3. | Ref   | erence | e Circuits                                              | 57  |

|    | 3.1   | Introd | luction                                                 | 57  |

|    | 3.2   | Perfor | mance measurement parameters                            | 57  |

|    |       | 3.2.1  | Line regulation                                         | 58  |

|    |       | 3.2.2  | Temperature coefficient                                 | 58  |

|    |       | 3.2.3  | Power supply rejection ratio                            | 58  |

|    |       | 3.2.4  | Power dissipation                                       | 59  |

|    |       | 3.2.5  | Output noise                                            | 59  |

|    |       | 3.2.6  | Phase noise and Jitter                                  | 59  |

|    | 3.3   | Propo  | sed voltage, current and frequency reference circuits . | 61  |

|    |       | 3.3.1  | Voltage reference circuit                               | 61  |

|    |       | 3.3.2  | Current reference circuit                               | 75  |

|    |       | 3.3.3  | Frequency reference circuit                             | 81  |

|    | 3.4   | Sumn   | nary                                                    | 87  |

| 4. | Ten   | ıperat | ure Sensors                                             | 89  |

|    | 4.1   | Overv  | iew                                                     | 89  |

|    | 4.2   | Propo  | sed temperature sensing methods                         | 90  |

|    |       | 4.2.1  | Voltage-based temperature sensor                        | 90  |

|    |       | 4.2.2  | Current-based temperature sensor                        | 95  |

|    | 4.3   | Sumn   | nary                                                    | 100 |

| 5. | Con   | clusio | ons                                                     | 101 |

| Re | efere | ences  |                                                         | 105 |

| Pι | ıblic | ations |                                                         | 125 |

### **List of Publications**

This thesis consists of an overview and of the following publications which are referred to in the text by their Roman numerals.

- I Chouhan S.S. and Halonen K. The design and implementation of DT-MOS biased all PMOS rectifier for RF energy harvesting. *Proceedings* of the 12th IEEE International New Circuits and Systems Conference (NEWCAS), Trois-Rivieres, QC Canada, pp. 444–447, Jun. 2014.

- II Chouhan S.S. and Halonen K.. The DTMOS based UHF RF to DC conversion. *Proceedings of the 20th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Abu Dhabi, UAE*, pp.629–632, Dec. 2013.

- III Chouhan S.S. and Halonen K. Internal Vth cancellation scheme for RF to DC rectifiers used in RF energy harvesting. *Proceedings of the 21st IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Marseille, France*, pp.235–238, Dec. 2014.

- **IV** Chouhan S.S. and Halonen K. Threshold voltage compensation scheme for RF-to-DC converter used in RFID applications. *Electronics Letters*, vol.51, no.12, pp.892-894, Jun. 2015.

- V Chouhan S.S. and Halonen K. A novel cascading scheme to improve the performance of voltage multiplier circuits. *Analog Integrated Circuits* and Signal Processing, Springer, vol.84, no.3, pp.373-381, Sep. 2015.

- VI Chouhan S.S. and Halonen K. Design and implementation of all MOS micro-power voltage reference circuit. *Analog Integrated Circuits and Signal Processing, Springer*, vol.80, no.3, pp.399–406, Sep. 2014.

- VII Chouhan S.S. and Halonen K. Design and implementation of a micropower CMOS voltage reference circuit based on thermal compensation of Vgs. *Microelectronics Journal, Elsevier*, vol.46, no.1, pp.36–42, Jan. 2015.

- VIII Chouhan S.S. and Halonen K. A  $0.67\mu$ W, 177 ppm/°C all MOS current reference circuit in  $0.18\mu$ m CMOS technology. Submitted to IEEE transaction on circuits and systems-II: Express Briefs, .

- IX Chouhan S.S. and Halonen K. A micro power temperature compensated frequency generating circuit. *Proceedings of 22nd European conference on circuit theory and design (ECCTD)*, Trondheim, Norway, Aug. 24–26, pp.1-4, Aug. 2015.

- **X** Chouhan S.S. and Halonen K. Design and implementation of micropower temperature to duty cycle converter using differential temperature sensing. *Microelectronics Journal, Elsevier*, vol.46, no.6, pp.482–489, Jun. 2015.

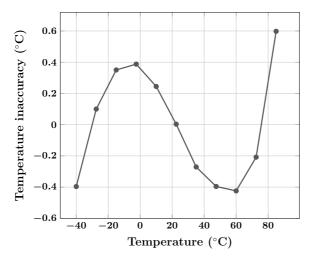

- **XI** Chouhan S.S. and Halonen K. Nano-ampere PTAT current source with temperature inaccuracy  $<\pm 1^{\circ}$ C. *Electronics Letters*, vol.51, no.1, pp.60–61, Jan. 2015.

- XII Chouhan S.S. and Halonen K. A low power temperature to frequency converter for the on-chip temperature measurement. *IEEE Sensors Journal*, vol.15, no.8, pp.4234-4240, Aug. 2015.

### **Author's Contribution**

## Publication I: "The design and implementation of DTMOS biased all PMOS rectifier for RF energy harvesting"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements, wrote the manuscript of the paper and presented the paper.

### Publication II: "The DTMOS based UHF RF to DC conversion"

The author performed all circuit analysis and simulations, wrote the manuscript of the paper and presented the paper.

# Publication III: "Internal Vth cancellation scheme for RF to DC rectifiers used in RF energy harvesting"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements, wrote the manuscript of the paper and presented the paper.

# Publication IV: "Threshold voltage compensation scheme for RF-to-DC converter used in RFID applications"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

# Publication V: "A novel cascading scheme to improve the performance of voltage multiplier circuits"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

## Publication VI: "Design and implementation of all MOS micro-power voltage reference circuit"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

# Publication VII: "Design and implementation of a micro-power CMOS voltage reference circuit based on thermal compensation of Vgs"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

# Publication VIII: "A 0.67 $\mu$ W, 177 ppm/°C all MOS current reference circuit in 0.18 $\mu$ m CMOS technology"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

# Publication IX: "A micro power temperature compensated frequency generating circuit"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements, wrote the manuscript of the paper and presented the paper.

# Publication X: "Design and implementation of micro-power temperature to duty cycle converter using differential temperature sensing"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

# Publication XI: "Nano-ampere PTAT current source with temperature inaccuracy $<\pm 1^{\circ} \text{C}$ "

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

# Publication XII: "A low power temperature to frequency converter for the on-chip temperature measurement"

The author performed all circuit analysis, was responsible for the reported chip, performed all measurements and wrote the manuscript of the paper.

### **List of Abbreviations**

ADC Analog to Digital Converter

**BJT** Bipolar Junction Transistor

BTMOS Body Tied to Source Metal Oxide Semiconductor

**BVR** Bandgap Voltage Reference

**CMOS** Complementary Metal Oxide Semiconductor

CTAT Complementary To Absolute Temperature

**DAC** Digital to Analog Converter

**DTMOS** Dynamic Threshold Metal Oxide Semiconductor

**EVC** External Vth Cancellation

**EIRP** Effective Isotropic Radiated Power

FCC Federal Communication Commission

FBB Forward Body Bias

**FOM** Figure Of Merit

FSNL Full Scale Non Linearity

**IoT** Internet-of-Things

IVC Internal Vth Cancellation

KVL Kirchoff Voltage Law

LR Line Regulation

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NMOS N-type Metal Oxide Semiconductor

PCE Power Conversion Efficiency

PMOS P-type Metal Oxide Semiconductor

**PSRR** Power Supply Rejection Ratio

**PTAT** Proportional to Absolute Temperature

**QoS** Quality of Service

**RBM** Resistor Less Beta Multiplier

RF Radio Frequency

**RFID** Radio Frequency Identification

SBB Swapped Body Bias

**SOI** Silicon-On-Insulator

**SVC** Self Vth Cancellation

TC Temperature Coefficient

VCE Voltage Conversion Efficiency

VNA Voltage Network Analyzer

VM Voltage Multiplier

WSN Wireless Sensor Network

## **List of Symbols**

$A_M$  Area of MOSFET  $A_E$  Junction area of BJT

$A_v$  Voltage gain of matching network  $C_{OX}$  Oxide capacitance of MOSFET  $C_{out}$  Load capacitance per stage

$C_{fly}$  Fly capacitance

$C_{pad}$  Equivalent capacitance of pad  $C_{rect}$  Equivalent capacitance of rectifier

$\Delta V_{ripple}$  Peak-to-peak ripple voltage

$\Delta X$  Difference of maximum and minimum value of reference signal

$f_{RF}$  Frequency of RF signal  $I_c$  Collector current of BJT

$I_s$  Reverse saturation current of BJT

$I_d$  Drain current of MOSFET

$I_{d0}$  Saturation current of MOSFET

$I_{load}$  Load current  $I_{supply}$  Supply current

$J_E$  Current density of BJT K Boltzmann constant L Length of MOSFET  $L_d$  Diffusion length  $L_{sc}$  Residual inductance  $LR_{nom}$  Nominal line regulation

n Number of fingers N Number of stages  $P_{out}$  Output power  $P_{in}$  Input RF power

$P_{loss}$  Power loss in each branch

$P_{source}$  Source power

$q \hspace{1cm} \textbf{Electronic charge}$

$Q_c$  Quality factor of capacitor  $R_{ON}$  ON-resistance of MOSFET  $R_{in}$  Input resistance of the rectifier

$R_L$  Load resistance

$R_{sc}$  Residual resistance

$S_{11}$  Single-ended reflection coefficient

$S_{dd11}$  Mixed mode differential-to-differential reflection coefficient

$S_{cd11}$  Differential-to-common mode reflection coefficient

S Aspect ratio of transistor

$t_d$  Delay

TC Temperature coefficient

T Temperature

$T_0$  Ambient temperature

$V_{BE}$  Base-emitter voltage of BJT

$egin{array}{ll} V_{in} & & & ext{Input voltage} \\ V_{out} & & & ext{Output voltage} \end{array}$

$egin{array}{lll} V_{sg} & ext{Source-gate voltage of MOSFET} \ V_{sd} & ext{Source-drain voltage of MOSFET} \ V_{th} & ext{Threshold voltage of MOSFET} \ V_{thp} & ext{Threshold voltage of pMOSFET} \ V_{thn} & ext{Threshold voltage of nMOSFET} \ \end{array}$

$V_{out_{ideal}}$  Ideal value of the rectified DC voltage

$V_{DC}$  DC voltage

$V_m$  Peak amplitude of RF voltage signal  $V_{thv0}$  Zero bias threshold voltage of pMOSFET

$egin{array}{lll} V_{SB} & & ext{Source-body voltage} \ V_{supply} & & ext{Supply voltage} \ W & & ext{Width of MOSFET} \end{array}$

$X_{nom}$  Nominal value of reference signal  $X_{max}$  Maximum value of reference signal  $X_{min}$  Minimum value of reference signal

$Z_{fly}$  Fly impedance  $Z_{source}$  Source impedance

$Z_{in}$  Input impedance

$\alpha_{\mu}$  Temperature independent constant for mobility

$\alpha_T$  Thermal slope of threshold voltage

$eta_n$  Transconductance parameter of nMOSFET  $eta_p$  Transconductance parameter of pMOSFET

$\begin{array}{ll} \Gamma & & \text{Reflection coefficient} \\ \gamma & & \text{Body effect coefficient} \\ \eta & & \text{Subthreshold slope} \end{array}$

$\eta_{ehu}$  Efficiency of energy harvesting unit

$\eta_{antenna}$  Efficiency of antenna

$\eta_{match}$  Efficiency of matching network

$\eta_{rect}$  Efficiency of the rectifier

$\mu$  Mobility parameter of MOSFET

$\phi_F$  Fermi potential  $\chi$  Voltage loss

$\omega_{srfc}$  Self resonating frequency

## **List of Figures**

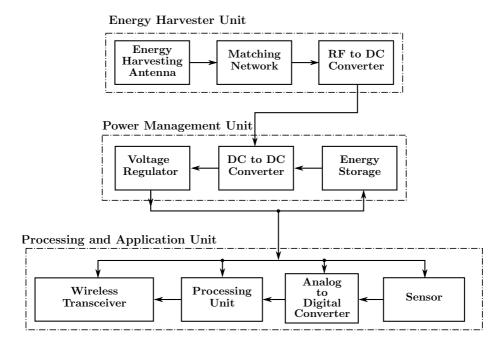

| 1.1  | Block diagram of RF-powered wireless sensor node or system.                                              | 2  |

|------|----------------------------------------------------------------------------------------------------------|----|

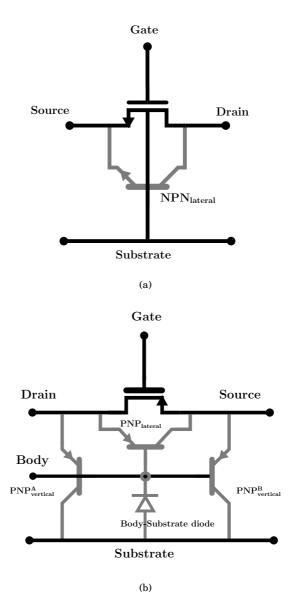

| 2.1  | (a) NMOS and (b) PMOS transistors with parasitics BJTs                                                   |    |

|      | in twin well process implementation                                                                      | 9  |

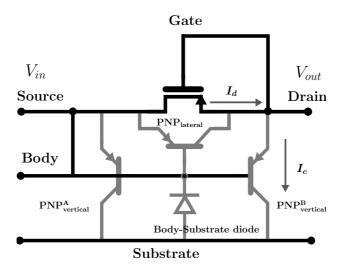

| 2.2  | Diode-connected PMOS transistor with parasitic BJTs                                                      | 10 |

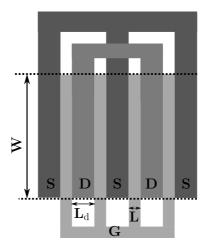

| 2.3  | Example of a layout with number of fingers (n) equal to 4                                                | 11 |

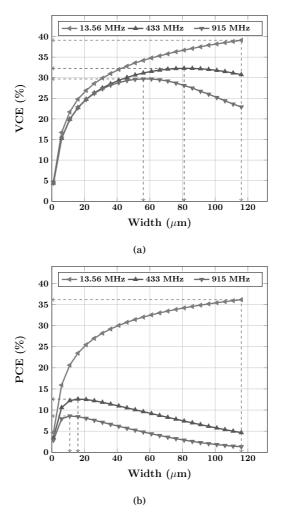

| 2.4  | Simulation results of (a) VCE and (b) PCE with varying                                                   |    |

|      | transistor width at different input RF frequencies for mini-                                             |    |

|      | mum length transistor                                                                                    | 13 |

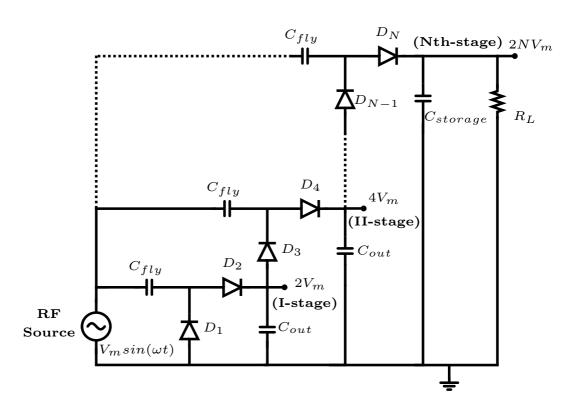

| 2.5  | Voltage multiplier circuit.                                                                              | 14 |

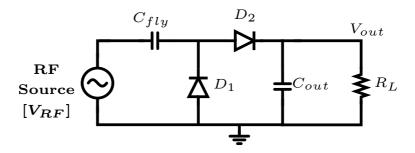

| 2.6  | Single-stage rectifier.                                                                                  | 15 |

| 2.7  | (a) Charging phase and (b) Discharging phase of single-stage                                             |    |

|      | rectifier                                                                                                | 16 |

| 2.8  | Simulation results of (a) VCE and (b) PCE with varying cou-                                              |    |

|      | pling capacitor size at different input RF frequencies                                                   | 17 |

| 2.9  | Simulated output DC voltage with increasing number of                                                    |    |

|      | stages (N)                                                                                               | 18 |

| 2.10 | $\label{eq:control_equal} AC \ equivalent \ schematic \ of \ N\text{-stage voltage multiplier circuit}.$ | 19 |

| 2.11 | $\label{prop:continuous} Variation of input resistance with increasing number of stages$                 |    |

|      | (N)                                                                                                      | 20 |

| 2.12 | Variation of power conversion efficiency with increasing num-                                            |    |

|      | ber of stages (N)                                                                                        | 21 |

| 2.13 | Matching network.                                                                                        | 22 |

| 2.14 | Power distribution network                                                                               | 24 |

| 2.15 | Circuit setup used for NMOS transistor characterization                                                  | 27 |

| 2.16 | NMOS transistor characterization plots obtained by vary-                                                 |    |

|      | ing source-body voltage.                                                                                 | 28 |

| 2.17 | NMOS transistor with parasitic diodes                                                                    | 29 |

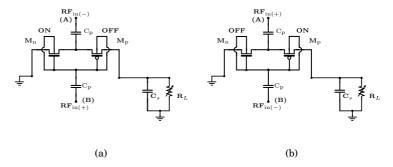

| 2.18 | (a) Conventional and (b) SBB-based differential rectifier. $$ . $$                     | 30 |

|------|----------------------------------------------------------------------------------------|----|

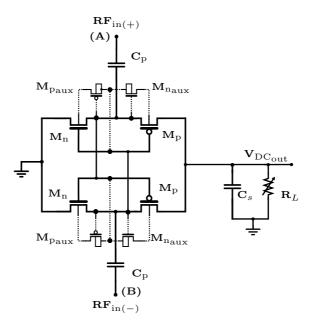

| 2.19 | DTMOS-biased differential rectifier                                                    | 33 |

| 2.20 | (a) Charging and (b) Discharging phase of DTMOS-biased                                 |    |

|      | differential rectifier                                                                 | 33 |

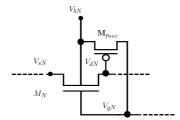

| 2.21 | Modified DTMOS-biased differential rectifier                                           | 35 |

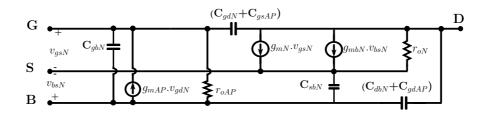

| 2.22 | Body connection for NMOS transistor                                                    | 36 |

| 2.23 | Small signal model equivalent of $\mathbf{M}_n$ and $\mathbf{M}_{p_{aux}}$ transistors | 36 |

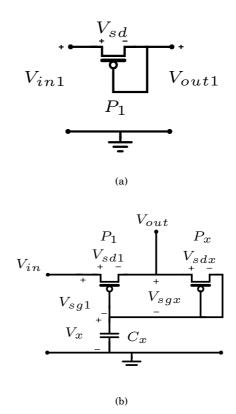

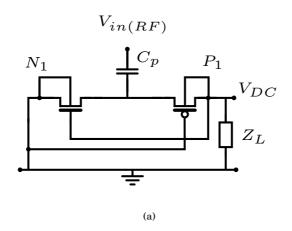

| 2.28 | (a) Conventional diode-connected transistor and (b) after                              |    |

|      | implementation of the proposed scheme                                                  | 47 |

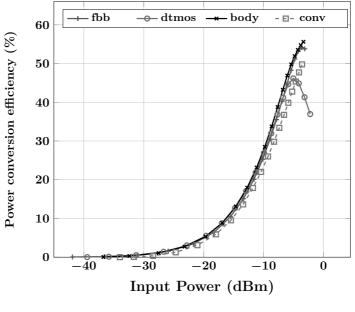

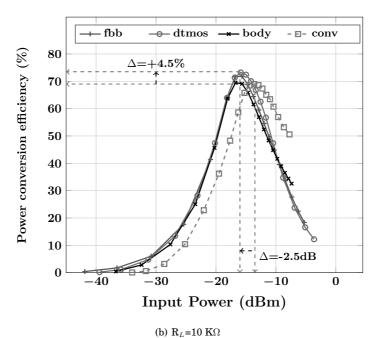

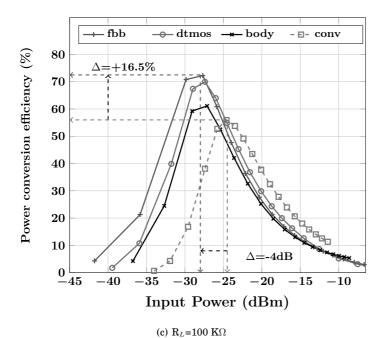

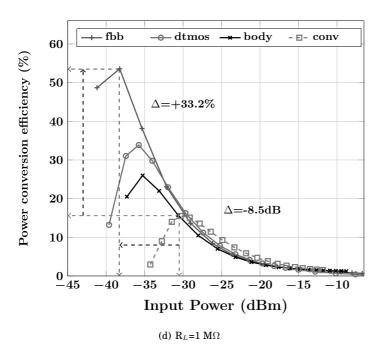

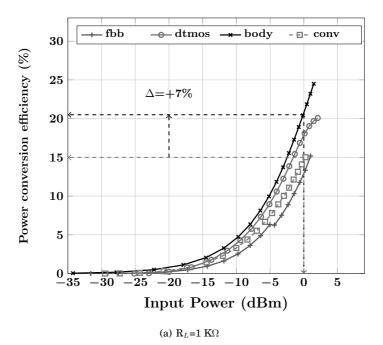

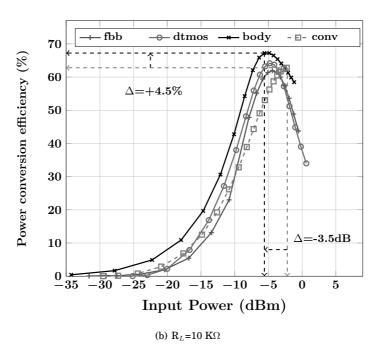

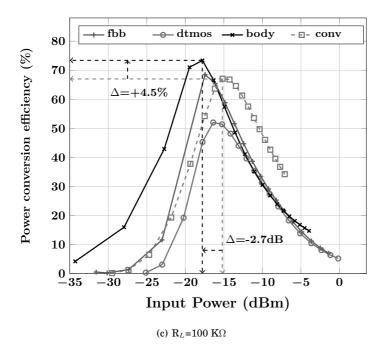

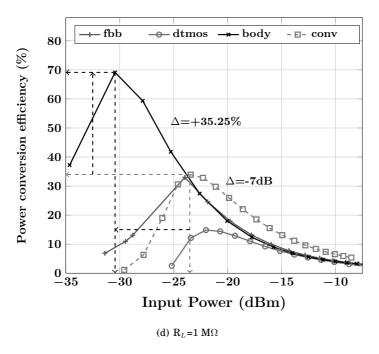

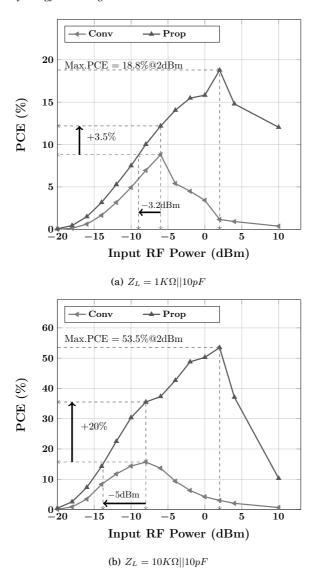

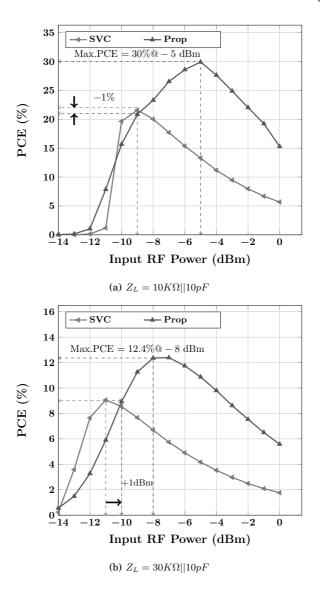

| 2.29 | Measured power conversion efficiency of the conventional                               |    |

|      | and proposed rectifiers for different load impedances                                  | 48 |

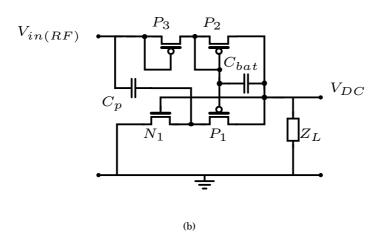

| 2.30 | (a) Self Vth Cancellation based CMOS rectifier and (b) after                           |    |

|      | implementation of the proposed scheme in PMOS transistor                               |    |

|      | (P1)                                                                                   | 50 |

| 2.31 | Measured power conversion efficiency of self Vth cancella-                             |    |

|      | tion scheme based CMOS rectifier (SVC) and the proposed                                |    |

|      | CMOS rectifier (Prop) for different load impedances                                    | 51 |

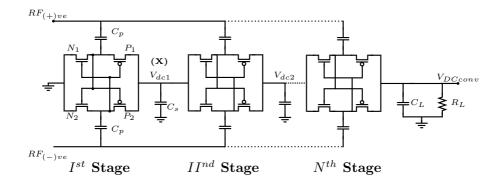

| 2.32 | Differential drive rectifier based voltage multiplier arrange-                         |    |

|      | ment                                                                                   | 52 |

| 2.33 | Differential drive rectifier-based voltage multiplier arrange-                         |    |

|      | ment with proposed signaling scheme.                                                   | 53 |

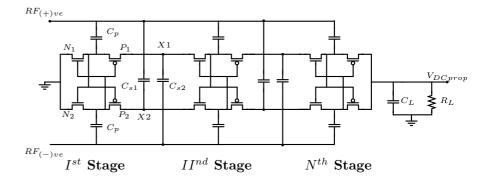

| 2.34 | Ideal and simulated plots of conventional ( $C_{\it ideal}$ and $C_{\it sim}$ )        |    |

|      | and the proposed ( $P_{\it ideal}$ and $P_{\it sim}$ ) voltage multiplier circuits.    | 54 |

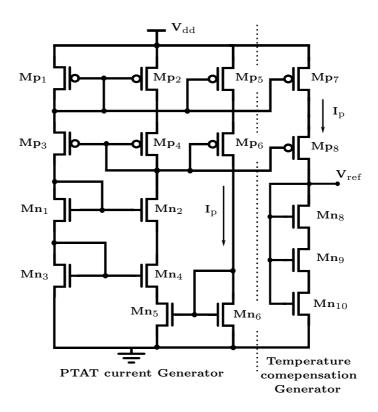

| 3.1  | Schematic of voltage reference circuit I [VI]                                          | 62 |

| 3.2  | Schematic of voltage reference circuit II [VII]                                        | 63 |

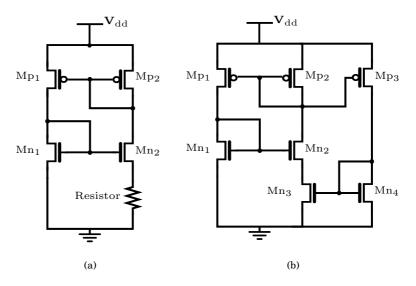

| 3.3  | Schematics of (a) classical beta multiplier circuit and its (b)                        |    |

|      | resistor-less implementation.                                                          | 63 |

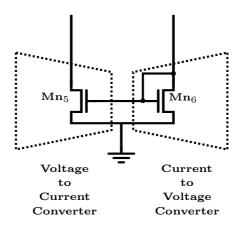

| 3.4  | Voltage-current conversion loop formed by transistors ${\cal M}n_5$                    |    |

|      | and $Mn_6$                                                                             | 65 |

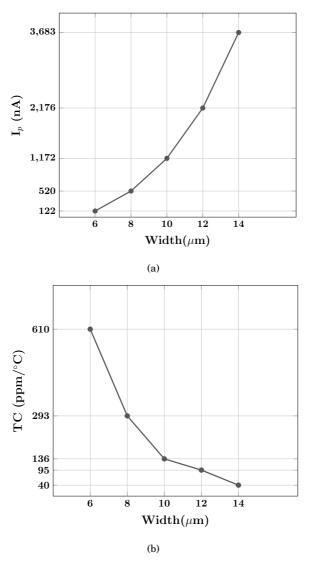

| 3.5  | Variation in the values of (a) current $(I_p)$ at room tempera-                        |    |

|      | ture and its (b) temperature coefficient with increasing width. \\                     | 66 |

| 3.6  | Simple diode-connected circuit                                                         | 67 |

| 3.7  | Temperature dependent behavior of various circuit param-                               |    |

|      | eters                                                                                  | 69 |

| 3.8  | Alternate architecture to achieve temperature compensated                              |    |

|      | voltage from a simple diode-connected circuit.                                         | 69 |

| 3.9  | Conceptual schematic arrangement for voltage reference cir-                            |    |

|      | cuit I                                                                                 | 70 |

| 3.10 | Simulation results for voltage reference circuit I                          | 71 |

|------|-----------------------------------------------------------------------------|----|

| 3.11 | Conceptual schematic arrangement for voltage reference cir-                 |    |

|      | cuit II                                                                     | 72 |

| 3.12 | Simulation results for voltage reference II. $\ \ldots \ \ldots$            | 72 |

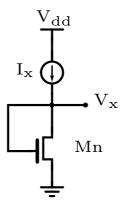

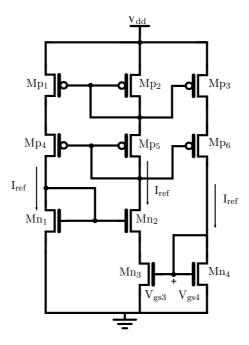

| 3.13 | Conventional current reference circuit                                      | 76 |

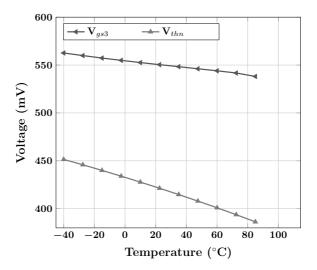

| 3.14 | Simulated temperature behavior of $V_{gs3}$ and $V_{thn}$                   | 77 |

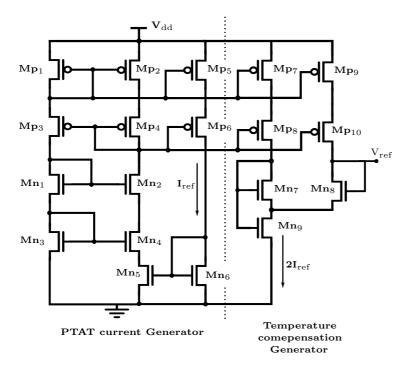

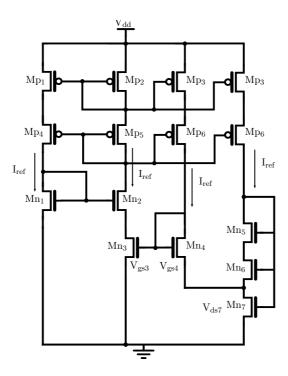

| 3.15 | Schematic of the proposed current reference circuit                         | 78 |

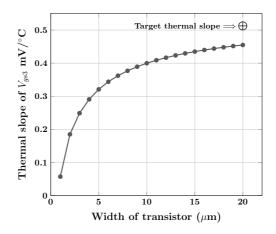

| 3.16 | Variation of thermal slope of ${\cal V}_{gs3}$ with respect to width of     |    |

|      | composite array transistors                                                 | 79 |

| 3.17 | Circuit setup to plot transfer characteristics of NMOS tran-                |    |

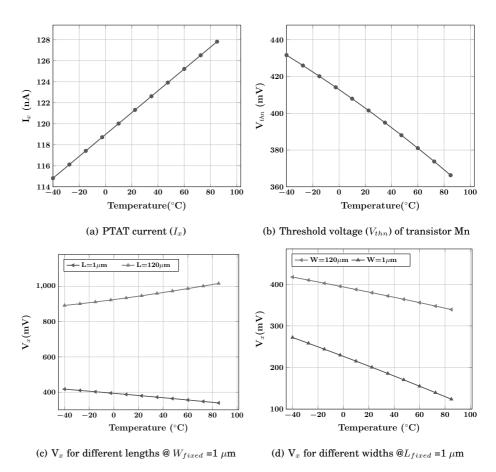

|      | sistor                                                                      | 82 |

| 3.18 | $Transfer\ characteristics\ of\ NMOS\ transistor\ at\ different\ tem-$      |    |

|      | peratures                                                                   | 83 |

| 3.19 | Variation of oscillation frequency with temperature for se-                 |    |

|      | lected supply voltage values                                                | 84 |

| 3.20 | Percentage change in frequency with supply voltage                          | 84 |

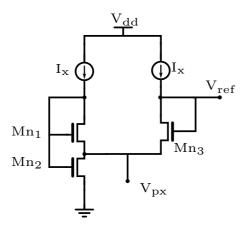

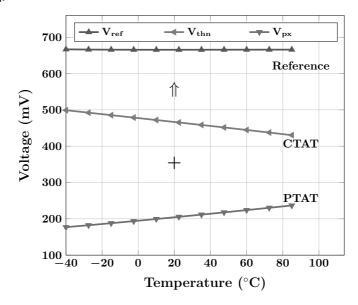

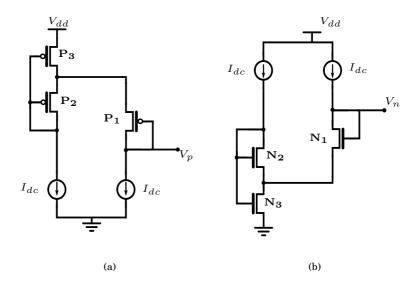

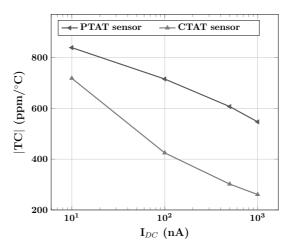

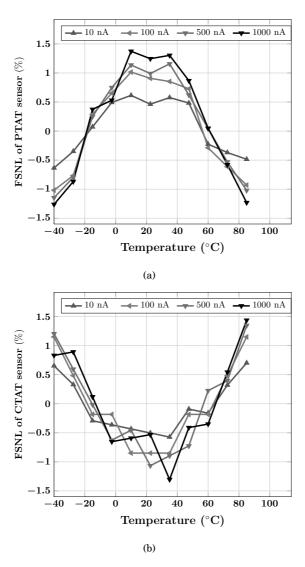

| 4.1  | Circuit arrangements to generate PTAT and CTAT voltages.                    | 91 |

| 4.2  | Variation of temperature coefficients with DC current. $\ \ . \ \ . \ \ .$  | 93 |

| 4.3  | Variation of full-scale non linearity (%) with temperature                  |    |

|      | (°C) of (a) PTAT and (b) CTAT sensors $\ \ldots \ \ldots \ \ldots \ \ldots$ | 94 |

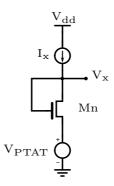

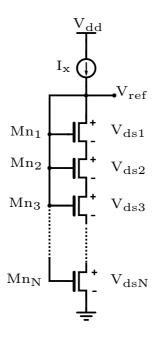

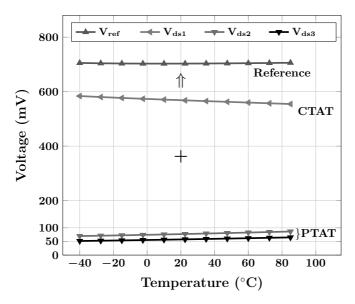

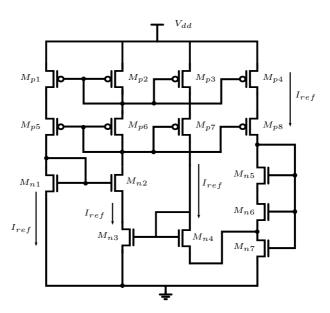

| 4.4  | Schematic of PTAT current generator circuit                                 | 95 |

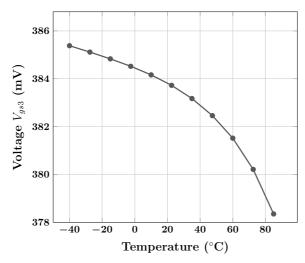

| 4.5  | Temperature independent behavior of voltage $V_{gs3}.$                      | 96 |

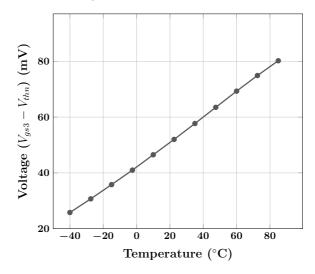

| 4.6  | Simulated temperature behavior of voltage (V $_{gs3}$ -V $_{thn}$ )         | 97 |

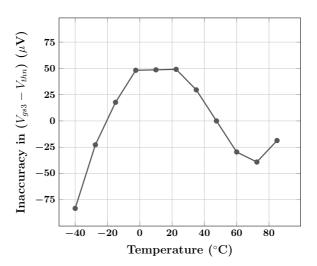

| 4.7  | Linearity error in voltage ( $V_{gs3}$ - $V_{thn}$ )                        | 97 |

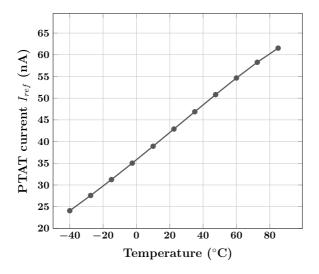

| 4.8  | Simulated temperature behavior of PTAT current ( $I_{ref}$ )                | 98 |

| 4.9  | Simulated temperature inaccuracy (°C) of PTAT current ( $I_{ref}$ ).        | 98 |

## **List of Tables**

| 2.1 | Simulation environment used to evaluate voltage multiplier.                | 19 |

|-----|----------------------------------------------------------------------------|----|

| 2.2 | Performance summary and comparison of differential recti-                  |    |

|     | fiers                                                                      | 31 |

| 2.3 | Performance summary and comparison of differential recti-                  |    |

|     | fiers                                                                      | 34 |

| 2.4 | Performance summary and comparison of differential recti-                  |    |

|     | fiers                                                                      | 37 |

| 2.5 | Performance comparison with state-of-the-art RF to DC con-                 |    |

|     | verters                                                                    | 55 |

| 3.1 | Methods to improve performance parameters of reference                     |    |

|     | circuits                                                                   | 60 |

| 3.2 | Transistors aspect ratios used in simulations                              | 65 |

| 3.3 | Performance comparison with state-of-the-art voltage refer-                |    |

|     | ence circuits                                                              | 74 |

| 3.4 | Simulation-based performance comparison                                    | 79 |

| 3.5 | Performance comparison of proposed current reference cir-                  |    |

|     | cuit with state-of-the art current reference circuits. $\ \ldots \ \ldots$ | 80 |

| 3.6 | $Performance\ comparison\ of\ proposed\ frequency\ reference\ with$        |    |

|     | state-of-the-art frequency reference circuits.                             | 86 |

| 4.1 | Simulation environment for proposed temperature sensors.                   | 92 |

| 4.2 | Performance comparison of proposed temperature sensors                     |    |

|     | with state-of-the-art temperature sensing circuits                         | 99 |

### 1. Introduction

### 1.1 Motivation

The Internet-of-Things (IoT) is becoming an essential part of daily life to bring about the implementation of the smart and proactive standards both at work and at home [1]. The Wireless Sensor Network (WSN) is one of the key building blocks of IoT [2], being a group of spatially located, specialized transducers with a communication infrastructure. These transducers commonly known as wireless sensor nodes, are used to monitor and record various physical, chemical and biological parameters at diverse locations [3]. The performance of the whole WSN is largely dependent on the performance of the individual wireless sensor nodes [4]. And these nodes are greatly affected by the strict power budget for sensing, computation and transmission of data [5].

Traditionally, the battery has been used as a power source for these sensor nodes [6–10], but due to their limited capacity the challenge lies with nodes becoming inoperable once the battery is drained. The maintenance of these batteries becomes costly as they require continuous monitoring and direct human involvement for management and battery replacement. It becomes impractical and unworkable when hundreds of sensor nodes are spread out widely over a large geographical expanse [11].

The limits associated with battery-operated sensor nodes has drawn interest towards the development of energy autonomous sensor nodes. Thus, to achieve energy autonomy in them an extra energy transducer is added to the board. As a result, it will be able to harvest energy from the surrounding environment or by using dedicated energy sources. The ambient energy sources present are mainly solar [12], heat [13], wind [14], water [15], inertial [16] and Radio Frequency (RF) waves [17] to self-

support the sensor node for an unlimited lifetime.

The strength of many of these sources is limited only by the environmental situation except for RF energy. The usage of RF energy is a promising option for energy harvesting due to the omnipresence of RF signals [18]. The concept of transmitting energy wirelessly was first proposed by Nikola Tesla in the year 1893 [19]. Since then, it has excited researchers and several experimental studies have been conducted to demonstrate the possibility of RF- energy harvesting [20].

In general practice, the maximum RF power level from the source has been restricted within Federal Communication Commission (FCC) exposure limits [21]. Therefore, with lower power density levels the conversion efficiency of RF energy transducers will be affected [22]. Hence, it will result in lower values of available power for sensor nodes to function.

This dissertation focused on developing new architectures for RF-energy transducers which can operate effectively with a lower input RF power level. In addition, low power Complementary Metal Oxide Semiconductor (CMOS) components or circuits, used in the sensor node were also developed,.

Figure 1.1. Block diagram of RF-powered wireless sensor node or system.

### 1.2 Research objectives

A typical block diagram of the RF-powered sensor node/system [23–25] is shown in Fig.1.1. The theoretical and the experimental work presented in the dissertation concentrates on three building blocks which are given in Fig.1.1. The specific contributions made in this dissertation for the development of a wireless sensor node are listed as follows:

### 1. RF-to-DC converters for Energy Harvesting Unit

- (a) Designed with body biasing techniques

- (b) Designed with threshold voltage compensation techniques

### 2. Reference circuits for Power Management Unit

- (a) Voltage reference circuit

- (b) Current reference circuit

- (c) Frequency reference circuit

### 3. Processing and Application Unit

- (a) Voltage-based temperature sensor

- (b) Current-based temperature sensor

These blocks and their design objectives differ widely from each other. However, all of the work focuses on the unified topic of making sensor nodes smaller and more efficient. The ultimate objective of the dissertation is to provide new implementations for RF energy harvesters and simple low-power CMOS components.

### 1.3 Content and thesis organization

The dissertation consists of two parts, the first providing an introductory background and the second being the compilation of the scientific publications [I]-[XII] by the author. The introductory part is comprised of five

chapters, which describe the design implementations and other relevant theories related to the original scientific contributions.

Chapter 2 provides an overview of the RF energy harvesting and highlights the key considerations and design challenges of the RF energy harvesters.

Chapter 3 is concerned with the temperature-independent reference circuits. The chapter opens with a discussion of the requirement and the performance parameters of the reference circuits It is then followed by a detailed investigation of the proposed voltage, current, and frequency reference circuits.

Chapter 4 incorporates the details related to realization of a low power temperature sensor. Two approaches have been adopted for temperature sensing namely, voltage and current based temperature sensing. The summary of these implementations and the experimental results are contained within this chapter.

The introductory part is concluded in Chapter 5 with a brief summary of the preceding chapters. In addition, the chapter also takes into account the primary outcomes of the dissertation and suggests directions for future work.

The second part of the dissertation consists of scientific publications [I]-[XII]. They are listed at pp. vii-viii and the author's contribution to each one is mentioned on pp. ix-xi. The publications explain the original contributions of this dissertation in greater detail.

### 1.4 Main scientific contributions

The most important scientific contributions to the research community to be found in Publications [I]-[XII] are summarized as follows:

- Different threshold compensation methods are suggested for RF-to-DC conversion [I]-[V].

- 2. Two different simple temperature compensation circuits are proposed which, when combined with the Resistor Less Beta Multiplier (RBM) circuit, generate the reference voltages [VI]-[VII].

- 3. A simple circuit arrangement is proposed to improve the temperature coefficient of the conventional RBM current reference circuit [VIII].

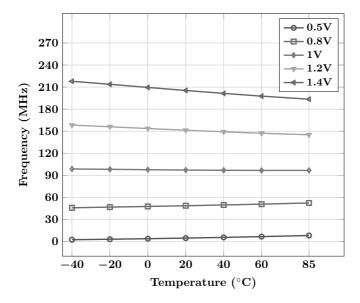

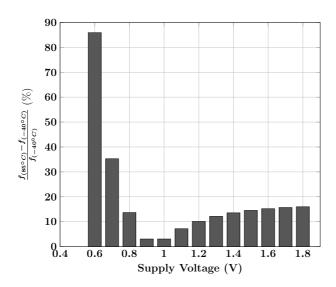

- 4. The utility of the principle of the reversal of the temperature behavior with the supply voltage is demonstrated by the measurement for generating the reference frequency [XI].

- 5. Architectures for temperature sensors are proposed which generate a Proportional to Absolute Temperature (PTAT) and Complementary To Absolute Temperature (CTAT) temperature equivalent signal. These sensors are capable of operating at ultra low power and can sense temperature with moderate inaccuracy [X]-[XII].

Introduction

## 2. Radio Frequency Energy Harvesting

### 2.1 Overview

Radio frequency (RF) energy transfer and harvesting techniques have recently become alternative methods for powering the next generation of electronic devices because they offer the possibility of transferring energy wirelessly. A rectifier (or RF-to-DC converter) is an important component present between the received RF signal and the system. It converts the RF energy to the DC energy and the system uses the rectified DC to perform various functions. A typical block diagram of an RF energy harvesting node/system is shown in Fig. 1.1.

This topology is widely used in wireless sensor networks [23–27], Radio Frequency Identification (RFID) [28–30] and implementation designed for biomedical instrumentation [31–33].

The power flow in the node (Fig. 1.1) is from the energy-harvesting unit to the processing unit. Thus, the energy-harvesting unit should deliver high performance to maintain high Quality of Service (QoS) from the node.

### 2.2 Performance affecting design parameters

The performance of an energy-harvesting unit depends on the conversion efficiencies of the RF-to-DC converter. Therefore, it is necessary to keep account of the performance affecting parameters to avoid the degradation of the power conversion chain. In this section, various parameters have been discussed, which inherently affects the performance of any rectifier. These discussions include all necessary design guidelines for improving the performance of the RF-to-DC converter.

### 2.2.1 CMOS implementation

In the CMOS technology, a diode-connected Metal Oxide Semiconductor Field Effect Transistor (MOSFET) is generally used as a diode [34]. Thus, both N-type Metal Oxide Semiconductor (NMOS) and P-type Metal Oxide Semiconductor (PMOS) transistors are useful as a rectifying element in an RF-to-DC converter design. It is well known that a CMOS implementation is done in four general forms: (i) n-well, (ii) p-well, (iii) twin-well and (iv) triple-well [35]. In a modern CMOS implementation, either twin-well or triple-well implementations are the preferred choices [36].

In a CMOS process with a twin-well implementation, an NMOS transistor resides directly in the substrate as shown in Fig. 2.1. Hence, the NMOS transistor will introduce high substrate noise compared with the PMOS transistor, which is sitting inside a well. For this reason, a diodeconnected PMOS transistor is the preferred choice for implementing the rectifier. Though an NMOS transistor has some inherent performance advantages over a PMOS transistor; the electron mobility is approximately twice that of hole mobility hence an n-channel device will have one-half the ON-resistance (or impedance) of an equivalent p-channel device with the same geometry under the same operating conditions. Therefore, it makes an NMOS transistor faster than a PMOS transistor [37].

Referring to Fig. 2.1 it can be noticed that the PMOS transistor has more parasitic Bipolar Junction Transistor (BJT)s in comparison to the NMOS transistor in a twin-well implementation. Generally, the lateral BJTs (NPN $_{\rm lateral}$ ) and PNP $_{\rm lateral}$ ) do not introduce any undesirable parasitic effects rather, they contribute to the input current and their contributions depend on the body biasing arrangement [38]. However, the presence of vertical BJTs (PNP $_{\rm vertical}$ ) are the main problem during the working of a rectifier. This is because it lead towards an increase in the leakage current due to the periodic forward biasing of the base emitter junctions.

To estimate the loss that occurs in the current because of  $PNP_{\rm vertical}$  the following guideline is suggested.

Consider a diode-connected PMOS transistor shown in Fig. 2.2 where  $V_{in}$  is the input RF signal applied at the source terminal, and  $V_{out}$  is the rectified DC output voltage obtained at the drain terminal. It can be seen in Fig. 2.2 that the body terminal is tied to the source terminal; hence the loss in drain current ( $I_d$ ) will be caused due to PNPB transition. Thus, the

Figure 2.1. (a) NMOS and (b) PMOS transistors with parasitics BJTs in twin well process implementation.

collector current  $(I_c)$  flowing through it is given by [39]:

$$I_c = I_S \cdot \exp\left(\frac{V_{BE}}{V_T}\right) = I_S \cdot \exp\left(\frac{V_{in} - V_{out}}{V_T}\right)$$

(2.1)

where  $I_S$  is the reverse saturation current in the range of  $10^{-15}$  amperes to  $10^{-12}$  amperes,  $V_{BE}$  is the base-emitter voltage and  $V_T$  is the thermal voltage which is  $\approx$  26 mV at 300 °K.

Similarly, the drain current  $(I_d)$  [35],[40] flowing through the diode-

Figure 2.2. Diode-connected PMOS transistor with parasitic BJTs.

connected PMOS transistor is:

$$I_d = I_{d0} \cdot \exp\left(\frac{V_{sg}}{\eta V_T}\right) = I_{d0} \cdot \exp\left(\frac{V_{in} - V_{out}}{\eta V_T}\right)$$

(2.2)

where  $I_{d0}$  is the saturation current,  $V_{sg}$  is the source-gate voltage and  $\eta$  is the subthreshold slope. Dividing (2.2) with (2.1) will result in:

$$\frac{I_d}{I_c} = \frac{I_{d0}}{I_S} \tag{2.3}$$

It can be noticed that equation (2.3) provides a dependency between circuit controlled currents ( $I_d$ ,  $I_c$ ) and device dependent currents ( $I_{d0}$ ,  $I_s$ ). Hence, to reduce the loss in drain current ( $I_d$ ), the ratio (2.3) should be maximized.

In the literature  $I_S$  and  $I_{d0}$  [35], [40] are defined as:

$$I_S = A_E \cdot J_S \tag{2.4}$$

and

$$I_{d0} = A_M \cdot 2\eta \mu_p C_{OX} V_T^2 \exp\left(\frac{V_{thp}}{\eta V_T}\right) = A_M \cdot I_M$$

(2.5)

where  $A_E$  is the junction area,  $J_E$  is the current density,  $\mu_p$  is the mobility,  $C_{OX}$  is the oxide capacitance value,  $V_{thp}$  is the threshold voltage, and  $A_M$  is the area of the MOSFET.

By substituting (2.4), (2.5) in (2.3), the ratio between drain current ( $I_d$ ) and collector current ( $I_c$ ) will be expressed in terms of the geometry and process parameters of the transistor.

$$\frac{I_d}{I_c} = \underbrace{\frac{I_M}{J_S}}_{Process} \cdot \underbrace{\frac{A_M}{A_E}}_{Geometry}$$

(2.6)

Hence, to maximize (2.6) a transistor layout will be an important design parameter for a designer.

Considering a PMOS transistor with a aspect ratio of  $n \cdot W/L$  where n is the number of fingers, W and L is the width and length of the basic cell. The junction area  $(A_E)$  and the MOSFET area  $(A_M)$  can be easily

Figure 2.3. Example of a layout with number of fingers (n) equal to 4.

calculated from a layout shown in Fig. 2.3 as:

$$A_E = n \cdot W \cdot L_d \tag{2.7}$$

$$A_M = n \cdot \frac{W}{L}$$

By substituting (2.7) in (2.6) will result in:

$$\frac{I_d}{I_c} = \frac{I_M}{J_S} \cdot \frac{1}{L \cdot L_d} \tag{2.8}$$

It can be concluded from equation (2.8) that a selection of smaller gate and diffusion lengths will reduce leakage due to parasitic vertical BJT.

### 2.2.2 Transistor sizing and operating frequency

It has been shown in equation (2.8) that the dimension of the transistor is an important factor to improve its performance. This performance is generally measured in terms of the conversion efficiency. Typically, in a rectifier circuit a MOSFET is either used as a switch or implemented in diodeconnected configuration. In these implementations the ON-resistance  $R_{ON}$  of MOSFET is an important design parameter. The  $R_{ON}$  of a PMOS

transistor is given by:

$$R_{ON} = \frac{1}{\mu_p C_{OX} \left(\frac{W}{L}\right) \left(V_{sg} - |V_{thp}|\right)}$$

(2.9)

where  $V_{sg}$  is the source-gate voltage.

It can be observed in (2.9) that the aspect ratio (W/L) is the primary design parameter. The increasing aspect ratio will lead to reduced ON-resistance and thus, will produce a larger saturation current. However, it will also increase the reverse current and parasitic capacitances. A higher reverse current will cause a reduction in the conversion efficiency of the rectifier [34]; while the presence of a large parasitic capacitance will proportionately result in lower bandwidth [41].

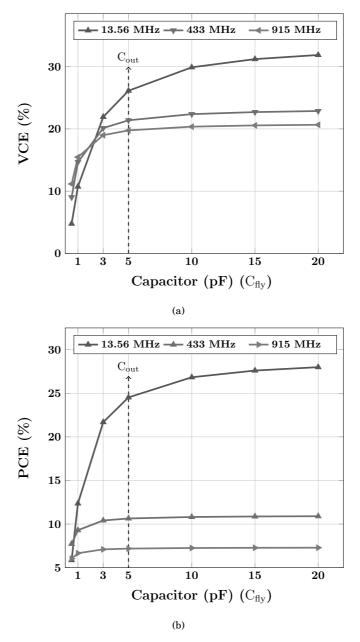

To further explain the impact of transistor sizes, the transient simulations have been performed on a diode-connected PMOS transistor (Fig. 2.2). These results are obtained by using the RF signal of peak amplitude 0.5 V with different RFID frequencies ( $f_{RF}$ ) for a resistive-capacitive load of value 30 k $\Omega$  || 5 pF. The simulations are performed using a standard 0.18  $\mu$ m CMOS technology by using the Spectre simulator in the Cadence environment. The performance of the rectifier is evaluated in terms of Voltage Conversion Efficiency (VCE) and Power Conversion Efficiency (PCE).

The VCE parameter is defined as:

$$VCE(\%) = 100 \cdot \left(\frac{V_{out}}{V_{out_{ideal}}}\right)$$

(2.10)

where  $V_{out}$  is the rectified output DC voltage and  $V_{out_{ideal}}$  is its ideal value. The PCE parameter is given by:

$$PCE(\%) = 100 \cdot \left(\frac{P_{out}}{P_{in}}\right) = 100 \cdot \left(\frac{R_{in}}{R_L}\right) \cdot \left(\frac{V_{out}}{V_{in}}\right)^2$$

(2.11)

where  $P_{out}$  is the output power across resistive load and  $P_{in}$  is the input RF power to the rectifier,  $R_{in}$  is the input resistance value of the rectifier,  $R_L$  is the load resistance value and  $V_{in}$  is the peak input RF voltage amplitude.

The values of VCE (%) and PCE (%) parameters obtained after the transient simulations are shown in Fig. 2.4.

The following conclusions can be drawn from Fig. 2.4:

The curves exhibit dependence over the transistor width. At low input RF frequency (13.56 MHz) the variation follows higher degree polynomial. But, with an increase in input RF frequency the functional dependency converges towards a parabolic nature.

**Figure 2.4.** Simulation results of (a) VCE and (b) PCE with varying transistor width at different input RF frequencies for minimum length transistor.

- 2. It is possible to comment that for lower input RF frequency (<13.56 MHz) values, the power conversion efficiency will approach towards the ideal value of 40.6%.

- 3. The conversion efficiencies have been reduced with an increase in input signal frequency and transistor size. This phenomenon is due to an increase in reverse current and higher parasitic capacitances.

- 4. One of the most important observations is the presence of the maxima of VCE and PCE curves at different values of transistor width. This behavior will introduce a trade-off for the designer between the selection of either maximum PCE or maximum VCE in a rectifier implementation.

## 2.2.3 Sizing of load, fly capacitors and number of stages

In practice, a single-stage rectifier is insufficient to produce an output voltage ( $\geq 2V_{th}$ ) value required to drive any typical CMOS circuit arrangement from a received small signal amplitude ( $\lesssim V_{th}$ ).

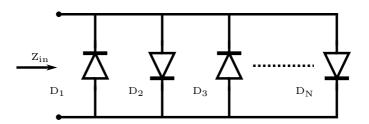

Hence, to obtain a higher voltage level a cascade arrangement is made by using a series of rectifiers. This stacked configuration, which is often known as the Voltage Multiplier (VM) circuit, is shown in Fig. 2.5.

Figure 2.5. Voltage multiplier circuit.

It can be seen that, the arrangement is powered up by using an RF source of peak amplitude value  $V_m$ . Each stage of the voltage multiplier is a voltage doubler. Thus, the first stage (I-stage) is generating the output DC voltage equal to twice the peak RF amplitude value  $(2V_m)$ . This progression will continue theoretically with the increase in the number of stages (N); thus, the maximum output DC voltage value of  $2NV_m$  will be obtained after the Nth stage. Generally, diodes  $(D_1...D_N)$  in this architecture are implemented by using the Schottky diode [42], [43–46], or a diode-connected MOSFET [47–52]

It can be observed in Fig. 2.5 that the schematic is constituted by the three circuit components: (i) the load capacitor per stage  $(C_{out})$ , (ii) the fly capacitor  $(C_{fly})$ , and (iii) the diode (D). The criteria for the sizing of the diode was discussed in the previous subsection. The following subsections present the design considerations for load capacitor per stage  $(C_{out})$ , fly capacitor  $C_{fly}$  and the number of stages (N) used in the VM circuit implementation.

# 2.2.3.1 The value of load capacitor/stage

The value of the load capacitance per stage ( $C_{out}$ ) is a function of the permissible peak-to-peak ripple voltage ( $\Delta V_{ripple}$ ) amplitude, which is given as [53]:

$$\Delta V_{ripple} = \frac{I_{load}}{C_{out} f_{RF}}$$

(2.12)

where  $I_{load}$  is the target load current and  $f_{RF}$  is the received RF frequency. It can be seen in (2.12) that the increase in  $C_{out}$  will result in less ripple voltage from the load current droop.

## 2.2.3.2 The value of fly capacitor

Figure 2.6. Single-stage rectifier.

A schematic of the single-stage rectifier is shown in Fig. 2.6, which is a half-wave voltage doubler (I-stage, Fig. 2.5). In the figure, D1 and D2 are the diode-connected MOSFET,  $C_{fly}$  and  $C_{out}$  are the fly and output capacitors respectively,  $R_L$  is the resistive load and an RF source  $V_{RF} = V_m \sin(\omega t)$  is used.

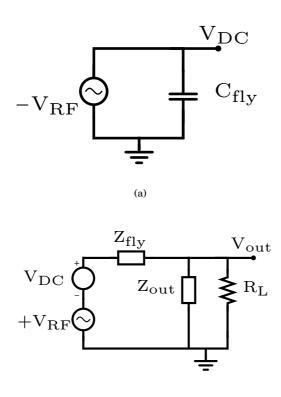

It should be noted that the analysis has been done by considering ideal components in the schematics. When the negative half cycle of the RF sinusoidal input waveform will appear, the diode  $D_1$  will become forward biased. Thus, the fly capacitor  $C_{fly}$  will enter into charging phase. As a result a DC voltage  $V_{DC}$  will appear across it (Fig. 2.7(a)). Ideally, this

Figure 2.7. (a) Charging phase and (b) Discharging phase of single-stage rectifier.

value is equal to the peak value of the input RF signal  $V_m$ . Since there is no path for capacitor  $C_{fly}$  to discharge into, it remains fully charged.

(b)

During the positive half cycle, the diode  $D_1$  is reverse biased blocking the discharging of  $C_{fly}$ . The voltage  $V_{DC}$  which was developed across  $C_{fly}$  will appear in series with the voltage supply and hence provide a DC shift to the input RF signal. Meanwhile, the diode  $D_2$  will become forward biased and start charging up the capacitor  $C_{out}$ . As a result, a voltage  $V_{out}$  will appear across the capacitor  $C_{out}$  which will ideally equal to twice the peak voltage value  $(V_m)$  of the input signal. The equivalent circuit for this phase is shown in Fig. 2.7(b).

Referring to Fig. 2.7(b), consider a voltage source of value  $(V_{RF} + V_{DC})$  with a source impedance of value  $Z_{fly}$  connected to the load impedance of value  $Z_{out}||R_L$ .

According to classical power transfer theorem:

$$Z_{fly} = Z_{out} || R_L \implies C_{fly} = \frac{1}{\omega R_L} + C_{out}$$

(2.13)

It can be observed from 2.13 that the  $C_{\rm fly} > C_{\rm out}$ . Similarly, higher load resistor values (i.e.  $R_L \to \infty$ ) will result in  $C_{fly} = C_{out}$ . Hence, increasing  $C_{out}$  will result in a large  $C_{fly}$  and thus, unnecessarily increases both circuit size and input capacitance.

Fig. 2.8 shows the transient simulation results of maximum VCE and maximum PCE approaches for a single-stage of the VM circuit (Fig. 2.6).

**Figure 2.8.** Simulation results of (a) VCE and (b) PCE with varying coupling capacitor size at different input RF frequencies.

The size of a diode-connected MOSFETs ( $D_1$  and  $D_2$ ) is selected by using the performance plots shown in Fig. 2.4. The load capacitor ( $C_{out}$ ) value is selected as 5 pF and the current requirement has been emulated in terms of a load resistor ( $R_L$ ) of value 30 K $\Omega$ . The RF signal of peak amplitude 0.5 V is used in transient simulations. Simulation results verify equation (2.13) that the fly capacitor  $C_{fly}$  should be equal to or greater than the load capacitor per stage  $C_{out}$  to achieve high conversion efficiency.

# 2.2.3.3 Number of stages

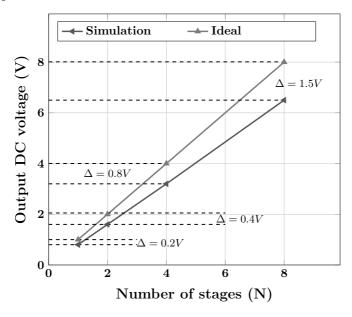

Theoretically with any increase in the number of stages (N), the  $V_{out}$  to  $V_{in}$  ratio will also increase (Fig. 2.5). In practical implementations, however an increase in the number of stages, increases the losses and hence the output DC voltage  $V_{out}$  decreases.

Fig. 2.9 shows the comparison between the ideal output DC voltage with the simulated output DC voltage obtained from the voltage multiplier with an increasing number of stages (N). The simulation environment parameters used to obtain the results are listed in Table. 2.1. It can

Figure 2.9. Simulated output DC voltage with increasing number of stages (N).

be observed from Fig. 2.9 that with an increase in the number of stages, the losses in the voltage multiplier increase correspondingly. Referring to Fig. 2.9 a empirical formula to estimate the output DC voltage can be written as:

$$V_{estimate} = 2NV_m - \chi * N \tag{2.14}$$

| S.No. | Parameter                             | Value                              |

|-------|---------------------------------------|------------------------------------|

| 1     | Architecture                          | Fig. 2.5                           |

| 2     | Peak RF amplitude                     | 500 mV                             |

| 3     | RF frequency                          | 433 MHz                            |

| 4     | Number of Stages                      | 1,2,4,8                            |

| 5     | Simulation Type                       | Harmonic Balance with 20 Harmonics |

| 6     | Transistor                            | PMOS                               |

| 7     | Size                                  | 4*10 μm/0.18 μm                    |

| 8     | Fly capacitor $C_{fly}$ size          | 5 pF                               |

| 9     | Capacitor/output stage $C_{out}$ size | 5 pF                               |

| 10    | Load                                  | Capacitive only                    |

Table 2.1. Simulation environment used to evaluate voltage multiplier.

where N is the number of stages,  $V_m$  is the peak input RF amplitude and  $\chi$  is the voltage loss (0.2 V) in a single-stage.

Figure 2.10. AC equivalent schematic of N-stage voltage multiplier circuit.

When a voltage multiplier is employed with a resistive load, then its performance becomes affected by both the number of stages (N) and the resistive load value  $(R_L)$ . To understand this phenomenon, consider the AC equivalent circuit of the voltage multiplier of Fig. 2.5 as drawn in Fig. 2.10.

In practice, the input power  $(P_{in})$  is the sum of the output power  $(P_{out})$  and the power lost in each branch  $(P_{loss})$ . In this case (Fig. 2.5), only half of the diodes  $(\frac{N}{2})$  will act during the conversion. Therefore:

$$P_{in} = P_{out} + \frac{N}{2} \cdot P_{loss} \tag{2.15}$$

where  $P_{in}$  is given by:

$$P_{in} = \frac{V_m^2}{2R_{in}} {2.16}$$

and  $R_{in}$  is the input resistance of the voltage multiplier. By using (2.16) in (2.15) will result in:

$$R_{in} = \frac{V_m^2}{2\left(P_{out} + \frac{N}{2}P_{loss}\right)} \tag{2.17}$$

Considering that the diodes are lossless, then  $P_{out} = P_{in}$  and  $V_{out}$  will be equal to  $2NV_m$  hence:

$$\frac{V_m^2}{2R_{in}} = \frac{V_{out}^2}{R_{out}} \implies R_{in} = \frac{R_L}{2N^2}$$

(2.18)

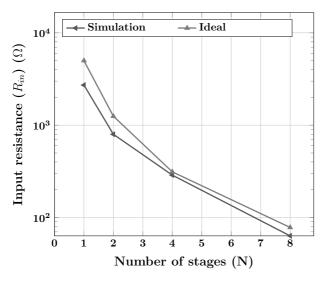

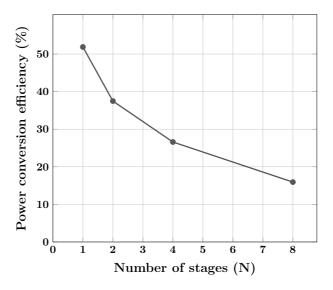

The equation (2.18) shows that with an increase in the number of stages (N), the input resistance  $(R_{in})$  of the rectifier will decrease for a given value of load resistance  $(R_L)$ . The simulated values of  $R_{in}$  with N are shown in Fig. 2.11. The simulation environment parameters used are listed in Table. 2.1 with the exception of the load condition. Here a resistive load of value 10 K $\Omega$  was selected to perform these simulations.

Figure 2.11. Variation of input resistance with increasing number of stages (N).

It can be verified from Fig. 2.11 that the simulated values of  $R_{in}$  follows equation (2.18). Thus, it can be concluded that the trend in the reduction of the input resistance with the number of stages will increase the input power (2.16), which will inherently decrease the power conversion efficiency (2.11). The simulation-based result obtained for the power conversion efficiency by using a resistive load of 10 K $\Omega$  is shown in Fig. 2.12 which verifies this conclusion.

**Figure 2.12.** Variation of power conversion efficiency with increasing number of stages (N).

### 2.2.4 Matching network

Ideally, the matching network (Fig.1.1.) is a lossless network placed between the RF source (antenna) and the load (rectifier). The purpose of a matching network is to provide a narrow-band impedance and voltage transformation between the two ports. It is one of the contributing factors to the overall efficiency of an energy harvesting unit as shown in equation (2.19):

$$\eta_{ehu} = \eta_{antenna} \cdot \eta_{match} \cdot \eta_{rect} \tag{2.19}$$

where  $\eta_{antenna}$  is the efficiency of the antenna,  $\eta_{match}$  is the efficiency of the matching network, and  $\eta_{rect}$  is the efficiency of the rectifier. In practice, the signal strength of a received RF signal is small, therefore along with the power-matching, a voltage gain-boosting is also mandatory for the matching network [45], [54], [55].

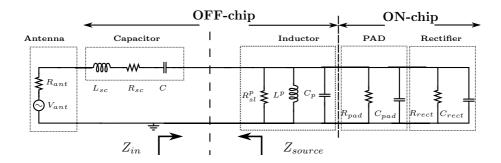

Fig. 2.13 shows a simplified schematic of an OFF-chip power-matching and gain-boosting network used in this work. The component models for the capacitor and inductor are selected from [56] and [57] respectively. The I/O pad and the rectifier are modeled as parallel RC circuits  $(R_{pad}||C_{pad})$  and  $(R_{rect}||C_{rect})$  respectively. In the following analysis, for simplicity, it has been considered that the series elements contribute in source impedance  $(Z_{source})$  while parallel elements form the input impedance  $(Z_{in})$ . Thus, in the schematic the source impedance  $(Z_s)$  is

Figure 2.13. Matching network.

given by:

$$Z_s = (R_{ant} + R_{sc}) + j\left(\omega L_{sc} - \frac{1}{\omega C}\right)$$

(2.20)

where  $R_{ant}$  is the antenna resistance,  $L_{sc}$  and  $R_{sc}$  are the residual inductance and the resistance in the lead wires and electrodes, and C is an actual capacitor. Rewriting (2.20) as:

$$Y_{s} = \frac{1}{(R_{ant} + R_{sc})} \left( \frac{1 - jQ_{c} \left( \left[ \frac{\omega}{\omega_{srfc}} \right]^{2} - 1 \right)}{1 + Q_{c}^{2} \left[ \frac{\omega}{\omega_{srfc}} \right]^{2}} \right)$$

(2.21)

where,  $\omega_{srfc}$  is the self-resonating frequency of capacitor (C) with parasitic inductance  $L_{sc}$  [58] and [59],  $Q_c$  is the quality factor of capacitor C, and it is defined as  $\frac{1}{\omega C(R_{ant}+R_{sc})}$ .

Similarly, input admittance  $(Y_{in})$  is given by:

$$Y_{in} = \frac{1}{R_{eq}} + j\left(\omega C_{eq} - \frac{1}{\omega L_p}\right)$$

(2.22)

In (2.22),  $R_{eq}$  and  $C_{eq}$  are the total equivalent shunt resistance and capacitance respectively, given as follows:

$$R_{eq} = R_{sl}^p ||R_{pad}||R_{rect}$$

$$C_{eq} = C_p + C_{pad} + C_{rect}$$

(2.23)

Solving (2.22) will result in:

$$Y_{in} = \frac{1}{R_{eq}} + j \left( \frac{\left[\frac{\omega}{\omega_{srfl}}\right]^2 - 1}{\omega L_p} \right)$$

(2.24)

where  $\omega_{srfl}$  is the self-resonating frequency of an inductor  $(L_p)$  with a shunt capacitance  $(C_{eq})$ .

It is known from fundamental theory on matching networks that to transfer maximum power the following condition holds:

$$Y_{in} = Y_s^* \tag{2.25}$$

Hence, by comparing the real parts it will result in:

$$\frac{R_{eq}}{R_{ant} + R_{sc}} = 1 + \left(1 - \left[\frac{\omega}{\omega_{srfc}}\right]^2\right) Q_c^2 \tag{2.26}$$

Assuming  $\omega_{srfc}>>\omega$  , than (2.26) is simplified to:

$$\frac{R_{eq}}{R_{ant} + R_{sc}} = 1 + Q_c^2 (2.27)$$

Similarly, by comparing the imaginary parts will result in:

$$\frac{\psi_c}{\omega L_p} = \frac{\psi_l}{\omega C (R_{ant} + R_{sc})^2} \cdot \left(\frac{1}{1 + (\psi_l Q_c)^2}\right)$$

(2.28)

where

$$\psi_c = \left(1 - \left[\frac{\omega}{\omega_{srfc}}\right]^2\right)$$

$$\psi_l = \left(\left[\frac{\omega}{\omega_{srfl}}\right]^2 - 1\right)$$

Typically  $\psi_l Q_c >> 1$  hence (2.28) can be written as:

$$\omega^2 = \omega_{LC}^2 \cdot \psi_l \cdot \psi_c \tag{2.29}$$

where

$$\omega_{LC} = \frac{1}{\sqrt{L_p C}}$$

Assuming that  $\omega_{srfc},\ \omega_{srfl}>>\omega$  then (2.29) is simplified to:

$$\omega = \omega_{LC} \tag{2.30}$$

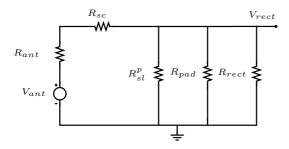

The power distribution equivalent circuit of Fig. 2.13 is shown in Fig. 2.14.

Thus, the power conversion efficiency  $\eta$  will be:

$$\eta(\%) = 100 \cdot \frac{P_{rect}}{P_{in}} = 100 \cdot \left(\frac{R_{ant}}{R_{rect}}\right) \left(\frac{R_{eq}}{R_{ant} + R_{sc} + R_{eq}}\right)^2 \tag{2.31}$$

where  $P_{in}$  is the power obtained from the RF source and  $P_{rect}$  is the power delivered to the rectifier. It is evident from (2.31) that the equivalent resistance  $R_{eq}$  (2.21) influences the power efficiency of the system. As a result, the efficiency is always less than 100%.

Figure 2.14. Power distribution network.

It has been pointed out earlier that a voltage gain is also demanded from the matching network. Therefore consider a matching network with a voltage gain of  $A_v$ : the voltage appearing across the rectifier will be  $V_{rect} = A_v V_{ant}$ . Thus, the power delivered to the matching network will become:

$$P_L = \frac{V_{rect}^2}{R_{sc} + R_{eq}} = \frac{(A_v V_{ant})^2}{R_{sc} + R_{eq}}$$

(2.32)

It is well known that if the matching is ideal, then the maximum power delivered is given by:

$$P_{eq}^{max} = \frac{V_{ant}^2}{4R_{ant}} \tag{2.33}$$

By equating (2.32) and (2.33) it is obtained that:

$$A_v = \frac{1}{2} \sqrt{\left(\frac{R_{sc} + R_{eq}}{R_{ant}}\right)} \tag{2.34}$$

The conclusions from the above analyses are as follows:

- 1. The self-resonant frequency of the discrete components must be greater than the matching frequency.

- 2. The voltage gain boosting is proportional to the quality factor of the discrete components from (2.27) and (2.34).

- The I/O pads also affect the power conversion and gain boosting ability of the matching network.

- 4. Estimation of the parasitic resistances is necessary before designing the rectifier to make  $R_{rect}$  dominant on parasitic resistances (2.21).

## 2.2.5 Figure of merits

The performance evaluation of the rectifier is done by using the following figure of merits.

### 2.2.5.1 Voltage conversion efficiency

The RF-to-DC converter (or rectifier) is an AC/DC converter and the level of output DC voltage will determine the capability to drive the load such as a transmitter or a receiver. The voltage conversion efficiency (VCE) is measured to determine the level of output DC voltage for a given peak RF amplitude. The VCE is defined as:

$$VCE(\%) = 100 \cdot \frac{V_{dc}}{V_{dc ideal}} = \frac{V_{dc}}{A_v \cdot 2N \cdot V_{in}}$$

(2.35)

where  $V_{dc}$  is the output DC voltage from the rectifier,  $V_{dc_{ideal}}$  is the ideal DC voltage from the rectifier, N is the number of stages of the voltage multiplier,  $V_{in}$  is the peak signal amplitude of the input RF signal and  $A_v$  is the voltage gain of the gain-boosting matching network.

### 2.2.5.2 Power Conversion Efficiency

The power conversion efficiency (PCE) is the ratio of the DC output power ( $P_{dc}$ ) to the power delivered to the rectifier ( $P_{in}$ ) given as follows:

$$PCE(\%) = 100 \cdot \frac{P_{dc}}{P_{in}} = 100 \cdot \left(\frac{V_{DC}^2}{R_L}\right) \cdot \left(\frac{1}{P_{source}(1 - |\Gamma|^2)}\right)$$

(2.36)

where  $V_{DC}$  is the rectified output DC voltage across the load resistor  $(R_L)$ ,  $P_{in}$  is the actual power delivered to the rectifier, which is calculated in terms of  $P_{source}$  and  $\Gamma$ . In (2.36)  $P_{source}$  is the power available from the RF generator and  $|\Gamma|$  is the reflection coefficient which is defined as,

$$|\Gamma|^2 = \begin{cases} |S_{11}|^2 & \text{for a single input rectifier} \\ |S_{dd11}|^2 + |S_{cd11}|^2 & \text{for a differential input rectifier} \end{cases}$$

(2.37)

Here  $S_{11}$  is the single-ended reflection coefficient with  $S_{dd11}$  and  $S_{cd11}$  being the mixed mode differential-to-differential and differential-to-common mode reflection coefficients respectively, which are measured by using the Voltage Network Analyzer (VNA).

#### 2.3 Proposed RF-to-DC converters

In RF energy harvesting applications the industrial, scientific and medical (ISM) bands at 433 MHz and 902- 928 MHz are most conveniently

used due to lower path loss with respect to the higher RF bands. Additionally, in this frequency range, a high 4W Effective Isotropic Radiated Power (EIRP) is sanctioned by the regulatory bodies [60–62] thus, allowing long node distance from the power transmitting module.

It is well known from the standard Friis free-space propagation equation [63] that the power available to the antenna is inversely proportional to  $d^2$  where d is the link distance. Thus, the input power delivered to the RF energy harvesting module will be low in order to maximize the link length. As a result the micro-watt ( $\mu$ W) power budget is estimated for remote RF-powered devices.

The minimum incident power level that is required by a rectifier is a function of the threshold voltage of rectifying devices, *i.e.* diodes and transistors. In the published literature, two methods have been adopted to decrease the threshold voltage. In the first method, devices like a Schottky diode [64], Zero- $V_{th}$  diode [65] or Native transistors [51] are used. It is well mentioned in the literature that these devices require additional fabrication steps. Hence, they do not provide cost-effective mass production. As a solution to this issue, a circuit-based method is a preferred choice. In this method, rectifiers are implemented by using standard CMOS transistors. Later, additional circuit arrangements are used to reduce the threshold voltage of these transistors [66], [67], [68].

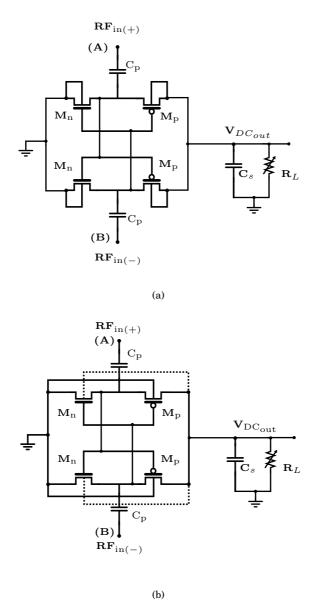

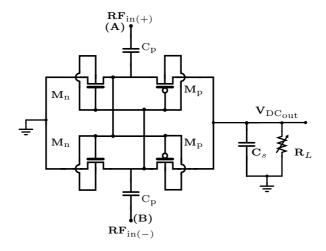

In this research, three approaches are proposed to improve the performance of the rectifier. The aim of these methods is to reduce the threshold voltage influence in the rectifier. In the first method, the involvement of the body terminal in designing the rectifier is proposed. While in the second method, the performance improvement of the rectifier was demonstrated by the use of the auxiliary circuits. The proposed third approach was targeted to the designing of voltage multiplier circuits. In this method, a signaling scheme has been proposed to improve the conversion performance of the voltage multiplier circuits.

A brief discussion of the proposed three methods follows here after.

### 2.3.1 Design based on controlling body voltage

The essential feature for achieving high rectification efficiency in a rectifier is the low threshold voltage (Vth). One obvious solution would be is the use of a Zero- $V_{th}$  [52] MOSFET. Unfortunately, however it suffers from reverse conduction loss. In addition, it will require an additional fabrication cost, which is not cost effective for mass production. In this work,

the aim has been rather to develop the circuit-based methods, which are capable of altering the threshold voltage of the switching transistors of the rectifiers.

In literature, the dependency of the threshold voltage  $(V_{thn})$  with the source-body voltage  $(V_{SB})$  is given in (2.38) for the NMOS transistor [35].

$$V_{thn} = V_{thn0} + \gamma \cdot \sqrt{2 \cdot \phi_F + V_{SB}} - \sqrt{2 \cdot \phi_F}$$

(2.38)

where,  $V_{thn0}$  is the zero-bias threshold voltage,  $\gamma$  is the body-effect coefficient,  $\phi_F$  is the flat-band voltage and  $V_{SB}$  is the source-body voltage.

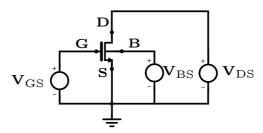

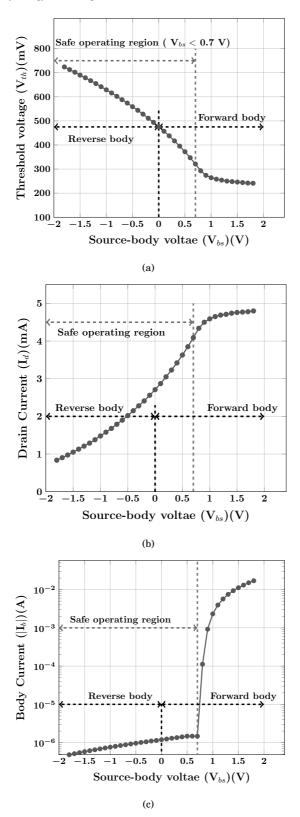

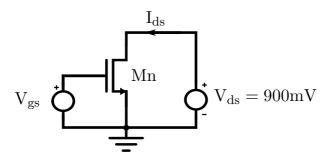

It can be noticed from equation (2.38) that the body-source voltage  $V_{SB}$  is the only circuit-based parameter. In order to understand the effect of the body-source voltage, the DC simulations were performed on the circuit arrangement shown in Fig. 2.15. The characterization of the transistor was done by varying the body-source voltage  $V_{SB}$  in the range of -1.8 V to 1.8 V. In these simulations, the gate-source voltage  $V_{GS}$  and the drain-source voltage  $V_{DS}$  were fixed at 900 mV and 1.8 V respectively. The aspect ratio of the NMOS transistor used for the simulation was 20  $\mu$ m/0.18  $\mu$ m. The simulated characterization plots for the threshold voltage, the

Figure 2.15. Circuit setup used for NMOS transistor characterization.

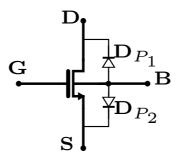

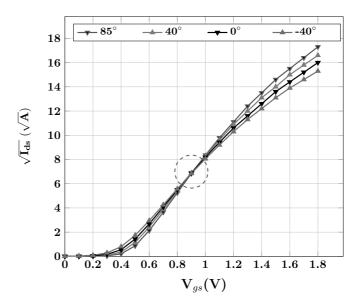

drain and the body currents are shown in Fig. 2.16(a), Fig. 2.16(b) and Fig. 2.16(c) respectively. The plots are divided into two regions depending on the source-body voltage. The region between  $1.8 \text{ V} \leq V_{SB} < 0 \text{ V}$  is termed as the 'Reverse body', while the region between  $0 \text{ V} < V_{SB} \leq 1.8 \text{ V}$  is termed as the 'Forward body' as shown in Fig.2.16. The  $V_{SB} = 0 \text{ V}$  corresponds to the zero-body biased condition where the threshold voltage of the transistor is equal to  $V_{thn0}$  (2.38). Conventionally,  $V_{SB} = 0 \text{ V}$ , i.e. the body terminal tied to the source terminal is preferred during CMOS-based rectifier circuit implementations [69]. This arrangement enables the threshold voltage value of the switching transistors to be set at  $V_{thn0}$ . It is observed from the simulation plots that by increasing the source-body

**Figure 2.16.** NMOS transistor characterization plots obtained by varying source-body voltage.

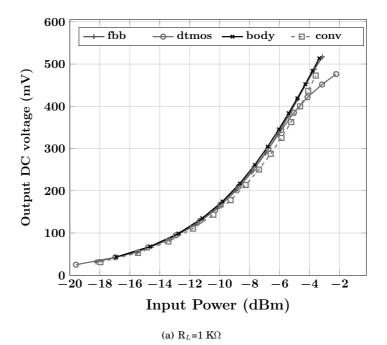

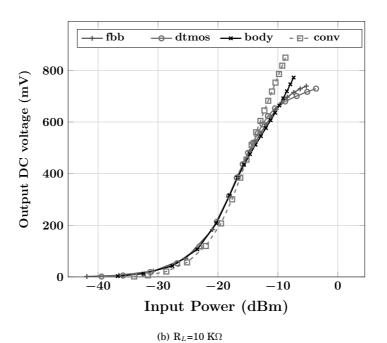

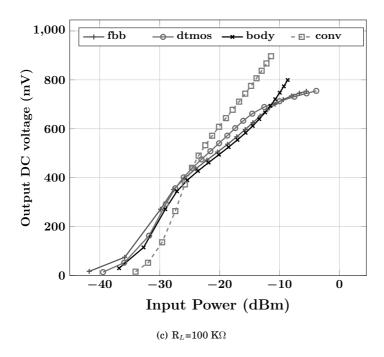

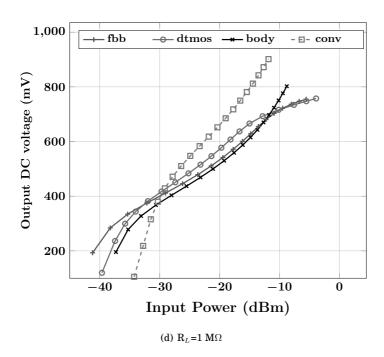

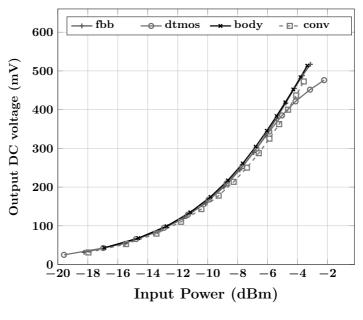

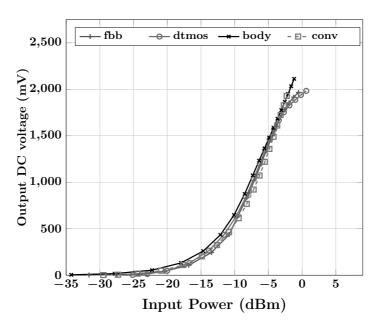

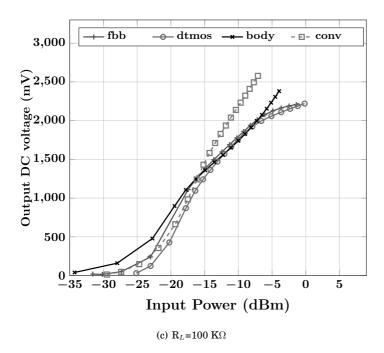

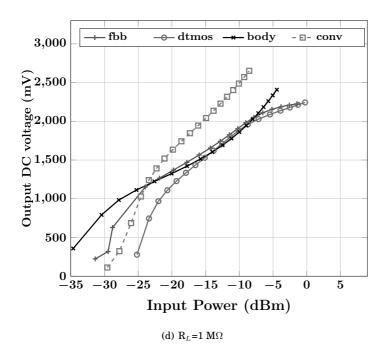

voltage the threshold voltage decreases. This variation is approximately  $\pm 50\%$  from  $V_{thn0}$ , thus it verified the dependence of the threshold voltage  $(V_{thn0})$  on the source-body voltage  $(V_{SB})$  as mentioned in equation (2.38).