This is an electronic reprint of the original article.

This reprint may differ from the original in pagination and typographic detail.

Author(s): Saira, Olli-Pentti & Meschke, Matthias & Giazotto, Francesco & Savin,

Alexander M. & Möttönen, Mikko & Pekola, Jukka

Title: Heat Transistor: Demonstration of Gate-Controlled Electronic

Refrigeration

Year: 2007

Version: Final published version

## Please cite the original version:

Saira, Olli-Pentti & Meschke, Matthias & Giazotto, Francesco & Savin, Alexander M. &

Möttönen, Mikko & Pekola, Jukka. 2007. Heat Transistor: Demonstration of

Gate-Controlled Electronic Refrigeration. Physical Review Letters. Volume 99, Issue 2.

027203/1-4. ISSN 0031-9007 (printed). DOI: 10.1103/physrevlett.99.027203.

Rights: © 2007 American Physical Society (APS). http://www.aps.org/

All material supplied via Aaltodoc is protected by copyright and other intellectual property rights, and duplication or sale of all or part of any of the repository collections is not permitted, except that material may be duplicated by you for your research use or educational purposes in electronic or print form. You must obtain permission for any other use. Electronic or print copies may not be offered, whether for sale or otherwise to anyone who is not an authorised user.

## Heat Transistor: Demonstration of Gate-Controlled Electronic Refrigeration

Olli-Pentti Saira, Matthias Meschke, Francesco Giazotto, Alexander M. Savin, Mikko Möttönen, Mikko P. Pekola Mikko P. Pekola

<sup>1</sup>Low Temperature Laboratory, Helsinki University of Technology, P.O. Box 3500, 02015 TKK, Finland

<sup>2</sup>NEST CNR-INFM and Scuola Normale Superiore, I-56126 Pisa, Italy

<sup>3</sup>Laboratory of Physics, Helsinki University of Technology, P.O. Box 4100, 02015 TKK, Finland

(Received 15 February 2007; published 9 July 2007)

We present experiments on a superconductor—normal-metal electron refrigerator in a regime where single-electron charging effects are significant. The system functions as a *heat transistor*; i.e., the heat flux out from the normal-metal island can be controlled with a gate voltage. A theoretical model developed within the framework of single-electron tunneling provides a full quantitative agreement with the experiment. This work serves as the first experimental observation of Coulombic control of heat transfer and, in particular, of refrigeration in a mesoscopic system.

DOI: 10.1103/PhysRevLett.99.027203 PACS numbers: 85.80.Fi, 73.23.Hk, 85.25.-j

In conventional transistors such as a field-effect or single-electron transistor [1], the electric current or voltage is controlled by a gate. More recently, a different kind of working principle was demonstrated in mesoscopic structures: the electron transport can also be controlled by manipulating the quasiparticle temperature, i.e., the energy distribution of charge carriers [2,3]. In these experiments, such manipulation resulted typically in an increase of electronic temperature. In subsequent experiments, the supercurrent of a superconductor-normal-metal-superconductor (SNS) Josephson junction was controlled not only by heating but also by cooling the electrons in the active region [4]. A typical electron refrigerator consists of a SNS system with two insulating barriers (I) defining a SINIS tunnel structure [5]. Biasing the device with a voltage of approximately twice the superconducting energy gap results in extraction of heat from the N island, and hence a drop in its temperature. Ultrasmall structures operated at low temperatures display pronounced charging effects which may profoundly affect the heat transport dynamics in mesoscopic systems.

In this Letter, we investigate a SINIS structure with very small tunnel junctions which behaves as a gate-controlled single-electron refrigerator. In such a system, we demonstrate experimentally gate modulation of the *heat flux* by more than a factor of 3. Our experimental findings are successfully explained through a model which associates the thermal current with single-electron tunneling [6]. This structure provides an ideal framework for the investigation of the interplay between charging effects and heat transport at mesoscopic scale.

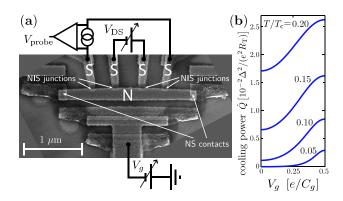

Figure 1(a) shows the measured heat transistor with a sketch of the measurement setup. The core of the sample consists of an N island, tunnel coupled to four superconducting leads, and a gate electrode with capacitive coupling to the island. Like in an ordinary single-electron transistor, the charging energy penalty for tunneling electrons can be modulated by the gate voltage. As we shall

show in the following, in the heat transistor under suitable bias conditions, Coulomb blockade allows the modulation of both the electric current and the heat flux. For a direct verification of the Coulomb blockade effect, we also fabricated and measured a reference sample with the same geometry and parameters, except for large capacitor pads (area  $5\times 10^4~\mu m^2$ ) attached to the island with normal-metal–superconductor (NS) contacts, thus suppressing the charging energy but ideally maintaining the thermal isolation of the N island. In the actual heat transistor we preserved only small superconducting protrusions instead of the large pads in order to maintain the same topology with a minimal effect on the charging energy. The samples were fabricated with electron beam lithography and three-

FIG. 1 (color online). (a) Scanning electron micrograph of the heat transistor, showing also the measurement setup. In the middle, the normal-metal (Cu) island subjected to cooling. Four superconducting probes (Al) with Al-Ox tunnel junctions can be seen above, and truncated capacitor plates (Al) with direct NS contacts on the left and right. (b) Theoretical heat flow from the N island at the optimal bias point at different temperatures as a function of the gate voltage. T denotes the common temperature of the island electrons and quasiparticles in the superconductor, and  $T_c = \Delta/(1.764k_B)$  is the superconducting critical temperature.

angle evaporation on an oxidized silicon wafer. The normal-metal island consists of a copper block with lateral dimensions 180 nm  $\times$  2300 nm and thickness 20  $\pm$  3 nm. The superconductor metal was aluminum, and the Al-Ox tunnel junctions had an approximate area  $120 \times 40 \text{ nm}^2$ . In the heat transistor, the two inner junctions with 110 k $\Omega$ resistances were used as a voltage-biased cooler pair. Consistent with the transistor terminology, we denote the bias voltage over the cooler junctions  $V_{DS}$ . The outer junctions with resistances of approximately 150 k $\Omega$  each were current biased at picoampere level, enabling accurate thermometry of the island electrons by exploiting the temperature sensitivity of a NIS junction I-V curve in the 100–500 mK range. As only the dc properties of the device were relevant, all signal lines to the sample stage were lowpass filtered.

Figure 1(b) illustrates the expected performance of the transistor, displaying the modulation of heat flow (Q) with gate voltage  $(V_{o})$  at different operating temperatures. The electric and thermal transport properties of a Coulombblockaded SINIS structure can be derived through the theory of single-electron tunneling assuming no exchange of energy due to environmental fluctuations. Cotunneling does not play a significant role due to large junction resistances compared to the resistance quantum  $h/e^2 \simeq$ 26 k $\Omega$ . To obtain a complete model of the experimental setup, we consider a normal-metal island with four tunnel junctions to superconducting leads numbered 1-4 with junction resistances and capacitances given by  $R_i$  and  $C_i$ , respectively, and the electric potential of each lead denoted by  $V_i$ . The gate electrode is coupled to the island with capacitance  $C_g$ . The total capacitance of the normal-metal island reads  $C_{\Sigma} = C_g + \sum_{i=0}^4 C_i$ , where  $C_0$  denotes the self-capacitance of the island. Let us denote the total excess charge on the island by q = -ne. The electrostatic energy of the system can be written in a form where the charging energy is expressed as  $E_{\rm ch}=E_c(n+n_g)^2$ . Here  $E_c\equiv e^2/(2C_\Sigma)$  and  $n_g=V_gC_g/e$  is the gate charge. The change in energy for an electron tunneling to ( + ) or from (-) the island through junction i reads [7]

$$E_n^{i,\pm} = \pm 2E_c(n + n_g \pm 1/2) \pm e(V_i - \phi),$$

(1)

where  $\phi = (1/C_{\Sigma})\sum_{j=1}^4 C_j V_j$  is the offset to the island potential from the bias voltages. The  $\phi$  term can be interpreted also as a shift to the gate position  $n_g$ , and hence we neglect it in the following analysis where we consider the range of gate modulation of electric and heat current at fixed bias points. The standard expressions for the tunneling rate  $\Gamma$  and average heat flux  $\dot{Q}$  as a function of the change in energy  $E_n^{i,\pm}$  for each tunneling event are identical to those given in Ref. [6]. The charge number distribution  $p_n$  is determined from the steady-state master equation [7]. The shape and position of the charge number distribution are crucial in describing the device properties in the

Coulomb blockade regime  $k_B T_N \lesssim E_c$ , where  $T_N$  is the N island electron temperature.

For an analytic investigation of Coulomb blockade effects on heat transport near the optimal bias point where the maximum cooling power is achieved, we neglect the small probe current, and assume the two cooling junctions to have the same resistance  $R_T$ . Furthermore, we consider the extreme cases  $n_g = 0$  (closed gate) and  $n_g = -1/2$ (open gate) in the regime  $E_c/(k_BT_N) \gg 1$ , so that the charge number distribution  $p_n$  is symmetric and narrow. Neglecting the population of the excited charge states, a symmetrically biased Coulomb-blockaded SINIS with an open gate behaves as a regular SINIS whose electric and heat currents have been scaled by 1/2: At charge state n =0 (n = 1), an electron can enter (leave) the island through the junction biased at  $\mp V_{\rm DS}/2$  with no increase in charging energy, while tunneling through the other junction is effectively blocked due to a charging energy penalty of  $2E_c$ . We can therefore apply the known results valid in the absence of charging effects [8], namely, that the optimal cooler bias voltage is  $V_{\rm DS}^{\rm opt} \simeq 2(\Delta - 0.66k_BT_{\rm N})/e$ , and the maximum cooling power for the heat transistor reads

$$\dot{Q}_{\text{open}}^{\text{opt}} \simeq 0.59 \frac{\Delta^{1/2} (k_B T_{\text{N}})^{3/2}}{e^2 R_T}.$$

(2)

With a closed gate, all tunneling events are affected by Coulomb blockade and the cooling power is minimized. The leading term of the cooling power corresponds to tunneling events occurring at the n=0 state, and employing similar approximations as in Eq. (2), the cooling power accounting for the charging energy penalty of magnitude  $E_c$  can be written

$$\dot{Q}_{\text{closed}}^{\text{opt}} \simeq 1.3 \frac{E_c}{k_B T_N} \exp\left(-\frac{E_c}{k_B T_N}\right) \frac{\Delta^{1/2} (k_B T_N)^{3/2}}{e^2 R_T}.$$

(3)

In the analysis of the measured data, all quantities were evaluated numerically. Comparison with the numerical computations shows that the above approximative formulas are accurate to within 10% when  $E_c/(k_BT_{\rm N}) \gtrsim 2.5$ .

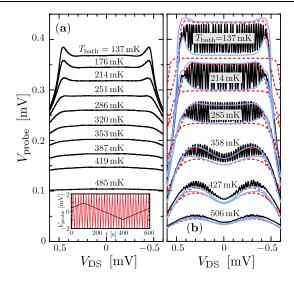

In the experiment, we recorded the voltage over the current-biased probe junctions as the gate voltage was swept at a rate of one gate modulation period per 4 s, while the voltage over the cooler junctions was swept over a range of  $-1, \ldots, 1$  mV with a 600 s period. The sample parameters  $\Delta = 230 \ \mu V$  and  $C_{\Sigma} = 1.5 \ \text{fF}$  were determined from a fit to the measured I-V characteristics and the gate modulation amplitude of  $V_{\text{probe}}$ , respectively. We charted a number of bath temperatures ranging from 50 to 560 mK. In Fig. 2, sweeps over cooler bias  $(V_{DS})$  are shown at selected bath temperatures for both the reference sample with vanishing charging energy [Fig. 2(a)] and for the heat transistor [Fig. 2(b)]. Due to very slow sweeping rate compared to the electron-phonon relaxation time [9], each data point represents the system in thermal steady state. In the reference sample which behaves as an ordinary

FIG. 2 (color online). Measured probe voltage as a function of the drain-source bias voltage for (a) the reference sample with negligibly small charging energy and (b) the heat transistor at different bath temperatures. Inset: gate voltage [gray (red) line] during one period of  $V_{\rm DS}$  sweep (black line). Electron charge corresponds to a gate voltage of 1.6 mV. Panel (b) thus illustrates the range of gate modulation at different bias voltages, whereas there was no observable gate modulation in the reference sample. Superimposed on panel (b) are theoretical curves for the two extremal gate positions. The solid blue curves are calculated assuming an electron-phonon heat load given by Eq. (4) with the experimentally determined value  $\Sigma = 2.3 \times 10^9~{\rm W\,K^{-5}\,m^{-3}}$ , and the dashed red curves given for reference show the expected behavior where the electron temperature is fixed at the bath temperature ( $T_{\rm bath}$ ) over the full bias range.

SINIS cooler (i.e., with negligible charging energy), there is a one-to-one correspondence between the island electron temperature and the measured probe voltage for a fixed current bias. The characteristics of the heat transistor are drastically different, as seen in Fig. 2(b). In order to perform accurate thermometry on the heat transistor sample with varying  $V_g$  and  $V_{\rm DS}$ , one needs to determine the temperature  $T_{\rm N}$  by using a complete model which takes into account the exact charge number distribution.

Steady state is reached at a temperature where the cooling power is matched to the external heat load. The dominating source of heat load into the island electrons is electron-phonon heat flux  $(\dot{Q}_{ep})$ , which can be modeled by [10]

$$\dot{Q}_{ep} = \Sigma \mathcal{V} (T_0^5 - T_N^5),$$

(4)

where  $\Sigma$  is a material parameter,  $\mathcal{V}$  is the volume of N island, and  $T_0$  is the phonon temperature. Using bulk values from Ref. [11] for the Kapitza resistance between the island and substrate phonons, we estimate that the change in the temperature of the island phonons due to electron cooling is less than 10% of the observed drop in

the electron temperature. The true Kapitza resistance for thin films is most likely even lower as one can assume a common phonon system for the film and substrate [12], and thus we neglect lattice cooling unlike in Ref. [13], and use  $T_0 = T_{\rm bath}$ . In our modeling, we further ignore heating of the superconducting reservoirs due to hot quasiparticles extracted from the island, whose effect is supposedly weak due to relatively high junction resistances and moderate cooling power. Consequently, we take  $T_S = T_{\rm bath}$ . On the other hand, at sub-100 mK bath temperatures, electrons are overheated due to noise via the electrical leads, and accurate comparison with the theoretical model becomes difficult.

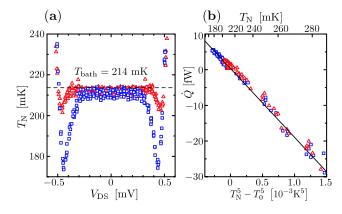

In analysis of the measurement data, we concentrate on characterizing the cooling properties of the device at the extremal gate positions. These have to be identified as the local minima and maxima of either  $V_{\text{probe}}$  or the drainsource current as the gate voltage is swept. In Fig. 3(a), we present the electron temperatures corresponding to open and closed gate positions derived from the experimental data at bath temperature 214 mK. Similar results were obtained at other bath temperatures as well, but only in the range 170-250 mK we have both accurate thermometry and significant temperature reduction. The temperature  $T_{\rm N}$  was evaluated numerically for each data point using the experimentally determined sample parameters, the observed values of  $V_{\text{probe}}$  and  $V_{\text{DS}}$ , and the set value of probe current, which was 3.2 pA in this measurement. The electron temperatures obtained from the model for small bias voltages  $V_{\rm DS}$ , for which no cooling is expected, differ less than 10 mK from the bath temperature for both open and closed gate, demonstrating a good agreement between the experiment and theory, and supporting the reliability of this method of thermometry. With open gate, the transistor should function almost like a regular SINIS cooler, and

FIG. 3 (color online). (a) Electron temperatures extracted from the data acquired at bath temperature 214 mK with the gate open  $(n_g = 1/2)$ , blue squares) and closed  $(n_g = 0)$ , red triangles). (b) The theoretical cooling power versus  $T_{\rm N}^5 - T_0^5$  for each data point of the left panel, and a linear fit to it. According to Eq. (4), the slope is given by  $-\Sigma \mathcal{V}$ .

cooling peaks are indeed found at bias voltages  $V_{\rm DS} \simeq \pm 2\Delta/e$ . Increasing the bias voltage over  $\sim 2\Delta/e$  brings the device rapidly into the Ohmic heating regime, which is observed as a sharp rise of the electron temperature. For the closed gate configuration, the cooling peaks are weaker and occur at a slightly larger bias voltage, as tunneling electrons have to overcome both the Coulomb and the superconducting gap.

A quantitative analysis of the observed temperature drops is presented in Fig. 3(b). The plot shows the numerically calculated total cooling power versus  $T_N^5 - T_0^5$ , using the  $T_{\rm N}$  values from Fig. 3(a). According to the heat balance equation  $\dot{Q} = \dot{Q}_{ep}$ , the dependence should be linear with the slope given by  $-\Sigma \mathcal{V}$ . Agreement with the model is excellent throughout the whole data range from cooling  $(\dot{Q} > 0)$  to resistive heating  $(\dot{Q} < 0)$ . Through a linear fit we obtain  $\Sigma = (2.3 \pm 0.3) \times 10^9 \text{ W K}^{-5} \text{ m}^{-3}$ , the main source of uncertainty being the effective island volume. The literature value  $\Sigma = 2 \times 10^9 \text{ W K}^{-5} \text{ m}^{-3}$  [14] is within the experimental error. Estimates for  $\Sigma$  obtained from data at other bath temperatures are consistent with the above result, demonstrating the stability of the method. Furthermore, the observed on/off ratio of cooling power upon gate variation at the optimal bias point was as large as 3.2.

Figure 2(b) displays the  $V_{\text{probe}}$  curves (solid blue lines) calculated using a model where the island electron temperature varies according to the experimentally determined electron-phonon coupling strength  $\Sigma = 2.3 \times$  $10^9$  W K<sup>-5</sup> m<sup>-3</sup>. For reference, we also show curves with the electron temperature fixed to  $T_{\text{bath}}$  (dashed red lines), demonstrating which of the observed features should be attributed to changes in temperature. All the qualitative features of  $V_{\text{probe}}$  are reproduced, including the gentle bumps appearing at higher temperatures, which are not indicative of cooling but of changes in the width of the charge number distribution. These features can be observed in  $V_{\text{probe}}$  when  $E_c \lesssim k_B T_{\text{N}}$ ,  $T_{\text{N}} \approx T_{\text{S}}$  and when  $V_{\text{probe}}$  is small. As expected, significant variations between the cooled  $T_N$  and  $T_N \equiv T_{\text{bath}}$  curves appear only at low temperatures and with open gate, whereas with closed gate, features due to change in the island electron temperature remain always small. The small difference between the theoretical curves for constant and variable  $T_{\rm N}$  near  $V_{\rm DS} =$ 0 at the lowest temperatures is due to approximately 0.5 fW cooling power from the probe junctions. The measured amplitude of gate modulation at  $T_{\text{bath}} = 137 \text{ mK}$  is slightly smaller than expected. The difference can be attributed to heat load from electrical noise, to which the measurement is increasingly sensitive at low temperatures. At high bath temperatures, the measured amplitude of the gate modulation and the shape of the envelope curves are as expected, although there are unexplained offsets of the order of  $10~\mu V$  in the measured data at different bath temperatures as compared to theoretical curves. We have also verified that the theoretical model reproduces accurately the measured cooler junction I-V curves at all bath temperatures (data not shown), which further validates the accuracy of the model and the fitted sample parameters.

In conclusion, we have investigated experimentally and theoretically the thermal dc properties of a Coulombblockaded SINIS structure. We have demonstrated that the system operates as a mesoscopic heat transistor; i.e., it shows a gate modulation of heat flux. In particular, cooling power modulation as large as 70% of its maximum has been observed. The agreement between the experiment and a theory based on Coulomb-blockaded single-electron tunneling is compelling. Furthermore, we have also proved that a NIS probe can be used as a sensitive thermometer even in the presence of charging effects, provided that the charge number distribution on the normal metal is carefully modeled. Our results indicate that the influence of this distribution is particularly pronounced when  $V_{\rm DS} \gtrsim V_{\rm probe}$ . Finally, our work might provide guidelines for the investigation of heat transport at the mesoscopic scale, e.g., to either avoid or make use of the effects arising from singleelectron charging in electronic refrigeration.

We acknowledge the NanoSciERA project "NanoFridge" of the EU and the Academy of Finland for financial support.

- [1] T. A. Fulton and G. J. Dolan, Phys. Rev. Lett. **59**, 109 (1987).

- [2] A. F. Morpurgo, T. M. Klapwijk, and B. J. van Wees, Appl. Phys. Lett. 72, 966 (1998).

- [3] J.J.A. Baselmans et al., Nature (London) 397, 43 (1999).

- [4] A. M. Savin et al., Appl. Phys. Lett. 84, 4179 (2004).

- [5] M. M. Leivo, J. P. Pekola, and D. V. Averin, Appl. Phys. Lett. 68, 1996 (1996).

- [6] J. P. Pekola, F. Giazotto, and O.-P. Saira, Phys. Rev. Lett. 98, 037201 (2007).

- [7] D. Averin and K. Likharev, Mesoscopic Phenomena In Solids (Elsevier Science, Amsterdam, 1991), Chap. 6, pp. 173–271.

- [8] D. V. Anghel and J. P. Pekola, J. Low Temp. Phys. 123, 197 (2001).

- [9] L. J. Taskinen et al., Phys. Status Solidi C 1, 2856 (2004).

- [10] M. L. Roukes et al., Phys. Rev. Lett. 55, 422 (1985).

- [11] E. T. Swartz and R. O. Pohl, Rev. Mod. Phys. **61**, 605 (1989).

- [12] S. I. Dorozhkin, F. Lell, and W. Schoepe, Solid State Commun. 60, 245 (1986).

- [13] S. Rajauria et al., arXiv:cond-mat/0612045.

- [14] F. Giazotto et al., Rev. Mod. Phys. 78, 217 (2006).