## Olaitan Olabode

# Dopamine oxidation readout sensor interface in $65\ \mathrm{nm}\ \mathrm{CMOS}$ technology

### **School of Electrical Engineering**

Thesis submitted for examination for the degree of Master of Science in Technology.

Espo<br/>o09.03.2015

Thesis supervisor:

Prof. Kari Halonen

Thesis advisor:

D.Sc. (Tech.) Marko Kosunen

## AALTO UNIVERSITY SCHOOL OF ELECTRICAL ENGINEERING

Author: Olaitan Olabode

Title: Dopamine oxidation readout sensor interface in 65 nm CMOS technology

Date: 09.03.2015 Language: English Number of pages:13+95

Department of Micro- and Nanosciences

Professorship: Micro and Nanoelectronic circuit design Code: S-87

Supervisor: Prof. Kari Halonen

Advisor: D.Sc. (Tech.) Marko Kosunen

Sensing and monitoring of neural activities within the central nervous system has become a fast-growing area of research due to the need to understand more about how neurons communicate. Several neurological disorders such as Parkinson's disease, Schizophrenia, Alzeihmers and Epilepsy have been reported to be associated with imbalance in the concentration of neurotransmitters such as glutamate and dopamine [1] - [5]. Hence, this thesis proposes a solution for the measurement of dopamine concentration in the brain during neural communication.

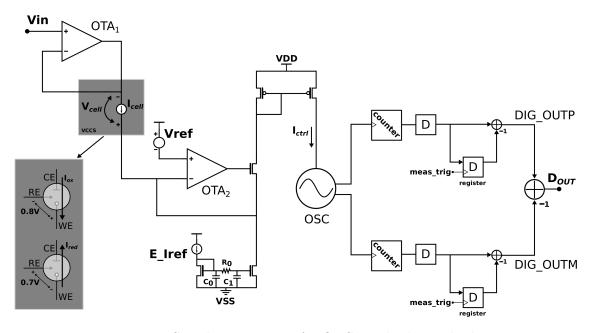

The proposed design of the dopamine oxidation readout sensor interface is based on a mixed-signal front-end architecture for minimizing noise and high resolution of detected current signals. The analog front-end is designed for acquisition and amplification of current signals resulting from oxidation and reduction at the biosensor electrodes in the brain. The digital signal processing (DSP) block is used for discretization of detected dopamine oxidation and reduction current signals that can be further processed by an external system.

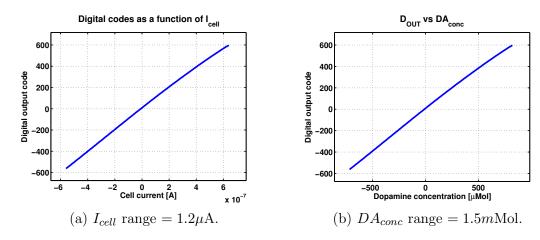

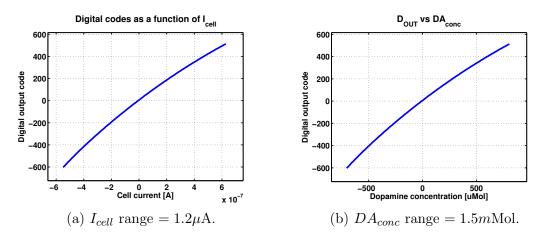

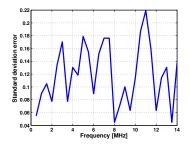

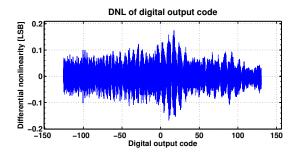

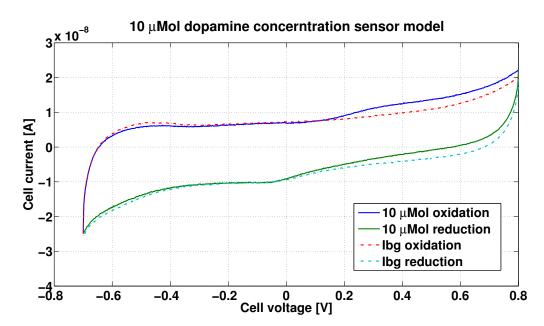

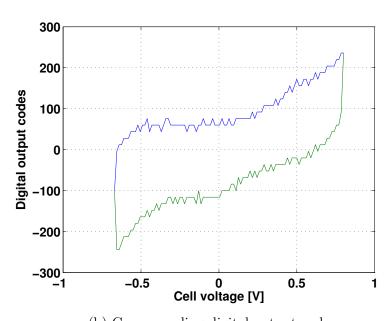

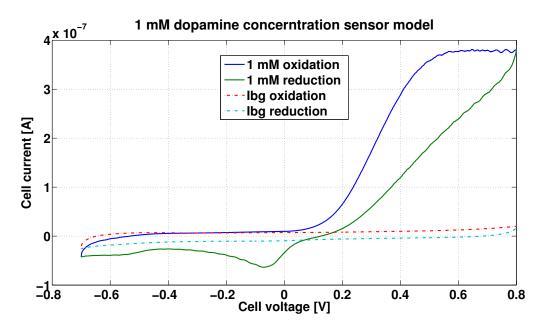

The results from the simulation of the proposed design show that the readout circuit has a current resolution of 100 pA and can detect minimum dopamine concentration of 10  $\mu$ Mol based on measured data from novel diamond-like carbon electrodes [6]. Higher dopamine concentration can be detected from the sensor interface due to its support for a wide current range of 1.2  $\mu$ A( $\pm$ 600 nA). The digital code representation of the detected dopamine has a resolution of 14.3-bits with RMS conversion error of 0.18 LSB which results in an SNR of 88 dB at full current range input. However, the attained ENOB is 8-bits due to the effect of non-linearity in the oscillator based ADC. Nonetheless, the achieved resolution of the readout circuit provides good sensitivity of released dopamine in the brain which is useful for further understanding of neurotransmitters and fostering research into improved treatments of related neurodegenerative diseases.

Keywords: Dopamine, Neurotransmitter, Neurochemical, Neurosensing, Biosensor, Biomedical, Bioelectronics, Sensor interfaces, Integrated potentiostat, CMOS readout circuits, Mixed signal front-end Tekijä: Olaitan Olabode

Työn nimi: Dopamiinin hapettumisen lukija-anturirajapinta 65 nm CMOS

teknologialla

Päivämäärä: 09.03.2015 Kieli: Englanti Sivumäärä:13+95

Mikro- ja nanotekniikan laitos

Professuuri: Piiritekniikka Koodi: S-87

Valvoja: Prof. Kari Halonen

Ohjaaja: TkT Marko Kosunen

Keskushermoston aktiivisuuden havainnointi ja tarkkailu on muodostunut tärkeäksi tutkimusalaksi, sillä tarve ymmärtää neuronien viestintää on kasvanut. Monien hermostollisten sairauksien kuten Parkinsonin taudin, skitsofrenian, Alzheimerin taudin ja epilepsian on huomattu aiheuttavan muutoksia välittäjäaineiden, kuten glutamaatin ja dopamiinin, pitoisuuksissa [1] - [5]. Aiheeseen liittyen tässä työssä esitetään ratkaisu dopamiinipitoisuuden mittaamiseksi aivoista.

Esitetty dopamiinipitoisuuden lukijapiiri perustuu sekamuotoiseen etupäärakenteeseen, jolla saavutetaan matala kohinataso ja hyvä tarkkuus signaalien ilmaisemisessa. Suunniteltu analoginen etupää kykenee lukemaan ja vahvistamaan dopamiinipitoisuuden muutosten aiheuttamia virran muutoksia aivoihin asennetuista elektrodeista. Digitaalisen signaalinkäsittelyn avulla voidaan havaita dopamiinin hapettumis-ja pelkistymisvirtasignaalit, ja välittää ne edelleen ulkoisen järjestelmän muokattavaksi.

Simulaatiotulokset osoittavat, että suunniteltu piiri saavuttaa 100 pA virran erottelukyvyn. Simuloinnin perustuessa hiilipohjaisiin dopamiinielektrodeihin piiri voi havaita 10  $\mu$ Mol dopamiinipitoisuuden [6]. Myös suurempia dopamiinipitoisuuksia voidaan havaita, sillä etupäärajapinta tukee 1.2  $\mu$ A( $\pm$ 600 nA) virtaaluetta. Digitaalinen esitysmuoto tukee 14.3 bitin esitystarkkuutta 0.18 bitin RMS virheellä saavuttaen 88 dB dynaamisen virta-alueen. Saavutettu ENOB (tehollinen bittimäärä) on kuitenkin 8 bittiä oskillaattoripohjaisen ADC:n (analogiadigitaalimuuntimen) epälineaarisuuden takia. Saavutettu tarkkuus tuottaa hyvän herkkyyden dopamiinin havaitsemiseksi ja hyödyttää siten välittäjäainetutkimusta ja uusien hoitomuotojen kehittämistä hermostollisiin sairauksiin.

Avainsanat: Dopamiini, Välittäjäaine, Neurokemia, Aivomittaus, Bioanturi, Biolääketiede, Bioelektroniikka, Anturirajapinnat, Sulautettu potentiostaatti, CMOS lukijapiirit, Sekamuotoinen signallietupää

# **Preface**

The work presented in this thesis was carried out in the Electronic Circuit Design Laboratory of the Department of Micro- and Nanosciences at Aalto University. The proposed design was implemented and fabricated on-chip as part of a collaborative project called Neurosens, between other departments in School of Science and Electrical Engineering, funded by Aalto University. As a result, measurement data from the sensor electrodes were provided by the Department of Electronics.

I would like to express my gratitude to my thesis supervisor, Professor Kari Halonen and instructor Marko Kosunen for their guidance and support during the design and implementation of this thesis. I especially appreciate their commitment and devotion to the success of this thesis and for the privilege to implement this thesis as a microchip. I am very thankful to my instructor Marko Kosunen for detailed and clear instructions, valuable advice and suggestions, insights into more complicated concepts and practical contributions during the completion of this thesis.

I would also like to extend my gratitude to Professor Tomi Laurila from the Department of Electronics for providing valuable insights and background into the research area of neurochemical sensing especially in the early stages of the design. I also wish to thank Tommi Palomäki for clarifications during the measurement of the dopamine sensor and for extracting the data that is used in the verification of the proposed design of the dopamine oxidation readout sensor interface (DORSI).

I am also thankful to all personnel and researchers at the laboratory for providing a warm and efficient learning environment. I wish to thank Olli Viitala, Tero Tikka, Enrico Roverato and Professor Jussi Ryynänen for their technical support and help throughout the implementation of this thesis and especially towards the submission of the readout chip to fabrication. In addition, I warmly thank my fellow colleagues Jakub Groniz and Shailesh Chouhan with whom I shared a room, for interesting discussions and exchange of ideas. Thanks to Antti Ontronen for cross-checking the Finnish translation of the Abstract.

Finally, I am deeply grateful to my parents for their relentless efforts in teaching and showing me the importance of diligence and hard-work. I am extremely thankful to my family, friends and in-laws for their moral and spiritual support throughout this entire process of studying abroad. I also wish to remember my beloved nephew Ayodeji Taiwo who passed away during the completion of this work. I know you were watching over me and you would forever be missed. Last and most definitely not the least, I would like to express my heartfelt appreciation to my husband Muyiwa Olabode for his patience and tremendous love. This work would not have been accomplished without your support. To God Almighty for the breath of life and for sustaining me through this phase of my life, I am eternally grateful.

# Contents

| $\mathbf{A}$ | bstract                                                                                      | ii                  |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------|---------------------|--|--|--|--|

| $\mathbf{A}$ | bstract (in Finnish)                                                                         | iii                 |  |  |  |  |

| Preface      |                                                                                              |                     |  |  |  |  |

| C            | ontents                                                                                      | $\mathbf{v}$        |  |  |  |  |

| Sy           | ymbols and abbreviations                                                                     | vii                 |  |  |  |  |

| 1            | Introduction                                                                                 | 1                   |  |  |  |  |

| 2            | Background  2.1 Neurotransmitters                                                            | 6<br>10<br>15<br>16 |  |  |  |  |

| 3            | Proposed design of the Dopamine Oxidation  Readout Sensor Interface  3.1 Design requirements | 28<br>35            |  |  |  |  |

| 4            | Results  4.1 Performance of the analog front-end                                             |                     |  |  |  |  |

| 5            | Conclusion                                                                                   | <b>76</b>           |  |  |  |  |

| $\mathbf{R}$ | eferences                                                                                    | <b>7</b> 8          |  |  |  |  |

| $\mathbf{A}$ | ppendix A                                                                                    | 86                  |  |  |  |  |

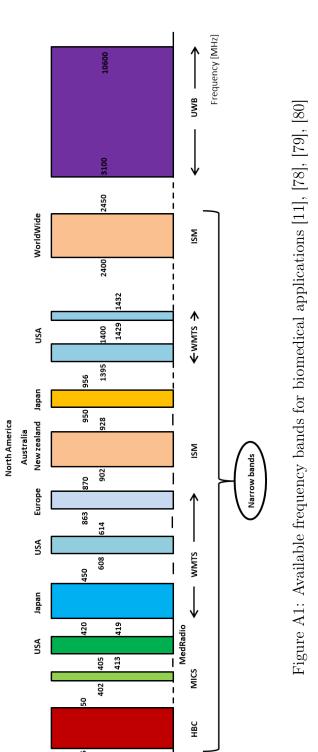

| $\mathbf{A}$ | Available frequency bands for biomedical applications                                        | 86                  |  |  |  |  |

| Aj           | ppen | dix B   |                                                             | 87 |

|--------------|------|---------|-------------------------------------------------------------|----|

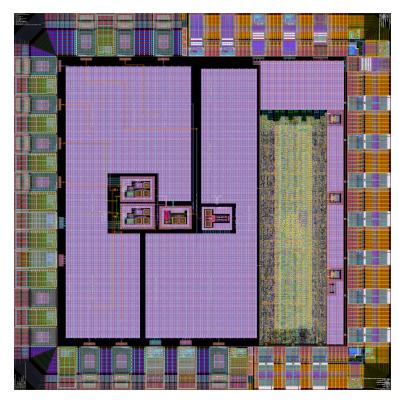

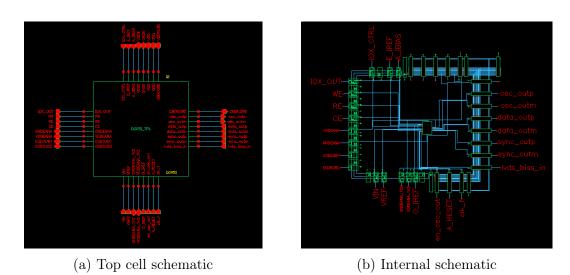

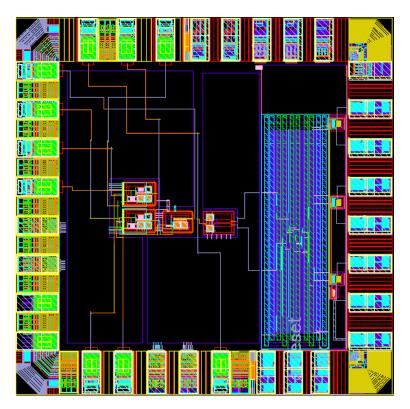

| В            | Lay  | out im  | plementation                                                | 87 |

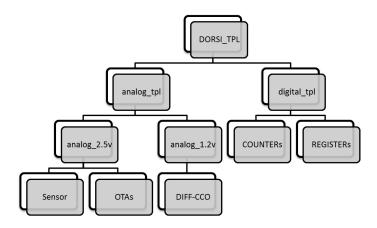

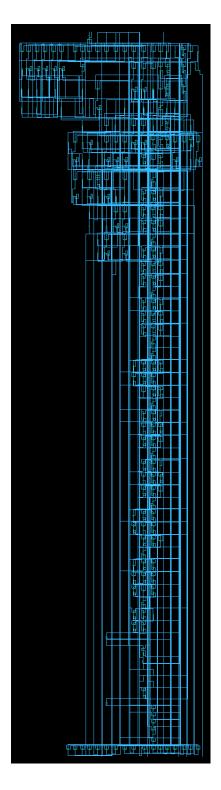

|              | В.1  | Hierard | chical diagram of DORSI layout                              | 87 |

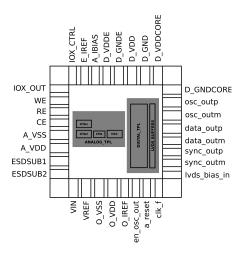

|              | B.2  |         | lan diagram of DORSI layout                                 |    |

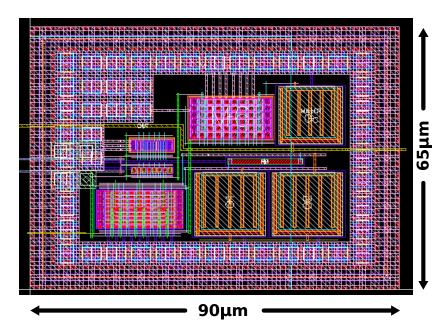

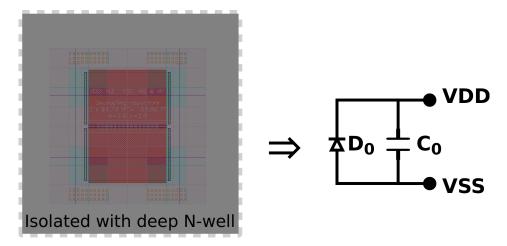

|              | B.3  |         | implementation of the OTA                                   |    |

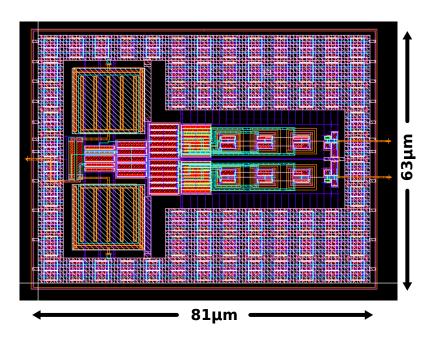

|              | B.4  | Layout  | implementation of the differential oscillator               | 88 |

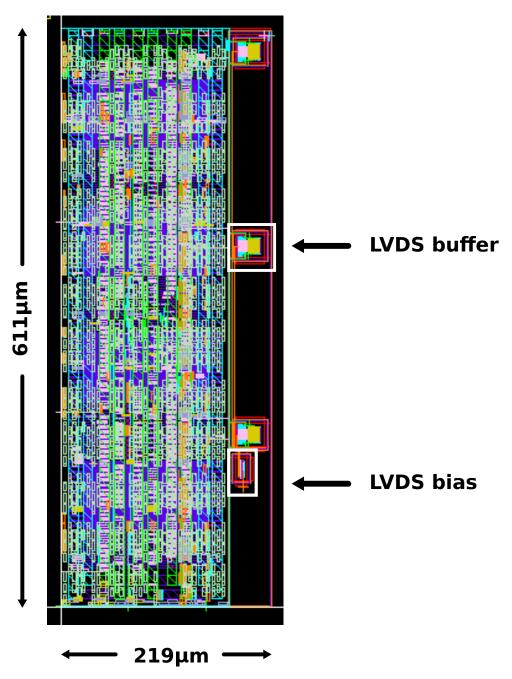

|              | B.5  | Layout  | implementation of the digital block                         | 89 |

|              |      | B.5.1   | Equivalent schematic of the digital block                   | 90 |

|              | B.6  |         | implementation of DORSI                                     |    |

|              |      | B.6.1   | Equivalent schematic of DORSI layout                        | 91 |

|              |      |         | Layout and equivalent schematic of supply mesh cell         |    |

|              |      |         | Layout implementation of DORSI without supply mesh          |    |

| Aj           | ppen | dix C   |                                                             | 93 |

| $\mathbf{C}$ | Der  | ivation | s related to sensitivity of the oscillator to variations in | Ĺ  |

|              |      | er sup  | _                                                           | 93 |

# Symbols and abbreviations

#### Abbreviations

A/D Analog-to-digital

AC Alternating current

ADC Analog-to-digital converter

AE Auxiliary electrode

AFE Analog front-end

AP Action potential

BW Signal bandwidth

CA Chronoamperometry

CCO Current controlled oscillator

CCS Carboxylated carbonaceous spheres

CE Counter electrode

CFM Carbon-fibre microelectrodes

CIC Cascaded integrated comb

CM Current mirror

CMOS Complementary metal-oxide-semiconductor

CMRR Common-mode rejection ratio

CNS Central nervous system

CNT Carbon nanotubes

CT Computed tomography

CV Cyclic voltammetry

D/A Digital-to-analog

DA Dopamine

DAC Digital-to-analog converter

dB Decibels

DBS Deep brain stimulation

DC Direct current

DEM Dynamic element matching

DIFF Differential

DIFF-CCO Differential current controlled oscillator

DLC Diamond-like carbon

DNL Differential nonlinearity

DNW Deep N-well

DOQ Dopamine-ortho-quinone

DORSI Dopamine oxidation readout sensor interface

DPV Differential pulse voltammetry

DR Dynamic range

DSP Digital signal processing

ECG Electrocardiography

EEG Electroencephalography

EIS Electrochemical impedance spectroscopy

ENOB Effective number of bits

FFT Fast Fourier Transform

FOM Figure of merit

FSCV Fast-scan cyclic voltammetry

GBW Gain bandwidth

GC Gray code counter

GCE Glassy carbon electrode

HBC Human Body Communication

I-F Current-to-Frequency

I/O Input/Output

IA Current acquisition

IC Integrated circuits

ICMR Input common mode range

ID Current discretization

INL Integral nonlinearity

ISM Industrial, Scientific and Medical

LNA Low-noise amplifier

LO Local oscillator

LOD Limit of detection

LSB Least significant bit

LVDS Low voltage differential signalling

MedRadio Medical Device Radiocommunications Service

MICS Medical Implant Communication Service

MOS Metal-oxide-semiconductor

MRI Magnetic resonance imaging

MWCNT Multi-walled carbon nanotubes

N-OTA Miller NMOS-based OTA

OPAMP Operational amplifier

OSC Oscillator

OTA Operational transconductance amplifier

P2S Parallel-to-serial

PBS Phosphate buffered saline

PET Positron emission tomography

PM Phase margin

POW Power management module

PSD Power spectral density

PSRR Power supply rejection ratio

RE Reference electrode

REDOX Reduction and oxidation

RF Radio frequency

RFIC Radio frequency integrated circuits

RFID Radio frequency identification

RHP Right-half-plane

RMS Root mean square

S2P Serial-to-parallel

SAR Specific absorption rate

SE Single-ended

SE-CCO Single-ended current controlled oscillator

SEM Scanning electron microscopy

SFDR Spurious-free dynamic range

SIE Sensor interface electronics

SNDR Signal-to-noise and distortion ratio

SNR Signal-to-noise ratio

SPECT Single photon emission computerized tomography

SQNR Signal-to-quantization noise ratio

SR Slew-rate

SWCNT Single-walled carbon nanotubes

UWB Ultra Wide Band

VCCS Voltage controlled current source

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

WE Working electrode

WMTS Wireless Medical Telemetry Service

**Symbols**

$A_e$  Cross-sectional area of an electrode

$C_e$  Double-layer capacitance of an electrode

$I_{bq}$  Background current

$I_{cell}$  Induced electrochemical cell current

$I_{ox}$  Oxidation current

$I_{redox}$  Induced redox current

$I_{red}$  Reduction current

$O_{Iref}$  Bias current of the oscillator

$O_{bulk}$  Oxidized form an electroactive specie

$R_{bulk}$  Reduced form an electroactive specie

$R_{WE}$  Working electrode charge-transfer resistance

$V_{cell}$  Electrochemical cell voltage

$V_{CE}$  Voltage over the counter electrode

$V_{redox}$  Applied redox voltage

$\beta$  MOS device transconductance parameter

$\Delta C$  Conversion error

$\Delta F_{osc}$  Change or deviation in oscillation frequency

$\Delta I_{min}$  Minimum change in current

$\Delta T$  Total timing error

$\Delta V_{dd}$  Change or deviation in supply voltage

$\epsilon_t(t)$  Timing error or jitter

γ MOS device bulk threshold parameter

$\kappa$  Boltzmann's constant

$\mu_0$  Effective charge carrier mobility of a MOS device

$\phi_F$  MOS device strong inversion surface potential

$\tau_d$  Propagation time delay of each inverter stage

C Conversion codes

$C_c$  Miller compensation capacitor

$C_L$  Output load capacitance of the OTA

$C_l$  Load capacitance of each inverter stage

$C_{ox}$  Gate-oxide capacitance of a MOS device

$D_{OUT}$  Data output

$DA_{conc}$  Dopamine concentration

DIG OUTM Negative digital output

DIG OUTP Positive digital output

$E_{Iref}$  Reference current for subtraction/addition of  $I_{cell}$  from the sensor

electrodes

$f_{-3dB}$  -3dB frequency or open-loop bandwidth

$f_c$  Cut-off frequency of a filter

$F_{osc}$  Oscillation frequency

$F_s$  Sampling frequency

$g_{ds}$  MOS device drain-source transconductance

$G_{II}$  Gain of output stage of the OTA

$G_I$  Gain of input stage of the OTA

$g_m$  MOS device transconductance

$I_{bias}$  Bias current

$I_{ctrl}$  Oscillator control current

$I_{ds}$  NMOS device drain-source current

$I_D$  MOS device drain current

$I_{sd}$  PMOS device drain-source current

meas\_trig Sampling clock that triggers measurement of pulses from the

oscillator and defines the decimation rate of the ID block

N Number of stages of the oscillator

n Digital output code resolution

$N_p$  Number of pulses from the oscillator or I-F stage

$N_s$  Number of samples

osc\_in Input signal from the oscillator

OSC OUTM Negative oscillator output

$OSC\_OUTP$  Positive oscillator output

$p_2$  Output pole of the OTA

$P_{cons}$  Power consumption

$P_{osc}$  Power consumption of the oscillator

$Q_{in}$  Quantity of interest from sensor

$R_o$  Output resistance of each inverter stage

$r_o$  MOS device output resistance

$T_{meas}$  Measurement time

$T_{osc}$  Oscillator period

$T_s$  Sampling time interval

$V_{bias}$  Input bias voltage

$V_{dd}$  Supply voltage

$V_{ds}$  MOS device drain-source voltage

$V_d$  MOS device drain voltage

$V_{gs}$  MOS device gate-source voltage

$V_g$  MOS device gate voltage

$V_{icm}$  Input common mode voltage

$V_{in}$  Bias voltage of OTA1 in the IA block

$V_{ov}$  Overdrive voltage of a MOS device

$V_{ref}$  Bias voltage of OTA2 in the IA block

$V_{RE}$  Voltage at the reference electrode

$V_{SB}$  MOS device source-bulk voltage

$V_{ss}$  Ground voltage

$V_{th}$  MOS device threshold voltage

$V_T$  MOS device thermal voltage

$V_{WE}$  Voltage at the working electrode

$z_1$  Right-half-plane zero of the OTA

M Multi-bit digital code

# 1 Introduction

In recent years, the need for real-time monitoring of physiological activities in the human body has accelerated the development of biomedical sensors. Thus, biosensing has become a fast-growing area of research especially the design of implantable and wearable devices for various biomedical applications. The use of biosensors in a wide range of biomedical applications provides possibility for remote monitoring and diagnosis of patients, improved treatment of diseases, compensating or restoring lost function to a part of the human body, further study and analysis of disorders that experts lack sufficient understanding about or that are incurable [7], [8], [9], [10]. An important application area that benefits from this bio-technological advancement is sensing and monitoring of neural activities in the brain.

Neurological activities in the brain are mainly transmitted by neuroelectrical or neurochemical signals that control the central nervous system of the human body. Transmission of neurochemical signals between neurons are carried out by bio-agents or bio-markers known as neurotransmitters. Neurochemical signals are responsible for controlling cognitive, learning and memory functions in the brain. Thus, neurological disorders such as Parkinson's disease, Epilepsy, Schizophrenia, Huntington's disease and Alzeihmers have been associated with deficient or unstable level of neurotransmitters such as glutamate and dopamine [1], [2], [3], [4], [5]. In addition, dopamine as a neurotransmitter undergoes two main reactions during transmission of neurochemical signals. Hence, the goal of this thesis is to detect the oxidation and reduction reaction cycles of dopamine from the biosensor interface in the brain.

Detection of neurological signals has its challenges which define the minimum limits of sensitivity and resolution of the sensor interface. These limitations are due to inherent noise sources that are introduced from surrounding tissues through contact interface with the biosensor. In addition, neurochemical signals have very small signal amplitudes at low frequencies. Thus, the main design requirement of the sensor interface to be able to achieve good signal quality is reduction of noise. Other requirements of the readout sensor interface include high sensitivity, high resolution, large dynamic range and low power consumption [3], [4], [5]. The proposed design of the readout sensor interface is based on a mixed-signal front-end architecture which combines both analog and digital circuits to minimize noise and discretize the detected dopamine current signals for further external processing.

Detection and monitoring of dopamine in the brain plays a vital role in improving the treatment of neurological disorders which may lead to reduced tremors, seizures and ultimately longer life expectancy of patients suffering from related diseases. Furthermore, the possibility of real-time monitoring and analysis of dopamine levels in affected patients will provide further understanding of neurotransmitters. Hence, this thesis presents the design and implementation of a proposed solution for readout of dopamine oxidation and reduction in 65 nm CMOS technology. Concepts related to neurochemical sensing and biomedical readout circuits are discussed in chapter 2. Subsequently, detailed description of the system level design of DORSI is presented in chapter 3. Finally, chapter 4 presents simulation results based on measured data from the sensor and inferences from the results are concluded in chapter 5.

# 2 Background

From the development of the electron microscope in the 1930s to the design of implantable pacemakers, the importance of advancement in electronics to the study of biology and medical instrumentation is undeniable [7]. The impact of rapid development in the evolving field of bioelectronics has become evident in various application areas such as medicine, environment, forensics and homeland security [7], [8]. Thus, the fusion between biology and electronics has led to remarkable solutions to important needs in the medical industry such as pathogen detection and analysis, disease prevention and treatment, compensating or restoring lost functions like sight, hearing and movement [7], [9]. Furthermore, there have been several bioelectronic innovations over past decades especially in the area of medical imaging, prosthetics and implantable devices; from which some examples are listed below.

- Medical imaging devices: electrocardiograph (ECG or EKG), ultrasound, magnetic resonance imaging (MRI), computed tomography (CT), positron emission tomography (PET) and Electroencephalography (EEG) [7], [8].

- Prosthetics and implantable devices: cochlear implants, retinal or cortical implant, muscle implants, cardiac pacemaker and defibrillators, glucose monitoring device, implantable neural electrodes and probes [9], [7], [11].

Despite the aforementioned breakthroughs in the development of bio-electronic devices, there are still areas open to further research and new emerging needs related to personalised healthcare. Thus, the demand for wearable, implantable and wireless devices is increasing and providing more research opportunities in a wide range of biomedical applications. In addition, the miniaturization of electronic devices as a result of the exponential growth in semiconductor technology as predicted by Moore's law <sup>1</sup>, has also been a driving force behind recent development in the field of bioelectronics. Hence, advances in semiconductor technology and development of bio-compatible materials offer promising prospects for future innovations in their application to life sciences especially in the design of biosensors.

The influence of development in the field of bioelectronics and semiconductor industry on sensing of biological molecules has increased in recent years [7]. Hence, one application area that benefits from the scaling down of electronics upto the nano-scale, is the field of neuroscience where there is a need for development of brain-machine interfaces that use detected neuron signals to control mobility functions in artificial prostheses [10], [13]. Another application that profits from advances in semiconductor technology is the design of closed-loop interfaces for sensing, monitoring, analysis and stimulation of neural activities in the brain [14]. Thus, measurement of dopamine concentration from the brain contributes to the realization of fully-implantable closed-loop interfaces.

<sup>&</sup>lt;sup>1</sup>Gordon E. Moore, the co-founder of Intel Corporation (formerly Fairchild Semiconductor) predicted in 1965 that the number of components on integrated circuits will double every 18-24 months [12]. Subsequently increasing computational power and speed while the cost and size reduces for each generation of an electronic device.

## 2.1 Neurotransmitters

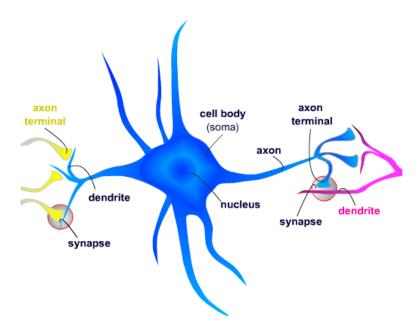

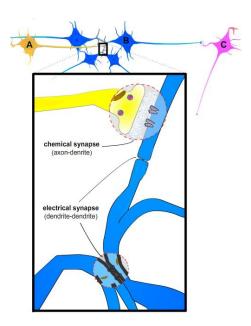

Further knowledge about how neurons communicate and transmit information within the central nervous system is of significant value to researchers in the field of neuroscience for improving treatment of neurological disorders and neurodegenerative diseases. Neurons in the central nervous system (CNS) are connected by synapses and communicate through electrical and chemical impulses or signals. Figure 2.1 describes the basic structure of neurons and their interconnections to synapses. In addition, neurons transmit information mainly via electrical signals also known as action potentials (AP) which travel across electrical and chemical synapses (i.e. the gap between two neuron cells). Neurotransmission originates from the neuron cell body where an action potential is initiated and travels along the axon to the synapse. Thus, neurotransmission in the brain can be classified into electrical neurotransmission (i.e. transfer of AP across electrical synapse) and chemical neurotransmission (i.e. transfer of AP across chemical synapse) as illustrated in Figure 2.2.

Figure 2.1: Structure of neurons [15].

Electrical neurotransmission occurs rapidly over long distance from the neuron cell body to the axon terminal and across electrical synapses in the order of 150 m/s within the central nervous system [15]. Electrical synapses are conductive by nature due to the existence of synaptic gap junctions between dendrites that aid the transmission of an AP as shown in Figure 2.2. On the other hand, chemical neurotransmission occurs over shorter distance in the order of (20-30) nm; across chemical synapses as a result of discharge and absorption of biochemical molecules also known as neurotransmitters [3], [15], [16]. Neurotransmitters are released in chemical synapses which are non-conductive by nature, to provide a "short" between an incoming AP and the synaptic potential that is established within the synaptic cleft as shown in Figures 2.3a and 2.3b [15], [17]. The synaptic cleft is the region of

Figure 2.2: Electrical and chemical synapses [15].

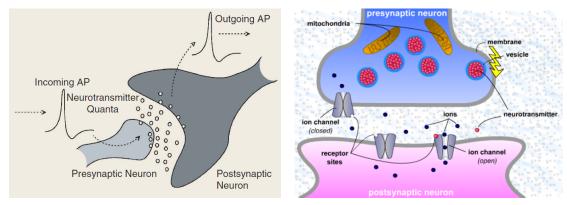

$\sim 1~\mu\mathrm{m}^2$  between axon terminals and dendrites that is filled with extracellular fluid [15], [16]. Hence, transmission of action potentials between pre-synaptic (source) and post-synaptic (target) neurons across the synaptic cleft is carried out chemically by neurotransmitters such as dopamine and glutamate as depicted in Figure 2.3a.

The process of chemical neurotransmission involves the transfer of ions such as sodium  $(Na^+)$ , potassium  $(K^+)$  and calcium  $(Ca^{++})$  through open ion channels when an action potential (in yellow) arrives at the pre-synaptic neuron as illustrated in Figure 2.3b [15], [16], [18]. The ion channels that are attached to the target neuron are opened when neurotransmitters released from vesicles through the pre-synaptic neuron membrane, adhere to post-synaptic receptor sites. The movement of ions from the source neuron to the target neuron induces current flow in the synaptic cleft which changes the electrical properties of the post-synaptic neuron membrane. Thus, producing a synaptic potential in the target neuron which increases as a result of exchange of ions through the open ion channels, until the sum of synaptic potentials of the target neuron is larger than the resting potential of the post-synaptic neuron membrane. This threshold is reported to be within -40 mV to -80 mV and the generated AP is known to last a few milliseconds depending on the type of ion channels, nature of receptors and neurotransmitters [15], [16], [18]. Furthermore, after the transmission of the stimulated outgoing AP, neurotransmitters are removed from the synaptic cleft and absorbed back into the pre-synaptic neuron also known as the process of re-uptake. The absorbed neurotransmitters are recycled and form new vesicles from the energy produced by the mitochondria structures in the pre-synaptic neuron. Hence, the release and re-uptake of electro-active neurotransmitters result in oxidation and reduction reactions during chemical neurotransmission.

Dopamine as a neurotransmitter is known to be primarily responsible for coordination, learning and memory functions in the brain [1]. Other functions of dopamine

(a) AP transfer through chemical synapse [17]. (b) structures at chemical synapse [15].

Figure 2.3: Chemical neurotransmission.

include behavioural changes, blood flow regulation and aiding secretion of hormones that control eating habits, appetite, sense of reward, pain and pleasure [1], [19], [20]. Thus, several cognitive and mobility related disorders have been attributed to imbalance in the concentration level of dopamine released in the brain during communication between neurons. In addition, irregular transmission of dopamine due to deficient or dysfunctional dopamine receptors has also been reported to be linked with various neurological and psychiatric disorders such as Parkinson's disease, Schizophrenia, Huntington's disease, Alzheimers, Epilepsy, senile dementia, drug addiction, depression, bipolar disorder and Tourette's syndrome [1], [2], [3], [5], [14], [6], [20]. In particular, Parkinson's disease has been associated with degeneration of dopamine neurons which leads to reduced concentration of dopamine that is released in the synaptic cleft [15], [19]. Thus, the resulting synaptic potential is insufficient to initiate an AP or the generated AP may occur late which in turn affects subsequent chain of reactions during transmission of information within the central nervous system.

The main cause of Parkinson's disease (i.e. a mobility disorder that results in muscle tremors, stiffness and instability in movement) remains unknown [3],[19]. Current treatments include medications and consumption of food reach in amino acids to increase the level of dopamine released in the brain. An alternative treatment in severe cases of Parkinson's disease is a neurosurgical technique for stimulating regeneration of dopamine neurons known as deep brain stimulation (DBS) [11], [14]. Hence, monitoring of the concentration of dopamine produced after DBS surgery and the response pattern of the generated action potential plays a vital role in improving the treatment of Parkinson's disease and other related disorders. Therefore, miniaturized closed-loop interfaces for real-time monitoring and stimulation of dopamine will provide pharmacologists and neuroscientists with further understanding about the structure and signalling mechanisms of dopamine as a neurotransmitter for development of new therapeutic medications for regulation of dopamine levels, correction or management of receptor abnormalities and regeneration of diminishing neurons.

# 2.2 Neurochemical sensing

As described in the previous section 2.1, neurotransmitters undergo electrochemical reactions in the brain during transmission of action potentials within the central nervous system. Neurotransmitters are either electrochemically active or non-electroactive by nature. Electrochemically active neurotransmitters such as dopamine, serotonin and histamine; produce reduction-oxidation (redox) currents in the presence of an induced action potential or applied electrical potential [3]. Thus, electroactive neurotransmitters can be directly detected from the brain by electrochemical transduction techniques. On the other hand, non-electroactive neurotransmitters such as glutamate need to be detected indirectly through their reactions with enzymes that produce electroactive biochemicals which can be detected [3], [4], [17].

Enzymatic sensing techniques monitor the products of the catalytic reaction that occurs between the enzyme and the specie of interest. Other quantities monitored by enzymatic indirect transduction include charge transfer, generation and transfer of heat which may result in detectable temperature gradient [21]. In the case of non-electroactive neurotransmitters, the concentration of the resulting electroactive product from the reaction is the quantity that is detected, not the concentration of the originating neurotransmitter. Available methods for in-direct detection of neurotransmitters include optical (based on light emitting reactions also known as chemiluminescence), liquid chromatography (based on separation of chemical ions) and imaging (based on single photon emission computerized tomography(SPECT) or PET) techniques [17], [20], [22]. Another method that can be used in the detection of neurotransmitters is based on affinity sensing techniques which monitor the chemical bonding between biochemical molecules and their corresponding receptors. Quantities such as changes in mass or refractive index can be detected and measured in affinity based biosensors which have been used in monitoring of changes at dopamine receptors [19], [21].

Considering the aforementioned techniques, direct electrochemical detection is the preferred option and most commonly used method for detection of dopamine and other electroactive neurotransmitters. In addition, it provides faster response, reproducible and more sensitive detection of changes in dopamine concentration due to direct relationship between the detected concentration levels and changes in measured currents [20]. Electrical signals induced by the flow of ions between neurons within the extracellular fluid of the synaptic cleft result in detectable forward and reverse currents corresponding to increase and decrease in the concentration of dopamine. Thus, variations in the dopamine concentration of the brain are further translated as activation or deactivation of specific functions within the CNS [1]. Furthermore, electrochemical analysis and measurement of induced currents can be easily integrated into miniaturized bioelectronic devices also known as potentiostats, that can be implanted for monitoring and regulation of dopamine levels.

#### 2.2.1 Operation principle

Neurochemicals and related analytes such as dopamine, glutamate, histamine, adenosine, noradrenalin and serotonin; are monitored with the help of potentiostats which

operate based on electrochemical transduction principle [3], [23], [24]. Electrochemical transduction principle is the process of applying an electrical potential across an electrochemical cell and measuring the induced redox current within the cell. The electrochemical transduction principle was first applied to biosensors by Leland C. Clark Jr. in late 1950s in the design of electrodes used for sensing oxygen in the body or environment [25]. As a follow-up to the oxygen electrodes, Leland C. Clark Jr. designed the first glucose sensor based on the same principle in early 1960s [25]. The electrochemical transduction principle has since become an integral part of the design of biochemical sensors.

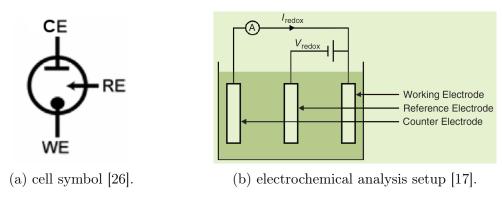

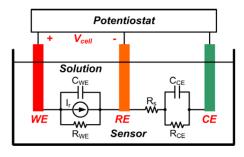

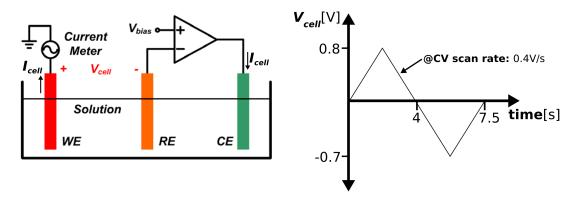

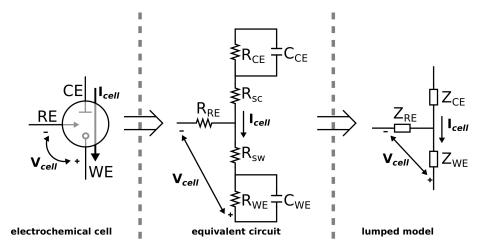

The structure of the electrochemical cell used in biosensors that apply the electrochemical transduction principle, is based on two or three electrodes namely working electrode (WE), reference electrode (RE) and counter electrode (CE) as shown in Figure 2.4. The counter electrode is also known as auxiliary electrode (AE) and can be discarded in the case of an electrochemical cell setup that utilizes two electrodes. The working electrode is where the electrochemical reaction occurs and the reference electrode is used for detecting the potential at which the reaction occurred with respect to the working electrode voltage. Therefore, the reference electrode is designed so that it is inert to the solution and the reaction occurring at the WE.

Figure 2.4: Electrochemical cell structure.

Potentiostats used in neurochemical monitoring are usually based on the three electrochemical cell structure as depicted in Figure 2.4b. Thus, the induced redox current  $I_{redox}$  is measured through the CE rather than through the RE, thereby minimizing instability in the reference voltage at the RE which is essential in ensuring stable cell voltage  $(V_{redox})$ . The readout circuit of the potentiostat is responsible for setting and controlling the cell voltage  $(V_{cell} \text{ or } V_{redox})$  at which the expected reaction occurs and measures the induced current through the cell  $(I_{cell} \text{ or } I_{redox})$ . Hence, stability of the cell voltage is an important requirement in the design of the potentiostat for reducing inaccuracies in the detection of the corresponding oxidation voltage at which the measured current peaks.

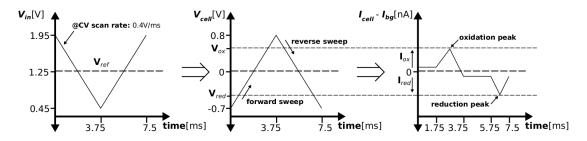

There are several techniques reported for sensing neurochemicals in the brain, but the most common methods are chronoamperometry (CA) and cyclic voltammetry (CV) [3], [27]. The chronoamperometry technique involves the application of constant potential  $V_{redox}$  across the WE and RE, and measuring the induced current

$I_{redox}$  through the CE. This method is appropriate for detecting neurochemical or biochemical molecules when the exact potential at which the expected electrochemical reaction occurs is known such as in glucose monitoring [27], [28]. Instead of chronoamperometry, cyclic voltammetry is used when the reaction potential is not accurately known which is the case for dopamine because the redox peak voltage varies for different patients and with the sensor electrode material [6]. However, the implementation of CV is more complex since it involves applying a range of voltages  $V_{redox}$  (typically a triangular waveform) across the WE and the RE in order to obtain a full redox current  $I_{redox}$  profile of the detected neurochemical. In addition, CV is especially useful for detecting both oxidation and reduction reactions of a neurochemical or biochemical within the forward and reverse voltage sweep of  $V_{redox}$ . Hence, this technique is an appropriate option for detection of dopamine where both oxidation and reduction reactions are of interest for studying the release and absorption patterns of dopamine.

Other forms of cyclic voltammetry are differential pulse voltammetry (DPV) and fast-scan cyclic voltammetry (FSCV). DPV is based on applying a staircase or step-like triangular voltage waveform where the difference in the detected currents before and after each pulse or step is measured against the corresponding potential difference. Thus, very high sensitivity can be achieved with the DPV technique due to reduction in underlying background current [20]. However, the complexity of the design of the waveform generator and subsequently the implementation of the integrated potentiostat is increased. On the other hand, FSCV is based on very high voltage sweep rate of the applied voltage waveform. FSCV has become the preferred option in detection of neurotransmitters due to its high scan rate which has been reported to increase sensitivity and selectivity of the electrodes to neurochemicals [3], [6], [20]. In addition, the response rate of FSCV in neurochemical sensing is comparable to the response time of neurotransmitters released within the synaptic cleft which are swiftly removed during re-uptake process [3], [6]. Thus, the detection of dopamine with high resolution is achieved with FSCV which makes FSCV a wellsuited approach for neurochemical monitoring.

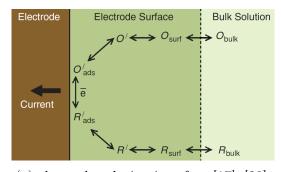

(a) electrode-solution interface [17], [29].

(b) cell model [30].

Figure 2.5: Electrochemical transduction principle.

In depth understanding of the chemical interactions that occur at the electrode interface during FSCV is important for the design of the potentiostat. Hence, Figure

2.5a illustrates the electrochemical transformation that occurs between the electrode and the chemical solution or electrolyte which contains the electroactive specie. The bulk solution in Figure 2.5a corresponds to the the extracellular fluid in the synaptic cleft and the electroactive specie of interest is dopamine. Electrons are transferred between both mediums (electrode  $\rightleftharpoons$  solution/electrolyte) as a result of redox reactions at the electrode surface. During the forward sweep of the applied voltage, the reduced form of the specie  $(R_{bulk})$  is transformed to its diffused form  $(R_{surf})$  as it approaches the surface of the electrode. The diffused form  $(R_{surf})$  is further transformed to its adsorbed form  $(R_{ads})$  after undergoing a chemical reaction (R') between the diffused form and chemical molecules at the electrode surface which results in electron loss (or oxidation). The oxidized form of the specie in its adsorbed state  $(O_{ads})$  diffuses back into the solution to produce an oxidized form of the specie in its bulk state  $(O_{bulk})$ . Hence, the oxidation reaction that occurs during the forward voltage sweep can be simplified as follows, where n is the number of electrons  $(e^-)$  lost.

$$R_{bulk} \Rightarrow O_{bulk} + ne^-$$

(2.1.a)

$$R_{bulk} - ne^- \Rightarrow O_{bulk}$$

(2.1.b)

On the other hand, the reverse of the described process occurs during the reverse sweep of the applied voltage. Thus, the oxidized bulk form of the specie  $(O_{bulk})$  is transformed to its diffused form  $(O_{surf})$  and further into its adsorbed form  $(O_{ads})$  after undergoing a chemical reaction (O') which results in electron gain (or reduction). The reduced form of the specie in its adsorbed state  $(R_{ads})$  diffuses back into the bulk solution to produce the oxidized bulk form of the specie  $(R_{bulk})$ . Thus, the following equation holds during the reverse sweep for the reduction reaction of the oxidized form of the electroactive specie, where n is the number of electrons  $(e^-)$  gained.

$$O_{bulk} + ne^- \Rightarrow R_{bulk}$$

(2.2)

Therefore, the redox reaction that dopamine as an electroactive neurotransmitter undergoes during FSCV, can be expressed as in Equation (2.3). Equation (2.3) is based on Equations (2.1) and (2.2), where DOQ (dopamine-ortho-quinone) is the oxidized form of dopamine (DA) [3].

$$DOQ + 2e^- \Rightarrow DA$$

(2.3)

This redox cycle continues for every voltage sweep  $(V_{redox})$  that is applied by the potentiostat across the WE and RE. Figure 2.5b describes the electrical representation of the electrode-solution sensor interface to the potentiostat. The electrical properties of the sensor interface and bio-compatibility issues are further discussed in section 2.2.2.

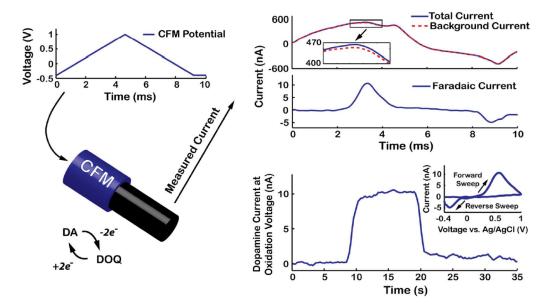

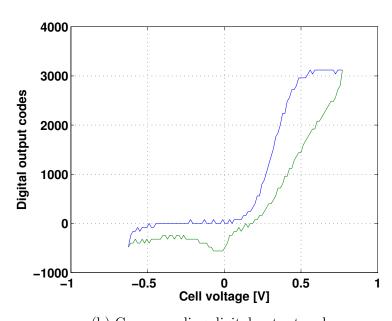

Electrochemical analysis based on the fast-scan cyclic voltammetry (FSCV) for the detection of dopamine is illustrated in Figure 2.6. The voltage sweep ( $V_{redox}$ ) that is applied by the potentiostat is based on the scan rate of the FSCV setup

Figure 2.6: Detection of dopamine using FSCV [3].

and the sensitivity range of the working electrode to both oxidation and reduction reactions. Carbon-based electrodes are known to provide very good sensitivity and selectivity to dopamine and other neurotransmitters because they are easily oxidized by carbon molecules [6], [24]. The detected current  $(I_{cell})$  is a combination of the faradaic current from the oxidation and reduction of the neurotransmitter  $(I_{redox})$ , and the background current  $(I_{bg})$  from the electrodes. The background current is introduced as a result of local reactions at the electrode surface from residues of adsorbed redox products that have accumulated unto the electrode surface. Hence, subtraction or reduction of background current is necessary to be able to effectively detect the faradaic current due to dopamine which are typically in the order of tens of nano-amperes (nA) depending on the concentration of the released dopamine and the sensitivity of the electrode.

Another advantage for using FSCV technique is that the use of high scan rates aids averaging of generated background current which in turn improves the resolution of the detected faradaic current. In addition, identification of oxidation and reduction current peaks and corresponding voltages serve as indicators of the variation in dopamine concentration which is essential for neuroscientists in understanding more about the release and re-uptake mechanisms of neurotransmitters in the brain and improving treatments of patients with dopamine deficiency or imbalance in dopamine levels.

#### 2.2.2 Sensor interface

Considering the complex environment of the human body, with thousands of reactions occurring at the same time within few milliseconds, issues such as biocompatibility, sensitivity and selectivity of bio-electronic devices remain main chal-

lenges. In general, sensitivity and selectivity of stimulating and sensing electrodes are important requirements in the design of biosensors. Thus, the structure and selection of materials of the biosensor electrodes have a significant impact on the performance of biosensors. Bio-compatibility of materials used in biosensors is also an important criteria in the selection of electrodes used in bio-sensing, especially in the area of neurochemical monitoring. There are several materials used in the design of electrodes that are utilized in neurochemical sensors. The reference electrode (RE) is usually based on silver/silver-chloride (Ag/AgCl) due to its excellent electrical and chemical characteristics such as small and stable electrode offset voltage, low electrode-solution interface impedance and low charge-transfer resistance [31]. The auxiliary or counter electrode (CE) is often based on noble metals such as platinum (Pt) or gold (Au) due to their bio-compatibility characteristics [3], [20], [32], [33]. The selection of the working electrode (WE) material is the most critical of the three electrodes because the electrochemical reaction occurs at the surface of the working electrode.

The most common WE materials used in detection of neurotransmitters are mainly a combination of carbon based materials, polymers, metal-oxides and noble metals [20]. Thus, there is more focus on research related to the design of working electrodes and the material used in order to improve its sensitivity, selectivity to the specific neurochemical of interest and biofouling reduction. Biofouling is the process of adsorption or accumulation of residual products from redox reactions onto the surface of the electrode [6]. As a result, the accumulated residue from the redox reactions changes the electrical properties of the electrode over time which causes a voltage drift in the WE voltage [7]. Consequently, the voltage drift in the WE voltage leads to inaccuracies in the measured current peaks and corresponding oxidation-reduction voltage. Hence, minimizing the effect of biofouling plays a key role in improving electrode sensitivity and resolution. Thus, reduction or elimination of biofouling remains an active area of research in the field of biomaterials for biochemical sensing.

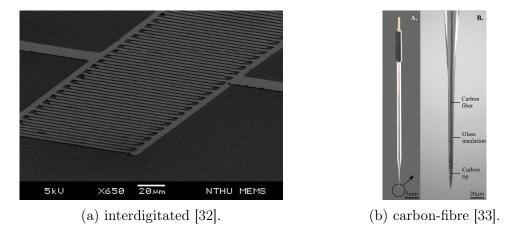

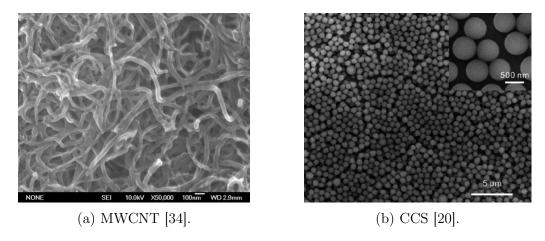

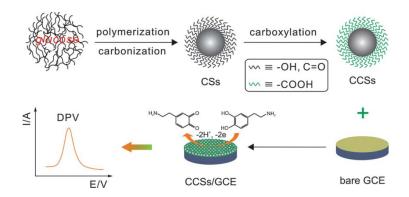

The structure and dimensions of electrodes used in biosensing also play a major role in the performance of the biosensor. There are several design structures available for neurochemical sensing, but the most common electrode structures used in neurotransmitter detection are interdigitated electrodes and carbon-based nanostructures such as carbon-fibre electrodes and carbon nanotubes (CNT) as illustrated in Figures 2.7a, 2.7b and 2.8a. Another interesting carbon based nanostructure, that shows promising performance in detection of dopamine, is carboxylated carbonaceous spheres (CCS) as depicted in Figure 2.8b. CCS nanostructures are formed by attaching carboxyl groups to carbon spheres, which are prepared from glucose and finally depositing the CCS on glassy carbon electrodes (GCE), as illustrated in Figure 2.9. The use of CCS results in reduction of biofouling due to less adsorption of redox products at the electrode surface [20].

In addition, CCS also shows high selectivity towards dopamine due to reduced interference from other analytes within the same oxidation potential window such as ascorbic acid and uric acid [6], [20]. CCS provides good selectivity to dopamine as a result of large number of carboxyls that are present on the surface of the CCS-GCE

Figure 2.7: SEM images of common electrode structures used in neurochemical sensors.

Figure 2.8: SEM images of other electrode structures used in neurochemical sensors.

electrode [20]. However, one drawback of using CCS is that detection of reduction current peaks has not been achieved and a definite reason for this shortcoming is still under further research. Hence, CCS-GCE electrodes are not well-suited for detection of redox species such as dopamine despite their outstanding performance in terms of sensitivity, selectivity and bio-compatibility.

Furthermore, certain dimensions of electrode structures are vital in optimization of the performance of the electrode and biosensor. Some of these dimensions are the tip-length of carbon-fibre electrodes, gap-distance of interdigitated electrodes and diameter of CNT or CCS. For instance, increase in the tip-length of carbon-fibre microelectrodes (CFM) has been reported to increase the detected current sensitivity [33]. Likewise, increasing the diameter of CCS increases the total surface area that is exposed to the biochemical of interest and in turn increases the sensitivity of the electrode. In contrast to CCS and CFM, the sensitivity of the electrode increases as the gap between the generator and collector plates of the interdigitated electrodes reduces [22]. Typical sensitivity range of carbon-fibre electrodes is around

Figure 2.9: Fabrication of carboxylated carbonaceous spheres (CCS) on glassy carbon electrode (GCE) [20].

(10-50) nA/ $\mu$ Mol which is sufficient to detect dopamine concentrations which are usually within the range of 10 nMol -1  $\mu$ Mol in the synaptic cleft [3], [6]. Performance comparison between several other carbon-based structures that are used in the detection of dopamine are summarized in Table 2.1. It is important to note that the detection method (CV-based or DPV-based) and scan rates differ in some of the structures which also affects the performance values that are listed in the comparison table below.

Table 2.1: Performance comparison of common working electrode (WE) materials used in dopamine detection

| Material and Structures                     | Detection          | Sensitivity             | Linear             |

|---------------------------------------------|--------------------|-------------------------|--------------------|

|                                             | limit ( $\mu$ Mol) | $({ m nA}/\mu{ m Mol})$ | range ( $\mu$ Mol) |

| Nafion/MWCNT [4], [35]                      | 0.07               | $16.26 \pm 1.41$        | 2 - 20             |

| Poly-glutamic acid/SWCNT [36]               | 0.38               | 250 <sup>(i)</sup>      | 3.3 - 26.6         |

| Poly-acrylic acid/MWCNT/GCE [37]            | 0.02               | $4*10^3$ (ii)           | 0.04 - 3           |

| Methylene blue/MWCNT [34]                   | 0.2                | $5.6 * 10^3$            | 0.4 - 10           |

| Graphene modified electrode [38]            | 2.64               | 80 (iii)                | 4 - 100            |

| Nitrogen-doped graphene [39]                | 0.25               | $\sim 30$               | 0.5 - 170          |

| Graphene sheets/imprinted polymers [40]     | 0.1                | $\sim 12.5$             | 0.1 - 830          |

| Chitosan-graphene modified electrode [41]   | 1                  | 20 <sup>(iv)</sup>      | 1 - 24             |

| Diamond-like carbon (DLC) electrode [6]     | 10                 | 780 <sup>2</sup>        | 10 - 100           |

| CCS-GCE [20]                                | 0.03               | 450 (v)                 | 0.1 - 40           |

| Carbon-fiber microelectrode (CFM) [3]       | 0.0167             | 10.2                    | 0.125 - 1          |

| Interdigitated carbon electrodes [32], [22] | $10^{-4}$          | 0.57                    | 2 - 30             |

i ii iii v estimated value: specific value not explicitly defined in the source

<sup>&</sup>lt;sup>2</sup>Note: the sensitivity value of the DLC electrode given in Table 2.1 is based on the current density  $(\mu A/cm^2)$  values provided by the source [6].

The performance of the whole read out circuit depends significantly on the interface between the sensor and the potentiostat. The electrical model of the sensor as depicted in Figure 2.5b describes the impedance structure that exists at the sensor-potentiostat interface. Thus, the impedance model provides a means of estimating the input impedance that the potentiostat is expected to support. The total input impedance is based on the surface or faradaic resistances from the working and counter electrodes (i.e.  $R_{WE}$  and  $R_{CE}$ ), inherent resistance from the solution  $(R_S)$  and the double-layer capacitances that are formed as a result of separation and accumulation of opposite charges at the WE and CE surface-solution interfaces [26], [30], [31]. The working electrode faradaic or charge-transfer resistance  $R_{WE}$  and the double-layer capacitances (i.e.  $C_{WE}$  and  $C_{CE}$ ) have the following relationship with the electrode cross-section area.

$$C_e \propto k_c * A_e \tag{2.4}$$

where  $C_e$  is the double-layer capacitance of the electrode,  $A_e$  is the electrode cross-sectional area, and  $k_c$  is a constant which is estimated to be 0.36  $\mu$ F/mm<sup>2</sup> [26].

$$R_{WE} \propto \frac{V_{cell}}{I_{cell}} \tag{2.5}$$

Since  $I_{cell}$  is directly proportional to  $A_e$ , Equation 2.5 can be simplified as:

$$R_{WE} \propto \frac{V_{cell}}{A_e} \propto \frac{k_c * V_{cell}}{C_e}$$

(2.6)

Therefore,  $R_{WE}$  is inversely proportional to the electrode area  $A_e$  while  $C_e$  is directly proportional to  $A_e$ ; which implies that  $R_{WE}$  is inversely proportional to the double-layer capacitance of the electrode  $C_e$ . Hence, increasing the electrode area will result in larger detectable current as a result of reduced surface resistance. Thus, improving the sensitivity and resolution of the sensor. On the other hand, increasing the electrode area, increases the double-layer capacitance which in turn increases the adsorption of products (or biofouling) at the electrode surface. Thus, increasing the background current, which reduces the sensitivity of the potentiostat and ultimately degrades the performance of the whole readout circuit.

In addition, the use of FSCV at high scan rates increases the double-layer capacitances due to its dependence on frequency [31]. There are a few techniques reported for reducing the effect of double-layer capacitances due to fast sweep rates of the cell voltage  $V_{cell}$  [24]. These techniques include the use of large amplitude sinusoidal voltammetry, square-wave voltammetry, and fourier transformed alternating current (AC) voltammetry. [42], [43], [44]. Another way to mitigate the effect of double-layer capacitances and to maximize the performance of the sensor is the use of carbon-based materials which are known to provide large surface area whilst having good and stable surface chemistry (i.e. charge-transfer characteristics) [20]. Thus, biofouling is reduced, which makes carbon-based materials and structures more beneficial for biochemical and neurochemical monitoring. As a result, carbon-based materials provide high sensitivity and improved bio-compatibility when compared with other materials.

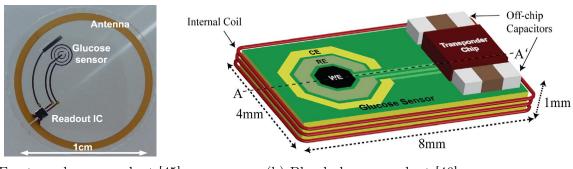

### 2.3 Biomedical readout circuits

Emerging need of personalized healthcare and rising demand for devices that offer real-time monitoring of physiological activities in several biomedical applications are the main driving forces behind recent development in the design of biomedical read-out circuits. The primary function of readout circuits that are used in biomedical applications is to detect physiological quantities of interest and convert the detected signals to another form (usually electrical or optical) which can be further processed to extract meaningful information about specific phenomena. Typical quantities of interest that are monitored by biomedical readout circuits include biochemicals, thermal changes, bio-electrical signals such as in EEG and ECG. Figures 2.10 and 2.11 present examples of state of the art implementation of biomedical readout circuits used in glucose and neurochemical measurements.

(a) Eye-tear glucose readout [45].

(b) Blood glucose readout [46].

Figure 2.10: Glucose monitoring wireless readout devices.

Figure 2.11: State-of-the-art of neurochemical wireless monitoring [14].

A 3  $\mu$ W wirelessly powered active contact lens glucose sensor for real-time monitoring of glucose from eye tear fluid is shown in Figure 2.10a and similar readout circuit for wireless monitoring of glucose within the blood is illustrated in Figure

2.10b [45]. Multifunctional in situ sensing and stimulation of neurotransmitters dopamine and glutamate in the brain is presented in Figure 2.11 which also transmits the detected neurochemical concentration levels across a wireless link operating at a frequency close to 433 MHz [47]. There are other examples of multifunctional, multichannel, low-power and highly sensitive readout circuits for detection of electrical and chemical signals from the brain with outstanding performance reported in literature [3], [4], [48], [49], [50].

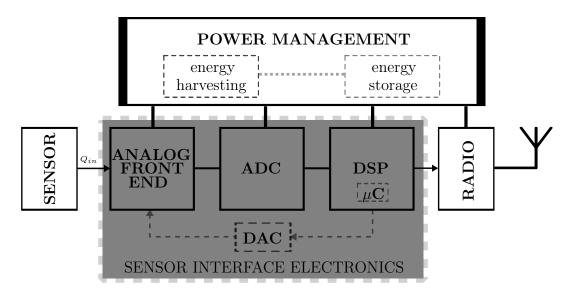

#### 2.3.1 System architecture

Biosensors are designed to sense biological quantities and transform them into electrical quantities  $(Q_{in})$  such as changes in resistance, capacitance, current and voltages which are easier to process by integrated electronics. The architectures employed in the design of sensor readout circuits are based on two main approaches. There is the conventional architecture where most of the signal processing is implemented in analog domain and converted to digital domain in later stages. This traditional approach is useful in the initial phase of development of prototypes to investigate how the system should work and study possible non-idealities [11]. However, the drawback of using this approach is that it provides less flexibility. Thus, the current trend in most sensor readout circuits is to digitalize the signal from the sensor as early as possible in order to minimize mismatch errors, provide more programmability and tuneability of analog blocks; and implement compensation techniques to further optimize the performance of the readout circuit [11], [51]. This

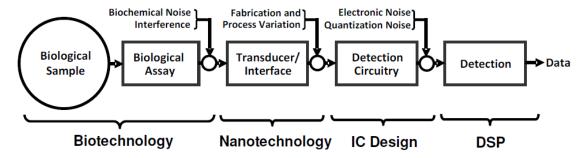

Figure 2.12: Typical system architecture in biomedical readout circuits.

approach is often known as mixed-signal architecture which is based on combination of analog and digital components in the operation of the readout circuit where digital techniques dominate most of the processing of the signal and may also control some aspects of the analog design in a feedback fashion through digital-to-analog converters (DAC) as illustrated in Figure 2.12.

The core processing block of most biomedical readout circuits is defined by the sensor interface electronics (SIE) unit. The SIE unit consists mainly of analog frontend (AFE), analog-to-digital converter (ADC) and digital signal processing (DSP) blocks as presented in Figure 2.12. In addition, for fully-functional implantable biomedical readout circuits, the SIE unit needs to be interfaced to power management (POW) and radio modules. The main function of the POW module is to supply power to the integrated circuits within the SIE core blocks and radio module. Hence, the incoming analog signal  $(Q_{in})$  from the sensor is processed via the SIE unit and the output of the SIE unit is usually in digital form which is transmitted via the radio module to an external system for further processing and visual presentation of the received data. Further details about the main blocks of the readout circuit are described briefly below.

- Analog front-end (AFE): This block interfaces directly with the sensor and consists of signal acquisition circuits. Hence, this block is responsible for acquiring the signal of interest, signal amplification and filtering. The noise generated from this block is usually dominated by flicker noise due to the nature of biosensor signals which have small signal amplitudes and at low-frequencies. Thus, noise optimization of the AFE block plays a critical role in the design and performance of biomedical readout circuits and has a significant impact on detected signal resolution.

- Analog-to-digital converter (ADC): This block is responsible for converting the pre-processed signal from the analog front-end into a form that can be easily processed by the digital signal processing block. Typically, the ADC block receives a continuous signal, samples the received signal periodically in time and outputs a quantized digital representation of the analog input signal. Thus, the discretized output is prone to inaccuracies as a result of quantization error, jitter and aliasing which in turn limits the resolution of the reconstructed signal after conversion. Hence, the ADC block usually consists of sample and hold (S/H) circuits and anti-aliasing filters for minimizing inaccuracies in the digital output codes.

- Digital signal processing (DSP): This block performs post-processing operations on the discretized output from the ADC such as additional filtering, encoding and extracting useful information required by other blocks that it interfaces to, such as the DAC and radio modules. In addition, this block may contain a micro-controller(μC) for implementing more complex and intelligent algorithms which enhance the operation and performance of the readout circuit. The DAC block may be included in the readout circuit for further optimization and programmability of the AFE. The DAC optimizes the AFE block based on the output of previous operations, which depends on the requirements of the biomedical application. The DAC block is especially useful in implementation of feedback systems, for example in closed-loop brain interfaces that also control stimulating electrodes in neurochemical monitoring as shown in Figure 2.11. The DSP block could also be used to implement

modulation of the data to be transmitted before forwarding it to the radio module.

- Power management (POW): This block is especially important in the design of autonomous readout circuits that need to be self-sufficient which is the case in implantable devices. This module typically consists of two main blocks namely the energy harvesting and energy storage blocks which can operate independently or co-dependently as illustrated in Figure 2.12. Thus, biomedical readout circuits are generally implemented either with only the energy storage block or with only the energy harvesting block or with both blocks. The energy harvesting block consists of circuits that collect and transform energy from forms such as radio frequency (RF), light and thermal energy; into electrical energy that can be used to power the readout circuit. In addition, the energy storage block often includes batteries or super-capacitors for storing the harvested electrical energy or for directly powering the readout circuit. However, the main challenge of using only the energy storage block in implantable devices is that it requires periodical surgery for replacement when it eventually runs out of charge. Furthermore, miniaturization of the storage unit in order to increase its lifespan presents another challenge of using only the energy storage block in implantable devices. Likewise, using only the energy harvesting block has its own challenges such as when the power received from the energy source is not sufficient to power the device or if the RF link is broken. Hence, the current trend and recommended approach is to implement both blocks such that the harvested energy is used to recharge the energy storage components [11].

- Radio: This module is primarily responsible for transmission of the digital output data from the DSP block to an external system for further analysis and processing. The radio module may also be used to receive the RF signal that is used by the POW module to harvest energy for powering the readout circuit. Hence, the radio module is often implemented as a transceiver and typically consists of radio frequency integrated circuits (RFIC) such as low-noise amplifier (LNA), frequency mixers, local oscillator (LO), baseband filters and antennas. On the other hand, the use of RFID based radio modules in implantable and wearable devices is becoming increasingly popular and promising for reducing power due to the use of passive components in the implementation of the radio module [52]. In addition, the RFIC circuits used in implantable devices are designed to operate at low frequency bands usually within the Industrial, Scientific and Medical (ISM) or Medical Implant Communication Service (MICS) bands or any of the other frequency bands that are allocated to or reserved by different countries and geographical regions as shown in appendix A1. There are other regulations that implantable RFICs are required to fulfil such as limit on maximum allowable data rates and specific absorption rate (SAR) that defines the maximum RF power that is allowed through the body depending on the location of the readout circuit in the body [11]. These standards are in place to reduce signal attenuation

at skin-tissue interface and to minimize the overall impact of RF signals on human body.

Having described the internal blocks of biomedical readout circuits, it is evident that the design of wearable and implantable devices for real-time monitoring of biological quantities and processes requires careful consideration of the system architecture, comprehensive understanding of the system component functions and implementation of underlying circuitry. There are two key design methodologies that govern the selection of circuit topology and architectures that are utilized in the design and implementation of biomedical readout circuits.

One methodology is based on low-noise driven system design with emphasis on reducing the effect of noise from various noise sources on the performance of the whole readout circuit. In general, the sensor limits the overall system performance and the readout circuitry should be designed to cause no harm or degrade the small sensor signal which is the main challenge in the design of sensor interface electronics [51]. Some of the common noise sources known to affect biomedical readout circuits are discussed in section 2.3.2.

The other methodology is low-power driven system design with emphasis on optimizing each block to either operate at low voltages or to consume as low current as possible. An important aspect of designing low-power implantable devices is to adopt energy-efficient techniques especially in the ADC and DSP blocks that often consume a lot of power during signal processing.

#### 2.3.2 Biosignal distortion and noise sources

Achieving good signal quality from biosensors with little or no distortion is the main challenge in the design of biomedical readout circuits. Biosignals such as blood pressure, heart potentials, eye, muscle and brain potentials, biochemical signals and other physiological quantities of interest have characteristics that further complicates their detection and measurement. These characteristics include small signal amplitudes, low frequency components, presence of competing signals within the same frequency range with higher signal amplitudes, interference from other reactions at biosensor interface and rate of occurrence of the biosignal of interest [6]. Hence, biosignals are prone to distortion from various sources and at different stages in the signal life-cycle from signal acquisition to signal readout as depicted in Figure 2.13.

The initial point of distortion of the biosignal is at the sensor interface to the environment where the signal is detected either by chemical, mechanical, optical or electrical methods. The detection is as a result of interaction between the captured biological assay from the sample collected from the region of the biological quantity of interest, and the electrodes or interface structures of the biosensor. However, in reality, the detected signal is not solely as a result of interactions from only the quantity of interest but may also include contributions from local reactions at the sensor interface due to bio-fouling that results in biochemical noise as earlier discussed in section 2.2.2. In addition, the detected signal may also include contributions from chemical or electrical interference as a result of reactions from other quantities that

Figure 2.13: Common noise sources in biomedical readout circuits [53].

are not of interest or due to variations in contact impedance and contact potential of the sensor electrodes at the skin or tissue interface. Hence, biosensors are designed to have high selectivity to the specific quantity of interest and to reduce or counter the effect of mismatches in the contact impedance and contact potential at the electrode-skin interface for wearable devices or at electrode-tissue interface for implantable devices. Thus, biosignal attenuation, distortion and interference are reduced due to the use of noble metals or carbon as electrode materials. As a result, these materials are bio-compatible because of their inert nature (i.e. they do not undergo reactions). The use of inert materials increases the contact or interface impedance which can be reduced by increasing the electrode surface area as given in Equation 2.6. The electrode surface area can be increased by using nanostructures such CCS or electrode surface-roughening techniques also known as electrode de-polarisation [31].

Another source of noise and biosignal distortion is at the sensor interface to the detection circuitry where the signal is acquired in electrical form and processed. Distortion of the biosignal occurs due to fabrication and process variations in the electrical properties of the electrodes and characteristics of transistors which introduces mismatches and limits the performance of the readout circuit. Hence, the use of integrated circuits (IC) techniques for compensating non-idealities such as offset and gain errors that occur due to CMOS technology manufacturing process spread should be considered especially in the design of the analog components within the detection circuitry. In addition, dynamic techniques such as chopping, auto-zeroing and dynamic element matching (DEM) can be explored to reduce the effects of flicker noise (also known as 1/f noise) and component mismatch, due to the low frequency operation and small bandwidth of biosignals [51], [54].

Other electronic noise sources include thermal noise and shot noise which are related to collisions between charge carriers along conductive channels within metal-oxide-semiconductor (MOS) devices. These collisions result in fluctuations in the input signal also referred to as white noise. Hence, reduction of thermal noise or KT noise is important in sensor readout circuits because it sets the minimum limit of detection of the sensor signal; and more importantly when the readout circuit is based on mixed-signal architecture, to prevent aliasing of under-sampled white noise into the sensor bandwidth [54], [55]. Thus, thermal noise can be reduced by sigma-delta modulation techniques such that errors caused as a result of thermal

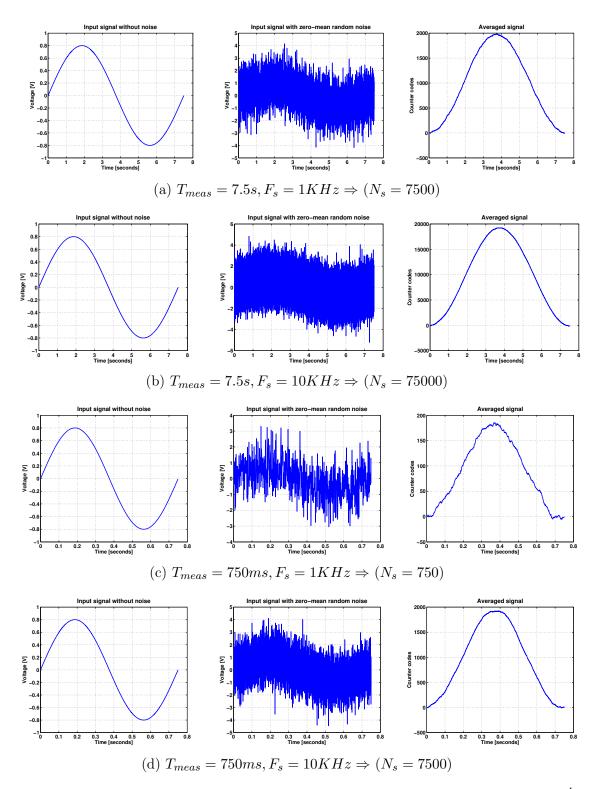

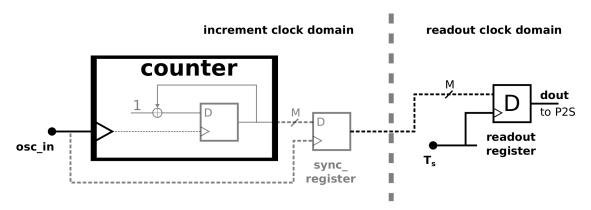

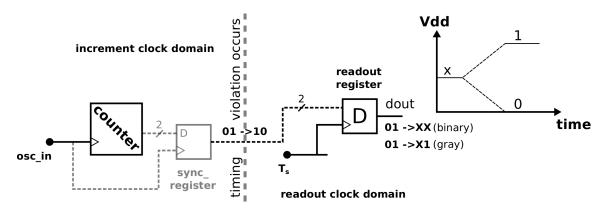

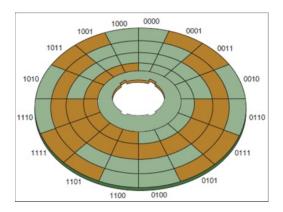

noise are modulated out of the sensor signal bandwidth [51], [54]. Another method for reducing thermal noise is the use of digital averaging techniques such as simple, moving, weighted-moving average filtering and successive sample averaging with decimation for anti-aliasing [54], [55], [56]. It is important to note that averaging techniques can only be used to minimize thermal noise but not to reduce flicker noise because the measurement samples of white or thermal noise are uncorrelated whereas that of flicker or 1/f noise are correlated between current and prior samples [55], [57]. In addition, there is a limit to which averaging techniques can improve the signal-to-noise ratio (SNR) and signal resolution at the expense of longer measurement time [56]. Hence, an optimum limit on measurement time and sampling frequency should be defined during which the benefits of using averaging techniques are maximized.

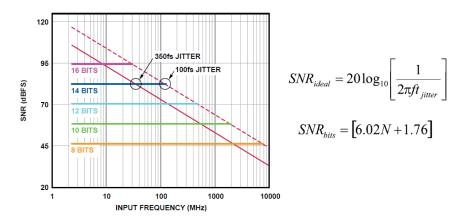

Figure 2.14: Effect of jitter and signal frequency on SNR and resolution of ADCs [58].

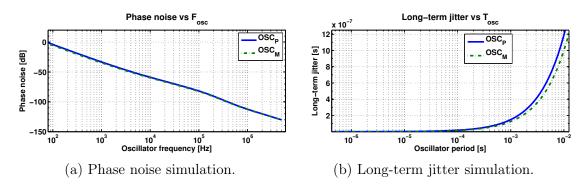

Finally, quantization noise and jitter (i.e. timing error as a result of phase noise from sampling of the analog signal) play crucial roles in the performance of biomedical readout circuits. Both noise sources are introduced within the ADC block, before sending the digitized biosignal to the DSP block of the readout circuit for further processing as depicted in Figure 2.13. Quantization noise is inevitable in any digital system because it is as a result of rounding up of the sampled data sequence to the nearest least significant bit (LSB) during conversion of the continuous signal to discretized form. However, the conversion error caused as a result of quantization can be minimized by avoiding unnecessarily high ADC resolution and optimizing the ADC to have very low jitter which in turn improves the signal-to-noise ratio [58]. In addition, lowering the jitter of the ADC, increases the resolution of the ADC for a given signal frequency as illustrated in Figure 2.14. On the other hand, increasing the signal frequency, lowers the resolution of the ADC for a constant jitter of an ADC [58]. Hence, reduction of phase noise and errors caused by jitter in the sampling clock and other sources such as jitter due to supply noise (i.e. variations in supply voltage) and substrate noise, is vital in the design of ADCs especially in biomedical applications given the low frequency range of biosignals [59]. Thus, an optimum resolution must be defined for the ADC that yields reasonable benefits with respect to the noise performance of biomedical readout circuits.

# 3 Proposed design of the Dopamine Oxidation Readout Sensor Interface

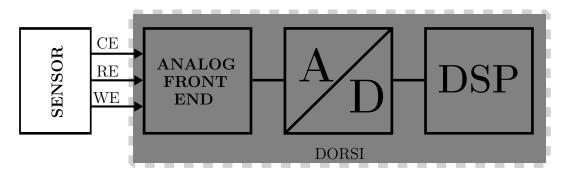

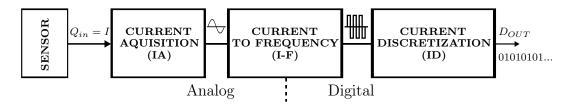

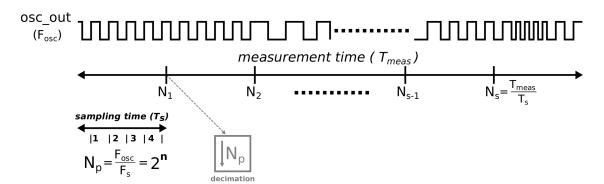

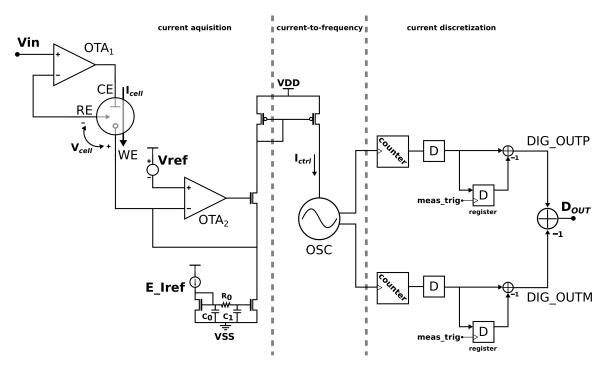

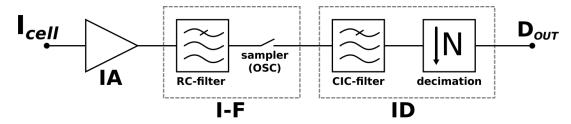

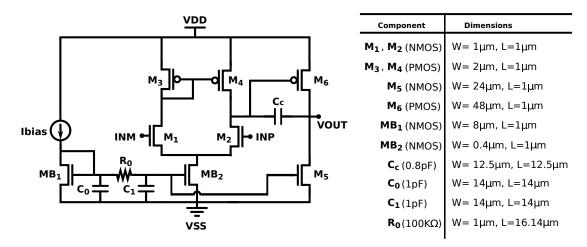

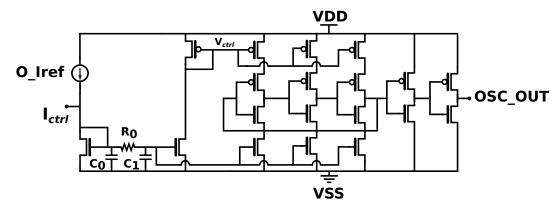

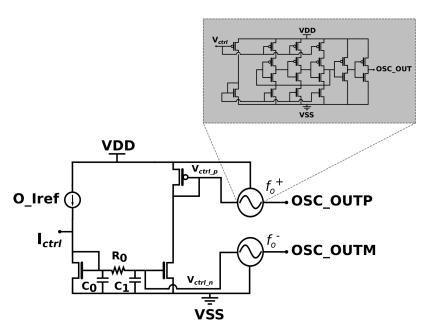

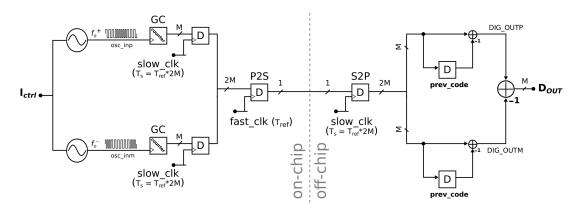

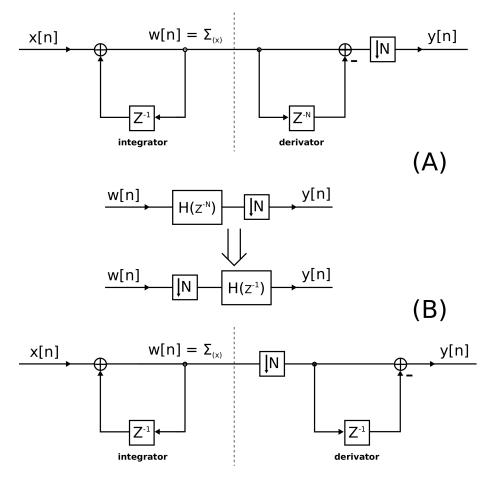

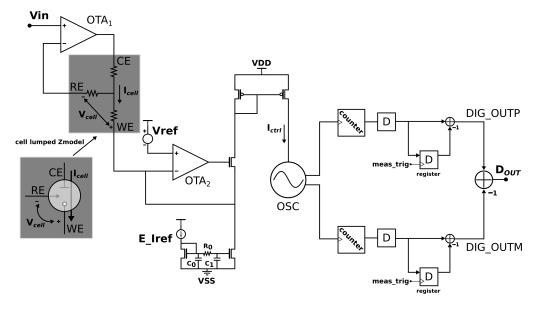

This chapter describes the design and implementation of the proposed readout sensor interface micro-system for detection of oxidation and reduction of dopamine. The proposed micro-system represents the sensor interface electronics (SIE) unit that can be integrated to an extensive and more elaborate readout system as presented in Figure 2.12 for dopamine monitoring. Hence, the scope of this thesis is based on the design of the SIE unit which is referred to as dopamine oxidation readout sensor interface (DORSI) throughout this document. DORSI is designed to interface with a biosensor which operates based on electrochemical transduction principle and three-electrode electrochemical cell structure as depicted in Figure 3.1. The structure of DORSI is based on three main blocks namely analog front-end (AFE), analog-to-digital converter (A/D) and digital system processing (DSP) as illustrated in Figure 3.1. The design of DORSI micro-system is based on mixed-signal front-end architecture where analog and digital techniques are employed in the processing of the measured redox current signals flowing between the working electrode (WE) and counter electrode (CE).

Figure 3.1: System block diagram.

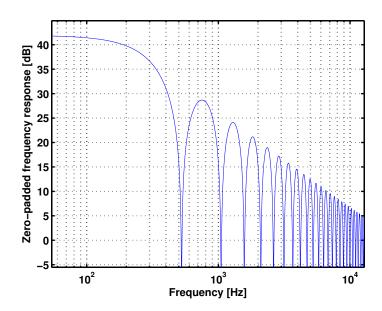

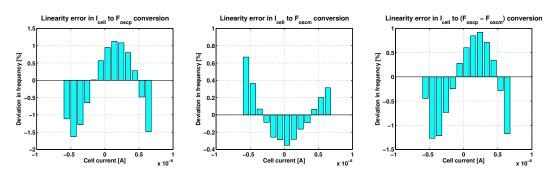

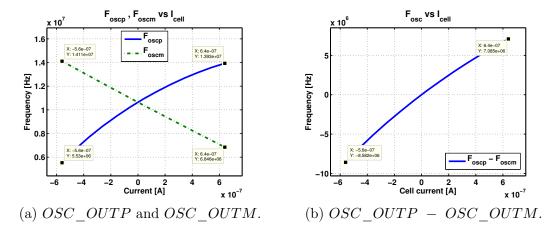

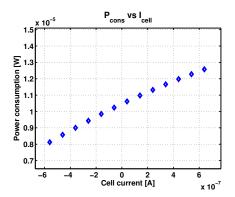

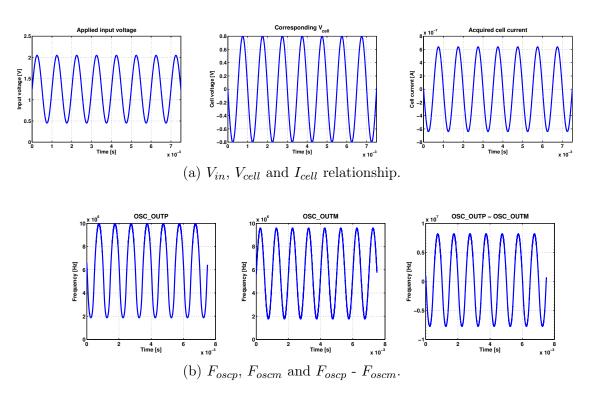

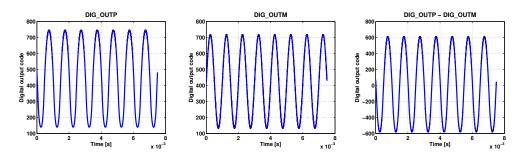

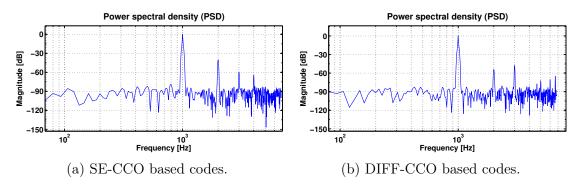

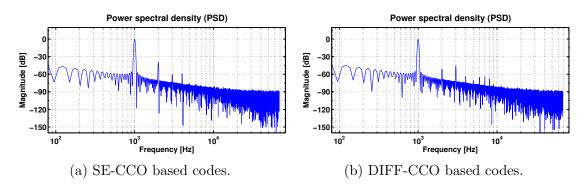

As described earlier in section 2.3.2, the main challenge in the design of sensor interface electronics is the presence of various noise sources at different stages in the biosignal processing that contribute to the overall performance of the readout circuit. Likewise, the design of DORSI also faces similar challenges and limitations set by the biosensor which influenced the design requirements and techniques used to achieve the required specifications for obtaining a functional readout system with good signal quality. Hence, the use of mixed-signal architecture resulted in early digitalization of the acquired current signal and implementation of digital averaging filtering technique for reduction of noise and conversion error. In addition, single-ended and differential conversion approaches were implemented for comparing their effect on conversion gain, sensitivity and noise reduction. The next chapter 4 presents post-layout simulation results of the whole readout system based on measured data from novel carbon-based electrodes that is used for modelling the dopamine sensor electrical characteristics. Finally, the layout implementation of the main blocks of DORSI are presented in the appendix B of this document.

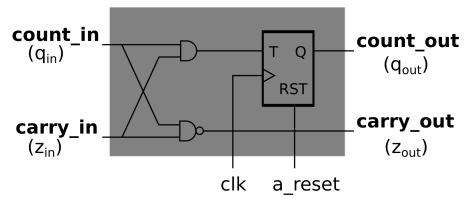

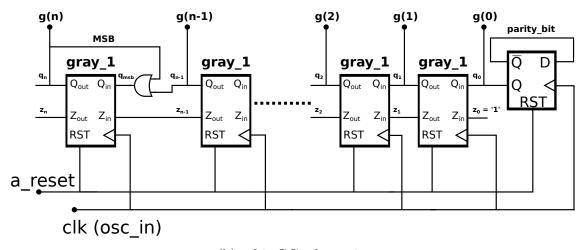

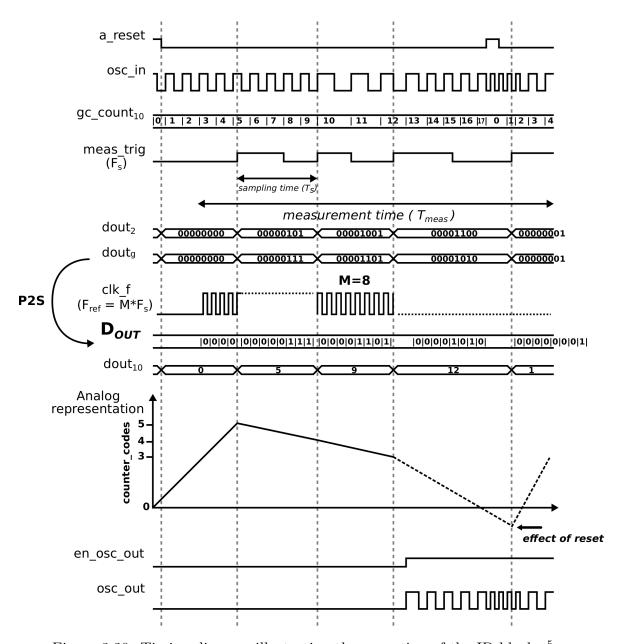

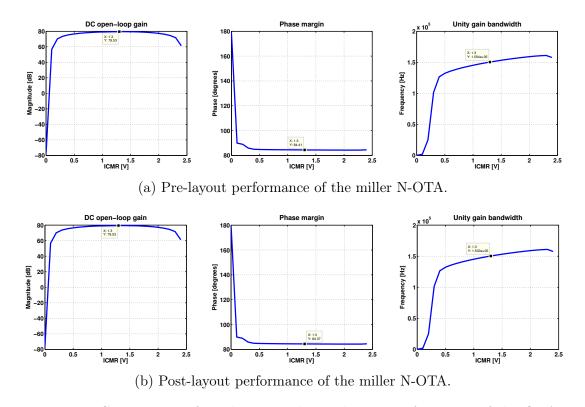

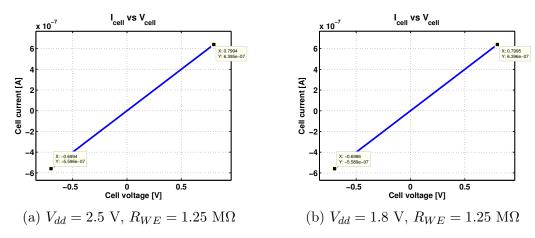

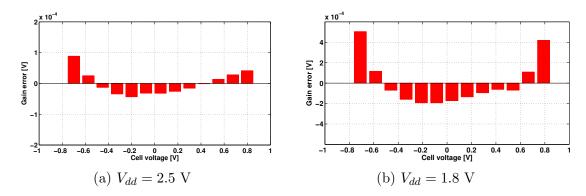

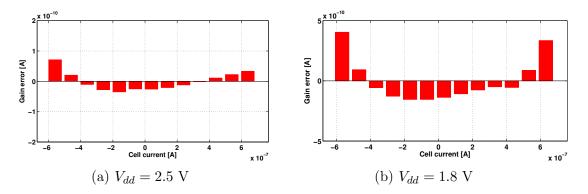

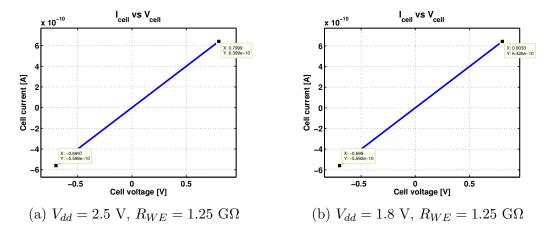

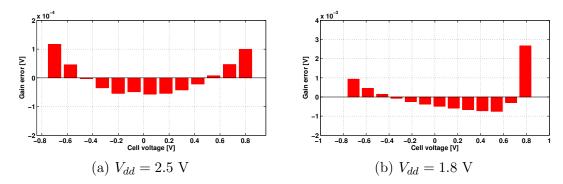

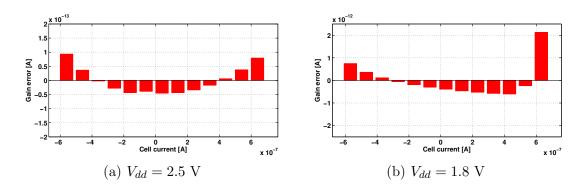

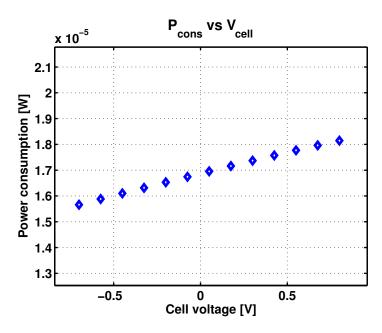

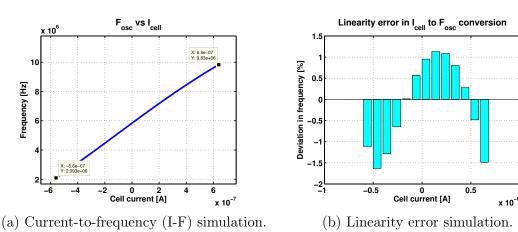

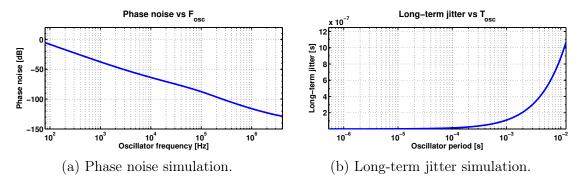

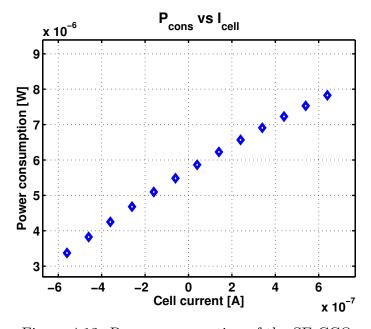

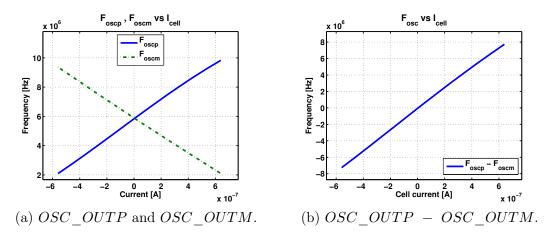

# 3.1 Design requirements