Aalto University School of Science Degree Programme in Computer Science and Engineering

Ivan Raul Lopez Guadarrama

# Virtual Platform for the ARM Cortex-M0 Processor

Master's Thesis

Espoo, February 20, 2015

| Supervisors: | Professor Heikki Saikkonen, Aalto University School of<br>Science<br>Professor Reinder J. Bril, Eindhoven University of<br>Technology |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------|

| Instructors: | Vesa Hirvisalo, D.Sc. (Tech.).<br>Pekka Nikander, Ph.D.                                                                               |

In memory of María del Carmen

| Aalto University<br>School of Science                |                   | ABSTRACT (       | OF THE MASTER'S THESIS |

|------------------------------------------------------|-------------------|------------------|------------------------|

| Degree Programme in Computer Science and Engineering |                   |                  |                        |

| Author: Ivan Raul Lopez Guad                         | larrama           |                  |                        |

| Title: Virtual Platform for the .                    | ARM Cortex-M      | 0 Processor      |                        |

| Number of pages: vii + 68                            | Date: 20/Feb/2015 |                  | Language: English      |

| Professorship: Software Systems                      |                   | Code: T-106      |                        |

| Supervisors: Professor Heikki                        | Saikkonen, Prof   | essor Reinder J. | Bril                   |

| Instructors: Vesa Hirvisalo (D.                      | Sc. Tech.), Pekk  | a Nikander (Ph.  | D.)                    |

| Abstract:                                            |                   |                  |                        |

AUSUACI.

Modern microcontrollers provide a 32 bit core, a rich set of peripherals and on chip memories. However, due to the recent slowing down of the exponential increase in RAM performance, memory has become the main cost factor of low-end MCUs. For enabling the IoT evolution, and until a technological breakthrough improves memory performance, inexpensive sensing and actuation nodes will be heavily memory constrained.

Ell-i Open Source Co-operative developed an Open Source Hardware prototype PoE enabled IoT node, which targets to use the smallest ARM Cortex-M0 MCU, with a maximum of 4kB of RAM. Although multiple Open Source Real-Time Operating Systems were available, none of them satisfied the requirements. These included fitting into the memory footprint without minimal configuration, properly handling of the hardware interrupt controller, or adequate alignment with the company's business plan.

This work provides a memory constrained scheduler that rivals in performance and memory footprint the evaluated Open Source RTOSs alternatives. Additionally, it provides safety features not present in other systems, while providing the necessary alignment to Ell-i Co-Operative. A comprehensive evaluation of popular RTOSs for the Cortex-M0 architecture is included, as it allows the benchmarking of the developed system.

Keywords: ARM, Cortex-M0, Real Time, voluntary preemption, context switch, semaphore, RTOS, PoE, IoT, Open Source, Open Source Hardware, Business Models

# Acknowledgements

I would like to be thankful with my instructors for their contributions to this project; Vesa Hirvisalo for his guidance in academic methods as well as writing, and Pekka Nikander for providing theoretical and technical assistance, suggested literature, and even personal help in times of need. Additionally, I would like to offer my gratitude to Heikki Saikkonen for taking the time to supervise this work, and to Reinder J. Bril for providing the initial ideas that seeded the topic selection.

Furthermore, I want to thank all the members of Ell-I Co-Operative, for giving me time to work on my thesis, even when there were more important things to do. Special thanks are directed to Teemu, Eero, Lari, Otso, and Asif.

Last, but not least, I want to thank my family and girlfriend for providing the support I needed, as well as times of peace and joy that allowed me to refocus and continue writing. This includes, but is not limited to: Paola, Rebeca, Raul and Katya. Finally, I want to send special thanks to my friends Simon and Vlad, for their resistance to my everyday complaints and unconditional support.

Espoo, February 20, 2015.

Ivan Raul Lopez Guadarrama

# Contents

| Acknowledgementsiii                            |

|------------------------------------------------|

| Contentsv                                      |

| Acronyms vii                                   |

| Chapter 1 - Introduction                       |

| 1.1 Problem1                                   |

| 1.2 Contributions                              |

| 1.3 Thesis Structure2                          |

| Chapter 2 - An Open Source Hardware Ecosystem4 |

| 2.1 Context of Open Source Projects4           |

| Open Source Software4                          |

| Open Source Hardware4                          |

| Open Source Hardware Business Models6          |

| 2.2 Ell-i business model                       |

| Ecosystem creation9                            |

| Chapter 3 - Scheduling in Real Time Systems    |

| 3.1 Beginnings and Development12               |

| Limited Preemption14                           |

| Context Switch Improvement15                   |

| 3.2 Synchronization in Real Time Systems16     |

| Priority Inheritance                           |

| Priority Ceiling and Stack Resource Policy17   |

| Chapter 4 – Ell-i Development Environment      |

| 4.1 Arduino Ecosystem                          |

| Background18                                   |

| Programming Model19                            |

| 4.2 Ell-duino Development Board22              |

| ARM Cortex-M0 Processor22                      |

| PoE and CoAP Support23                         |

| Arduino Compatibility                          |

| 4.3 Provided Runtime25                         |

| Peripheral Initialisation                      |

| Context Switch Prototype26                     |

| 4.4 Other (Open Source) RTOS28                 |

| Previously Published Benchmarks29              |

| Chapter 5 - Memory Constrained Scheduler                      | 31 |

|---------------------------------------------------------------|----|

| 5.1 System Architecture                                       | 31 |

| System Exceptions and Priorities                              |    |

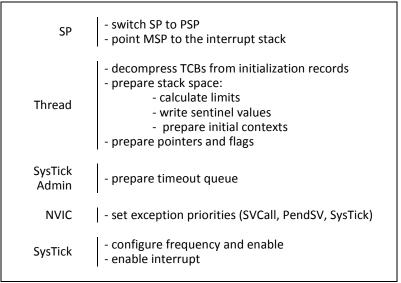

| Initialization                                                |    |

| API                                                           |    |

| 5.2 Scheduler                                                 |    |

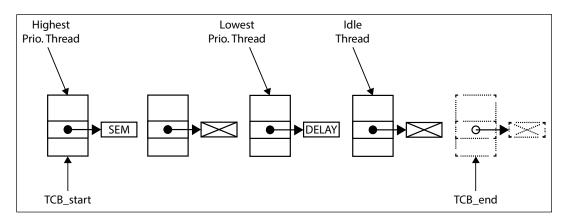

| Data Structures                                               | 34 |

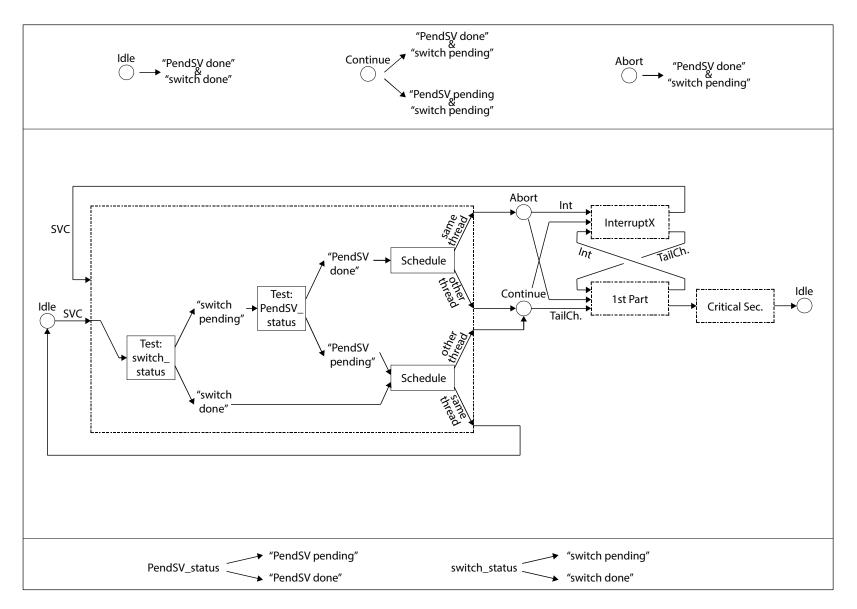

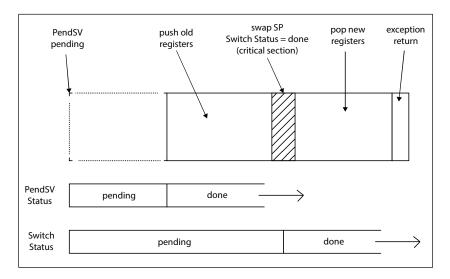

| Context Switch State Space                                    | 35 |

| 5.3 Semaphores                                                | 37 |

| Data Structures                                               |    |

| Blocking Pre-Check                                            |    |

| 5.4 Time Management                                           | 40 |

| Data Structures                                               | 41 |

| Interaction with Scheduler                                    | 42 |

| 5.5 Memory Management                                         | 43 |

| Linker Interaction                                            | 43 |

| Thread Initialisation Records                                 | 43 |

| Decompression Process                                         | 44 |

| Chapter 6 – Evaluation                                        | 46 |

| 6.1 Setting                                                   | 46 |

| 6.2 Procedure and Metrics                                     | 47 |

| Software Testing Framework                                    | 47 |

| Hardware Testing Framework                                    | 48 |

| 6.3 Workload                                                  | 50 |

| 6.4 Results                                                   | 52 |

| 6.5 Discussion                                                | 55 |

| Timing                                                        | 55 |

| Memory                                                        | 57 |

| Chapter 7 - Conclusions and Future Work                       | 59 |

| References                                                    | 61 |

| Appendix A - Measurement of Hardware Exception Handling Times | 68 |

| Direct Measurements                                           | 68 |

| Indirect Measurements                                         | 68 |

|                                                               |    |

# Acronyms

| CAD  | Computer Aided Design                                 |

|------|-------------------------------------------------------|

| FPDS | Fixed Priority Scheduling with Deferred Preemption    |

| FPNS | Fixed Priority Non-Preemptive Scheduling              |

| FPPS | Fixed Priority Preemptive Scheduling                  |

| IoT  | Internet of Things                                    |

| IP   | Intellectual Property                                 |

| M2M  | Machine to Machine                                    |

| MCU  | Microcontroller Unit                                  |

| MPS  | Maintain Power Signature (PoE standard specific term) |

| OSHW | Open Source Hardware                                  |

| OSS  | Open Source Software                                  |

| РСВ  | Printed Circuit Board                                 |

| РСР  | Priority Ceiling Protocol                             |

| PD   | Powered Device (PoE standard specific term)           |

| PIP  | Priority Inheritance Protocol                         |

| РоЕ  | Power over Ethernet                                   |

| RTOS | Real Time Operating System                            |

| SoC  | System on Chip                                        |

| SRP  | Stack Resource Policy                                 |

| ТСВ  | Task Control Block                                    |

# **Chapter 1 - Introduction**

The advance in semiconductor technologies has allowed an exponential improvement of the processing power, memory capacity and other metrics of computing hardware during the last fifty years. This continuous evolution, predicted by Gordon Moore in 1965, is the reason why modern microcontrollers can fit a 32bit processor, a rich set of peripherals, and integrated memories in a very small and cheap package. Additionally, the widespread use of processing cores designed by ARM Holdings in mobile and embedded applications has led to a commoditisation of the low-end MCUs.

This commoditisation process generates an extensive offer of cheap, yet powerful MCUs. Thus, it has been one of the main driving forces behind the Internet of Things (IoT) evolution or the Open Source Hardware movement. However, in recent years the pace of the Moore's law progression has started to slow down. This trend is particularly affecting the memory component of computing systems, making it a bottleneck to the performance of comparatively faster processors, and the main cost factor of microcontrollers and mobile systems.

In order to enable the IoT evolution, the development of inexpensive embedded systems capable of sensing, actuating and communicating in real time is essential. Therefore, as memory is the main pricing element, the software stack targeted for those devices should limit as much as possible the memory usage, while still providing comprehensive networking and sensing capabilities.

Moreover, this thesis is based on the internship work at Ell-i Open Source Co-operative. Ell-i is an Open Source Hardware organisation which targets to provide Power over Ethernet (PoE) enabled nodes as part of the IoT ecosystem. This prototype nodes are planned to be relatively inexpensive by the inclusion of the smallest MCUs from the Cortex-MO family, which are very limited in RAM memory.

## **1.1 Problem**

Real Time Operating Systems (RTOSs) for microcontrollers are not new, neither are their Open Source implementations. In fact, Open Source RTOSs have widespread usage due to the performance they provide at zero cost. However, even if there exist a variety of options available for the ARM powered MCUs, this variety diminishes drastically towards the low-end devices. Consequently, none of them fulfilled the specific requirements for driving the Ell-i PoE node prototype, which targets to use the cheapest Cortex-M0 processors, with very limited RAM in the range of 2 - 4 KB. In particular there are three key aspects that none of the available Open Source RTOSs managed to fulfil. Two are technical and the third one is related to the Ell-i business strategy.

The first technical problem is that the majority of systems available are targeted to more powerful processors, and require a 'minimal' configuration to fit on the low-end MCUs. Although some systems have ports to architectures part of the Cortex-M family, only a few are available for the Cortex-M0 processor. Some of the issues with 'minimal' configurations include that the system still provides more functionality than needed, removing functionality is not efficient, or the reduced configuration does not translate into memory savings or performance increase. As a consequence, designers either select a device closer to the high-end, or prefer solutions which obviate threading requirements, if possible.

The second problem is that most Open Source RTOSs are designed to be as generic and platform independent as possible. Although this is generally a benefit, it becomes a problem when some

architectures have peculiarities that challenge the soundness of the software design. In particular, the interrupt system of the ARM Cortex-M provides very low latency at the cost of possible complex hardware events interleaving. This complexity not entirely addressed by the available RTOSs, and generates a latent risk for systems used in hard real-time applications and other mission-critical situations.

The third problem is closely related to the alignment between the scheduling software and the business model of Ell-i. In concrete, two specific requirements were not fulfilled by other Open Source RTOSs. The most critical is the necessity to collectively own the copyright of the software, in order to license it to companies as part of the business strategy. The second requirement is that, as an Open Source Hardware organisation, it is ideal to provide software specially tailored to the designed hardware.

# **1.2 Contributions**

The main contributions of this thesis are related to the design and implementation of a memory constrained scheduler tailored for the Cortex-M0 architecture, with focus on its hardware interrupt controller. The objective is to enable basic threading applications on the low-end MCUs with a maximum 4KB of RAM and very limited Flash. There are three key benefits the developed system provides in comparison with available Open Source RTOS.

First, the implementation provides a very small footprint for both, RAM and Flash. Moreover, it follows a similar strategy as the data-driven peripheral initialisation concept developed at Ell-i, generating a complete solution. Second, the system provides low latency for synchronisation primitives and context switches. This leads to fast performance for Real Time applications which require very limited interference from system interrupts. A key benefit is that there is no 'minimal' configuration, leading to the efficient usage of all the involved resources. The third benefit is the safety derived from the careful analysis of the hardware interrupt system of the Cortex-M0 architecture and the static allocation of all the system level resources at compile time.

An additional contribution regards to the business side of Ell-i: the ownership of the copyright of the developed scheduler. This element is a key factor for the licencing business of Open Source material. Moreover, this thesis represents a detailed documentation of the implemented system, which serves as a reference for further development. It is also important for the strategy to provide Open Source Software as a bundle specifically crafted to highlight the possible use cases of Open Source Hardware.

# **1.3 Thesis Structure**

The rest of this thesis is organised as follows. In the two following chapters, the background of the thesis is discussed. Chapter 2 deals with the business background, locating the current development in the framework of an Open Source Hardware ecosystem. Chapter 3 deepens into the technical details of Real Time Systems as a basis to analyse RTOSs implementations.

Chapter 4 provides insight on the material that served as a basis for the development of this project. This includes a description of the hardware platform used as a target for the software stack, the previously developed peripheral initialisation system from Ell-i, and a discussion of various RTOSs which codebase is available (including Open Source and Proprietary systems). Chapter 5 offers a detailed description of the implemented scheduler, as well as the design rationale behind the selection of particular data structures and interfaces. In particular, section 5.2 offers details of the core scheduling system and serves as a basis for the other sections of this chapter.

Chapter 6 describes the evaluation methodology, provides the results, and offers a discussion based on them. Specifically, the resulting data is presented in section 6.4, while its discussion is located in section 6.5. Finally, Chapter 7 concludes the thesis by revising its contributions, attempts to relate them to a broader problem space, and describes possible directions of future developments.

# **Chapter 2 - An Open Source Hardware Ecosystem**

The purpose of this chapter is to review the literature regarding Open Source Software (OSS) and Open Source Hardware (OSHW). It begins by discussing the history and current state of Open Source projects, both OSS and OSHW. Then, a detailed description of business models for OSHW is presented. Finally, the specific business model of Ell-i is discussed, with particular focus on the ecosystem creation.

# 2.1 Context of Open Source Projects

## **Open Source Software**

The idea of free software is not new. During the beginning of the computer evolution, computers were regarded as research tools and only owned by universities and corporations. At that time, software was shared freely among educational institutions, as the act of programming was paid, not the program itself. When the costs of computers decreased and they became widespread available, programmers started to restrict the rights to their software and charging fees for each copy [1].

The origins of the current use of the "Free Software" can be tracked to 1984 when it was used as a political argument by Richard Stallman [1]. This movement was also the beginning of the Free Software Foundation, the GNU Project, and the GNU General Public License (GPL). Similarly, Eric Raymond popularized the idea of Open Source in his classic article "The Cathedral and the Bazaar" [2]. The importance of the "source code" is particularly relevant, as the openness of the source implies not only free distribution, but the possibility to modify and build upon the provided software.

The Open Source Software (OSS) has proven to benefit multiple components of the IT ecosystems. For the developer group it reduces the costs of the development process and enables a virtually no cost distribution strategy. For business users, it enables the deployment of servers without the OS license fees. In addition, Ubuntu, a variation of the Linux Open Source OS, was regarded as the most secure end user operating system for end users by the UK government [3].

Nevertheless, the OSS trend has not only become politically important, but also has proven to be a profitable business by its own. Red Hat, one of the companies that sells support for their own Linux Open Source OS, reported a revenue of 1.33 billion USD for the 2013 fiscal year [4], and employs more than six thousand people worldwide [5].

## **Open Source Hardware**

The idea of Open Source Hardware (OSHW) can be historically related to the open interfaces in the computer industry. When IBM competed with Apple at the personal computer market, they decided to use off-the-shelf parts instead of internally designed components. The decision was necessary in order to reduce internal costs and handle the very short time to market. As a result, they enabled the first open interface computer platform [6]. In short time, other companies like Dell and Gateway started producing completely compatible IBM PC's.

The availability of the internal details of hardware was at some point necessary for enabling adequate support. An example is found in the Tektronix Oscilloscopes form the 1950's. Some of the devices were very expensive, around half a year salary of an engineer, and had vacuum tubes with very short

lifespan [7]. The necessity for constant changing required the product to be sold together with very detailed service manuals. The documents not only described how to operate the device, but detailed the entire internal functionality, with a bill of materials and schematic diagrams, in order to allow the user to replace parts as needed.

Although the OSHW is based on very similar philosophical roots as OSS, it was not until the reduction of prices of components and the widespread use of Internet services that the first practical projects started to materialize. Nevertheless, the differences with OSS have posed new challenges, some of which still require advances in technology and legislation. The main practical differences between OSHW and OSS have already been drafted by the academic literature. The differences and problems detailed below are based on the analysis of Locke [7], Acosta [8], and Rubow [9].

One practical difference regards distribution. Software is a non-tangible asset that can be distributed at practically no cost through Internet. In contrast, hardware has inherent costs of distribution and storage. Another problem is updatability. While software can be automatically updated and with no cost, hardware requires the substitution of sections, parts, or even the whole unit, which is not automatic and definitively not free.

An additional constraint, which is projected to drop rapidly, is the cost of manufacturing and testing equipment. While software requires a relatively inexpensive personal computer, the infrastructure required to manufacturing and testing of electrical and electronic hardware can be very expensive. This factor limits certain processes to be solely available to large companies, excluding in practice the participation of amateur and semi-professional developers. Nevertheless, the prices of this kind of equipment are dropping very rapidly, partially as a consequence of the open hardware trend, which also affects manufacturing and testing hardware.

An additional problem related to the physical existence of OSHW, which is also expected to decline at some point in the future, is the reliance on suppliers. Although many of the passive and simple components are available from multiple suppliers, the more advanced ones, like MCU's and specific peripherals are only provided by one specific manufacturer. As the configuration of the hardware is designed to work with that particular component, substitution requires extensive modification of hardware designs and related software. However, the commoditization led by ARM Holdings has partially diminished the costs of changing MCU manufacturer, at least from the software side, as the common architecture allows partial reuse of existing code and related tools with changes only required on the proprietary peripherals.

While software is essentially the output of text (source code) passed through a compiler, it was not until the maturation of the GCC compiler (first widespread Open Source compiler) that the Open Source trend growth rapidly. This compiler was one of the main enabling factors for the Open Source success. In the same way, hardware is designed used specialized Computer Aided Design (CAD) tools. Currently, the majority of these tools is proprietary and the open source options are not mature enough. Furthermore, the proprietary and most used ones are from competing companies, decreasing considerably compatibility. Although it is possible to "export" the design to open formats, it is not possible to modify the design and returning it to the proprietary format.

Another problem generated by the use of current proprietary CAD tools is the impossibility of automatic merging. While there exist extensive sets of tools for merging and version control for software (Source Code Management), they are all based upon the fact that source code is actually

plain text. However, that trend is also in decrease, and merging of hardware models is expected to be more automated, as the collaboration of teams through internet services is becoming the most frequently and cost efficient solution. Unfortunately, in the hardware design nowadays, merging requires human effort, making the process more costly.

Furthermore, copyright is the legal framework that protects software. Concretely, it can be used to prevent deviations of the terms of the license that would fall into copyright infringement. Unfortunately, the majority of the components of OSHW, such as particular circuit designs or the selection of specific components, is not covered by the protection of copyright [7]. A possible alternative is to protect hardware designs by patent laws. However, it is not as simple as copyright: apart from being expensive and very time consuming, it requires the invention novelty. The problem is that patents were designed for protecting a different kind of intellectual output. In summary, the protection of OSHW is still an open discussion, with multiple prototype license types already present but with no general acceptance.

## **Open Source Hardware Business Models**

The purpose of this section is to review the most prominent business models available for OSHW. Although some of the models described below were initially designed for the software, they are carefully selected as they can also provide channels of revenue for the hardware counterpart. Nevertheless, there are also models which origins and validity are closely related to the specific tangible characteristics of hardware.

#### Support Sellers

First, it is necessary to provide a brief reference to the usage of OSS. Although the Open Source characteristic implies that the software can be modified at will, the reality is that just a few individuals and organizations outside the main developer group actually touch the code and build upon it. In fact, the majority of users only "use" the code, as the technical skills and background required to successfully modify the source code to add functionalities are relatively unique and specific [10].

As a consequence, when an organization which requires a specific change or simply support for the OSS commonly seeks for assistance from the main developers. The main advantage of is a zero cost advertisement and distribution campaign, while support is the main revenue channel. This model has been widely referenced in literature related to Open Source [7, 11, 12], and is probably one of the first successful business strategies built around an open source ecosystem.

The custom development and support for hardware also requires expertise on the fields that the project of the customer encompasses. In fact, the set of abilities required is even more unique, as the core development team should have proficiency in both, hardware and software. The two main kinds of support for open source projects [10] will be discussed in the sections below.

### **Professional Support**

The first kind of strategy that proved profitable consisted of selling professional services, such as customer support and maintenance, for an open source codebase. However, as the workforce behind the service providing corporation is limited, only particular versions (revisions) of the software are

supported. Additionally, the software is only supported with the constraint that the user does not modify to source code. Such modifications commonly lead to violations of the service agreement [10].

## Custom Development and Support

One special case of the support business model is to provide support to the modifications that the client makes to the original code. As discussed earlier, support sellers only provide service to the unmodified and updated versions. However, it is also possible to provide services and support the modifications the client makes to the original codebase. Two notable examples for OSS are Gluecode, later acquired by IBM [13], and Specifix [10].

In the case of hardware, the same kind of personalization can be offered. Instead only supporting the reference designs, tailored services can be provided to generate hardware and software solutions that fit the particular needs of the client. The particularity that hardware requires software to run over it provides an additional layer of customization. Additionally to the proficiency in software and hardware (which is specific and unique), expertise on the field of the client's project is also necessary.

## Brand Licensing

The branding model is based on the ownership of a trademark, and the free distribution of the open source outcomes [11]. In particular, only the products, either software or hardware, generated by the development group can hold the brand name. This brand represents some added value to the customer, either in the form of additional testing phases to ensure quality, increased confidence in the support and extended periods of sustained maintenance, or simply by the expertise represented by the core developer team [12].

However, the revenue generation for an open source company following this strategy is not based solely on the possession of the trademark, but in the selling of this brand qualifier in a fashion similar to franchising. This strategy is particularly effective in the commercialization of OSHW, which manufacturing is relatively expensive and leads to a non-free distribution cost. A branded scheme benefits the manufacturer that buys the brand, as it can charge an additional price to the product, and compete on basis of quality and other attributes.

Additionally, three benefits are presented to the core developer team. First, it obtains revenue for the trademark commercialization. Second, the quality and other attributes of the product can be ensured by the agreement. Third and finally, it is not necessary to produce large quantities of the hardware product in order to generate revenue for the manufacturer, which is particularly important when the company is at its start-up stage as the demand is very low compared to fully established products.

## Core Open (Loss Leaders)

The loss leader business strategy is commonly used by established companies that release a piece of software as open source in order to increase their market share where they have low participation [11, 12]. The classic example of this strategy is the Android OS developed by Google. The target of the development was the revenues that an application market associated with the platform can generate. At the time of development, the market share was completely dominated by Apple and their iOS operating system for smartphones. Nevertheless, the open source distribution strategy proved extremely successful, as Android has more than 80% of the smartphone OS market share by the first

quarter of 2014 [14]. The application for hardware follows the same strategy. In particular, large MCU manufacturing companies could provide OSHW designs that use their own devices.

## Dual License Model

This model is based on the fact that *reciprocal licenses* (which enforce any modification to be distributed with the same license) do not allow additional modifications to be released as closed products. This limitation reduces the possibilities of commercialization, as organizations usually prefer to keep their changes private. Nevertheless, the utilization of OSS and OSHW as a component of closed, private products is possible by the implementation of *academic licenses*, which allow the distribution of modifications in either open or closed approach [10, 15].

However, in order to enable the use of an Open Source project in a closed fashion, the development organization should own the copyright of the material. In order to achieve this, the organization either employs all the developers, or agrees the transfer of rights with the outside developers that modify to the core distribution. As this requires additional effort, it can directly be monetized. In other words, the client pays for the right to choose what license is more adequate for their purpose [10].

## Bulk Discount Model

The bulk discount model is based on the reduced costs that economies of scale provide when a manufacturing process is increased in numbers. As a consequence, this model only valid to OSHW. However, during the initial phase of most OSHW projects, the quantities required for the testing prototypes or initial demands are too small in comparison with the ones that benefit from economies of scale. Nevertheless, this effect can be reduced by the addition of an exclusivity or branding model. Consequently, manufacturers can afford some initial loss in exchange of possible future profits and lack of competition. This model is mainly used by the designers of the Raspberry Pi, which have an exclusive distribution agreement with RS and Farnell [16].

## 2.2 Ell-i business model

The strategy from Ell-i focuses on designing inexpensive Power over Ethernet (PoE) development boards compatible with the Arduino ecosystem. The use of ARM 32 bit architecture in conjunction with simple Ethernet controllers and carefully crafted PoE components allows the use of only one MCU device per board.

The computing power of the Cortex-MO architecture allows the integration of the network stack into the main MCU, which reduces the additional cost of Ethernet controllers with integrated network stack, or the use of an additional MCU to handle the networking services. Additionally, the integration of PoE to the board eliminates the need of external components, such as the proprietary devices used for the PoE support in the Arduino platform [17, 18].

Ell-i proposes the co-operative organizational model and the egalitarian ownership as a form of innovation in the electronics industry and the OSHW community. The co-operative concept provides benefits from both, external and internal perspectives. From the external side, it is a strategy to cope with the negative forces that the world economic policies can exert over companies [19]. From the internal side, it is a channel to distribute responsibility more evenly across members, compared to other organizational models.

In particular, the application of egalitarian ownership increases further the uniformity of responsibility distribution, as employees own equal parts of the company. This leads to important benefits, such as decisions being taken in a democratic fashion, increase in the involvement on strategic planning, and a very flat hierarchical relationship among members [20]. This kind of ownership is also positive to the external ecosystem, as responsibility can extend beyond the boundaries of the organization and spread among the community, which is ideal for an open source project.

#### **Ecosystem creation**

As discussed earlier, the co-operative model with egalitarian ownership is also innovative for the Open Source ecosystem. The hierarchical structure among OSS teams can be quite challenging, in particular for new developers. Although the hierarchy is more dynamic when compared to proprietary projects [7], it still requires considerable effort. As an example, new developers for the Linux kernel are expected to work at least two years before receiving committer status [10]. As a consequence, Ell-i organizational structure is very attractive for new developers, which benefit from a less steep start and are able to participate in organizational decisions as soon as they become members. For the cooperative point of view, a fast community growth in comparison to more hierarchical projects is a very important differentiator, mainly during the start-up phase.

As in any other Open Source project, the identification of the reasons why developers participate without economic remuneration is of high importance. In general, the revised literature groups the motivating factors between internal and external. From the internal side, the most cited motivators are altruism and satisfaction of psychological needs. From the external ones, the most commonly referred are: reputation or prestige, access to the knowledge base and building of skills, and satisfaction of specific personal needs that the Open Source project solves.

Altruism is regarded as the most obvious internal motivation [21, 22, 23]. It is simply translated in the gratification of sharing a solution for a complex problem to anyone who might need it. In addition, the satisfaction of diverse psychological needs (equivalent to the upper Maslow needs [24]), is referred in multiple forms, such as intellectual gratification and creativity [7], intrinsic motivation and community identification [22], or simply as psychological needs [23]. In particular, Open Source projects provide a level of liberty that is hardly available for developers working inside corporations with hard structures.

Reputation is the most important external factor, as it provides present and future opportunities for personal career of the developers. It is referred as reputation [7, 21, 23], prestige [7], or peer recognition and self-marketing [22]. The access to the knowledge base and the acquisition of new skills are another important motivations for developers. It is referred as access to knowledge [21] or development of human capital [22]. In particular, Open Source projects give opportunities to students to participate in real life projects, which would be very complicated in a normal organization. Finally, the solution for a personal problem of the developer can be a strong motivation, mainly for the first movers of new projects [22].

The interaction between these motivating factors is also relevant for the general performance of the participating developers. In general, external motivations have more weight on the decision of participating or continuing in an open source project. However, students and hobbyists are a special case, mainly driven by internal motivations [22]. Regarding internal motivations, the effort intensity

of developers is commonly strengthened by the satisfaction of psychological needs, mainly autonomy, and decreased by the altruistic behaviour. Apparently, the enjoyment of sharing knowledge distracts the participant from reaching specific goals and providing significant results [23].

# **Chapter 3 - Scheduling in Real Time Systems**

As the literature regarding real time systems scheduling is extensive, it would be out of the scope of this literature analysis to target all its extent. For this reason, this literature review will be limited to the fixed priority preemptive scheduling (FPPS) upon a single processor, its evolution and selected topics of current development. However, it is relevant to briefly describe the most important topics that real time scheduling covers nowadays. As multiple variables can be selected to divide and classify real time scheduling algorithms and applications, the most relevant ones are described below.

First, the algorithms can be classified based on the stage at which calculations of the scheduling decisions are done. In that sense, algorithms can be classified as either static or dynamic. From one hand, static algorithms set the scheduling decisions in advance, require previous knowledge of the characteristics of the tasks, and result in little runtime overhead. Additionally, if the calculations of the scheduling sequence are done before the running the system, the static algorithm is also classified as offline [25]. From the other hand, dynamic algorithms take decisions during runtime, leading to more adaptable systems able to handle unexpected levels of activity. As a consequence, they are suitable for systems that include with soft deadlines, or situations where a processing upper bound cannot be calculated.

Second, scheduling algorithms can be classified by the restrictions to preemption that they enforce. From one side, preepmtive algorithms allow tasks to be halted at any point in time, and continue at a later moment without affecting the behaviour and correctness of their operation. The only difference is that the total execution time is extended. From the other side, non-preemptive algorithms treat tasks as continuous processing sections that cannot be stopped once they are started. This kind of behaviour offers a solution to mutual exclusive operations in concurrency situations, and is closely related to blocking.

An additional type of algorithms, referred as hybrid, or of limited preemption [25], present a behaviour between the fully preemptive and the non-preemptive schemes. This strategy allows tasks to execute for a short extra time before they are suspended. The systems that implement limited preemption use preemptive behaviour as a general policy, but treat special sections of execution as non-preemptable. In case a task is requested to be halted at this sections, the preemption is deferred until the atomic section is completed. For this reason, the algorithms are also called of deferred preemption.

Third, scheduling mechanisms are classified by the level of interaction between tasks they allow. The simplest case treats all tasks as independent entities, without precedence relationships or resource sharing constraints. Unfortunately, this case is greatly simplified to be useful for practical system. The opposite case, closer to reality, treats tasks as highly interrelated entities. The extended analysis of the interaction between tasks by synchronization primitives will be detailed on section 3.2 Synchronization in Real Time Systems

Fourth, the set of tasks can contain either only periodic processes, or a mixture of periodic and aperiodic requirements. In general, aperiodic or non-periodic are terms used to define any process that do not match with the fixed period, bounded computation time, hard deadline scheme. The analysis of the strictly periodic case was the seminal work of the fixed priority scheduling theory. However, it has been extended by subsequent work in to encompass more general cases like soft deadlines, sporadic task arrival, or highly variable execution time tasks.

Fifth, algorithms can be further classified by their ability to schedule tasks to more than one processor. In general, the extension of algorithms from the uniprocessor case to a multiprocessor architecture leads to counter intuitive, suboptimal results. In fact, the problem of optimally scheduling on multiple processor is NP-hard, as meeting low latencies and balanced utilization exceedingly challenging [25]. As a consequence, the multiprocessor case usually needs to be simplified in order to enable the use of uniprocessor techniques, which leads to suboptimal results.

# **3.1 Beginnings and Development**

- 1. All tasks are periodic

- 2. All tasks have a deadline equal to their period

- 3. All tasks are independent (no shared resources or precedence relationships)

- 4. All tasks have fixed computation time, or at least, a fixed upper bound

- 5. A task cannot suspend itself

- 6. All tasks are released at the beginning of their period

- 7. All overheads are ignored, and assumed to be zero

- 8. A critical instant exists

- 9. All tasks are fully preemptive

- 10. Just one processor is available

Table 1. Constraints of the Liu and Layland model

The seminal work for the evolution of FPPS theory was the 1973 article from Liu and Layland that elaborated a polynomial feasibility test for the rate-monotonic scheduling algorithm [26]. From that point onwards, the constraints posed by this work (listed in Table 1) were steadily removed by subsequent research. Consequently, new directions and applications emerged from the field of real time scheduling. The most relevant trends of evolution are described below.

The first trend is related with the feasibility

analysis. In general, new methods were devised to allow relaxation in the constraints imposed by the model of Liu and Layland [26]. Initial approaches, during the beginnings of the 80's, were based on the calculation of the Least Common Multiple (LCM) of the periods of tasks. However, this approach became inefficient even for small sets, preventing extension and applicability [27]. As a result, response time analysis became the preferred tool for the analysis of rate-monotonic scheduling.

One consequence of advancing the response time theory was that the priorities were no longer restricted to the rate-monotonic scheme to allow feasibility analysis. The only limitation was that the priorities of tasks should remain constant during runtime (static). Another consequence was the removal of the deadlines equal to period constraint, which resulted in a framework that included valid analysis for deadlines less than or greater than periods [26, 27]. This extension provided the foundations for the deadline-monotonic scheduling algorithm, which is closely related to the rate-monotonic one. The third result was the partial relaxation of the critical instant requirement, allowing arbitrary phasing. In general, the critical instant analysis leads to pessimistic results when applied to a set with arbitrary offsets.

Although the response time analysis is useful for the offline analysis of systems, computational efficient tests are still preferred for the evaluation during runtime. One of the recent advances is the Hyperbolic Bound test [28] for the rate-monotonic priority assignment. This test "improves" the feasibility of the original Liu and Layland test, while keeping polynomial complexity. However, both tests are necessary but not sufficient, as some task sets are still schedulable even if they fail to satisfy the schedulability bounds.

The second trend is related with the interaction between tasks and the subsequent relaxation of the independence constraint. However, these topics will be treated in detail in section 3.2 Synchronization in Real Time Systems

The third trend deals with the extensions to the model to allow the inclusion of aperiodic tasks. As briefly discussed earlier, aperiodic tasks do not fit the classical periodic model, including cases with soft deadlines, significantly varying inter arrival time, or significantly varying computation time [29]. The initial and simplest approach is to allocate these tasks with lower priority with respect to the hard deadline set, effectively relying them to the background. However this strategy greatly increases latency. As a solution, more advanced approaches were devised to improve response time (quality of service) of soft deadline tasks without affecting the hard time constraints.

One of the first approaches was to use a Polling server, which behaves like a periodic task and is usually located at the highest priority level. This design approach consisted on extending the capacity of this server to the maximum possible, such that the set is still schedulable. However, multiple drawbacks emerged, such as wasting high priority capacity (in the case that no soft processes were available at the time), and long response times when capacity was depleted previous to an aperiodic request.

The drawbacks of the polling server were addressed by a set of algorithms known as "bandwidth preserving", which include the Priority Exchange server, the Deferrable server, and the Sporadic server. They allow the conservation of processing time even when no aperiodic task workload is available. However, they easily degrade and provide the same performance as the Polling server. As a consequence, another family of algorithms was designed to recover the unused capacity left by the hard deadline tasks.

The most prominent of this family is the Slack Stealing algorithm. It is optimal in the sense that it minimizes the response time of soft tasks amongst all algorithms that that meet the required hard deadlines [26, 27]. However, the limitations that preclude it widespread application include the calculation of the LCM of the task set. This only allows the use of periodic tasks without jitter, as well as only being feasible in practice for sets with small LCM.

In general, an open question remains of finding ways of improving system utility by using the spare capacity released by multiple factors, which include:

- Tasks completing in less than their worst case execution time

- Sporadic tasks not arriving at their maximum rate

- Periodic tasks not arriving at their worst case, critical instant, phasing

The fourth trend is related to the handling of transient overloads and adaptability to unexpected conditions. The main reason for this situations is that, in some cases, the calculation of the worst case execution time might be inaccurate or simply impossible [29]. Just as an example, an overload of a system based on the rate-monotonic algorithm will cause tasks with longer periods to miss their deadlines. However, this behaviour might be problematic, as the importance of a tasks could be not directly related to its priority. In general, the feasibility analysis with pessimistic assumptions, or the assignment of high criticality to certain set of tasks are valid alternatives to handle transient overloads.

The fifth trend discusses the simplifications and related considerations applied porting real time systems to either software or hardware. In general, the constraint of zero overhead is not valid on

implemented systems, as the kernel operations need to be accounted. These operations, such as time progress handling (in either event driven or tick driven systems) or context switch overheads impose additional delays which deviate from the ideal operation. Further details on strategies to reduce this overheads are presented in the Context Switch Improvement section.

This section has briefly described the last decades of evolution of the fixed priority scheduling theory. As some of the topics are closely related to this dissertation, a more detailed and updated discussion will be presented in further sections. In concrete, two particular topics will be analysed in the next sections, as they are tightly linked to the software development of the main contribution of this dissertation.

## **Limited Preemption**

As briefly explained earlier, limited preemption systems present a behaviour in the middle of the space stretched by fixed priority preemptive scheduling (FPPS) and fixed priority non-preemptive scheduling (FPNS). This kind of systems, and their analysis, are important as implementations of synchronization primitives and other resource sharing concepts rely on executing of procedures without the interference from other tasks. This behaviour is commonly referred as atomic. From multiple strategies available in the literature, this section focuses on two different approaches to the problem of providing a trade-off between FPPS and FPNS.

The first related strategy is based on a dual priority system that schedules tasks based on their classic priority, and later elevates their priority to the "priority threshold" upon execution. This strategy for assigning priorities allows to control the "preemptability" of tasks, as only procedures with higher priority than the priority threshold are able to suspend the running task [30]. This model is equivalent to the normal FPPS when the priority threshold and the classic priority are the same. Equivalently, when the priority threshold is set to the highest priority level, this model behaves as a system based on FPNS.

The schedulability analysis for this model is an extension of the framework available for FPPS and FPNS, which were briefly discussed in previous sections. This model is proven optimal in the sense that, if a set of tasks is schedulable by either FPPS or FPNS, it will also be schedulable by the priority threshold algorithm. In fact, it improves schedulability, as certain sets of tasks are only schedulable by this method [30]. Additionally, the model is fully extended to allow the integration of polling and sporadic servers to the analysis without constraints in the validity of the results.

However, finding of the optimal "priority threshold" values based on a given set of fixed priorities is non-trivial. Additionally, the size of the search space for obtaining the optimal set of fixed priorities and preemption thresholds from a set of tasks requires heuristic approaches, which preclude the usage for online scheduling algorithms. Nevertheless, if the priorities are calculated offline, no runtime overhead is added to the system. Furthermore, this schedulability system leads to less than or equal number of context switches when compared to FPPS [30]. This property effectively improves performance and decreases temporal interference from the kernel to the user tasks.

Another approach to the problem of limited preemption is to represent each task as a series of sub jobs that are non-preemptable. In other words, preemption for a particular task is only possible at certain well defined points. This kind of scheduling, formally known as fixed priority scheduling with

deferred preemption (FPDS), provides multiple advantages. Such benefits include the reduction of the cost associated with arbitrary preemption, or the obviation of resource access protocols [31].

Although this kind of algorithms were proposed since the 90's, the maturity of the response time analysis was not sufficient to provide a correct worst case scheduling results. The correct solution arises from the use of a continuous scheduling model rather than a discrete one, as well as the distinction that the worst case response time is a supremum rather than a maximum for all tasks except the lowest priority one [31]. This novel analysis proves all precedent analysis to be either pessimistic or optimistic. In fact, the analysis for FPDS can be used for FPNS (which is considered a subcase), leading to situations where the worst caser response time is not present on the first instance of the task (which was a common assumption in the analysis of real time networks, such as CAN [32]).

Returning briefly to the subject of costs related to preemption, is important to distinguish between *arbitrary* and *voluntary* preemption. The term *voluntary* preemption was first used during the beginnings of the 90's to describe the points at which a program scheduled under FPDS is allowed to be halted [33]. In particular, this technique allows the reduction of the overhead cost related to context switching in comparison with *arbitrary* preemption. As preemption places can be selected by the user, they are chosen where the context to be saved is minimum. In practice, these points can be locations that avoid pipeline flushes, prevent the interruption of multicycle instructions, or reduce the number of registers that need to be saved (for example, obviating the necessity of saving the state of any coprocessor in architectures that include one).

#### **Context Switch Improvement**

As described on the previous section, the overhead generated by the context switch can be reduced by carefully selecting the processor conditions and memory elements that need to be saved. As cache memory is one of the main strategies to improve average latencies of modern processors, it is common that context switch improving techniques target it. In particular, they focus on strategies that prevent cache misses and their side effects, such as pipeline flushing [34]. However, as the target processor architecture for this work is not cache-enabled, these strategies are considered to be out of the scope of this review.

One effective strategy is to reduce the set of registers that need to be saved by locating instructions where the registers that need to be saved is minimum. These places, called *fast context switch points*, emerge from an analysis of register properties such as liveness [35]. In general, registers in a processor can be distinguished between user allocable registers and system registers. The latter always need to be saved, as they contain data related to the internal processor state, such as the stack pointer, the program counter, or the link register. In turn, the user allocable registers only require to be saved in case they are *live* at the time of preemption. A register is considered to be *live* in case it contains data that will be used in the future, and is considered to be *dead* in any other case.

The process of calling functions within the code provides additional insight about the liveness of registers. In general, the hybrid caller convention is used to distinguish the program section that has the responsibility of saving registers, either the caller function or the callee function. From one hand, caller-save registers are scratch registers that should be saved and restored if they are live across a function call. From the other hand, callee-save registers are non-scratch registers that are saved and restored if they are used within the function. As non-scratch registers not used within a function need

interprocedural analysis to determine if they are live, a *fast context switch point* is defined as a program section where no scratch registers are live [35]. Additionally, the ARM processor used in this work follows the same convention for caller / callee saved registers [36].

The back-end of a compiler can be optimized to generate more locations for fast context switch in a method called register remapping. This technique reorganizes the use of registers without decreasing the overall performance, by mapping scratch registers to non-scratch registers that are not used within the live range of the scratch register [35]. A similar approach optimizes a compiler to minimize the context size, and then propagates this information back to a statically generated OS. This OS then generates special code that is able to context switch these sets of variable number of registers [37].

# **3.2 Synchronization in Real Time Systems**

The roots of the synchronization theory can be attributed to Edsger W. Dijkstra. During the 60's, he conceived the idea of the semaphore and made the special distinction for the mutex, which is a special binary semaphore targeted to solve the mutual exclusion problem [38]. Since then, the semaphore concept has found extended applicability in the design of OS and the implementation of real time systems. However, the usage of semaphores without special cautions frequently leads to problematic situations, such as deadlocks when accessing multiple resources, or cases of priority inversion which violate the basic premises of any priority based system.

As a consequence, synchronization protocols have been designed to prevent the catastrophic consequences that hard real time systems failures can lead to. These protocols are a set of implementation guidelines as well as extensions to the schedulability analyses. Three of the most widely used protocols will be described in the text below.

## **Priority Inheritance**

The Priority Inheritance Protocol (PIP) consist of dynamically adjusting the priority of a task holding a resource to the highest priority of any other task waiting for that resource, as long as this priority is higher than the original one. Upon release of the resource, the priority of the task is restored to its original value [39]. As a consequence, this protocol solves the problem of the priority inversion. Additionally, it is important to highlight that the priority elevation occurs when the resource is accessed by the higher priority thread.

The Priority Inheritance scheme is widely used in RTOS's, as its implementation is transparent and straightforward. However, this protocol has multiple drawbacks. First, it does not prevents deadlock. Second, chained blocking is still possible, although it is limited. Third, the calculation of the maximum blocking time for schedulability analysis is relatively complex, which prevents its usage for online scheduling decisions.

Due to the transparency of this protocol, it can be extended to decrease the occurrences of context switches and their related cost. In particular, embedded applications can be analysed during compile time to find the specific order locks will be acquired. This is possible as real time embedded systems are commonly constituted of cyclic threads that acquire resources always in the same order. With that information, the scheduler can prevent the activation (and related context switches) of threads that will block on resources which are not available [40]. This extension does not decrease the original

schedulability or response time of the threads compared with simple PIP. However, in case the locking order is decided at runtime, this extension is not implementable.

## **Priority Ceiling and Stack Resource Policy**

The Priority Ceiling Protocol (PCP) was designed to overcome the problems of the PIP. In particular, it addresses the problems of deadlock formation and chained blocking [39]. This strategy ensures that a task can only execute its critical section when its priority is higher than all the other preempted critical sections. If this is not the case, the task is blocked and inherits its priority to the task that caused the blocking. In order to achieve this behaviour, each resource (mutex) has a value referred as priority ceiling, which is the highest priority of all the tasks that could possibly lock that resource.

A runtime system designed to implement this protocol is aware all the time of the allocated resource  $(r^*)$  that has with the highest priority ceiling on the system  $(p^*)$ . A task is only allowed to enter its critical section in case its priority is higher than the priority  $p^*$ . In any other case, the task is blocked and inherits the priority of the task that holds  $r^*$  (not the priority  $p^*$ ). In case a task generates blocking to multiple tasks without releasing the resource, the priority of those tasks is transitively inherited.

Apart from avoiding deadlock and chained blocking, PCP ensures that a task can be blocked at most by one critical section of a lower priority task. However, this protocol has some disadvantages, such as the necessity of calculating the priority ceiling for each resource (mutex) beforehand, or the generation of *ceiling blocking* [39]. From one hand, the priority ceiling calculation is frequently done during the design phase, which requires constant maintenance and analysis of system schedulability, which prevents its online, dynamic calculation. From the other hand, *ceiling blocking* is a kind of blocking not present on other schemes. However, the usage of the protocol reduces dramatically the worst case blocking time of tasks.

In the same way PIP can be extended for reducing the number context switches, a strategy known as *priority ceiling preemption protocol* extends PCP for the same purpose [41]. In general, the threads need to be analysed, either at compile time or at runtime, for detecting the next resource to be acquired. The scheduler activates tasks not only based on the global ceiling priority, but also on the parameters of the resource that will be immediately locked by the new thread. Additionally, the schedulability is not only maintained, but improved. In particular, the worst case response time of certain tasks can be improved. However, the analysis required at runtime decreases slightly the overall improvement of this protocol extension.

The Stack Resource Policy (SRP) scheme is almost identical to PCP, with the only difference that the blocking is enforced at the time the task is activated and selected to execute (preemption), in comparison with blocking on resource access. As such, this property makes SRP adequate not only for FPPS, but also for algorithms with non-preemptable sections, such as FPDS or FPNP. In general, offers the same advantages of. An additional advantage of SRP is that tasks can share the same stack, as it was designed to enable reduction and control of RAM for constrained automotive applications [42].

# **Chapter 4 – Ell-i Development Environment**

This part of the thesis discusses the material that served as a basis for the development of the scheduling system. First, a brief summary of the Arduino ecosystem is provided, as it was the basis for the development of the Ell-i prototype PoE node. The next part focuses on this node, the Ell-duino development board. The following sections discuss the software basis, which includes the Arduino compatible Ell-i Runtime, and the publicly available code from Open Source and proprietary RTOSs.

## 4.1 Arduino Ecosystem

## Background

The Arduino project focuses on providing to users without technical expertise related to electronics (mainly hobbyists, students, designers and artists) a platform of inexpensive devices capable of interacting with their surroundings [43]. It started as a project for providing students with cheap and accessible developing boards at the Interaction Design Institute Ivrea, in Italy [44]. Although it was originally based on 8 bit AVR architecture MCU's, the steady decrease in price of 32 bit ARM MCU's leaded to new versions based on the Atmel implementation of the ARM Cortex-M core.

The Arduino boards are supported by an Opens Source, cross-platform, Integrated Development Environment (IDE) written in Java [45]. This IDE is based on the one used by the Processing project [46], which was also targeted to hobbyists and artists. The Arduino IDE also integrates a special library targeted to simplify the access and control of input / output peripherals. This library is based on the Wiring project [47], which was also initiated at the Ivrea Institute, and is also partially based on the Processing project. It is important to highlight the idea behind Processing, which was to allow artists to "sketch" ideas through code [46] (Actually, the idea behind Wiring is just slightly changed to "sketching with hardware" [47])

The Arduino project uses a reciprocal license for the OSHW boards, the Creative Commons Attribution-ShareAlike [48], which enforces that every modification is released with the same license, and gives credit to the original developer. From the IDE and OSS side that interacts with the hardware, the GPL reciprocal license is used for the Java environment and a slightly different LGPL reciprocal license for the MCU libraries [49]. The LGPL library is special as it only enforces reciprocity (release with the same license) on changes made to the open part. Any other component can be licensed according to the requirements of the developer, as long as there is a clear distinction between the open modules and the modules with different license attributes [50].

However, the main revenue channel for this company is based on the commercialization of their trademark. This is the most prominent example of the application of the branding model discussed in the Open Source Hardware Business Models section. Apart from ensuring the quality of the produced boards, which has been a strategic advantage against competition [51], the business model has been very profitable, generating a revenue of more than one million USD by 2010 [52, 53]. In detail, they charge to manufacturers a general license fee, and an additional royalty charge of 10% over the wholesale price [54].

Unfortunately, the evolution of the electronics industry has posed transition problems for the Arduino team. Apart from the fact that ARM owns the largest share in the embedded 32 bit market since the

2000's [55], the general trend points toward the eventual adoption of energy efficient 32 bit processors in the place of 8bit and 16 bit counterparts [56]. In fact, ARM launched the Cortex-M0+ architecture targeting the 8 bit market, commonly driven by low cost and very low power consumption [57].

This trend is particularly problematic for the Arduino project lifetime, since the majority of their sold products and professional expertise is based on the 8 bit AVR architecture. Although they produced the first board based on ARM 32bit architecture (Arduino Due, Cortex-M3) in 2012 [58, 59], and their second (Arduino Zero, Cortex-M0+) in 2014 [60], the transition is far from being complete. Apart from maximum voltage differences that rendered the majority of external shields incompatible with newer boards, the software adaptation is still a work in progress, for both, the Arduino team, and all the third party providers.

The requirements for internet connectivity for IoT applications has generated additional pressure for the Arduino project. Although they have provided extensions (in the form of shields) to their boards to enable wired [17] or wireless [61] Internet connectivity, the overall cost of a board plus a shield is far from optimal. They proposed a board with integrated wired Internet access [18], although the price of this board is almost equivalent to price of the board plus shield packet as of 2014 <sup>1</sup> [62, 63].

As discussed earlier, the lack of expertise on 32 bit architectures is forcing the Arduino team to take design decisions which optimize the time to market, at the cost of a steep increase in the prices for 32bit based devices. Such devices include boards based on newer MCU's, network enabled systems, and Power over Ethernet (PoE) applications. In particular, the choice of Ethernet controllers [17, 18] and WiFi modules [61, 64] with integrated network stacks, or the integration of closed source components for PoE support [17, 18], make evident that the market trends are moving the team out of their locus of expertise.

### **Programming Model**

The Arduino project uses a simplified program template called "sketch". In its most basic form, a sketch is composed of two C-like functions with no arguments or return values: the "setup" function, which is run only once when the board is powered up (or after a reset), and the "loop" function, which is cyclically run until the board is powered off (or until a reset is generated). Additional functions from the Arduino libraries, standard C libraries, libraries provided by 3<sup>rd</sup> parties and user defined functions, can be used to generate the desired behaviour. As the program defined as "sketch" is not fully C or C++ compliant, it requires additional steps before being provided to a standard C/C++ build system.

This modification target mainly three objectives. The first is to generate prototypes for the user defined functions. However this process is not perfect, as it is unable to generate declarations for functions defined within particular namespaces or classes, or with default argument values [65]. The

<sup>&</sup>lt;sup>1</sup> For a fair comparison, the *Uno* and the *Ethernet* board use the same AVR Atmega328 MCU at 16Mh. Without PoE support:

| - Arduino Uno Board (€20) + Ethernet Shield (€30) =          | €50 |

|--------------------------------------------------------------|-----|

| - Arduino Ethernet Board (€40) =                             | €40 |

| With PoE support:                                            |     |

| - Arduino Uno Board (€20) + Ethernet Shield with PoE (€45) = | €65 |

| <ul> <li>Arduino Ethernet Board with PoE (€55) =</li> </ul>  | €55 |

second objective is to add all the necessary library references. This step adds a reference for the "Arduino.h" library (or to the "WProgram.h" library for legacy code based on the original Wiring project). The third and last step consists on appending a "main" function that matches the target board. The specific options that this code transformation requires are defined in the XML files included with the Arduino IDE distribution. For clarity, Snippet 1 describes a simplified output of the code transformation for a sample sketch.

| Original "Sketch"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Transformed "Sketch" (correct C code)                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>1. int led = 13;<br/>2.<br/>3. // the setup routine runs once when you press reset:<br/>4. void setup() {<br/>5. // initialize the digital pin as an output.<br/>6. pinMode(led, OUTPUT);<br/>7. }<br/>8.<br/>9. // the loop routine runs over and over again forever:<br/>10. void loop() {<br/>11. digitalWrite(led, HIGH); // turn the LED on<br/>12. delay(1000); // wait for a second<br/>13. digitalWrite(led, LOW); // turn the LED off<br/>14. delay(1000); // wait for a second<br/>15. }<br/>16.<br/>17. // user defined function<br/>18. void my_function() {<br/>19. //do something<br/>20. }</pre> | <pre>1. #include "Arduino.h" 2. 3. int main(void); 4. 5. void setup(void); 6. void loop(void); 7. 8. void my_function(void); 9. 10. int led = 13; 11. 12. void setup() { 13. pinMode(led, OUTPUT); 14. } 15. 16. void loop() { 17. digitalWrite(led, HIGH); 18. delay(1000); 19. digitalWrite(led, LOW); 20. delay(1000); 21. } 22. 23. void my_function() { 24. } 25. 26. int main() { 27. setup(); 28. for (;;) 29. loop(); 30. return 0; 31. } </pre> |

Snippet 1. Arduino Sketch Pre-Processing

After the transformation, the sketch code is a fully compliant C/C++ program. Then, it is compiled and linked by a standard build process. As the Arduino project initiated with boards based on the 8 bit AVR architectures, the code has been always compiled and linked with the latest AVR GCC toolchain distribution. As new 32 bit board models also use the ARM core processors manufactured by AVR, the same toolchain is used for both, the 8 bit boards and the new 32 bit boards. As a consequence, additional functions supported by the AVR GCC libraries can be used within the Arduino IDE.

The main advantage of the Arduino software system is the availability of function libraries that effectively simplify the interaction with the underlying hardware. This property enables its use by any person without knowledge of the electronics field. In other words, the Arduino system provides a layer of abstraction that reduce complex operations to single statements. As a generality, the libraries are focused on some kind of input / output process, such as network or serial communication, display handling or motor control.

A useful example of this simplification is the abstraction of the configuration of a PWM output. Depending on the architecture, a pin which outputs a PWM pattern usually reflects the interaction of at least two peripherals: a GPIO controller and a Timer. If the MCU supports some sort of clock gate control, the initial step is to enable the gate to the required peripherals. Then, the timer is configured

for PWM operation, which commonly involves frequency, counting thresholds, and output settings. Finally, the GPIO is configured to be controlled by the Timer and output the desired pattern.

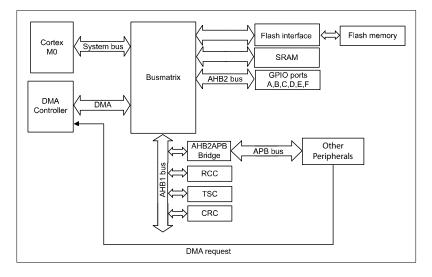

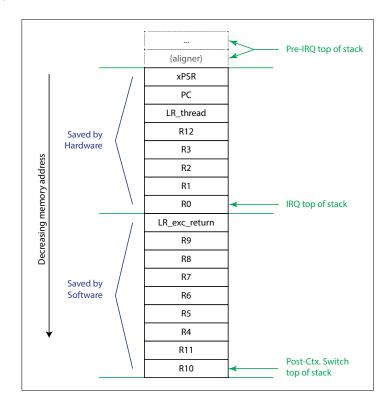

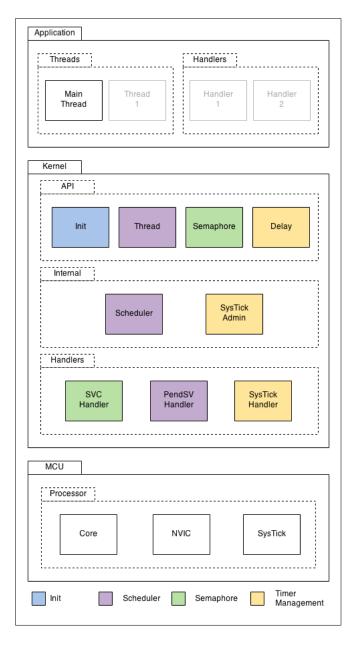

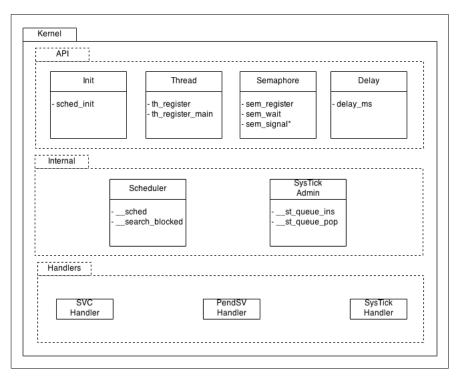

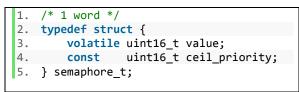

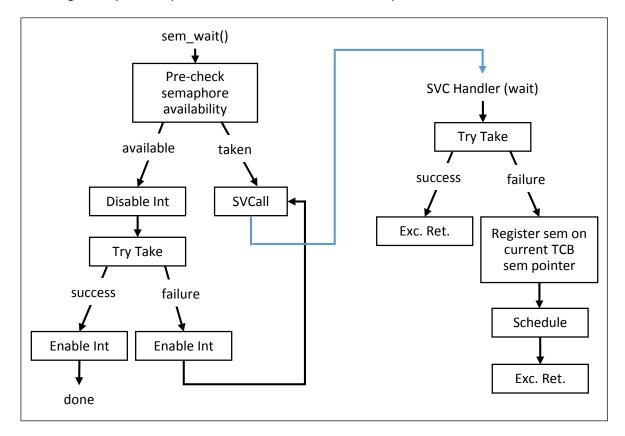

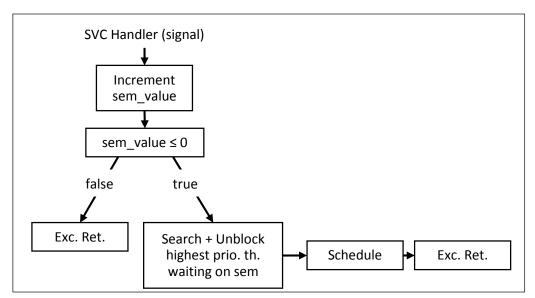

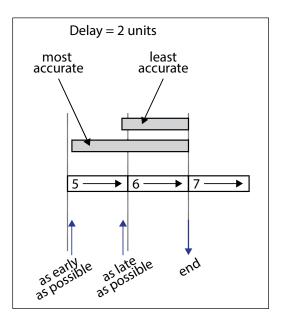

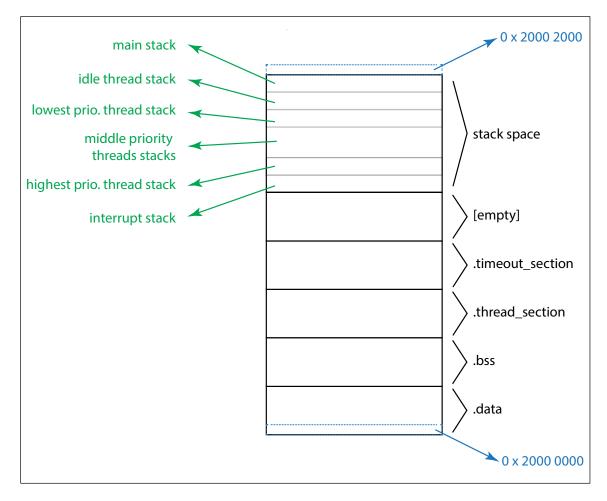

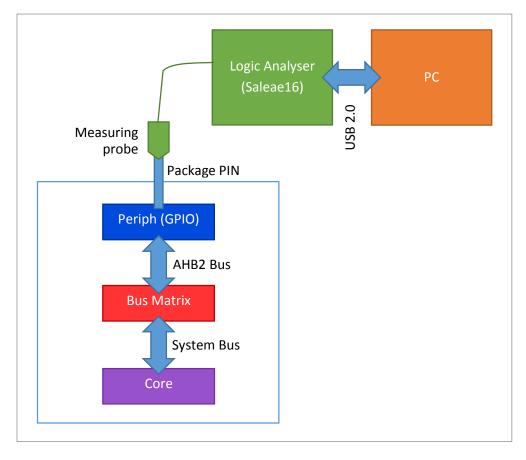

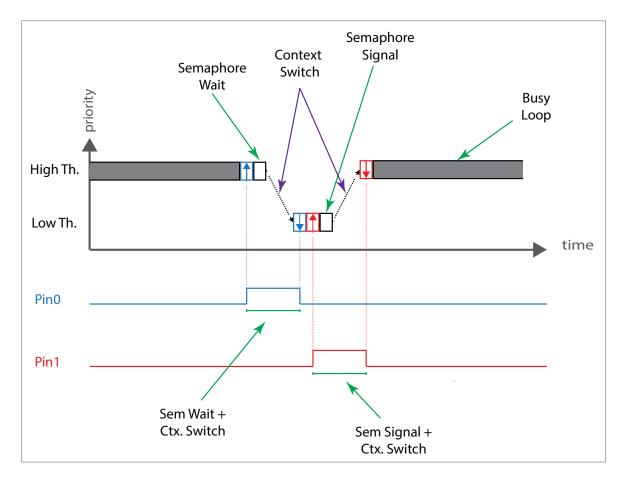

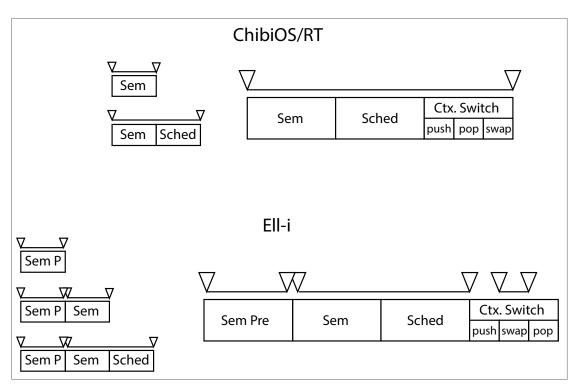

In contrast, the Arduino system silently enables and configures the desired peripherals before the code from the programmer is executed. Then, only two actions are required from the user: one that redirects the output from the Timer to the desired GPIO, and another that selects the desired threshold for controlling the PWM duty cycle. This operations are elegantly wrapped by functions that only request from the user the relevant parameters, and realize all the calculations and register accesses on behalf of the programmer.