Aalto University School of Science Degree Programme in Computer Science and Engineering

Mikael Simberg

# Linear-time encoding and decoding of low-density parity-check codes

Master's Thesis Espoo, 2015

Supervisor: Professor Petteri Kaski Advisors: Professor Petteri Kaski

Professor Camilla Hollanti

Code:

F3008

Aalto University School of Science

Degree Programme in Computer Science and Engineering

AUTHOR: Mikael Simberg

TITLE: Linear-time encoding and decoding

of low-density parity-check codes

Date: 2015 Pages: 108 + 12

Major: Systems and Operations Research

Supervisor: Professor Petteri Kaski Advisors: Professor Petteri Kaski

Professor Camilla Hollanti

### ABSTRACT:

Low-density parity-check (LDPC) codes had a renaissance when they were rediscovered in the 1990's. Since then LDPC codes have been an important part of the field of error-correcting codes, and have been shown to be able to approach the Shannon capacity, the limit at which we can reliably transmit information over noisy channels. Following this, many modern communications standards have adopted LDPC codes. Error-correction is equally important in protecting data from corruption on a hard-drive as it is in deep-space communications. It is most commonly used for example for reliable wireless transmission of data to mobile devices. For practical purposes, both encoding and decoding need to be of low complexity to achieve high throughput and low power consumption.

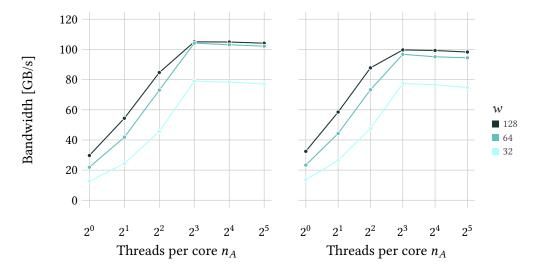

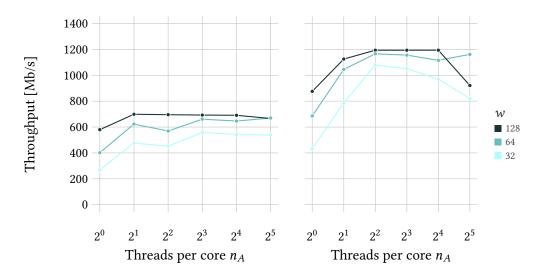

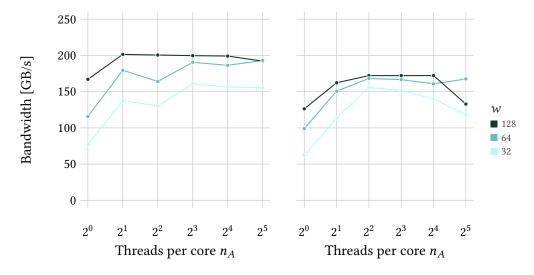

This thesis provides a literature review of the current state-of-the-art in encoding and decoding of LDPC codes. Message-passing decoders are still capable of achieving the best error-correcting performance, while more recently considered bit-flipping decoders are providing a low-complexity alternative, albeit with some loss in error-correcting performance. An implementation of a low-complexity stochastic bit-flipping decoder is also presented. It is implemented for Graphics Processing Units (GPUs) in a parallel fashion, providing a peak throughput of 1.2 Gb/s, which is significantly higher than previous decoder implementations on GPUs. The error-correcting performance of a range of decoders has also been tested, showing that the stochastic bit-flipping decoder provides relatively good error-correcting performance with low complexity. Finally, a brief comparison of encoding complexities for two code ensembles is also presented.

KEYWORDS: bit-flipping, coding theory, error-correcting codes, graphics pro-

cessing unit, linear time complexity, low-density parity-check

codes

Language: English

# ACKNOWLEDGMENTS

First and foremost, I would like to thank my supervisor Petteri Kaski for his great help and guidance throughout the preparation of this thesis, and for introducing me to the exciting world of error-correcting codes and the study of decoding using stochastic bit-flipping with Alexander Mozeika and Pekka Orponen.

I also wish to thank Camilla Hollanti for fruitful discussions and helpful comments throughout the thesis work, and for introducing me to and providing insights about information transmission standards.

I gratefully acknowledge the use of computing resources available via project "Science-IT" at Aalto University School of Science and via CSC—the Finnish IT Center for Science. As regards the latter I would especially like to thank Maarit Mantere for her advice that NVIDIA Tesla K40 graphics processing units are available at CSC.

Finally, I would like to thank my wonderful girlfriend and friends for always being there, and my family for showing interest in my work and fully supporting me in what I do.

Mikael Simberg Espoo, 15.12.2014

# Contents

| A  | BSTR | ACT                                            | ii   |

|----|------|------------------------------------------------|------|

| A  | CKNO | DWLEDGMENTS                                    | v    |

| Lı | ST O | F ACRONYMS                                     | xi   |

| Lı | ST O | F MATHEMATICAL SYMBOLS                         | xiii |

| 1  | Int  | RODUCTION                                      | 1    |

| 2  | Eri  | ROR-CORRECTING CODES                           | 5    |

|    | 2.1  | Preliminaries                                  | 5    |

|    | 2.2  | Noisy channels                                 | 7    |

|    | 2.3  | Low-density parity check codes                 | 9    |

|    |      | 2.3.1 Tanner graph representation              | 9    |

|    | 2.4  | LDPC code constructions                        | 10   |

|    |      | 2.4.1 Regular codes                            | 10   |

|    |      | 2.4.2 Irregular codes                          | 11   |

|    |      | 2.4.3 Code ensembles and their properties      | 13   |

|    |      | 2.4.4 Quasi-cyclic LDPC codes                  | 17   |

|    | 2.5  | Codes used in practice                         | 18   |

|    |      | 2.5.1 Digital Video Broadcasting               | 18   |

|    |      | 2.5.2 WIMAX AND WIFI                           | 19   |

|    |      | 2.5.3 ETHERNET                                 | 19   |

|    | 2.6  | Summary                                        | 19   |

| 3  | End  | coding of LDPC codes                           | 21   |

|    | 3.1  | Encoding using the systematic generator matrix | 21   |

# **CONTENTS**

|   | 3.2 | Encoi  | DING WITH APPROXIMATE LOWER-TRIANGULAR PARITY-CHECK   |    |

|---|-----|--------|-------------------------------------------------------|----|

|   |     | MATRI  | CCES                                                  | 23 |

|   |     | 3.2.1  | IRREGULAR CODES WITH A FIXED GAP                      | 27 |

|   |     | 3.2.2  | Quasi-cyclic LDPC codes with approximate lower-       |    |

|   |     |        | TRIANGULAR PARITY-CHECK MATRICES                      | 27 |

|   | 3.3 | Summ   | ARY                                                   | 28 |

| 4 | Dec | CODING | G OF LDPC CODES                                       | 29 |

|   | 4.1 | Naïve  | DECODING                                              | 31 |

|   | 4.2 | Віт-ғі | LIPPING DECODING                                      | 31 |

|   |     | 4.2.1  | Gallager's bit-flipping decoder                       | 31 |

|   |     | 4.2.2  | Weighted bit-flipping decoders                        | 32 |

|   |     | 4.2.3  | SCHEDULES FOR BIT-FLIPPING DECODERS                   | 34 |

|   |     | 4.2.4  | STOCHASTIC BIT-FLIPPING DECODERS                      | 35 |

|   |     | 4.2.5  | STOCHASTIC BIT-FLIPPING DECODER WITH HARD CHANNEL     |    |

|   |     |        | VALUES                                                | 37 |

|   | 4.3 | Messa  | AGE-PASSING DECODING                                  | 39 |

|   |     | 4.3.1  | EXACT INFERENCE ON FACTOR GRAPHS AND THE SUM-PRODUCT  | ı  |

|   |     |        | ALGORITHM                                             | 40 |

|   |     | 4.3.2  | The sum-product algorithm for decoding                | 47 |

|   |     | 4.3.3  | Implementing the sum-product decoder                  | 52 |

|   |     | 4.3.4  | Binary message-passing decoder                        | 55 |

|   |     | 4.3.5  | Message-passing schedules                             | 57 |

|   | 4.4 | Turbo  | CODES                                                 | 58 |

|   | 4.5 | Summ   | ARY                                                   | 59 |

| 5 | DEC | CODER  | IMPLEMENTATIONS                                       | 61 |

|   | 5.1 | Hard   | WARE SIMULATIONS                                      | 62 |

|   | 5.2 | GPU 1  | MPLEMENTATIONS                                        | 63 |

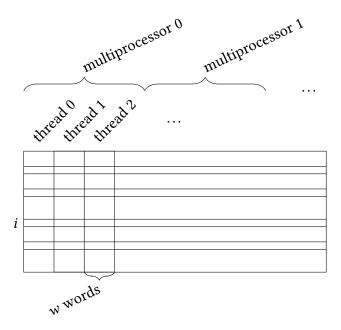

|   | 5.3 | A GPU  | U implementation of a stochastic-bit flipping decoder | 64 |

|   |     | 5.3.1  | Architecture and programming of CUDA devices          | 65 |

|   |     | 5.3.2  | Decoder implementation                                | 67 |

| 6 | Exp | PERIME | NTAL RESULTS                                          | 77 |

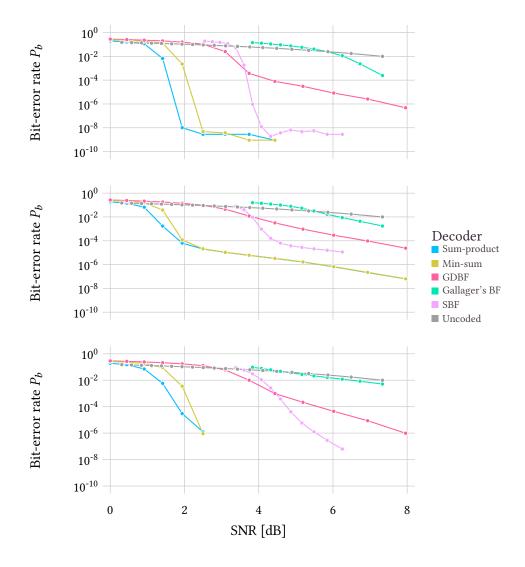

|   | 6.1 | Сомра  | ARISON OF DECODERS                                    | 77 |

|   |     | 6.1.1  | Choosing the decoder parameters                       | 79 |

|   |     | 6.1.2  | RESULTS                                               | 80 |

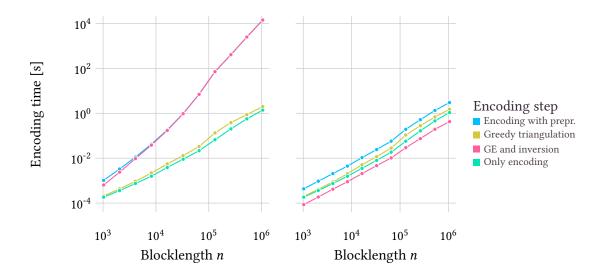

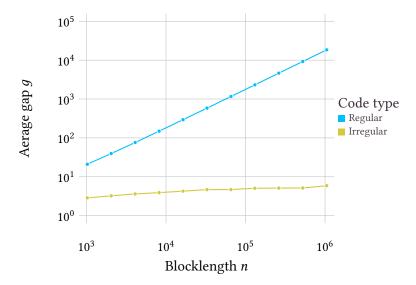

|   | 6.2 | Сомр   | LEXITY OF APPROXIMATE LOWER TRIANGULAR ENCODING       | 85 |

|   |     | 6.2.1  | Results                                               | 85 |

# CONTENTS

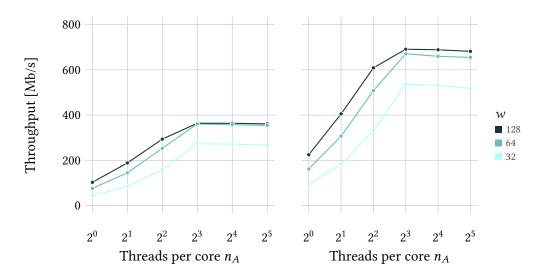

|    | 6.3  | THE STOCHASTIC BIT-FLIPPING DECODER ON THE GPU             | 89  |

|----|------|------------------------------------------------------------|-----|

|    |      | 6.3.1 Results                                              | 90  |

| 7  | Cor  | NCLUSION                                                   | 95  |

| Bı | BLIO | GRAPHY                                                     | 99  |

| A  | Der  | RIVATIONS                                                  | 109 |

|    | A.1  | Derivation of the gradient-descent bit-flipping decoder    | 109 |

|    | A.2  | Derivation of the tahn-rule for the sum-product decoder    | 110 |

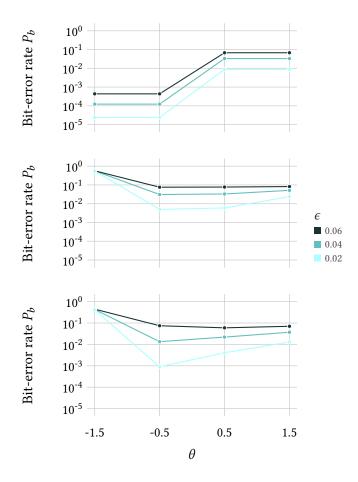

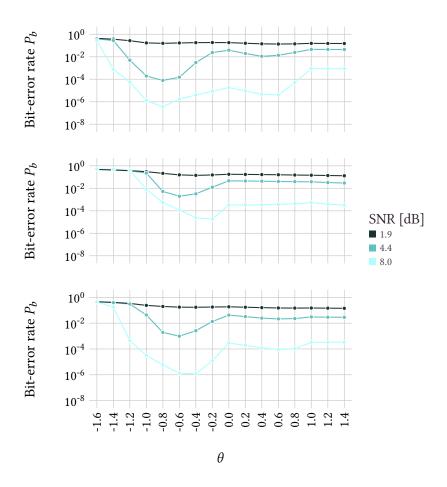

| В  | Par  | AMETER SEARCHES                                            | 115 |

|    | B.1  | PARAMETER SEARCHES FOR THE STOCHASTIC BIT-FLIPPING DECODER | 116 |

|    | B.2  | PARAMETER SEARCHES FOR THE GRADIENT-DESCENT BIT-FLIPPING   |     |

|    |      | DECODER                                                    | 119 |

# LIST OF ACRONYMS

LDPC code Low-density parity-check code

QC-LDPC code Quasi-cyclic low-density parity-check code

BEC Binary erasure channel

BSC Binary symmetric channel

BAWGNC Binary additive white Gaussian noise channel

BER Bit-error rate FER Frame-error rate

CPU Central processing unit

RAM Random access memory or random access machine

MBRAM Random access machine with addition, subtraction, multipli-

cation, division and bitwise Boolean operations

GPU Graphics processing unit

CUDA Compute unified device architecture

PTX Parallel thread execution ISA Instruction set architecture

# LIST OF MATHEMATICAL SYMBOLS

H Parity-check matrixG Generator matrix

$H_{ai}$  The *i*th element of the *a*th row of a matrix H

$H^T$  The transpose of a matrix H

x A vector

$x_i$  The *i*th element of the vector **x**

$\mathbf{x} \setminus x_i$  The vector  $\mathbf{x}$  with the *i*th element removed

$I_n$  Identity matrix of dimension  $n \times n$

$\begin{array}{ccc} \mathbf{0} & & \text{An all-zero vector} \\ \mathbb{F}_2 & & \text{The binary field} \end{array}$

N(i) The set of neighbors of a node i in a graph

$N(i) \setminus j$  The set of neighbors of a node *i* excluding the node *j*

$P_b$  Bit-error rate  $P_B$  Block-error rate

[*P*] Iverson's bracket notation, evaluates to 1 if the predicate *P* is true

and 0 otherwise

$\mathcal{N}(\mu, \sigma^2)$  The Gaussian distribution with mean  $\mu$  and variance  $\sigma^2$

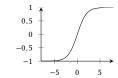

sgn(x) The sign function

tanh(x) The hyperbolic tangent function

$tanh^{-1}(x)$  The inverse hyperbolic tangent function

# Chapter 1

# Introduction

The field of information theory was started by Shannon in 1948 with his "A mathematical theory of communication" (Shannon, 1948). In it he presented the problem of transmitting information reliably over noisy channels, together with an initial solution on how to tackle the problem. Although there is a limit to how much information we can transmit over a channel—the *Shannon capacity*—Shannon also showed that we can come arbitrarily close to this limit using *error-correcting codes*. Shannon's work gave answers to a practical and common problem, and error-correcting codes are today in use in practically every communications scenario, from mobile networks to deep-space communications, in addition to reliable storage.

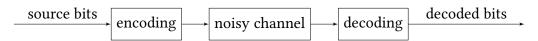

The classical communications problem is the following: we have a string of bits that we want to send from one place to another. The problem we are facing is that when we send the bits, some amount of noise will be added along the way and the receiving end will not receive what we originally sent. Error-correcting codes attempt to solve this problem by *encoding* the given string of bits into a longer string of bits, adding some form of *redundancy* to the bits that are sent. The longer string of bits is then sent over the channel and, on the receiving end, even with a certain amount of noise added to the bits, one can *decode* the sent bits uniquely to the original bits. Figure 1.1 presents the situation graphically. The problem is usually thought of as involving physical transmission of data from one point to another. However, the problem applies equally well in a situation where bits are not physically transferred at all. A hard-drive is one such example, where errors will accumulate over time.

**Figure 1.1:** Transmission over a noisy channel: given source bits are encoded before transmission over a noisy channel; decoding of the encoded noisy bits attempts to recover the source bits.

# Introduction

How could one start to approach the problem of making sure that the right bits are received? Say that one would like to send the following string of 8 bits:

#### 01001101.

We want to make sure that the receiver does not mistake the bits for any of the other  $2^8 - 1$  possible bit strings of length 8 in the case that some of the bits are flipped along the way. One way of dealing with this is to send the following string of bits instead:

#### 000 111 000 000 111 111 000 111.

What we have done is replaced each bit by three occurrences of the same value. After receiving the longer string of bits, but with possibly some bits flipped, we can then decide that we decode the received bits so that for each group of three bits we set the value of that bit to the majority value. That is, if for example two or three of the three bits in a group are ones, we decide that the group of three bits represents a one. With this scheme one of the bits in each group of three bits can be flipped and we will still decode the correct string of bits.

The above scheme is called a repetition code which does not work well in practice. It does, however, demonstrate the essence of error-correcting codes: to allow us to recover from as many errors as possible, and to do so efficiently. The repetition code does the first if we repeat each bit enough times, but loses on efficiency as we have to repeat each bit many times to achieve reliable transmission. On the other hand, keeping the number of repetitions low and fixed maintains efficiency but we cannot recover from many errors. The codes considered in this thesis, low-density parity-check codes, are one type of codes that can do both tasks well.

Low-density parity-check codes were first introduced by Gallager (1962). Despite the current knowledge of their good properties, the codes were largely forgotten after their discovery until the 1990's. The codes were rediscovered independently by MacKay (1995), as well as Sipser and Spielman (1996). It was quickly realized that the new codes were largely equivalent to the codes Gallager first presented. Following the rediscovery there has been a considerable amount of research into low-density parity-check codes. They have been shown to have good error-correcting properties and have practical algorithms for both encoding and decoding. Recently, the codes have also been included in standards for wireless and wired communication, joining and in some cases replacing Turbo codes (Berrou et al., 2005) which have, together with low-density parity-check codes, been shown to be able to approach the Shannon capacity.

As the field of low-density parity-check codes has grown more mature since their rediscovery there has been more focus on making the codes perform better, as well as improving the algorithms used for encoding and decoding of the codes. For example, encoding can as of today not be done in linear time for general low-density parity-check codes. On the decoding side, most decoders are linear-time, but there is room for improvement in terms of the constants involved in implementations. The need for faster practical encoders and, more importantly, decoders is twofold. First, power consumption is an important factor in mobile devices, and reducing the complexity of hardware implementations can have a positive effect on the power consumption. Second, faster encoders and decoders can allow improvements in a combination of throughput, latency and error-correction. Linear-time encoders and decoders allow us to scale the so-called block length of low-density parity-check codes, ultimately leading to better error-correction. Most importantly, encoders and decoders with small constants give practical improvements to error-correction, throughput and latency. For this reason it is important to consider practical issues when implementing encoding and decoding algorithms, and not only the theoretical properties of the algorithms. With this in mind, we will in this thesis review the current stateof-the-art in encoding and decoding of low-density parity-check codes together with experimental results on encoding complexity and the error-correcting performance of decoders. Most importantly, this thesis presents a low-complexity decoder for GPUs.

We will begin with an overview of definitions relating to coding theory, define what low-density parity-check codes are, and look into various code constructions in Chapter 2. Chapter 3 contains a summary of useful encoding methods, one of which allows linear-time encoding for a limited but useful set of codes. A majority of the research is focused the on decoding of low-density parity-check codes. In Chapter 4 we review the advances in decoding algorithm designs, which aim to reduce the complexity of the decoders to reach higher throughputs, and to improve the error-correcting properties of the decoders. In Chapter 5 we present existing work on implementing decoders in hardware, where the focus generally is to achieve high throughput. Partly, the aim of this thesis is to provide a comprehensive overview of the current state-of-the-art in lowdensity parity-check codes. However, the main contribution of this thesis is the implementation of a simple decoder implemented for GPUs. The need for simpler algorithm designs becomes apparent as decoders are implemented in hardware. The implementation aims at achieving high decoding throughputs by using a simple design which is easily parallelized. In Chapter 6 we will present some experimental results concerning encoding complexity, compare five decoders in terms of error-correcting performance, and present results on the performance of the GPU implementation. We conclude the thesis in Chapter 7.

# Chapter 2

# **ERROR-CORRECTING CODES**

In this chapter we set up the terminology and basic concepts concerning error-correcting codes. In Section 2.1 we will present the basic concepts concerning error-correcting codes in general and in Section 2.2 we present three noisy channels. In Section 2.3 we present low-density parity-check codes, some constructions of low-density parity-check codes and the most important results relating to them. By the end of this chapter we will have the prerequisites to consider encoding and decoding of low-density parity-check codes in the following chapters.

# 2.1 Preliminaries

There are two main types of codes, of which the first adds redundancy to continuous *streams* of data and the second does so to *blocks* of data. We will concern ourselves with the second type of codes, *block codes*, as low-density parity-check codes are of this second type. Block codes work with finite blocks of data, encoding each block of data into a longer block, and each block is *independent* from each other. With this, we can define a block code more formally, and since we will only consider one type of block codes in this thesis we will refer to block codes simply as codes. We will largely follow the notation and terminology of Richardson and Urbanke (2008).

# DEFINITION 1 (CODE)

Let  $\mathbb{F}$  be a finite field. A code C of block length n and cardinality M is a set of  $M \geq 2$  elements from  $\mathbb{F}^n$ .

We call the elements of a code its *codewords*. In contrast, a *word* refers to a vector which is part of  $\mathbb{F}^n$ , but is not necessarily a codeword. We will denote vectors, or words, from  $\mathbb{F}^n$  by small bold letters, and the *i*th element of a vector  $\mathbf{x}$  by  $x_i$ .

### **Error-correcting codes**

DEFINITION 2 (LINEAR CODE)

A linear code C is a code which satisfies

$$\alpha \mathbf{x} + \alpha' \mathbf{x}' \in C$$

,  $\forall \mathbf{x}, \mathbf{x}' \in C \text{ and } \forall \alpha, \alpha' \in \mathbb{F}$ .

Low-density parity-check codes are linear codes. A direct consequence of linearity is that the all-zero word is always a codeword. A second consequence of the linearity of a code is that the error-correcting performance of the code is independent of the sent codeword. Hence we usually assume that the all-zero codeword was sent when examining decoding performance.

The weight of a vector and the distance between two vectors are useful concepts for analyzing error-correcting codes in terms of the *minimum distance* of a code.

DEFINITION 3 (WEIGHT OF A VECTOR AND DISTANCE BETWEEN TWO VECTORS)

The weight of a vector  $\mathbf{x}$ , denoted by  $w(\mathbf{x})$ , is the number of nonzero entries in  $\mathbf{x}$ . The distance between two vectors  $\mathbf{x}$  and  $\mathbf{x}'$  is  $d(\mathbf{x}, \mathbf{x}') = w(\mathbf{x} - \mathbf{x}')$ .

DEFINITION 4 (MINIMUM DISTANCE OF A CODE)

The minimum distance of a code C is the smallest distance between any two distinct elements of the code. More precisely, the minimum distance of a code is defined as

$$\min_{\substack{\mathbf{x},\mathbf{x}'\in C\\\mathbf{x}\neq\mathbf{x}'}}d(\mathbf{x},\mathbf{x}').$$

The essence of an error-correcting code is that we map a set of shorter strings to a set of longer strings, the codewords. In doing so we can increase the distance between any two elements in the code resulting in the code becoming more robust to errors. The extent to which we have improved the error-correcting properties of a code is partly captured by the minimum distance of the code, as a larger minimum distance means that the code can tolerate more errors while still allowing decoding to the correct codeword.

Although codes can be formulated on larger finite fields, the binary field  $\mathbb{F}_2$  consisting of the elements  $\{0,1\}$  is most commonly used. On the binary field the addition operation is the logical XOR operation. More precisely, 0+0=1+1=0 and 1+0=0+1=1. The binary field can also be represented by the elements in the set  $\{1,-1\}$ . Instead of mod-2 addition, we now use multiplication, meaning  $1\cdot 1=(-1)\cdot (-1)=1$  and  $(-1)\cdot 1=1\cdot (-1)=-1$ . The field will be assumed to be the binary field for the rest of this thesis.

# Noisy channels

We say that a binary code with M elements has  $\log_2 M$  information bits, as this is the number of bits of information that we are sending over the channel in each codeword. The rate of a code is then defined as the ratio of information bits in a codeword to the total number of bits in a codeword.

# DEFINITION 5 (RATE OF A CODE)

The rate of a code C with block length n and cardinality M is the number of information bits sent over the number of total bits sent. More precisely, the rate r(C) is

$$r(C) = \frac{\log_2 M}{n}.$$

It will later be convenient to consider *ensembles* of codes. They are essentially sets of codes, constructed using some random process, from which codes are chosen at random. Shannon's random ensemble is one example.

# Example 1 (Shannon's random ensemble)

Let Shannon(n, M) denote Shannon's random ensemble where each code has block length n and M elements. A code is chosen from the ensemble by choosing each of the M codewords uniformly at random from  $\mathbb{F}_2^n$ .

# 2.2 Noisy Channels

Noisy channels are the fundamental reason that error-correcting codes are used. For that reason we will take a small detour to look at channels before continuing to low-density parity-check codes. A *binary channel* is a mapping  $\{0,1\} \rightarrow S$  where S can be a finite or infinite set. We will in general denote the sent codeword by  $\mathbf{x}$  and the received codeword after transmission over a noisy channel by  $\mathbf{y}$ .

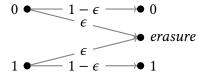

**Figure 2.1:** The transition diagram for the BEC. The input can have the value 0 or 1, and will after transmission have changed to an erasure with probability  $\epsilon$  and stayed at the input value with probability  $1 - \epsilon$ .

# **Error-correcting codes**

The binary erasure channel (BEC) simply performs the following operation: with some probability  $\epsilon$ , a bit becomes an *erasure*. The set of symbols received thus has the added *erasure* symbol. Put differently, on the binary erasure channel we assume that the receiver knows that a bit has been erased but simply does not know what value the erased bit had originally. The transition diagram of the BEC is shown in Figure 2.1.

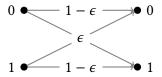

**Figure 2.2:** The transition diagram for the BSC. The input can have the value 0 or 1, and will after transmission on the BSC have flipped to the other value with probability  $\epsilon$ .

The binary symmetric channel (BSC) has the same input and output symbols and is determined by the parameter  $\epsilon$ , often called the *crossover probability*. The crossover probability determines the amount of noise in the channel in the sense that a bit passing through the channel is simply flipped from 0 to 1 or from 1 to 0 with probability  $\epsilon$ . The transition diagram of the BSC is shown in Figure 2.2.

The binary additive white Gaussian noise channel (BAWGNC) maps the set of input symbols to the set of real numbers. For the BAWGNC it is convenient to use  $\{1,-1\}$  as the set of input symbols. The mapping for the BAWGNC is

$$y_i = x_i + e_i$$

for each bit  $x_i$  that we wish to send, where  $e_i$  is an independently and normally distributed random variable with zero mean and variance  $\sigma^2$ . That is,

$$e \sim \mathcal{N}(0, \sigma^2)$$

.

Two quantities are useful when considering the BAWGNC. The *signal-to-noise* ratio (SNR) is the ratio of the energy per transmitted bit  $E_s$  to the energy of the noise  $\sigma^2$ . That is, SNR =  $\frac{E_s}{\sigma^2}$ . Here,  $E_s=1$  because the set of input symbols is  $\{1,-1\}$ . A related quantity is the ratio of the energy per transmitted information bit  $E_b=\frac{E_s}{r}$  to the double-sided power spectral density  $N_0=2\sigma^2$ . Here we have simply written r for the rate of a code C. The quantities are usually shown in dB. That is, they are shown as  $10\log_{10}\left(\frac{E_s}{\sigma^2}\right)$  and  $10\log_{10}\left(\frac{E_s}{2r\sigma^2}\right)$ . For codes of rate  $\frac{1}{2}$  the two quantities are the same. The BAWGNC is useful as a model for real channels.

# 2.3 Low-density parity check codes

A low-density parity-check code, or LDPC code, is defined by a matrix  $H \in \{0,1\}^{m \times n}$ . The defining characteristic of LDPC codes is that H is *sparse*. This means that H has O(n) nonzero elements. Given a matrix H the set of codewords is defined by

$$C = \{ \mathbf{x} \in \{0,1\}^n \mid H\mathbf{x}^T = \mathbf{0}^T \},\$$

where  $\mathbf{0}$  is the zero vector and we assume that all vectors are *row* vectors. The matrix H is referred to as the *parity-check matrix*, since it requires that a codeword  $\mathbf{x}$  have even parity in the so-called parity-check equations

$$s_a = \sum_{i=1}^n H_{ai} x_i = 0,$$

for all a = 1, 2, ..., m. Each parity-check equation is often called a *checksum* or *check*, and the vector s of sums  $s_a$  is called the *syndrome*. If a check has even parity we say that the check is *satisfied* and otherwise we say that the check is *unsatisfied*. Assuming that the parity-check matrix of an LDPC code is of full rank, the cardinality of the code is  $M = 2^{n-m}$ . The rate of an LDPC code with a parity-check matrix of full rank is  $\frac{n-m}{n}$ . A parity-check matrix uniquely defines a code up to row operations, meaning row permutations and additions of one row to another.

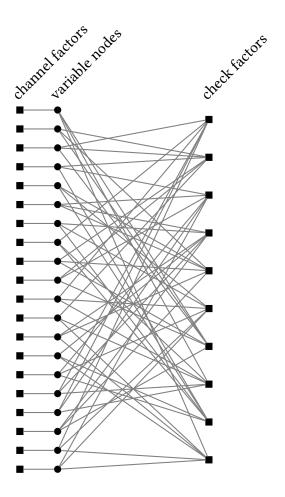

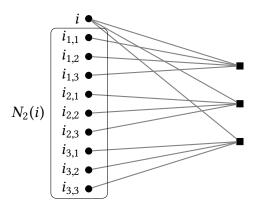

# 2.3.1 Tanner graph representation

It is often convenient to consider a graph representation of a parity-check matrix. The graph representation of a parity-check matrix is more commonly referred to as its  $Tanner\ graph$  (Tanner, 1981). The Tanner graph is a bipartite graph with two sets of nodes. The first set consists of the  $check\ nodes$ , each corresponding to the rows, or checks, of H. The second set consists of the  $variable\ nodes$ , each corresponding to a column of H, or a symbol of a word. There is an edge between a check node a and a variable node i if and only if  $H_{ai}=1$ . Put differently, the Tanner graph corresponding to a parity-check matrix H has an adjacency matrix given by

$$\begin{pmatrix} 0 & H \\ H^T & 0 \end{pmatrix}$$

.

We denote the neighbors of a node i by N(i). As a shorthand, the notation  $N(i) \setminus j$  means the neighbors of the node i excluding the node j. A parity-check matrix and a Tanner graph are equivalent up to permutation of rows and columns. In general, we will also treat a *code* as equivalent to a parity-check matrix or Tanner graph, even though a code can be defined by more than one parity-check matrix, and likewise by more than one Tanner graph.

# 2.4 LDPC code constructions

The definition of LDPC codes does not state how the codes should be constructed. Next we will look at some ways of doing so. Most importantly, we will present *regular* and *irregular* code ensembles. We will, in relation to code ensembles, also state two central theorems regarding the performance of codes. In addition, we will present so-called *quasi-cyclic* LDPC codes and briefly look at LDPC codes used in communications standards.

#### 2.4.1 Regular codes

A simple way to construct an LDPC code results in what is called a *regular* code. An (l,r)-regular LDPC code is defined by a parity-check matrix H where each column of H has weight l and each row has weight r. Such a code has, by double counting, e = mr = nl ones in its parity-check matrix or, equivalently, e edges in its Tanner graph representation.

**Figure 2.3:** Drawing a random bipartite graph with the configuration model. In the above example each node on the left has degree 3 and thus 3 "sockets" indicated by the small gray nodes connected to each node. Likewise, each node on the right has degree 6 and thus 6 sockets. Thus, there are in total  $10 \cdot 3 = 5 \cdot 6 = 30$  sockets on each side. We can then, using a random permutation, connect each socket on the left to a unique socket on the right. The result is a bipartite graph which may not be simple. That is, it may have more than one edge connecting a pair of nodes.

One way of constructing a regular code is with the help of a random permutation. For the construction of a regular code it is easiest to think of the code in terms of its graph representation. As the graph is bipartite we know that the two sets of nodes will both have e edges incident to them. We then define each

### LDPC CODE CONSTRUCTIONS

node to have a number of "sockets" equal to the degree of the node. Each socket will be used to attach one end of an edge to it. If we number the sockets from 1 to e on one side (say, the variable nodes) we can then, given a permutation of  $1,2,\ldots,e$ , connect the sockets of the check nodes to a socket of a variable node with a number given by the permutation. The model for constructing a graph in such a way is called the *configuration model* (Bollobás, 2001). In this way, we can construct a random bipartite graph but the graph is not necessarily simple. That is, there may be multiple edges between a pair of nodes. However, we can simply draw a new permutation until we get a simple graph. In other words, we perform rejection sampling to get a simple bipartite graph. More importantly, the probability of drawing a simple graph approaches zero exponentially only in the degrees of the nodes and not in the block length n. The probability of drawing a simple bipartite graph approaches a nonzero constant in the block length given fixed degrees (Greenhill et al., 2006).

Example 2 (Parity-check matrix of a (3,6)-regular LDPC code)

The following matrix defines a randomly generated (3,6)-regular LDPC code of block length 20. That is, parity-check matrix has 3 ones in each column and 6 ones in each row.

EXAMPLE 3 (TANNER GRAPH OF A (3,6)-REGULAR CODE)

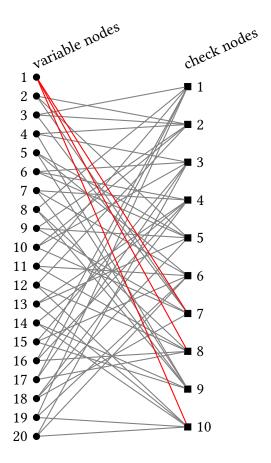

The Tanner graph corresponding to the parity-check matrix in (2.1) is shown in Figure 2.4. The convention for drawing Tanner graphs is to draw the variable nodes as circles on the left-hand side and the check nodes as squares on the right hand side.

#### 2.4.2 Irregular codes

*Irregular* codes are a more general class of codes, which include the regular case. The terminology and notation of irregular degree distributions was first presented by Luby et al. (1997). They also presented the idea of *optimizing* the properties of a degree distribution using linear programming. Richardson et al. (2000, 2001) expanded on the work.

**Figure 2.4:** The Tanner graph of the parity-check matrix (2.1). The nodes on the left are the variable nodes and the nodes on the right are the check nodes. The edges corresponding to the nonzero entries of the first column of (2.1) have been highlighted in red.

For a code of length n, let  $\Lambda_i$  be the number of variable nodes of degree i. Thus  $\sum_i \Lambda_i = n$ . Likewise, let  $P_i$  be the number of check nodes of degree i, such that  $\sum_i P_i = m$ . It must hold that the number of edges emanating from both sides are equal, so  $\sum_i i\Lambda_i = \sum_i iP_i = e$ . For convenience, we represent the degree distributions in terms of the following polynomials:

$$\Lambda(x) = \sum_{i=1}^{d_v} \Lambda_i x^i$$

and  $P(x) = \sum_{i=1}^{d_c} P_i x^i$ ,

where  $d_v$  and  $d_c$  are the maximum degrees of the variable and check nodes, respectively. Using this representation we can write

$$\Lambda(1) = n$$

and  $P(1) = m$ .

We also define the *normalized* degree distributions

$$L(x) = \frac{\Lambda(x)}{\Lambda(1)}$$

and  $R(x) = \frac{P(x)}{P(1)}$ .

The normalized degree distributions give the fraction of nodes with a given degree. That is, a term  $L_i x^i$  in L(x) means that there are  $\frac{L_i}{n}$  variable nodes of degree i, and likewise for the check nodes.

An (l,r)-regular code is a special case of an irregular code. We can define a (l,r)-regular code with block length n with a degree distribution  $(\Lambda(x),P(x))=(nx^l,\frac{l}{r}nx^r)$ . Alternatively, in terms of a normalized degree distribution, the (l,r)-regular code is defined by  $(L(x),R(X))=(x^l,x^r)$ .

As in the case of a regular code, we can generate irregular codes by assigning unique names to sockets at each variable node, where the number of sockets at each node is equal to the degree of the node. Using a permutation we then again assign edges to a pair of variable and check nodes. The only difference to the regular case is that the number of sockets at each node need not be constant for the variable and check nodes. The probability of drawing a simple graph again approaches a nonzero constant in the block length *n* (Greenhill et al., 2006).

### 2.4.3 Code ensembles and their properties

We have already seen Shannon's ensemble as an example of a code ensemble. We can also, with the help of the construction in the previous section, define an ensemble of irregular LDPC codes. More precisely, an ensemble of *irregular* LDPC codes consists of codes constructed using the configuration model corresponding to the degree distributions  $\Lambda(x)$  and P(x), where the permutations are drawn uniformly at random. To further simplify analyzing code ensembles we can make the additional simplification that we do not reject any codes even if they have duplicate edges. Instead we take the number of edges between two nodes modulo 2. This way we may end up with parity-check matrices which are not of full rank, but the probability approaches zero as the block length is increased (Di et al., 2002). We will denote the ensemble of LDPC codes with block length n constructed using the configuration model by LDPC(n,  $\Lambda$ , P).

One of the main results is that for an ensemble of irregular codes constructed using the configuration model the codes from the ensemble are concentrated around the average in terms of error-correcting performance. A second, perhaps

### **Error-correcting codes**

more important theorem is the *channel coding theorem* by Shannon, which states that there is a limit to the rate at which we can send information over a channel with a given level of noise. We will present the case for the BSC here.

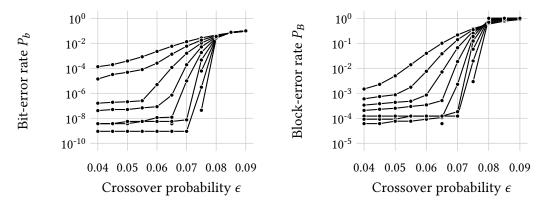

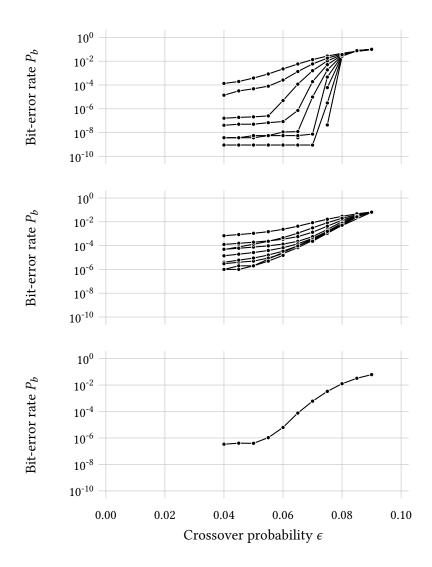

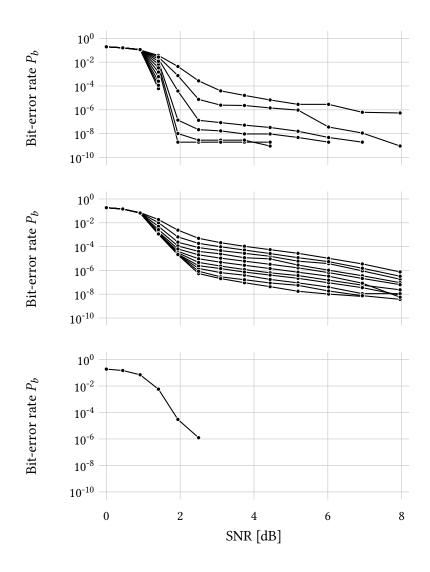

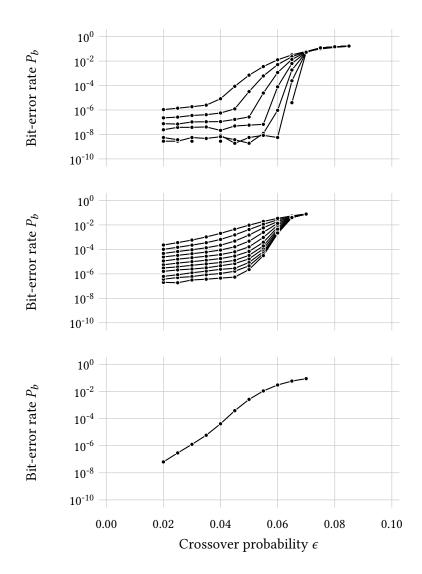

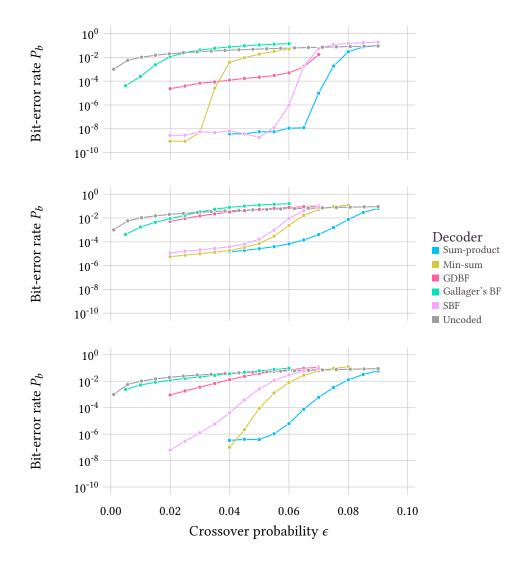

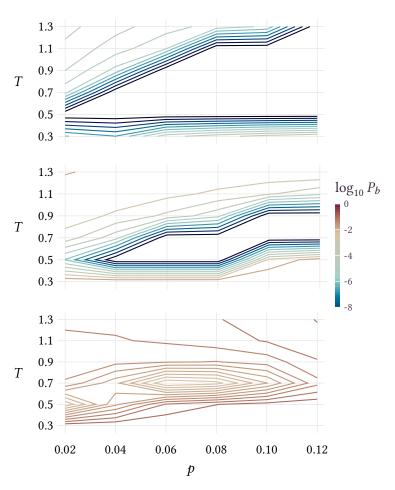

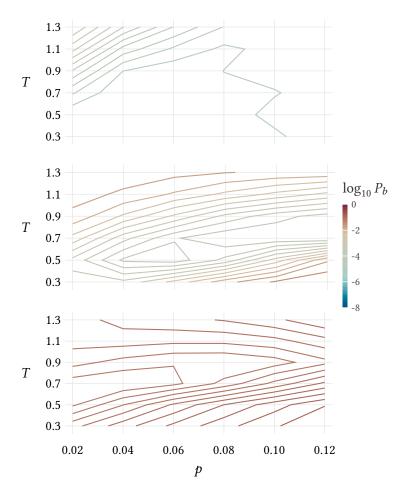

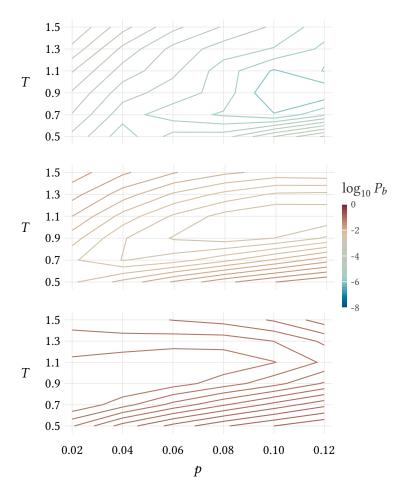

Before we state the theorems, let us introduce some additional terminology commonly used when talking about the performance of codes and decoders. The error-correcting performance is generally stated in terms of the bit-error rate of an ensemble of codes paired with a decoder. In the case of codes that have for example been defined in standards, we will of course talk about the bit-error rate of the single code paired with a decoder. The bit-error rate  $P_b$  is simply the probability that a transmitted bit has, after decoding, the wrong value. The bit-error rate is often abbreviated BER. One often also talks about the block- or frame-error rate, which we denote by  $P_B$ . This is the probability of a decoded block differing from the transmitted block in at least one bit. This is sometimes abbreviated FER. Figure 2.5 shows typical behavior of an LDPC code in terms of the bit-error rate and the block-error rate, as a function of the noise and the block length. Bits were encoded with codes from the (3,6)-regular ensemble (without duplicate edges) and transmitted over the BSC. The resulting words were decoded using the so-called sum-product algorithm. One can see a clear limit where increasing the block length of the code does not improve error-correction. This is called the *threshold* of the code and decoder, which we will define more precisely with Theorem 2.2. The region where the bit-error rate decreases sharply towards lower levels of noise is called the waterfall region. Following that, one can see the so-called *error floor*. The error floor is the flat region at lower levels of noise than the waterfall region. It is typical for LDPC codes to exhibit this error floor, although it is not desirable. The error floor is often caused by some inherent weakness in the code which leaves some bits particularly prone to being erroneous (Richardson, 2003).

With the above terminology, we can now state the theorems more precisely. The theorem regarding concentration around the average code in an ensemble enables us to choose essentially any code from an ensemble and be nearly certain that we have picked a code which is representative of the ensemble in general. We will state the following theorems as presented by Richardson and Urbanke (2008), omitting the proofs.

# THEOREM 2.1 (CONCENTRATION AROUND THE ENSEMBLE AVERAGE)

Let a parity-check matrix H be chosen uniformly at random from an ensemble  $LDPC(n,\Lambda,P)$  and let transmission occur over the BEC with erasure probability  $\epsilon$ . We decode the received word with l iterations of message-passing decoding and let  $P_b(H,\epsilon,l)$  denote the final bit-error probability. Then, for a fixed number of iterations l and for any given  $\delta > 0$ , there exists an  $\alpha > 0$ ,  $\alpha = \alpha(\Lambda,P,\epsilon,\delta,l)$ , such

# LDPC CODE CONSTRUCTIONS

**Figure 2.5:** Bit-error rate (left) and block-error rate (right) as a function of the crossover probability  $\epsilon$  on the BSC. The following was repeated for each block length  $2^i$  for  $i=10,11,\ldots,20$  until  $2^{30}$  total bits were transmitted: draw a new code from the (3,6)-regular ensemble, assume the all-zero codeword and simulate transmission over the BSC, decode using 20 iterations of the sum-product decoder. The vertical axis is logarithmic. A bit- or block-error rate of 0 is not plotted.

that

$$P\left\{|P_b(H,\epsilon,l) - \mathbb{E}_{H'\in LDPC(n,\Lambda,P)}\left[P_b(H',\epsilon,l)\right]| > \delta\right\} \le e^{-\alpha n}.$$

Shannon's channel coding theorem gives us limits on how much information we can hope to send over a channel. In this setting we consider transmission over the BSC and look at the block error probability after so-called maximum a posteriori decoding. The binary entropy function is defined by

$$h(p) = -p \log_2(p) - (1-p) \log_2(1-p).$$

THEOREM 2.2 (SHANNON'S CHANNEL CODING THEOREM FOR THE BSC)

Assume transmission over the BSC with crossover probability  $\epsilon$ . Let  $P_B(C, \epsilon)$  be the block-error rate after transmission on the BSC with crossover probability  $\epsilon$  using a code C and decoding using maximum a posteriori decoding. If the rate r satisfies  $0 < r < 1 - h_2(\epsilon)$  then

$$\min_{C \in Shannon(n,2^{\lfloor rn \rfloor})} P_B(C,\epsilon) \xrightarrow{n \to \infty} 0.$$

The above theorem says that we can only hope to transmit with a bit-error rate that approaches zero if the rate of the code is below  $h(\epsilon)$  on the BSC. This is also called the *Shannon capacity* of the channel. Perhaps more importantly, the converse also holds: if we transmit at a rate above the capacity of the channel,

### **Error-correcting codes**

the error probability is bounded away from 0 asymptotically in the block length. It is often more convenient to consider the behavior with a fixed rate r and let the crossover probability  $\epsilon$  vary. In the case that the rate is fixed we want to find the largest  $\epsilon$  such that the error probability still approaches 0 in the block length. We will refer to this as the *threshold* of the channel. That is, the threshold of the channel gives the limit given any code and decoder with a fixed rate. While the limit given any code and decoder is useful, we will more often consider the threshold of a combination of a code and decoder. With a given code and decoder we then mean by the threshold the largest  $\epsilon$  such that the error probability approaches 0 in the block length, using the given code and decoder. Equivalent results can be shown for the BEC and BAWGNC (Richardson and Urbanke, 2008).

Luby et al. (1998, 2001a,b, 1997) as well as Richardson et al. (2001); Richardson and Urbanke (2001a) presented a majority of the tools used to analyze random irregular LDPC code ensembles. An important tool is that of *density evolution*, which is a method for determining the threshold under message-passing decoding. An approximation to density evolution was presented by Chung et al. (2001b). Chung et al. (2001a); Richardson et al. (2000) presented optimized degree distributions with thresholds approaching the Shannon capacity and Richardson and Urbanke (2001a) generalized many results to more general channels.

Finally, while Chung et al. (2001a); Richardson et al. (2000) presented ensembles that approach the Shannon capacity, this was done in a setting where the number of iterations and the block length tend to infinity. Clearly, neither of these assumptions are feasible in practice. Degree distributions that approach the Shannon capacity asymptotically can perform badly with a finite number of iterations and finite block lengths. For this reason, designing good codes in the finite setting requires slightly different tools. Richardson et al. (2001) note that density evolution can be applied to some extent to codes of finite length which are decoded using a finite number of iterations. The performance of codes with practical limitations has been studied by Amraoui et al. (2009); Di et al. (2002); Richardson (2003); Richardson et al. (2002), and some ways to construct good finite-length codes are presented by Mao and Banihashemi (2001); Yue et al. (2007). Of particular importance for the error-correcting performance of codes decoded using message-passing algorithms are so-called *stopping sets* and short cycles in the Tanner graph. Since the focus of this thesis is more on encoding and decoding of given codes, rather than code constructions, we will not go into detail about what makes a good code. However, the intuition behind the reason for stopping sets and short cycles being problematic is easy to see. Stopping sets are subsets of the nodes of a Tanner graph in which it is in some sense difficult to resolve what the real values of the variable nodes should be. Variables nodes in a stopping set will therefore often be decoded wrongly, and if the stopping

# LDPC CODE CONSTRUCTIONS

sets are large the error floor of a code will be higher. We will take a closer look at message-passing decoders in Chapter 4 and why short cycles in the Tanner graph are harmful for them.

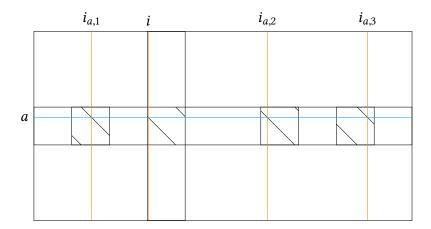

# 2.4.4 Quasi-cyclic LDPC codes

Different constructions of *quasi-cyclic* LDPC (QC-LDPC) codes were presented by Tanner et al. (2004) and Myung et al. (2005). The general structure of the parity-check matrix of a QC-LDPC code is the following: H consists of several square submatrices, each of which is either the zero matrix or the identity matrix with the diagonal shifted cyclically to the right by some amount. More precisely, for a code of length n, the parity-check matrix consists of submatrices of size  $z \times z$ . The code is compactly described by a smaller matrix of size

$$m_M \times n_M = \frac{m}{z} \times \frac{n}{z}$$

where we assume that z divides both m and n. The smaller matrix  $H_M$  is called the *model* matrix. Each entry of the model matrix specifies the kind of submatrix at that position in H. A non-negative integer entry specifies an identity matrix shifted by the given entry, and "-" specifies a zero matrix.

# Example 4 (WiMAX model matrix)

The rate- $\frac{1}{4}$  code with block length 2304 and submatrix size 96 in the WiMAX standard is specified by the model matrix

$$H_{M} = \begin{pmatrix} 6 & 38 & 3 & 93 & - & - & - & 30 & 70 & - & 86 & - & 37 & 38 & 4 & 11 & - & 46 & 48 & 0 & - & - & - \\ 62 & 94 & 19 & 84 & - & 92 & 78 & - & 15 & - & - & 92 & - & 45 & 24 & 32 & 30 & - & - & 0 & 0 & - & - \\ 71 & - & 55 & - & 12 & 66 & 45 & 79 & - & 78 & - & - & 10 & - & 22 & 55 & 70 & 82 & - & - & 0 & 0 & - \\ 38 & 61 & 1 & 66 & 9 & 73 & 47 & 64 & - & 39 & 61 & 43 & - & - & - & 95 & 32 & 0 & - & 0 & 0 & - \\ - & - & - & - & 32 & 52 & 55 & 80 & 95 & 22 & 6 & 51 & 24 & 90 & 44 & 20 & - & - & - & - & 0 & 0 \\ - & - & 61 & 31 & 88 & 20 & - & - & - & 6 & 40 & 56 & 16 & 71 & 53 & - & - & 27 & 26 & 48 & - & - & - & 0 \end{pmatrix}.$$

(2.2)

QC-LDPC codes are convenient because they have a compact description. In addition, the same model matrix can be used for a range of block lengths. For example, in the WiMAX standard (IEEE, 2009), the same model matrix defines codes for block lengths from 576 bits to 2304 bits. The description of QC-LDPC codes above still leaves room for choosing the model matrix in different ways. One possibility is presented by Myung et al. (2005). The degrees of the model matrix are retained when it is expanded to the full parity-check matrix and so Myung et al. propose to choose an appropriate degree distribution for the model matrix to obtain a parity-check matrix which has similar properties to an irregular code with the same degree distribution. The positions of the nonzero block matrices and the shifts are chosen to maximize the girth, meaning the length of the shortest cycle, of the resulting parity-check matrix, or more accurately of its Tanner graph.

### **Error-correcting codes**

The parity-check matrix in Example 4 has additional structure on the right-hand side, which ensures that the code can be encoded in linear time. We will present the construction in more detail in the following chapter.

# 2.5 Codes used in practice

LDPC codes have been included in several standards in the recent years. We review some of them here as they are of interest for decoding purposes. A code, once in a standard, remains fixed for the lifetime of the standard. However, decoders can be changed independently of the codes as inprovements are made to decoders. Thus it is useful to know the structure of codes used in practice, and use them as benchmarks for decoding algorithms.

#### 2.5.1 DIGITAL VIDEO BROADCASTING

The Digital Video Broadcasting (DVB) standards for terrestrial, satellite and cable broadcasts (ETSI, 2012, 2013a,b) employ a compact scheme for describing the codes. The DVB codes are defined by o lists of offsets, each of length  $o_i$ . The offsets determine the positions of the ones in the parity-check matrix. The parity-check matrix has the following structure:

$$(H_0 \quad H_1 \quad \cdots \quad H_{s-1} \quad H_p,)$$

where  $H_p$  is an  $m \times m$  matrix with ones only on the full diagonal and in one position below the diagonal. The matrices  $H_i$  for i = 0, 1, ..., s - 1 are each of size  $m \times 360$ , where 360 is a constant defined for all LDPC codes in the DVB standards. The ith list of offsets determines the positions of the ones in  $H_i$ . Let  $b_{ia}$  denote the ath element of the ith list of offsets. Then, for column j of the full parity-check matrix H, where the column is within a submatrix  $H_i$ , the positions of the ones in that column are determined by

$$(b_{ia} + (j \mod 360)Q) \mod m, \quad \forall a \in 1, 2, \dots, o_i.$$

The value *Q* is another constant defined in the standard which is dependent on the rate of the code. The right-hand side of each parity-check matrix in the DVB standards is lower triangular which, as we will see in the next chapter, means that the code can be encoded in linear time.

#### 2.5.2 WIMAX AND WIFI

The WiMAX standard defines a few different code types for error-correction. One of them is LDPC codes (IEEE, 2009). The code type used in the WiMAX standard is a quasi-cyclic code. It defines codes of lengths between 576 and 2304 bits. Example 4 shows the rate- $\frac{1}{4}$  code defined in the standard. The standard has defined codes of rates  $\frac{1}{2}$  and  $\frac{1}{4}$ .

The WiFi standard also uses a QC-LDPC code for error correction. The structure is the same as in the WiMAX standard. The block lengths are 648, 1296 and 1944 bits with rates of  $\frac{1}{2}$ ,  $\frac{2}{3}$ ,  $\frac{3}{4}$  and  $\frac{5}{6}$ .

# 2.5.3 ETHERNET

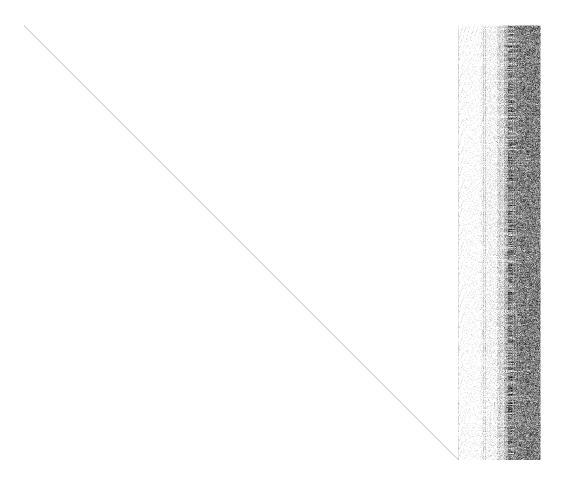

The Ethernet standard (IEEE, 2012a) also uses LDPC codes for error-correction. Figure 2.6 shows the parity-check matrix of the rate-0.84 LDPC code defined in the Ethernet standard.

**Figure 2.6:** The parity-check matrix of the rate-0.84 LDPC code with block length 2048 defined in the Ethernet standard. Each black dot denotes a 1 in the parity-check matrix.

# 2.6 Summary

We have now presented the basics of codes and in particular LDPC codes, which are a class of binary linear codes with sparse parity-check matrices. Particularly important are the code constructions. The irregular codes based on the configuration model are the basis for codes that can in general be encoded in linear time and perform well under message-passing decoding. The tools developed for irregular codes can also be used for QC-LDPC codes, and in these are used in practice in many standards.

One type of LDPC codes that we have left out are codes based on finite geometries (Kou et al., 2001). Kou et al. have shown that finite geometry codes can have good theoretical properties. However, they often contain high degree variable and check nodes, which increases the complexity significantly (Cho et al., 2010). To the best of the author's knowledge, they have also not been included in any current communications standards.

# Chapter 3

# Encoding of LDPC codes

Although much of the focus in research of LDPC codes has been on *decoding* of the codes, encoding is equally important in terms of time complexity. For general LDPC codes, encoding can not as of today be done in linear time. The biggest contribution to date is that of Richardson and Urbanke (2001b). They show that LDPC codes with a carefully chosen degree distribution can be encoded in linear time. In addition, they show that these codes are good for message-passing decoders in the sense that they can approach the Shannon limit using message-passing decoders. Simpler code constructions can also yield linear time encoding but may not be as good for error-correction.

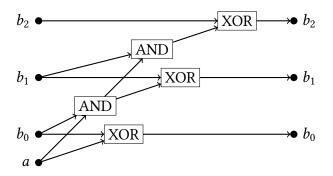

Encoding consists of taking *k* information bits and adding *parity bits* such that the information bits and the parity bits together form a codeword. The parity bits are essentially chosen by first setting the information bits in fixed positions of the codeword. Once the information bits have been fixed, the parity bits can be determined by solving a set of linear equations. The naïve method, which we will present first in Section 3.1, does this by Gaussian elimination. This method is simple but has quadratic time complexity. In Section 3.2 we will present the method by Richardson and Urbanke (2001b) where the rows and columns of a parity-check matrix are only *permuted* such that the system of linear equations we are solving is defined by a nearly triangular matrix. Doing this reduces complexity significantly.

# 3.1 Encoding using the systematic generator matrix

An LDPC code is defined by its parity-check matrix H of size  $m \times n$ . By setting H in an appropriate form we can form what is called a *generator matrix* of the code. With the help of the generator matrix G, we can then encode the binary vector  $\mathbf{u}$ , also called the *information bits*, into a codeword  $\mathbf{x}$  by  $\mathbf{u}G = \mathbf{x}$ . We assume that all vectors are *row* vectors. We let k = n - m be the number of information bits.

### **ENCODING OF LDPC CODES**

Let  $I_m$  be the identity matrix of size  $m \times m$ . To begin with, we transform the parity-check matrix into its *systematic form*

$$H = \begin{pmatrix} -P^T & I_m \end{pmatrix}.$$

A parity-check matrix can always be brought into the systematic form using Gaussian elimination without changing the code. This means that we only use standard row operations: permutations and additions of rows. We can thus for the purposes of encoding assume that H is in systematic form. Now, given H, we denote

$$G = \begin{pmatrix} I_{n-m} & P \end{pmatrix}.$$

Any word generated by the generator matrix *G* is a codeword, which we can see by checking that the syndrome is the zero vector:

$$Hx^{T} = H (\mathbf{u}G)^{T}$$

$$= (-P^{T} I_{m}) (\mathbf{u} (I_{n-m} P))^{T}$$

$$= (-P^{T} I_{m}) (\mathbf{u} \mathbf{u}P)^{T}$$

$$= (-P\mathbf{u} + P\mathbf{u})^{T}$$

$$= \mathbf{0}^{T}$$

We can also see that the resulting codeword is of the form  $\mathbf{u}G = \mathbf{x} = (\mathbf{u} \ \mathbf{x}_p) = (\mathbf{x}_s \ \mathbf{x}_p)$ . The first part of the codeword,  $\mathbf{x}_s$ , has length k and is called the systematic part of the codeword. It is also exactly the information bits we wish to send. The second part,  $\mathbf{x}_p$ , is of length m and contains the *parity bits*. If we assume that the parity-check matrix can be brought into systematic form it implies that the parity-check matrix is of full rank, and if we assume that the parity-check matrix is of full rank there will be a unique codeword for each word we wish to encode. We will for the remainder of this thesis assume that the parity-check matrix is of full rank. As an example, Figure 3.1 shows the generator matrix of the code specified in the Ethernet standard in systematic form.

While this method can be useful for shorter codes, it becomes impractical for larger block lengths. For general LDPC codes, the matrix P will be dense, meaning it will have  $O(n^2)$  nonzero elements as a result of the Gaussian elimination. This leads to  $O(n^2)$  time complexity for the encoding due to the matrix-vector multiplication. Given that an LDPC code by definition only has a linear number of elements in its parity-check matrix, one could wish that encoding could also be done in linear time. In the next section we will see how this can be done for certain codes.

**Figure 3.1:** The generator matrix of the rate-0.84 LDPC code with block length 2048 defined in the Ethernet standard. Each black dot denotes a 1 in the matrix.

# 3.2 Encoding with approximate lower-triangular parity-check matrices

MacKay (1999) introduced the idea of LDPC codes that can be encoded in linear time with parity-check matrices that are almost lower triangular. In that case we can perform back-substitution for most of the parity-check bits, but some additional work still has to be done. Richardson and Urbanke (2001b) expanded on this idea and generalized the results on when random irregular LDPC codes can be encoded in linear time. They showed that if the degree distribution of an ensemble of irregular codes is chosen appropriately encoding of a code in that ensemble can in expectation be done in linear time. They also showed that if an ensemble has a degree distribution for which linear time encoding is possible, that ensemble of codes will also behave well under message-passing decoding.

This is a particularly interesting result. While the problem of linear time encoding for general LDPC codes was not solved, the codes that one often wants to use in practice can be encoded in linear time.

However, with the rising popularity of bit-flipping decoders, the above result still calls for an answer to the question whether or not all LDPC codes can be encoded in linear time. Optimal degree distributions for message-passing algorithms do not necessarily lead to optimal performance for bit-flipping algorithms. It is also good to note here that the linear time complexity really only applies to the *encoding* process, and ignores a preprocessing step which needs to be done only once for a code.

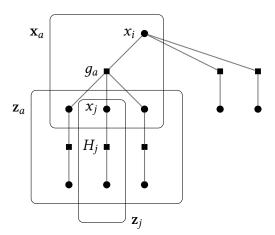

The encoding method of Richardson and Urbanke has three steps: (i) a preprocessing step, in which the parity-check matrix is brought into an appropriate form by only column and row permutations, (ii) a second preprocessing step, in which a matrix inverse is calculated; and (iii) the actual encoding step, in which the parity-check matrix from the previous step can be used to encode the information bits **u** in linear time. We will begin by looking at the second and third steps, but it is useful to keep in mind that in the first step we only use row and column *permutations*, meaning that the modified parity-check matrix still has a linear number of nonzero elements.

In the encoding step, we assume that the parity-check matrix has been brought into the following form:

$$H = \begin{pmatrix} A & B & T \\ C & D & E \end{pmatrix}.$$

The matrix A is of size  $m-g\times k$ , B is of size  $m-g\times g$ , T is of size  $m-g\times m-g$ , C is of size  $g\times k$ , D is of size  $g\times g$  and E is of size  $g\times m-g$ . The matrix T is a lower triangular matrix. We say that the parity-check matrix is in an *approximate lower-triangular form*. The parameter g is called the gap of the parity-check matrix. If the gap is zero, encoding can be done simply by back-substitution: first set the information bits in the first positions of the codeword after which the parity bits can be solved by back-substitution. If the gap is of size  $O(\sqrt{n})$ , it turns out that encoding can still be done in linear time. To proceed with the encoding, we first premultiply H by

$$\begin{pmatrix} I_{m-g} & 0 \\ -ET^{-1} & I_g \end{pmatrix}$$

resulting in

$$\begin{pmatrix} A & B & T \\ -ET^{-1}A + C & -ET^{-1}B + D & 0 \end{pmatrix}.$$

As we are premultiplying by an invertible matrix the code remains equivalent to the original code. After this step, encoding corresponds to solving two sets of linear equations:

$$A\mathbf{x}_s^T + B\mathbf{x}_{p_1}^T + T\mathbf{x}_{p_2}^T = \mathbf{0}^T,$$

$$(-ET^{-1}A + C)\mathbf{x}_s^T + (-ET^{-1}B + D)\mathbf{x}_{p_1}^T = \mathbf{0}^T.$$

Similarly to the case of systematic encoding, the codeword is  $\mathbf{x} = (\mathbf{x}_s \ \mathbf{x}_{p_1} \ \mathbf{x}_{p_2})$ . The parity bits are now split up into two parts,  $\mathbf{x}_{p_1}$  and  $\mathbf{x}_{p_2}$ , where  $\mathbf{x}_{p_1}$  is of length g and  $\mathbf{x}_{p_1}$  of length m - g.

We then define  $\phi = -ET^{-1}B + D$  and assume that it is invertible. Then, given  $\phi^{-1}$  we can solve the first set of parity bits by

$$\mathbf{x}_{p_1}^T = -\phi^{-1}(-ET^{-1}A + C)\mathbf{x}_s^t.$$

Once we have solved for  $\mathbf{x}_{p_1}$ , we can determine  $\mathbf{x}_{p_2}$  by back-substitution from

$$T\mathbf{x}_{p_2}^T = -A\mathbf{x}_s^T - B\mathbf{x}_{p_1}^T$$

as *T* is lower triangular.

In practice, one performs the premultiplication step by Gaussian elimination. The matrix  $\phi$ , however, might not be invertible after performing Gaussian elimination. In that case we permute columns from the left part of the parity-check matrix into  $\phi$  so that it is invertible. If this is in fact not possible, the parity-check matrix is not of full rank, but as we mentioned earlier the probability of this happening decreases with the block length and in practice we need not worry about this.

On the whole, we now have that if the parity-check matrix is in an approximate lower-triangular form, and the matrix inverse  $\phi^{-1}$  has been precalculated we can perform encoding in  $O(n+g^2)$  time. Let us see why this is so. First, inverting T need not be done explicitly and can be done by backsubstitution. Additionally, since T is sparse this requires O(n) operations. Second, all matrix-vector multiplications involve sparse matrices with O(n) elements, again requiring O(n) operations. Finally, we can avoid performing matrix-matrix multiplications and instead always perform matrix-vector multiplications. The exception to sparse matrix-vector multiplication is the multiplication by  $\phi^{-1}$  which is a dense matrix-vector multiplication. This contributes the  $g^2$  term in the running time.

What remains is to show that the original parity-check matrix can be brought into the needed approximate lower-triangular form. Richardson and Urbanke do not show a way to find the minimum gap, but propose a greedy algorithm which they show is good enough for achieving linear-time encoding complexity for some codes. The algorithm proceeds in rounds, incrementally building up

the right-hand side lower-triangular matrix T. Following the terminology of Richardson and Urbanke (2008) we let two parameters, g and t run during the algorithm. The current gap is given by g and the iteration number is given by t. The *residual* parity-check matrix H is at each step the submatrix of H consisting of rows 1 to m - g - t - 1 and columns 1 to n - t - 1. The *residual degree* of a column or row in the residual parity-check matrix is equivalent to the *weight* of that column or row in the residual matrix.

The algorithm consists of two main steps, *extend* and *choose*. In the extend step we assume that there exists a column of residual degree one. We choose one column with residual degree one uniformly at random. Let c be the chosen column and r the row containing the only nonzero entry of that residual column. We then swap column c with column n-t-1 and row r with row m-g-t-1. This places the nonzero entry in the lower-right corner of the residual matrix and extends the diagonal on the right-hand side by one. Finally, t is incremented by one.

The choose step is performed when there are no columns with residual degree one. We choose a column uniformly at random from the column or columns with the minimum residual degree d, and call this column c. Then, choose an arbitrary row with a nonzero entry in the residual part of column c and call it r. Swap column c and row r into the lower-right corner of the residual matrix as in the extend step. Move the remaining d-1 rows with nonzero entries in column c to the bottom of the full parity-check matrix. Finally, increment t by one and t by t d t 1.

The algorithm begins by considering the full parity-check matrix H and setting t = g = 0. The algorithm stops when t + g = m. If there is at least one column with residual degree one, perform the extend step, and otherwise perform the choose step. At the end of the algorithm, the resulting parity-check matrix is in approximate lower-triangular form with gap g.

Finally, for linear time encoding, we would need to show that the gap g will on average be of size  $O(\sqrt{n})$  if we choose the degree distribution appropriately. We will not show how to achieve this here because of the lengthy details, but the general idea is to model the residual degree distributions of the parity-check matrix and the gap using a set of differential equations along the course of the greedy upper triangulation algorithm. This way one can arrive at an asymptotic value for the gap such that elements from the ensemble will have a gap that is close to the asymptotic value with high probability. Although Richardson and Urbanke (2001b) give more detailed conditions on when the average gap will be small enough for linear-time encoding, the intuition is that there needs to exist a large enough number of variable nodes of degree two. When this holds, there will more often exist a column of residual degree one in the extend step meaning

that the gap is not increased. If no column of residual degree one exists, the gap will still often be increased by only one in the choose step because of the large number of variable nodes with degree two.

#### 3.2.1 IRREGULAR CODES WITH A FIXED GAP

Although Richardson and Urbanke (2001b) show that codes with certain irregular degree distributions can be brought to a form where the parity-check matrix has a gap which is proportional to  $\sqrt{n}$ , and the codes corresponding to those distributions can therefore be encoded in linear time, Freundlich et al. (2007) present an alternative approach to achieve this. Instead of letting all configurations be possible with a given degree distribution pair, they propose to constrain the construction of the code so that it will have a predetermined gap q. They achieve this by essentially fixing the diagonal elements of T in the approximate lowertriangular decomposition to be ones, such that T is of size m - q. After that one proceeds to again randomly assign edges between variable and check nodes, but disallowing edges that go above the diagonal in T, enforcing the approximate lower-triangular form. They show through examples that forcing the gap to be proportional to  $\sqrt{n}$  does not noticeably impact the performance of the code, while it of course guarantees linear-time encoding. On the other hand, setting the gap to be 0 or close to 0 does decrease the error-correcting performance of the codes.

## 3.2.2 Quasi-cyclic LDPC codes with approximate lower-triangular parity-check matrices

The encoding method of Richardson and Urbanke was applied to quasi-cyclic codes to achieve linear-time encoding when the cyclic shifts of the submatrices are chosen appropriately (Myung et al., 2005). The construction leads to the matrix  $\phi$  being an identity matrix, meaning that the encoding method becomes a linear-time operation even when one includes preprocessing. For this to hold, the model matrix specifying the parity-check matrix must be of the form

$$H_{M} = \begin{pmatrix} b_{1} & 0 & - & \cdots & - & - \\ - & b_{2} & 0 & \cdots & - & - \\ \vdots & - & b_{3} & \cdots & - & - \\ y & \vdots & \vdots & \cdots & \vdots & \vdots \\ \vdots & \vdots & \vdots & \cdots & 0 & - \\ - & - & - & \cdots & b_{m-1} & 0 \\ x & - & - & \cdots & - & b_{m} \end{pmatrix},$$

where the part of the model matrix corresponding to the information bits  $H_I$  can be freely chosen. The shift values x, y and  $b_i$  for i = 1, ..., m must, however, fulfill one of the following two criteria:

$$x \equiv \sum_{i=1}^{m} b_i \mod L \quad \text{and} \quad y \equiv -\sum_{i=l+1}^{m} b_i \mod L$$

(3.1)

or

$$\sum_{i=1}^{m} b_i \equiv 0 \mod L \quad \text{and} \quad x \equiv y + \sum_{i=l+1}^{m} b_i \mod L.$$

(3.2)

We will without proof state that if the shift values fulfill one of the two criteria (3.1) or (3.2), then  $\phi$  becomes the identity matrix in which case it is trivially invertible. We also do not need to perform the matrix-vector multiplication which causes the  $O(q^2)$  term in the general encoding algorithm.

The authors performed limited tests with these kinds of codes but showed that a QC-LDPC code of this kind performed equally well as a non-quasi-cyclic code with the same degree distribution. The degree distribution of the random code was an optimized distribution obtained by Richardson and Urbanke (2001b). The degree distribution for the quasi-cyclic code was chosen to be the same as for the non-quasi-cyclic code but the coefficients were rounded to fit the block structure of the code. The LDPC codes in the WiMAX standard are quasi-cyclic LDPC codes with the structure presented here allowing them to be encoded in linear time. In the code presented in (2.2), the set of equations in (3.1) is satisfied by setting  $b_1 = x = 48$  and  $y = b_2 = b_3 = \ldots = b_6 = 0$ .

#### 3.3 Summary

While the state of encoding of LDPC codes is in some aspects a solved problem in practice, the lack of a linear-time encoding algorithm for *all* types of LDPC codes still leaves something to be desired. The QC-LDPC construction is a convenient construction that has proven itself to work well enough for inclusion in communications standards. In addition, it allows for a compact implicit description of the parity-check matrix. The irregular ensembles of LDPC codes which can be encoded in linear time have the additional benefit of working well with message-passing decoders. However, being able to use arbitrary LDPC codes that can still be encoded in linear time may allow the use of codes which have better error-correcting capabilities.

## Chapter 4

## DECODING OF LDPC CODES

Decoding of LDPC codes has, unlike encoding, essentially been a linear-time operation since Gallager's introduction of LDPC codes. More precisely, there are linear-time algorithms for *approximate* decoding. Optimal decoding, on the other hand, is difficult. Berlekamp et al. (1978) showed that a certain decision problem related to binary linear codes is NP-complete. The approximate schemes are often, however, good enough in practice and can in some cases approach the capacity of the channel asymptotically in the block length n. In addition, any decoding algorithm that is superlinear is bound to be impractical for arbitrarily large block lengths n as in most situations the decoding throughput needs to equal the channel throughput. The reason for wanting to use longer block lengths is the improvement in error-correcting performance as the block length is increased. One of the reasons for this is that a longer code is more robust to noise in the sense that variations in the level of noise are less significant for larger block lengths. For example on the BSC, we can consider the number of bits that are flipped by the channel constant for large enough block lengths. Another aspect is that correlated noise is more likely to corrupt whole blocks if the block length is short. A code with longer block length is robust to longer *bursts* of errors.

One should keep in mind that when we talk about decoding we mostly talk about the process of recovering a codeword given word received from the channel. However, the full process of decoding of course includes recovering the original information bits but, as we saw in Chapter 3, doing this is easy as the information bits will generally explicitly be part of the codeword.

Gallager (1962) introduced two types of decoders: (i) a simple, so called bit-flipping decoder, which was then deemed insufficient in its ability to decode; and (ii) a message-passing decoder which performed much better but was more complex. The bit-flipping decoders and the message-passing decoders are the two major classes of decoders being actively researched at this point. A third class of decoders into which research is being done is that based on linear programming as first presented by Feldman (2003); Feldman et al. (2005). To the best of the author's knowledge, these decoders are to date neither efficient enough nor good enough

at correcting errors compared to the two other classes of decoders. However, their benefits lie in easy analysis with established tools from linear programming theory, and work is also being made to reduce the complexity of the decoders (Burshtein, 2009; Burshtein and Goldenberg, 2011; Goldin and Burshtein, 2013; Vontobel and Kötter, 2007). In this thesis, however, we will restrict ourselves to only consider message-passing decoders and bit-flipping decoders.

The message-passing decoders are in general better at correcting errors and were the main type of decoders considered as LDPC codes were rediscovered in the 1990's. However, more recently bit-flipping decoders have received much more attention because of their low complexity which is beneficial for efficient hardware implementations. To clarify, when we talk about complexity in the context of decoders we refer to arithmetic complexity of the decoders, not asymptotic complexity. In addition, the decoders used are in essence linear-time algorithms by choice, and the error-correcting performance and arithmetic complexity is then improved given the constraint that the decoding must be linear-time. The main focus for message-passing decoders has been to decrease complexity without loosing too much in terms of error-correction performance. The focus for bit-flipping decoders has been the opposite: improve the error-correction performance while keeping the complexity low. Currently there is essentially a continuum of decoders all making a trade-off between complexity and error-correction performance.

To be precise, we are assuming an MBRAM machine model for the computations: a random access machine (RAM) with addition, subtraction, multiplication, division and bitwise Boolean instructions, where we assume that all operations take  $O(\log n)$ -time where n is the size of the largest input operand or output involved in the instructions. In practice, however, we assume that instructions take O(1)-time with fixed-width inputs and outputs (van Leeuwen, 1990).

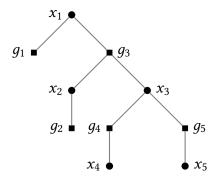

We will look at the decoders roughly in order of complexity. We begin by considering bit-flipping decoders in the next section because of their relative simplicity and to get a first idea of how decoding can be done. We will then move on to message-passing decoders which require some background in graphical models. We will review the most important aspects of *factor graphs* to present the *sum-product* algorithm, which is also known as *belief propagation*. However, the message-passing decoders can be intuitively understood even without the factor graph framework.

## 4.1 Naïve decoding

Before looking at the practical algorithms, we will note that we can perform exact maximum-likelihood decoding of LDPC codes with the caveat that it has exponential time complexity. For completeness we state here the simple algorithm. If we assume the BSC, maximum-likelihood decoding for a code C simply consists of finding the codeword  $\mathbf{x}'$  which is nearest to the received word  $\mathbf{y}$ . We then hope that the decoded codeword  $\mathbf{x}'$  is the same as the sent codeword  $\mathbf{x}$ . The decoded codeword is chosen to be

$$\mathbf{x}' = \arg\min_{\mathbf{z} \in C} w(\mathbf{z} - \mathbf{y}).$$

Here we clearly have an exponential number of candidates. Trying to be more clever and beginning the search with the words closest to the received word is also of no help, as we want that the code has a minimum distance which increases linearly with the block length. This way we will still end up looking at an exponential number of candidates.

## 4.2 BIT-FLIPPING DECODING

Bit-flipping decoders take a straightforward approach to decoding. Given the received word y one can start flipping bits in y according to some appropriate order and criterion in the hope that one will eventually arrive at the original codeword x. In a sense we wish perform a local greedy search in promising directions around the received word. This approach leads at its simplest to low-complexity decoders, which however lack in error-correcting performance compared for example to the sum-product decoder. Adding more information or noise to the decisions of a bit-flipping decoder can already lead to much better performance while keeping the complexity of the decoder fairly low.

## 4.2.1 Gallager's bit-flipping decoder

Gallager's bit-flipping decoder (Gallager, 1962) is the first and perhaps the simplest bit-flipping decoder for LDPC codes. It proceeds as follows: for each variable node count the number of adjacent check nodes that are unsatisfied or, equivalently, how many parity-check equations in which the variable is involved are unsatisfied; if the number of unsatisfied checks is greater than or equal to some chosen constant K, flip the value of the bit. The algorithm proceeds for a fixed number of rounds through all variables, or until all parity-check equations are satisfied.

There are two main considerations to bit-flipping decoders. The first is how to decide whether a bit should be flipped or not. The second is in which order bits are considered, and if multiple bits are considered at the same time. The second aspect will be referred to as a *schedule* in the following.

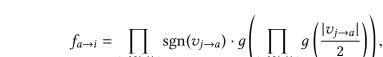

#### 4.2.2 Weighted bit-flipping decoders