Jussi Hanhirova

# Performance analysis of hardware accelerated scheduling

School of Science

Thesis submitted for examination for the degree of Master of Science in Technology. Espoo 12.11.2014

Thesis supervisor:

Prof. Heikki Saikkonen

Thesis advisor:

D.Sc. (Tech.) Vesa Hirvisalo

Code: T-106

Author: Jussi Hanhirova

Title: Performance analysis of hardware accelerated scheduling

| Date: 12.11.2014     | Language: English           | Number of pages: $7+71$ |

|----------------------|-----------------------------|-------------------------|

| Department of Comput | ter Science and Engineering |                         |

Professorship: Software systems / Embedded systems

Supervisor: Prof. Heikki Saikkonen

Advisor: D.Sc. (Tech.) Vesa Hirvisalo

Performance analysis of heterogeneous MPSoCs (Multiprocessor System-on-Chip) is difficult. The non-determinism of parallel computation, communication delays and memory accesses force the system components into complex interaction. Hard-ware acceleration is used both to speedup the computations and the scheduling on MPSoCs. Finding a accompanying software structuring and efficient scheduling algorithms is not a straightforward task.

In this thesis we investigate the use of simulation, measurement and modeling methods for analyzing the performance of heterogeneous MPSoCs. The viewpoint of this thesis is in simulation and modeling: How a high abstraction level simulation methodology can be used in modeling and analyzing of parallel systems based on MPSoCs. In particular we are interested in efficient use of hardware accelerated scheduling mechanisms and how they can be analyzed.

Both parallel simulation and simulation of parallel systems contains many different methods, tools and approaches that attempt to balance between competing goals and cope with a specific subset of the problem space. Challenge is that in all approaches most of the simulation and modeling related problems remain and new challenges emerge.

This thesis shows that the resource network methodology and dynamic scheduling models are a viable approach in modeling heterogeneous MPSoCs with accelerators. Concrete contributions are based on upgrading an existing simulation framework to support parallelism. Main contribution is on one hand that modeling concepts have been widened, and on the other hand that the supporting mechanisms have been implemented. The thesis work in progress was published in a peer reviewed international scientific workshop and the final results in a peer reviewed international scientific conference. The toolset has also been used in multi-university organized teaching and by the industry.

Keywords: performance analysis, modeling, simulation, parallelism, hardware accelerated scheduling, MPSoC

Tekijä: Jussi Hanhirova Tvön nimi: Laitteistokiihdytetyn vuoronnuksen suorituskykyanalyysi Päivämäärä: 12.11.2014 Kieli: Englanti Sivumäärä:7+71 Tietotekniikan laitos Professuuri: Ohjelmistotekniikka / Sulautetut järjestelmät Koodi: T-106 Valvoja: Prof. Heikki Saikkonen Ohjaaja: TkT Vesa Hirvisalo Heterogeenisten moniydinjärjestelmien suorituskykyanalyysi on haasteellista. Laskennan epä-deterministisyys, kommunikaatioviiveet ja lukuisat muistioperaatiot saattavat järjestelmän komponentit monimutkaisiin vuorovaikutus-Laitteistokiihdytettyjä ajoitusmenetelmiä käytetään nopeuttamaan suhteisiin. ajoituspäätöksiä. Sopivan ohjelmarakenteen ja tehokkaiden ajoitusalgoritmien löytäminen ei ole helppoa. Tässä työssä tutkitaan miten simulointi-, mittaus- ja mallinnusmenetelmiä voi käyttää laitteistokiihdytettyjen moniydinjärjestelmien suorituskykyanalyysiin. Työn näkökulma on simuloinnissa ja mallinnuksessa: Miten korkean abstraktiotason simulointimenetelmät soveltuvat moniydinjärjestelmiin pohjautuvien rinnakkaisten järjestelmien mallinnukseen ja suorituskykyanalyysiin. Erityisen kiinnostuksen kohteena on laitteistokiihdytteisten ajoitusmenetelmien tehokas käyttö sekä analysointi. Rinnakkaissimulointi pitää sisällään erilaisia menetelmiä, työkaluja ja lähestymistapoja jotka pyrkivät tasapainottelemaan ristiriitaisten tavoitteiden välillä. Haasteena on se että kaikissa lähestymistavoissa simulaation ja mallinnuksen useimmat ongelmat säilyvät ja uusia ongelmia ilmaantuu. Työn tulokset viittaavat siihen että resurssiverkkopohjainen menetelmä dynaamisen ajoituksen kanssa on toimiva lähestymistapa rinnakkaisten järjestelmien suorituskykyanalyysiin. Työn konkreettiset tulokset pitävät sisällään olemassaolevan simulointiympäristön päivittämisen rinnakkaisuutta tukevaksi. Keskeinen tulos on toisaalta se että mallinnusmenetelmiä on laajennettu ja toisaalta se että näitä tukevat mekanismit on toteutettu. Keskeneräisen työn tulokset on julkaistu vertaisarvioidussa tieteellisessä seminaarissa ja valmiin työn tulokset vertaisarvioidussa tieteellisessä konferenssissa. Simulointiympäristöä on käytetty usean vliopiston järjestämässä yhteisopetuksessa sekä teollisuudessa. Avainsanat: suorituskykyanalyysi, mallinnus, simulointi, rinnakaisuus, laitteis-

tokiihdytetty vuoronnus, moniydinjärjestelmä

# Preface

I would like to thank Prof. Heikki Saikkonen for supervising the thesis and giving me the opportunity to work full-time with the topic.

I am grateful to D.Sc.(Eng.) Vesa Hirvisalo for support, guidance and all the enlightening discussions during the thesis process.

Finally, I want to thank my wife Piia and my daughter Hilla. I am thankful to Piia for her love and never-ending support and encouragement with my studies and the thesis. Hilla I thank for the happy moments of play at home that always make me realise what really matters in life.

Otaniemi, 12.11.2014

Jussi Hanhirova

Contents

| Ał       | bstract                                                                                                                                                                                                                                                                                           | ii                                                                     |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| Ał       | bstract (in Finnish)                                                                                                                                                                                                                                                                              | iii                                                                    |

| Pr       | reface                                                                                                                                                                                                                                                                                            | iv                                                                     |

| Co       | ontents                                                                                                                                                                                                                                                                                           | v                                                                      |

| Ał       | bbreviations                                                                                                                                                                                                                                                                                      | vii                                                                    |

| 1        | Introduction         1.1       Research problem                                                                                                                                                                                                                                                   | <b>1</b><br>1<br>1<br>2                                                |

| <b>2</b> | Heterogeneous computing systems                                                                                                                                                                                                                                                                   | 4                                                                      |

|          | <ul> <li>2.1 Internet of Things</li></ul>                                                                                                                                                                                                                                                         | $4 \\ 5 \\ 6 \\ 8$                                                     |

| 3        | Performance analysis of computing systems3.1Performance analysis3.2Simulation3.3Parallel simulation3.4Simulators3.5Resource networks                                                                                                                                                              | <ol> <li>11</li> <li>12</li> <li>13</li> <li>15</li> <li>17</li> </ol> |

| 4        | PSE – Performance Simulation Environment         4.1 Queuing network simulation         4.2 Toolset overview         4.3 Modeling workflow         4.3.1 Editor tools         4.3.2 Compiler tools         4.4 Basic building blocks         4.5 Monitoring         4.6 RNS runtime               |                                                                        |

| 5        | Mechanism for resource network simulation         5.1       Modeling hardware accelerated scheduling         5.1.1       Pull mode scheduler         5.1.2       Push mode scheduler         5.1.3       Dynamic scheduling         5.1.4       Modeling memory         5.1.5       Fork and join | <b>31</b><br>31<br>33<br>35<br>36<br>39                                |

|   | 5.2                      | Mapping PSE to hardware                 | 41             |

|---|--------------------------|-----------------------------------------|----------------|

|   | 5.3                      | Parallelizing discrete event simulators | 42             |

|   |                          | 5.3.1 PSE replicated trials             | 43             |

|   |                          |                                         | 45             |

| 6 | Den                      | nonstrative experiment                  | 47             |

|   | 6.1                      | Experiment setup                        | 47             |

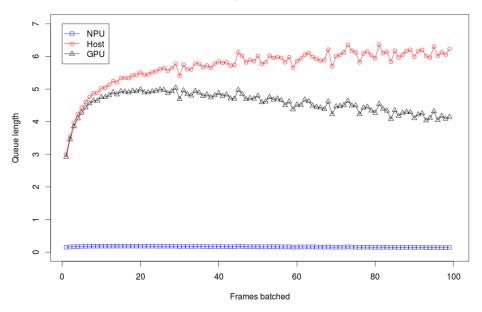

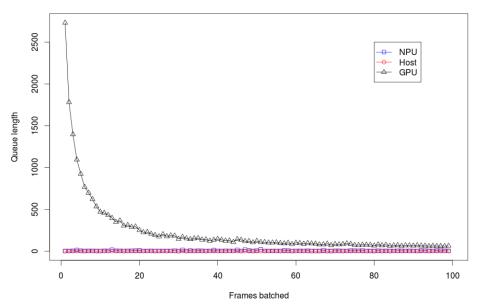

|   | 6.2                      | Simulation results                      | 50             |

|   | 6.3                      | Conclusions on experiment results       | 52             |

|   |                          |                                         |                |

| 7 | Disc                     | cussion                                 | <b>54</b>      |

| 7 | <b>Disc</b><br>7.1       |                                         |                |

| 7 |                          | Challenge                               | 54             |

| 7 | 7.1                      |                                         | 54<br>54       |

| 7 | $7.1 \\ 7.2$             | Challenge                               | 54             |

| 8 | 7.1<br>7.2<br>7.3<br>7.4 | Challenge                               | 54<br>54<br>56 |

# Abbreviations

| API                  | Application Programming Interface     |

|----------------------|---------------------------------------|

| CPU                  | Central processing unit               |

| DATE                 | Design, Automation and Test in Europe |

| DES                  | Discrete event simulation             |

| DSP                  | Digital Signal Processing             |

| ESM                  | European Simulation and Modeling      |

| FIFO                 | First In First Out                    |

| GB                   | Gigabyte                              |

| Gbps                 | Gigabytes per second                  |

| GNU                  | GNU's Not Unix                        |

| GNU Pth              | GNU Portable threads                  |

| GUI                  | Graphical User Interface              |

| HW                   | Hardware                              |

| IP                   | Intellectual property                 |

| ISA                  | Instruction Set Architecture          |

| MB                   | Megabyte                              |

| MPSoC                | Multiprocessor System-on-Chip         |

| NoC                  | Network on Chip                       |

| NPU                  | Network Processing Unit               |

| NSN                  | Nokia Solutions and Networks          |

| OpenEM               | Open Event Machine                    |

| PSE                  | Performance Simulation Environment    |

| QoS                  | Quality of Service                    |

| RNS                  | Resource Network Simulator            |

| RTL                  | Register Transfer Level               |

| $\operatorname{SMP}$ | Symmetric Multi Processing            |

| $\operatorname{SoC}$ | System-on-Chip                        |

| SW                   | Software                              |

| TLB                  | Translation Lookaside Buffer          |

| WCET                 | Worst Case Execution Time             |

# 1 Introduction

This thesis investigates the use of modeling, simulation and measurement for analyzing performance of parallel systems implemented on MPSoCs with accelerators. The contribution of this thesis is to present a way to model and simulate these systems. Concrete contributions are based on updating an existing simulation framework and describing mechanisms necessary for modeling hardware accelerated scheduling.

While simulation is a widely studied field and there are many methods that are used for it, both simulation of parallel systems and parallel simulation are hard. PSE (Performance Simulation Environment) is a toolset aimed at performance analysis of hardware and software co-scheduled manycore systems. PSE fits into the active research field of parallel simulators. PSE applies discrete event simulation of models represented using the resource networks methodology. This thesis shows that the resource network methodology and dynamic scheduling models are a viable approach for modeling heterogeneous MPSoCs with accelerators.

#### 1.1 Research problem

Modern MPSoCs (Multiprocessor System-on-Chip) are tightly connected parallel systems with complex interactions. Performance analysis of these systems is hard because the non-determinism of parallel computation, communication delays and memory accesses force the system components into complex interaction. On top of this, the internal data streams on the MPSoC interact with computation and communication resources affecting their behavior. The resource interaction is further mixed with scheduling, which is usually performed at multiple points in the system. Finally, MPSoCs are usually used to process data streams of dynamic behavior. Generally the worst case inputs for MPSoCs are unknown.

Parallelism is hard to analyze directly using traditional computer system methods, but using different abstraction levels systems based on MPSoCs can be modeled and simulated. Detailed monitoring of the simulation is required to be able to retrieve metrics and traces for performance analysis.

The viewpoint of this thesis is in simulation and modeling: How a high abstraction level simulation methodology can be used in modeling and analysis of parallel systems based on MPSoCs. The research question is following: how to efficiently use hardware accelerated scheduling mechanisms and how hardware accelerated scheduling can be analyzed?

#### 1.2 Contributions

This thesis presents a way how MPSoCs can be modeled using a resource reservation based mechanism. Focus of this thesis is in scheduling, how to model and analyze hardware, software and hybrid scheduled systems. Performance analysis is done by constructing executable models of systems with adjustable monitoring mechanisms. Modeling is based on the use of graphical editor tools which allow model description using basic building blocks. Models are simulated using discrete event based approach.

Concrete contributions of this thesis are based on upgrading an existing simulation framework to support parallelism. Main contribution is on one hand that modeling concepts have been widened and on the other hand that the supporting mechanisms have been implemented. Work done in the thesis has been presented to international scientific community and it has also been used in the university teaching and by the industry.

Contributions can be summarized as follows:

- Upgrading of an existing simulation framework (PSE) to support modeling and simulation of parallel systems.

- Implementation of fundamental models required for performance modeling of hardware scheduled systems.

- The thesis work in progress was published in a peer reviewed scientific workshop 3PMCES at the DATE2014 conference (on 28th March 2014 in Dresden, Germany).[1]

- The results of the thesis were published in a peer reviewed scientific conference ESM'2014 (on 22-24th October 2014 in Porto, Portugal).[37]

- The PSE toolset has been used in multi-university organized teaching [86] during the ParallaX project<sup>1</sup>.

- PSE has been used by the industry partners of the ParallaX project.

The result of the first contribution is an upgrade to an Open Source toolset PSE (Performance Simulation Environment). The upgrading consisted of the implementation and testing of the fork-join mechanism required for modeling simultaneous resource requests. The second contribution includes concrete models and documented description on how they can be used to model the key structures of heterogeneous MPSoCs. The thesis work in progress was presented in form of an abstract paper and a poster at the 3PMCES workshop at the DATE2014 conference. The results of the thesis were presented in form of a regular paper in the ESM'2014 conference. Contribution for the multi-university organized teaching, the ParallaX education day, was to create performance analysis learning material package and teach the basics of PSE modeling workflow for the participants.

#### 1.3 Structure

The structure of this thesis is as follows. First an overview to the context of this thesis is given in Chapter 2 which is titled as Heterogeneous computing systems. Chapter 2 begins by introducing the concept of Internet of Things. Next the multi-and manycores are presented, after which the term high performance embedded

<sup>&</sup>lt;sup>1</sup>ParallaX project is an industry-driven research consortium lead by finnish universities. It is focused in research of parallel systems.[66]

computing is explained. Chapter 2 is concluded by a view to embedded system design.

Chapter 3 takes a wider look to the performance analysis of computing systems. The Chapter 3 begins with an introduction to performance analysis, after which the simulation methodology is presented. Chapter 3 also presents main approaches for parallel simulation and review some recent simulators. Chapter 3 concludes in opening up the resource networks concept.

Chapter 4 presents the PSE (Performance Simulation Environment) toolset. First an overview to PSE is made and the basic modeling workflow is described. Next the basic building blocks of PSE are introduced, after which the monitoring functionality and the RNS runtime are presented.

In Chapter 5 the mechanisms for resource network simulation are introduced and problems related to parallelizing the simulator are discussed. In particular concrete examples are given how hardware accelerated scheduling and memory systems can be modeled.

In Chapter 6 a demonstrative experiment using PSE is presented. The demonstrative experiment shows how PSE can be used in early design space exploration of networked computing systems.

Chapter 7 sets PSE into a wider context, underlines the main problems facing the field of parallel simulation and discusses possible solutions for the problems.

The conclusions are presented in Chapter 8 which forms the last Chapter of this thesis.

# 2 Heterogeneous computing systems

In this chapter the context of this thesis is presented. This chapter begins with a view to the Internet of Things (IoT) and the main technologies behind its evolution. Next, implications of IoT to the requirements in computational performance are presented. To conclude this chapter the challenges in embedded system design are presented.

The interested reader can refer to [89] for a hardware point of view to parallelism and to [69] for a software point of view on programming heterogeneous parallel systems, [53] can be used as a reference for performance analysis and [40] for parallel simulation. Additional materials have been referred to with the introduction of the topics.

#### 2.1 Internet of Things

Internet of Things (IoT) refers to connecting objects as independently identifiable entities to the Internet. In year 2008 the number of devices connected to the Internet outnumbered the human population, and in 2013 the number had reached 13 billion. According to Cisco there will be about 50 billion Internet-connected devices in 2020. [38]

These IoT objects have a large variance in size, in the type of data they produce or process, and in the real-time performance requirements. The objects can be anything from vehicles like boats or cars to agricultural field sensors, or from medical implants to everyday things such as food packages, furniture and clothes. What these objects share in common is that they are embedded systems equipped with sensors and Internet connection.[38]

The massive boom in the number of new Internet-connected devices has been enabled by the development in chip and sensor manufacturing technologies [52] and in the wireless communication technologies [39], such as software defined radio [69]. Chips and sensors are not just unprecedentedly cheap to make, but they also consume negligible amounts of energy. Multiple small devices can be interconnected to form wireless sensor networks and using energy harvesting technologies they can be made self-sustaining.[106, 113]

An important branch of IoT is the ITS (Intelligent Traffic System) applications. The concept of ITS is based on collecting data with sensors installed in vehicles and the surrounding infrastructure, processing and extraction information out of that data, and then sharing that through different communication means. Many of the ITS applications are hard-real time systems, where missing a deadline in computation could lead into fatal consequences.[99]

Another branch of IoT is the industrial Internet, where physical machines and networked sensors are integrated to form complex control systems. An overview of IoT and related technologies can be found from [8]. Current trends and future visions of IoT can be read from [24]. A survey to (energy efficient) wireless communication technologies is in [39], wireless sensor networks are described in [113], energy harvesting technologies are surveyed in [113, 106] and the concept of Intelligent Traffic Systems is presented in [99].

In general IoT applications can be seen as systems that process sensor data streams. The amount of data being transmitted in the Internet is constantly growing. The data stream behavior, which can be static or dynamic, is central to the computational requirements of the system. In case of dynamic data streams system scheduling is a key issue. Hardware scheduling is used in systems that process dynamic data streams because hardware by nature is parallel and can see the system as whole. This contrasts to software which needs to browse through data structures step-by-step.[89]

In contrast to general IoT applications, many applications in the High Performance Computing (HPC) domain are considered tightly connected. They generate vast amounts of data that needs to be aggregated on-the-fly near the sensors. Software does not seem to scale for this kind of work, instead hardware schedulers and supporting hardware structures need to be used.[20]

#### 2.2 Multi and manycores

Moore's law still holds today – more and more transistors can be packed to a smaller area.[74] Dennard scaling, introduced in 1974, has been the driving force behind Moore's law. Dennard scaling argumented that the performance per watt of processors is growing exponentially at roughly the same rate as transistor density in Moore's law.[32] But Dennard scaling no longer holds – at small sizes current leakage power becomes significant and leads to the so-called *power wall* [89]. The power wall and other challenges related to chip manufacturing techniques has lead chips to the age of *dark silicon* [97]. Dark silicon refers to current chip architectures which utilize dynamic voltage and frequency management to power up only certain regions of a chip at a time. As power has become the main limiting factor in computation, more power efficient implementations of hardware functionalities translate directly to better computational performance.[89]

Multicores are systems in which from two to slightly over ten processors are connected to resources via a shared bus. Manycores refer to systems with much more processors or simple cores and accelerators, that are connected using some other interconnect than traditional bus. A SoC, System-on-Chip, integrates all computer components on one chip and a MPSoC, multiprocessor System-on-Chip, is a SoC that uses multiple processors. All MPSoC components are connected with on-chip interconnects.[110]

The ability to pack more and more transistors on a chip makes it possible to implement special hardware units for different chip functionalities to minimize energy consumption. This has lead to the development of heterogeneous manycores, which contain different types of cores and special purpose accelerators. Examples of such systems are MPSoCs with a traditional multicore processor connected to a GPU such as the AMD APU (Accelerated Processing Unit) [4] or a NPU (Network Processing Unit) MPSoC with a pipeline of special purpose hardware accelerators and an array of MIPS cores such as the Cavium Octeon family.[22] The miniaturization of the digital functions on a chip is also referred to as *More Moore* and the diversification of chip functionalities is referred as *More-than-Moore*.[52]

#### 2.3 High performance embedded computing

High-performance computing (HPC) is traditionally associated to the field of scientific applications requiring large amounts of computations. Embedded computing on the other hand has been associated with embedded systems requiring real-time performance. High-performance embedded computing (HPEC) refers to real-time embedded systems with high-performance requirements and strict power and cost budget requirements.[110]

After the processor manufacturers have hit the power wall, heterogeneous manycore SoCs have become their main product in attempts to increase computational performance.[110] The most efficient systems at the moment use pipelined processors of five-to-eight stages, which is the most efficient design in terms of performance per joule and silicon area.[7]

The large set of HPEC applications and the strict power and cost budgets has lead to a huge selection of many different MPSoC designs.[110] They all have their own peculiarities and need tailored software to fully benefit from the available hardware. Problem is how to program these platforms efficiently, and will such methods scale and offer code and performance portability.[55]

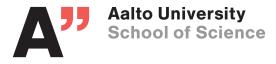

Traditionally the computer system stack has consisted of applications described using a programming language on top of a runtime, which is being managed by an operating system providing hardware resources through an ISA interface.[55]

Figure 1: The traditional view to the computer system stack on the left and on the right one alternative for the evolvement needed.

With the new manycore SoCs and parallel programming models this traditional stack structure is breaking. The traditional thread based programming methods and the software based thread scheduling is ineffective in modern MPSoCs. Threads induce too much overhead to these systems in the form of context-switches and surplus context information. Also the concurrent programming model associated with software threads is not scaling with increasing core count. [46, 64]

Instead of redesigning the whole computer system stack from scratch, evolution of existing components is needed, as the existing computer and embedded systems are full of legacy code that is too laborious and in practise impossible to be rewritten from scratch.[7]

Figure 1 illustrates the evolvement needed in the traditional way of abstracting the computer system stack. In the traditional programming stack (left), the application is a single process and the operating system abstracts other concurrent processes away by creating a virtual machine for the process. Adding multithreading has happened by making all the layers of the picture thread safe (i.e., cache coherency in hardware, memory consistency models at ISA, safe-grained locking at OS level, threading support in runtimes, and concurrency in languages). But the traditional methods do not scale with increasing core counts. Instead hardware accelerated functionalities must be used (right side of the picture) and the software and runtime must be configured according to the underlying hardware.

Different approaches for describing applications have emerged to allow software to scale with increasing core counts. The new approaches access resources using concepts such as worker threads, run-to-completion loops and describe applications using work units such as microthreads, events, jobs, tasks or tags. [78, 85, 7] But the main problem remains: how to allocate the computing resources to get maximal utilization with given dependencies and timing constraints?

Traditional software based scheduling is not efficient with the new work units. Evolution is needed close to the hardware at OS and ISA levels. In order to open the ISA bottleneck<sup>2</sup>, hardware functionality needs to be expanded and exploited in new manners.[89]

Hardware-based or hardware-accelerated scheduling and runtime operation must be used to accelerate access to the resources. Hardware accelerated scheduling is based on the use of special hardware to access simultaneously and in parallel different structures in a MPSoC. Scheduling is restricted by computational dependencies and hardware latencies.[89] Power efficient scheduling and related power management issues can be found in [109, 100, 114]. Regarding schedulers there exists pure software implementations, pure hardware implementations and mixtures of both worlds. Choice between software and hardware implementations is always a trade-off between numerous factors, for example between performance and general applicability. Examples of hardware schedulers include: Carbon [60], Isonet [65], task-superscalar [36], ADM [93], TMU [96] and the tag based approach [23].

Real-time scheduling on a manycore platform requires executing tasks so that their time constraints are always met. While the increased number of cores generally

<sup>&</sup>lt;sup>2</sup>ISA bottleneck, or scalability bottleneck at ISA level, relates to architectures performing computation using the fetch-decode-execute cycle and a limited number of processor registers. Limited number of registers and the complex logic involved e.g. in out-of-order execution and branch prediction form a performance hindrance between the SW and the HW. HW behind the ISA is forced to make guesses about the SW. More communication between SW and HW is needed and more and smaller cores with simpler datapath would help to solve these issues.[89]

means better average case execution time, the worst-case execution time (WCET) might get worse because of the more complex interactions. Measuring the average performance of heterogeneous systems is hard and their cycle-accurate simulation is too slow. Traditional methods such as WCET analysis are not automatically working on manycores.[2] Although some research has been done for example with GPUs [49], embedded streaming applications with data-dependent tasks [10], and multi-core processors with shared caches and bus [27], accurate performance prediction of multi- and manycores is still considered unfeasible to make.[2] A survey on hard real-time scheduling for multiprocessor systems in done in [31].

Using memory over interconnects is the normal method of communications needed in parallel computation.[47, 33] Transaction memories are an attempt to hide the difficulties from application programmers, but the field has still many problems to solve.[63, 62] Current approaches are towards memory consistency.[44] How the memory models have influenced programming languages is studied in [3].

Main methods of parallel programming can be divided into implicit and explicit approaches. In the explicit approach the programmer is in control to expose parallelism in the code (e.g. OpenMP [81], MPI [75], OpenCL [80], CUDA [79]). The implicit way relies to for example parallelizing compilers [57] or speculative multithreading for speeding up sequential code [51]. Parallelizing compilers have been studied extensively, but currently effective parallelism extraction still requires domain-specific knowledge.[57] Hardware aware approach to the programming of manycores is presented in [17]. A through-out view to the programming of heteogeneous MPSoCs is given in [69].

#### 2.4 Embedded System design

MPSoC platform usefulness is determined by a large set of different aspects, e.g. supported programming languages and compiler technologies, portability of code and performance and available runtime support. Usually most of the final product customization comes from software needs. That is why the software development environment plays such a crucial role in defining the usefulness of a MPSoC platform.[55]

Embedded System design allows implementation of system functionalities either in software, in hardware or as a mixture of both. HW/SW co-design techniques can be used to explore the design space of systems based on MPSoCs. The HW/SW partitioning is in key role when performance goals have to be met with chip area, power dissipation and total system cost constraints. Methods for iterative HW/SW co-design have been described e.g. in [56, 45, 43].

The HW/SW co-design space is huge, with many interactions between and within hardware and software. Design Space Exploration (DSE) techniques are used to determine the minimum number of resources needed to schedule the applications. Depending on the application and target platform complexity, DSE may take much effort. This is especially true in designing a system running multiple applications with hard-real time constraints. Higher abstraction levels are used to narrow the search. Some methods that employ simulators at early design space exploration are for example in [11, 107, 73].

Modern embedded MPSoCs have tight constraints: They have real-time guarantees to fulfill, they have limited resources and they have a limited power budget. Model-driven development restricts an application to a certain model of computation, which facilitates quantitative analysis with respect to e.g. schedulability and worst-case execution time.[35]

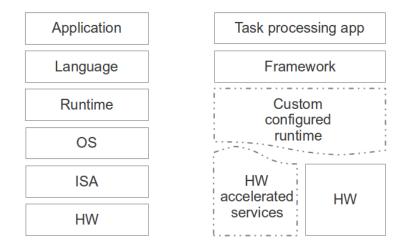

Figure 2: The HW-SW design gap is caused by the fact that the productivities and demands of HW and SW are growing at different pace with regard to Moore's law. Although the HW design productivity has been improved in recent years with the IP component reuse, the HW design productivity still lags behind the technological capabilities dictated by Moore's law. New HW designs demand new SW in increasingly growing numbers, but the productivity especially for HW-dependent SW is far behind. The red arrow shows the SW-HW design gap. Adapted from ITRS [52].

In Figure 2 the advancements in SW and in HW design productivity is portrayed with technological capabilities dictated by Moore's Law. Figure 2 shows a gap between the requirements and current productivity of MPSoC related technologies. New methods and tools are needed to help the system designers in making critical design decisions. To simplify the specification, verification and implementation of MPSoCs, and to enable more efficient design space exploration, a new level of abstraction is needed above the familiar register-transfer level.[52]

Designing large scale systems for the Internet of Things widens the already extensive design space of MPSoCs. Central questions when designing IoT application focus on partitioning the required computation between different system elements. In a hypothetical IoT application computation could be partitioned for example between a sensor's microcontroller, a mobile device, a node of the communication infrastructure and a cloud server. Optimization problem includes minimizing energy consumption and cost of all components, using only a limited set technologies at the consumer devices and a limited budget for developing new software or hardware. Early design space exploration of above described systems calls for higher levels of abstraction. High-level simulation models and automated design space exploration can be seen as an essential element in designing these new systems.[52]

# 3 Performance analysis of computing systems

This thesis studies how the performance of hardware accelerated scheduling and parallel systems in general can be analyzed. The chosen approach is modeling and simulation using resource networks as the modeling basis.

First in this chapter performance analysis is defined. Next a general view to modeling and simulation is done. Finally the resource network methodology is presented.

#### 3.1 Performance analysis

In computation performance has always been a key issue. In general the goal is to find the best cost-performance trade-off and acquire the highest performance at the lowest cost.[53]

Depending on the system under study there are different performance goals that need to be minimized/maximized. E.g. Maximizing throughput and minimizing latency of a packet processing system [23] or minimizing power consumption while providing a satisfying level of functionality for a mobile device.[100] On some fields, such as the vehicle industry, the main performance metrics can be for example maximizing reliability and fault tolerance with minimal manufacturing costs.[99]

Performance evaluation can be done in many different ways. The three main approaches are analytical modeling, simulation and measurement. Analytical modeling uses mathematical models to abstract main characteristics of a system and analyzes or predicts it's behavior. Analytical models require assumptions and generalizations in order that the analysis methods can be used. Simulation is based on modeling the system and then measuring its behavior when it is executed. Direct measurements can be used when an executable system exists. In general the three main methods of performance analysis: measurement, analytical modeling and simulation, should complement each other and be used to validate results of other methods, but in practice this is not always possible.[53]

Selecting an evaluation technique and suitable metrics for it are the main first steps in performance evaluation. Availability, or the life cycle stage, of the system under study poses constraints for the methods that can be applied to it. Measuring a yet not existing system is not possible, whereas it can usually be modeled for simulation or for analytical modeling. Another constraint is set by the time available for evaluation. Analytical modeling is in general considered to require least time of the three, while for simulation and measurement the time varies greatly. Simulation and measurement require special tools that have their strengths and weaknesses and a learning and application curve to take. Both simulation and measurement can be made more accurate using more time and resources, but in general a suitable balance between time and accuracy is sought. There exists no recipe to mechanically conduct a successful performance evaluation. One could argue that performance analysis is a form of art, that requires considerable amount of insight and experience for successful completion.[53]

#### 3.2 Simulation

Simulation is about mimicking the behavior of a defined system. Simulations are based on models, which describe the system at an appropriate level of detail. Simulation of computation includes simulating hardware, software and their co-operation with regard to inputs for the system. Simulation of complex systems usually requires the use of several abstraction layers.[83]

Simulation models are interpreted by executing them, alas by computing changes in the model with respect to possible input and time change. The model can be continuous or discrete and its interpretation can also be either of these. A dynamic model reacts to time while a static model represents a steady-state model that is time-invariant. Models can have an uncountable number of instances or states, or they can be enumerable. Similarly the model can be deterministic or stochastic. A deterministic model's states can be uniquely determined by parameters in the model and by its previous states, while in a stochastic model the transitions between different model states are also affected by probabilities. Input for a simulation model can be based on random number generation or on using fixed traces.[83]

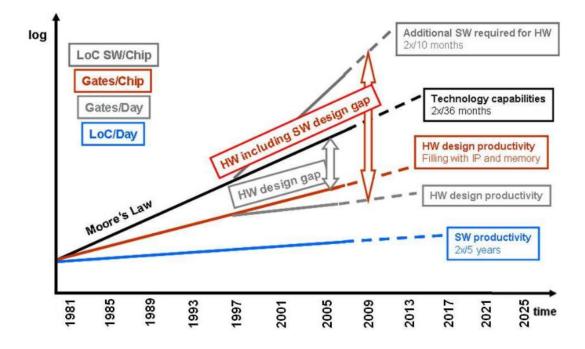

Figure 3: Simulation is an iterative process involving multiple steps. Here an overview to the different phases is presented. After problem description and data analysis follows the modeling of the system. An executable simulator program is created from the model. The model and the simulator are refined until they can be validated. Experiments are designed and then executed using the simulator. Monitoring the execution of simulation experiments produces traces for analysis.[83].

Simulation is an iterative process involving multiple steps, Figure 3 summarizes the process. After initial problem definition and analysis of system data, the system is modeled. After the model is ready a simulation program is prepared using automated tools or manually. Successful validation usually requires iteration by going back to previous phases of the process. After the simulation program is successfully validated the simulation experiments can be designed. Experiments are executed on the simulator and the execution is measured to obtain results for analysis.[83]

There are different designs for building simulation models. In [83] three types of sequential simulation model designs are identified: Event-advance, unit-time advance and activity based design. Event-advance and unit-time advance designs model the system using events that occur and change its state. They differ on how the global simulation time is advanced. In event-advance design the time is advanced (and the state of the system is changed) each time an event occurs. In unit-time advance design the global simulation time is advanced in fixed increments of time and events occur when their trigger time is met. Activity-based designs model the system as a collection of activities or processes and with conditions determining when the processes start and end.[83]

#### 3.3 Parallel simulation

Simulation of parallel systems is possible using the sequential simulation approaches described in the previous chapter and by updating the global simulation time only after all parallel events have been processed. Parallel simulation on the other hand refers to executing a single simulation program in parallel. Aim is to improve the execution speed of the simulation. Parallel discrete event simulation (PDES) has a long research tradition dating back to late 1970's.[25, 16]

Basic approaches for PDES can be categorized into functional decomposition, replicated trials, time-stepped / synchronous approach and the asynchronous approach.[40]

In the functional decomposition approach the tasks that the simulation program does are split into parallelizable entities, e.g. random number generation, event list processing and monitoring are performed in separate threads. This approach suffers from scaling issues as the functions to be parallelised are limited.[40]

In the replicated trials approach the simulator is executed as independent instances using multiple threads. This approach can be used for example to reduce variability of results or to explore a wider set of parameters. This approach has the potential to scale well with increasing core count as the instances are independent of each other. But on the other hand replicating the simulator instances easily leads to excessive use of memory which can form a bottleneck for the scalability.[40]

In the synchronous designs the entire design is controlled by a global simulation time and the simulation is proceeded and updated in lock-stepped intervals. Global time can only be advanced when all parallel processes have finished, which requires frequent and and centralized communication. This approach suffers also from the fact that events generally occur at irregular intervals. Maximization of the number of events for each interval requires assumptions in the timing model, which can easily lead to poor performance.[40]

In the asynchronous approach the simulation design is partitioned into disjoint

processes (logical processes) that may advance asynchronously. Each logical process maintains a local pending event queue and carries out simulation.[40]

Specification and partitioning of the simulation models in a way to exploit parallelism and properly executing them on parallel hardware is not a straight forward task. The fundamental problem of parallel execution is to decide whether event A can be executed in parallel with event B, when we cannot know for certain if A will affect B without executing it first. (A can affect B through a complex sequence of events.) On a larger scale this means that each component of a simulator will produce state updates that are possibly relevant for other components. These updates need to be distributed and their ordering in time must be preserved. The asynchronous PDES approach requires that the local causality constraint has to hold. This means that the parallel execution must yield the same results as sequential execution of the simulation program. [40]

Processing of PDES events is generally of low computational complexity, as each event only updates state variables and possibly schedules new events. PDES is difficult to parallelize because of the fine grained nature of the application and the frequent communication and the complex dynamic dependencies involved. On shared memory multi-core systems PDES simulators easily generate pressure on the memory subsystem.[111]

Discrete event simulation parallelization strategies can be categorized into conservative and optimistic approaches. In conservative approaches the causality errors are not tolerated. This is achieved by using different strategies to determine when it is safe to process an event. The optimistic approaches use detection and rollback mechanisms. An optimistic simulation is proceeded in parallel and upon a causality error the state is recovered by re-execution. Conservative methods can easily end in a deadlock situation and require to use different lookahead mechanisms to avoid them. Their performance depends on the degree to which lookahead can be used an on the messaging overhead involved in the deadlock avoidance and recovery. Optimistic methods risk on spending a lot of time in recovering and re-executing events sequentially. They also require to save a history of the model states to enable rollback, which on large models can greatly increase the underlying resource usage.[40]

The type of the modeled system greatly influences how much events interact and change each others states, which affects whether the conservative or optimistic approach is better suited. Similarly application specific knowledge can be used in building a simulation program so that parallelism would be maximized.[40]

Parallel simulation is generally considered to be a very hard problem. The obstacles that are faced are common to all parallel programming and execution. Research done within the field of parallel simulation can have impact and direct applications on general parallel computation. For example, the time stamped events have an analogy in the indexes of an iteration of a loop.[40]

#### 3.4 Simulators

Simulator is a program that executes a simulation model. Typically a simulator uses three data structures: state variables, an event list and a global simulation clock. State variables are used to describe the state of the system. The event list is used to store all pending events that have not yet occurred. The global simulation clock stores how far the simulation has proceeded.[83]

A discrete event simulators can be summarized using the following pseudocode, which abstracts the main loop of the program.

#### while simulation is in progress

remove smallest time stamped event from event list process the event:

- (a) update state variables

- (b) schedule new events

General purpose simulators do not exist, instead a simulator is always built with some goals in mind. Some metrics to evaluate different simulators include performance, flexibility, and detail. Performance determines the amount of workload the model can process given the computing resources available for simulation. Flexibility indicates how the models are constructed and how easy it is to modify and vary different designs. Detail defines the level of abstraction used in the models. The choice of modeling detail and abstraction level mostly dictates both the execution time of the simulation and also the time it takes to model a system.[9]

There exists a wide variety of different simulator tools and frameworks. Broadly simulators can be classified into cycle accurate, functional and high level simulators. The most accurate level is used when microarchitectural design decisions are sought and when hardware designs are evaluated and verified. At that level the models are generally described using hardware description languages, such as VHDL or Verilog, and the simulations are executed cycle accurately.[55] Cycle-accurate simulators give precise numbers of the hardware performance, but they are too slow to execute any larger application. Typically a cycle-accurate simulator runs 1000-100000 times slower than what the native execution would be.[72] Besides being slow, they are tedious to update and do not necessarily produce significantly more accurate results than e.g. functional simulators. Problems related to cycle-accurate simulators have been investigated in [105].

Functional simulators model the hardware on a more abstract level than cycleaccurate simulators. They implement what programmers see of the system architecture and generally allow execution of real program binaries. Functional simulators are generally used to investigate how different application behave on a certain hardware. Examples of functional simulators include GPGPU-Sim and Barra, which are simulators of NVIDIA GPUs, both capable of executing CUDA code.[67] Authors in [103] use GPGPU-Sim with gem5 [41] to simulate a CPU-GPU SoC. Several other functional simulators aimed for simulating heterogeneous systems are surveyed in [67].

Cycle-accurate simulators are vital for microarchitecture exploration and for making detailed design decisions, similarly functional simulators are a fundamental tool for software architects. But for early high-level exploration both are too slow and can actually produce misleading results. For high-level simulation the abstraction level of the simulated hardware can be raised. Also the simulated application does not need to be represented as an instruction stream, instead some higher level of abstraction can be adapted.[90]

High-level abstraction is generally used in early design space exploration of future systems. In the early design space exploration it is not cost effective to model a system on a too detailed level, instead it is desirable to be able to get coarse results from several different designs to then further direct the exploration. High-level simulators can be used to examine how a model behaves using different parameter sets for the hardware and software configurations.[72]

Heterogeneous MPSoCs can be modeled and simulated at different levels of details. SystemC [82] and SpecC [34] are design languages and methodologies which are intended for specification and design of SOCs or embedded systems including software and hardware. They can use fixed platforms, integrate systems from different IPs, or synthesize the system blocks from programming or hardware description languages. SystemC and SpecC support system modeling and simulation at different levels of abstraction, from pure functional un-timed models to cycle-accurate register transfer level models. SystemC is a C++ class library based language, while SpecC is a super-set extending ANSI-C.[19] While SystemC and SpecC allow highlevel modeling of computer systems, their main use is the iterative development and model refinement into register transfer level models, ready to be deployed on silicon.

Simulator toolsets suitable for modeling and simulating parallel target architectures are numerous. Some examples include: Proteus [15], RSIM [50], SimOS [91] and SimpleScalar [9]. The previous simulators are sequential discrete event simulators, whereas the following simulator examples employ parallelism: BigSim [112], COTSon [6], GEMS [68], Graphite Multicore Simulator [72], ISE [42], SlackSim [28], SimFlex [108], SimNow [5], Sniper [21], TaskSim [90], Wisconsin Wind Tunnel (WWT) [88] and Wisconsin Wind Tunnel II (WWT II) [76].

With simulators there is always a tradeoff between accuracy and speed. Some of the simulators support execution on multiple levels of abstraction. For example TaskSim uses four levels of abstraction. Applications can be modeled on the highest level of abstraction as computation and MPI calls, on the second highest abstraction level as computation and required synchronizations, on the second lowest level of abstraction using memory access list and on the lowest abstraction level as instruction list.[90]

Two recent and still actively developed simulators are the Graphite Multicore Simulator by Carbon research group, MIT and Sniper simulator from Ghent University. Graphite Multicore Simulator is a distributed, parallel simulator for designspace exploration of large-scale multicores and application research.[72] It has been recently updated with a support for runtime power modeling.[61] Sniper is a multicore simulator based on the Graphite simulation infrastructure and the interval core model that allows exploring different homogeneous and heterogeneous multi-core architectures. Sniper also supports power modeling of multi-core architectures.[21]

#### 3.5 Resource networks

Modeling of computer systems makes extensively use of different networks. Networks are useful because with them it is easy to bring structures into the model. Networks used in modeling computer systems include e.g. Petri nets [84], Queuing networks [30] and Markov Chains [14].

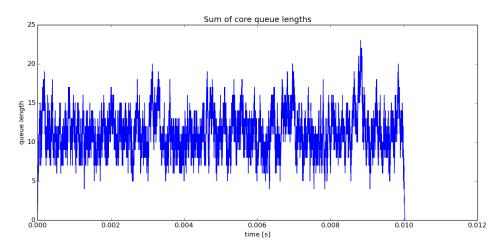

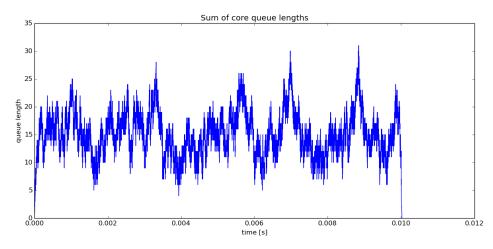

Aim of this thesis is to prototype a way to model parallel systems and allow monitoring the simulated execution at different levels of detail. For example Queuing Networks do not directly support detailed monitoring. On the other hand they can be solvel analytically to obtain some key metrics of the behavior.[14] Detailed monitoring of simulation execution can reveal model behavior that would not be deducible from some general metrics of the execution. For example monitoring the queue length of tasks waiting a hardware resource can have a average mean of N, but when the queue lengths are plotted with regard to time a periodic behavior might be observed. This observed periodicity can be more crucial for understanding the model behavior than a set of metric values.

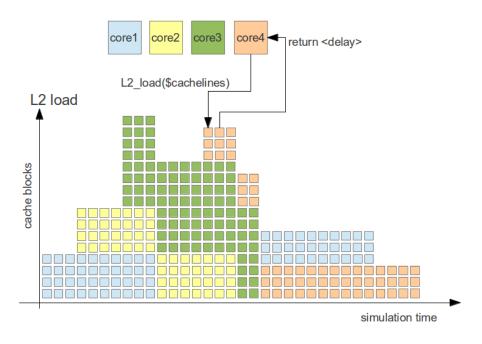

Resource network [30] is a modeling concept suitable for high-level modeling and simulation of parallel computer systems which supports monitoring at different levels of detail. Resource networks concept is based on describing the resources and the resource usage of a computer system using a resource provision network and a resource utilization network. Resource networks use the modeling abstraction of active and passive resources.[30]

The resource provision networks are directed graphs where nodes represent different resources of the system and edges represent their interconnections. Resource usage network is also a directed graph where edges represent possible paths for events and nodes represent resource requests. Both the resource description network and the resource usage network can contain loops. Workload model is a directed acyclic graph which generates events that enter and use the resource usage network.

Resource networks support fork-join queue [58] methodology which allows modeling of simultaneous resource requests. With dynamic scheduling the resource network models can employ load balancing schemes. The resource network methodology can be modeled and simulated using discrete event simulation.

# 4 PSE – Performance Simulation Environment

This chapter presents PSE – Performance Simulation Environment. PSE is based on an in-house toolset QNS (Queuing Network Simulation). First the motivation to use QNS as base and update it to support modeling and simulation of parallel systems instead of a large variety of other possible simulation tools is done. Next an overview of the PSE toolset and the modeling workflow is done, after which the basic building blocks of PSE models are described. After that a look at the monitoring system of PSE is done. Finally the PSE runtime system RNS – Resource Network Simulator is presented.

### 4.1 Queuing network simulation

The PSE simulator toolset is based on an older simulation toolset QNS (Queuing network simulator) [48]. The QNS toolset was upgraded during this thesis into PSE. PSE adds new functionality to QNS that is needed to support the simulation of parallel systems.

There exists many alternative modeling and simulation tools that could have been used to model and analyze the performance of parallel systems. These have been briefly surveyed in the previous chapter. QNS was chosen because it is a moderately sized simulator software (QNS consists of about 30k lines of code, while e.g. Graphite consists of 140k lines of code [95]). Besides of the moderate size of QNS, it being an in-house tool supported the choice.

#### 4.2 Toolset overview

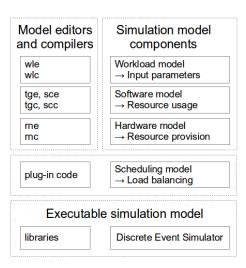

Figure 4: PSE contains a set of model editor and compiler tools that are used to create individual simulation model components. With simulator engine libraries and optional plug-in scheduling and timing code these files are turned into an executable discrete event simulation program.

PSE (Performance Simulation Environment) is a heterogeneous modeling and simulation environment. It is an extendable environment where various components can be changed or added. The PSE toolset is integrated by using a resource reservation based mechanism as the modeling basis. PSE runs on commodity Linux hardware.

Evaluation of PSE models is based on simulation. The default simulator in PSE is a discrete event simulator that has been tuned for simulating parallel processing systems. The simulation monitor is a central part of the simulator as it produces the simulation output for post-processing tools.

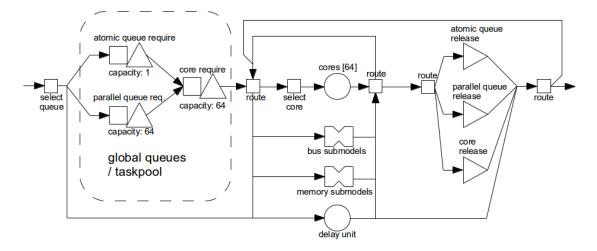

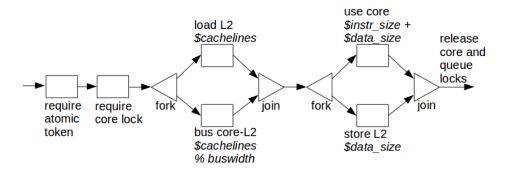

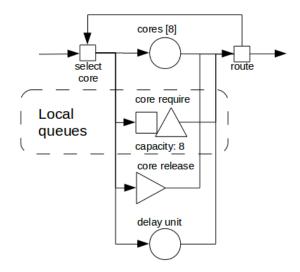

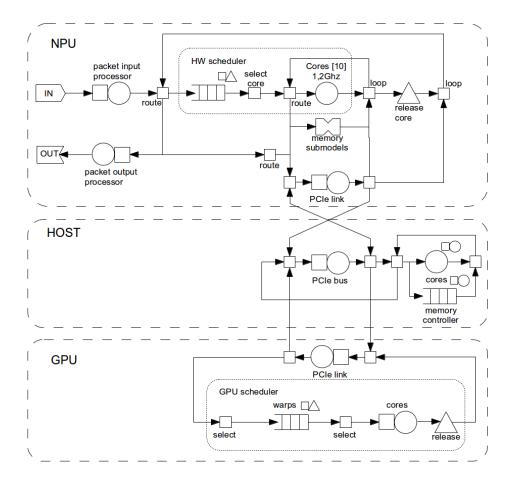

Figure 5 presents a high-level view of the PSE tools. The basic set-up of PSE consists of several integrated tools. Model editors *wle*, *tge*, *sce* and *rne* are graphical user interface tools which are used to describe different components of the simulation model. Compiler tools *wlc*, *tgc*, *scc* and *rnc* turn the model files into C code. Optional plug-in C code can be used to provide additional scheduling and timing details. The model files with PSE libraries are compiled into an executable discrete event simulator program.

The main components of a system model are a resource network for providing the resources and a usage network for utilizing the resources. In addition to these, PSE uses a workload model and optional scheduling and timing models.

An essential part of PSE models are the monitoring probes. Probes can be attached to all model components on all model layers. The probes produce traces of the simulation execution, which can then be further analyzed using different postprocessing tools.

In general, resource provision models are used to describe the underlying hardware and resource usage models are used to describe the software. But in practice the modeling of HW/SW co-scheduled systems requires using both the resource provision and the resource usage models to capture the functionality of the mixed HW/SW components.

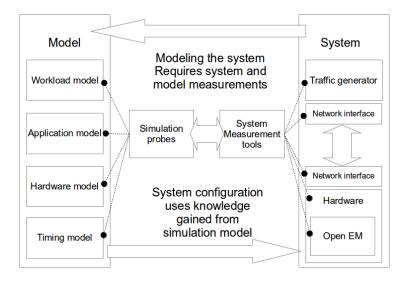

Figure 5: System model measurement loop.

#### 4.3 Modeling workflow

In a larger context PSE fits the iterative modeling-measurement-configuration loop described in Figure 5. System and model measurements are needed to model the system. The knowledge gained from experiments with the model are used to configure system parameters in order to attain better system performance. The modeling and system configuration can be done on different levels and at different system design phases.

The example presented in Figure 5 refers to the configuration of a packet processing system based on the OpenEM programming framework. The application and runtime configuration is an iterative process where PSE can be used to explore the large design space of different runtime configurations and application partitionings.

#### 4.3.1 Editor tools

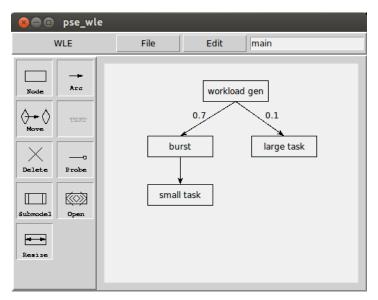

PSE models are created using model editor tools. The PSE editor tools are created using Tcl/Tk[98]. Figure 6 represents the graphical user interface of the workload model editor, Figure 8 represents the graphical user interface of the task graph editor and Figure 9 represents the graphical user interface of the resource network editor. All editor tools have drop down menus from which model files can be loaded and saved or new design can be started. The dropdown menu is also used to enable a grid onto the drawing canvas and to export model files in postscript format. The editor tools have a toolbar (on the left) that contains the supported drawing canvas using these tools.

Figure 6: The graphical user interface of the workload model editor. The various tools and symbols are used to create and modify PSE workload model files.

The workload model is a directed graph, where each node represents an action to be taken and arcs represent invocations for new actions. The arcs can be equipped with a probability that determines whether the child node is activated upon activation of the parent or not. With the *text* tool the contents of nodes and arcs can be edited.

| Entity description                                                                                                                                                                                                                                                   |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <pre>name:small_task group:msg job:SOFTWARE lifetime:RNS_random_uniform(0.02,0.04) interval:RNS_random_uniform(0.01,0.02) codelines:RNS_random_int(100,1500) LIreadhit:RNS_random_bernoulli(0.6) LIwritehit:RNS_random_bernoulli(0.2) portnumber:1 portname:IN</pre> |  |

| done                                                                                                                                                                                                                                                                 |  |

Figure 7: Example contents of a node in a workload model.

Figure 7 shows the contents of an example node. The key parameters are the *job, lifetime and interval.* Parameter *job* defines the application model that the generated event will enter. Parameter *lifetime* determines the duration that the node will be kept alive after invocation. *Lifetime* parameter can also be omitted which means that the node is invoked just once. Parameter *interval* determines how often the node is activated (during its lifetime). Other parameter *codelines, LIreadhit and LIwritehit* are user specified variables that can be referenced from the resource provision and resource usage models. The parameters *portnumber and portname* determine the entry point in the application model determined by the

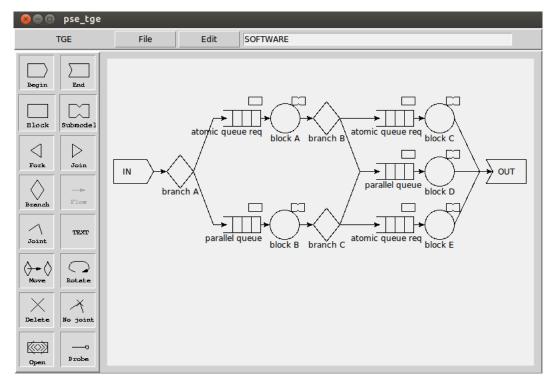

Task graphs are used to model the resource usage of a system. Figure 8 represents the graphical user interface of the task graph editor. Task graphs are directed graphs consisting of arcs connecting different types of nodes. Arcs define the paths an event can take while in the model. With the *text* tool the contents of nodes can be edited.

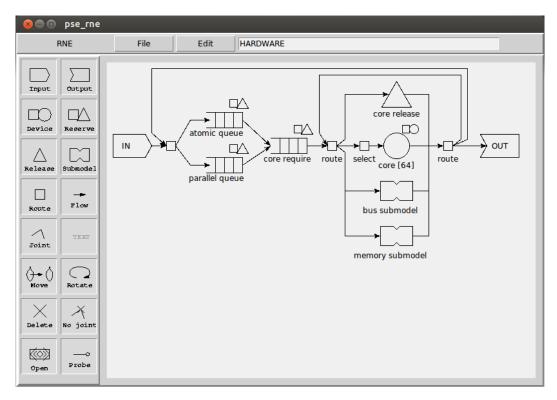

The resource provision network consists of different types of nodes connected with arcs. Figure 9 represents the graphical user interface of the resource network editor. The nodes of the resource network can be edited using the *text* tool.

Figure 8: The graphical user interface of the task graph model editor. The various tools and symbols are used to create and modify PSE task graph model files.

Figure 9: The graphical user interface of the resource network model editor. The various tools and symbols are used to create and modify PSE resource network model files.

#### 4.3.2 Compiler tools

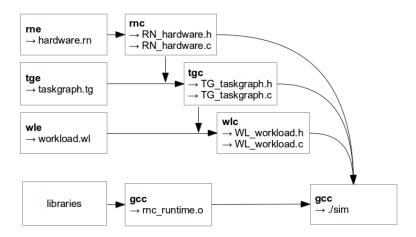

The editor tools of PSE use a textual representation for the models. The model files are compiled into C code using the corresponding compiler tools. In Figure 10 the workflow of creating a complete PSE model is presented. A hardware model created using the *rne (resource network editor)* tool is compiled using the *rnc (resource network editor)* tool is created using the *tge (task graph editor)* tool. The *tgc (task graph compiler)* is used to compile the application model. The *wle (workload editor)* tool is used to model the system workload and the *wlc (workload compiler)* generates code from the model file. Finally with a reference to RNS libraries *gcc* is used to compile all model files into an executable simulation.

Figure 10: The workflow for creating an executable simulator program begins by describing the model components using the graphical editor tools. The model files are compiled into C code using the PSE compilers. All model files are compiled together with RNS libraries into an executable simulator.

PSE modeling philosophy is based on combining elementary building blocks to model more complex system structures and functionalities. Models formed using the simple building blocks can be grouped into into submodels for semantical clarity and functional reuse.

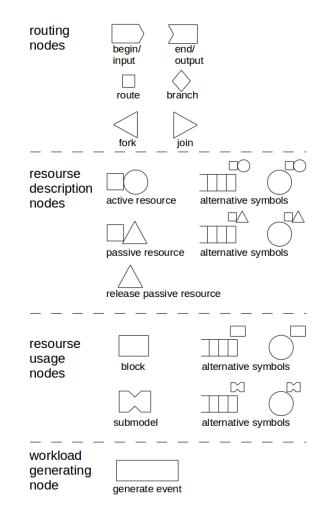

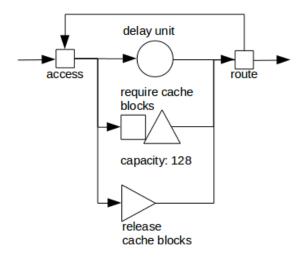

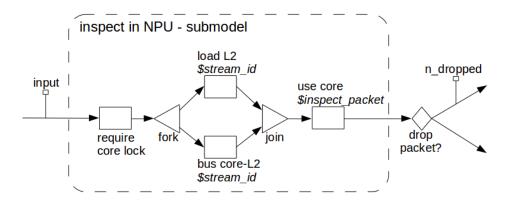

Figure 11: PSE building blocks. Routing nodes define the flow of tasks in the application models. Resource description nodes are used to describe the resources (usually the HW) of a system. Resource usage nodes define the resource requests from the application layer to the hardware layer of the model. Workload generating nodes are used to generate input for the PSE models.

The PSE building blocks can be categorized into routing nodes, resource description nodes and resource usage nodes. The PSE building blocks are presented in the Figure 11. Routing nodes include the *begin* and *end* (*input* and *output* in the RNE) nodes that define the entry and exit points for models. The *Route* and *branch* nodes are used to direct events to target devices or paths using rules defined in the models. The *fork* node allows splitting the flow into two simultaneously taken paths and the *join* gathers both of the flows before it is allowed to proceed. There are two kinds of resource types in PSE, active and passive. Active resources have a speed parameter that defines how quickly they are able to fulfill requests. Active resources are requested for service for a certain amount and they return a service delay depending on the amount requested. Block is the node that is used to define the type and amount of a resource request. Passive resources can be used to provide exclusive access to regions in models. They can be acquired by requesting service from them and they must be released afterwards. Both the active and the passive resources can have count and capacity parameters defined. These are used to specify the amount of parallel tasks that can be served simultaneously. Submodel nodes are used to group different models together to form hierarchical models.

In Figure 11 alternative symbols are shown for the nodes representing active and passive resources, use resource and submodel. These function similarly as the main symbol, but can be used to underline the semantical meaning.

The parameters of the building blocks can be edited with the *text* tool. Clicking on a node opens a dialog window where parameters are written. Example contents of a branch node are presented in Listing 1.

| Listing 1: | Example | contents | of a | branch node. |

|------------|---------|----------|------|--------------|

|            |         |          |      |              |

| cache hit?<br>name: LIcachehit<br>expr: LIreadhit |       |            |  |  |

|---------------------------------------------------|-------|------------|--|--|

|                                                   | cache | hit?       |  |  |

| expr: LIreadhit                                   | name: | LIcachehit |  |  |

|                                                   | expr: | LIreadhit  |  |  |

In this example the *LIreadhit* variable defined in the workload model (see e.g. Figure refsmalltask) evaluates to zero or one. The two nodes following the brach node must contain identifiers *tag:0* and *tag:1* to direct the flow based on the value of LIreadhit.

Resources are defined using the attributes presented in in Listing 2.

| -          | (          | 5        |                              |

|------------|------------|----------|------------------------------|

| name       | value type | optional | applies to nodes             |

|            |            |          |                              |

| name       | alphanum   | no       | active and passive resource, |

|            |            |          | release, submodel            |

| count      | integer    | yes      | active and passive resource, |

|            |            |          | release, submodel            |

| discipline | alphanum   | yes      | active and passive resource, |

| capacity   | integer    | yes      | active and passive resource, |

| group      | alphanum   | ves      | active and passive resource, |

| speed      | float      | yes      | active resource              |

Listing 2: Resource description attributes.

*Count* creates an array of the resources. *Discipline* is used to specify the queueing policy of a resource (default is FCFS, First Come First Served). *Capacity* defines how many tasks can be served concurrently. *Group* is used to form monitoring groups. *Speed* defines the service per time of the resource.

Resource usage requests are defined using the attributes presented in Listing 3.

Listing 3: Resource usage attributes.

| name        | value type | optional | applies to nodes            |

|-------------|------------|----------|-----------------------------|

|             | <u> </u>   |          |                             |

| type        | alphanum   | no       | (see below)                 |

| name        | alphanum   | no       | all                         |

| port        | integer    | no       | enter                       |

| time/amount | float      | no       | active resource             |

| pc          | integer    | yes      | active and passive resource |

| group       | alphanum   | yes      | active and passive resource |

| exits       | alphanum   | yes      | submodel                    |

| enters      | alphanum   | yes      | submodel                    |

| tag         | aplhanum   | no       | following a branch          |

The type of resource usage is defined using the *type* attribute. Valid values are: *device* for active resource, *resource* for passive resource, *release* for releasing a passive resource and *submodel*, *exits or enters* to control movement in and out of submodels. *name* attribute is used to identify the requested resource. *Port* attribute can be used to classify entering events of a model. The *time* and *amount* attributes are used to determine the amount or time requested from an active resource. Attribute *pc* defines the priority of a request. *Group* is used to form monitoring groups. Attributes *exits* and *enters* define the movement inside the submodel hierarchy. *Tag* is used after a branch node to identify the target for an evaluated branch expression.

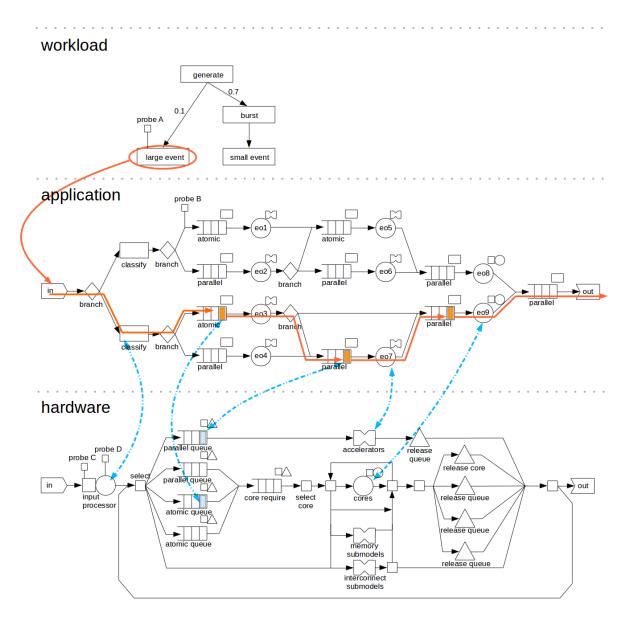

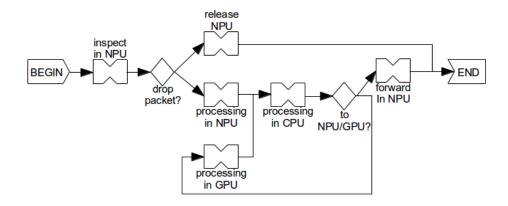

The basic building blocks are used to model larger entities. Figure 12 represents an example PSE model. The model shows how OpenEM based applications can be modeled.

In the example events are generated by the workload model. The generated events enter the application model where they make resource requests at the nodes of the model. The resource requests are served from the hardware model. Depending on the amount of service requested and the internal state of the hardware model the events are delayed for a specified amount of time.

Figure 12: An example of a layered PSE model, which represents how OpenEM[78] based and other similar systems can be modeled using the PSE tools. The workload layer model generates events that enter the application layer model. The events flow in the application model and are placed into queues until access to resources is granted. A resource request is made for example in the *classify* node in the application model, this resource request is for the resource named *input processor* in the hardware model. Similar resource requests are made in the EO submodels. Depending on the state of the hardware layer model, each resource request induces a timing delay to the flow of the events in the application model.

#### 4.5 Monitoring

When simulations are used for performance estimation time is in a key role. Performance simulations use time stamping to keep things ordered with regard to time. Simulators use monitoring techniques to obtain metrics of the simulation behavior. Basic approaches for this are trace-based and on-the-fly approaches. Trace-based simulator produces a trace that is saved for post-processing. An on-the-fly monitored simulator produces metrics of the simulation execution. If only certain metrics of the simulation are under study then collecting a trace file is not necessary.

PSE offers a comprehensive set of simulation monitoring tools. Monitoring is based on probes, which can be attached to the graphically presented models. Probes are used to generate traces or to measure statistics from the simulation execution. In PSE *trace probes* produce trace files that track certain events, whereas *metric probes* compute statistics from the measured target.

In resource description models probes can be attached to resources for measuring utilization or to queues to measure queue length. Trace probes produce a trace file where either every change in the queue length or in the resource utilization is recorded. Metric probes produce statistics of the queue length or the utilization. The statistics produced by metric probes are the mean, standard deviation, minimum, maximum, sum, and total number of events.

In resource usage models *time probes* can be attached to the edges of the graph. Time probes can be used to produce a trace with a timestamp whenever an event passes the measurement point. The timestamps can be a list of absolute times or times relative to process start. Time probe can also measure the average time of all events relative to process start. In workload models probes can be used to group together measurements from other probes.

Trace probes write tracefiles, whereas metric traces write a single line containing average values. Each probe produces one trace file. If traces are not needed then metric probing should be used as the trace files can easily become very large and the required file operations could saturate the system.

Probes are represented graphically in the PSE models. This is illustrated In Figure 12 where four probes (A,B,C and D) are attached to different parts of the system models. Probe A is attached to the workload model, probe B to an edge of the application model, probe C is attached to the queue of the *input processor* node and probe D measures the utilization of the same node.

#### 4.6 RNS runtime

RNS (Resource Network Simulator) is a discrete event simulator engine designed to execute the PSE models. RNS keeps track of the global time of the simulation, schedules simulation events and manages the monitoring of simulation execution. RNS provides the abstractions and interface used by the model file compilers. Main components of RNS are the event scheduler, the process abstraction with accompanying service routines and the monitoring system.

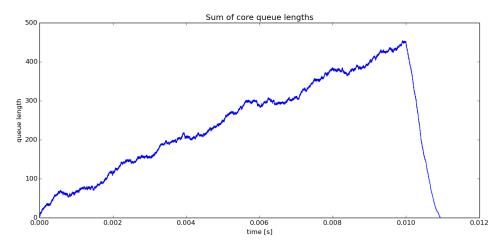

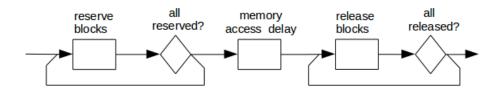

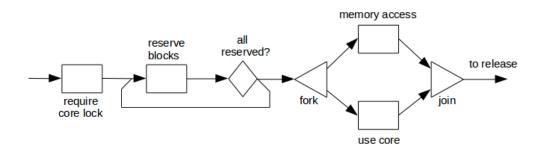

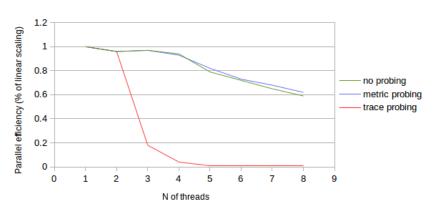

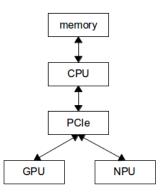

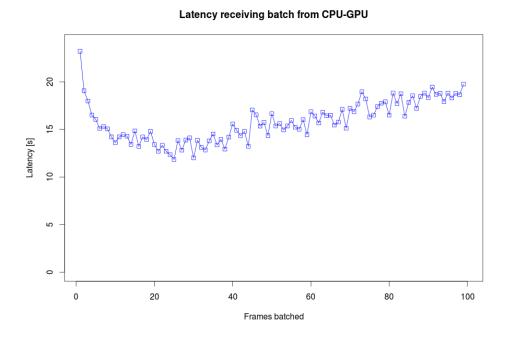

The RNS scheduler runs in a loop picking the event with the smallest trigger