#### Jonas Nyberg

### **Development of a Universal EtherCAT-Based Fieldbus Module**

#### School of Electrical Engineering

Thesis submitted in partial fulfillment of the requirement for the degree of Master of Science in Technology

Espoo 27.5.2013

Thesis supervisor:

Professor Raimo Sepponen

Thesis instructor:

Ari Lindvall

#### AALTO UNIVERSITY SCHOOL OF ELECTRICAL ENGINEERING

ABSTRACT OF THE MASTER'S THESIS

Author: Jonas Nyberg

Title: Development of a Universal EtherCAT-Based Fieldbus Module

Date: 27.5.2013

Language: English

Number of pages: 10+47

Code: S3007

Department of Electronics

Professorship: Electronics and applications

Supervisor: Prof. Raimo Sepponen

Instructor: Ari Lindvall

A product development project was set up at the Finnish company SKS Control Oy in order to renew an older product portfolio consisting of a number of different devices used in electrically implemented motion control systems. These products include, for example, a range of programmable CPU units, display devices, HMIs, and I/O devices. This work focuses on the process of developing one of the new products, which is an EtherCAT-based fieldbus module. The purpose of this product is to replace a number of older products by integrating their functionality into one extensive modular-structured device. Along with this, the new module is intended to provide various new features that were hard or impossible to implement with the older products.

The part of the product development work which is presented here consists of three main parts. The first one presents some of the most relevant theoretical background behind the field-bus module along with a list of wanted features and properties. Together with the theory, this part discusses a way of satisfying these design constraints while using a module structure similar to the other products in the portfolio.

Second, the work covers the hardware design of the module by dividing it into smaller functional blocks and discussing them separately. Here the focus lies on the electronic design rather than the mechanical.

Finally, the work includes a section about the software work included in the product development. This part mainly focuses on the hardware description language VHDL and, to a smaller extent, on additional software, such as C, used in the product or together with it.

Keywords: EtherCAT, FPGA programming, VHDL, XML, C, I/O, PCB design, product design, field-bus

#### AALTO YLIOPISTO SÄHKÖTEKNIIKAN KORKEAKOULU

DIPLOMITYÖN TIIVISTELMÄ

Tekijä: Jonas Nyberg

Työn nimi: Development of a Universal EtherCAT-Based Fieldbus Module

Päivämäärä: 27.5.2013

Kieli: Englanti

Sivumäärä: 10+47

Elektroniikan laitos

Professuuri: Elektroniikka ja sovellukset

Koodi: S3007

Valvoja: Prof. Raimo Sepponen

Ohjaaja: Ari Lindvall

Suomalaisessa yrityksessä SKS Control Oy:ssa aloitettiin tuotekehitysprojekti jonka tarkoitus oli uusia eräs vanha tuoteportfolio. Portfolio sisältää tuotteita jotka käytetään sähköiseen liikkeenohjauksen yhteydessä ja portfoliossa löytyy esimerkiksi erilaisia CPU-moduuleja, näyttöjä, HMI:ta ja I/O laitteita ym. Tämä kirjoitelma keskittyy yhteen uuteen tulevaan moduuliin, joka on EtherCAT pohjanen kenttäväylämoduuli. Tämän uuden tuotteen tarkoitus on korvata muutama vanha tuote ja samalla tuoda uusia ominaisuuksia jotka olisi ollut vaikeita tai mahdottomia toteuttaa vanhoilla tuotteilla.

Sitä osaa tuotekehitysprojektia joka esitetään tässä työssä sisältää kolmea eri osaa. Ensimmäinen osa käsittelee olennaisimmat alueet tuotteen teoreettisesta taustasta ja samalla esittelee tuotteen halutut spesifikaatiot ja ominaisuudet. Tämän yhteydessä esitetään myös erilaiset keinot toteuttaa nämä halutut ominaisuudet.

Työn toinen osa käsittelee tuotteen rautapuolen suunnittelua jakamalla kaikki toiminnalliset osat pienempiin osakokonaisuuksiin ja käsittelemällä niitä erikseen. Tässä osassa keskitytään enemmän elektroniikan suunnitteluun kun mekaaniseen.

Lopuksi työ käsittelee tuotteeseen liittyvää ohjelmointiosuutta joka pääosin käsittelee rautapuolen ohjelmointia VHDL kielellä ja pienemmissä määrissä muita tuotteeseen liittyviä ohjelmointikieliä kuten C.

Avainsanat: EtherCAT, FPGA ohjelmointi, VHDL, XML, C, I/O, PCB suunnittelu, tuotesuunnittelu, kenttäväylä

First of all, I want to thank my thesis instructor Ari Lindvall for granting me the opportunity to complete my Master's degree at SKS Control Oy in form of an interesting product development project.

Least but not last I would like to thank both Raimo and Ari for their time they took by reading through the work and correcting and commenting on it.

Sipoo, 27.5.2013

Jonas Nyberg

# Contents

| A | bstra | act     |                                                            | ii                                                                                                                |

|---|-------|---------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| A | bstra | act (ir | ı Finnish)                                                 | iii                                                                                                               |

| P | refac | e       |                                                            | iv                                                                                                                |

| С | onte  | nts     |                                                            | iii<br>iv<br>iv<br>v<br>viii<br>1<br>2<br>3<br>4<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>-<br>- |

| S | ymbo  | ols an  | d abbreviations                                            | viii                                                                                                              |

| 1 | In    | trodu   | iction and objectives                                      | 1                                                                                                                 |

|   | 1.1   | Pro     | oduct overview                                             | 2                                                                                                                 |

|   | 1.2   | Pro     | oduct development goals and comparison to similar products | 3                                                                                                                 |

|   | 1.3   | Th      | e scope of the thesis                                      | 4                                                                                                                 |

|   | 1.4   | Th      | esis organization                                          | 4                                                                                                                 |

| 2 | T     | heory   | of the EtherCAT protocol and module operation              | 5                                                                                                                 |

|   | 2.1   | Etł     | nerCAT protocol                                            | 5                                                                                                                 |

|   | 2.    | 1.1     | The EtherCAT standard and ETG (EtherCAT technology group)  | 5                                                                                                                 |

|   | 2.    | 1.2     | Operating principle and frame processing                   | 5                                                                                                                 |

|   | 2.    | 1.3     | The Physical layer, PHY                                    | 6                                                                                                                 |

|   | 2.    | 1.4     | FMMU and SyncManagers                                      | 7                                                                                                                 |

|   | 2.    | 1.5     | Distributed clocks                                         | 8                                                                                                                 |

|   | 2.    | 1.6     | EtherCAT master and slave implementation                   | 8                                                                                                                 |

|   | 2.2   | Mo      | odule architecture and design                              | 9                                                                                                                 |

|   | 2.3   | Mo      | odule as a part of a larger automation system              | 11                                                                                                                |

|   | 2.4   | Int     | erfaces to other systems and devices                       | 12                                                                                                                |

|   | 2.    | 4.1     | Encoders                                                   | 12                                                                                                                |

|   | 2.    | 4.2     | D/A and A/D converters                                     | 13                                                                                                                |

|   | 2.    | 4.3     | Digital I/O                                                | 13                                                                                                                |

|   | 2.    | 4.4     | Additional and future modules                              | 13                                                                                                                |

|   | 2.5   | FP      | GA                                                         | 14                                                                                                                |

|   | 2.    | 5.1     | Overview of architecture and applications                  | 14                                                                                                                |

|   | 2.    | 5.2     | FPGA programming                                           | 15                                                                                                                |

|   | 2.    | 5.3     | FPGA usage in the project fieldbus module                  | 15                                                                                                                |

| 3 | E     | lectro  | nic and mechanical hardware design                         | 17                                                                                                                |

|   | 3.1   | Me      | chanical design                                            | 17                                                                                                                |

| 3.1.1   | Module and motherboard PCB mechanical layout             | 17 |

|---------|----------------------------------------------------------|----|

| 3.2 H   | Electronic design                                        | 19 |

| 3.2.1   | Power supply                                             | 19 |

| 3.2.2   | Bottom I/O and serial ports                              | 20 |

| 3.2.3   | Diagnostic, test and programming                         |    |

| 3.2.4   | Option module connectors                                 |    |

| 3.2.5   | Front panel connector                                    |    |

| 3.2.6   | EtherCAT ports                                           | 23 |

| 3.2.7   | FPGA and memory                                          | 24 |

| 3.3 I   | PCB design                                               | 25 |

| 3.3.1   | PCB board stack-up and properties                        |    |

| 3.3.2   | Routing                                                  |    |

| 3.3.3   | Manufacturing the PCB                                    |    |

| 3.4 (   | Component selection                                      |    |

| 3.4.1   | Active components - ICs                                  |    |

| 3.4.2   | Passive components - capacitors, resistors and inductors |    |

| 3.4.3   | Connectors                                               |    |

| 3.5 I   | Evaluation and testing                                   |    |

| 3.5.1   | Test phases                                              |    |

| 4 Softv | vare design                                              |    |

| 4.1 V   | VHDL software design                                     |    |

| 4.1.1   | The overall structure of the VHDL description            |    |

| 4.1.2   | The complete VHDL module hierarchy                       |    |

| 4.1.3   | Functional descriptions of the different VHDL modules    |    |

| 4.1.4   | Working with Xilinx FPGA design tools                    |    |

| 4.1.5   | Future expansion                                         |    |

| 4.2 (   | Other additional software                                | 40 |

| 4.2.1   | Microcontroller C and Assembly                           | 40 |

| 4.2.2   | XML markup file for an EtherCAT master                   | 41 |

| 4.3     | Testing and evaluation of software                       | 41 |

| 5 Resu  | lts and conclusions                                      | 43 |

| 5.1     | Testing and confirmation of function                     |    |

| 5.2 H   | Future work                                              | 43 |

| 5.3     | Final summary | .44 |

|---------|---------------|-----|

| Referen | ces           | .45 |

| Append  | ix            | .47 |

# Symbols and abbreviations

| ABS              | Absolute                                              |

|------------------|-------------------------------------------------------|

| AoE              | ADS over EtherCAT                                     |

| ASIC             | Application specific integrated circuit               |

| A/D              | Analog to digital                                     |

| BGA              | Ball-grid array                                       |

| CMOS             | Complementary metal oxide semiconductor               |

| СоЕ              | CANopen over EtherCAT                                 |

| CPLD             | Complex programmable logic device                     |

| СРИ              | Central processing unit                               |

| DC               | Direct current / Distributed clocks                   |

| DCM              | Digital clock manager                                 |

| DPRAM            | Dual port random access memory                        |

| DSP              | Digital signal processing                             |

| D/A              | Digital to analog                                     |

| EEPROM           | Electronically erasable programmable read-only memory |

| EMC              | Electromagnetic compatibility                         |

| ENI              | EtherCAT network information                          |

| EoE              | Ethernet over EtherCAT                                |

| EOF              | End of frame (EtherCAT frame)                         |

| ESC              | EtherCAT slave controller                             |

| ESI              | EtherCAT slave information                            |

| ESM              | EtherCAT state machine                                |

| EtherCAT         | Ethernet for control and automation technology        |

| ETG              | EtherCAT technology group                             |

| FCS              | Frame check sequence                                  |

| FET              | Field-effect transistor                               |

| FLASH            | Non-volatile computer storage memory                  |

| FMMU             | Fieldbus memory management unit                       |

| FPGA             | Field programmable gate array                         |

| FR4              | Grade designation assigned to PCBs' core material     |

| GPIO             | General purpose Input / Output                        |

| I <sup>2</sup> C | Inter-integrated circuit two-wire interface           |

| IC               | Integrated circuit                                    |

|                  |                                                       |

| ID   | Identification                                      |

|------|-----------------------------------------------------|

| INC  | Increment                                           |

| IEC  | International electro-technical commission          |

| IEEE | Institute of electrical and electronics engineers   |

| IP   | Internet protocol                                   |

| IP   | Intellectual property                               |

| ISO  | International organization for standardization      |

| I/O  | Input / Output                                      |

| JTAG | Joint test action group                             |

| LCD  | Liquid crystal display                              |

| LED  | Light emitting diode                                |

| LUT  | Lookup table                                        |

| LVDS | Low voltage differential signaling                  |

| MAC  | Media access control                                |

| MMU  | Memory management unit                              |

| MUX  | Multiplexer                                         |

| NIC  | Network interface controller                        |

| PAL  | Programmable array logic                            |

| PC   | Personal computer                                   |

| PCB  | Printed circuit board                               |

| PDI  | Process data interface                              |

| PDO  | Process data object                                 |

| PE   | Protection earth                                    |

| РНҮ  | Physical layer                                      |

| PLD  | Programmable logic device                           |

| PLL  | Phase-locked loop                                   |

| PTC  | Positive temperature coefficient                    |

| QFN  | Quad-flat no-leads                                  |

| RJ45 | A common connector type used for Ethernet           |

| RTOS | Real-time operating system                          |

| R/W  | Read / Write                                        |

| SEMI | Semiconductor equipment and materials international |

| SFR  | Special function register                           |

| SM   | Sync manager                                        |

| SMD  | Surface-mount device                                |

| SMPS  | Switched-mode power supply            |

|-------|---------------------------------------|

| SoC   | System on chip                        |

| SoE   | Servo profile over EtherCAT           |

| SOF   | Start of frame (EtherCAT frame)       |

| SPI   | Serial peripheral interface bus       |

| SRAM  | Static random access memory           |

| SSI   | Synchronous serial interface          |

| TTL   | Transistor-transistor logic           |

| TVS   | Transient voltage suppression         |

| UDP   | User datagram protocol                |

| VHDL  | VHSIC hardware description language   |

| VHSIC | Very high speed integrated circuit    |

| VLAN  | Virtual local area network            |

| VoE   | Vendor specific profile over EtherCAT |

| WD    | Watchdog                              |

| XML   | Extensible markup language            |

|       |                                       |

## 1 Introduction and objectives

As the demand for faster performing and more complex automation systems arises, the need for new innovations and solutions is brought into light and has to be answered by the automation technology companies. One such cost-effective solution that provides the customer with an efficient and flexible system is the real-time EtherCAT® fieldbus system. By using the same underlying commodity technology in the EtherCAT® system as with standard Ethernet, which is mainly driven by the office sector, the overall system cost reduces significantly. The office Ethernet technology does not only bring cost-reduction, but also gives rise to another one of the main advantages with EtherCAT®, namely that it makes allowance for internet access (e.g. webserver) within the same system. The internet access can quite possibly reduce the number of interfaces in the automation system as nowadays system access over the internet is widely implemented. However, comparing EtherCAT® with the office Ethernet shows clearly that EtherCAT® is better suited for automation systems than the standard office Ethernet technology. One reason for this is the lack of real-time operation with the office Ethernet. Another reason is the small utilization of the Ethernet packages and slower speed due to the fact that the packages have to be received, copied and interpreted before forwarding. This is not the case with EtherCAT® as will be seen later in the thesis.

EtherCAT® differs from standard Ethernet in many ways by the most prominent one being the determinacy i.e. real-time characteristics. The EtherCAT® real-time capability, using time-stamps based on a distributed clock system, allows for faster system response and easier synchronization of modules in larger systems, which is a much desired feature due to the fact that some grade of synchronization is involved in a large number of automation systems. The EtherCAT® fieldbus competes with other similar real-time solutions on the market, with the most visible ones being the Siemens Profinet® industrial Ethernet and Powerlink® systems, all with their own pros and cons.

The root of a simple automation system using the EtherCAT® fieldbus technology consists of one master controller and one or more EtherCAT® slave(s). The master can but does not have to be a normal PC, with suitable software and hardware, and is usually connected via standard Ethernet cables to the slaves, without the need of any hubs or switches in between. The EtherCAT® master controller is nothing more than a software program that usually uses the same network controllers and hardware as the slaves in the Ethernet physical layer. The master creates and sends out the EtherCAT® frames or packages to be forwarded by the slaves. The slave's role is to forward the EtherCAT® frames on the fly, while simultaneously extract and insert data into the frames which has been specifically addressed for each slave. The master also controls and executes the application specific automation program by using the slaves as the electrical interfaces to the other devices in the system. The program's complexity can for example range from a simple I/O reading task to a much more complex motion control task involving sophisticated synchronous motion of several axes.

A product development project was set up at the Finnish company SKS Control Oy, with the main objective being to develop a competitive EtherCAT®-based fieldbus module as a part of a product portfolio modernizing project. The new products to be developed in the modernizing process are meant to replace an old much wider product portfolio by integrating more functionality into fever products and make use of the other

benefits that EtherCAT® gives rise to compared to the old system. The two most central products of the portfolio are an EtherCAT® master CPU module and an EtherCAT® slave I/O module, of which the latter one is the subject of this thesis. Although the project covers the whole product development process from idea to the complete sales-ready product, the scope of this thesis doesn't cover all parts in the process as will be explained later.

My personal part of this product development project involving this particular EtherCAT® slave module is quite comprehensive. It involves all the hardware prototyping and design, all the software design and the major part of the documentation. However, areas such as sales & marketing, some of the ideation around the product features and the final production management are outside my field of work.

The objective of this thesis is to provide the reader with comprehensive information about the work that has been done and knowledge that can be used for similar future development, such as new spin-off products or updated versions of the original one. The thesis simultaneously stands as a technical documentation, leaving out some of the deeper knowledge behind the implementations due to the fact that they are trade secrets. This product documentation stands alongside with other documentation such as the user's manual and technical datasheets etc.

#### 1.1 Product overview

As shortly stated before, the product that is being discussed in this thesis is an EtherCAT slave fieldbus module. The module is operated by a master device connected to it using standard Ethernet NICs that are compatible with the EtherCAT protocol. The specifications for the EtherCAT protocol allow one master to be connected to one or more slaves of different or the same type. Because the protocol is standardized and all vendors have to develop their products according to it, the master and the slave modules don't have to be from the same vendor or product family to work together. The protocol also supports different network topologies, such as a line-, tree-, star- and ring-topology or an arbitrary combination of them all. These different possibilities give the system architect more freedom while simultaneously adding more qualities to the system, such as the possibility for redundancy. Communication is not only restricted from master to the slaves and vice versa but also allows for a fast slave to slave communication.

The electronics of the slave module itself is encapsulated inside a plastic box consisting of one motherboard, with electrical connectors, upon which a number of PCBs with different functionality can be stacked, to fulfill the required specifications of the system. This allow making one more basic and cheaper version of the product for simpler projects, containing only the motherboard without add-ons, but with some basic functionality integrated, such as digital I/O. On the contrary, if a more complex system is needed, there is a possibility to use a number of different add-on PCBs, with different functions and electrical connections, by stacking them onto the motherboard. The add-on PCBs, which are referred to as option modules thorough the thesis, provide the module with more complex functions such as A/D-, D/A-converters, ABS- and INC-encoder interfaces, additional I/O with special properties etc. A more thorough description of the possibilities this modularity gives rise to is given later on.

# 1.2 Product development goals and comparison to similar products

The main goal of the product development is to manage the many needs of today's automation systems with one extensive modifiable fieldbus module. Therefore pressure is set to plan and design the module for maximum flexibility and adaptability. This adaptability will not only reduce the costs in some applications, but will also allow the module to be modified to meet the customers' specific needs in special cases. These special cases can be situations when no off-the-shelf module is available to satisfy some desired arbitrary function(s) and the alternative solution would be somehow cumbersome. One example of this could be a simple thing as measuring the frequency or pulse width to a high precision of a digital input channel. Another example could be applying a digital filter of variable length to digital inputs. These are examples of things not easily implemented by using simple off-the-shelf modules, but can be implemented into the module with a small effort using the hardware description language VHDL together with a programmable FPGA, as will be seen later.

Another goal is to keep the module and the building-blocks it consists of rather simple in construct and reduce the component amount as much as possible. This will help to manage the production costs and increase the reliability, while still providing a flexible and easy solution. Implementing an FGPA chip in the design which is programmed using the hardware description language VHDL will help to reduce the component count significantly. This is due to the fact that most of the complex hardware functions can be implemented inside one FPGA chip, simply by programming it.

A third goal related to the electrical design is to keep the motherboard as open as possible for future improvements. Specifically to keep the add-on PCB-board connectivity as flexible as possible to allow for more and easy improvement of the module properties by using future add-on boards of different kinds and complexity. The FPGA comes in handy here once again because new add-on boards can be taken into use by simply modifying the VHDL software and leaving the electrical connections the same as before.

Conventional EtherCAT systems sold by larger vendors, such as Beckhoff and Wago, all build their systems using one EtherCAT coupler, which is connected to a master, together with off-the-shelf EtherCAT slave modules stacked onto the coupler. This gives a similar modular construction as the one described in the chapter before and the system is built similarly by stacking the needed slave modules together. This method lacks the ability to arbitrarily modify each module for specific special needs, which is one downside with off-the-shelf modules.

The last but not least advantage with developing a module of one own is the in-depth knowledge and understanding of the product it provides. This will naturally give aid to the technical support and therefore also give more value to the customers.

#### 1.3 The scope of the thesis

The scope of this thesis is mainly restricted to the hardware and software development of the EtherCAT-based fieldbus module, together with some basic theory of operation. Nevertheless, a short introduction is given regarding its use and role as a part of a bigger automation system including some discussion about communication and interfaces to other devices. The hardware part of the thesis focuses more on the electronic than the mechanical product design and gives the reader in-depth knowledge about the electronic building-blocks used and how they work together. In the same manner, the software part of the thesis discusses the software blocks which builds up a functioning product with the desired features and are programmed into the FPGA. It is assumed that the reader is familiar with the hardware description language VHDL. The thesis software part also slightly touches the subject of XML coding and its use in an EtherCAT system.

The thesis does not go in-depth discussing the product development process as a whole but rather focuses on the decisions already made and discusses them more closely. Although the product all together is built up using a varying number of PCB-boards connected to the motherboard, only the development of the motherboard itself is discussed closer. Also nothing is said about production and production related testing and verifying.

#### 1.4 Thesis organization

The thesis is organized into five main parts, starting off with an introduction and overview of the work that has been accomplished. Along with this is a short description of the product and the system it is used with.

The second part discusses the architecture or build-up of the product along with some theory behind the features and technologies used. This chapter also includes a short discussion about the communication interfaces of the product and the role of the product as a part of a bigger automation system.

The third part is the hardware part of the thesis, which begins with an overview and layout of the product and then proceeds to discuss a short examination of the mechanical design and a more comprehensive one about the electronic schematic design, extended with sections considering the PCB design and component selection. Finally, testing and evaluation is discussed in the last subsection.

The fourth part examines the software design involved in the product development. First, there is a more in-depth discussion regarding the hardware description language VHDL. Second, there is a shorter discussion about the XML markup language used when interfacing the product to a master device. Last in this section is a discussion about testing and validating the software.

The fifth and last part of the thesis concerns testing and confirmation of function for the complete product and finally sums up everything analyzed and discussed throughout the thesis, together with some cogitation of future improvements.

# 2 Theory of the EtherCAT protocol and module operation

This chapter starts with a presentation of the EtherCAT protocol and the theory behind its functional principle along with the standard and organization behind it. After this, the fieldbus module is presented in greater detail and the function of the module as a part of an automation system together with its interfaces, is discussed. The last part will discuss the FPGA used in the product design along with the possibilities it allows for and why it is important for the module.

#### 2.1 EtherCAT protocol

The idea of EtherCAT got its beginning in the millennium shift at the German-based company named Beckhoff and was presented to the world for the first time at the Hannover fair in 2003. The first EtherCAT fieldbuses were introduced in the same year, consisting of I/O terminals, encoder readers and drives [p. 18-21, 1]. These fieldbuses were at the time already used in pilot projects, in which conventional fieldbuses could not be used. One example of this is the Schuler AG press controllers, in which EtherCAT was used for communication between peripheral devices and a PC-based control system [p.22-25, 2].

#### 2.1.1 The EtherCAT standard and ETG (EtherCAT technology group)

EtherCAT is an open source protocol and is an IEC, ISO and SEMI standard. To begin with, EtherCAT is part of IEC standards such as the IEC 61158, IEC 61784 and IEC 61800. The IEC 61158 and IEC 61784 are international fieldbus standards and one part of the IEC 61800 includes drive profile standards in which also the EtherCAT drive profile is included. Secondly, EtherCAT is also a part of ISO 15745, which deals with device descriptions. Finally, The SEMI organization has added the EtherCAT SEMI E54.20 to their standards. [p.7, 3]

EtherCAT is maintained and managed by the EtherCAT technology group, which today consists of about 2000 member companies worldwide. One of the fundamental ideas of the EtherCAT technology group is to encourage the members to influence the future enhancements of the open standard by attending technical working classes and other meetings. This gives each member company direct possibility to influence the development of EtherCAT and indirect possibility to represent one's interest to the national standardization companies, such as IEC and ISO, via ETG. [4]

#### 2.1.2 Operating principle and frame processing

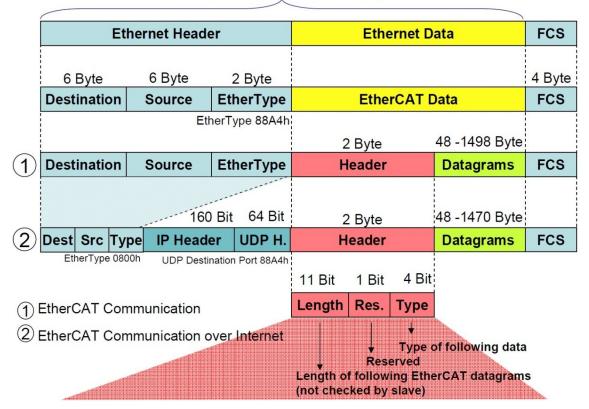

The data packets i.e. the Ethernet frames used by EtherCAT exert the same IEEE 802.3 standard as the frames used in the well familiar home or office Ethernet. First off, this allows for the use of standard network controllers and hardware on the master side. Second, EtherCAT has its own reserved EtherType, which allows for other protocols such as IP to be used parallel with the EtherCAT frames on the same bus. Alternatively EtherCAT frames can be encapsulated in UDP/IP frames or in VLAN frames. The real-time properties are not compromised even when using other protocols in parallel with the EtherCAT protocol in the same bus. On the next page, in picture 1, is an overview

of an Ethernet frame containing EtherCAT data raw and inside a UDP/IP internet frame. The first blue part from the left is the package header, which for a basic EtherCAT frame contains the destination, source and EtherType. The second (Yellow or red/green) part contains the EtherCAT data which can be further split into an EtherCAT header and one or more EtherCAT datagrams. The EtherCAT header contains the protocol type and info about the length of the EtherCAT datagrams. After the header, there are one or more datagrams which contain the raw data bits (EtherCAT configuration data and read/write process data) which are being transceived. The last part of the frame is the FCS or frame check sequence that is used for error detection.

Picture 1: Build-up of an Ethernet frame containing EtherCAT data.

No processor power is needed to process the frames as they are processed on the fly in hardware by the ESCs. Processing on the fly means that data are read and written as the bits are passing by the ESC and directly forwarded to the next closed port. This method gives the system a very low forwarding delay because the frames are not first stored, evaluated and then passed on, as is the case with the office Ethernet. [p.I-4 – I-5, 5]

#### 2.1.3 The Physical layer, PHY

The EtherCAT physical layer consists of the components and connectors that make up the interface that transmit the EtherCAT frames from one device to another. The EtherCAT protocol supports two types of physical layers. The first one is the Ethernet interface mentioned earlier that uses a standard EtherCAT compatible MAC which have to support a 100Mbit/s full duplex link, according to the requirements for EtherCAT. The typical connectors used with the Ethernet approach are the same as in the normal office sector Ethernet, namely RJ45 connectors. The cable length with this method can

be up to 100m for copper cables and up to 2km for optical fiber. The second physical layer type is the E-bus, which is a LVDS bus intended to be used as a backplane module-to-module bus but can occasionally be used for communication up to 10m distances. The E-bus is designed to reduce components and costs while achieving the same 100Mbit/s speed as with the Ethernet link. More technical information regarding the E-bus is given in reference [p. I-34 – I-37, 5]. The physical layer can be changed at any time anywhere in the system and the Ethernet protocol approach allows for hotplug-and-play compatibility. The only requirement for the transport medium is that is has to be full-duplex, leaving out solutions using half-duplex communication, such as radio transmissions. [p. 3, 6]

#### 2.1.4 FMMU and SyncManagers

The data utilization with the EtherCAT protocol is usually very high and can come up to over 97% when an Ethernet frame is fully utilized. The high utilization grades come from the fact that several slaves in the system can be addressed in both send and receive direction within one EtherCAT frame by using logical addressing. This can be compared to a system the other way around where each slave has its own addressed Ethernet packet [p. 8-9, 3]. The logical addressing is made possible by the EtherCAT FMMU function. The addressing works by mapping each slave's data bits or bytes to a respective memory area within the FMMU's logical address space that spans 4GBytes in total. The FMMU function can be compared to a CPU's MMU and its function is to convert a logical memory address to a physical one via an internal table, within each slave. Accordingly, each slave uses one or more hardware configured FMMU's located in their respective ESCs to fulfill this function. The system can be regarded as a large distributed memory which can be written and read without restriction. The maximum data size of an Ethernet frame is 1500 byte, as can be seen in picture 1, which means that the whole memory area of the 4GByte address space is fragmented over several frames. [p. 2-3, 6]

To ensure that the data transfer between a master and a slave's local application is consistent and secure, a so called SyncManager or better described as a memory manager, is used. The SyncManagers are configured by the master and initialize a buffer for exchanging the data between master and slave. This buffer function results in that no polling of the memory is needed, to know when the other side (master or slave) has finished accessing the memory. The SyncManagers can be configured in two ways, the first one is a buffered mode and the second one is a mailbox mode. The buffered mode is typically used for cyclic process data and allows both the producer and consumer to access the buffer simultaneously. The buffer works as a 3-buffer with one reserved buffer for the consumer and one for the producer while the third one keeps the latest consistently written data by the producer. This function ensures that there is always the latest data available for the consumer. In contrast, the mailbox mode alternates the access to the buffer in a way that the consumer or producer has to finish its access first before the other side has access to the buffer. This works like a handshake mechanism to ensure that all data reaches the consumer from the provider and no data is lost. The mailbox mode is usually used for application layer protocols such as EoE, SoE and CoE, to name a few examples. [p. I-40 – I-44, 5]

#### 2.1.5 Distributed clocks

One of the bigger advantages of EtherCAT compared to conventional Ethernet is the possibility to use the so called distributed clock (DC) feature which makes it possible for all EtherCAT devices to share the same EtherCAT system time. This does not only allow all the devices to be synchronized to each other, but also allow the local applications to be synchronized with each other as well. The clock synchronization works by defining one (usually the first ESC with DC compatibility) slave for holding the system reference time and then synchronizing all the other clocks (including the master's) to it. All the differences between the local clocks and the reference clock, such as drifting, offset and propagation delays can be accurately calculated, measured and compensated for with sophisticated compensation methods. For more information about how the system clock compensation is calculated the reader are encouraged to consult reference [I-45 – I-65, 5]. The ESCs can be configured to generate sync- and latch-signals synchronized to the EtherCAT system time for synchronous output signals and precise time-stamping for input signals.

While enabling synchronized clocks in the system, the time jitter between devices can achieve values of well below 1uS which can come in handy, for example in applications where several servo axes carry out synchronous coordination of movements. Naturally, this well-defined time reference is well-suited for motion control, where velocities are often calculated from sequentially measured positions. The distributed clocks can also be used to provide for accurate information about various local data acquisition and usually give better reaction times in the system. [p. 12-13, 3]

#### 2.1.6 EtherCAT master and slave implementation

A master controller in an EtherCAT system does not need any special hardware to work and can thereby be fully implemented in software using standard on-board Ethernet MACs (in PC) or an additional passive NIC card as the physical interface to the slaves. The master functionality does not put much stress on the processor and can be implemented by using open-source projects or alternatively bought as commercial software. The master stack can be implemented on many RTOSs, not only including the well familiar Windows, Linux and OS-9 but also smaller ones such as CodeSYS RTOS. The burden on the host processor is eased due to the fact that the Ethernet frame is already sorted and all the mapping (the slave FMMU functionality) happens in the slaves i.e. the slaves insert their data at respective places in the passing frame. The master software stack is also applicable for embedded systems consisting of a broad range of microcontrollers or CPUs running different operating systems or no operating system at all. Even though embedded systems often have a limited amount of memory and possibly no hard disk, a freely sizeable and scalable version of the master stack can be implemented serving the need at hand. A freely scalable and sizeable master in this case means a master for which some of the features and/or protocols can be omitted if necessary, in order to reduce the size and therefore better work together with the memory and CPU used in the specific system. [7]

The EtherCAT protocol can support up to 65535 nodes or slaves in one network. Each slave has its own ESC, as described before, implemented either in a single ASIC chip or coded into an FPGA. An EEPROM is used together with the ASIC but not always with the FPGA (can be emulated with FPGAs), which holds the configuration and general information about the slave in question. At the system initialization, the master reads

this information from each slave and can gather information such as product ID, vendor, general PDI-configuration and distributed clocks settings etc. The PDI is the communication interface between the ESC and the local application. There are a number of different types of PDIs ranging from more simple I/O-wires to more complex 8/16-bit microcontroller interfaces and 32-bit parallel busses, to name a few. The more complex PDIs naturally need a microcontroller or CPU on the application side, while the simplest ones can be implemented without any. The PDI gives the application access to the ESC DPRAM (0-64kB), which is the internal ESC memory used for exchanging data with the master. The DPRAM is handled by the SyncManagers and further on mapped onto the Ethernet frames by the FMMU, as explained before. Some of the DPRAM is reserved for configuration and status data, but up to 60kB of RAM for each slave can be used by the local application for process data exchange with the master or other slaves. The memory size available is naturally dependent on the type of ESC used or its configuration, when talking about FPGAs. [p. 20-21, 3]

Furthermore, to coordinate the master and slave applications at start up and under operation, a so called EtherCAT state machine (ESM) is implemented in the ESCs. The function of the ESM is to initialize a controlled startup of the slave and to inform the master about possible problems or errors within the application. The master is the one that requests state changes of the slave and the slave answers accordingly by changing its state or jumping to a defined state in situations when an error or other unsuspected situation has occurred. In the different states of the slave, different types of communication and amounts of data exchange between the application and the master is allowed. For example, in a safe state, the slave is not allowed to change its outputs but is however allowed to read the inputs. This is an example how to avoid dangerous situations when some error or other problem has occurred. [I-66 – I-70, 5]

In summary, the simplest slave possible, which is a digital I/O, can be implemented by using only one EtherCAT ASIC or FPGA, one EEPROM and one Ethernet PHY together with their connectors and components. On one hand, this gives a very cost effective solution for simple devices and on the other hand even the simplest slaves share the same underlying technology as for more complex and costlier ones.

#### 2.2 Module architecture and design

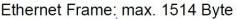

Now that the features of EtherCAT and the techniques behind EtherCAT slaves and masters have been covered, it is time to look closer at the slave that is being discussed in this thesis. As stated before, the slave module consists of one simple skeleton motherboard with the required minimum amount of components for a fully working slave. Additionally to this, there are a number of connectors on the motherboard used for interfacing other devices. First off, there are four option module connectors for addon PCBs, as described before. Second, there is one connector for a base PCB containing the power input and the physical connectors for the always present digital I/O. Third, there is one additional connector for a PCB front panel containing an LCD display together with some buttons and LEDs. Finally, one connector is reserved for diagnostic, programming and testing purposes. The minimum component requirements consist of a programmable FPGA and two EEPROMs together with a power supply and other auxiliary components and connectors. The FPGA itself contains the ESC, which is configured to use the microcontroller PDI interface. The EEPROMs are needed for the ESI information and for holding the FPGA configuration file. No microcontroller is actually used as the interface is operated using a VHDL programmed module inside the FPGA. All this, except for the base PCB, is contained inside a plastic box, giving the module non-changing physical dimensions independent of the number of option boards connected and is therefore also independent of the overall complexity of the module.

Below, in picture 2, an overall principal layout of the module's motherboard and its surroundings is presented. In the picture, the area inside the dotted line is the master side of the system, showing the EtherCAT master software alternatives and some elemental parts and configurations that go with them. The master part is shown here only for reference and will be discussed more in-depth in chapter 4.2.2 which concerns XMLs. Earlier in this chapter the non-dotted area were discussed, which consists of the FPGA in the middle together with all its connectors and possible add-on devices connected to the option module slots. The physical presence and layout of the module is presented later in chapter 3.1.

Picture 2: Module connections and functional part layout.

#### 2.3 Module as a part of a larger automation system

As known from before, the EtherCAT slave module discussed in this thesis is usually a smaller part of a bigger automation system, possibly consisting of several EtherCAT slaves, servo- / motor-drives, motors, servos and hydraulics etc. The EtherCAT fieldbus system is suitable for a wide range of applications where the strengths such as easy implementation, flexibility, speed and cost-effectiveness come into play. Some typical applications in which EtherCAT fieldbus systems are used and well suited for often relate to some sort of machine controls e.g. metal forming, packaging, robotics and other complex motion control, assembly systems, printing machines and theater scenery control.

The EtherCAT slave module, which this thesis focuses on, handles the electrical connections and acts as the interface between the master and all possible devices to be connected to the EtherCAT fieldbus. These devices can range from simple relays and contactors directly connected to the digital I/O, to more complex analog input / output modules or encoder inputs. The analog inputs are often used to connect different types of sensors that use voltage or current outputs. The analog outputs however can be used in a motor control loop as the analog speed reference output to a servo drive. Different types of encoders are often used as position feedback from electrical motors in closed loop motor control systems. These examples do not include all the types of devices that can be connected or used, but rather the most typical ones seen in practical applications. A more comprehensive description of the module interfaces and connectable devices is given later in chapter <u>2.4</u>.

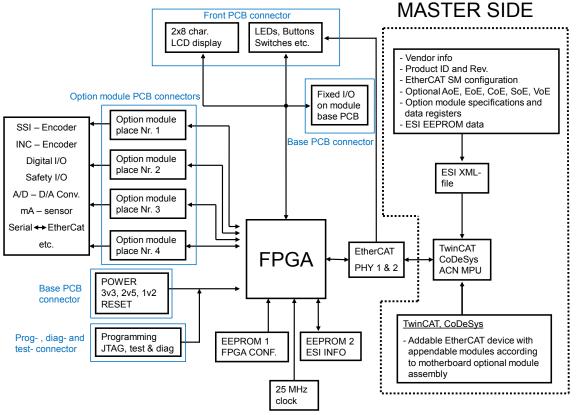

A practical example of an automation system will be given next, including the slave module as an essential part providing for the major part of the functions and interfaces between the devices. The system is shown on the next page in picture 3 and is a hoist operated by an electrical motor which is controlled by a speed reference signal originating from the EtherCAT slave and connected to a frequency inverter. The motor control loop and the application interface of the hoist system itself is operated by software inside for example a PC, using suitable EtherCAT master software for communication over the fieldbus. The system uses one master and one slave that handle all the communication between all the devices. Two encoders, one incremental and one absolute are used for the position feedback to the EtherCAT master. The incremental encoder, used in the motor control loop for position feedback, is directly connected to the motor, while the absolute encoder is connected to the wire drum after the gearbox and brake. This gives the system a fail-safe mechanism in case of a gearbox breakdown, which cannot be seen by the control system using only the incremental encoder. A magnetic brake is connected to the shaft after the gearbox and is operated with the slave's digital I/O. The brake status i.e. is the brake open or close and possible failures can also be read with the digital inputs. The digital I/O is also connected to the inverter for enabling and disabling the drive at need. Further on, An A/D-converter inside the slave is connected to a load cell on the wire mechanism used for measuring the load and forwarding the value to the PC using the EtherCAT fieldbus.

Picture 3: Example system including the slave module

#### 2.4 Interfaces to other systems and devices

Devices such as absolute or incremental encoders, A/D-D/A-converters and additional I/O are in first hand connected to the EtherCAT slave via the four option module connectors situated on the motherboard. The connectors provide for power and data communication between the option modules and the motherboard. Also, the option modules themselves provide for the same (data and possibly power) to the devices connected them. The digital I/O is connected to the base PCB and is routed to the motherboard via the motherboard's bottom connector. The connectors' physical placement on the product is shown in picture 5 in chapter <u>3.1.1</u>.

#### 2.4.1 Encoders

One of the device types that can be connected to the module via an option module is position encoders. The module will at first only accept rotary incremental and SSI-absolute encoders leaving out the option for Sin/Cos encoders which can be added in the future if needed. The INC- and SSI-ABS-encoders usually have a six- versus four-wire digital TTL interfaces which can be easily connected to the FPGA by using auxiliary driver and receiver buffers. The position is read, internally stored and sent via EtherCAT to the EtherCAT master of the system. These types of encoders are widely used in different industrial automation systems where the angular position or motion of an axle or shaft is needed.

In contrast to traditional EtherCAT encoder interfaces, the FPGA can be used to calculate additional information such as speed, acceleration etc. from the incremental encoders. This is done inside the FPGA by using logic to calculate the time difference

between the pulses and forwarding this information over EtherCAT to the master or using it internally. When this additional information is pre-processed in the FPGA, it does not only ease the burden on the master CPU but also provides very accurate speed and acceleration values usually not achievable with conventional methods. Another advantage that comes with the FPGA is the possibility to oversample and multiply the pulse count of the incremental encoders using interpolation between pulses. This can for example come in handy in cases where an expensive high resolution incremental encoder is needed but instead a cheaper one can be used together with the pulse multiplication inside the FPGA.

#### 2.4.2 D/A and A/D converters

Modules converting analog signals (current or voltage) to digital and vice versa can also be interfaced to the FPGA via the module slots. The A/D-type of converter is often used in industrial automation together with different kinds of sensors providing voltage or current outputs. These sensors can be for example load cells, such as in the example in chapter 2.3 or temperature sensors or pressure sensors, to name a few. In practice, any type of sensor providing voltage or current output could be connected. Furthermore, the A/D option module could be multiplexed providing a number of analog inputs on the same physical module. The FPGA together with its internal RAM-memory could be used if needed to oversample the analog inputs in the means of taking more than one sample during one EtherCAT update cycle and sending them in bulk whenever asked for by the EtherCAT master.

The other type of module, the D/A-converter is in most cases used as a  $\pm 10V$  speed reference output module to inverters not accepting digital speed references. These inverters are usually cheaper and therefore preferred in some cases, compared to the ones that have a digital reference which could be sent over a fieldbus, such as EtherCAT. This type of module is also included in the example in chapter 2.3

#### 2.4.3 Digital I/O

The digital I/Os of the slave module are situated on the bottom PCB and are connected to the FPGA through intelligent buffer ICs. The buffers are intelligent in the manner of automatic overload-, current limit-, short circuit-, over temperature- and over voltage protection. These buffers also have a diagnostic feedback output providing information to the user about different conditions such as overload, open-load, over temperature and short circuit. The I/Os are 24V high which is the typical voltage used in industrial automation.

The FPGA can also add some additional features to the digital I/O. The logic can for example be programmed to calculate input pulse widths or frequencies, which are of greater precision compared to the situation where the master CPU does the same operation. Naturally, this pre-processing of data also relieves stress from the master CPU. In addition to this feature, another example could be programmable digital filters which could be programmed into the FPGA and used with the digital inputs for damping glitches.

#### 2.4.4 Additional and future modules

The option module types are not restricted to the modules described in the last three chapters and in practice any module with a digital interface to the FPGA can be added.

However, the module types described before are the only ones that are developed before the product is released on the market. Depending on future needs, modules such as serial-to-EtherCAT converters, CPU & memory modules, Safety I/O s and converters for interfacing other industrial protocols with EtherCAT, can be developed.

#### 2.5 FPGA

An FPGA is a digital IC that is fitted somewhere between PLDs and ASICs in terms of complexity and configurability. An FPGA contains configurable programmable logic blocks which are freely customizable by the design engineer, just as with PLDs but can contain a lot more logical gates. The FPGAs are still not as optimized in size and performance as an ASIC performing the same function. However, one of the drawbacks using an ASIC compared to an FPGA is the loss of flexibility and upgradability because the design is frozen in silicon once it is done. Some other drawbacks are the high price and the time consuming process of developing ASICs.

The flexibility of FPGAs is further enhanced by some vendors by introducing other systems or functions inside the same IC, such as processors, microcontrollers, RAM, DSP-units and multipliers etc. This gives the FPGA IC additional functionality in the same manner as a SoC IC. Some of these functions can also be added as vendor supplied or third party software IP-cores, such as the EtherCAT core used in this project. The FPGAs arrived in the market in the mid-1980 and were at the time a new and more complex product originating from the widely used CPLDs and PAL ICs. [p. 1-4, 8]

#### 2.5.1 Overview of architecture and applications

FPGAs from different vendors usually have different underlying architecture but can all be programmed in at least the two most common used hardware programming languages, VHDL and Verilog. The architecture of FPGAs is not described in detail in this work but a short idea of how FPGAs work will be given next. All vendors use slightly different naming of their FPGA building blocks and internal functions, but the underlying idea is the same for them all.

In short, the buildings blocks of an FPGA consist of some sort(s) of LUTs, MUXs, SRAM and registers together with signal and clock connectors. These blocks are programmable to perform different functions and can be stacked or chained together to form bigger systems performing more complex functions. One FPGA can contain millions of these building blocks together with other logic, special functions or hardware described before. For more detailed information the reader is referred to the book in reference [p. 1-4, 8].

FPGAs are very widely used in different fields of application due to their wide suitability and broad complexity and cost range. The FPGAs are well suited in application fields requiring advanced parallel computations, a large number of I/Os and re-programmability etc. A few examples of application fields are DSP, ASIC prototyping, computer vision, medical imaging, cryptography, telephony centrals, industrial fieldbuses etc.

#### 2.5.2 FPGA programming

The internal functions of the FPGAs are mainly written using programming languages such as VHDL, Verilog or System C. In this project however, VHDL was chosen as the programming language. As goes for the code itself, it can of course be produced with any text editor program available but each FPGA vendor offer their own design environment that is preferred to be used together with their FPGA. The design environment is needed at least when synthetizing the code and creating a configuration file for the target FPGA. Additional to this, each vendor usually offers different kinds of chargeable or free-of-charge software for design-aid such as IO-planning-, power optimization-, simulator- and IP-core generator software etc. to ease the design process. The vendors' own tools generate the configuration file from the hardware description written in VHDL, Verilog or System C and usually there is little or no need for the designer to interfere with this process. After the configuration file is written the user can download it to the physical device using a JTAG, a microcontroller or some memory device containing the file, such as an SPI FLASH.

#### 2.5.3 FPGA usage in the project fieldbus module

An FPGA suites this project very well because the module has a lot of complex functions that cannot be implemented with a PLD or microcontroller. A microcontroller cannot be used because the project involves a lot of fast switching I/O together with several simultaneous internal processes. Thus, the fastest microcontrollers would not be able to execute the instructions fast enough to satisfy the timing constraints in the processes. Due to the loss of upgradability and production volume size, an ASIC is not suitable for this project either.

The EtherCAT functionality is bought from a third party vendor (Beckhoff) as an encrypted IP-core that has to be inserted in the project inside the FPGA development tools. The IP-core is seen by the developer as a configurable black-box with visible I/O pins for interfacing. The design engineer can then add additional logic or other functions needed in the system design around this black-box.

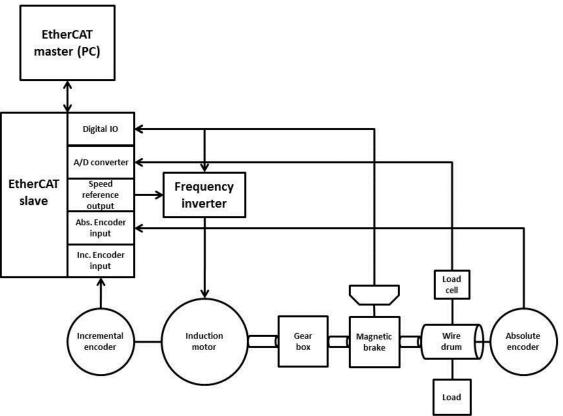

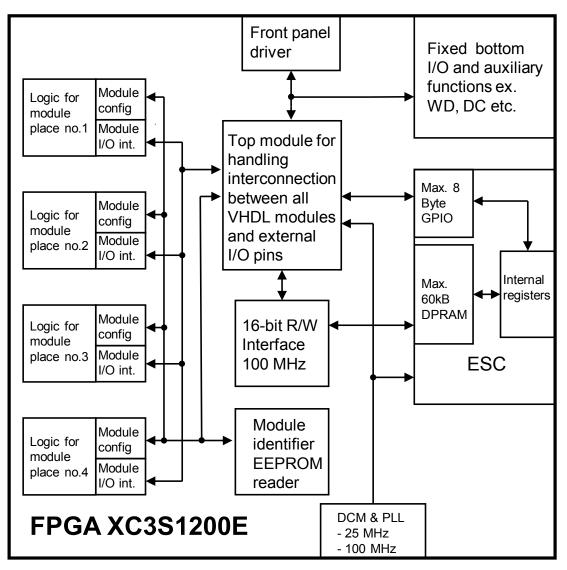

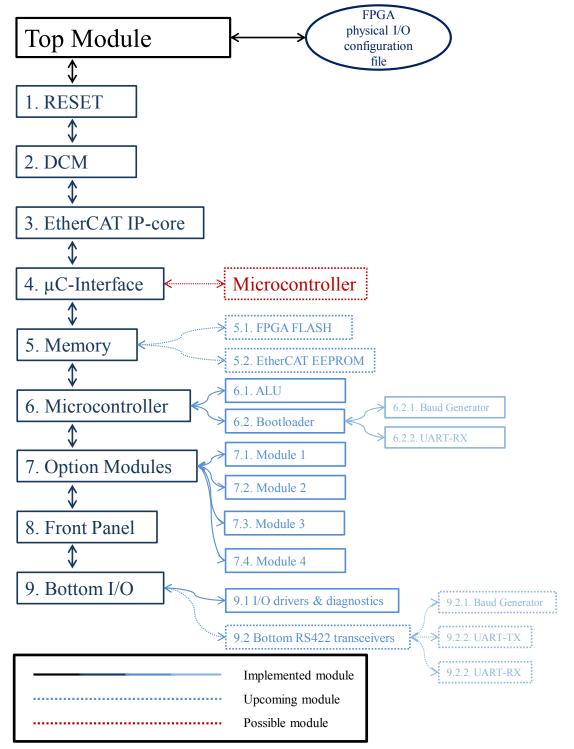

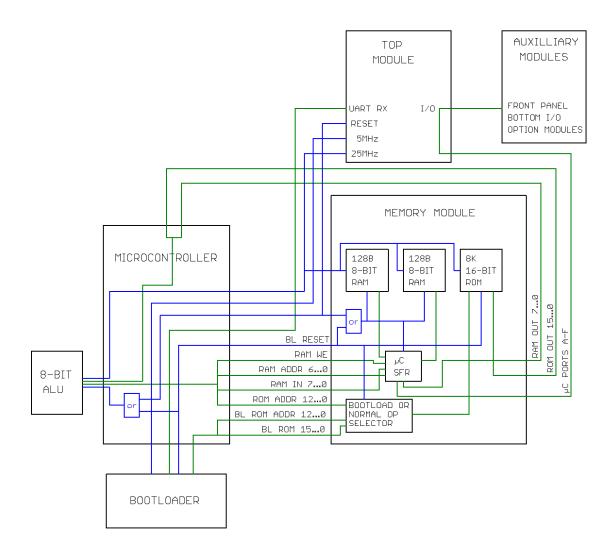

Picture 4 on the next side shows the internal module blocks of the FPGA. In the center of the picture is the so called top module which is sort of a linking module, linking together the physical FPGA pins with the internal function blocks. It also links the internal modules together via signals and buses inside the FPGA. On the left side are four boxes labeled as logic for the optional modules. These functional blocks contain all the logic needed for all possible optional modules that can be connected. The system first reads the EEPROM of the option module connected using the module identifier block and then associates the correct logic with the option module and chooses the correct internal I/O going to the top module. In the top of the picture is the front panel driver which contains the logic needed for the front panel LCD, buttons and LEDs. The data is sent out to the front panel in serial mode to a daughter FPGA situated on the front panel PCB. In the right upper corner of the picture is the module that handles the 32 digital I/Os connected to the base PCB and handles some possible auxiliary functions such as the distributed clocks and watchdog, if used. Beneath this block is the Beckhoff EtherCAT IP-core with its internal registers and DPRAM. The DPRAM is connected to the other parts of the system via the 16-bit read/write µC interface, which controls the data flow to and from the EtherCAT DPRAM. The GPIOs of the EtherCAT module are as the name says general purpose not usually suitable as application I/O but can be used with indicator LEDs and general buttons and switches. The last module of the picture is the digital clock manager module which together with a PLL generates the 100MHz internal clock from the 25MHz physical oscillator. The practical implementation inside the VHDL blocks in the picture will be dealt with in chapter 4.1.

Picture 4: Functional blocks inside the FPGA

## 3 Electronic and mechanical hardware design

This chapter starts with an overview of the mechanical design of the product, discussing both the design limitations and possibilities. After this, the electronic design is discussed and towards the end of the chapter there are two subsections discussing component selection and prototype testing and evaluation of the product. The component selection section discusses why the particular components were chosen and the prototype testing section discusses the different test phases and the observations made throughout the testing process. However, this chapter focuses mainly on the electronic design of the product, including both functional theory and PCB design, along with some discussion regarding the design related decisions that have been made in order to reduce costs, increase reliability and decrease noise etc. This section of the thesis focuses on the first near production-ready product as most of the electronic functions have been tested on breadboards and design-kits before this motherboard PCB was designed. The product is said to be near production-ready because naturally always some design errors and other surprises occur when designing a new complex PCB and testing it for the first time.

#### 3.1 Mechanical design

The overall mechanical layout of the product including the PCBs, connectors and the plastic enclosure etc. is strictly limited to the same format as the other products in the product portfolio. Some small adjustments and modifications can be done, although the overall physical appearance has to be kept the same in order to fit all the parts together in the same manner inside the same enclosure as with the other products in the portfolio. As a result, the uniformity, both mechanical and visual, between the products is kept and the same plastic mold used for the enclosures can therefore be used for all the products in the family.

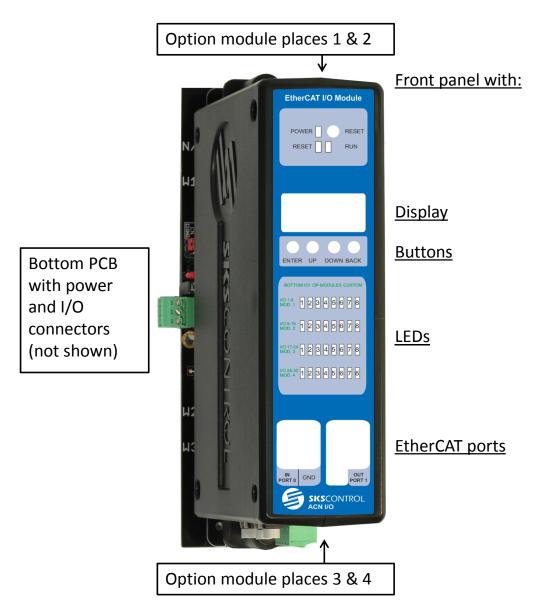

All the products in the portfolio also share the same type of bottom connector which is attached to the motherboard PCB and connects it with the bottom PCB. The bottom PCB is further on attached by screws to a metallic base plate, which for example can be fastened inside an electric cabinet. The bottom PCB of this product provides the motherboard with power and the physical connectors for the main part of the digital I/O. In Appendix A, the construction discussed is shown for illustrative purposes. Shown in the picture is the complete product, but not necessary exactly the final production version, inside the enclosure together with the bottom PCB and a preliminary front panel. The metallic base plate is not shown in the picture.

#### 3.1.1 Module and motherboard PCB mechanical layout

As discussed in the previous section and shown in Appendix A, the motherboard PCB is fitted inside a plastic enclosure and therefore has to be of a specific size and shape. As a result, the enclosure sets the limits for all type of physical connectors to and from the motherboard and naturally also has an influence on the component placement to some extent.

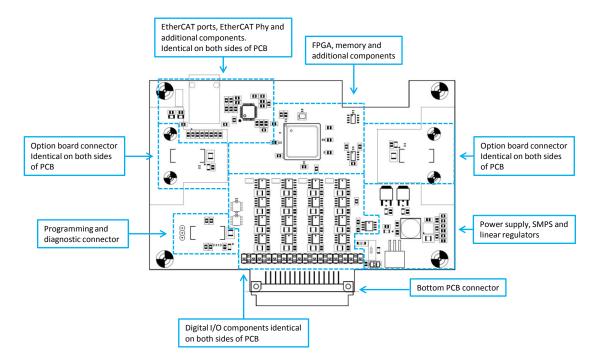

In accordance to the enclosure layout, the four option module connectors have to be placed on both edges and on both sides of the PCB in order to practically get the physical connectors of the option modules outside the enclosure on both sides. The picture in Appendix A. shows the option module placement on the enclosure and picture 5 below shows the connector placement on the motherboard PCB. Regarding the front panel, a small cut-out has to be done on the motherboard in order for an LCD display to fit. A connector with a flexible ribbon cable is used for the power and communication interface to the front panel. The EtherCAT RJ45-connectors are placed on the upper part of the PCB, accessible through holes in the front panel, to ease the EtherCAT wiring and to improve the visibility of the connectors' indicator lights. The PCB itself is held in place inside the enclosure by sockets, which go through the PCB's four mounting holes in the corners. The bottom connector is placed in the middle, on the lower edge of the PCB. The complete layout with some explanations can be seen in picture 5.

Picture 5. The complete layout of the motherboard PCB with some functional areas shown.

This picture will be further on referred to and explained in the section discussing the PCB layout and component placement.

#### 3.2 Electronic design

The electronic design is next up now that the mechanical properties of the product have been discussed and examined. The electronic realization of the product is not nearly as limited with predefined restrictions as the mechanical. However, the mechanical limits also mirror themselves to the electronic design, at least to some extent. Some of these electrical predefined things are worth mentioning. First off, the overall physical measurements of the product naturally set limits to the component placement, number of components and to the overall size of the PCB. However, these limits are not difficult to overcome as the PCB is relatively large and almost all the logical functions are fitted inside one chip, which is the FPGA. Second, the input voltage to the product, which at the same time is the digital I/O voltage, is 24V with some tolerance. All the other needed voltages have to be derived from this voltage. Last, regarding the design in general, the product also has to comply with the international EMC and other standards concerning electronic products and therefore it has to be designed and tested accordingly.

In the next subsections the electronic design and component placement of the motherboard is divided into smaller functional blocks, which are discussed separately more in-depth.

#### 3.2.1 Power supply

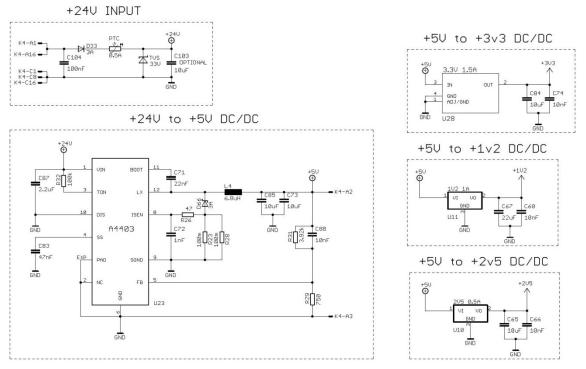

As mentioned before, the motherboard itself is fed via the bottom PCB by a 24V power supply and from this voltage all the other necessary voltages have to be created. The motherboard needs a total of five different voltages in order to work. First is the 24V which is used by the bottom digital I/O and is also routed to the option board connectors. The second voltage is 5V, which is used by a small part of the ICs and all the linear voltage regulators in the design and further on fed to the option module connectors and front panel connector. The third one is 3.3V, which is used for the FPGA I/O banks, the EEPROM, the flash memory, the EtherCAT macs and also fed to the same connectors as the 5V. The fourth and fifth ones are 2.5V and 1.2V and are only used as the internal core and auxiliary voltages for the FPGA.

The power supply of the motherboard providing these voltages was designed to consist of one SMPS, which converts 24V to 5V, together with three linear regulators for each remaining voltage. This solution gives a very high efficiency ratio on the largest voltage drop together with a low-cost and low-noise solution on the lower voltages (3.3V, 2.5V and 1.2V). The two lowest can be made by two very small linear regulators because of the low current consumption. However, the 3.3V regulator has to be of a type capable of currents over one ampere because this voltage is used by most of the internal FPGA I/O, option board ICs, front panel, LEDs etc. This naturally results in more effort regarding the thermal design for the 3.3V than for the 2.5V and 1.2V. The thermal design considerations for these linear regulators as well as for the SMPS will be dealt with in the PCB section later on.

Next up will be a more in-depth discussion about the SMPS as it is the most complex part of the power supply. Beginning with the controller of the SMPS, an Allegro A4403 valley current mode control buck converter was chosen [9]. This part was chosen mainly because of the high switching frequency (smaller and cheaper passive components), high current output (up to 3A), wide input voltage range (9V to 46V) and minimum number of external components required. The controller schematic with

component selections was directly taken from one of the example schematics in the datasheet [p. 14, 9] for a 5V supply running at 1 MHz. The controller itself contains the switching FET, leaving the auxiliary components needed down to a schottky diode, an inductor and some filter and control capacitors and resistors. Faulty conditions such as overheating, over current, over voltage and under voltage etc. are directly detected by internal logic inside the controller and don't need any external arrangements. The complete schematic for the SMPS and linear regulators are shown in picture 6 below.

Picture 6. Schematics of the power supply

As seen in the picture, all the linear regulators are connected to the 5V supply and only accompanied by a few input and output capacitors working as filters, which is enough for proper operation. The upper left part of the picture shows the protection components of the 24V input to the module, which consists of a diode, a PTC, a Zener, a TVS and two filter capacitors.

#### 3.2.2 Bottom I/O and serial ports

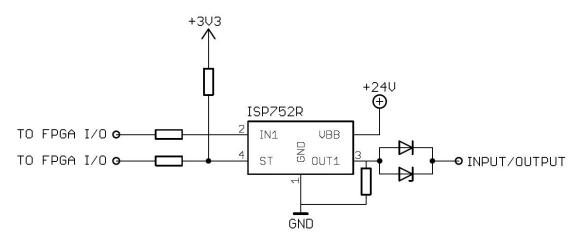

The digital bottom I/O are the module's 32 24V I/Os with their physical screw terminals located on the bottom PCB and their respective electronic implementations on the motherboard, electrically connected via the bottom PCB connector. These I/Os are bidirectional, as will be explained later and consume the major part of the 48-pin bottom PCB connector. The I/Os are implemented using an ISP752R IC [10], which is a smart power high-side switch. This is basically an N-channel power FET with a CMOS compatible input and a diagnostic feedback, that are both connected to the FPGA via series resistors, for protection in case of failure. Further on, the ISP752R-switch also includes a lot of protective functions inside the chip, such as ESD protection, overvoltage detection, current limiting and thermal shutdown etc. The reader is encouraged to consult the datasheet for more information on these.

In order to get the same physical I/O pin to work in a bi-directional manner, as an input and an output, the diagnostic feedback feature of the ISP752R is used. The diagnostic

pin is an open-collector type and can therefore be read by an FPGA I/O pin using a suitable pull-up resistor. By using this configuration, the diagnostic pin will go low when a voltage is applied to the buffer output but no input is detected on the buffer input pin. This feature normally resembles a fault condition, indicating a short circuit to the supply voltage (24V), but is now used as the digital inputs in the module. According to the datasheet, the normal short-circuit-to-supply detection voltage is around 2.8V, which is a little low for an input-high signal when using 24V logic. This detection voltage is the voltage for which the diagnostic pin goes low, when a voltage is applied to the output at the same time as the input pin is low. To overcome this problem and raise the detection voltage a schottky diode parallel with a suitable zener was put in series with the output pin. By using this configuration the zener is raising the input detection voltage by the zener-voltage and the diode is providing a low voltage-drop path when the buffer is used as an output. A zener with a breakdown voltage of 9.1V was chosen in order to get the input threshold to be about 12V which is half of the 24V supply voltage. However, one important thing to keep in mind is the sensitivity of the input. As can be seen in the  $V_{bb}$  vs.  $R_0$  graph in the datasheet [p. 14, 10], the maximum thinkable output pull-down resistance would be about 300KOhm under extreme conditions. This value only needs about 10µA of reverse current to raise the output over the 2.8V threshold mentioned above. This current value is far too low to be used in practice because already a very small inductive or capacitive coupled noise current or even the diode reverse current alone would trigger the input. To overcome this problem, a load resistor with a suitable value is put parallel with the output pin to raise the input current to about 1mA @ 12V before the triggering happens.

When the digital inputs are implemented in this way, the normal diagnostic features when using the buffer as an output are not disrupted i.e. the diagnostic pin can be normally used to detect different fault conditions as described in the datasheet. The schematics of a single type of this digital I/O implementation are shown below in picture 7.

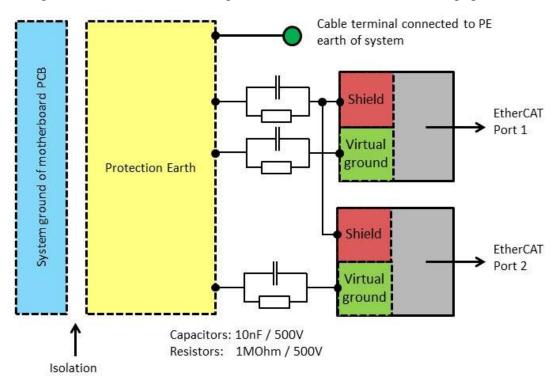

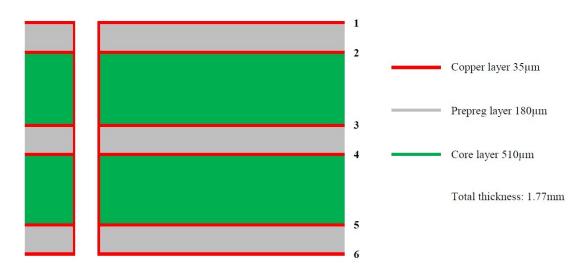

Picture 7. Implementation of one of the 32 digital I/O:s. The ST-pin (Status) is the diagnostic open collector output of the driver.