# Covert Timing Channels, Caching, and Cryptography

**Billy Bob Brumley**

## Covert Timing Channels, Caching, and Cryptography

**Billy Bob Brumley**

Doctoral dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the School of Science for public examination and debate in Auditorium AS1 at the Aalto University School of Science (Espoo, Finland) on the 16th of December 2011 at 12 noon.

Aalto University School of Science Department of Information and Computer Science

#### Supervisor

Prof. Kaisa Nyberg

#### **Preliminary examiners**

Prof. Bart Preneel, Katholieke Universiteit Leuven, Belgium Prof. Juha Röning, University of Oulu, Finland

#### **Opponent**

Prof. Nigel Smart, University of Bristol, United Kingdom

Aalto University publication series **DOCTORAL DISSERTATIONS** 136/2011

© Billy Bob Brumley

ISBN 978-952-60-4416-3 (printed) ISBN 978-952-60-4417-0 (pdf) ISSN-L 1799-4934 ISSN 1799-4934 (printed) ISSN 1799-4942 (pdf)

Unigrafia Oy Helsinki 2011

Finland

441 697 Printed matter

The dissertation can be read at http://lib.tkk.fi/Diss/

#### Aalto University, P.O. Box 11000, FI-00076 Aalto www.aalto.fi

| ■ Monograph                                                                  | ssertation (summary + original articles) |

|------------------------------------------------------------------------------|------------------------------------------|

| Date of the defence 16 December 2011                                         | Language English                         |

| Manuscript submitted 29 July 2011                                            | Manuscript revised 14 November 2011      |

| Field of research Theoretical Computer                                       | Science                                  |

| Series Aalto University publication serie                                    | s DOCTORAL DISSERTATIONS 136/2011        |

| Unit Department of Information and Com                                       | iputer Science                           |

| Publisher School of Science                                                  |                                          |

| Name of the doctoral dissertation<br>Covert Timing Channels, Caching, and Cr | yptography                               |

| Billy Bob Brumley                                                            |                                          |

| Author                                                                       |                                          |

#### **Abstract**

Side-channel analysis is a cryptanalytic technique that targets not the formal description of a cryptographic primitive but the implementation of it. Examples of side-channels include power consumption or timing measurements. This is a young but very active field within applied cryptography. Modern processors are equipped with numerous mechanisms to improve the average performance of a program, including but not limited to caches. These mechanisms can often be used as side-channels to attack software implementations of cryptosystems. This area within side-channel analysis is called microarchitecture attacks, and those dealing with caching mechanisms cache-timing attacks. This dissertation presents a number of contributions to the field of side-channel analysis. The introductory portion consists of a review of common cache architectures, a literature survey of covert channels focusing mostly on covert timing channels, and a literature survey of cache-timing attacks, including selective related results that are more generally categorized as side-channel attacks such as traditional timing attacks. This dissertation includes eight publications relating to this field. They contain contributions in areas such as side-channel analysis, data cache-timing attacks, instruction cache-timing attacks, traditional timing attacks, and fault attacks. Fundamental themes also include attack mitigations and efficient yet secure software implementation of cryptosystems. Concrete results include, but are not limited to, four practical side-channel attacks against OpenSSL, each implemented and leading to full key recovery.

**Keywords** cryptography, covert channels, side-channel analysis, timing attacks, cache-timing attacks

| ISBN (printed) 978-952 | -60-4416-3 <b>ISBN (pdf)</b> | 978-952-60-4417-0                  |

|------------------------|------------------------------|------------------------------------|

| ISSN-L 1799-4934       | ISSN (printed) 1799-4934     | ISSN (pdf) 1799-4942               |

| Location of publisher  | Espoo Location of printi     | ing Helsinki Year 2011             |

| Pages 238              | The dissertation can         | be read at http://lib.tkk.fi/Diss/ |

#### **Preface**

The following entities generously support the work in this dissertation.

- Helsinki Doctoral Programme in Computer Science Advanced Computing and Intelligent Systems (Hecse).

- Academy of Finland (project #122736).

- The European Commission through the ICT program under contracts ICT-2007-216499 CACE and ICT-2007-216676 ECRYPT II.

- The Nokia Foundation.

I am indebted to the following individuals for their gracious support. Please accept my sincerest thanks.

- Prof. Kaisa Nyberg, my supervisor and mentor.

- My fellow colleagues in the cryptography group at Aalto University School of Science.

- My co-authors with whom I've had the pleasure to collaborate.

Espoo, November 14, 2011,

Billy Bob Brumley

### **Contents**

| Preface                     | 1  |

|-----------------------------|----|

| Contents                    | 3  |

| List of Publications        | 5  |

| Author's Contribution       | 7  |

| List of Acronyms            | 9  |

| 1. Introduction             | 11 |

| 2. Microprocessor Caches    | 21 |

| 3. Covert Channels          | 27 |

| 4. Cache-Timing Attacks     | 37 |

| 5. Cryptography Engineering | 75 |

| 6. Conclusion               | 81 |

| Bibliography                | 85 |

| A. Recipes                  | 93 |

| Publications                | 99 |

Contents

#### **List of Publications**

This dissertation consists of an overview and of the following publications which are referred to in the text by their Roman numerals.

- I Billy Bob Brumley and Risto M. Hakala. Cache-timing template attacks. In Advances in Cryptology - ASIACRYPT 2009, 15th International Conference on the Theory and Application of Cryptology and Information Security, Tokyo, Japan, December 6-10, 2009, LNCS vol. 5912, pages 667-684, Springer, 2009.

- II Onur Aciçmez, Billy Bob Brumley, and Philipp Grabher. New results on instruction cache attacks. In Cryptographic Hardware and Embedded Systems, CHES 2010, 12th International Workshop, Santa Barbara, CA, USA, August 17-20, 2010, LNCS vol. 6225, pages 110-124, Springer, 2010.

- III Billy Bob Brumley, Risto M. Hakala, Kaisa Nyberg, and Sampo Sovio. Consecutive s-box lookups: a timing attack on SNOW 3G. In *Information and Communications Security 12th International Conference, ICICS 2010*, Barcelona, Spain, December 15-17, 2010, LNCS vol. 6476, pages 171-185, Springer, 2010.

- IV Billy Bob Brumley and Nicola Tuveri. Cache-timing attacks and shared contexts. In 2nd International Workshop on Constructive Side-Channel Analysis and Secure Design, COSADE 2011, Darmstadt, Germany, 24-25 February 2011, pages 233-242, Technische Universität Darmstadt / CASED, 2011.

- V Billy Bob Brumley and Dan Page. Bit-sliced binary normal basis multiplication. In 20th IEEE Symposium on Computer Arithmetic, ARITH 2011,

Tübingen, Germany, 25-27 July 2011, pages 205-212, IEEE Computer Society, 2011.

VI Billy Bob Brumley and Nicola Tuveri. Remote timing attacks are still practical. In Computer Security - ESORICS 2011 - 16th European Symposium on Research in Computer Security, Leuven, Belgium, September 12-14, 2011, LNCS vol. 6879, pages 355-371, Springer, 2011.

VII Billy Bob Brumley, Manuel Barbosa, Dan Page, and Frederik Vercauteren. Practical realisation and elimination of an ECC-related software bug attack. Accepted for publication in *Topics in Cryptology - CT-RSA 2012 - The Cryptographers' Track at the RSA Conference 2012*, San Francisco, CA, USA, February 27-March 2, 2012, LNCS, 18 pages, Springer, 2012.

VIII Billy Bob Brumley. Secure and fast implementations of two involution ciphers. Accepted for publication in 15th Nordic Conference on Secure IT Systems, NordSec 2010, Helsinki, Finland, 27-30 October 2010, LNCS vol. 7127, 14 pages, Springer, 2011.

#### **Author's Contribution**

#### Publication I: "Cache-timing template attacks"

The current author is responsible for proposing this research topic, implementing the side-channel and lattice portions of the attack, and the related writing.

#### Publication II: "New results on instruction cache attacks"

The current author is responsible for the attack portion of the work as well as the related writing.

## Publication III: "Consecutive s-box lookups: a timing attack on SNOW 3G"

The current author is responsible for formalizing and implementing the sidechannel, proposing improvements to the state recovery algorithm, implementing the bit-sliced version of the cipher, and the related writing.

#### Publication IV: "Cache-timing attacks and shared contexts"

The current author is responsible for proposing this research topic, interpreting experiment results, and the related writing.

#### Publication V: "Bit-sliced binary normal basis multiplication"

The current author is responsible for proposing this research topic, implementing the multiplication circuits, and the related writing.

#### Publication VI: "Remote timing attacks are still practical"

The current author is responsible for proposing this research topic, devising the attack, implementing the lattice portion of the attack, and the related writing.

## Publication VII: "Practical realisation and elimination of an ECC-related software bug attack"

The current author is responsible for proposing this research topic, implementing the attack, and the related writing.

## Publication VIII: "Secure and fast implementations of two involution ciphers"

The current author is solely responsible for this work.

#### **List of Acronyms**

3GPP3rd Generation Partnership Project

AES Advanced Encryption Standard

AES-NI Advanced Encryption Standard Instruction Set

ALU Arithmetic Logic Unit Advanced Micro Devices AMD Advanced RISC Machines ARM BPA **Branch Prediction Analysis**

Cipher Block Chaining mode CERT Computer Emergency Response Team

CFS Completely Fair Scheduler CLMUL Carryless Multiplication CPU Central Processing Unit

CTRCounter mode

CBC

CVE Common Vulnerabilities and Exposures

dcache data cache

DEC Digital Equipment Corporation DES Data Encryption Standard DSA Digital Signature Algorithm Elliptic Curve Cryptography ECC

ECDH Elliptic Curve Diffie-Hellman key exchange

**ECDHE** Elliptic Curve Diffie-Hellman key exchange, Ephemeral type

ECDSA Elliptic Curve Digital Signature Algorithm

FSM Finite State Machine GCM Galois Counter Mode

**GPGPU** General Purpose computing on Graphics Processing Units

GPU Graphics Processing Unit HMMHidden Markov Model

Hyper-Threading Technology HTT

IBM International Business Machines

icache instruction cache

ISO International Organization for Standardization

KB Kilobyte, 1024 bytes

KVM Kernelized Virtual Machine System 370

LFSR Linear Feedback Shift Register

LFU Least Frequently Used

LNCS Lecture Notes in Computer Science

LRU Least Recently Used

MIPS Microprocessor without Interlocked Pipeline Stages

MIT Massachusetts Institute of Technology

MRU Most Recently Used NAF Non-Adjacent Form

NIST National Institute of Standards and Technology

NSA National Security Agency

OR bitwise OR, logical disjunction

OS Operating System

PC Personal Computer

PGP Pretty Good Privacy

RAM Random-Access Memory

RSA Rivest, Shamir and Adleman public key cryptosystem

SIMD Single Instruction Multiple Data SMT Simultaneous Multithreading

SPN Substitution Permutation Network

SSE Streaming SIMD Extensions SSE2 Streaming SIMD Extensions 2

SSH Secure Shell

SSL Secure Sockets Layer

SSSE3 Supplemental Streaming SIMD Extensions 3

TCP Transmission Control Protocol

TCSEC Trusted Computer System Evaluation Criteria

TLS Transport Layer Security

VAX Virtual Address extension

VM Virtual Machine

VMM Virtual Machine Monitor

VQ Vector Quantization

XOR bitwise exclusive OR, exclusive disjunction

#### 1. Introduction

Much like signal processing, cryptology is a peculiar science due to its symbiotic relationship with application. Theory alone without an express use case can be difficult to justify in this field. One good example of this gap between theoretical and applied cryptography is the problem of secure pseudorandom number generation, perhaps for use in a stream cipher. On one hand, the venerable Blum-Blum-Shub construction has an extremely strong security proof and theorists might assert the problem solved. On the other hand, it is rarely used in practice due to its implementation aspects: it is not particularly fast and requires large area. The stream ciphers used in practice are instead built using easily implementable components such as feedback shift registers and/or native microprocessor instructions such as integer additions, but in contrast little can usually be proved about the security of said constructions.

Proposals for cryptographic primitives such as a block cipher are expected to be accompanied by extensive security proofs demonstrating resistance to known cryptanalytic techniques such as differential and linear cryptanalysis. Such proofs make certain assumptions about the abilities of the attacker and are defined by the security model. If a primitive is at all useful, at some point it must make its way from the formal written specification to a concrete implementation, perhaps in software. This task is inevitably the burden of an engineer.

When this leap from paper to practice occurs, a natural concern is how well the physical implementation of the primitive preserves the assumptions of the security model. Or perhaps, from another perspective, how well the theoretical security model reflects the realities imposed by practical applied cryptography.

Over the past two decades, the irrefutable stance of both academia and industry is clear: implementation aspects can easily invalidate the assumptions of the security model and lead to serious vulnerabilities. This breed of cryptanalytic attack is known as side-channel analysis and additionally makes use of a platform, architecture, and/or implementation dependent signal procured during the execution of a cryptographic primitive. Examples of side-channels include power consumption measurements, electromagnetic radiation measurements, acoustic emanations, computation faults, and various timing measurements. These channels are not theoretical and are born out of practice.

This dissertation exclusively concerns side-channel attacks, and within this area focuses on timing attacks. One specific type of timing attack exploits the caching mechanism commonly featured in modern microprocessors. These cache-timing attacks exploit the fact that the latency of fetching data from main memory is essentially governed by the availability of said data in the cache and, by definition and design, is not a constant duration. Cache-timing attacks are the main topic of this dissertation.

The bulk of this dissertation consists of eight publications that represent novel contributions and advance this field of study. A summary of said publications follows.

**Publication I.** One of the major challenges when implementing a cache-timing attack is how to accurately and efficiently process the signal, i.e., the sidechannel made up of timing data. When attacking a block cipher that uses table lookups the strategy is to directly interpret the timing data to infer part of an index used into a lookup table, depending on how this lookup table maps into the cache. In contrast, the implementation of a public key cryptosystem often uses dynamic memory where a different strategy is needed: these types of cache-timing attacks attacks are essentially more about memory access patterns. With that in mind, Publication I presents a framework for efficiently processing large quantities of this type of cache-timing data. The framework uses Vector Quantization (VQ) and Hidden Markov Models (HMMs) to accomplish this. Roughly speaking, VQ reduces the dimension of the data and the HMM accounts for the control flow of the algorithm that produced the signal. This framework is used as part of a cache-timing attack on OpenSSL's implementation of ECDSA. After processing the cache-timing data with the framework, the derived key material is used to mount a lattice attack to recover the private key. The attack succeeds with only a few thousand traces and less than one hour of offline computation on a single desktop machine. The current author is responsible for proposing this research topic, implementing the side-channel and lattice portions of the attack, and the related writing.

**Publication II.** In contrast to data cache-timing attacks that seek to exploit key-dependent memory references, instruction cache attacks exploit the variable execution of code segments that might be caused, for example, by a logic

branch. Building on previous work on instruction cache-timing attacks, Publication II presents improved analysis techniques for these attacks and also considers mitigation strategies. The signal of an instruction cache side-channel is often quite similar to that of a data cache. The work applies the framework in Publication I to timing data from the instruction cache. This is used to attack OpenSSL's implementation of DSA. Similar to the data cache attack in Publication I, the first stage uses the framework to process the signal and last stage using lattice methods to recover the private key. The work furthermore proposes, implements, and evaluates a number of countermeasures to these attacks at both software and hardware levels. The current author is responsible for the attack portion of the work as well as the related writing.

Publication III. Based on the stream cipher SNOW 2.0, SNOW 3G is a softwareoriented stream cipher used in 3GPP mobile networks. Roughly speaking, the cipher consists of some linear state implemented as a word-based LFSR and some nonlinear state that emulates a block cipher round function: the linear process masks the output of the nonlinear process to produce keystream words. Both processes are often implemented using table lookups that pose a cachetiming attack threat. Building on previous work that attacks the linear process of SNOW 2.0, Publication III presents a cache-timing attack on SNOW 3G. The attack intuition is that the lookups within the nonlinear process in fact leak much more information than that of the linear process which can be leveraged to dramatically trim the search space of a state recovery algorithm. At a high level, the attack is an exhaustive search of the state space using a backtracking algorithm where the side-channel data constrains the search space. Finally, the work proposes and implements an efficient bit-slicing countermeasure that applies to batch keystream generation. The current author is responsible for formalizing and implementing the side-channel, proposing improvements to the state recovery algorithm, implementing the bit-sliced version of the cipher, and the related writing.

**Publication IV.** With respect to performance-critical software, dynamic allocation of memory is an expensive operation. A logical strategy is to allocate the data only once and save it for reuse later. A shared context is a software mechanism that implements said strategy. OpenSSL uses a shared context to initialize all of its element representations, such as integers or finite field elements. The mechanism works roughly like a stack, keeping a double linked list of elements and dynamically allocating memory for new elements as required, appending to the list. As suggested in Publication I, this behavior can lead to a cache-timing attack vulnerability since temporary variables get reused in a de-

terministic way. One countermeasure proposed, but not implemented, therein suggests that the context should randomize its allocation. To this end, Publication IV explores the ability of a shared context to mitigate cache-timing attacks. The work performs a detailed analysis of OpenSSL's shared context implementation and, based on said analysis, implements a simple memory alignment countermeasure. Surprisingly, the results suggest that this is ineffective and that the allocation policy of a shared context has little to no influence on the resulting signal. The work raises some interesting questions concerning the true origin of the side-channel. The current author is responsible for proposing this research topic, interpreting experiment results, and the related writing.

Publication V. Most mainstream processors feature at least some form of an integer multiplication instruction that can be used to implement finite fields with large prime characteristic. On the other hand, implementation of (large) binary fields requires a carryless multiplication instruction that only a minority of processors feature. The textbook way to implement said fields involves some online precomputation into a lookup table, then any number of methods resembling schoolbook multiplication but with shifts, XORs, and lookups into said table. This is not comparatively efficient and can also lead to a cachetiming attack vulnerability. Two standard representations used for finite field elements are a polynomial basis and a normal basis. The latter is normally not particularly competitive with respect to performance. Bit-slicing is a software technique where essentially a w-bit processor is used as w 1-bit processors to run w logic computations in parallel: this allows a quasi-hardware design approach to software components. Furthermore, bit-slicing has inherent resistance to cache-timing attacks since state-dependent memory accesses are replaced by their computational equivalent in terms of bit logic. Motivated by cache-timing attacks and surveying existing hardware normal basis multiplication techniques, Publication V applies the bit-slicing approach to realize secure parallel multiplications in software. The results encompass a multitude of field sizes and compare the timings to those of an existing library for efficient polynomial basis multiplication on a number of different platforms. The results suggest that, for batch operations, the performance gap between polynomial and normal basis multiplication is smaller than suggested in the literature. The current author is responsible for proposing this research topic, implementing the multiplication circuits, and the related writing.

**Publication VI.** In contrast to cache-timing attacks that often require some malicious code executing locally, general timing attacks measure the overall execution time of a high level operation. Hence both are side-channel attacks yet

the latter is a much weaker attack. A key component to an elliptic curve cryptography implementation is the scalar multiplication routine that computes multiples of a point on the curve with itself. Montgomery's ladder is one method to perform said routine and has the inherent potential to resist many types of side-channel attacks due to its extremely regular nature: it always performs the same sequence of finite field operations regardless of the certain value of a key bit. Exploiting a timing attack vulnerability in OpenSSL's ladder implementation, Publication VI devises and implements an attack that leads to private key recovery. The attack is able to recover the private key of a TLS server that authenticates using ECDSA signatures by using only the timings of exchanged handshake messages, the messages themselves, and the signatures on the messages. The final stage of the attack uses lattice methods to compute the private key. The attack only requires a few minutes and is demonstrated to succeed in both local and remote scenarios. The current author is responsible for proposing this research topic, devising the attack, implementing the lattice portion of the attack, and the related writing.

Publication VII. Fault attacks can be considered as a type of side-channel attack in which, at some stage during operation, a device makes a computation error. This is traditionally a hardware-related topic. Modeling a known OpenSSL software bug as a fault attack, Publication VII gives a detailed analysis of said bug, discusses implications, and outlines a number of attacks exploiting it. Briefly, the modular reduction routines in OpenSSL for some finite fields associated with standardized elliptic curves can fail in very rare instances. Exploiting this bug, Publication VII devises and implements an attack against various ECDH modes in TLS that recovers the server's static private key by querying the server with cleverly chosen inputs. The work postulates that formal verification techniques, while challenging, could have prevented this bug. The current author is responsible for proposing this research topic, implementing the attack, and the related writing.

Publication VIII. Anubis and Khazad are two block ciphers that resemble AES in many respects. But different from AES, they have an involution property: decryption differs from encryption only by the key schedule, i.e., the code the cipher executes in operation is the same both ways. Motivated by cache-timing attacks and building on two recent results on AES software implementations, Publication VIII gives both serial and bit-sliced implementations of these ciphers. The intuition for the serial Anubis implementation is that the nonlinear layer has a very elegant implementation using a byte shuffler, e.g., that available through Intel's SSSE3 instruction set. This version is competitive with the

reference implementation that uses table lookups, yet in contrast is resistant to cache-timing attacks. On the bit-slicing side, interestingly the results show that, in software on the considered platform, the per-round operation of Anubis is slightly faster than that of AES. The current author is solely responsible for this work.

**Themes and scope.** With the previous description of the publications making up this dissertation, a number of unequivocal themes emerge. A non-exhaustive list of these themes follows, along with a short discussion of each theme, defining the scope of this dissertation.

- 1. Naturally, the most prevalent theme of this dissertation is that of side-channel analysis. There are many ways to approach this topic, but regarding microarchitecture attacks perhaps the most logical and classical in some respects is to begin by constructing a covert channel from the microarchitecture mechanism and determine how it can be used for information transfer. Then turning said channel into a side-channel by one of the party's inadvertent use of the channel. Publication I and Publication II include cache-timing attacks on asymmetric key cryptosystems, Publication VII a timing attack on an asymmetric key cryptosystem, and Publication VII a fault attack on an asymmetric key cryptosystem. While their channels are realized in very different ways, these works all fall under the theme of side-channel analysis.

- 2. After successfully devising, and even implementing, a side-channel attack, it is tempting to proudly disseminate the results, declare victory and move on to the next conquest. This approach is not constructive. Successfully implementing an attack gives the experimenter a unique perspective on the result, including the intuition for why and how it works and, in particular, the best way to prevent it. Indeed, countermeasures are an integral, even obligatory part of the research process in this field. While all of the publications making up this dissertation treat countermeasures at least as an aside, a number of them deal exclusively with this crucial theme. In particular, Publication IV focuses on a single cache-timing attack countermeasure for asymmetric key cryptosystems, Publication V even more general timing-attack countermeasures for asymmetric key cryptosystems, and Publication VIII cache-timing attack countermeasures for symmetric key cryptosystems.

- 3. In light of side-channel attacks, a practical concern is whether it is possi-

ble to realize implementations that resist these attacks, yet at the same time are still computationally efficient. Since side-channel attacks themselves are implementation-specific and depend, for example, on the architecture where the compiled code executes, it is natural to consider architecture-specific features that can aid in side-channel mitigation. For example, parallel computation via Single Instruction Multiple Data (SIMD) featured on many commodity microprocessors is often used to improve efficiency but can also, in some instances, be used to thwart timing attacks. This is sometimes even an unintentional consequence of optimization. Efficient yet secure software implementations of cryptosystems is a strong theme of this dissertation. In particular, Publication V concerns asymmetric key cryptosystems and Publication VIII symmetric key cryptosystems. This theme relates to the previous one, but approaches the issue from the opposite direction and with different priorities.

In order to provide a concise yet thorough coverage on the subject matter and avoid lengthy tangents, this dissertation attempts to restrict the scope as reasonably as possible. With that in mind, regretfully there are a number of fascinating topics that, although related to this dissertation in some respects, do not fall under this scope. A short yet inevitably non-exhaustive list of these topics follows.

- 1. Pioneered by Aciçmez et al. [AScKK06, AcKKS07], another type of microarchitecture attack is that which exploits the behavior of the branch predictor. To avoid excessively stalling the instruction pipeline, the job of a microprocessor's branch predictor is to intelligently guess the outcome of a logic branch based on previous outcomes, fetch the resulting instructions, and speculatively execute them. Branch predictor attacks execute malicious code that essentially spies on the branch target buffer to determine if the victim code takes a logic branch or not by measuring the execution time of its own branch statements. If the victim executes key dependent logic branches, this yields a side-channel that can be used for cryptanalytic purposes. This dissertation omits this topic.

- 2. The framework in Publication I leverages two well-established signal processing techniques: VQ and HMMs. VQ maps vectors from a given domain to a finite set of vectors called a codebook. This is usually implemented by mapping said vectors to the closest codebook vector by Euclidean distance. HMMs

are formal models of discrete-time stochastic processes. Given such a process that, with certain probabilities, emits one of many observable events when changing states, one use of an HMM is calculating the most likely sequence of states that explains the observations. This dissertation does not cover the theory behind these techniques. The textbook by Russell and Norvig is a standard reference for HMMs [RN10].

- 3. Lattices are mathematical objects that have many uses in cryptography from cryptographic primitives to attacking schemes with partially known secret data. They are generally useful for finding small solutions to underdetermined systems of equations. Lattice methods are an effective endgame for many side-channel attacks: combining public information with (private) partial key material derived in the analysis phase, i.e., procured from the signal, to recover the complete private key. The work of Howgrave-Graham and Smart is an excellent example [HGS01]. Although three publications that are part of this dissertation apply lattices accordingly, the scope does not encompass the theory behind lattice methods.

- 4. This dissertation gives an extensive survey of existing results on cachetiming attacks and also advances the field by presenting some novel contributions to the topic. In the end, caching is the culprit here and one natural response is to consider alternative cache designs and architectures that can provide a higher degree of security. Such designs do indeed exist (e.g., Page's partitioned cache [Pag05]), but are not discussed in this dissertation.

- 5. Traditional models for provable security of ciphers fail to capture side-channel attacks. In response, some recent models (e.g., leakage-resilient cryptography), attempt to account for side-channels and even parameterize the security as a function of the side-channel capacity. Such models are not a topic of this dissertation. In fact, one can argue that such models are predisposed to failure and can do more harm than good: see the work of Koblitz and Menezes for an insightful discussion [KM11].

**Outline.** The structure of this dissertation is as follows. Chapter 2 contains brief background on caching mechanisms. Chapter 3 contains background on covert channels, including a selective chronological literature survey. Transitioning from the previous chapter, Chapter 4 contains a selective chronological literature survey of timing attacks that focuses on cache-timing attacks. Said

survey is interleaved with discussions summarizing the main contribution of the publications appearing in this dissertation, placing them in context to show how they build and improve upon previous work. Chapter 5 is similar in structure, but is less extensive and concerns efficient and secure software methods for cryptography engineering. Chapter 6 draws conclusions, summarizes the impact of this dissertation, and examines outlook in this field. Much of the subject matter of this dissertation deals with concrete realization of side-channels, and to this end Appendix A contains some helpful tools of the trade. This culminates with the listed publications, in order.

Introduction

#### 2. Microprocessor Caches

cache: a secure place of storage.

Webster's New Collegiate

Dictionary

There are a number of thorough references for cache design that treat the subject very formally. This dissertation is not one of them. In particular, the textbooks by Hennessy and Patterson [PH90, 8.3], Patterson and Hennesey [PH07, 7.2], and Page [Pag09, 8.3] are excellent references on the topic.

This chapter contains a brief review of practical cache architectures. These concepts are useful in understanding the nature of the cache as a covert channel and side-channel, that being the focus of subsequent chapters.

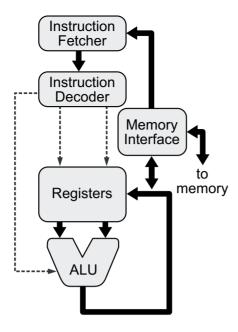

**Microprocessor operation.** Figure 2.1 illustrates typical microprocessor operation. The instruction fetcher is responsible for fetching instructions to be executed from main memory. It then passes these to the instruction decoder that interprets these instructions. The result then gets executed, generally by, for example, passing it to the arithmetic logic unit (ALU) that might operate on a number of register values and store the result in a register or main memory, or move a value between a register and main memory.

Cache architectures. The memory interface component depicted in Fig. 2.1 commonly contains at least two critical components: a data cache and an instruction cache. The discussion focuses on the former. Moving values between registers is an extremely low latency operation, while movement between registers and main memory suffers higher latency. The number of registers is unfortunately limited. To offset the cost of such movement, modern microprocessors employ a data cache; this has a much higher capacity than the working set of registers, higher latency than register access, but much lower latency than memory access. Data from main memory is stored first in the cache; when the CPU needs data from main memory, it looks for it initially in the cache. If it finds it, this is a cache hit and it looks no further; otherwise, a cache miss

Figure 2.1. Simplified microprocessor operation. Source: http://commons.wikimedia.org/ wiki/File:CPU\_block\_diagram.svg

and it reads the data from main memory. The blocks of memory in the cache are called **cache lines**. There are three common ways to implement such a cache.

Direct mapped cache. The simplest form allows a block of memory to be stored in one and only one location in a direct mapped cache, illustrated in Fig. 2.2. The bits in a memory address are split into three parts. The tag is a unique identifier for a block of memory. The line identifies which cache line a block of memory can be stored in. The offset identifies the byte offset within the block. Along with the data, the cache lines also have a tag associated with them, representing what block of memory currently resides within a cache line. The cache logic works as follows when processing a request for data at a given memory address. The line portion of the address identifies the specific cache line for the memory block; the cache controller compares the corresponding tag of the cache line to the tag of the memory address. If they match, a cache hit occurs and it uses the offset portion of the address to load the data at an offset within the given cache line. Otherwise, a cache miss occurs and it loads the data from the next level in the memory hierarchy. Advantages of a direct mapped cache include simplicity and low latency. The minimal amount of logic means they are easy to implement compactly. Disadvantages can include poor cache utilization and cache thrashing. Consider an extreme example where only two memory blocks are accessed. By chance, these memory blocks have

|            |         |      |          |     | address | tag | line | offse |

|------------|---------|------|----------|-----|---------|-----|------|-------|

| ++-        | +       |      |          |     |         |     |      |       |

| 0          | 1       | +    |          |     | D831    | D8  | 3    | 1     |

| ++-        | +       | 1    |          |     | 35A6    | 35  | Α    | 6     |

| 1          | 1       | 1    |          |     | 937F    | 93  | 7    | F     |

| ++-        | +       | 1    |          |     | 0384    | 03  | 8    | 4     |

| 2          | 1       | 1    |          |     | 2B93    | 2B  | 9    | 3     |

| ++-        | +       | 1    |          |     | FA63    | FA  | 6    | 3     |

| 3   MM   Y | YYY  <- | -+   |          |     | 4B91    | 4B  | 9    | 1     |

| ++-        | +       | MM = | = D8 ? H | : M | 0F9C    | 0F  | 9    | C     |

| 4          | 1       |      |          |     | CD44    | CD  | 4    | 4     |

| ++-        | +       |      |          |     | D49F    | D4  | 9    | F     |

| 5          | 1       |      |          |     | 14BA    | 14  | В    | A     |

| ++-        | +       |      |          |     | E4F1    | E4  | F    | 1     |

| 6          | 1       |      |          |     | B319    | В3  | 1    | 9     |

| ++-        | +       |      |          |     | 14F3    | 14  | F    | 3     |

| 7          | 1       |      |          |     | 3E09    | 3E  | 0    | 9     |

| ++-        | +       |      |          |     | 13DA    | 13  | D    | Α     |

| 8          | 1       |      |          |     | 0C6E    | 0C  | 6    | E     |

| ++-        | +       |      |          |     | 6BBC    | 6B  | В    | C     |

| 9          | 1       |      |          |     | 44A2    | 44  | Α    | 2     |

| ++-        | +       |      |          |     | 26D4    | 26  | D    | 4     |

| A          | 1       |      |          |     | 04A3    | 04  | Α    | 3     |

| ++-        | +       |      |          |     | 5F59    | 5F  | 5    | 9     |

| B          | 1       |      |          |     | 9FB3    | 9F  | В    | 3     |

| ++-        | +       |      |          |     | 65DE    | 65  | D    | E     |

| C          | 1       |      |          |     | D65B    | D6  | 5    | В     |

| ++-        | +       |      |          |     | 6D6F    | 6D  | 6    | F     |

| D          | 1       |      |          |     | 8FAC    | 8F  | Α    | C     |

| ++-        | +       |      |          |     | 90DC    | 90  | D    | C     |

| E          | 1       |      |          |     | C8E0    | C8  | E    | 0     |

| ++-        | +       |      |          |     | 7A4B    | 7A  | 4    | В     |

| F          | 1       |      |          |     | 76D3    | 76  | D    | 3     |

| ++-        | +       |      |          |     | 05A9    | 05  | Α    | 9     |

Figure 2.2. A 256B direct mapped cache with 16 lines of 16B each. The line portion of a memory address points to a single line in the cache. Only said line can match the tag portion of the memory address.

the same line portion of the address: they both map to the same cache line and compete for the same cache space. The remaining cache lines go unused. When memory accesses occur at these addresses, the cache controller **evicts** the current data: it replaces the data in the cache line with the new data loaded as a result of a cache miss. These evictions as a result of repeatedly accessing different memory locations is called cache thrashing: the data ends up being continually swapped out and the cache becomes a burden instead of an asset.

Fully associative cache. The disadvantages of a direct mapped cache are unfortunately fundamental; each memory block can only reside in one cache line. To remedy this, one might consider an extreme solution and instead allow each memory block to reside in *any* cache line; Fig. 2.3 illustrates a fully associative cache. The cache logic works as follows. The cache controller compares the corresponding tag of *each* cache line to the tag of the memory address. If there is a match, a cache hit occurs; otherwise, a cache miss. Advantages of a fully associative cache include better cache utilization and minimal cache thrashing. The main disadvantage is implementation complexity. Instead of

|   |                                       |                        |    |     |   |   |   |   | address | tag | offset |

|---|---------------------------------------|------------------------|----|-----|---|---|---|---|---------|-----|--------|

|   | +++                                   |                        |    |     |   |   |   |   |         |     |        |

| 0 | $  \mathtt{NN}   \mathtt{YYYY}    <+$ |                        |    |     |   |   |   |   | D831    | D83 | 1      |

|   | +++                                   | NN                     | == | D83 | ? | Н | : |   | 35A6    | 35A | 6      |

| 1 | ZZ    <+                              |                        |    |     |   |   |   |   | 937F    | 937 | F      |

|   | +++                                   | ZZ                     | == | D83 | ? | Н | : |   | 0384    | 038 | 4      |

| 2 | LL    <+                              |                        |    |     |   |   |   |   | 2B93    | 2B9 | 3      |

|   | +++                                   | LL                     | == | D83 | ? | Н | : |   | FA63    | FA6 | 3      |

| 3 | MM     <+                             |                        |    |     |   |   |   |   | 4B91    | 4B9 | 1      |

|   | +++                                   | $\mathtt{M}\mathtt{M}$ | == | D83 | ? | Н | : |   | 0F9C    | 0F9 | C      |

| 4 | TT    <+                              |                        |    |     |   |   |   |   | CD44    | CD4 | 4      |

|   | +++                                   | TT                     | == | D83 | ? | Н | : |   | D49F    | D49 | F      |

| 5 | YY    <+                              |                        |    |     |   |   |   |   | 14BA    | 14B | A      |

|   | +++                                   | YY                     | == | D83 | ? | Н | : |   | E4F1    | E4F | 1      |

| 6 | HH     <+                             |                        |    |     |   |   |   |   | B319    | B31 | 9      |

|   | +++                                   | НН                     | == | D83 | ? | Н | : |   | 14F3    | 14F | 3      |

| 7 | KK    <+                              |                        |    |     |   |   |   |   | 3E09    | 3E0 | 9      |

|   | +++                                   | KK                     | == | D83 | ? | Н | : |   | 13DA    | 13D | A      |

| 8 | WW     <+                             |                        |    |     |   |   |   |   | 0C6E    | 0C6 | E      |

|   | +++                                   | WW                     | == | D83 | ? | Н | : |   | 6BBC    | 6BB | C      |

| 9 | II    <+                              |                        |    |     |   |   |   |   | 44A2    | 44A | 2      |

|   | +++                                   | II                     | == | D83 | ? | Н | : |   | 26D4    | 26D | 4      |

| A | GG    <+                              |                        |    |     |   |   |   |   | 04A3    | 04A | 3      |

|   | +++                                   | GG                     | == | D83 | ? | Н | : |   | 5F59    | 5F5 | 9      |

| В | RR    <+                              |                        |    |     |   |   |   |   | 9FB3    | 9FB | 3      |

|   | +++                                   | RR                     | == | D83 | ? | Н | : |   | 65DE    | 65D | E      |

| C | UU    <+                              |                        |    |     |   |   |   |   | D65B    | D65 | В      |

|   | +++                                   | UU                     | == | D83 | ? | Н | : |   | 6D6F    | 6D6 | F      |

| D | SS    <+                              |                        |    |     |   |   |   |   | 8FAC    | 8FA | C      |

|   | +++                                   | SS                     | == | D83 | ? | Н | : |   | 90DC    | 90D | C      |

| E | XX    <+                              |                        |    |     |   |   |   |   | C8E0    | C8E | 0      |

|   | +++                                   | XX                     | == | D83 | ? | Н | : |   | 7A4B    | 7A4 | В      |

| F | 33    <+                              |                        |    |     |   |   |   |   | 76D3    | 76D | 3      |

|   | +++                                   | ננ                     | == | D83 | ? | Н | : | M | 05A9    | 05A | 9      |

|   |                                       |                        |    |     |   |   |   |   |         |     |        |

Figure 2.3. A 256B fully associative cache with 16 lines of 16B each. Any single line in the cache can match the tag portion of the memory address.

needing to check only one cache line, the cache controller must check all cache lines; this fundamental difference is noticeable in the input to the compare logic in Fig. 2.3. Furthermore, the cache controller must also implement some kind of intelligent policy for evicting data from the cache. Such policies are covered later.

Set associative cache. The logical compromise between the previous two approaches is to allow each memory block to reside in one of *many* cache lines; Fig. 2.3 illustrates a **set associative cache**. The cache logic works as follows. The **set** portion of the address identifies the subset of cache lines in which the memory block can reside; the cache controller compares the corresponding tag of each cache line in the subset to the tag of the memory address. If they match, a cache hit occurs; otherwise, a cache miss. A set associative cache enjoys the benefits of both previous types. It is a trade-off between performance and complexity. Compared to a fully associative cache, the cache controller can more easily identify if a memory location resides in the cache, and the needed policy is easier to implement. This is by far the most widely implemented cache architecture for modern microprocessors.

|   |         |     |        |      |    |   | address |     |   |   |

|---|---------|-----|--------|------|----|---|---------|-----|---|---|

|   | +++<br> |     |        |      |    |   | D831    |     |   |   |

|   | +++     |     |        |      |    |   | 35A6    |     |   |   |

|   | 1 1 1   |     |        |      |    |   | 937F    |     |   |   |

|   | +++     |     |        |      |    |   |         | 038 |   |   |

|   | 1 1 1   |     |        |      |    |   |         | 2B8 |   |   |

|   | +++     |     |        |      |    |   | FA63    |     |   |   |

|   | MM YYYY |     |        |      |    |   | 4B91    |     |   |   |

|   | +++     |     | M D    | 80 2 | н. |   | 0F9C    |     |   |   |

|   | 1 1 1   |     | D      |      |    |   |         | CD4 |   |   |

|   | +++     |     |        |      |    |   | D49F    |     |   |   |

|   | i i i   |     |        |      |    |   | 14BA    |     |   |   |

|   | +++     |     |        |      |    |   | E4F1    |     |   |   |

|   | i i i   |     |        |      |    |   | B319    |     |   |   |

|   | +++     |     |        |      |    |   | 14F3    |     |   |   |

|   | KK      |     |        |      |    |   |         | 3E0 |   | 9 |

| • | +++     |     | K == D | 80 7 | н. |   | 13DA    |     |   |   |

| 8 | 1 1 1   |     | D      |      |    |   | OC6E    |     |   |   |

|   | +++     |     |        |      |    |   | 6BBC    |     |   |   |

|   | 1 1 1   |     |        |      |    |   | 44A2    |     |   |   |

|   | +++     |     |        |      |    |   |         | 26C |   |   |

|   | 1 1 1   |     |        |      |    |   |         | 048 |   |   |

|   | +++     |     |        |      |    |   | 5F59    |     |   |   |

| В | RR      | <+  |        |      |    |   | 9FB3    | 9F8 | 3 | 3 |

|   | +++     | F   | R == D | 80 ? | н: |   | 65DE    | 65C | 1 | E |

| С | 1 1 1   | i   |        |      |    |   | D65B    | D64 | 1 | В |

|   | +++     | i   |        |      |    |   | 6D6F    | 6D4 | 2 | F |

| D | 1 1 1   | i   |        |      |    |   | 8FAC    | 8F8 | 2 | С |

|   | +++     | i   |        |      |    |   | 90DC    | 90C | 1 | С |

| E | 1 1 1   | i   |        |      |    |   | C8E0    | C8C | 2 | 0 |

|   | +++     | - 1 |        |      |    |   | 7A4B    | 7A4 | 0 | В |

| F | 33      | <+  |        |      |    |   |         | 76C | 1 | 3 |

|   | +++     | 3   | J == D | 80 ? | н: | M | 05A9    | 058 | 2 | 9 |

|   |         |     |        |      |    |   |         |     |   |   |

**Figure 2.4.** A 256B set associative cache with 16 lines of 16B each and 4 ways. The set portion of a memory address points to four distinct lines in the cache. Only one of these four lines can match the tag portion of the memory address.

Cache replacement policies. When data at a memory location can reside in more than one place in the cache, a policy must exist for evicting existing data in the event of a cache miss. What data should be evicted from possible cache locations to make room for the new data? Said logic defines the cache replacement policy. The most common cache replacement policy is Least Recently Used (LRU). The cache controller can implement this by maintaining age fields for the cache lines; the cache line with the oldest field, or least recently used, gets evicted. A microcontroller used for a common desktop workstation generally benefits from such a policy. If data is used, it is likely to be used again in the near future. For large data sets or random access patterns, LRU poses a problem; an item from the set is not likely to be needed in the near future once accessed. The exact opposite idea of a Most Recently Used (MRU) policy would be more appropriate, where the cache controller instead evicts the line with the youngest field. A microcontroller used for such a special purpose would benefit from this. Instead of an age, a valuable metric might be the number of times a memory block is accessed; a Least Frequently Used (LFU) policy discards data that is used least often. Last but not least, a random policy evicts a random line from the cache to make room for incoming data. A big advantage of such a policy is ease of implementation: it involves very little logic and does not hinge on any assumptions about the memory access habits of a typical program.

#### 3. Covert Channels

The topic of covert channels usually falls under the umbrella of system security. Academic interest in this specific area dates back to at least the 1970s. Roughly speaking, covert channels provide a method to transmit information in an unconventional way in a system where such communication is not explicitly allowed. These channels can be either **intentional** and used between consenting parties to communicate unregulated by the system, or **unintentional** and used by a malicious party to monitor the activities of a legitimate party. In this context, a party can be a user, program, or process. This chapter contains a selective literature review of results pertaining to covert channels, focusing mostly on covert timing channels, beginning from the initial works and proceeding chronologically. These concepts build the foundation for sidechannel attacks (i.e., attacks that exploit unintentional covert channels) and, in particular, cache-timing attacks.

The confinement problem. In his seminal work, Lampson defines the confinement problem [Lam73].

This note explores the problem of confining a program during its execution so that it cannot transmit information to any other program except its caller.

He gives a number of examples of how a program might leak data, among them the following that he attributes to A. G. Fraser at Bell Laboratories.

By varying its ratio of computing to input/output or its paging rate, the service can transmit information which a concurrently running process can receive by observing the performance of the system. The communication channel thus established is a noisy one, but the techniques of information theory can be used to devise an encoding which will allow the information to get through reliably no matter how small the effects the service on system performance are, provided they are not zero. The data

rate of this channel may be very low, of course.

This is an important example for a number of reasons, but mostly because it captures the essence of covert and side-channels succinctly: the observation that the ratio or rate at which a program performs a given task can provide information. Classifying the channels for numerous examples of program leakage, he goes on to give an informal definition of a **covert channel**.

Covert channels [are] those not intended for information transfer at all.

Analyzing the confinement problem. Taking a more policy-based approach and applying existing principles of computer security, Lipner further examines the confinement problem [Lip75]. The discussion on closing covert timing channels suggest that the system assign a virtual time or virtual clock to each process that depends solely on its own activity and not any outside process. Continuing from the example of Lampson [Lam73], Lipner gives an example of paging, i.e., the touching of each page must take a constant amount of time. The work observes that the problem of limiting the observed time of a process to the virtual one is indeed difficult: the program can choose to perceive the passage of time however it wishes, independent of the virtual clock provided by the system. The goals and implementation of a dynamic time-based scheduler are counteractive to those of eliminating the ability of a process to correlate between virtual and real time. The compromise results in (at best) reduced timing granularity: introducing more noise into the covert channel and reducing the throughput.

Covert storage and timing channels. In 1972, IBM released an operating system for their mainframes called VM/370. While retrofitting a security architecture to this operating system called KVM/370, Schaefer et al. explore the confinement problem [SGLS77]. They give their own informal definition of a covert channel.

Covert channels are [data] paths not meant for communication but that can be used to transmit data indirectly.

They further distinguish between two types of covert channels: **storage channels** and **timing channels**. This dissertation concerns mainly the latter.

Storage channels consist of variables that are set by a system process on behalf of the sender, e.g., interlocks, thresholds, or an ordering. In timing channels, the time variable is controlled: resource allocations are made to a receiver at intervals of time controlled by the sender. In both cases, the state of the variable ("on" or "off", "time-interval is 2 seconds") is made to represent information, e.g., digits or characters.

They go on to give numerous examples of practical covert channels they encountered including CPU scheduling, I/O scheduling, and timing of I/O operations. One of the most interesting examples they give is disk arm movement that exploits the disk scheduling algorithm. This is now one of the classical examples of a storage channel. An elevator disk scheduling algorithm behaves similarly to a normal elevator, moving the arm in one direction until no further requests are pending in that direction, then starts moving in the opposite direction. They explain how a covert channel exists essentially because the order in which cylinder requests are filled depends on the current direction of the arm.

Let R own a minidisk at cylinders 51 through 59 of some real disk, to which S has read access. R issues a request for cylinder 55, loops until notified of its completion, then relinquishes the CPU. S then issues a request for either cylinder 53 (to send a 0) or 57 (for a 1) and relinquishes the CPU. R then issues requests for both cylinder 58 and 52. If the request for cylinder 58 completes first, a 1 is received because S left the arm at cylinder 57 and the algorithm continues the upward motion; a 0 is similarly received if the request for cylinder 52 completes first.

They remain pessimistic about the feasibility of eliminating all said channels and settle on mitigations that minimize the bandwidth and increase the noise of the covert channels.

**Identifying covert channels.** In contrast to previous work that identifies covert storage and timing channels in an ad hoc fashion, Kemmerer presents a more rigorous methodology [Kem83]. He gives his own definition of a covert channel, noting that it differs from that of Lampson [Lam73] due to the distinction between storage and timing channels.

Covert channels use entities not normally viewed as data objects to transfer information from one subject to another. These nondata objects, such as file locks, device busy flags, and the passing of time, are needed to register the state of the system.

The methodology first identifies all shared resources of the system. This includes not only the resource itself, but possibly numerous attributes of the resource. For example, a file can be a shared resource but attributes like a lock flag or file size are distinct attributes. It then identifies various primitives available on the system, for example read file or write file. One can then examine every possible pair and determine what the potential throughput of the channel is, if one exists. This allows incremental evaluation as new resources and primitives are added to the system. Kemmerer lists quite concrete requirements for the existence of storage and timing channels, the latter of which follows.

The minimum criteria necessary in order for a timing channel to exist are as follows:

- The sending and receiving processes must have access to the same attribute of a shared resource.

- The sending and receiving processes must have access to a time reference such as a real-time clock.

- 3. The sender must be capable of modulating the receiver's response time for detecting a change in the shared attribute.

- There must be some mechanism for initiating the processes and for sequencing the events.

The work reinforces the idea that it is infeasible to eliminate all covert channels and efforts should concentrate on identifying such channels and minimizing their throughput.

The Orange Book. The Rainbow Series is a collection of security-related guide-lines issued jointly by the United States Department of Defense (DoD) and the National Computer Security Center (NCSC), part of the National Security Agency (NSA). Appearing in 1983, the first publication in the series is the DoD "Trusted Computer System Evaluation Criteria" (TCSEC) fondly referred to as the Orange Book. Its purpose is to more rigorously define security aspects of computer systems and allow for a concrete evaluation with respect to the defined criteria. It contains a chapter dedicated to covert channels and offers the following definition [dod85, Sec. 8].

A covert channel is any communication channel that can be exploited by a process to transfer information in a manner that violates the system's security policy.

It also differentiates between covert storage and timing channels, offering the rather insightful definition of the latter.

Covert timing channels include all vehicles that would allow one process to signal information to another process by modulating its own use of system resources in such a way that the change in response time observed by the second process would provide information.

Although now dated, the Orange Book heavily influences its modern successor, the ISO Common Criteria. The inclusion of covert channels in the Orange Book is significant because it formally recognizes covert channels as a security threat in a documented standard. The guidelines suggest identifying covert channels and their associated throughput.

A practical covert timing channel. Multiplexed Information and Computing Service (Multics) is an operating system that began development in 1964 and originally was a joint effort between MIT, General Electric, and Bell Laboratories. In a concrete realization (on Multics) of the covert timing channel using paging described by Lampson [Lam73], Van Vleck gives an account of what is now one of the most classical examples of practical covert timing channels [Vle90].

My friend, Bob Mullen, astounded me a few days later by showing me two processes in the terminal room. You could type into one and the other would type out the same phrase a few seconds later. The processes were communicating at teletype speed by causing page faults and observing how long they took. The sender process read or didn't read certain pages of a public library file. The receiver process read the pages and determined whether they were already in core by seeing if the read took a long or short real time.

Considering mitigation of general covert timing channels, similar to the permission attribute that controls the reading and writing of files, Van Vleck suggests a certification attribute that controls the execution of a program. Furthermore, similar to review process of operating system kernels, software should be examined manually for covert channels to classify their certification level.

Operating system design and covert channels. Ideally, security should be considered a first class citizen when designing an operating system, and not an afterthought through retrofitting. Digital Equipment Corporation (DEC) adopted this principle beginning in 1981 when designing a VMM security kernel for their VAX architecture, described by Karger et al. [KZB+90]. Somewhat different from a modern operating system, the task of the VAX Virtual Machine Monitor (VMM) is to manage virtual machines at different security levels. One of its design goals is to identify covert channels from the onset and apply appropriate countermeasures.

Disk scheduling algorithms and covert channels. In the early 1990s, a team of researchers at DEC dedicated to the analysis of covert channels within the VAX security kernel released a flurry of results to the academic community. Inspired by the disk arm covert channel described by Schaefer et al. [SGLS77], Karger and Wray analyze said channel with respect to VAX [KW91]. Building on the existing result of the elevator disk scheduling algorithm covert channel, the work examines a number of different disk scheduling algorithms for potential covert channels. They show that the straightforward countermeasure of repositioning the arm after every request is, in general, too costly. One reason the work is significant is because it demonstrates that covert channels are not solely problems to consider at the operating system level. The specific related hardware they work with implements an efficient disk scheduling algorithm on the controller itself that provides a covert channel, yet the operating system has no authority over the controller's policy. Ironically, in deploying covert channel countermeasures the operating system must spend disproportional time in nullifying the optimizations implemented at the lower hardware level.

Mitigating covert channels with fuzzy time. The drawback of Lipner's idea to use virtual time to eliminate covert timing channels is that each process still has some concept of real time, independent of whatever virtual time the operating system presents to it [Lip75]. Furthermore, exposing only a virtual time to programs inherently imposes formidable restrictions on them: the functionality of those relying on being able to accurately measure the passage of time comes into question. Focusing on the VAX security kernel, Hu proposes fuzzy time to address these concerns and mitigate covert timing channels introduced by either the operating system or attached hardware [Hu91]. To address operating system clocks, fuzzy time randomizes the length of the operating system tick interval and reduces the granularity of the system-wide time register. To address I/O clocks, fuzzy time randomizes the response time of requests, i.e., the time at which notification of the completion of an event occurs. Hu

states that the implementation of fuzzy time within the VAX security kernel proved to be an extremely effective mechanism to mitigate covert timing channels, overwhelmingly inhibiting their usability measured by increase of noise and reduced throughput.

Data caching and covert channels. The line between a covert storage channel and a covert timing channel is not always clear, as demonstrated by Wray [Wra91]. Using the disk arm storage channel example of Schaefer et al. [SGLS77] previously discussed, Wray explains that if, in the final step, S issues only a single request and measures the time required for the request to complete, S can infer the exact same bit value by relatively comparing the obtained timings. Although this is the same physical channel, with respect to classification it changes from a storage to a timing channel. As such, Wray questions the common distinction between storage and timing channels since such a classification can be misleading, for example when auditing covert channels using a classification-based methodology. For the purposes of this dissertation, one of the most interesting examples Wray gives of a covert channel is as follows.

Consider a uniprocessor with a direct-mapped cache, running two processes containing covert channel exploitation programs. One, at low secrecy, reads sufficient memory locations to fill the cache with low secrecy data, and then relinquishes the CPU. The other process, running at a high secrecy level, read certain memory locations, causing some cache slots to be re-filled with high secrecy data, and then relinquishes the CPU. Finally, the first process re-reads the data it read earlier, but measuring the time of each read attempt against a reference clock. Those memory locations which correspond to cache locations that were filled with high secrecy data will take significantly longer to read than the locations that still contain low secrecy data, as the displaced low-secrecy data must be re-fetched from main memory. This exploitation allows the timing of individual instructions to be modulated with precision.

This lovely example demonstrates how microprocessors equipped with caching mechanisms run the risk of introducing a covert timing channel through the use of a cache as a shared resource. Furthermore, it is another good example of a covert channel introduced by the underlying hardware instead of the operating system. An extended version of the work appears later in a journal [Wra92].

**Data caching and further covert channels.** As Wray's example of the cache channel illustrates [Wra91], hardware timing channels potentially pose a much greater risk to security than software channels. This is in part due to their com-

paratively higher throughput. Hu reiterates this point and uses the cache channel as a case study, providing the following example of its exploitation [Hu92].

The cache channel can be exploited as follows. Assume that there are only 2 user processes in the system: a Trojan horse process at a high access class and a Spy process at a lower access class. The Spy process initially loads the cache with known values by making a series of memory references. It then releases the CPU. Since the Trojan horse process is the only other process, the scheduler runs the Trojan horse process next. To send a "1", the Trojan horse process would overwrite all the contents of the cache. To send a "0", the Trojan horse process would immediately give up the CPU so as to minimize its effect on cache contents. When the Spy process regains the CPU, it reads the same memory locations it previously accessed and measures the read latency. The read latency is just the amount of time it takes to read the memory location. If the references take a relatively short time to complete, then the Spy process knows that the references were satisfied from the cache. Thus, the original cache contents were undisturbed, and the Trojan horse transmitted a "0". Otherwise, the Trojan horse transmitted a "1".

Flushing the cache during context switching is a straightforward mechanism to mitigate the cache channel. This usually has a detrimental effect on performance and hence can only be applied in rare cases. One logical trade-off is to flush the cache only when necessary, i.e., when lower secrecy data can potentially evict higher secrecy data from the cache. This poses an interesting research challenge: scheduling processes in a manner which minimizes the invocation of costly timing channel mitigations, such as cache flushing in the case of the cache channel. Hu proposes such a novel scheduler called a lattice scheduler.

Architectural approaches to covert channel mitigation. Multilevel security seeks to manage data with different sensitivity levels and users with different clearances within a single system. There are different ways to realize this, but any shared resource between security levels is a potential covert channel and/or violation of the security policy. For example, a data cache in a multilevel processor can yield a covert channel. A disk scheduling algorithm in a multilevel disk drive can yield a covert channel. A job scheduling algorithm in a multilevel operating system can yield a covert channel. Lamenting the current state of covert channel mitigation and research trends aimed at multilevel processors, Proctor and Neumann argue that the problem of covert channels in multilevel

security systems is insurmountable and suggest solutions at the architecture level [PN92]. For example, instead of attempting to identify and mitigate all possible covert channels in a multilevel processor (this is arguably not even feasible, let alone practical), assign a single-level processor to each level. They argue that the trend of decreasing hardware costs makes this approach viable. Indeed, decades later a modern common desktop system is equipped with multiple CPUs and/or multiple computing cores, and even possibly one or more graphics processing units (GPUs) with hundreds of computing cores. In contrast to covert channel security in multilevel processors, they suggest research should focus on multilevel disk drives and networks, where covert channel security can be more adequately addressed and, in the end, provide more concrete guarantees.

The Light Pink Book. Achieving the higher TCSEC security ratings detailed in the Orange Book requires an analysis of covert channels and, in the case of high bandwidth, assurance that the channel has been closed or sufficiently throttled using documented countermeasures. Another entry in the Rainbow Series, the Light Pink Book "A Guide to Understanding Covert Channel Analysis of Trusted Systems" aims to help developers meet these criteria, in part by identifying and classifying covert channels [ncs93]. The document contains a number of interesting, practical examples of both storage and timing channels, including those introduced by CPU scheduling, shared hardware resources, resource exhaustion, I/O scheduling, I/O operation completion, and memory management. The guidelines recommend various tools for identifying storage channels, but emphasize that the tools do not address timing channels.

## 4. Cache-Timing Attacks

cache: a secure place of storage.

B. B. Brumley

A **side-channel** or **side-band** is an unintentional covert channel: one party is knowingly communicating via the channel yet the other is unaware. This chapter makes the transition from covert channels as a security topic to side-channels as a cryptology topic, using them for cryptanalytic purposes. The topic of side-channels is a history-rich one, dating back at least to World War II. Koblitz and Menezes give a concise review of its origins [KM11, Sec. 4.1]. Academic interest in this specific area dates back to at least the 1990s.

In contrast to traditional cryptanalytic techniques such as differential and linear cryptanalysis that target the formal mathematical description of a cryptographic primitive, **physical attacks** or **implementation attacks** target a concrete implementation of said primitive. A non-exhaustive list of physical attack techniques includes power analysis, timing analysis, electromagnetic radiation analysis, acoustic analysis, fault injection, power glitching, physical tampering, bus probing, cold boots [CPGR05], and bug attacks [BCS08]: consult Popp's work for a survey [Pop09]. Standaert offers the following classification of physical attacks [Ver10, p. 27].

- 1. Invasive vs. non-invasive: Invasive attacks require depackaging the chip to get direct access to its inside components; a typical example of this is the connection of a wire on a data bus to see the data transfers. A non-invasive attack only exploits externally available information (the emission of which is, however, often unintentional) such as running time, power consumption.

- 2. Active vs. passive: Active attacks try to tamper with the devices' proper functioning, for example, fault-induction attacks will try to induce errors in the computation. As opposed, passive attacks will simply observe the devices behavior during

their processing, without disturbing it.

As the above definitions connotate, hardware devices (e.g., smart cards and cryptographic tokens) are ordinarily the main target of physical attacks. **Side-channel attacks** are a class of physical attacks that often fall into the non-invasive, passive category: they utilize a side-channel exposed through, for example, power consumption or timing measurements.

The above physical attacks classification is more rigorous for hardware-based side-channel attacks, while most of the side-channels considered in this dissertation are software-based. On the software side, a subset of the attacks will require execution of a malicious program or **spy process** that runs in unprivileged user space [GGP07, Sec. 2]. Precisely how to place said attacks in the above context of physical attacks is debatable. The following examples support this statement.

- 1. The victim is a system. The spy process must execute within this system.

The attack is therefore invasive.

- The victim is a legitimate process within a system. The spy process executes in unprivileged user space, independent of the legitimate process. The attack is therefore non-invasive.

- 3. The spy process influences the execution of the legitimate process indirectly by manipulating the system state. The attack is therefore active.

- 4. It is normal, not disturbing, for a multitasking operating system to handle multiple processes (including the spy process) pseudo-concurrently. The attack is therefore passive.

Irrespective of how these attacks requiring execution of a spy process are classified as physical attacks, the threat model is clear. The typical attack scenario is a spy process running concurrently on the same physical CPU as the victim process (usually the execution of a cryptographic primitive). This dictates that the attacker must gain authorization to execute the spy process locally. This would be trivial, for example, if the attacker has valid login credentials to a victim Secure Shell (SSH) server. This would be impossible, for example, if the attacker cannot install and execute the spy process on the target system.

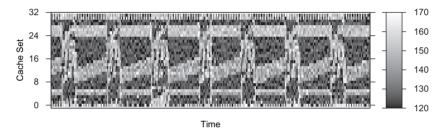

A timing attack is a side-channel attack that recovers key material by ex-