TKK Dissertations 237 Espoo 2010

# INTEGRATED REFERENCE CIRCUITS FOR LOW-POWER CAPACITIVE SENSOR INTERFACES

**Doctoral Dissertation**

Matti Paavola

Aalto University School of Science and Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences

### INTEGRATED REFERENCE CIRCUITS FOR LOW-POWER CAPACITIVE SENSOR INTERFACES

**Doctoral Dissertation**

#### Matti Paavola

Doctoral dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Faculty of Electronics, Communications and Automation for public examination and debate in Auditorium S4 at the Aalto University School of Science and Technology (Espoo, Finland) on the 1st of October 2010 at 12 noon.

Aalto University School of Science and Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences

Aalto-yliopisto Teknillinen korkeakoulu Elektroniikan, tietoliikenteen ja automaation tiedekunta Mikro- ja nanotekniikan laitos Distribution:

Aalto University

School of Science and Technology

Faculty of Electronics, Communications and Automation

Department of Micro and Nanosciences

P.O. Box 13000 (Otakaari 5 A)

FI - 00076 Aalto

**FINLAND**

URL: http://nano.tkk.fi/ Tel. +358-9-470 22271 Fax +358-9-470 22269

E-mail: matti.paavola@gmail.com

#### © 2010 Matti Paavola

ISBN 978-952-60-3318-1 ISBN 978-952-60-3319-8 (PDF) ISSN 1795-2239 ISSN 1795-4584 (PDF)

URL: http://lib.tkk.fi/Diss/2010/isbn9789526033198/

TKK-DISS-2797

Multiprint Oy Espoo 2010

| ABSTRACT OF DOCTORAL DISSERTATION |                                                                                                   | AALTO UNIVERSITY<br>SCHOOL OF SCIENCE AND TECHNOLOGY<br>P.O. BOX 11000, FI-00076 AALTO<br>http://www.aalto.fi |  |  |  |

|-----------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|

| Author Matti F                    | Paavola                                                                                           |                                                                                                               |  |  |  |

|                                   | Name of the dissertation Integrated Reference Circuits for Low-Power Capacitive Sensor Interfaces |                                                                                                               |  |  |  |

| Manuscript submitt                | Manuscript submitted May 24, 2010 Manuscript revised August 24, 2010                              |                                                                                                               |  |  |  |

| Date of the defence               | Date of the defence October 1, 2010                                                               |                                                                                                               |  |  |  |

| Monograph                         |                                                                                                   | X Article dissertation (summary + original articles)                                                          |  |  |  |

| Faculty                           | Faculty of Electronics, Communication                                                             | ations and Automation                                                                                         |  |  |  |

| Department                        | Department of Micro and Nanosci                                                                   | ences                                                                                                         |  |  |  |

| Field of research                 | Electronic Circuit Design                                                                         |                                                                                                               |  |  |  |

| Opponent(s)                       | Professor Trond Ytterdal                                                                          |                                                                                                               |  |  |  |

| Supervisor                        | Professor Kari Halonen                                                                            |                                                                                                               |  |  |  |

| Instructor                        |                                                                                                   |                                                                                                               |  |  |  |

| A1 ( (                            |                                                                                                   |                                                                                                               |  |  |  |

#### **Abstract**

This thesis consists of nine publications and an overview of the research topic, which also summarizes the work. The research described in this thesis concentrates on the design of low-power sensor interfaces for capacitive 3-axis micro-accelerometers. The primary goal throughout the thesis is to optimize power dissipation. Because the author made the main contribution to the design of the reference and power management circuits required, the overview part is dominated by the following research topics: current, voltage, and temperature references, frequency references, and voltage regulators.

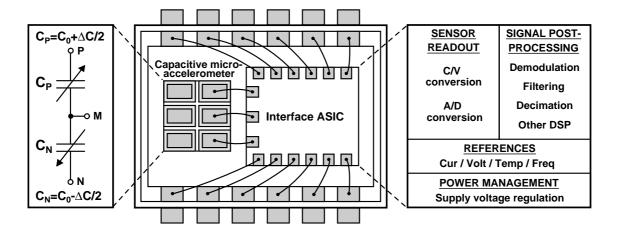

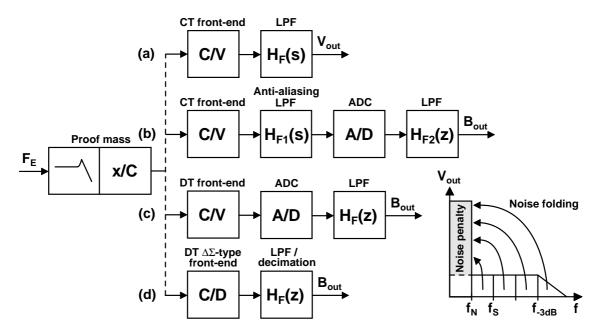

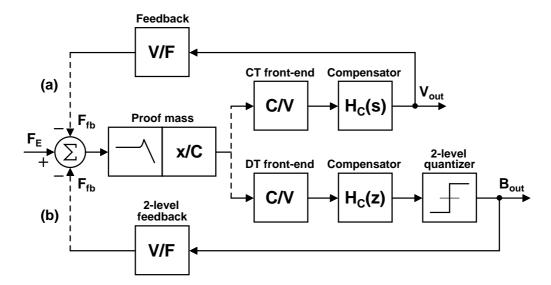

After an introduction to capacitive micro-accelerometers, the work describes the typical integrated readout electronics of a capacitive sensor on the functional level. The readout electronics can be divided into four different functional parts, namely the sensor readout itself, signal post-processing, references, and power management. Before the focus is shifted to the references and further to power management, different ways to realize the sensor readout are briefly discussed.

Both current and voltage references are required in most analog and mixed-signal systems. A bandgap voltage reference, which inherently uses at least one current reference, is practical for the generation of an accurate reference voltage. Very similar circuit techniques can be exploited when implementing a temperature reference, the need for which in the sensor readout may be justified by the temperature compensation, for example.

The work introduces non-linear frequency references, namely ring and relaxation oscillators, which are very suitable for the generation of the relatively low-frequency clock signals typically needed in the sensor interfaces. Such oscillators suffer from poor jitter and phase noise performance, the quantities of which also deserve discussion in this thesis.

Finally, the regulation of the supply voltage using linear regulators is considered. In addition to extending the battery life by providing a low quiescent current, the regulator must be able to supply very low load currents and operate without off-chip capacitors.

| Keywords capacitive accelerometer, CMOS, power                                                              | management circuit, reference circuit, sensor interface |  |  |  |

|-------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| ISBN (printed) 978-952-60-3318-1                                                                            | ISSN (printed) 1795-2239                                |  |  |  |

| ISBN (pdf) 978-952-60-3319-8                                                                                | ISSN (pdf) 1795-4584                                    |  |  |  |

| Language English                                                                                            | Number of pages 134 p. + app. 91 p.                     |  |  |  |

| Publisher Aalto University, School of Science and Technology, Department of Micro and Nanosciences          |                                                         |  |  |  |

| Print distribution Aalto University, School of Science and Technology, Department of Micro and Nanosciences |                                                         |  |  |  |

| X The dissertation can be read at http://lib.tkk.fi/Diss/2010/isbn9789526033198/                            |                                                         |  |  |  |

| VÄITÖSKIRJAN TIIVISTELMÄ                 |                                                                                        | AALTO-YLIOPISTO<br>TEKNILLINEN KORKEAKOULU<br>PL 11000, 00076 AALTO<br>http://www.aalto.fi |                    |

|------------------------------------------|----------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--------------------|

| Tekijä Matti F                           | Paavola                                                                                |                                                                                            |                    |

| Väitöskirjan nimi<br>Integroidut referer | nssipiirit matalan tehonkulutuksen ka                                                  | apasitiivisille anturirajapinnoille                                                        |                    |

| Käsikirjoituksen p                       | Käsikirjoituksen päivämäärä 24.05.2010 Korjatun käsikirjoituksen päivämäärä 24.08.2010 |                                                                                            |                    |

| Väitöstilaisuuden                        | ajankohta 01.10.2010                                                                   |                                                                                            |                    |

| ☐ Monografia                             |                                                                                        | X Yhdistelmäväitöskirja (yhteenveto +                                                      | erillisartikkelit) |

| Tiedekunta                               | Elektroniikan, tietoliikenteen ja au                                                   | itomaation tiedekunta                                                                      |                    |

| Laitos                                   | Mikro- ja nanotekniikan laitos                                                         |                                                                                            |                    |

| Tutkimusala                              | Piiritekniikka                                                                         |                                                                                            |                    |

| Vastaväittäjä(t)                         | Professori Trond Ytterdal                                                              |                                                                                            |                    |

| Työn valvoja                             | Professori Kari Halonen                                                                |                                                                                            |                    |

| Työn ohjaaja                             |                                                                                        |                                                                                            |                    |

|                                          | ·                                                                                      | ·                                                                                          |                    |

#### Tiivistelmä

Tämä väitöskirja koostuu yhdeksästä julkaisusta sekä tutkimusaiheen yhteenvedosta. Väitöskirjassa esitetty tutkimus keskittyy matalan tehonkulutuksen anturirajapintojen suunnitteluun kapasitiivisille kolmiakselisille mikromekaanisille kiihtyvyysantureille. Tutkimuksen keskeinen tavoite on tehonkulutuksen optimointi. Koska kirjoittajan pääasiallinen panos keskittyi tarvittavien referenssi- ja tehonhallintapiirien suunnitteluun, yhteenveto-osuutta hallitsee seuraavat tutkimusaiheet: virta-, jännite- ja lämpötilareferenssit, taajuusreferenssit, sekä jänniteregulaattorit.

Kapasitiivisten mikromekaanisten kiihtyvyysanturien johdannon jälkeen työ esittää tyypillisen integroidun kapasitiivisen anturin lukuelektroniikan toiminnallisella tasolla. Anturin lukuelektroniikka voidaan jakaa neljään toiminnalliseen osaan, jotka ovat itse anturin lukeminen, signaalin jälkikäsittely, referenssit, ja tehon hallinta. Ennen referenssi- ja tehonhallintapiireihin siirtymistä käsitellään lyhyesti erilaisia anturin luvun toteutustapoja.

Sekä virta- että jännitereferenssejä tarvitaan useimmissa analogia- ja analogia-digitaalijärjestelmissä. Bandgap-jännitereferenssi, joka itsessään sisältää ainakin yhden virtareferenssin, on käytännöllinen tarkan referenssijännitteen tuottamisessa. Hyvin samanlaisia piiritekniikoita voidaan hyödyntää toteutettaessa lämpötilareferenssi, jonka tarve anturin lukuelektroniikassa voi liittyä esimerkiksi lämpötilakompensointiin.

Työ esittelee epälineaarisia taajuusreferenssejä, eli rengas- ja relaksaatio-oskillaattoreita, jotka sopivat hyvin suhteellisen matalataajuisten kellosignaalien muodostamiseen, joita anturin lukuelektroniikassa tyypillisesti tarvitaan. Kyseiset oskillaattorit kärsivät heikosta jitteri- ja vaihekohinasuorituskyvystä. Näitä suorituskykyparametreja tullaan myös käsittelemään tässä väitöskirjassa.

Lopuksi tarkastellaan käyttöjännitesäätelyä lineaaristen regulaattorien avulla. Sen lisäksi, että patterin kestoa pidennetään pienellä lepotilan virralla, regulaattorin täytyy pystyä syöttämään hyvin pieniä kuormavirtoja sekä toimimaan ilman ulkoisia kondensaattoreita.

| Asiasanat anturirajapinta, CMOS, kapasitiivinen kiihtyvyysanturi, referenssipiiri, tehonhallintapiiri |                           |  |  |

|-------------------------------------------------------------------------------------------------------|---------------------------|--|--|

| ISBN (painettu) 978-952-60-3318-1                                                                     | ISSN (painettu) 1795-2239 |  |  |

| ISBN (pdf) 978-952-60-3319-8                                                                          | ISSN (pdf) 1795-4584      |  |  |

| Kieli Englanti Sivumäärä 134 s. + liit. 91 s.                                                         |                           |  |  |

| Julkaisija Aalto-yliopisto, Teknillinen korkeakoulu, Mikro- ja nanotekniikan laitos                   |                           |  |  |

| Painetun väitöskirjan jakelu Aalto-yliopisto, Teknillinen korkeakoulu, Mikro- ja nanotekniikan laitos |                           |  |  |

| X Luettavissa verkossa osoitteessa http://lib.tkk.fi/Diss/2010/isbn9789526033198/                     |                           |  |  |

#### **Preface**

The research work of this thesis was carried out in the Electronic Circuit Design Laboratory, Aalto University School of Science and Technology (formerly Helsinki University of Technology), Espoo, Finland, during the years 2004-2010. The research was divided into two projects, namely "Capacitive Sensor Interface" (CAPACIF) and "Miniaturized Capacitive Sensor Interface" (MINICIF) projects, in both of which a low-power sensor interface for reading a capacitive 3-axis micro-accelerometer was studied. The first one, in the years 2004-2006, was funded by the Nokia Research Center, VTI Technologies, and the Finnish Funding Agency for Technology and Innovation (TEKES), while the second one, in the years 2006-2008, was funded by VTI Technologies and TEKES. During the years 2006-2010 I had the privilege of participating in the doctoral program of the Graduate School in Electronics, Telecommunications and Automation (GETA), which partially funded the research. The Centre of Excellence program (SMARAD2) funded partially the research work during the years 2008-2010. The work was also supported by the Finnish Foundation for Technology Promotion (TES), the Emil Aaltonen Foundation, the Ulla Tuominen Foundation, and the Walter Ahlström Foundation. I gratefully acknowledge all those who provided financial support.

In addition to providing funding, VTI Technologies and the Nokia Research Center are acknowledged for giving their permission to publish the original articles of this thesis. VTI Technologies is further acknowledged for providing the sensor elements and for the assistance and equipment necessary for the rate table measurements. I want to thank my colleagues at VTI Technologies and the Nokia Research Center with whom I co-operated with. Particularly, Mr. Teemu Elo, Dr. Teemu Salo, Mr. Tero Sillanpää, and Mr. Kimmo Törmälehto are acknowledged for many valuable discussions and comments.

I would like to thank my supervisor, Professor Kari Halonen, for giving me the opportunity to work in the laboratory during these years. Professor Halonen provided me with an interesting research topic and a research team with irreplaceable colleagues. I also wish to warmly thank Professor Philip K. T. Mok and Dr. Teemu Salo for reviewing this thesis and for their comments and suggestions.

The staff of the Electronic Circuit Design Laboratory, together with the colleagues who left the laboratory before me, deserve my gratitude for creating a pleasant and encouraging workplace. I warmly thank all the project members I had the pleasure of working with (in alphabetical order): Dr. Jere Järvinen, Dr. Lauri Koskinen, Dr. Marko Kosunen, Mika Kämäräinen, Dr. Mika Laiho, Erkka Laulainen, and Dr. Mikko Saukoski. In particular, I want to thank my great colleague Mika Kämäräinen for our seamless and memorable teamwork, my very talented project manager, Dr. Mikko Saukoski, for his valuable motivation, contribution, and nu-

merous paper reviews, and the instructor of my Master's and Licentiate's thesis, Dr. Mika Laiho, for his important contribution. I would also like to express my special gratitude to Lasse Aaltonen for his significant assistance since I settled at the same laboratory in 2004. I would also like to thank Lasse Aaltonen, Dr. Jere Järvinen, Mika Kämäräinen, Dr. Mika Laiho, and Dr. Mikko Saukoski for all the great free-time activities we have had together. I thank the office colleagues not mentioned above, Antti Kalanti, Pasi Rahikkala, and Timo Speeti, for our countless discussions and for creating a good working atmosphere. Moreover, Antti Kalanti and Mika Kämäräinen deserve special thanks, among others, for all the tight but relaxing badminton games we have played during the current and the last year. I would like to express my gratitude to the secretaries of the laboratory, Anja Meuronen, Lea Söderman, and Helena Yllö, for their kind help with all the practical matters.

My parents, Hilkka and Eero<sup>(† 26th May 2009)</sup>, and my brothers, Jani and Jukka, deserve my warmest gratitude for all the support and love they have given me throughout my life. I also dearly want to thank my parents-in-law, Arja and Juhani Luohio, for their kind support and all the great times we have spent together. I want to thank each and every dear friend not mentioned by name for all the relaxing times we have experienced together.

Finally, and foremost, I want to thank my beloved wife, Laura. You have brought so much love and happiness into my life, and your loving support helps me to get over all my worries.

Espoo, August 2010

Matti Paavola

### Contents

| Pı               | refac              | e                                                      | 7               |

|------------------|--------------------|--------------------------------------------------------|-----------------|

| $\mathbf{C}_{0}$ | onter              | nts                                                    | g               |

| Li               | st of              | Publications                                           | 13              |

| $\mathbf{A}$     | utho               | r's Contribution                                       | 15              |

| Sy               | mbo                | ls and Abbreviations                                   | 17              |

| 1                | Intr<br>1.1<br>1.2 | Poduction  Background and Motivation                   | <b>33</b><br>33 |

| <b>2</b>         | Mic                | romechanical Accelerometers                            | 35              |

|                  | 2.1                | General Accelerometer Structure                        | 35              |

|                  | 2.2                | MEMS Fabrication Technologies                          | 37              |

|                  |                    | 2.2.1 Bulk Micromachining                              | 37              |

|                  |                    | 2.2.2 Surface Micromachining                           | 38              |

|                  | 2.3                | Capacitive Micro-Accelerometers                        | 39              |

|                  |                    | 2.3.1 Bulk-Micromachined Capacitive Accelerometers     | 36              |

|                  |                    | 2.3.2 Surface-Micromachined Capacitive Accelerometers  | 41              |

|                  | 2.4                | Discussion                                             | 43              |

| 3                | Elec               | ctronic Interfacing of Capacitive Micro-Accelerometers | <b>4</b> 4      |

|                  | 3.1                | System Description                                     | 44              |

|                  |                    | 3.1.1 Electrostatic Forces                             | 46              |

|                  |                    | 3.1.2 Open-Loop Interfaces                             | 47              |

|                  |                    | 3.1.3 Closed-Loop Interfaces                           | 48              |

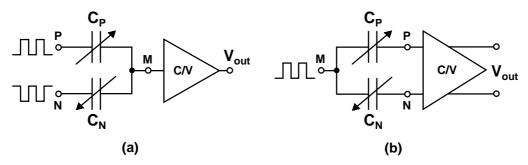

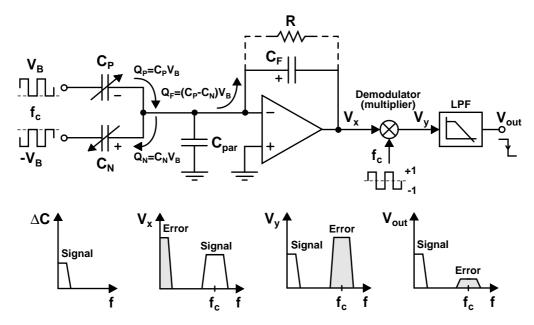

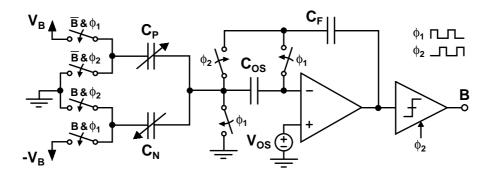

|                  | 3.2                | C/V Conversion                                         | 50              |

|                  |                    | 3.2.1 Continuous-Time Readout                          | 51              |

|                  |                    | 3.2.2 Discrete-Time Readout                            | 52              |

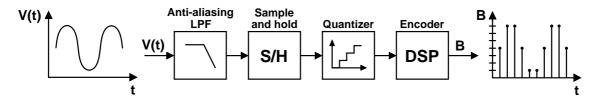

|                  | 3.3                | A/D Conversion                                         | 53              |

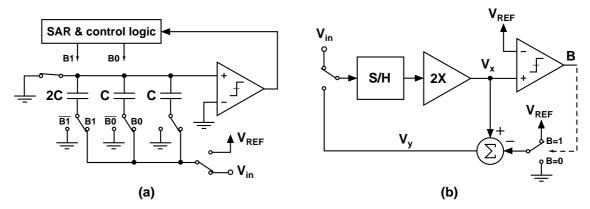

|                  |                    | 3.3.1 Successive Approximation ADC                     | 54              |

|                  |                    | 3.3.2 Algorithmic ADC                                  | 55              |

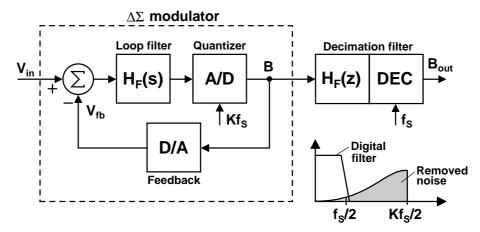

|                  |                    | 3.3.3 $\Delta\Sigma$ ADC                               | 56              |

|                  | 3.4                | Discussion                                             | 57              |

| 4                | Cur                | rent, Voltage, and Temperature References              | 59              |

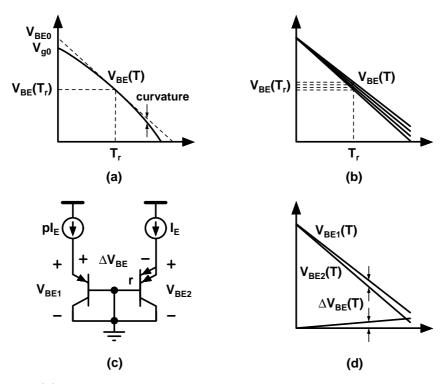

|                  | 4.1                | Bipolar Transistor Characteristics                     | 59              |

|                  |                    | 4.1.1 Base-Emitter Voltage                             | 59              |

|                  |                    | 4.1.2 Base-Emitter Voltage Difference                  | 61              |

|                  |                    | 4.1.3 Non-idealities in Base-Emitter Voltage           | 61              |

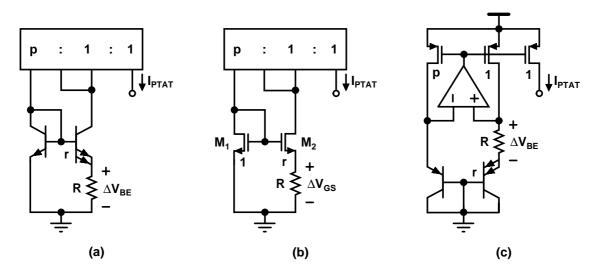

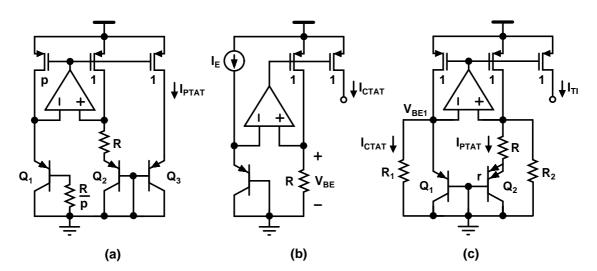

| 4.2.1 PTAT Current References 4.2.2 CTAT Current References 4.2.3 TI Current References 4.2.4 Start-Up Circuits 4.3 Voltage References 4.3.1 First-Order Voltage References 4.3.2 Curvature Correction Techniques 4.3.3 Non-ideal Effects 4.4 Temperature References 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques 6.3.1 Current-Efficient Buffer |       |   |  | . 62  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|--|-------|

| 4.2.3 TI Current References 4.2.4 Start-Up Circuits 4.3 Voltage References 4.3.1 First-Order Voltage References 4.3.2 Curvature Correction Techniques 4.3.3 Non-ideal Effects 4.4 Temperature References 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Relaxation Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                            |       |   |  | . 63  |

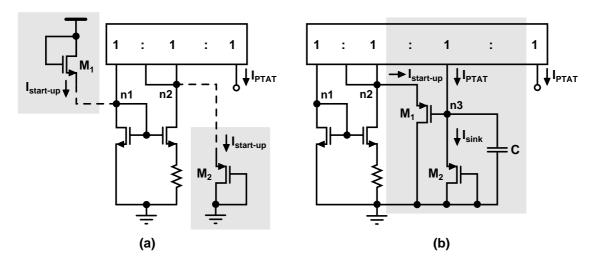

| 4.2.4 Start-Up Circuits  4.3 Voltage References  4.3.1 First-Order Voltage References  4.3.2 Curvature Correction Techniques  4.3.3 Non-ideal Effects  4.4 Temperature References  4.4.1 Summary of Literature  4.4.2 Ratiometric Temperature Measurement  4.4.3 Ratiometric Curvature Correction  4.4.4 Optimized Charge Balancing Readout  4.5 Discussion  5 Non-linear Frequency References  5.1 Oscillator Basics  5.1.1 Oscillator Models  5.1.2 Oscillator Categories  5.1.3 Voltage-Controlled Oscillators  5.2 Non-linear Oscillators  5.2.1 Ring Oscillators  5.2.2 Relaxation Oscillators  5.2.3 Jitter and Phase Noise  5.3.1 Summary of Literature  5.3.2 Relation between Jitter and Phase Noise  5.3.3 Impulse Sensitivity Function Theory  5.3.4 Phase Noise of Ring and Relaxation Oscillators  5.4 Discussion  6 Low-Dropout Linear Regulators  6.1 Linear Regulator Basics  6.1.1 Basic Structure and Operation  6.1.2 Linear vs. Switching Regulators  6.1.3 Overall Accuracy  6.1.4 Transient Variations  6.2 Frequency Compensation  6.2.1 Uncompensated Response  6.2.2 Compensated Response  6.2.3 Compensation Methods  6.3 Circuit Techniques                                                                                     |       |   |  | . 64  |

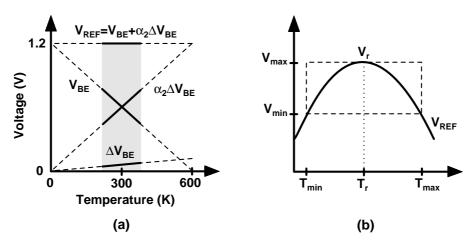

| 4.3 Voltage References 4.3.1 First-Order Voltage References 4.3.2 Curvature Correction Techniques 4.3.3 Non-ideal Effects 4.4 Temperature References 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                |       |   |  | . 65  |

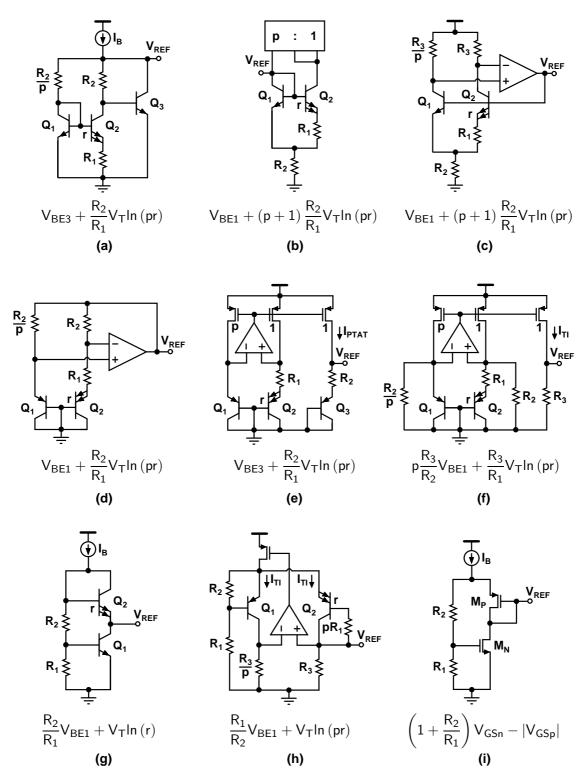

| 4.3.1 First-Order Voltage References 4.3.2 Curvature Correction Techniques 4.3.3 Non-ideal Effects 4.4 Temperature References 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                       |       |   |  | . 66  |

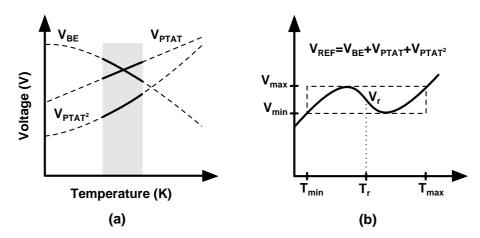

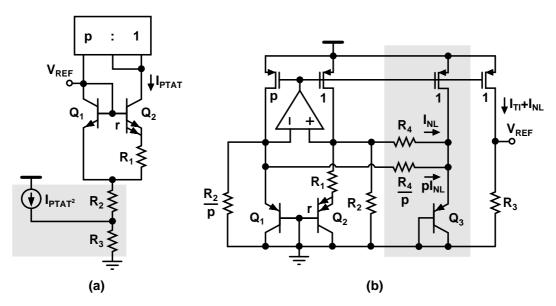

| 4.3.2 Curvature Correction Techniques 4.3.3 Non-ideal Effects  4.4 Temperature References 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                           |       |   |  | . 67  |

| 4.3.3 Non-ideal Effects 4.4 Temperature References 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.5 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                 |       |   |  | . 67  |

| 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2.1 Ring Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                    |       |   |  | . 71  |

| 4.4.1 Summary of Literature 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                |       |   |  |       |

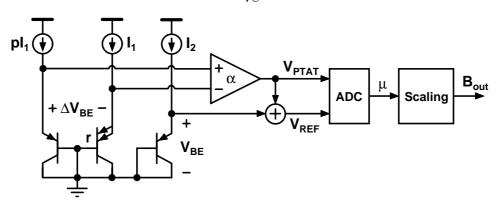

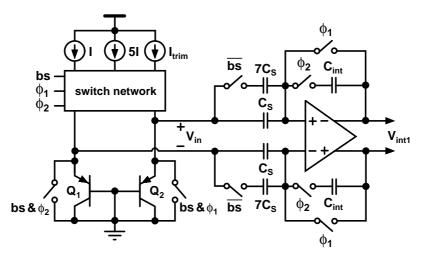

| 4.4.2 Ratiometric Temperature Measurement 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                |       |   |  | . 76  |

| 4.4.3 Ratiometric Curvature Correction 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                              |       |   |  | . 76  |

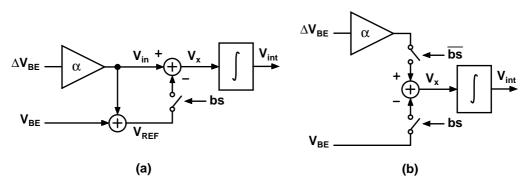

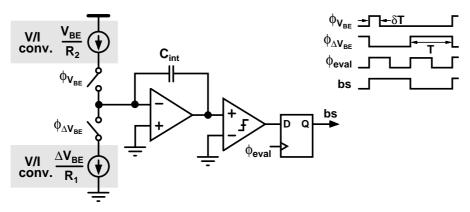

| 4.4.4 Optimized Charge Balancing Readout 4.5 Discussion  Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.2.2 Relaxation Oscillators 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  Linear Regulator Basics 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                          |       |   |  | . 77  |

| 4.5 Discussion  Non-linear Frequency References  5.1 Oscillator Basics  5.1.1 Oscillator Models  5.1.2 Oscillator Categories  5.1.3 Voltage-Controlled Oscillators  5.2 Non-linear Oscillators  5.2.1 Ring Oscillators  5.2.2 Relaxation Oscillators  5.3 Jitter and Phase Noise  5.3.1 Summary of Literature  5.3.2 Relation between Jitter and Phase Noise  5.3.3 Impulse Sensitivity Function Theory  5.3.4 Phase Noise of Ring and Relaxation Oscillators  5.4 Discussion  6 Low-Dropout Linear Regulators  6.1 Linear Regulator Basics  6.1.1 Basic Structure and Operation  6.1.2 Linear vs. Switching Regulators  6.1.3 Overall Accuracy  6.1.4 Transient Variations  6.2 Frequency Compensation  6.2.1 Uncompensated Response  6.2.2 Compensated Responses  6.2.3 Compensation Methods  6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  | . 78  |

| 5 Non-linear Frequency References 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion 6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |   |  | . 78  |

| 5.1 Oscillator Basics 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | <br>• | • |  | . 81  |

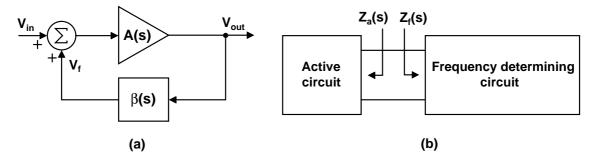

| 5.1.1 Oscillator Models 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.2.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |   |  | 83    |

| 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |   |  | . 83  |

| 5.1.2 Oscillator Categories 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |   |  | . 83  |

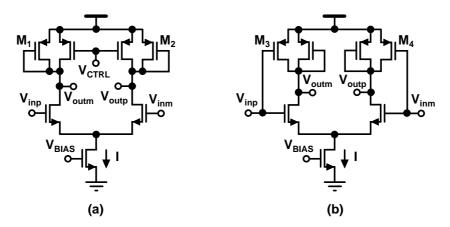

| 5.1.3 Voltage-Controlled Oscillators 5.2 Non-linear Oscillators 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |   |  |       |

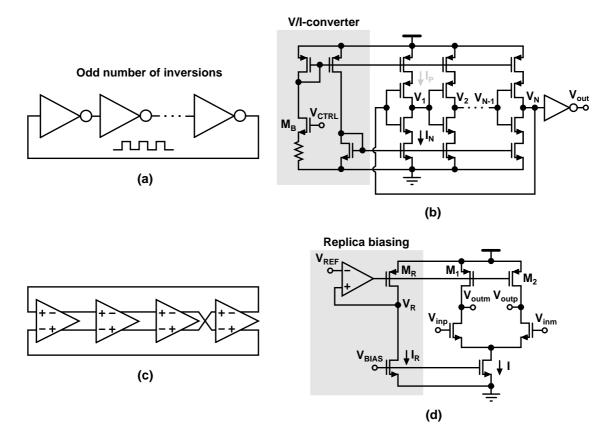

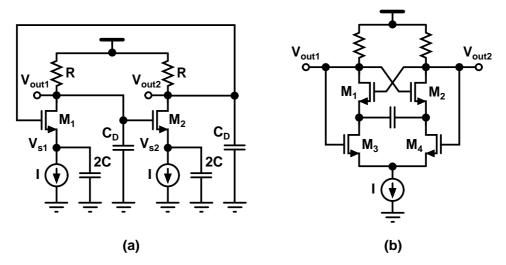

| 5.2.1 Ring Oscillators 5.2.2 Relaxation Oscillators 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |   |  |       |

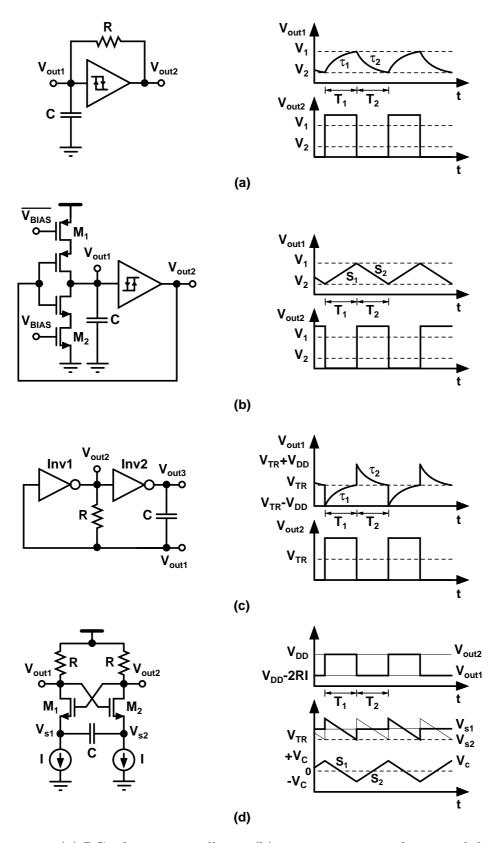

| 5.2.2 Relaxation Oscillators  5.3 Jitter and Phase Noise  5.3.1 Summary of Literature  5.3.2 Relation between Jitter and Phase Noise  5.3.3 Impulse Sensitivity Function Theory  5.3.4 Phase Noise of Ring and Relaxation Oscillators  5.4 Discussion  6 Low-Dropout Linear Regulators  6.1 Linear Regulator Basics  6.1.1 Basic Structure and Operation  6.1.2 Linear vs. Switching Regulators  6.1.3 Overall Accuracy  6.1.4 Transient Variations  6.2 Frequency Compensation  6.2.1 Uncompensated Response  6.2.2 Compensated Responses  6.2.3 Compensation Methods  6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |   |  | . 86  |

| 5.3 Jitter and Phase Noise 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |   |  | . 86  |

| 5.3.1 Summary of Literature 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |   |  | . 89  |

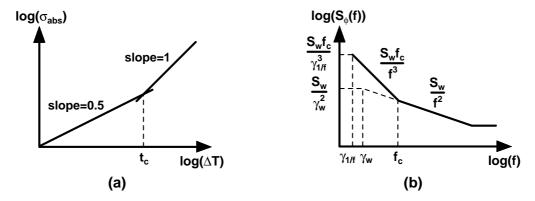

| 5.3.2 Relation between Jitter and Phase Noise 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |   |  | . 93  |

| 5.3.3 Impulse Sensitivity Function Theory 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Response 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |   |  | . 93  |

| 5.3.4 Phase Noise of Ring and Relaxation Oscillators 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       |   |  | . 93  |

| 5.4 Discussion  6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |   |  | . 96  |

| 6 Low-Dropout Linear Regulators 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |   |  | . 98  |

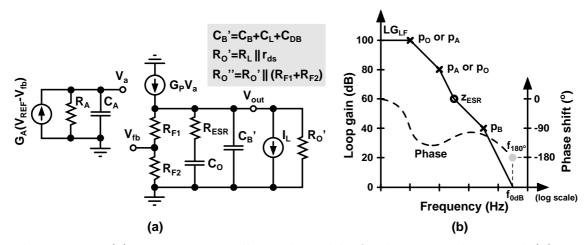

| 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | • |  | . 101 |

| 6.1 Linear Regulator Basics 6.1.1 Basic Structure and Operation 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |   |  | 103   |

| 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |   |  | . 103 |

| 6.1.2 Linear vs. Switching Regulators 6.1.3 Overall Accuracy 6.1.4 Transient Variations 6.2 Frequency Compensation 6.2.1 Uncompensated Response 6.2.2 Compensated Responses 6.2.3 Compensation Methods 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       |   |  | . 103 |

| 6.1.4 Transient Variations  6.2 Frequency Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |       |

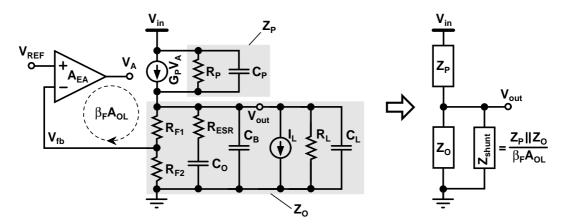

| 6.2 Frequency Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |   |  | . 105 |

| 6.2 Frequency Compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |   |  | . 106 |

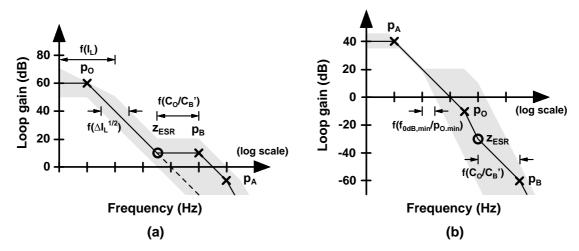

| 6.2.2 Compensated Responses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |   |  |       |

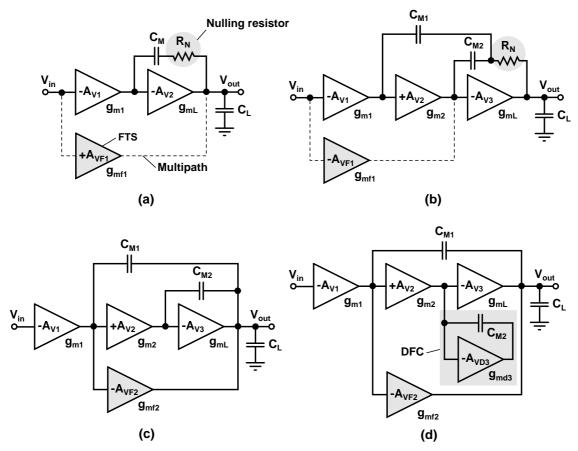

| 6.2.3 Compensation Methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |   |  | . 107 |

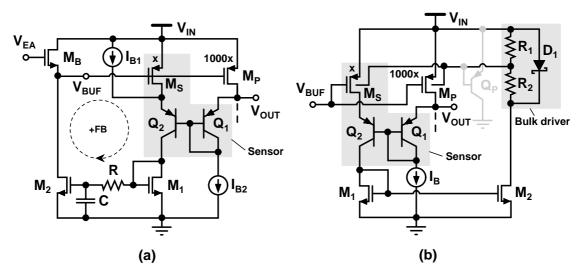

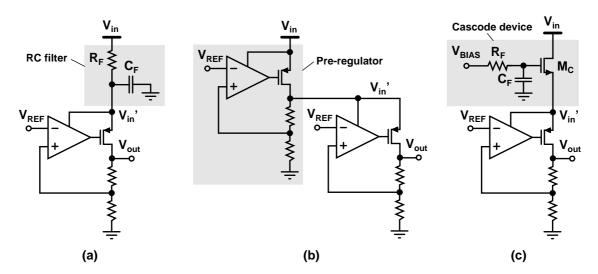

| 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  | . 108 |

| 6.3 Circuit Techniques                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |   |  |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |   |  |       |

| 6.3.2 Current Boosting                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  | . 114 |

| 6.3.3 Improving Power Supply Rejection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |   |  | . 114 |

|    | 6.4 Discussion          | 116 |

|----|-------------------------|-----|

| 7  | Summary of Publications | 118 |

| 8  | Conclusions             | 121 |

| R  | eferences               | 123 |

| Eı | rrata                   |     |

### List of Publications

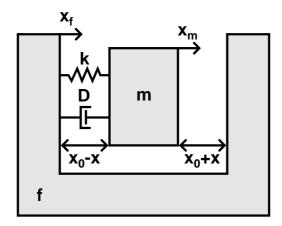

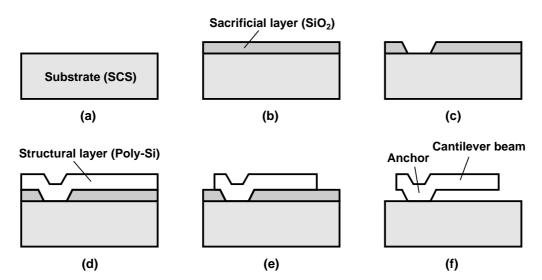

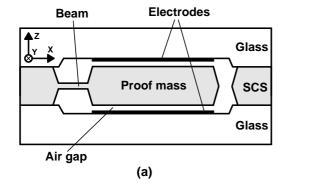

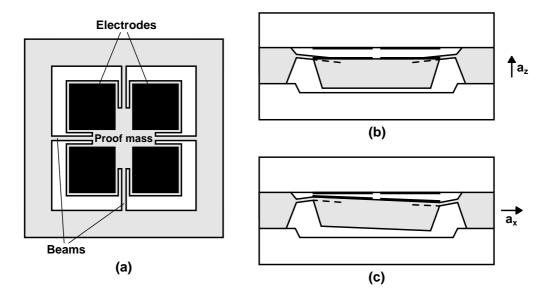

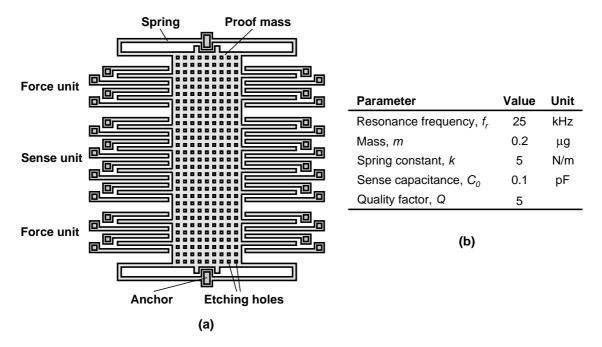

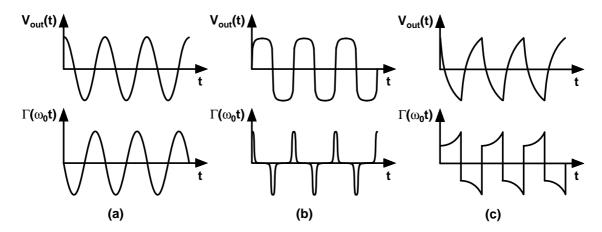

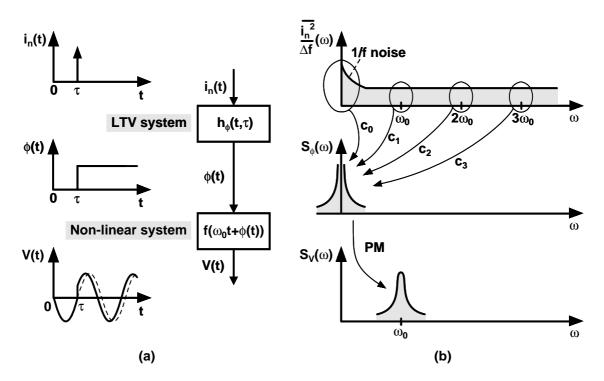

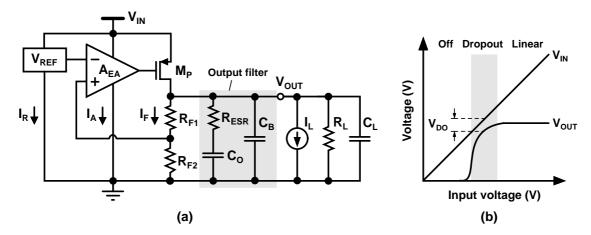

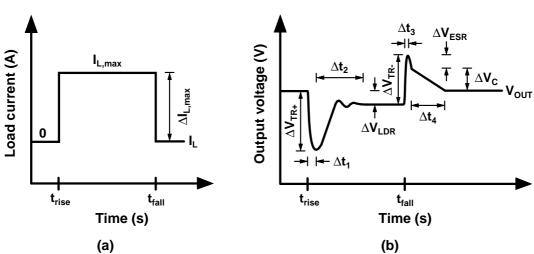

This thesis consists of an overview and of the following publications.