TKK Dissertations 163 Espoo 2009

# CRYOGENIC DEEP REACTIVE ION ETCHING OF SILICON MICRO AND NANOSTRUCTURES

**Doctoral Dissertation**

Lauri Sainiemi

Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences TKK Dissertations 163 Espoo 2009

# CRYOGENIC DEEP REACTIVE ION ETCHING OF SILICON MICRO AND NANOSTRUCTURES

**Doctoral Dissertation**

#### Lauri Sainiemi

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Faculty of Electronics, Communications and Automation for public examination and debate in Large Seminar Hall of Micronova at Helsinki University of Technology (Espoo, Finland) on the 22nd of May, 2009, at 12 noon.

Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences

Teknillinen korkeakoulu Elektroniikan, tietoliikenteen ja automaation tiedekunta Mikro- ja nanotekniikan laitos Distribution: Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Micro and Nanosciences P.O. Box 3500 (Tietotie 3) FI - 02015 TKK FINLAND URL: http://nano.tkk.fi/ Tel. +358-50-309 9799 Fax +358-9-451 6080 E-mail: Lauri.Sainiemi@tkk.fi

© 2009 Lauri Sainiemi

ISBN 978-951-22-9866-2 ISBN 978-951-22-9867-9 (PDF) ISSN 1795-2239 ISSN 1795-4584 (PDF) URL: http://lib.tkk.fi/Diss/2009/isbn9789512298679/

TKK-DISS-2598

Multiprint Oy Espoo 2009

| ABSTRACT OF DOCTORAL DISSERTATION                                                                   |                                                               |                           | HELSINKI UNIVERSITY OF TECHNOLOGY<br>P.O. BOX 1000, FI-02015 TKK<br>http://www.tkk.fi |

|-----------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------------------|---------------------------------------------------------------------------------------|

| Author Lauri Sainiemi                                                                               |                                                               |                           |                                                                                       |

| Name of the dissertation<br>Cryogenic deep reactive ion etching of silicon micro and nanostructures |                                                               |                           |                                                                                       |

| Manuscript submitted7.1.2009Manuscript revised16.4.200                                              |                                                               | uscript revised 16.4.2009 |                                                                                       |

| Date of the defend                                                                                  | ce 22.5.2009                                                  |                           |                                                                                       |

| Monograph                                                                                           |                                                               |                           | Article dissertation (summary + original articles)                                    |

| Faculty                                                                                             | Faculty Faculty of Electronics, Communications and Automation |                           |                                                                                       |

| Department                                                                                          | Department of Micro and Nanosciences                          |                           |                                                                                       |

| Field of research                                                                                   | esearch Semiconductor Technology                              |                           |                                                                                       |

| Opponent(s)                                                                                         | Prof. Ole Hansen                                              |                           |                                                                                       |

| Supervisor                                                                                          | Supervisor Prof. Pekka Kuivalainen                            |                           |                                                                                       |

| Instructor                                                                                          | nstructor Doc. Sami Franssila                                 |                           |                                                                                       |

Abstract

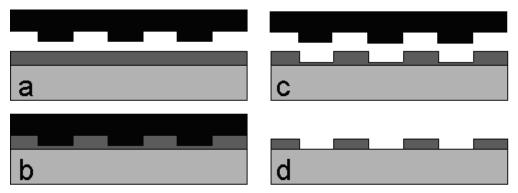

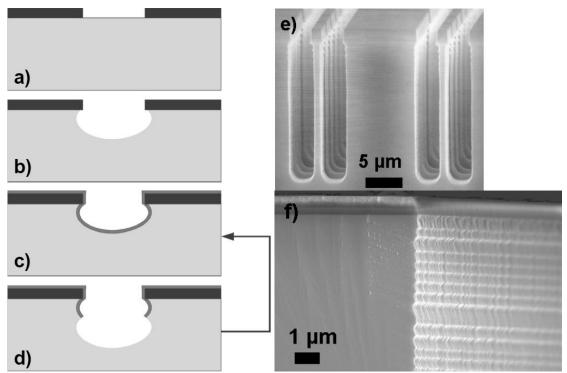

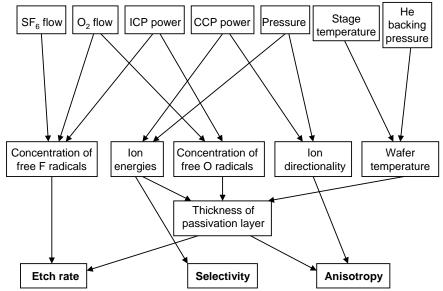

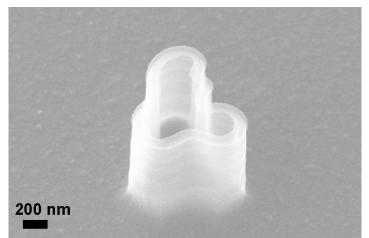

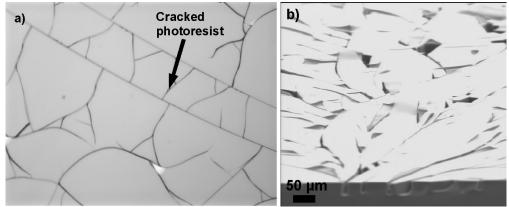

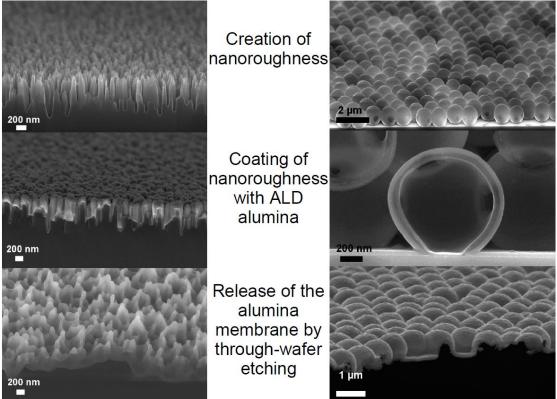

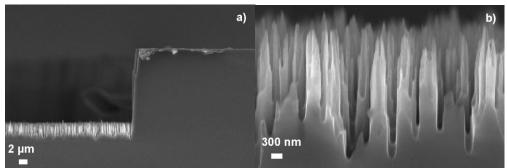

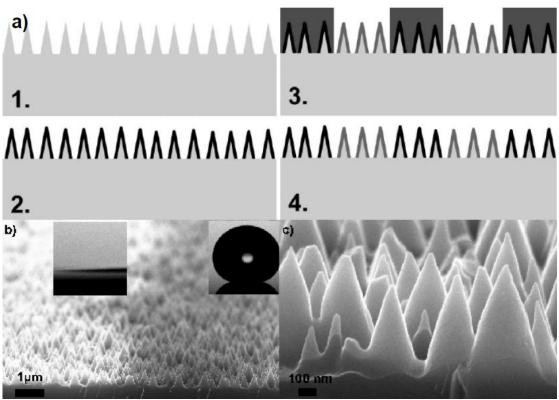

This thesis focuses on cryogenic deep reactive ion etching (DRIE) and presents how it can be applied to the fabrication of silicon micro- and nanostructures that have applications in microfluidics and micromechanics. The cryogenic DRIE process relies on inductively coupled  $SF_6/O_2$  plasma at temperatures below -100 °C. Low etching temperatures can cause some photoresist materials to crack, but  $Al_2O_3$  has been shown to be a very well-suited masking material for cryogenic etching. The anisotropy of the etching process is enhanced by a thin passivation layer on sidewalls that prevents lateral etching. The main parameters that are used to adjust the thickness of the passivation layer are the process temperature and the  $O_2$  flow. Under adequate conditions vertical sidewalls are obtained, whereas passivation layers that are too thin result in negatively tapered sidewall slopes. Under conditions where a passivation layer is not formed, at higher temperatures and/or without oxygen flow, the etching profiles are isotropic. On the other hand, too high oxygen flow results in over passivation. Under conditions where the sidewall is slightly over passivated, its slopes are positively tapered, while more pronounced over passivation results in the formation of black silicon (or silicon nanograss, silicon nanoturf or columnar microstructures).

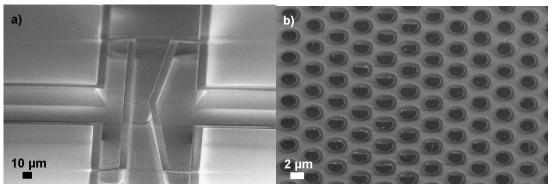

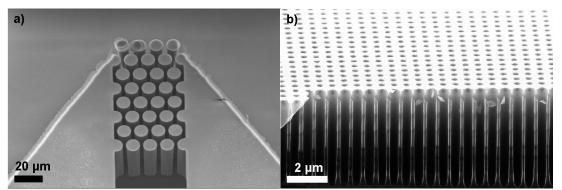

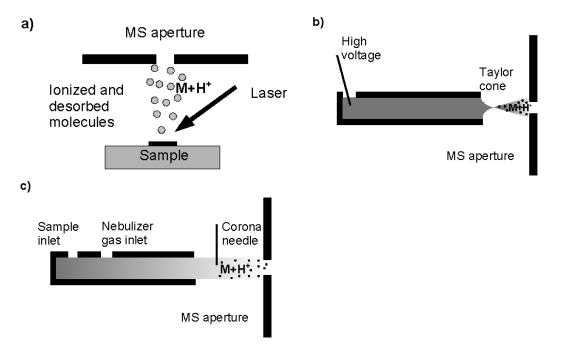

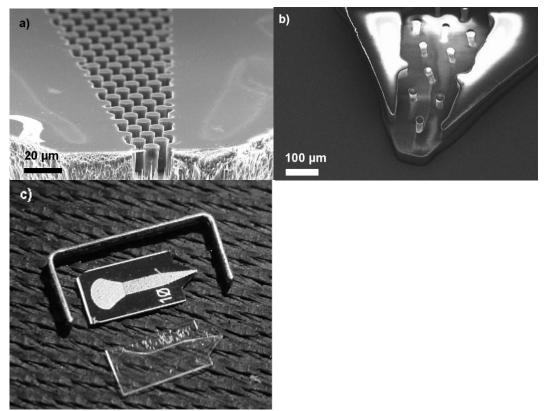

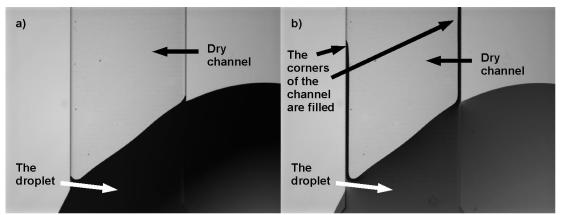

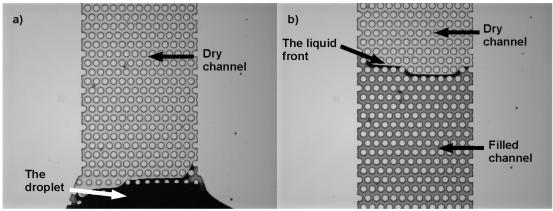

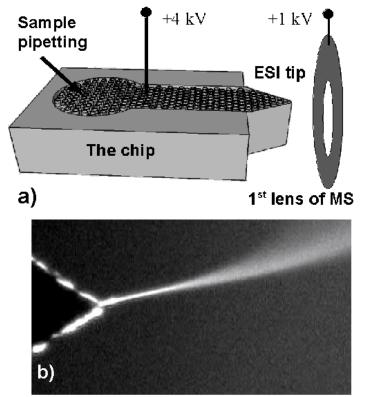

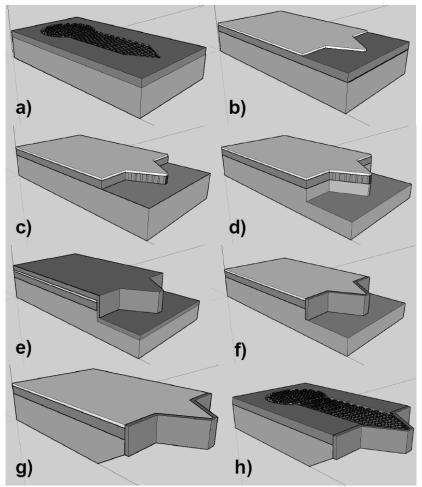

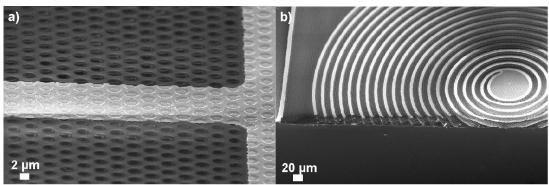

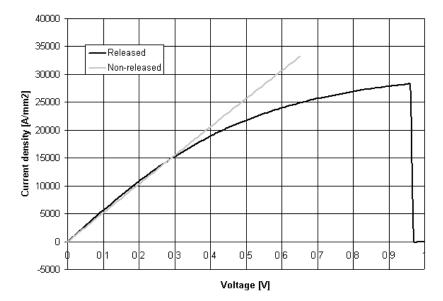

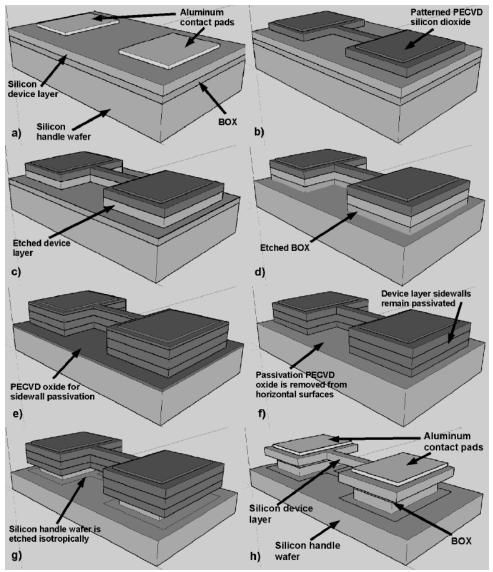

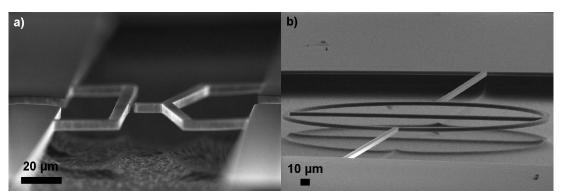

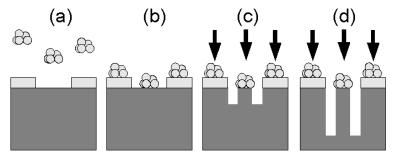

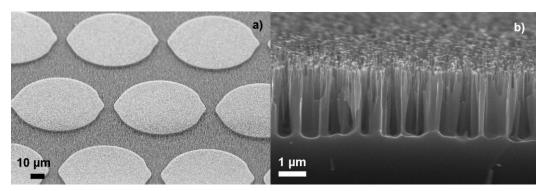

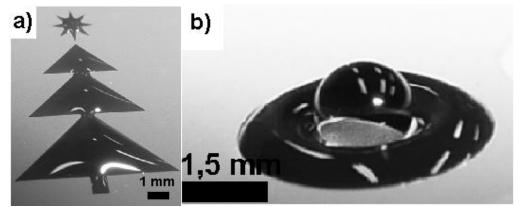

Typically, vertical sidewall profiles are desirable. However, this thesis shall also demonstrate the usefulness of under and over passivation regimes. Here, highly anisotropic etching conditions are utilized to create trenches with vertical sidewalls, fluidic channels with regular micropillar arrays, and high aspect ratio silicon nanopillars. An isotropic etching process is utilized during the release of aluminum heaters fabricated on top of perforated free-standing Al<sub>2</sub>O<sub>3</sub> membranes and silicon dioxide coated thermal silicon actuators. The fabrication process of three-dimensional sharp electrospray ionization (ESI) tips takes advantage of etching conditions that result in negatively tapered sidewalls. A self-feeding ESI interface for mass spectrometry (MS) is fabricated by combining a lidless micropillar filled channel with a sharp tip. Two approaches to the fabrication of silicon nanopillars are presented, both of which are suitable for wafer-scale manufacturing. One method combines silica nanoparticles with a highly anisotropic DRIE step, while the other method relies on highly over passivating conditions in a maskless DRIE process. Due to a large surface area and efficient light absorption in UV-range, silicon nanopillar structured surfaces are utilized as sample plates in laser desorption/ionization (LDI) MS. The wetting of nanopillar structured silicon surfaces is also studied. Fluoropolymer coated nanopillar structured surfaces have a contact angle of more than 170° and are ultrahydrophobic, whereas oxidized nanostructured surfaces are completely wetting. The accurate patterning of both completely wetting and ultrahydrophobic areas side by side allows complex droplet shapes and droplet splitters to be tailored.

| <u> </u>                                                                                 |                   |                 |           |

|------------------------------------------------------------------------------------------|-------------------|-----------------|-----------|

| Keywords Cryogenic deep reactive ion etching; microfabrication; nanofabrication; silicon |                   |                 |           |

| ISBN (printed)                                                                           | 978-951-22-9866-2 | ISSN (printed)  | 1795-2239 |

| ISBN (pdf)                                                                               | 978-951-22-9867-9 | ISSN (pdf)      | 1795-4584 |

| Language                                                                                 | En                | Number of pages | 61+89     |

| Publisher TKK, Department of Micro and Nanosciences                                      |                   |                 |           |

| Print distribution TKK, Department of Micro and Nanosciences                             |                   |                 |           |

| The dissertation can be read at http://lib.tkk.fi/Diss/2009/isbn9789512298679/           |                   |                 |           |

| VÄITÖSKIRJAN TIIVISTELMÄ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | TEKNILLINEN KORKEAKOULU<br>PL 1000, 02015 TKK<br>http://www.tkk.fi |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--|--|

| Tekijä Lauri Sainiemi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

| Väitöskirjan nimi<br>Mikro- ja nanorakenteiden valmistaminen rekatiivisella i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | onietsaus menetelmällä piistä kryogeenisissä lämpötiloissa         |  |  |

| Käsikirjoituksen päivämäärä 7.1.2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Korjatun käsikirjoituksen päivämäärä 16.4.2009                     |  |  |

| Väitöstilaisuuden ajankohta 22.5.2009                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                    |  |  |

| Monografia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Yhdistelmäväitöskirja (yhteenveto + erillisartikkelit)             |  |  |

| Tiedekunta Elektroniikan, tietoliikenteen ja auto                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | maation tiedekunta                                                 |  |  |

| Laitos Mikro ja nanotekniikan laitos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

| Tutkimusala Puolijohdeteknologia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |  |  |

| Vastaväittäjä(t) Prof. Ole Hansen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                    |  |  |

| Työn valvoja Prof. Pekka Kuivalainen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                    |  |  |

| Työn ohjaaja Dos. Sami Franssila                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |  |  |

| Tiivistelmä<br>Väitöskirja käsittelee kryogeenistä lämpötilaa hyödyntävää reaktiivista ionietsausmenetelmää ja sen soveltamista piistä<br>tehtyjen mikro- ja nanorakenteiden valmistukseen. Rakenteita hyödynnetään mikrofluidistisissa ja mikromekaanisissa<br>komponenteissa. Etsausprosessi perustuu SF <sub>c</sub> /O <sub>2</sub> -plasman käytöön alle -100 °C lämpötilassa. Osa fotoresisteistä ei ole<br>yhteensopivia matalan lämpötilan kanssa, vaan ne halkeilevat, kun taas A1 <sub>2</sub> O <sub>3</sub> soveltuu hyvin kryogeenisen etsausprosessin<br>etsausmaskimateriaaliksi. Ohut passivointikerros rakenteen sivuseimämillä parantaa etsausprosessin anisotropiaa estämällä<br>sivusuuntaisen etsaantumisen. Tärkeimmät parametrit, joilla passivointikerrosken paksuutta voidaan säätää, ovat prosessin<br>lämpötila ja O <sub>2</sub> -virtaus. Sopivissa olosuhteissa on mahdollista saavuttaa täysin pystysuorat sivuseinät, kun taas liian ohut<br>passivointikerros aiheuttaa levenevän (negatiivisen) sivuseinäkulman. Olosuheissa, joissa passivointikerrosta ei muodostu<br>(esim. korkeammissa lämpötiloissa tai ilman happivirtausta), etsausprofiilista tulee isotrooppinen. Toisaalta liian korkea<br>happivirtaus johtaa ylipassivointiin. Hieman ylipassivoivissa olosuhteissa sivuseinän kulma on kapeneva (positiivinen), ja<br>voimakas ylipassivointi johtaa mustan piin syntymiseen. Musta pii tunnetaan myös nimellä piinanoruoho.<br>Tyypillisesti rakenteisiin halutaan pystysuorat sivuseinät. Tässä väitöskirjassa osoitetaan myös yli- ja alipassivointi-<br>olosuhteiden hyödyllisyys. Anisotrooppisia etsausolosuhteita hyödynnetään syvänteiden, mikrofluidististen pilarikanavien<br>ja korkean aspektisuhteen nanopilareiden valmistuksessa. Isotrooppista prosessia hyödynnetään itsekantavan reitietyn<br>aluminakalvon päälle valmistetujen valmistus hyödyntää negatiivia sivuseinäprofileja tuotavia<br>etsausolosuhteita. Kun kanneton pilarikanava ja terävä kärki yhdistetään, voidaan valmistaa itsesyöttävä sähkösumutus-<br>ionisaatiolähde massaspektrometriaan. Työssä esitellään myös kaksi tapaa valmistaa piistä tehtyjä nanopailareita.<br>Valmistustavat soveltuvat |                                                                    |  |  |

| AsiasanatReaktiivinen ionietsaus kryogeenisissä lämpötiloissa; mikrovalmistus; nanovalmistus; piiISBN (painettu)978-951-22-9866-2ISSN (painettu)1795-2239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                    |  |  |

| ISBN (pdf) 978-951-22-9867-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ISSN (pdf) 1795-4584                                               |  |  |

| Kieli En                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Sivumäärä 61+89                                                    |  |  |

| Julkaisija TKK, Mikro- ja nanotekniikan laitos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                    |  |  |

| Painetun väitöskirjan jakelu TKK, Mikro- ja nanotekniikan laitos                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |  |  |

| Luettavissa verkossa osoitteessa http://lib.tkk.fi/Diss/2009/isbn9789512298679/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                    |  |  |

| ∑ Lucuavissa veikossa osoineessa inip.//110.1KK.11/DISS/2009/180119/893122980/9/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |  |  |

# Preface

The work presented in this thesis was carried out at the Microfabrication group at the Helsinki University of Technology during the years 2006-2008. There are so many people who have helped and supported me along the way that this page is not big enough to mention everyone, but below I have listed some of the many people and organizations whom I am grateful to.

The biggest thanks go to soon-to-be professor Sami Franssila, who has given me the opportunity to work in this interesting field. Your guidance, supervision, and encouragement have been invaluable. I am also grateful to my present and former colleagues at the Microfabrication group and the TKK-Micronova group's technical staff. Because of you it has always been a pleasure to come to work, even when the research results have not been that great.

I wish to thank all the bright scientists with whom I have had the privilege to collaborate with. Especially, I want to thank Kestas Grigoras, Ville Jokinen, and Ville Saarela from the Microfabrication group, Teemu Nissilä, Laura Luosujärvi, Tiina Sikanen, Tapio Kotiaho, Raimo Ketola, Risto Kostiainen, Ivan Kassamakov, Kalle Hanhijärvi, Juha Aaltonen, and Edward Hæggström from the University of Helsinki and Helmi Keskinen, Mikko Aromaa and Jyrki Mäkelä from the Tampere University of Technology and Ji Fan from Detection Technologies, who all are co-authors of the journal articles attached to this thesis. I also want to acknowledge doctors Franz Lärmer, Kai Kolari and Marc Baumann. Without your contributions I would not have been able to finish my thesis. I am also grateful to my thesis supervisor Prof. Pekka Kuivalainen and the pre-examiners Prof. Peter Enoksson and Dr. James Dekker. Thank you for your constructive comments.

For supporting my research financially, I would like to acknowledge The Finnish National Graduate School in Nanoscience (NGS-NANO), The Finnish Funding Agency for Technology and Innovation (Tekes), The Academy of Finland, The Finnish Foundation for Technology Promotion, The Finnish Cultural Foundation, and The Walter Ahlström Foundation.

Big thanks go also to all my friends who have given me things to do and think about other than my research and thesis. I would like to send special thanks to my girlfriend Nina.

Finally, I want to thank my parents Annukka and Jukka who have always supported me by all possible means in my studies and in life in general.

Espoo, April 2009

Lauri Sainiemi

# Contents

|   | -                | cations included in the thesis:                                    |       |

|---|------------------|--------------------------------------------------------------------|-------|

|   |                  | ntribution to the publications included in the thesis              |       |

| A | bbreviation      | ns                                                                 | 10    |

| 1 | <b>T</b> / 1     |                                                                    | 11    |

| 1 | Introdu          | ction                                                              | 11    |

| 2 | Fundan           | nentals of silicon micro- and nanofabrication                      | 15    |

| 4 |                  | hography                                                           |       |

|   | 2.1 Liu          | Optical lithography                                                |       |

|   | 2.1.1            | Electron beam lithography (EBL)                                    |       |

|   | 2.1.2            | Nanoimprint lithography (NIL)                                      |       |

|   | 2.1.3            | Other masking techniques                                           |       |

|   |                  | hing                                                               |       |

|   | 2.2 Lie<br>2.2.1 | Wet etching                                                        |       |

|   | 2.2.1            | Dry etching                                                        |       |

|   | 2.2.2            |                                                                    |       |

| 3 | Cryoger          | nic deep reactive ion etching processes                            |       |

| · |                  | sk material effects and issues                                     |       |

|   | 3.1.1            | Introduction                                                       |       |

|   | 3.1.2            | Photoresist cracking                                               |       |

|   | 3.1.3            | Hard masks                                                         |       |

|   | 3.1.4            | Peeling mask                                                       |       |

|   | 3.2 Min          | niaturized devices for analytical applications                     |       |

|   | 3.2.1            | Ionization methods for mass spectrometry                           |       |

|   | 3.2.2            | Miniaturized electrospray ionization source                        |       |

|   | 3.3 Dry          | y fabrication of suspended microstructures                         |       |

|   | 3.3.1            | Alumina membranes                                                  |       |

|   | 3.3.2            | Thermal silicon actuators                                          | 40    |

|   | 3.4 Fat          | prication of silicon nanopillars                                   | 43    |

|   | 3.4.1            | Silicon nanopores and pillars                                      | 43    |

|   | 3.4.2            | Black silicon                                                      | 43    |

|   | 3.4.3            | Silicon nanopillars defined by liquid flame spray deposited silica | L     |

|   |                  | nanoparticle agglomerates                                          | 45    |

|   | 3.5 The          | e chemical modification of nanostructured silicon surfaces         | 46    |

|   | 3.5.1            | Wetting of surfaces                                                |       |

|   | 3.5.2            | The fabrication of accurately defined completely wetting domain    | is on |

|   |                  | ultrahydrophobic surfaces                                          |       |

|   | 3.6 Etc          | hing parameters for different processes                            | 49    |

| - | a -              |                                                                    |       |

| 4 | Conclus          | sions and future outlook                                           | 51    |

| р | oforonooc        |                                                                    | 52    |

| R |                  | •••••••••••••••••••••••••••••••••••••••                            |       |

# List of publications included in the thesis:

The following peer-reviewed publications form the basis for this thesis. The publications are hereafter referred to by their Roman numerals:

- I Handbook of Silicon Based MEMS Materials and Technologies, editors Veikko Lindroos, Markku Tilli, Ari Lehto and Teruaki Motooka:

Franz Lärmer, Sami Franssila, Lauri Sainiemi, Kai Kolari: parts of the chapter "Deep reactive ion etching", Elsevier (to be published autumn 2009)

- II Lauri Sainiemi, Sami Franssila, Mask material effects in cryogenic deep reactive ion etching, *Journal of Vacuum Science and Technology B*, 25, 801-807, 2007, DOI:<u>10.1116/1.2734157</u>

- III Lauri Sainiemi, Teemu Nissilä, Ville Jokinen, Tiina Sikanen, Tapio Kotiaho, Risto Kostiainen, Raimo A. Ketola, Sami Franssila, Fabrication and fluidic characterization of micropillar array electrospray ionization chip, *Sensors and Actuators B, Chemical*, **132**, 380-387, 2008, DOI:<u>10.1016/j.snb.2007.09.077</u>

- IV Lauri Sainiemi, Kestas Grigoras, Sami Franssila, Suspended nanostructured alumina membranes, *Nanotechnology*, 20, 2009, 075305, DOI: <u>10.1088/0957-</u> <u>4484/20/7/075306</u>

- V Lauri Sainiemi, Kestas Grigoras, Ivan Kassamakov, Kalle Hanhijärvi, Juha Aaltonen, Ji Fan, Ville Saarela, Edward Hæggström, Sami Franssila, Fabrication of thermal microbridge actuators and characterization of their electrical and mechanical responses, *Sensors and Actuators: A Physical*, **149**, 305-314, 2009 DOI:10.1016/j.sna.2008.11.031

- VI Lauri Sainiemi, Helmi Keskinen, Mikko Aromaa, Laura Luosujärvi, Kestas Grigoras, Tapio Kotiaho, Jyrki M. Mäkelä, Sami Franssila, Rapid fabrication of high aspect ratio silicon nanopillars for chemical analysis, *Nanotechnology*, 18, 505303, 2007, DOI:<u>10.1088/0957-4484/18/50/505303</u>

- VII Ville Jokinen, Lauri Sainiemi, Sami Franssila, Complex droplets on chemically modified silicon nanograss, *Advanced Materials*, **20**, 3453-3456, 2008 DOI:<u>10.1002/adma.200800160</u>

# Author's contribution to the publications included in the thesis

#### **Publication I:**

One of the authors of the book chapter. Author's contributed especially to chapters 23.3, DRIE processes and 23.5, DRIE applications.

#### **Publication II:**

Planning the experiments, all the experimental work and writing the article.

#### **Publication III:**

Planning the experiments, experimental work with the exception of mass spectrometry, and writing the article.

#### **Publication IV:**

Planning the experiments, experimental work with the exception of the nanobead processes and atomic layer deposition, and writing the article.

#### **Publication V:**

Planning the experiments, experimental work with the exception of the white light interferometry part, and writing the article.

#### **Publication VI:**

Planning the experiments, micro- and nanofabrication work with the exception of the porous silicon fabrication, and writing the article.

#### **Publication VII:**

The planning of the experiments, experimental work and the writing of the article were all done together with Ville Jokinen. Equal contribution with the first author.

# Abbreviations

| μPESI                           | micropillar array electrospray ionization            |

|---------------------------------|------------------------------------------------------|

| μTAS                            | micro total analysis systems                         |

| ADRE                            | aspect ratio dependent etching                       |

| ALD                             | atomic layer deposition                              |

| $Al_2O_3$                       | aluminum oxide / alumina                             |

| APCI                            | atmospheric pressure chemical ionization             |

| APPI                            | atmospheric pressure photo ionization                |

| BOX                             | buried oxide layer                                   |

| CHF <sub>3</sub>                | carbon hydro trifluoride                             |

| CF <sub>4</sub>                 | carbon hydro trindonde<br>carbon tetrafluoride       |

| -                               | trifluoroacetamide                                   |

| $C_2H_2F_3NO$                   |                                                      |

| $C_4F_8$                        | octofluoro cyclobutane                               |

| CTE                             | coefficient of thermal expansion                     |

| CVD<br>DIOS                     | chemical vapor deposition                            |

|                                 | desorption/ionization on silicon                     |

| DRIE                            | deep reactive ion etching                            |

| EBL                             | electron beam lithography                            |

| EDP                             | ethylene diamine-pyrocatechol                        |

| ESI                             | electrospray ionization                              |

| FIB                             | focused ionbeam etching                              |

| $H_2$                           | hydrogen                                             |

| HF                              | hydrofluoric acid                                    |

| IC                              | integrated circuits                                  |

| KOH                             | potassium hydroxide                                  |

| LDI                             | laser desorption ionization                          |

| LFS                             | liquid flame spray                                   |

| MALDI                           | matrix assisted laser desorption ionization          |

| MEMS                            | microelectromechanical systems                       |

| MOSFET                          | metal oxide semiconductor field effective transistor |

| MS                              | mass spectrometry                                    |

| NIL                             | nanoimprint lithography                              |

| HNO <sub>3</sub>                | nitric acid                                          |

| NSL                             | nanosphere lithography                               |

| $O_2$                           | oxygen                                               |

| PECVD                           | plasma enhanced chemical vapor deposition            |

| RF                              | radio frequency                                      |

| RIE                             | reactive ion etching                                 |

| SALDI                           | surface activated laser desorption/ionization        |

| SEM                             | scanning electron microscopy                         |

| $SF_6$                          | sulfur hexafluoride                                  |

| SOI                             | silicon on insulator                                 |

| S-FIL                           | step & flash imprint lithography                     |

| $SiO_2$                         | silicon dioxide / silica                             |

| SiO <sub>x</sub> F <sub>y</sub> | silicon oxyfluoride                                  |

| TEOS                            | nanoparticles tetra-ethyl-ortho-silicate             |

| TMAH                            | tetramethyl ammonium hydroxide                       |

| UV                              | ultraviolet                                          |

|                                 |                                                      |

# **1** Introduction

## Historical perspective

The first transistor was fabricated in 1947 by Bardeen, Brattain, and Shockley and the first patent application concerning integrated circuits (IC) was filed over ten years later in 1959 by Jack Kilby [1]. The first transistors were made out of polycrystalline germanium, but soon the superiority of single crystalline materials was noticed. The single crystalline materials offered reproducible and uniform device properties with longer carrier lifetimes and higher carrier mobility [2]. Point contact transistors were already commercially available by the mid 1950s. Germanium was still the dominant material, despite the fact that the fabrication of silicon transistors was demonstrated very soon after the first germanium transistor. The dominant fabrication techniques of point contact transistors were grown junction and alloy junction technologies. At this stage, there were no means for integrating multiple transistors on a single chip [3].

The next big leaps towards modern IC technology were the inventions of the gas phase diffusion process and the planar transistor fabrication process. At this point, silicon quickly replaced germanium as the main transistor material. The silicon transistor enabled higher output powers and operating temperatures than germanium. Also the good availability of silicon, the possibility to fabricate single crystalline silicon wafers and tailor the resistivity of the material made its use feasible. Furthermore, the single most important factor that made silicon the transcendent material for electronic applications was possibility of growing a silicon dioxide layer on top of the wafer in a controllable manner [2]. Chemically, silicon dioxide is a fairly inert material and therefore often utilized as a passivating coating to protect silicon from reacting with environmental impurities. Patterned silicon dioxide layers also work as a diffusion and an etch mask. Silicon dioxide is an insulating material which, even today, is used as a gate oxide material in metal oxide semiconductor field effective transistors (MOSFET).

After these developments, the first integrated circuits were demonstrated. The first IC was fabricated by Kilby, again based on germanium transistors. Less than a year later, Robert Noyce demonstrated the first silicon based IC. The design presented by Noyce took advantage of the planar process. The emitters and the collectors were diffused into the substrate. The individual components fabricated on a single substrate were interconnected using evaporated aluminum [1]. The circuit presented by Noyce was, in principle, very similar to modern integrated circuits. The usefulness of integrated circuits was soon realized and they completely revolutionized the world of electronics to such an extent that today all electronic devices (computers, cellular phones etc.) rely on integrated circuits. The scientific community also realized the value of these inventions. Bardeen, Brattain and Shockley were awarded the Nobel Prize in Physics in 1956 for their researches in semiconductors and their discovery of the transistor effect. Kilby received the same honor in the year 2000 for his part in the invention of integrated circuits.

Since the 1960s, basic technology has advanced steadily and the demand for higher numbers of components on smaller chips has made it necessary to develop more accurate silicon micro- and nanofabrication techniques. Gradually, the benefits of miniaturization in other fields of engineering became apparent, and the miniaturization of, for example, mechanical, optical and fluidic devices was begun [4-12]. Silicon was also the most obvious choice of material for non-electronic applications, due to its good mechanical properties and the fact that fabrication techniques had already been developed for the needs of IC industry. The first resonator based on silicon surface micromachining techniques was published already 1967 [4]. Later, a similar but more sophisticated device was fabricated and utilized in radio frequency switching applications [7]. The device fabrication utilized methods such as bulk micromachining and epitaxial growth of silicon. Today, there are many research groups that devote their efforts entirely to the development of radio frequency microelectromechanical systems (RF-MEMS). Similar membrane structures and small moving parts that are important in RF-MEMS have also played a key role in the development of miniaturized sensors and transducers [8, 9, 11]. Pressure sensors and accelerometers were among the first sensors that were miniaturized, and today both of these devices have been commercialized [13]. Lately, the feasibility of MEMS technology has also been applied to the field of optics [12]. The polished silicon surface is a good substrate for a micromirror, and the mechanical properties of silicon offer the possibility of fabricating fatigue free components. These are key elements in optical switches.

The first microfluidic devices emerged in 1970's [5, 6, 9]. A microfluidic nozzle, used for ink jet printing, was one of the first fluidic applications that took advantage of silicon micromachining [6]. The first nozzles were simply through-wafer anisotropically wet etched holes. Since their initial release, ink jet nozzles have developed substantially and they still are probably the most widespread and most successfully commercialized miniaturized fluidic devices. In addition, much more complex fluidic devices have been created by means of silicon microfabrication. Terry et al. fabricated a gas chromatograph on a silicon wafer [5, 9]. This miniaturized chromatograph, just as a conventional one, consisted of inlets for the sample and carrier gases, a capillary column for the sample separation, and a thermal conductivity detector. A glass cover was anodically bonded onto silicon wafer to enclose the channels. Anodic bonding is still frequently used to seal the fabricated silicon micro channels. This miniaturized gas chromatograph was around the size of a matchbox. A new boost was given to the development of miniaturized fluidic systems capable of chemical analysis in the early 1990's, when Manz et al. introduced the concept of miniaturized total analysis systems (µTAS) [10]. Since then, the goal of many research groups has been to integrate several functions such as sample concentration, separation and analysis on a single fluidic chip.

#### Etching of silicon

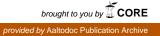

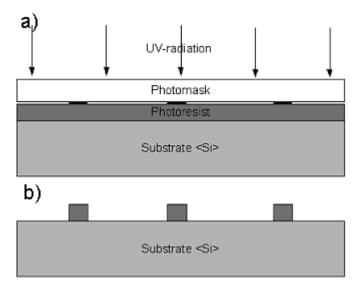

When creating desired structures into a silicon wafer, some parts of the wafer must be protected while the unprotected parts are etched. The protective material is known as an etch mask, and a common substance used for this purpose is silicon dioxide. Silicon etching is typically divided to two main categories: wet etching and dry etching according to the type of etchant. In wet etching, the partially protected silicon wafer is immersed in an aqueous solution such as potassium hydroxide, which etches silicon from unprotected areas. In dry etching gaseous etchants etch the silicon substrate. Reactive ion etching (RIE) and plasma etching are, on some occasions, used somewhat incorrectly as synonyms for dry etching. Reactive ion etching is the most common dry etching method, which combines the effects of chemically active gaseous radicals and physical ion bombardment. Other dry etching methods include spontaneous chemical etching (E.g. XeF<sub>2</sub> etching) and ion beam etching.