Espoo 2008

# DYNAMIC ANALYSIS AND QFT-BASED ROBUST CONTROL DESIGN OF SWITCHED-MODE POWER CONVERTERS

Ali Al.Towati

TEKNILLINEN KORKEAKOULU TEKNISKA HÖGSKOLAN HELSINKI UNIVERSITY OF TECHNOLOGY TECHNISCHE UNIVERSITÄT HELSINKI UNIVERSITE DE TECHNOLOGIE D'HELSINKI Espoo September 2008

## DYNAMIC ANALYSIS AND QFT-BASED ROBUST CONTROL DESIGN OF SWITCHED-MODE POWER CONVERTERS

#### Ali Al.Towati

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Faculty of Electronics, Communications and Automation, for public examination and debate in Auditorium AS1 at Helsinki University of Technology (Espoo, Finland) on the 21st of October, 2008, at 12 noon.

Helsinki University of Technology Faculty of Electronics, Communications and Automation Department of Automation and Systems Technology Distribution: Helsinki University of Technology Department of Automation and Systems Technology P.O. Box 5500 FI-02015 TKK, Finland Tel. +358-9-451 5201 Fax. +358-9-451 5208 E-mail: control.engineering@tkk.fi http://autsys.tkk.fi/

ISBN 978-951-22-9574-6 (printed) ISBN 978-951-22-9575-3 (pdf) ISSN 0356-0872

Yliopistopaino Helsinki 2008

Available on net at http://lib.tkk.fi/Diss/2008/isbn9789512295753

| ABSTRACT OF DOCTORAL DISS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | SERTATION           | HELSINKI UNIVERSITY OF TECHNOLOGY<br>P.O. BOX 1000, FI-02015 TKK<br>http://www.tkk.fi |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------------------------|--|--|

| Author Ali Al.Towati                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |                                                                                       |  |  |

| Name of the dissertation<br>Dynamic Analysis and QF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | T-Based Robust Con  | trol Design of Switched-Mode Power Converters                                         |  |  |

| Manuscript submitted 11.6.2008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     | Manuscript revised 8.9.2008                                                           |  |  |

| Date of the defence 21.10.2008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                     |                                                                                       |  |  |

| Monograph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                     | Article dissertation (summary + original articles)                                    |  |  |

| Faculty Electronics, Con                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | nmunications and Au | itomation                                                                             |  |  |

| Department Automation and                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Systems Technology  | 1                                                                                     |  |  |

| Field of research Control Enginee                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ring                |                                                                                       |  |  |

| Opponent(s) Prof. Riku Pöllänen and Dr. Mikko Hankaniemi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |                                                                                       |  |  |

| Supervisor Prof. Heikki Koivo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                     |                                                                                       |  |  |

| Instructors Prof. Teuvo Suntio and Dr. Kai Zenger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |                                                                                       |  |  |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                     |                                                                                       |  |  |

| The use of switched-mode power converters is continuously growing both in power electronics products and systems, e.g. in Telecom applications, commercial grid systems etc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                     |                                                                                       |  |  |

| The switching converters are required to provide robust behavior and to operate without instability under a variety of operation conditions. Hence the converter system may be subject to disturbances due to load, input voltage, and system parameter variations. In the thesis a robust control design procedure based on the QFT method (Quantitative Feedback Theory) is applied successfully for switching-mode DC-DC converters in order to achieve robust output in spite of different uncertainties. Simulation results are presented to demonstrate and validate the control design, showing good dynamic performance of the QFT controller. |                     |                                                                                       |  |  |

| desirable to divide the system into manageable subsystems which can then be designed independently. The subsystems may then be connected together to form a complete integrated system. One of the major difficulties in integrated subsystems is the stability performance degradation due to the interaction between the subsystems.                                                                                                                                                                                                                                                                                                                 |                     |                                                                                       |  |  |

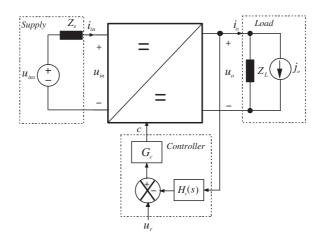

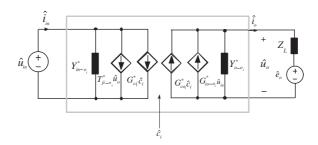

A formalism to analyze the interaction between subsystems using the unterminated two-port small-signal representation is derived. Two-port models are first defined as unterminated models, where the effect of load is excluded but may be easily included using the developed reflection rules. The use of the impedance ratio as a minor loop gain, which can be used to check system stability, is outlined.

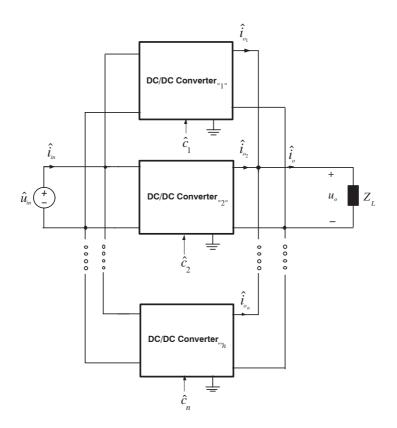

Recently, there has been increasing interest in the parallel operation of DC-DC converters for reasons of increasing system reliability, facilitating system maintenance, allowing for future expansion, and reducing system design cost. However, paralleled DC-DC converters require a systematic modeling methodology and a categorical current-sharing mechanism to improve a performance of the overall system.

In order to achieve desirable characteristics when operating converter modules in parallel, a unified systematic approached for modeling of parallel DC-DC converter with current-sharing control, is proposed, developed, and analyzed.

| Keywords Switched-mode converters, QFT-based robust control, subsystem interaction, current-sharing control. |                                                                                    |  |  |  |

|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| ISBN (printed)                                                                                               | 978-951-22-9574-6 ISSN (printed) 0356-0872                                         |  |  |  |

| ISBN (pdf)                                                                                                   | 978-951-22-9575-3 ISSN (pdf)                                                       |  |  |  |

| Language                                                                                                     | English Number of pages 145                                                        |  |  |  |

| Publisher                                                                                                    | Helsinki University of Technology, Department of Automation and Systems Technology |  |  |  |

| Print distribution Helsinki University of Technology, Department of Automation and Systems Technology        |                                                                                    |  |  |  |

| The dissertation can be read at http://lib.tkk.fi/Diss/2008/isbn9789512295753                                |                                                                                    |  |  |  |

### Preface

This research work has been carried out at the Department of Automation and Systems Technology of Helsinki University of Technology.

First of all I would like to thank my God for blessing me with the ability to complete this work successfully.

I am indebted to my supervisor *Professor Heikki Koivo* for giving me the opportunity to work in his laboratory and providing me with an excellent atmosphere for doing research. I am deeply grateful to my instructor, *Professor Teuvo Suntio* from Tampere University of Technology for his invaluable guidance and patience during the process. I wish to express my sincere appreciation to *D.Sc. Kai Zenger* for his support and all the time he spent with me discussing this work. I am grateful to the pre-examiners Prof. Pertti Silventoinen and Dr. Mikko Hankaniemi for their valuable comments and recommendations.

I would also like to thank all the people in the Control Engineering Group for creating an enjoyable atmosphere to work. The Academy of Finland and the Research Foundation of Helsinki University of Technology through different technology programs have supported this research financially, which are gratefully acknowledged. In addition, the grants received from Finnish Society of Automation, Elektroniikkainsinöörien Säätiö, Finnish Cultural Foundation and Alfred Kordelin Säätiö are gratefully acknowledged.

Deepest gratitude to my family and relatives for their continuous support. Finally, my dearest thanks go to my wife Salha, my daughters Fatma and Arwa for providing me with their everlasting love and confidence. Great thanks to all friends here in Finland and in Libya or elsewhere for their care and commitment.

Espoo, September, 2008

Ali Al.Towati

"This work is dedicated to the memory of my father, Mohammed, who has always been very supportive, patient, understanding, and encouraging. To the memories of my dearest brother, Elmuntaser and my beloved sister, Nafeesa, who have both passed away a few months ago, you will always have a place in my heart. It is also dedicated to my mother Fatma, for her continuous love, support, and encouragement"

## List of Symbols

| ( <i>A</i> , <i>B</i> , <i>C</i> , <i>D</i> ) | State-space realization of a linear system                      |

|-----------------------------------------------|-----------------------------------------------------------------|

| $B(\omega)$                                   | QFT bound                                                       |

| c                                             | Control variable                                                |

| C                                             | Capacitor or capacitance                                        |

| $C_f$                                         | Filter capacitance                                              |

| d                                             | Duty cycle                                                      |

| D                                             | Steady state duty cycle                                         |

| $D_i$                                         | Diode                                                           |

| $d_s$                                         | Output disturbance signal                                       |

| $e_o$                                         | Voltage-source in current-output converter                      |

| F                                             | Prefilter                                                       |

| $f_o$                                         | Filter resonance frequency                                      |

| $f_c$                                         | Crossover frequency                                             |

| $f_f$                                         | The resonant frequency of output averaging filter               |

| $f_{g}$                                       | Feedforward gain from the input voltage                         |

| $f_s$                                         | Switching frequency                                             |

| $F_m$                                         | Duty cycle gain                                                 |

| $f_v$                                         | Feedback gain from the output voltage                           |

| $G_c$                                         | Controller transfer function                                    |

| $G_{ci}$                                      | Control-to-input transfer function                              |

| $G_{cid}$                                     | Cross-coupling transfer function                                |

| $G_{cL}$                                      | Transfer function from control-to-inductor current              |

| $G_{co}$                                      | Control-to-output transfer function                             |

| $G_{csc}$                                     | Current-sharing controller transfer function                    |

| $G_D$                                         | Output disturbance model                                        |

| $G_{io-o}$                                    | Open-loop line-to-output transfer function                      |

| $G_{ic-o}$                                    | Transfer function from line-to-capacitor voltage                |

| $G_{iL-o}$                                    | Transfer function from line-to-inductor current                 |

| $G_{io-c}$                                    | Closed-loop line-to-output transfer function                    |

| $G_{io-f}$                                    | Filter forward-voltage transfer function                        |

| $G_{jc-o}$                                    | Transfer function from output current-to-capacitor voltage      |

| $G_{jL-o}$                                    | Transfer function from output-to-inductor current               |

| $G_a$                                         | Gain factor matching the voltage control signal to the internal |

| **                                            | control signal                                                  |

| $H_{se}$                                      | Sensor gain                                                     |

| $H_{\infty}$                                  | Hardy space of transfer functions with bounded $\infty$ -norm   |

| $H_v$                                         | Voltage-sensing gain                                            |

| $i_C$             | Capacitor current                                                 |

|-------------------|-------------------------------------------------------------------|

| $i_{co}$          | Control command                                                   |

| $i_{in}$          | Input current                                                     |

| $i_{inc}$         | Bus current                                                       |

| $i_{L}^{i_{inc}}$ | Inductor current                                                  |

|                   | Peak of inductor current                                          |

| $i_p$             | Output current                                                    |

| i <sub>o</sub>    | ±                                                                 |

| I <sub>in</sub>   | DC-value of input current                                         |

| $I_L$             | DC-value of inductor current                                      |

| $I_o$             | DC-value of output current                                        |

| j(s)              | Gain of controlled current source in canonical equivalent circuit |

| $j_N$             | Norton current sink                                               |

| j <sub>o</sub>    | Load current sink                                                 |

| $J_o$             | DC-value of load current sink                                     |

| K                 | Controller gain                                                   |

|                   | Inductor or inductance                                            |

| $L_g(s)$          | Loop gain                                                         |

| $L_{g_{nom}}(s)$  | Nominal loop gain                                                 |

| $L_c(s)$          | Current loop gain                                                 |

| $L_{co}(s)$       | Current-output loop gain                                          |

| $L_{csc}(s)$      | Current-sharing loop gain                                         |

| $L_m(s)$          | Minor loop gain                                                   |

| $L_v(s)$          | Voltage loop gain                                                 |

| $m_1$             | Inductor current slope when the switch is ON                      |

| $m_2$             | Inductor current slope when the switch is OFF                     |

| M(D)              | Voltage conversion ratio                                          |

| $M_c$             | Compensating ramp slope                                           |

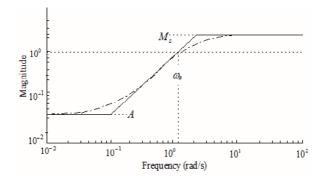

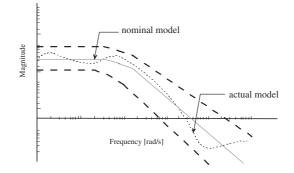

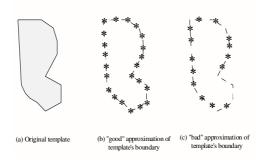

| $M_s$             | Maximum peak magnitude                                            |

| n                 | measured noise                                                    |

| N                 | Number of dc-dc converters in parallel                            |

| $Q_c$             | Charge received by capacitor                                      |

| $Q_f$             | Quality Factor                                                    |

| P                 | Plant model                                                       |

| $P_{in}$          | Converter input power                                             |

| $P_o$             | Converter output power                                            |

| $r_C$             | Equivalent series resistance of capacitor of the converter        |

| $r_{CF}$          | Equivalent series resistance of capacitor of the filter           |

| $r_d$             | The dynamic resistance associated to diode                        |

| $r_{rds}$         | The MOSFET on-time channel resistance                             |

| $r_L$             | Equivalent series resistance of inductor of the converter         |

| $r_{LF}$          | Equivalent series resistance of inductor of the filter            |

| R                 | Resistance or resistor                                            |

| $R_{eq}$          | Equivalent resistance                                             |

| $R_{in}$          | Converter input resistance                                        |

| $R_L$             | Resistive load                                                    |

| $R_s$             | Current-sensing resistor                                          |

| $S_{\alpha^T}$    | Switch                                                            |

| $S_P^T$           | Sensitivity function                                              |

| t                 | Time in seconds                                                   |

|                   |                                                                   |

| +               | ON-time of the switch                                           |

|-----------------|-----------------------------------------------------------------|

| $t_{on}$        | OF-time of the switch                                           |

| $t_{of}$ $T$    | Complementary sensitivity function                              |

| -               |                                                                 |

| $T_{ji-o}$      | Open-loop input susceptibility to load changes                  |

| $T_{ji-c}$      | Closed-loop input susceptibility to load changes                |

| $T_{ji-f}$      | Filter reverse-current transfer function                        |

| $T_L$           | Lower tracking bound                                            |

| $T_s$           | Switching time interval                                         |

| $T_U$           | Upper tracking bound                                            |

| $u_c$           | Output of voltage controller                                    |

| $u_C$           | Output capacitor voltage                                        |

| $u_{CF}$        | Filter output capacitor voltage                                 |

| $u_d$           | Plant input                                                     |

| $u_L$           | Inductor voltage                                                |

| $u_{in}$        | Input voltage                                                   |

| $u_{inc}$       | Filter output voltage                                           |

| $u_o$           | Output voltage                                                  |

| $u_r$           | Reference signal                                                |

| U               | Input vector                                                    |

| $U_C$           | DC-value of capacitor voltage                                   |

| $U_D$           | Voltage loss of the diode                                       |

| $U_{in}$        | DC-value of input voltage                                       |

| $U_o$           | DC-value of output voltage                                      |

| $V_{st}$        | Sawtooth waveform amplitude, i.e. PWM gain                      |

| $W_s(s)$        | Weighting function                                              |

| X               | State-variable vector                                           |

| y               | Plant output                                                    |

| Y               | Output vector                                                   |

| $Y_{in-\infty}$ | Input admittance of ideally controlled converter                |

| $Y_{in-o}$      | Open-loop input admittance                                      |

| $Y_{in-c}$      | Closed-loop input admittance                                    |

| $Y_{in-f}$      | Filter input admittance                                         |

| $Y_{in-sc}$     | Input admittance of nulled output voltage                       |

| $Y_{o-csc}$     | Current-sharing output admittance of slave module               |

| $Z_{in}$        | Input impedance                                                 |

| $Z_{in-o}$      | Open-loop input impedance                                       |

| $Z_{in-c}$      | Closed-loop input impedance                                     |

| $Z_L$           | Load impedance                                                  |

| $Z_{L_v}$       | Impedance of parallel-connected output capacitor and load       |

| -               | impedance                                                       |

| $Z_o$           | Output impedance                                                |

| $Z_{o-o}$       | Open-loop output impedance                                      |

| $Z_{o-c}$       | Closed-loop output impedance                                    |

| $Z_{o-f}$       | Filter output impedance                                         |

| $Z_s$           | Source impedance                                                |

| $\Delta i_L$    | The difference between a peak inductor current and its averaged |

| $\gamma$        | Robust stability bound                                          |

| $\omega_B$      | Bandwidth frequency                                             |

|                 |                                                                 |

## List of Abbreviations

| AC            | Alternating current                               |

|---------------|---------------------------------------------------|

| AC/DC         | AC to DC rectifier                                |

| BW            | Bandwidth                                         |

| CCM           | Continuous conduction mode                        |

| $\mathbf{CS}$ | Current sharing                                   |

| DC            | Direct current                                    |

| DC-DC         | DC to DC converter                                |

| DCM           | Discontinuous-conduction mode                     |

| DPA           | Distributed power architecture                    |

| DPS           | Distributed power supply                          |

| DSP           | Digital signal processor                          |

| EET           | Extra-element-theorem                             |

| EMI           | Electromagnetic interference                      |

| ESR           | Equivalent series resistance                      |

| GM            | Gain margin                                       |

| GMPM          | Gain margin and phase margin criterion            |

| GUI           | Graphical user interface                          |

| KCL           | Kirchhoff's Current Law                           |

| KVL           | Kirchhoff's Voltage Law                           |

| LC            | Inductance-capacitance                            |

| LCR           | Inductance-capacitance-resistance                 |

| m LFT         | Linear fractional transformation                  |

| LTI           | Linear time invariant                             |

| LHP           | Left-hand plane                                   |

| LQG           | Linear Quadratic Gaussian                         |

| MIMO          | Multi input/multi output                          |

| MOSFET        | Metal-oxide-semiconductor field-effect transistor |

| MSC           | Master-Slave Control                              |

| NRO           | Negative-resistance-oscillator                    |

| PCMC          | Peak current-mode control                         |

| PI            | Proportional-integral control                     |

| PFC           | Power factor correction                           |

| $_{\rm PM}$   | Phase margin                                      |

| PWM           | Pulse-width modulator                             |

| QFT           | Quantitative feedback theory                      |

| RHPZ          | Right-hand plane zero                             |

|               |                                                   |

| SISO | Single input/single output  |

|------|-----------------------------|

| SMPS | Switching-mode power supply |

| SSA  | State-space averaging       |

| TODF | Two degree of freedom       |

| VMC  | Voltage-mode control        |

## Contents

| A  | bstra                                                        | ict                                                                                         | iii                                  |

|----|--------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------|

| Pı | refac                                                        | e                                                                                           | $\mathbf{v}$                         |

| Li | st of                                                        | Symbols                                                                                     | ix                                   |

| Li | st of                                                        | Abbreviations                                                                               | xiii                                 |

| C  | onter                                                        | nts                                                                                         | $\mathbf{x}\mathbf{v}$               |

| 1  | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6<br>1.7<br>1.8 | Background                                                                                  | 1<br>1<br>2<br>3<br>3<br>3<br>4<br>4 |

| 2  | 2.1                                                          | -DC Switching Converters The Buck DC-DC Converter                                           | <b>7</b><br>8                        |

|    | 2.2<br>2.3<br>2.4                                            | The Boost DC-DC Converter                                                                   | 8<br>9<br>9<br>10                    |

|    | 2.5                                                          | 2.4.2       Discontinuous Conduction Mode DCM         Control Structures of DC-DC Converter | 10<br>10<br>11<br>11                 |

|    | 2.6                                                          | Modeling of DC-DC Switching Power Converters                                                | 11<br>12<br>15                       |

|    | 2.7                                                          | Modeling of Pulse-Width Modulator                                                           | 20<br>20<br>25                       |

| 3        | Rob   | oust Control Design for Switching-Mode Power Converters                  | 33  |

|----------|-------|--------------------------------------------------------------------------|-----|

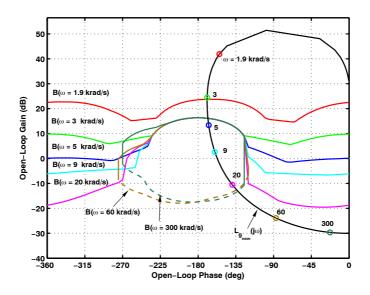

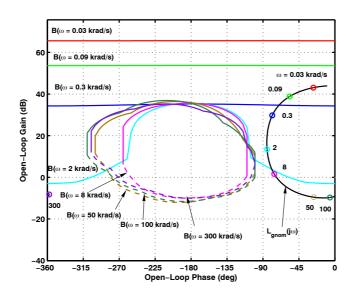

|          | 3.1   | Quantitative Feedback Theory (QFT)                                       | 34  |

|          |       | 3.1.1 Closed-Loop Formulation                                            | 34  |

|          |       | 3.1.2 Robust Performance                                                 | 36  |

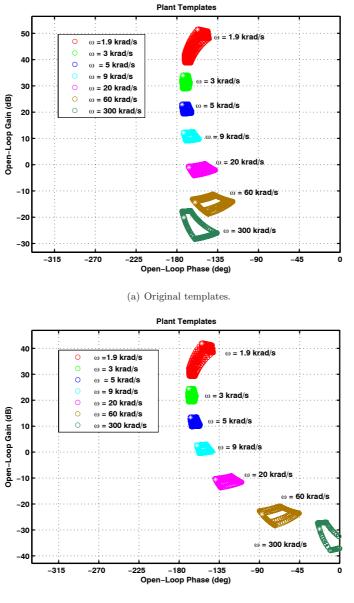

|          |       | 3.1.3 Uncertainty Model and Plant Templates                              | 38  |

|          |       | 3.1.4 QFT Design Procedure                                               | 39  |

|          |       | 3.1.5 QFT Design for Uncertain Non-minimum Phase Systems                 | 41  |

|          | 3.2   | QFT-Based Robust Controller Design for Switching-Mode Power Converters . | 43  |

|          |       | 3.2.1 Voltage-Mode-Controlled Converter                                  | 43  |

|          |       | 3.2.2 Peak-Current-Mode-Controlled Converter                             | 57  |

|          | 3.3   | QFT-Based Robust Controller Design for Non-minimum Phase Converters      | 66  |

|          |       | 3.3.1 QFT-Based Robust Controller Design for a Boost Converter           | 66  |

|          |       | 3.3.2 QFT-Based Robust Controller Design for a Buck-Boost Converter      | 78  |

| 4        | Sub   | osystem Interaction Analysis                                             | 85  |

|          | 4.1   | Two-Port Network                                                         | 86  |

|          |       | 4.1.1 Unterminated Modeling Approach                                     | 86  |

|          | 4.2   | System Stability and Performance                                         | 87  |

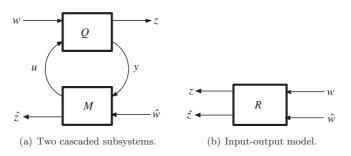

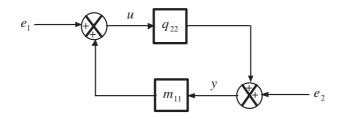

|          |       | 4.2.1 Linear fractional transformations: The matrix star product         | 87  |

|          |       | 4.2.2 Internal Stability                                                 | 89  |

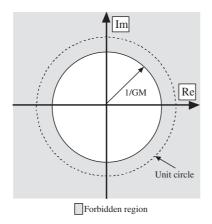

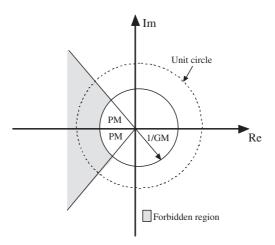

|          |       | 4.2.3 Forbidden region concept                                           | 90  |

|          | 4.3   | Load and Supply Interaction Analysis                                     | 91  |

|          |       | 4.3.1 Load Interaction Analysis                                          |     |

|          |       | 4.3.2 Source Interaction Analysis                                        | 101 |

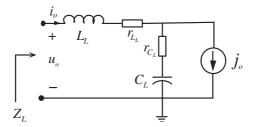

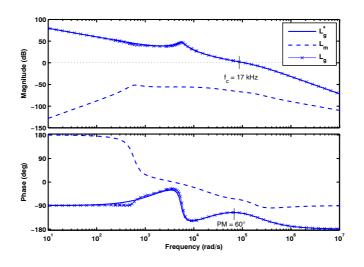

|          | 4.4   | Input Filter Interactions in Switched-Mode Power Converters              | 102 |

|          |       | 4.4.1 EMI Filters for Switching-Mode Power Converters                    | 102 |

|          |       | 4.4.2 Nature of the Oscillation Problem                                  | 104 |

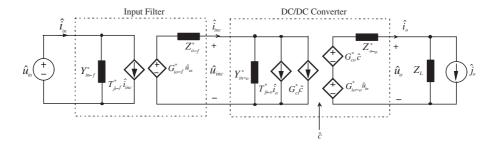

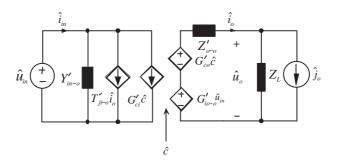

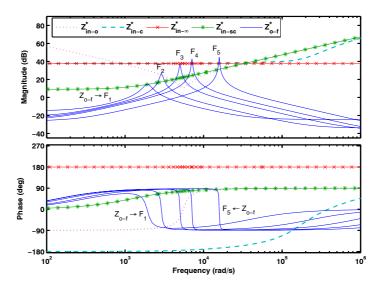

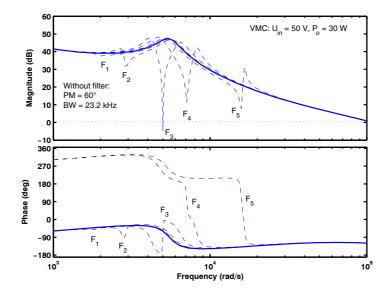

|          |       | 4.4.3 Application of Two-Port Representation                             | 105 |

| <b>5</b> | Dyr   | namics Analysis of Paralleled DC-DC Converters                           | 117 |

|          | 5.1   | General Constraints on Paralleling DC-DC Converters                      |     |

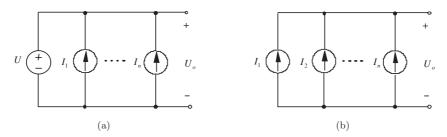

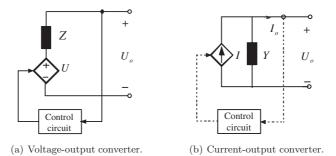

|          |       | 5.1.1 Current-Output Converters                                          |     |

|          |       | 5.1.2 Equivalent Circuit Models for DC-DC Switching Converters           | 120 |

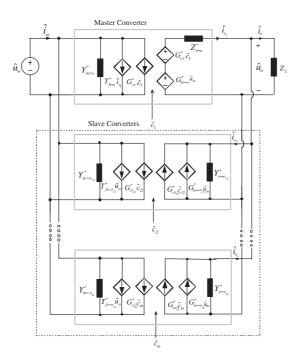

|          | 5.2   | Paralleled DC-DC Converters with Master-Slave Control MSC                | 121 |

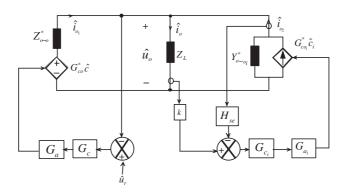

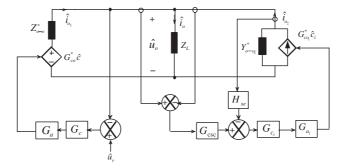

|          |       | 5.2.1 Modeling of Multimodule Converters with MSC                        |     |

|          |       | 5.2.2 QFT-Based Robust Controller Design                                 | 125 |

| 6        | Con   |                                                                          | 135 |

|          | 6.1   | Summary                                                                  |     |

|          | 6.2   | Future Prospects                                                         | 137 |

| Bi       | bliog | graphy                                                                   | 139 |

| A        | Ap    | 1                                                                        | A-1 |

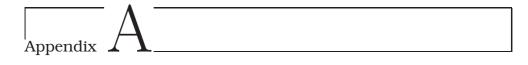

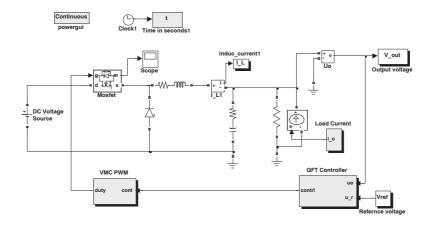

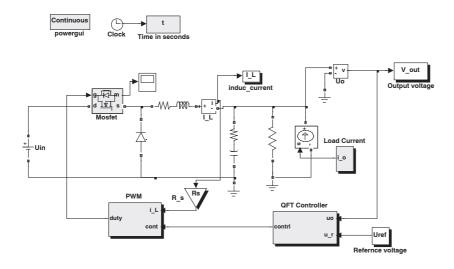

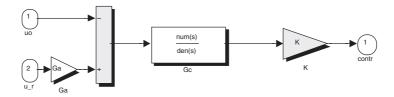

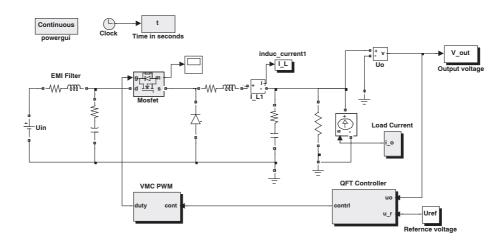

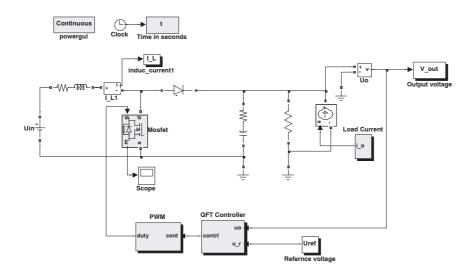

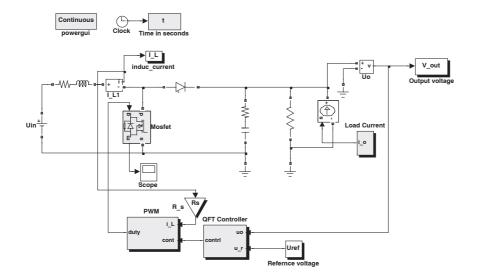

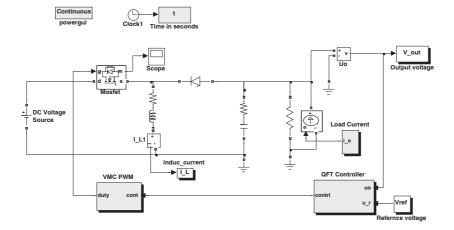

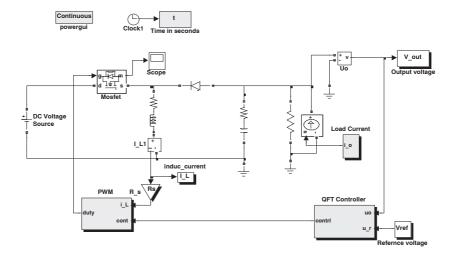

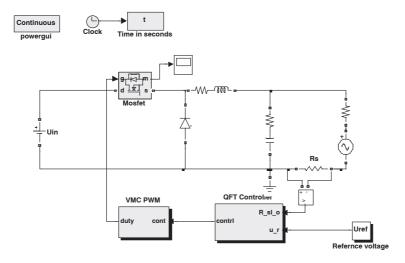

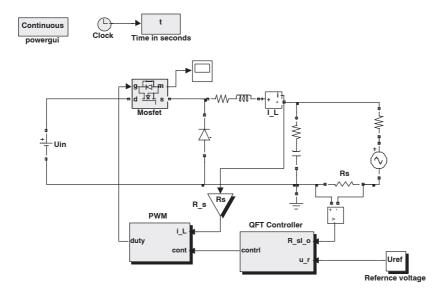

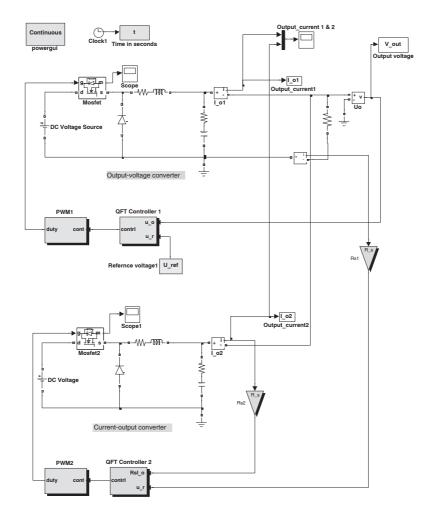

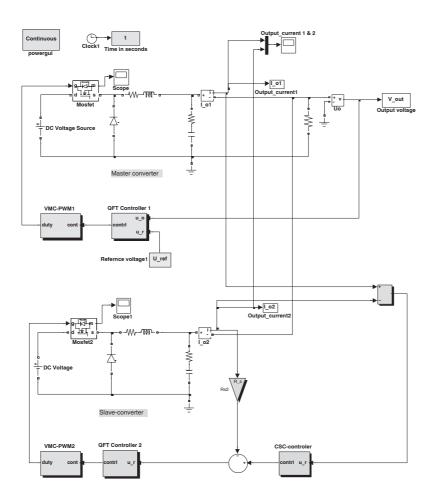

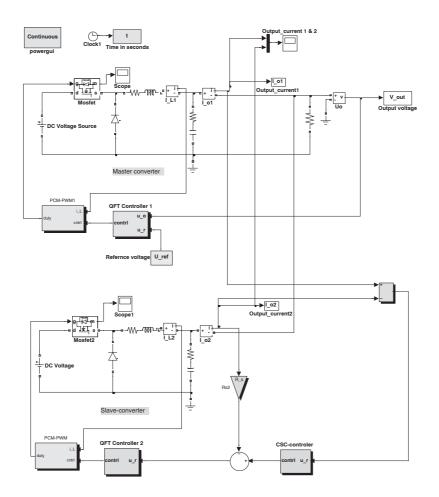

|          | A.1   | $Matlab^{TM}/Simulink Simulation Setup$                                  |     |

|          |       | A.1.1 Single Output-Voltage DC-DC Converters                             |     |

|          |       | A.1.2 Single Output-Current DC-DC Converters                             |     |

|          |       | A.1.3 Multimodule DC-DC Parallel Converters with MSC                     | A-7 |

## Chapter

### Introduction

#### 1.1 Background

The electric power is not normally used in the form in which it was produced or distributed. Practically all electronic systems require some form of power conversion. A device which transfers electric energy from the source to the load using electronic circuits is called a Power Supply, although power converter would be a more accurate term for such a device. A typical application of a power supply is to convert utility AC voltage into regulated DC voltages required for electronic equipment. Nowadays in most power supplies providing more than a few watts the energy flow is controlled with power semiconductors that are continuously switching on and off with high frequency. Such devices are called Switch Mode Power Supplies or SMPS. In general, SMPS can be classified into four types according to the form of input and output voltages: AC to DC (off-line power supply or a rectifier); DC to DC (voltage converter); AC to AC (frequency changer or cycloconverter); DC to AC (inverter). In this thesis, the modeling, control design challenges and subsystems interaction issues will be treated only for DC-DC converters.

Switching-mode power-electronic converters are nonlinear dynamical systems. The nonlinearities arise primarily due to switching, power devices, and passive components such as inductors, capacitors and parasitics. SMPS's represent different circuit topologies or configurations within each switching cycle. For the continuous conduction mode, there are two topologies. For the discontinuous conduction mode of operation, a third configuration has to be added to yield a total of three topologies. In each configuration, the system can be described by linear state equations. Switching between the different topologies will vary from cycle to cycle depending on the output of the system, and this complicates the analysis further.

The static conservation properties of the elementary switching converters (buck, boost, and buck-boost) have been thoroughly understood since the early 1970s. This is one of the main reasons of their ever-increasing number of applications in electrical energy conversion. However, the complete dynamics behavior of switching power converters still has to be further understood and improved. This is not possible without an in-depth understanding of the operation of such circuits and without easy-to-use and accurate models.

#### 1.2 Modeling of Switching DC-DC Converters

Modeling and analysis of switching DC-DC converters can be either numerical or analytical. In numerical techniques, several algorithms or circuit simulators are used to produce quantitative results. These methods are easy to use. They posses accuracy and universality and they are applicable when no equivalent model is available. However, they are fail to provide the design insight needed to understand the behavior of switching converters. In contrast to numerical techniques, analytic techniques provide analytic expressions representing the operation and performance of the converters.

The most popular continuous-time technique is the small-signal analysis, which uses either circuit averaging [1], state-space averaging [2], or PWM switch modeling [3, 4]. In [1] analytical techniques were developed to represent buck, boost and buck-boost converters by approximate continuous models. Simple analytical expressions in terms of the circuit components were derived to characterize the low-frequency response of such systems. In [2] the above technique was generalized by introducing the state-space averaging method. The state-space descriptions of each switching mode were replaced by a single state-space description, hence eliminating the switching process from consideration and representing the average effect of the switched networks during operation cycle. The system was further simplified by perturbing the averaged system and then linearizing the resulting perturbed equations around the steady-state values. After a considerable amount of matrix manipulations, the system characteristics such as input impedance, output impedance, line-to-output transfer function, and control to-output characteristics, were obtained.

#### 1.3 Control Design of Switching DC-DC Converters

The converters are required to provide robust behavior and to operate without instability under a variety of operation conditions. Hence the converter system may be subject to the disturbances of load, input voltage, and system configuration variations.

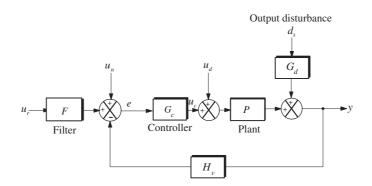

To improve the dynamic performances of converters, closed-loop control is indispensable. Generally, the linear small-signal model obtained using state-averaging and linearization techniques around an operating point is adopted for the controller design. However, since the model is dependent on the operating conditions and system configuration, the controller with fixed parameters (e.g., the PI and optimal controllers) which are adequate under the designed condition may not be so for other operating conditions. It is well known that robust control technic is one of the most effective techniques for dealing with parameter variations.

Several attempts have been made to apply robust control theory for DC-DC power converters. The linear quadratic Gaussian/loop transfer recovery methodology was used in [5] to design a controller for a series parallel resonant converter. In [6], a controller for a buckboost converter with peak current control was designed using the  $\mu$ -synthesis procedure. In [7, 8],  $H_{\infty}$  approach was applied to design controllers for boost and buck-boost converters. Nonlinear  $H_{\infty}$ -control theory has been applied to regulate a PWM Cuk converter under parameter uncertainties and exogenous inputs which generate the reference trajectories [9]. In [10],  $H_{\infty}$  and  $\mu$ -synthesis control methods have been applied to Telecom power supplies. But most of the existing robust control techniques are too complex theoretically for practical engineers to understand. It follows that optimal performance is generally not achieved, because traditional control methods design are used in practice.

This thesis proposes the use of robust control techniques to derive a controller for dc-dc converters, which are able to cope with the parameter variations in the converter's power stage. In particular, this thesis proposes the use of "Quantitative Feedback Theory" or QFT approach [11] which operates on the frequency domain to design a robust output voltage controller for switching-mode power converters. It was introduced by Isaac Horowitz in 1960s. This technique takes into account the uncertainty that may be present in the process and its environment, and establishes a balance between the complexity of controller and

complexity of design. It also differs in the way in which uncertainty is characterized as gain-phase variations or templates in the Nichols chart.

#### 1.4 Stability and Subsystems Interactions

Stability is the most important requirement for switching-mode power supply systems. The issue of stability is closely related to the EMI filter design for subsystems powered through switching power converters. Improper designs of the input filter for such subsystems may result in undesirable interactions [12, 13].

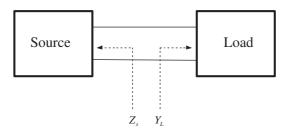

Considerable interest is focused on evaluating the stability of subsystem interactions in distributed power systems. Usually, the impedance ratio stability criterion suggested in [12] is used to analyze the stability of interactions between two interconnecting subsystems. For example, the stability of a spacecraft DC distributed power system is addressed in [14]. Stability analysis for a system with a source converter and one or more load converters is given in [15, 16]. The design rules are usually based on the separation of the impedance levels at the interface of the subsystems. After [12, 17], many efforts have been taken in defining less conservative rules, see e.g. [18].

All these examples covered relatively simple system configurations, with an ideal voltage source, one source converter, and one or more load converters with resistive loads. The examples represented particular case studies rather than universal analysis tools. The results were obtained by tedious analytical developments for a particular system configuration rather than applying computer-aided analysis techniques to easily reconfigurable global system model.

#### 1.5 Modeling and Dynamics Analysis of Multimodule DC-DC Converters

As a viable solution to demanding power requirements, power supplies for distributed power applications employ several converter modules in parallel. The resulting multimodule converters offer efficient processing of high current and built-in redundancy [19, 20, 21, 22]. However, standard converter modules may not have identical characteristic, which causes unbalance of current sharing. Modules delivering large currents will have their life-time shortened and the system reliability degraded [21]. Many factors contribute to the fact that modules not being identical, such as component tolerances, non-identical electrical conductors connected from the converters to current distribution and so on. Therefore, a unified consistent modeling approach is necessary to understand the dynamic behavior of the power supply and also to design a controller that regulates the output voltage and achieves balanced current distribution of the converter.

With current-sharing control, the output current of a multimodule converter is equally distributed among parallel modules, thereby improving reliability and reducing current stress on switching devices. Furthermore, the parallel processing of the load current provides fault tolerance to the system against the failure of a single module.

#### 1.6 Research Objectives

Objectives of this thesis can roughly be divided into the following main categories:

• To give clear physical insight into the concept of switching-mode power converters, and to present a unified modeling methodology of the buck, boost and buck-boost convert-

ers operating in continuous-conduction mode (CCM) and discontinuous-conduction mode (DCM).

- To implement a robust control approaches (i.e. QFT) in synthesizing robust controllers for DC-DC switching power converters in order to improve their dynamic performance by minimizing the effects of load disturbances over the specified region of plant uncertainties.

- To study the interaction of the subsystems in a distributed power supply system to ensure proper overall operation. The aim is to analyze the effect of the input filter and load on the dynamics of the converter. The main purpose is to develop design guidelines which prevent instabilities and performance degradations of the converter.

- To improve the performance characteristics of multimodule parallel DC-DC converter system through modeling, control design and simulation.

#### 1.7 Outline of the Thesis

The thesis is organized as follows: In Chapter 2, an overview of a switched-mode supply system is given, and the modeling methodology of the system is discussed. In Chapter 3, the Quantitative Feedback Theory (QFT) is applied successfully to design a robust controller for DC-DC buck, boost and buck-boost converters operating in continuous conduction mode (CCM) and discontinuous conduction mode (DCM). In Chapter 4, the use of two-port unterminated network representation is demonstrated. Subsystem impedance interactions and stability analysis for distributed power supply systems are analyzed. The guidelines for how to design an optimal input filter for a switching power supply application, which prevents instabilities and performance degradations of the converter, are presented.

In Chapter 5, the small-signal model of DC-DC paralleled converters with individual voltage loop and Master-Slave Control (MSC) circuit is developed using small-signal equivalent two-port model. The dynamic characteristics of the current-sharing loop is derived. A robust current-sharing controller which takes into account the stability and ensures distribution of currents among the modules is designed.

Conclusions are drawn and some further work considerations are presented in Chapter 6. Appendix A.1 gives some Simulink/SimPower Systems<sup>TM</sup> models which have been used to generate the results presented in the thesis.

The following notation is adopted: The capital letters denote the DC values of associated quantities, the "hatted" small letters the ac or perturbed value excluding the switching ripple, and the small letters denote the total values. In equations the notation for the time variable t is suppressed, when no confusion is possible, e.g. i instead of i(t) etc. The calculus is usually done in Laplace domain, which is not expressed explicitly except in the special cases when there is a chance of confusion.

#### 1.8 Thesis's Contribution

The main contributions of this thesis can be summarized as follows:

• A new application of QFT to the control design of DC-DC switching-mode power converters is presented and examined for all basic converters operating in CCM and DCM in VMC and PCMC configurations.

- The analysis and simulation results show the practical applicability and performance of QFT in power converters.

- Subsystem interaction and stability problems for switching-mode power converter systems are illustrated and analyzed. In general, the interaction problem can be defined as the interaction between an unterminated component and its terminating subsystem.

- General formulations to determine the necessary conditions for system stability based on the impedance ratio inequality are derived.

- A unified systematic approach for modeling parallel DC-DC converters is proposed.

- A robust current-sharing controller, which ensures distribution of currents among the modules and grantees system stability, is designed using the QFT method.

# Chapter 2

## **DC-DC Switching Converters**

Modern electronic systems require high-quality, small, lightweight, reliable, and efficient power supplies. Linear power converters, whose principle of operation is based on a voltage or current divider, are inefficient. This is because they are limited to output voltages smaller than the input voltage, and also because their power density is low due to the low frequency (50 or 60 Hz) line transformers and filters needed. Linear converters can, however, provide a very high-quality output voltage. Their main area of application is at low power levels. Electronic devices in linear converters operate in their active (linear) modes, but at higher power levels switching converters are used. Switching converters use power electronic semiconductor switches in on and off states. Because there is a small power loss in those states (low voltage across a switch in the on state, zero current through a switch in the off state), switching converters can achieve high energy conversion efficiencies [23, 24].

The functions of dc-dc converters are:

- to convert a dc input voltage into a dc output voltage ;

- to regulate the dc output voltage against load and line variations; and

- to provide isolation between the input source and the load (isolation is not always required);

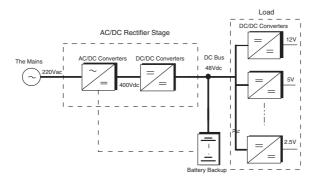

To power the new information technology equipment, the distributed power architecture (DPA) has been widely adopted in the industry [25, 26, 27]. In DPA, the load converters are placed near the loads. Therefore, the conversion from the high or medium voltage to low voltage is done locally in front of each load. This allows the use of very high switching frequency and guarantees a fast response to load current transients. Furthermore, the current ratings in the entire power supply system are not so high. An example of a typical distributed power system (DPS) telecom power system is shown in Fig. 2.1, [25]. There are two power processing stages. In the figure, the first stage is the AC-to-DC rectifier that converts the AC line voltage into a 48V DC bus. This stage consists of two parts. One part is the AC-to-DC converter that converts the AC line voltage into a nintermediate DC voltage (usually 400V). Also the power factor correction (PFC) is often included in this stage. However, Boost converter is usually used for this stage, because it is easier for input current shaping and it is suitable for high DC output voltage.

The other part is the DC-to-DC converter that converts the 400V DC to 48V DC. Electrical isolation is provided at this stage. Then the 48V bus is feeding the entire telecom load system. There is often a battery backup in the dc line, which powers the dc bus when the mains fails. In this case, the AC-to-DC rectifier should also be able to charge the battery when needed. The second level consists of DC-to-DC power converters that convert the 48V DC into tightly regulated logic voltage such as 12V, 5V, 3.3V or 2.5V.

Figure 2.1: Distributed power system architecture in a telecom application.

In this chapter, the fundamentals and earliest topologies - the buck, boost and buck-boost converters are analyzed. Their basic operation is described and the modeling methodology of the system is discussed and explained.

#### 2.1 The Buck DC-DC Converter

The buck converter is one of the simplest and mostly used among power converters: a chopper circuit that converts a dc input to a lower dc output voltage. Many switched-mode power supplies employ circuits closely related to the buck converter [28, 29].

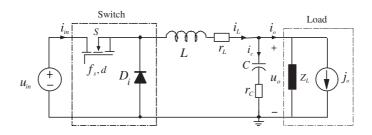

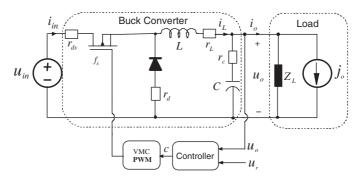

The basic open-loop buck converter connected to the load is shown in Fig. 2.2. The impedance  $Z_L$  with constant-current  $j_o$  represents the non-ideal load system. In practice, the switch circuit is realized using power semiconductor devices, such as MOSFET S and diode  $D_i$ . The switch S opens and closes periodically at the switching frequency  $f_s$ , with a duty ratio d (the fraction of time that the switch is on during the whole switching cycle  $T_s$ ,  $d = t_{on}/T_s$ ). When S is closed, the input voltage  $u_{in}$  is transferred to the LC low-pass filter. When S is open, the inductor maintains its current flow, forcing the diode  $D_i$  to conduct and grounding the input of the LC filter. Thus the filter sees a square wave between 0 and  $u_{in}$ . The cutoff frequency of the filter is much lower than  $f_s$ , removing most of the switching ripple and delivering a relatively smooth output voltage  $u_o$  to the load. The output voltage can be varied by changing the duty ratio d (by pulse-width modulation (PWM)).

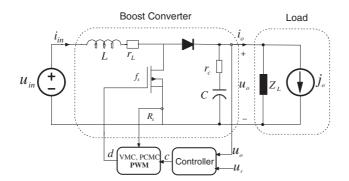

#### 2.2 The Boost DC-DC Converter

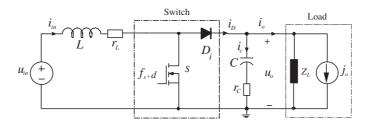

A boost converter is shown in Fig. 2.3. When the switch S is on, the diode is reverse biased, and the input supplies energy to the inductor. The load receives energy from the capacitor. When the switch S is off, the output stage receives energy from the inductor as well as from the input. The output voltage is always larger than the input voltage. Ideally it can be infinite, but in practice it is constrained to some maximum value. The input current is triangular waved, which means that the harmonic content of it is not so high as that of a buck converter.

Figure 2.2: The open-loop buck converter.

Figure 2.3: The open-loop boost converter.

#### 2.3 The Buck-Boost DC-DC Converter

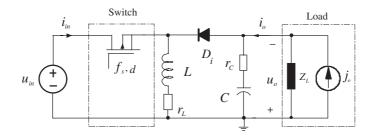

A buck-boost is mainly used in regulated DC power supplies, where a negative-polarity output may be desired with respect to the common terminal of the input voltage, and the output voltage can be either higher or lower than the input voltage, depending on the duty ratio [29]. A buck-boost converter is constructed by the cascade connection of the two basic converters: the buck converter and the boost converter as shown in Fig. 2.4. When the switch is on, the input provides energy to the inductor and the diode is reverse biased. When the switch is off, the load receives energy from the inductor. No energy is supplied by the input in this interval.

Figure 2.4: The open-loop buck-boost converter.

#### 2.4 Modes of Operation of the DC-DC Converter

The dc-dc converters can have two distinct modes of operation: (1) continuous conduction mode (CCM) and (2) discontinuous conduction mode. In practice, a converter may operate

in both modes, which have significantly different characteristics. Therefor, a converter and its control should be designed based on both modes of operation.

#### 2.4.1 Continuous Conduction Mode CCM

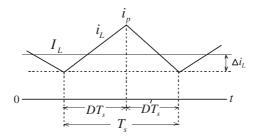

If the current through the inductor L never falls to zero during a commutation cycle, the converter is said to operate in continuous conduction mode (CCM). The inductor current waveforms in a converter can be seen in Fig. 2.5.

Figure 2.5: Inductor current waveform in CCM.

#### 2.4.2 Discontinuous Conduction Mode DCM

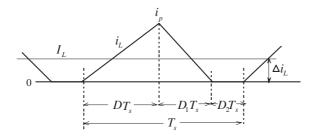

If the inductor current stays at zero level during a part of the off time, the converter is said to operate in discontinuous conduction mode (DCM).

The discontinuous conduction mode (DCM) of operation is often associated with light loads. In order to avoid the reverse recovery problem of the diode for low power applications, the designers usually prefer to operate the converter in DCM even for all loads. The inductor current waveforms of a converter is shown in Fig. 2.6.

Figure 2.6: Inductor current waveform in DCM.

#### 2.5 Control Structures of DC-DC Converter

In a dc-dc converter application, it is desired to obtain a constant output voltage despite of changes and disturbances in the input voltage or the load current. It is desired that essentially all of this variation fall within a specified range; however, this is not possible to achieve without the use of negative feedback. Given an input voltage, the average output voltage is controlled by controlling the switch on and off durations. One of the methods for controlling the output voltage employs switching at a constant frequency and adjusting the on duration of the switch to control the average output voltage. In this method, called the pulse-width modulation (PWM) switching, the switch duty ratio d is varied.

The two main control schemes used in practice are the voltage mode control (VMC) and peak-current mode control (PCMC).

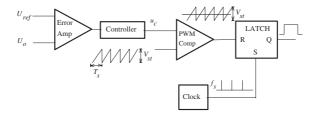

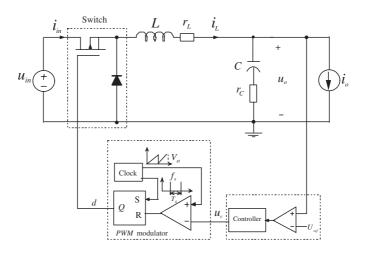

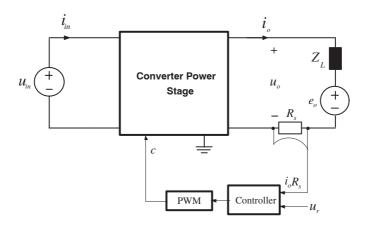

#### 2.5.1 Voltage-Mode Control VMC

The VMC scheme is the most popular and simple PWM control scheme. The basic voltage mode configuration is shown in Fig. 2.7. In voltage-mode control VMC, the output-voltage feedback loop tracks the output voltage variations and adjusts the duty cycle accordingly. The control voltage signal  $u_c$  is generated by amplifying the error between the output voltage and the reference voltage. The control voltage is then compared to the sawtooth waveform, having frequency  $f_s$  and peak voltage  $V_{st}$ . When the amplified error signal is larger than the sawtooth waveform, the switch control signal becomes high, causing the switch to turn ON. Otherwise, the switch is OFF.

The main drawback of voltage-mode control is the fact that, any change in the line or load must first be sensed as an output change and then compensated by the feedback loop. There is then an unavoidable delay in the compensation of these disturbances.

Figure 2.7: Voltage-mode control structure.

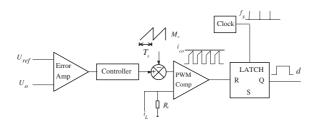

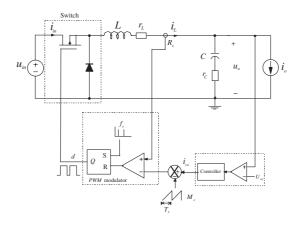

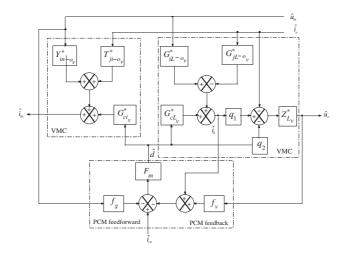

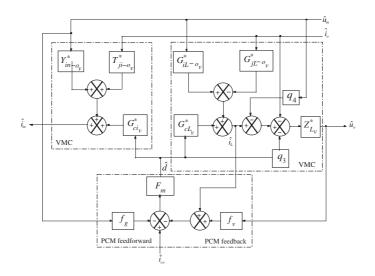

#### 2.5.2 Peak Current-Mode Control PCMC

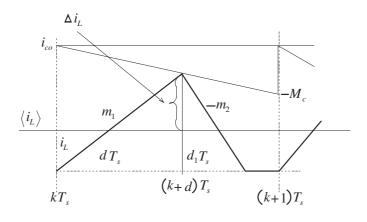

Peak current-mode control is a direct extension of voltage-mode control. In PCMC, an inner inductor-current feedback loop is added to improve the system dynamics. The inner loop forces the maximum value of the inductor current to track the control current, while the outer loop regulates the output voltage. The duty cycle is generated by comparing the inductor current and control current  $i_{co}$ .

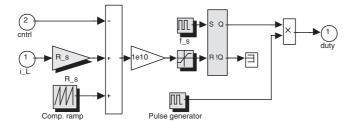

The main problem in current-mode control is the instability for duty cycles above 50%. The problem is well known and discussed in the literature, e.g. in [28]. This limitation can be removed by adding a compensation ramp  $M_c$ , to the control current signal, as shown in Fig. 2.8.

#### 2.6 Modeling of DC-DC Switching Power Converters

The inherent switching operation of power converters results in the circuit components being connected together in periodically changing configurations, in which each configuration is described by a separate set of equations. The transient analysis and control design for converters are therefore difficult since a number of equations must be solved in sequence.

Figure 2.8: Peak-current-mode control structure.

The technique of averaging provides a solution to this problem. A single equation may be formed to describe the converter approximately over a number of switching cycles by simply taking a linearly weighted average of the separate equations for each switched configuration of the converter. State space averaging [29, 23, 2, 24] is the most common averaging technique, and is used here to model the switching dc-dc converter.

#### 2.6.1 Continuous Conduction Mode CCM

The state-space averaging technique will be reviewed next to model all basic dc-dc converters (i.e., Buck, Boost and Buck-Boost converters) operating in continuous conduction mode CCM.

#### State-Space Averaging Technique

In state-space averaging (SSA), the switching circuit is divided into two (CCM) different structures. The derivatives of inductor currents and capacitor voltages are defined based on circuit theory for every substructure. These currents and voltages are averaged over one switching cycle. Consider the state space representation for a buck converter shown in Fig. 2.2. The voltage loss of the free-wheeling diode is assumed to be  $U_D$ .

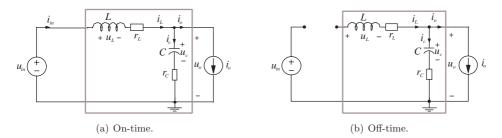

During the on time, the switch is on, and the diode is off. Therefore, the corresponding subcircuit is as shown in Fig. 2.9(a). Applying Kirchhoff's Voltage Law (KVL) and Kirchhoff's Current Law (KCL) we obtain

Figure 2.9: On and Off time subcircuits of buck converter.

$$\frac{d_{i_L}}{dt} = -\frac{r_C + r_L}{L} \cdot i_L - \frac{1}{L} \cdot u_C + \frac{1}{L} \cdot u_{in} + \frac{r_C}{L} \cdot i_o$$

(2.1a)

$$\frac{du_C}{dt} = \frac{1}{C} \cdot i_L - \frac{1}{C} \cdot i_o \tag{2.1b}$$

$$u_o = r_C \cdot i_L + u_C - r_C \cdot i_o \tag{2.1c}$$

$$i_{in} = i_L \tag{2.1d}$$

During the off time, the switch is off, and the diode is conducting. Therefore, the corresponding subcircuit is as shown in Fig. 2.9(b), Applying (KVL) and (KCL) we get, correspondingly

$$\frac{di_L}{dt} = -\frac{r_C + r_L}{L} \cdot i_L - \frac{1}{L} \cdot u_C - \frac{1}{L} \cdot U_D + \frac{r_C}{L} \cdot i_o \tag{2.2a}$$

$$\frac{du_C}{dt} = \frac{1}{C} \cdot i_L - \frac{1}{C} \cdot i_o \tag{2.2b}$$

$$u_o = r_C \cdot i_L + u_C - r_C \cdot i_o \tag{2.2c}$$

$$i_{in} = 0 \tag{2.2d}$$

The averaged state equations can be obtained by weighting the equations in (2.1) and (2.2) by their proportional time d, and d' = 1 - d respectively, and the resulting equations are added together

$$\frac{d\langle i_L\rangle}{dt} = -\frac{r_C + r_L}{L} \cdot \langle i_L\rangle - \frac{1}{L} \cdot \langle u_C\rangle + \frac{\langle d\rangle}{L} \cdot \langle u_{in}\rangle - \frac{\langle d'\rangle}{L} \cdot U_D + \frac{r_C}{L} \cdot \langle i_o\rangle$$

(2.3a)

$$\frac{d\langle u_C \rangle}{dt} = \frac{1}{C} \cdot \langle i_L \rangle - \frac{1}{C} \cdot \langle i_o \rangle \tag{2.3b}$$

$$\langle u_o \rangle = r_C \langle i_L \rangle + \langle u_C \rangle - r_C \cdot \langle i_o \rangle \tag{2.3c}$$

$$\langle i_{in} \rangle = \langle d \rangle \langle i_L \rangle$$

(2.3d)

where the symbol " $\langle \rangle$ " denote the averaging over an entire switching cycle.

#### Small Signal Model

The problem with the state equations (2.3) is that they are nonlinear. The nonlinearity is due to the multiplication of two time-varying components (i.e.  $d(t)u_{in}(t)$ ). This problem can be solved by linearizing the model in the vicinity of the steady-state operating point. The small-signal representation can be obtained from (2.3) by applying the linearization procedure presented in [31]. This procedure gives the linearized state-space representation as follows

$$\dot{\hat{\mathbf{x}}} = \mathbf{A}\hat{\mathbf{x}} + \mathbf{B}\hat{\mathbf{u}}$$

(2.4a)

$$\hat{\mathbf{y}} = \mathbf{C}\hat{\mathbf{x}} + \mathbf{D}\hat{\mathbf{u}} \tag{2.4b}$$

where the symbol ( $^{\wedge}$ ) over the variables means small perturbation around the corresponding steady-state value. The inductor current  $i_L$  and the capacitor voltage  $u_C$  are selected as the state variables, the input voltage  $u_{in}$ , the output current  $i_o$  and duty cycle d as the input variables, and the input current  $i_{in}$  and the output voltage  $u_o$  as the output variables,

$$\hat{\mathbf{x}} = \begin{bmatrix} \hat{i}_L & \hat{u}_C \end{bmatrix}^T, \hat{\mathbf{u}} = \begin{bmatrix} \hat{u}_{in} & \hat{i}_o & \hat{d} \end{bmatrix}^T, \hat{\mathbf{y}} = \begin{bmatrix} \hat{i}_{in} & \hat{u}_o \end{bmatrix}^T$$

After linearization the SSA matrices for a buck converter become

$$\mathbf{A} = \begin{bmatrix} -\frac{r_L + r_C}{L} & -\frac{1}{L} \\ \frac{1}{C} & 0 \end{bmatrix}, \quad \mathbf{B} = \begin{bmatrix} \frac{D}{L} & \frac{r_C}{L} & \frac{U_{in} + U_D}{L} \\ 0 & -\frac{1}{C} & 0 \end{bmatrix}$$

$$\mathbf{C} = \begin{bmatrix} D & 0 \\ r_C & 1 \end{bmatrix}, \quad \mathbf{D} = \begin{bmatrix} 0 & 0 & I_L \\ 0 & -r_C & 0 \end{bmatrix}$$

Likewise, the SSA matrices for a boost converter are represented by

$$\mathbf{A} = \begin{bmatrix} -\frac{D'r_C + r_L}{L} & -\frac{D'}{L} \\ \frac{D'}{C} & 0 \end{bmatrix}, \quad \mathbf{B} = \begin{bmatrix} \frac{1}{L} & \frac{D'r_C}{L} & \frac{U_o + U_D + r_C(I_L - I_o)}{L} \\ 0 & -\frac{1}{C} & -\frac{I_L}{C} \end{bmatrix}$$

$$\mathbf{C} = \begin{bmatrix} 1 & 0 \\ D'r_C & 1 \end{bmatrix}, \quad \mathbf{D} = \begin{bmatrix} 0 & 0 & 0 \\ 0 & -r_C & -r_C I_L \end{bmatrix}$$

and for a buck-boost converter

$$\mathbf{A} = \begin{bmatrix} -\frac{D'r_C + r_L}{L} & -\frac{D'}{L} \\ \frac{D'}{C} & 0 \end{bmatrix}, \mathbf{B} = \begin{bmatrix} \frac{D}{L} & \frac{D'r_C}{L} & \frac{U_{in} + U_D + r_C(I_L - I_o)}{L} \\ 0 & -\frac{1}{C} & -\frac{I_L}{C} \end{bmatrix}$$

$$\mathbf{C} = \begin{bmatrix} D & 0 \\ D'r_C & 1 \end{bmatrix}, \mathbf{D} = \begin{bmatrix} 0 & 0 & I_L \\ 0 & -r_C & -r_C I_L \end{bmatrix}$$

#### The steady-state operating point

The steady-state operating point of a buck converter can be obtained from (2.3) letting the average derivative to be equal to zero and replacing the values of variables with their steady-state values. The expressions for the state and output variables of all basic converters are summarized in Table (2.1).

Table 2.1: Steady-state operating point for all basic ideal converters in CCM.

| Type       | $I_L$            | $I_{in}$          | D                                                                                                                                                                               | $U_o$ |

|------------|------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Buck       | $I_o$            | $DI_o$            | $\frac{U_D + r_L I_o + U_o}{U_{in} + U_D}$                                                                                                                                      | $U_C$ |

| Boost      | $\frac{I_o}{D'}$ | $\frac{I_o}{D'}$  | $1 - \frac{\left(1 + \sqrt{1 + 4\frac{r_{L}I_{o}(U_{o} + U_{D} - r_{C}I_{o})}{(U_{in} - r_{C}I_{o})^{2}}}\right)}{\frac{2(U_{o} + U_{D} - r_{C}I_{o})}{(U_{in} - r_{C}I_{o})}}$ | $U_C$ |

| Buck-Boost | $\frac{I_o}{D'}$ | $\frac{DI_o}{D'}$ | $1 - \frac{\left(1 + \sqrt{1 + 4\frac{r_L I_o(U_o + Uin + U_D - r_C I_o)}{(U_{in} - r_C I_o)^2}}\right)}{\frac{2(U_o + Uin + U_D - r_C I_o)}{(U_{in} - r_C I_o)}}$              | $U_C$ |

#### 2.6.2 Discontinuous Conduction Mode DCM

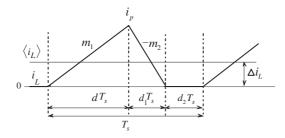

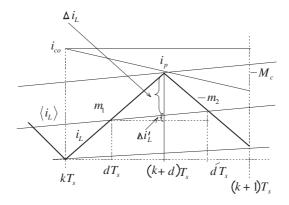

The DCM operation of switching converters differs from CCM operation by an additional third time interval in each switching cycle during which an inductor current is clamped to zero. In DCM operation the inductor current rises in the first interval when the switch is turned on, reaches a peak when the switch is to be turned off, and resets to zero at the end of the second interval. However, we use d and  $d_1$  to denote the duty ratio of the first and the second interval, respectively (see Fig. 2.10).

Figure 2.10: Inductor current waveforms within a switching cycle in DCM.

A basic idea in forming the state-space equations for a continuous linear time-invariant system (LTI) is to describe the derivatives of the state variables as a function of state, input, and control variables. In the conventional SSA method [32, 28] applied to switching converters, the derivatives are derived using circuit theory and averaged over one switching cycle. This approach has proved to be efficient in CCM, because the instantaneous inductor current is continuous, and therefore, the average currents within ON and OFF times are related directly to the duty ratio and its complement. The situation is different in DCM, and therefore, the SSA method does not give correct formulation [33, 34]. Alternatively, those derivatives will be derived based on the physical phenomena associated to the inductor current (i.e., average slope) and the capacitor voltage (i.e., average charge), resulting in a consistent formulation in DCM for all basic converters.

Based on inductor current waveform shown in Fig. (2.10), the average inductor current  $\langle i_L \rangle$  and its derivative for all basic converters (i.e., buck, boost and buck-boost) can be expressed as

$$\langle i_L \rangle = \frac{i_P}{2} \left( d + d_1 \right) \tag{2.5}$$

$$\frac{d\langle i_L\rangle}{dt} = dm_1 - d_1m_2 - \frac{r_L}{L}\langle i_L\rangle \tag{2.6}$$

where  $i_p$  is the peak of the inductor current  $i_L$ ,  $m_1$  and  $m_2$  are the up and down slopes of instantaneous inductor current expressed as positive quantities. Their expressions of buck, boost and buck-boost converters are defined in Table 2.2, [33, 34].

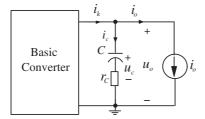

The output circuitry (Fig. 2.11) is the same for all the basic converters with respect to the formulation for the derivative of average capacitor voltage  $\langle u_C \rangle$ , and therefore, the derivative of average capacitor voltage can be approximated by computing the average charge delivered into the capacitor as an average charge of charge as following

| Type       | $m_1$                  | $m_2$                       |

|------------|------------------------|-----------------------------|

| Buck       | $\frac{u_{in}-u_o}{L}$ | $\frac{u_o + U_D}{L}$       |

| Boost      | $\frac{u_{in}}{L}$     | $\frac{-u_{in}+u_o+U_D}{L}$ |

| Buck-Boost | $\frac{u_{in}}{L}$     | $\frac{u_o + U_D}{L}$       |

Table 2.2: Up and down slopes of basic converters.

Figure 2.11: Basic converter.

$$\frac{d\langle u_C \rangle}{dt} = \frac{\Delta Q_c}{T_s} = \frac{\langle i_k \rangle}{C} - \frac{\langle i_o \rangle}{C}$$

(2.7)

where  $i_k$  denotes the current coming through the inductor, for a buck converter

$$\langle i_k \rangle = \langle i_L \rangle \tag{2.8}$$

and for boot and buck-boost converters

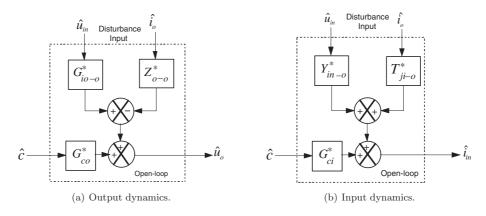

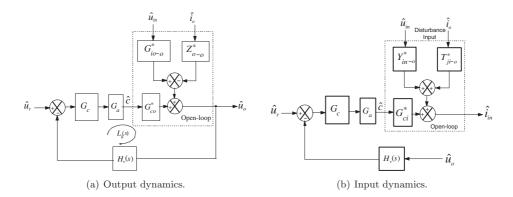

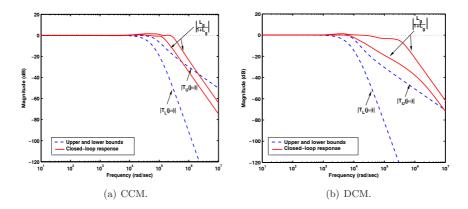

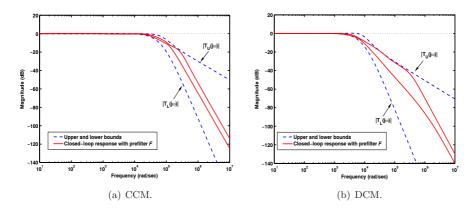

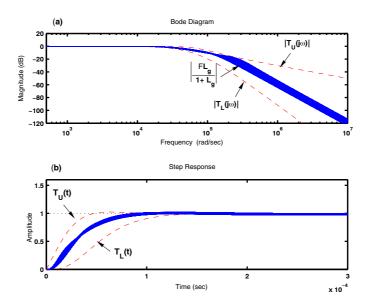

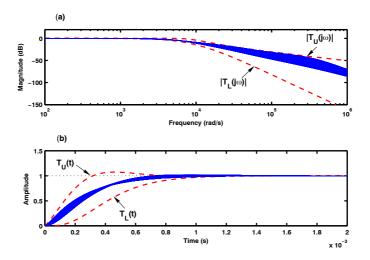

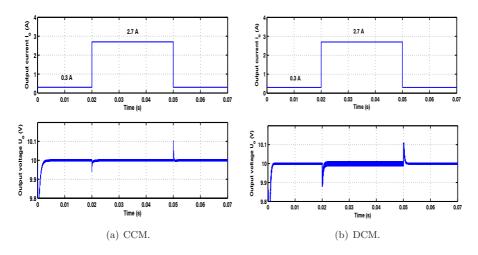

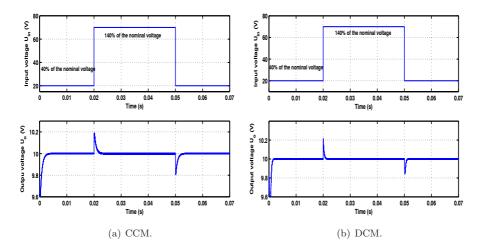

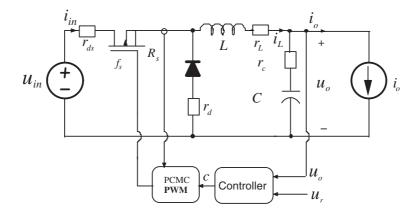

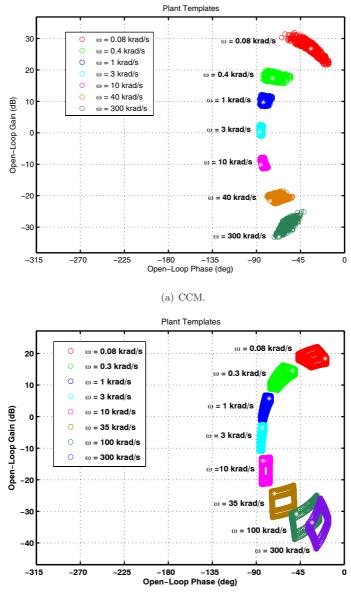

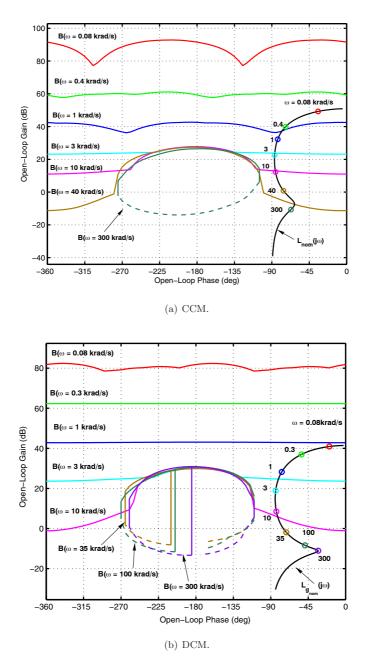

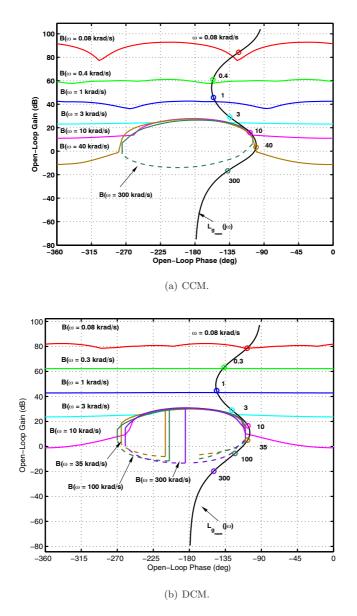

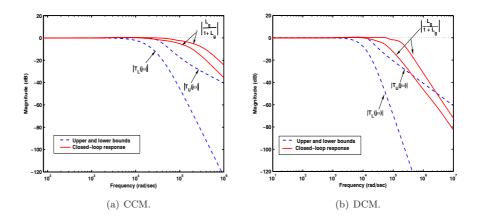

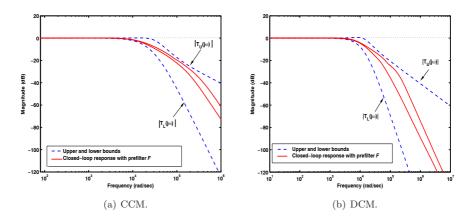

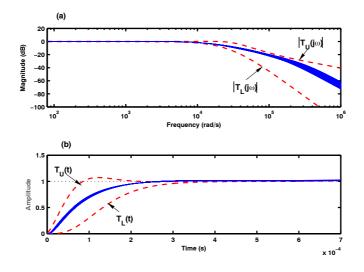

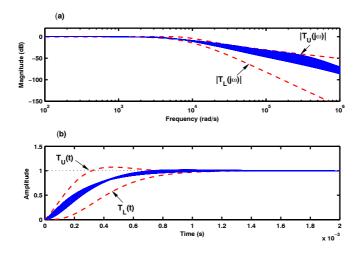

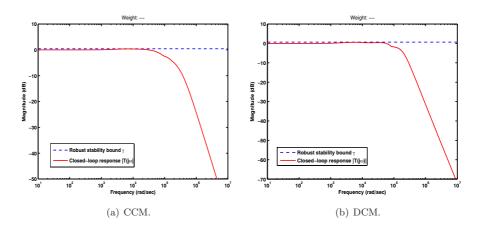

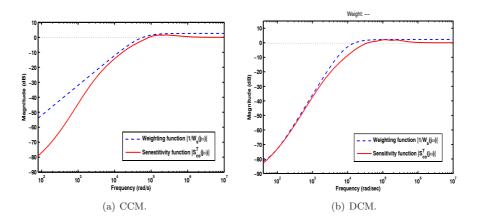

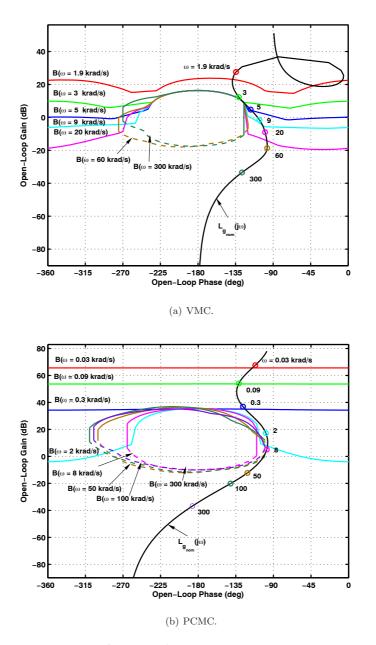

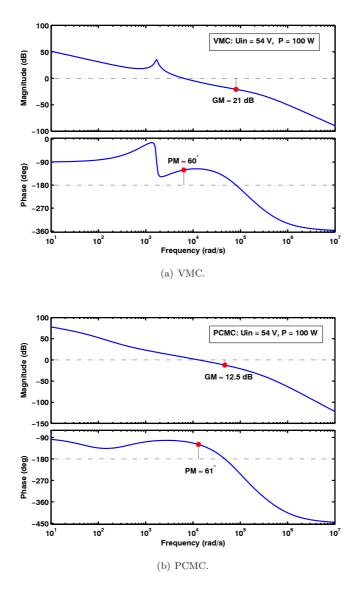

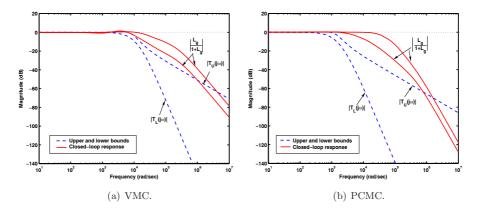

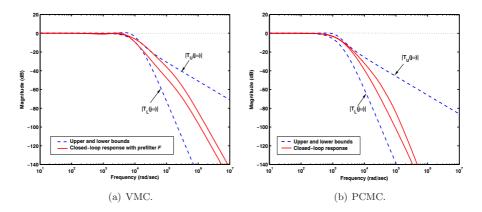

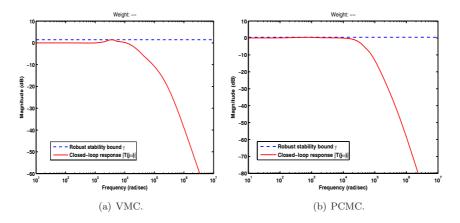

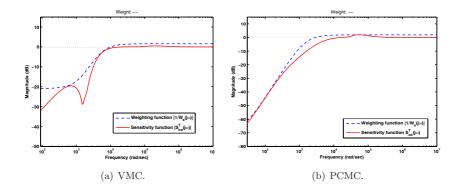

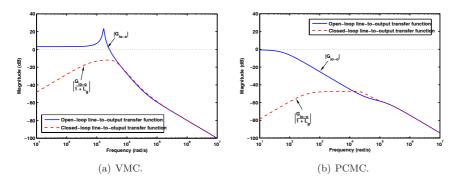

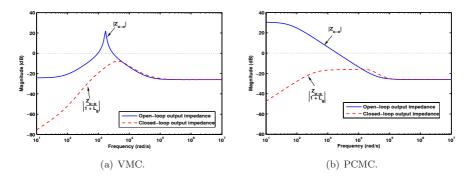

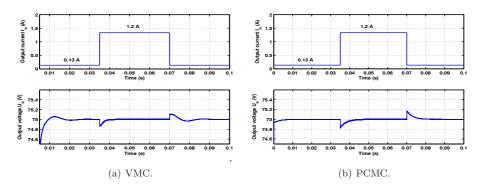

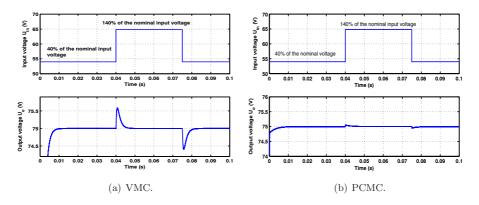

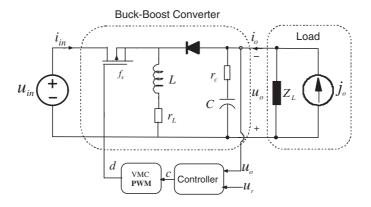

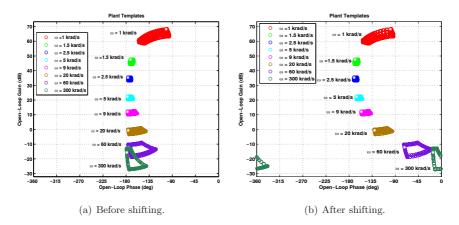

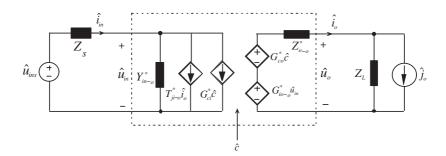

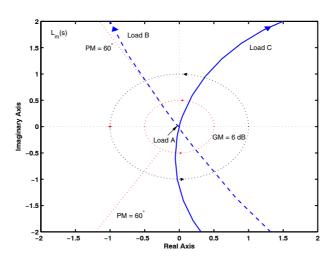

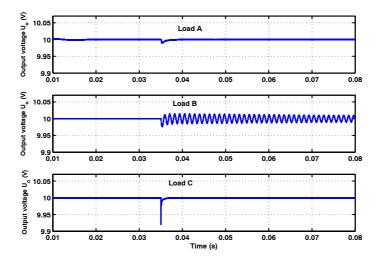

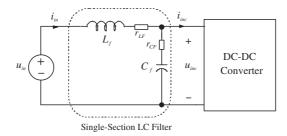

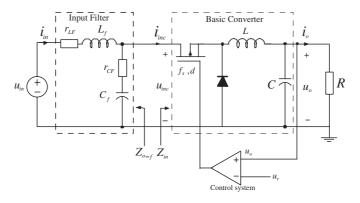

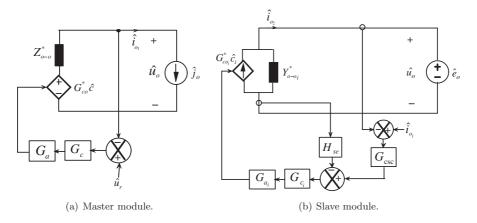

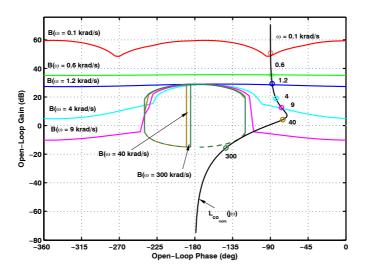

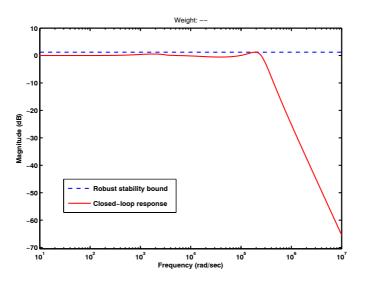

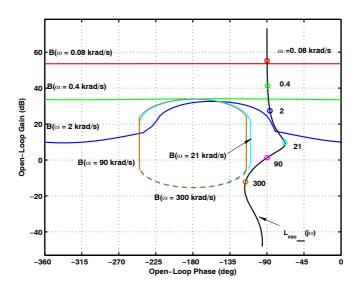

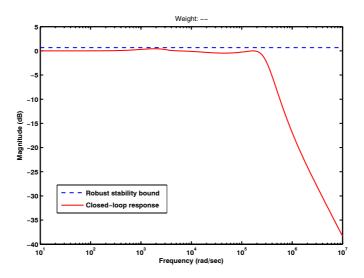

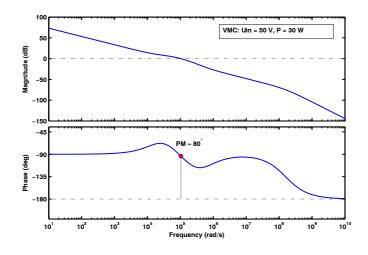

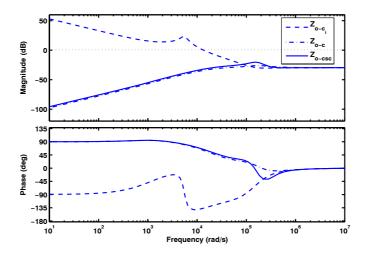

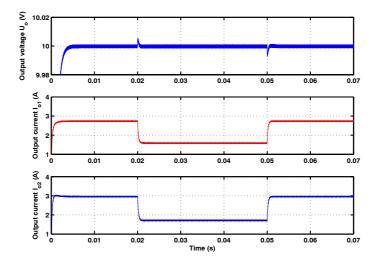

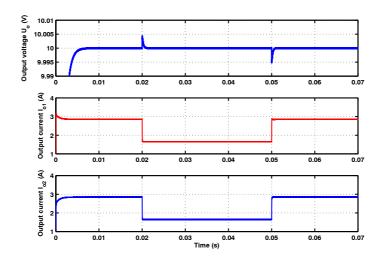

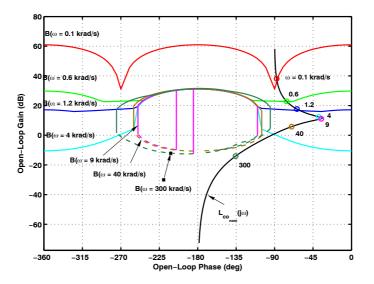

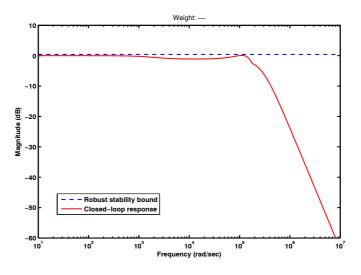

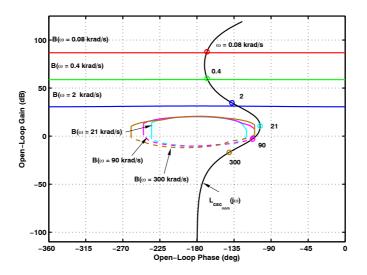

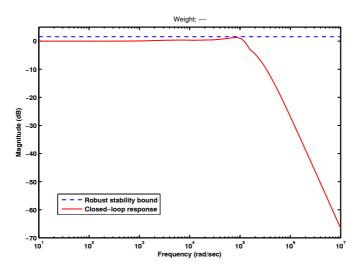

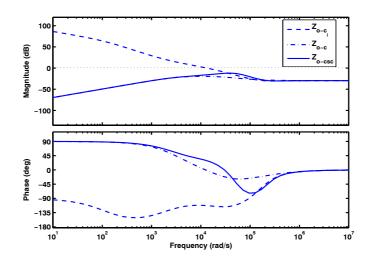

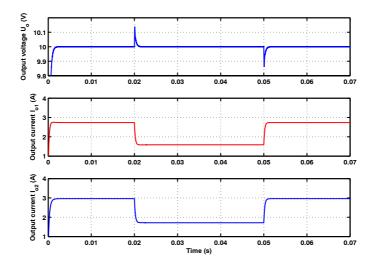

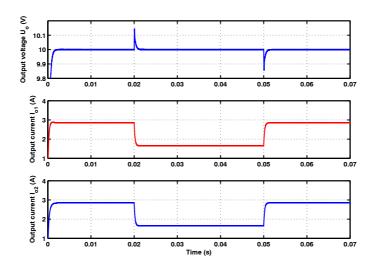

$$\langle i_k \rangle = \frac{d_1}{d+d_1} \left\langle i_L \right\rangle \tag{2.9}$$