## Xu Lei

# Bordered Block-Diagonal Preserved Model-Order Reduction for RLC Circuits

#### **School of Electrical Engineering**

Thesis submitted for examination for the degree of Master of Science in Technology. Espoo 25.5.2011

Thesis supervisor:

Prof. Martti Valtonen

Thesis instructor:

Lic.Sc. (Tech.) Mikko Honkala

Aalto University School of Electrical Engineering

| Author: Xu                                                                               | Lei                                                                                                                 |                                                                                                                              |                                                                                                       |                                                                                                                                                                                                   |

|------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title: Borde<br>Circu                                                                    | -                                                                                                                   | gonal Preserved M                                                                                                            | Iodel-Order R                                                                                         | Reduction for RLC                                                                                                                                                                                 |

| Date: 25.5.2                                                                             | 2011                                                                                                                | Language: Engl                                                                                                               | sh                                                                                                    | Number of pages:8+40                                                                                                                                                                              |

| Department                                                                               | of Radio Scien                                                                                                      | ce and Technolog                                                                                                             | 5y                                                                                                    |                                                                                                                                                                                                   |

| Professorshi                                                                             | ip: Circuit theo                                                                                                    | ry                                                                                                                           |                                                                                                       | Code: S-55                                                                                                                                                                                        |

| Supervisor:                                                                              | Prof. Martti Va                                                                                                     | altonen                                                                                                                      |                                                                                                       |                                                                                                                                                                                                   |

| Instructor:                                                                              | Lic.Sc. (Tech.)                                                                                                     | Mikko Honkala                                                                                                                |                                                                                                       |                                                                                                                                                                                                   |

| order reduc<br>designed for<br>or linear sul<br>linear RLC<br>reduction us<br>The impler | tion (BVOR) n<br>facilitating the<br>bcircuits of a no<br>parts of the circ<br>sing an appropri-<br>nented algorith | nethod and imple<br>simulation of ind<br>onlinear circuit. The<br>cuit from any giv<br>iate algorithm for<br>mms in this too | ementation of<br>lustrial, very la<br>The BVOR to<br>en typical SPI<br>r optimum eff<br>l are bordere | gonal preserved model-<br>the corresponding tool<br>arge sized linear circuits<br>ol is able to extract the<br>ICE netlist and perform<br>iciency.<br>ed block-diagonal ma-<br>ck Arnoldi method. |

| *                                                                                        | bordered block-<br>cuits, circuit sin                                                                               | ° -                                                                                                                          | ed model-orde                                                                                         | r reduction, RLC cir-                                                                                                                                                                             |

|                                                                                          |                                                                                                                     |                                                                                                                              |                                                                                                       |                                                                                                                                                                                                   |

# Preface

This thesis was written in the research group of Circuit Theory of Department of Radio Science and Engineering of Aalto University.

I wish to express my gratitude to Prof. Martti Valtonen for giving me the opportunity to work in the research group of Circuit Theory and to write this thesis. Especially, I would like to thank my instructor Lic.Sc.(Tech.) Mikko Honkala and Lic.Sc.(Tech.) Pekka Miettinen for their help and guidance in writing this thesis.

Otaniemi, 25.5.2011

Xu Lei

# Contents

| A        | bstra                                               | ict                                                                                                                                                                                                                                                                                                                         | ii                                               |

|----------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| P        | refac                                               | e                                                                                                                                                                                                                                                                                                                           | iii                                              |

| C        | onter                                               | nts                                                                                                                                                                                                                                                                                                                         | iv                                               |

| Sy       | mbo                                                 | ols and abbreviations                                                                                                                                                                                                                                                                                                       | vi                                               |

| 1        | Intr<br>1.1<br>1.2<br>1.3<br>1.4<br>1.5<br>1.6      | coductionModel-Order Reduction in generalPartitioning a circuitBordered Block-Diagonal Preserved Model-Order Reduction (BVOR)BackgroundOverview of the thesisAuthor's contribution                                                                                                                                          | 1<br>1<br>1<br>2<br>2<br>2                       |

| <b>2</b> | For                                                 | mulation of circuit equation with MNA                                                                                                                                                                                                                                                                                       | 4                                                |

| 3        | <b>Kry</b><br>3.1                                   | Passive reduced-order macromodeling algorithm (PRIMA)                                                                                                                                                                                                                                                                       | <b>6</b><br>7                                    |

| 4        | <b>BV</b><br>4.1<br>4.2<br>4.3<br>4.4<br>4.5<br>4.6 | OR method         Vector-potential based nodal analysis (VNA)         BBD structure         4.2.1         Stretching of nodal voltages         4.2.2         Stretching of branch currents         VNA matrix with BBD structure         BBD Solver         BBD Solver         Q constructed with individual diagonal block | 8<br>8<br>10<br>11<br>12<br>14<br>18<br>19<br>21 |

| <b>5</b> | Ma                                                  | cromodel realization                                                                                                                                                                                                                                                                                                        | 22                                               |

| 6        | <b>BV</b><br>6.1<br>6.2<br>6.3<br>6.4<br>6.5        | OR Implementation         Total BVOR flow         Netlist parsing and circuit partitioning         Matrix construction         BVOR method         Macromodel realization and netlist reconstruction                                                                                                                        | 25<br>25<br>25<br>25<br>26<br>26                 |

| 7        | <b>Sim</b><br>7.1<br>7.2                            | Aulation examplesSimulation setupQ generated with full BBD matrix as input7.2.1RC netlist7.2.2RL netlist                                                                                                                                                                                                                    | 27<br>27<br>28<br>28<br>29                       |

| partition |

|-----------|

| 8 Summary |

# Symbols and abbreviations

# Symbols

| Λ                                                                                   | a diagonal matrix containing the eigenvalues of $\widetilde{\mathbf{G}}^{-1}\widetilde{\mathbf{C}}$ as its diagonal elements |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| $\mathcal{A}$                                                                       | diagonal elements                                                                                                            |

|                                                                                     | moment generation matrix                                                                                                     |

| $\mathcal{B}_{\mathrm{MNA}}$                                                        | MNA selector matrix consisting of ones, minus ones, and zeros                                                                |

| $egin{array}{c} \mathcal{B} \ \widetilde{\mathbf{B}} \end{array}$                   | VNA selector matrix consisting of ones, minus ones, and zeros                                                                |

|                                                                                     | reduced port matrix                                                                                                          |

| $\mathbf{B}_{	ext{main}}$                                                           | main block port matrix                                                                                                       |

| $\mathbf{B}_{	ext{sub}}$                                                            | sub block port matrix                                                                                                        |

| $b_i$                                                                               | one circuit branch                                                                                                           |

| $\mathcal{C}_{\mathrm{MNA}}$                                                        | MNA capacitance matrix                                                                                                       |

| $\mathcal{C}$ $\widetilde{\mathbf{C}}$                                              | VNA capacitance matrix                                                                                                       |

| $\widetilde{\mathbf{C}}$                                                            | reduced capacitance matrix                                                                                                   |

| $\mathbf{C}_{	ext{main}}$                                                           | main block capacitance matrix                                                                                                |

| $\mathbf{C}_{	ext{sub}}$                                                            | sub block capacitance matrix                                                                                                 |

| $\mathbf{C}_1$                                                                      | matrix containing the stamps for capacitances                                                                                |

| С                                                                                   | the number of capacitances                                                                                                   |

| $c_x$                                                                               | capacitor                                                                                                                    |

| $c_0$                                                                               | self-capacitor                                                                                                               |

| Cond.                                                                               | condition number of $\widetilde{\mathbf{G}} + s_0 \widetilde{\mathbf{C}}$                                                    |

| $\mathbf{E}_l$                                                                      | additional incidence stamps for branch currents generated for                                                                |

| i                                                                                   | the MNA equations                                                                                                            |

| $\mathbf{E}_i$                                                                      | additional incidence stamps for nodal voltages generated for the                                                             |

| U                                                                                   | MNA equations                                                                                                                |

| $E_{y_{ii}}$                                                                        | average error of total y parameters $(\frac{1}{n}\sum_{i=0}^{n} \Delta y_i)$                                                 |

| $\mathcal{G}_{	ext{MNA}}$                                                           | MNA conductance matrix $(n \angle_{i=0} \angle g_i)$                                                                         |

| $\mathcal{G}$                                                                       | VNA conductance matrix                                                                                                       |

| $\mathcal{G}$<br>$\widetilde{\mathbf{G}}$                                           | reduced conductance matrix                                                                                                   |

| ${f G}_{ m main}$                                                                   |                                                                                                                              |

|                                                                                     | main partitioned block<br>sub block                                                                                          |

| ${f G}_{ m sub}$                                                                    |                                                                                                                              |

| $\mathbf{G}_1$                                                                      | matrix containing the stamps for inductances                                                                                 |

| $\begin{array}{c} \mathcal{G}_{i,i} + s\mathcal{C}_{i,i} \\ \mathbf{G} \end{array}$ | diagonal block<br>the number of resistances                                                                                  |

| -                                                                                   | conductor                                                                                                                    |

| $g_x$                                                                               | self-conductor                                                                                                               |

| $g_0$                                                                               | transfer function                                                                                                            |

| $\mathbf{H}(s)$                                                                     |                                                                                                                              |

| H(s)                                                                                | reduced system                                                                                                               |

| 1                                                                                   | port currents                                                                                                                |

| $\mathbf{i}_l$                                                                      | inductive-branch current                                                                                                     |

| $\mathbf{i}_i$                                                                      | branch current for voltage sources                                                                                           |

| $\mathbf{I}_0$                                                                      | identity matrix                                                                                                              |

| $k_0$                                                                               | self susceptor                                                                                                               |

| $k_x$                                                                               | mutual susceptor                                                                                                             |

| $\mathbf{L}$                                                                        | inductance matrix                                                                                                            |

| <b>T</b> _1                 |                                                                     |

|-----------------------------|---------------------------------------------------------------------|

| $\mathbf{L}^{-1}$           | susceptance matrix                                                  |

| L                           | the number of inductances                                           |

| $L_m$                       | the number of mutual inductances                                    |

| M                           | diagonal matrix in BBD-structured state matrix                      |

| $\mathbf{M}_i$              | the block moments of $\mathbf{H}(s)$                                |

| $\mathbf{M}_i$              | partitioning block                                                  |

| $n_i$                       | number of internal nodes                                            |

| $n_e$                       | number of external nodes                                            |

| $n_l$                       | number of inductances                                               |

| $n_p$                       | number of partitions $\sim \sim \sim$                               |

| $N_{\rm nz}$                | number of non-zero elements in $\mathbf{G} + s_0 \mathbf{C}$        |

| $N_{\rm pp}$                | positive poles                                                      |

| N                           | number of ports                                                     |

| $N_q$                       | the number of iterations of Block Arnoldi method                    |

| $N_{\rm red}$               | size of the reduced matrix $\mathbf{G} + s_0 \mathbf{C}$            |

| n                           | the number of all nodes                                             |

| $\mathbf{Q}$                | projection matrix                                                   |

| $\mathbf{Q}_i$              | projection block matrix                                             |

| $Q_{\rm col}$               | order of reduction                                                  |

| q                           | refers to the number of iterations of Block Arnoldi method, the     |

|                             | number equals to $\lfloor q/n_e \rfloor$                            |

| ${\cal R}$                  | moment generation matrix                                            |

| $\mathbf{S}$                | transformation matrix                                               |

| $s_0$                       | expansion point                                                     |

| t                           | computational time of calculating certain $y$ parameter             |

| u                           | port voltages                                                       |

| $\mathbf{v}_n$              | nodal voltages                                                      |

| $v_i$                       | nodal voltage                                                       |

| $\mathbf{X}$                | off-diagonal matrix in BBD-structured state matrix                  |

| $\mathbf{X}_{i,0}$          | connection matrix                                                   |

| $\mathbf{x}_{\mathrm{MNA}}$ | MNA variables (nodal voltages, branch currents of inductances       |

|                             | and voltage sources)                                                |

| x                           | VNA variables (nodal voltages, magnetic fluxes and voltage sources) |

| $y_{11}$                    | element of y-parameter matrix                                       |

| Φ                           | magnetic flux                                                       |

| $\phi_i$                    | branch flux                                                         |

# Abbreviations

| APLAC  | an object-oriented analog circuit simulator and design tool |

|--------|-------------------------------------------------------------|

|        | (originally Analysis Program for Linear Active Circuits)    |

| AC     | Alternating Current                                         |

| BBD    | Bordered Block-Diagonal form                                |

| BVOR   | Bordered Block-Diagonal Preserved Model-Order Reduction     |

| DC     | Direct Current                                              |

| hMETIS | a software package for partitioning hypergraphs             |

| MATLAB | a programmable mathematics toolbox (MATrix LABoratory)      |

| METIS  | a software package for partitioning graphs                  |

| MNA    | Modified Nodal Analysis                                     |

| MOR    | Model-Order Reduction                                       |

| PRIMA  | Passive Reduced-Order Interconnect Macromodeling Algorithm  |

| SPICE  | a circuit simulator software                                |

| VNA    | vector-potential based nodal analysis                       |

|        |                                                             |

## 1 Introduction

## 1.1 Model-Order Reduction in general

The rapidly-increasing size and complexity of industrial circuits results in the substantial need for faster simulation methods. One way to speed up transistor-level simulations is to apply model-order reduction (MOR). As a discipline, MOR utilizes the properties of the dynamical systems, reduces the complexity of the systems, while preserves the original functionality of the systems within an acceptable margin of error.

There exists numerous MOR tools for reducing the large-scale circuits, for example: Reduced-Order Interconnect Macromodeling Algorithm (PRIMA) [7], SPRIM [3], PACT [2], Liao-Dai [20], Time constant Equilibration Reduction (TICER) [21] [22], PartMOR [12], BVOR [6], HiPRIME [16], and hiePrimor [17]. Liao-Dai and TICER are used for circuit containing only RC elements, PRIMA, SPRIM, and PACT can be used for RLC circuit. PartMOR, BVOR, HiPRIME, and hiePrimor are partitioning-based MOR method and they can also be used for RLC circuits.

## **1.2** Partitioning a circuit

Circuit partitioning plays an important role in partitioning-based MOR method. In order to analyze large circuit more easily, the large circuit is partitioned into smaller subcircuits. Different partitioning algorithms are available, such as METIS and hMETIS [8]. These two methods operate on graphs and hypergraphs in general.

As introduced previously, the existing partitioning-based MOR methods are: BVOR, PartMOR, HiPRIME, hiePrimor etc. The first two methods are utilized to deal with the mutual inductance feature in/between the partitioned subcircuits. BVOR reduces mutual inductances by decoupling the inductive branch, while Part-MOR in Ref. [19] and its extension in Ref. [12] utilizes the physical characteristics of a transmission line to add the mutual inductance information. HiPRIME is used to analyze RLCK power delivery systems. The last method performs the projectionbased reduction on partitioned subcircuits. BVOR, PartMOR and hiePrimor use hMETIS partitioning algorithm.

## 1.3 Bordered Block-Diagonal Preserved Model-Order Reduction (BVOR)

Bordered Block-Diagonal Preserved Model-Order Reduction (BVOR) is a partitioningbased MOR method.

Large-scale interconnect dominant RLC circuits are usually analyzed using modified nodal analysis (MNA) [4]. The MNA formulation uses nodal voltage variables and currents of inductance. The inductance part of MNA matrix may become dense with a large number of elements. An efficient MOR needs to first sparsify the dense inductance matrix. Since matrix  $\mathbf{L}$  is not diagonal-dominant, sparsifying  $\mathbf{L}$  directly thereby leads to an instable state matrix.  $\mathbf{L}^{-1}$  matrix is however more diagonaldominant than  $\mathbf{L}$ , and hence,  $\mathbf{L}^{-1}$  can be more effectively sparsified while preserving stability. The new circuit stamping for such RLC circuits is introduced and the corresponding new analysis method is called vector-potential based nodal analysis (VNA) [5]. In addition, a bordered block-diagonal form (BBD) is presented for the flat VNA matrix in order to preserve the strucutre of the state matrices such as sparsity and hierarchy as well as efficiently build and simulate the circuit. Corresponding model-order reduction is called BBD-structure preserving model order reduction (BVOR).

Another remarkable advantage of BVOR method is the possibility to apply parallel processing on the BBD-based matrix.

## 1.4 Background

The thesis is description, implementation, testing and evaluation of paper "Fast Analysis of a Large-Scale Inductive Interconnect by Block-Structure-Preserved Macro-modeling" of IEEE transactions on very large scale integration (VLSI) systems [5].

In the course of the project, circuit theory reserch group of Aalto University developed and implemented the circuit partition tool, MNA matrix formulation tool and linear MOR tool prototype using MATLAB and C programming language. My implementation started from the formulation of the MNA matrix.

## 1.5 Overview of the thesis

Section 2 describes the circuit formulation using MNA method. Based on the state matrices, Krylov subspace model-order reduction and one specific method PRIMA are introduced in detail in Section 3. Section 4 discusses BVOR method. Specifically it presents the VNA method and BBD structure with several examples and comparisons. After this, BBD solver, Block Arnoldi method, the combination of the two methods are studied separately.

Section 5 discusses macromodel realization applied on the reduced blocks. Section 6 describes the total BVOR flow and the implementation of the BVOR algorithms. Section 7 documents the extensive simulations and bench mark tests performed and compares the different BVOR algorithms in the light of these results. Finally, conclusions of the work are given in Section 8.

## **1.6** Author's contribution

The author's main contribution to this project was the implementation of VNA matrix formulation, implementation of BBD solver, implementation of Block Arnoldi Algorithm, utilization of existing macromodel realization and test simulations in the final phase of the project.

The performance of BVOR is also compared with PRIMA method. Projection matrices produced from individual diagonal block is discussed briefly and corresponding simulation results are compared with the projection matrices generated from original BBD system. Macromodel realization is also studied.

# 2 Formulation of circuit equation with MNA

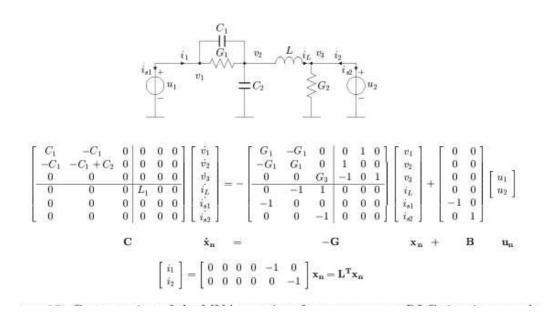

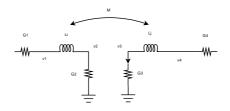

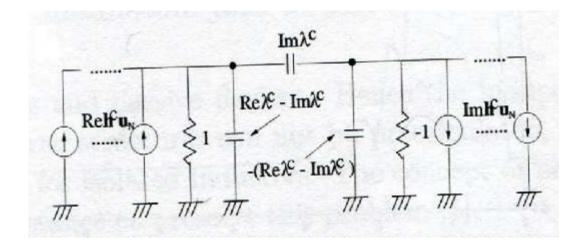

Figure 1: Construction of the MNA matrices for y-parameters from a two-port RLC circuit example [10]

One way to describe N-port circuit is to utilize the y-parameter matrix. Here, voltage sources are used at the input and output ports to excite the circuit, as shown in Fig. 1. The time-domain modified nodal analysis (MNA) circuit equations for a linear N-port RLC circuit can be expressed as

$$\begin{cases} \mathcal{C}_{\text{MNA}} \frac{\mathrm{d}\mathbf{x}_{\text{MNA}}(t)}{\mathrm{d}t} = -\mathcal{G}_{\text{MNA}}\mathbf{x}_{\text{MNA}}(t) + \mathcal{B}_{\text{MNA}}\mathbf{u}(t), \\ \mathbf{y}(t) = \mathcal{B}_{\text{MNA}}^{\text{T}}\mathbf{x}_{\text{MNA}}(t), \end{cases}$$

(1)

the corresponding first-order state equation in frequency domain is

$$\begin{cases} s \mathcal{C}_{\text{MNA}} \mathbf{x}_{\text{MNA}}(s) = -\mathcal{G}_{\text{MNA}} \mathbf{x}_{\text{MNA}}(s) + \mathcal{B}_{\text{MNA}} \mathbf{u}(s), \\ \mathbf{y}(s) = \mathcal{B}_{\text{MNA}}^{\text{T}} \mathbf{x}_{\text{MNA}}(s), \end{cases}$$

(2)

where  $C_{MNA}$  and  $\mathcal{G}_{MNA}$  are susceptance and conductance matrices, respectively, and **y**,  $\mathbf{x}_{MNA}$ , **u** and **i** denote the port current, the MNA variables (nodal voltages and branch currents of inductances and voltage sources), port voltages, and port currents, respectively. Here,  $\mathcal{B}_{MNA}$  is a selector matrix consisting of ones, minus ones, and zeros. The matrices  $C_{MNA}$  and  $\mathcal{G}_{MNA}$  are defined as

$$\mathcal{C}_{\text{MNA}} \equiv \begin{bmatrix} \mathbf{C}_1 & 0 & 0 \\ 0 & \mathbf{L} & 0 \\ 0 & 0 & 0 \end{bmatrix}, \quad \mathcal{G}_{\text{MNA}} \equiv \begin{bmatrix} \mathbf{G}_1 & \mathbf{E}_l & \mathbf{E}_i \\ -\mathbf{E}_l^{\text{T}} & 0 & 0 \\ -\mathbf{E}_i^{\text{T}} & 0 & 0 \end{bmatrix}, \quad \mathbf{x}_{\text{MNA}} \equiv \begin{bmatrix} \mathbf{v}_n \\ \mathbf{i}_l \\ \mathbf{i}_i \end{bmatrix}$$

where  $\mathbf{C}_1$ ,  $\mathbf{L}$  and  $\mathbf{G}_1$  are the matrices containing the stamps for capacitances, inductances, and resistances respectively;  $\mathbf{E}_l$  and  $\mathbf{E}_i$  consist of ones, minus ones and zeros, which represent the additional incidence stamps for branch currents and nodal voltages generated for the MNA equations; and the vector  $\mathbf{x}_{\text{MNA}}$  contains the nodal voltages  $\mathbf{v}_n$  and branch currents  $\mathbf{i}_l$ ,  $\mathbf{i}_i$  for inductances and voltage sources. For RLC circuits, the dimension of the  $\mathcal{C}_{\text{MNA}}$  and  $\mathcal{G}_{\text{MNA}}$  matrix is thus  $n \times n$ , with  $n = n_i + n_l + N$ , where  $n_i, n_l$  and N are the number of internal nodes, inductances and ports respectively. One important property of the MNA formulation is that the transposed summations of state matrices are symmetric and semipositive-definite, i.e.,  $\mathcal{G}_{\text{MNA}} + \mathcal{G}_{\text{MNA}}^T > 0$  and  $\mathcal{C}_{\text{MNA}} + \mathcal{C}_{\text{MNA}}^T > 0$ . This is one of the sufficient conditions for a system to be passive. [5]

## 3 Krylov subspace Model-Order Reduction

There are other types of MOR methods than Krylov subspace method, but the thesis focused on Krylov subspace method.

Solving Eq. (2) following transfer function is obtained:

$$\frac{y(s)}{u(s)} = \mathbf{H}(s) = \mathcal{B}_{\mathrm{MNA}}^{T} (\mathcal{G}_{\mathrm{MNA}} + s\mathcal{C}_{\mathrm{MNA}})^{-1} \mathcal{B}_{\mathrm{MNA}}$$

(3)

Expanding  $\mathbf{H}(s)$  at some frequency point  $s_0$ , state variable is contained in a block Krylov subspace

$$span\{\mathcal{R}, \mathcal{AR}, ..., \mathcal{A}^{N_q - 1}\mathcal{R}, ...\}$$

$$\tag{4}$$

with two moment generation matrices

$$\mathcal{A} = (\mathcal{G}_{\text{MNA}} + s_0 \mathcal{C}_{\text{MNA}})^{-1} \mathcal{C}_{\text{MNA}}, \ \mathcal{R} = (\mathcal{G}_{\text{MNA}} + s_0 \mathcal{C}_{\text{MNA}})^{-1} \mathcal{B}_{\text{MNA}}$$

(5)

First lemma [5] related to Krylov subspace and MOR is: if a small-dimensioned matrix **Q** that spans the  $N_q$ th-order ( $N_q = \lfloor q/N \rfloor$ ) block Krylov subspace is

$$\mathcal{K}(\mathcal{A}, \mathcal{R}, q) = span\{\mathcal{R}, \mathcal{A}\mathcal{R}, ..., \mathcal{A}^{N_q - 1}\mathcal{R}\} \subseteq span\{\mathbf{Q}\}$$

(6)

then applying  $\mathbf{Q}$  to project the original system

$$\widetilde{\mathcal{G}}_{MNA} = \mathbf{Q}^T \mathcal{G}_{MNA} \mathbf{Q}, \quad \widetilde{\mathcal{C}}_{MNA} = \mathbf{Q}^T \mathcal{C}_{MNA} \mathbf{Q}, \quad \widetilde{\mathcal{B}}_{MNA} = \mathbf{Q}^T \mathcal{B}_{MNA}$$

(7)

the first q block moments of the reduced system  $\mathbf{H}(s)$

$$\widetilde{\mathbf{H}}(s) = \widetilde{\mathcal{B}}_{\mathrm{MNA}}^T (\widetilde{\mathcal{G}}_{\mathrm{MNA}} + s\widetilde{\mathcal{C}}_{\mathrm{MNA}})^{-1} \widetilde{\mathcal{B}}_{\mathrm{MNA}}$$

(8)

expanded at  $s_0$  are identical to the original one  $\mathbf{H}(s)$ .

The projection-based model-order reduction is essentially to construct an invariant subspace that can approximate the dominant system response in terms of the first few moments expanded at  $s_0$ . The  $N_q$  determines the accuracy of the reduced model and depends on both the number of ports (N) and the order of reduction (q). A detailed analysis on how to select q can be found in [13]. Note that PRIMA applies a block Arnoldi method to construct an orthonormalized projection matrix  $\mathbf{Q}$ . Section 3.1 introduces PRIMA in brief.

Second lemma [5] is: when the input and the output are symmetric, the reduced model  $\widetilde{\mathbf{H}}(s)$  is passive when projected by an orthonormalized  $\mathbf{Q}$  in a fashion similar to that of the congruence transformation Eq. (7).

Let us consider the special case  $s_0 = 0$ , Eq. (5) becomes:

$$\mathcal{A} = \mathcal{G}_{MNA}^{-1} \mathcal{C}_{MNA}, \ \mathcal{R} = \mathcal{G}_{MNA}^{-1} \mathcal{B}_{MNA}$$

(9)

the corresponding transfer function at  $s_0 = 0$  is written as

$$\mathbf{H}(s) = \mathcal{B}_{\mathrm{MNA}}^{\mathrm{T}} (\mathbf{I} + s\mathcal{A})^{-1} \mathcal{R}, \qquad (10)$$

where **I** is the  $n \times n$  identity matrix. The block moments of  $\mathbf{H}(s)$  are defined as the coefficients of the Taylor expansion of **H** around  $s_0 = 0$ :

$$\mathbf{H}(s) = \mathbf{M}_0 + \mathbf{M}_1 s + \mathbf{M}_2 s^2 + \cdots.$$

(11)

Here,  $(\mathbf{I} + s\mathcal{A})^{-1}$  is expanded into a Neumann series. For analysis purposes, the zeroth block moment may be perceived as the DC properties of the circuit, with the higher moments corresponding to the frequency behavior of the circuit. The block moments can be computed using the relation

$$\mathbf{M}_i = \mathcal{B}_{\mathrm{MNA}}^{\mathrm{T}} \mathcal{A}^i \mathcal{R}.$$

(12)

Note that the dimension of the block moments  $\mathbf{M}_i$  is the same as the number of ports in the circuit.

#### 3.1 Passive reduced-order macromodeling algorithm (PRIMA)

Based on the block Arnoldi algorithm, a passive reduced-order macromodeling algorithm (PRIMA) is presented below. This algorithm is a general method for the passive reduction of the RLC circuits.

Algorithm 1

Connect voltage sources to the multi-port & obtain the MNA matrices  $\mathcal{G}_{MNA}$ ,  $\mathcal{C}_{MNA}$ ,  $\mathcal{B}_{MNA}$  from Eq. (2).

Solve  $\mathcal{G}_{MNA}\mathcal{R} = \mathcal{B}_{MNA}$  for  $\mathcal{R}$   $(\mathbf{Q}_0, \mathbf{T}) = qr(\mathcal{R})$ ; qr factorization of  $\mathcal{R}$ If q/N is not an integer, set  $N_q = \lfloor q/N \rfloor + 1$ , else set  $N_q = q/N$ For  $k = 1, 2, ..., N_q$ Set  $\mathbf{V} = \mathcal{C}_{MNA}\mathbf{Q}_{k-1}$ Solve  $\mathcal{G}_{MNA}\mathbf{Q}_k^{(0)} = \mathbf{V}$  for  $\mathbf{Q}_k^{(0)}$ For j = 1, ..., k  $\mathbf{H} = \mathbf{Q}_{k-j}^{\mathbf{T}}\mathbf{Q}_k^{(j-1)}$   $\mathbf{Q}_k^{(j)} = \mathbf{Q}_k^{(j-1)} - \mathbf{Q}_{k-j}\mathbf{H}$  $(\mathbf{Q}_k, \mathbf{T}) = qr(\mathbf{Q}_k^{(k)})$ ; qr factorization of  $\mathbf{Q}_k^{(k)}$

Set  $\mathbf{Q} = [\mathbf{Q}_0, \mathbf{Q}_1, ..., \mathbf{Q}_k]$  and truncate  $\mathbf{Q}$  so that it has  $N_q$  columns only.

## 4 BVOR method

BBD-structure (bordered block-diagonal form) preserving model order reduction, shortly BVOR, is a partitioning-based MOR method which is utilized to reduce large-scale RLC circuit containing mutual inductances.

BVOR method uses hMETIS algorithm to partition the circuit into subcircuit. Then form VNA (vector-potential based nodal analysis) matrices for each subcircuit. Afterwards, BVOR method applies node splitting and branch tearing procedures to the couplings and connections between subcircuits such that state matrix (VNA) in BBD structure is generated for the large-scale RLC network. The state matrix is further reduced using a set of orthonormalized projection vectors  $\mathbf{Q}$  by BVOR method. The projection is performed by the block Arnoldi procedure.

Summary of BVOR method:

- 1. Use hMETIS algorithm to partition the circuit

- 2. Form VNA matrices for each subcircuit

- 3. Apply node splitting and branch tearing on VNA matrices to produce VNA matrices in BBD structure

- 4. Perform BBD-based block Arnoldi method that utilizes BBD matrix solver to reduce the BBD matrices

- 5. Generated structured projection matrix  $\mathbf{Q}$  is further used to reduce the original BBD matrices

This section discusses BVOR method in detail. Firstly VNA formation and BBD structure are introduced, then corresponding matrix-based model-order reduction (BVOR) is studied. At last alternative way to construct orthonormalized projection vectors  $\mathbf{Q}$  using individual diagonal block is discussed briefly.

The reduced matrices are realized by macromodel realization which will be discussed in next section.

### 4.1 Vector-potential based nodal analysis (VNA)

The relation between a magnetic flux  $\Phi$ , a branch inductance **L**, and an inductivebranch current  $\mathbf{i}_l$  is:

$$\Phi = \mathbf{L}\mathbf{i}_l \tag{13}$$

Note that the branch voltage drop at an inductor can be calculated as  $\mathbf{v}_l = s \mathbf{L} \mathbf{i}_l$ , or can be selected from the nodal voltage  $\mathbf{v}_n$  by  $\mathbf{v}_l = \mathbf{E}_l^T \mathbf{v}_n$ . Thus the following relation between the magnetic flux  $\Phi$  (branch variable) and the nodal voltage  $\mathbf{v}_n$ can be derived by

$$s\Phi = \mathbf{E}_l^T \mathbf{v}_n \tag{14}$$

Furthermore, first equation of Eq. (2) leads to

$$\begin{bmatrix} \mathbf{G}_1 & \mathbf{E}_l & \mathbf{E}_i \\ -\mathbf{E}_l^{\mathrm{T}} & 0 & 0 \\ -\mathbf{E}_i^{\mathrm{T}} & 0 & 0 \end{bmatrix} + s \begin{bmatrix} \mathbf{C}_1 & 0 & 0 \\ 0 & \mathbf{L} & 0 \\ 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} \mathbf{v}_n \\ \mathbf{i}_l \\ \mathbf{i}_i \end{bmatrix} = \begin{bmatrix} 0 \\ 0 \\ -\mathbf{B} \end{bmatrix} u(s)$$

then the following two independent equations can be led to:

$$s\mathbf{i}_l = \mathbf{L}^{-1} \mathbf{E}_l^T \mathbf{v}_n \tag{15}$$

and

$$(\mathbf{G}_1 + s\mathbf{C}_1)\mathbf{v}_n + \mathbf{E}_l\mathbf{i}_l + \mathbf{E}_i\mathbf{i}_i = 0$$

(16)

According to Eq. (13), Eq. (15) becomes

$$\mathbf{i}_l = \mathbf{L}^{-1} \Phi \tag{17}$$

and Eq. (16) becomes

$$(\mathbf{G}_1 + s\mathbf{C}_1)\mathbf{v}_n + \mathbf{E}_l(\mathbf{L}^{-1}\Phi) + \mathbf{E}_i\mathbf{i}_i = 0$$

(18)

As a result, based on Eq. (14) and Eq. (18), a new MNA equation with a first-order admittance can be obtained

$$\begin{cases} s\mathcal{C}\mathbf{x}(s) = -\mathcal{G}\mathbf{x}(s) + \mathcal{B}\mathbf{u}(s), \\ \mathbf{y}(s) = \mathcal{B}^{\mathrm{T}}\mathbf{x}(s), \end{cases}$$

(19)

where

$$\mathbf{x} = \begin{bmatrix} \mathbf{v}_n \\ \Phi \\ \mathbf{i}_i \end{bmatrix}$$

(20)

is a new vector of state variables composed by the nodal voltage, flux, and branch current for the external voltage source. The new state matrices  $\mathcal{G}$ ,  $\mathcal{C}$  and  $\mathcal{B}$  become

$$\mathcal{G} = \begin{bmatrix} \mathbf{G}_1 & (\mathbf{E}_l \mathbf{L}^{-1}) & \mathbf{E}_i \\ -(\mathbf{L}^{-1} \mathbf{E}_l^T) & \mathbf{0} & \mathbf{0} \\ -\mathbf{E}_i^T & \mathbf{0} & \mathbf{0} \end{bmatrix}$$

$$\mathcal{C} = \begin{bmatrix} \mathbf{C}_1 & \mathbf{0} & \mathbf{0} \\ \mathbf{0} & \mathbf{L}^{-1} & \mathbf{0} \\ \mathbf{0} & \mathbf{0} & \mathbf{0} \end{bmatrix}$$

$$\mathcal{B} = \begin{bmatrix} \mathbf{0} \\ \mathbf{0} \\ -\mathbf{B} \end{bmatrix}$$

We call such a new MNA the VNA.

Since the aforementioned derivation is just to replace the state variable of  $\mathbf{i}_l$  by  $\Phi$ , the resulting MNA has the same structure as the original MNA. The new VNA stamping results in a passive formulation of  $\mathbf{L}^{-1}$  because both

$$\mathcal{G} + \mathcal{G}^{T} = \begin{bmatrix} 2\mathbf{G}_{1} & 0 & 0\\ 0 & 0 & 0\\ 0 & 0 & 0 \end{bmatrix}, \ \mathcal{C} + \mathcal{C}^{T} = \begin{bmatrix} 2\mathbf{C}_{1} & 0 & 0\\ 0 & 2\mathbf{L}^{-1} & 0\\ 0 & 0 & 0 \end{bmatrix}$$

(21)

are symmetric and semipositive-definite [5].

## 4.2 BBD structure

One efficient solution for a large-scale network is to apply hMETIS to partition the network into sub-networks and then utilize network decomposition to further decompose the couplings of node and mutual inductances between sub-networks. Network decomposition is achieved by node splitting and branch tearing for nodal voltage and branch current variables, respectively. In order to save memory, one large matrix is divided into several smaller blocks, each smaller block is solved at a time: the BBD solver is designed to efficiently solve divided blocks, which can be solved in parallel.

In addition, the network decomposition usually results in a state matrix with a bordered block diagonal (BBD) structure. The BBD matrix stretching basically introduces new columns/rows for decoupled nodes or branches. It provides a way to tear the state matrix with sparse inverse inductance in the frame work of VNA.

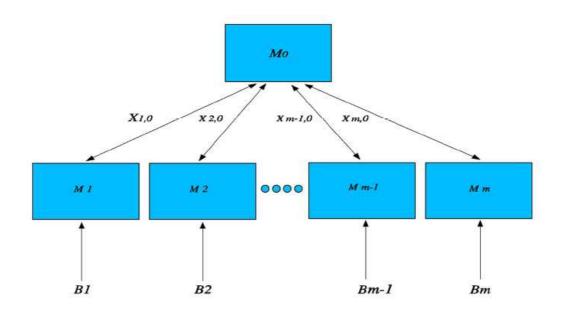

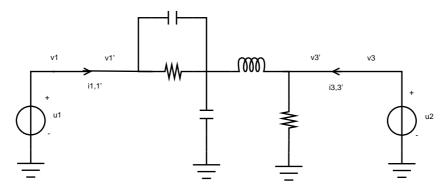

Figure 2: Two-level BBD representation of a flat VNA circuit. There is no coupling in bottom blocks, but each bottom block is connected to a centric interconnection block. (From [5])

#### 4.2.1 Stretching of nodal voltages

A matrix stretching of nodal voltages can be described by the following rule.

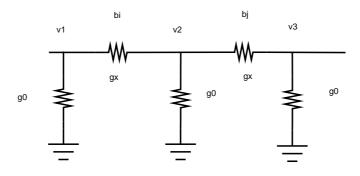

Rule 1: Assume that two resistive (or capacitive) branches  $b_i$  and  $b_j$  are coupled at a common node  $v_2$  with a conductor  $g_x$  (or a capacitor  $c_x$ ). Branch  $b_i$  has nodal voltages  $(v_1, v_2)$  and  $b_j$  has nodal voltages  $(v_2, v_3)$ . They can be decoupled by introducing: 1) a duplicated state variable  $v'_2$  with  $v_2 = v'_2$  and 2) an auxiliary state variable  $i_{2,2'}$  for a new branch current between nodes  $v_2$  and  $v'_2$

Figure 3: circuit before node splitting

Figure 4: circuit after node splitting

The corresponding transformations from the old  ${\mathcal G}$  and  ${\mathcal C}$  to new  ${\mathbf G}$  and  ${\mathbf C}$  are

$$\mathcal{G}: \begin{bmatrix} v_1 & v_2 & v_3 \\ \hline v_1 & g_0 + g_x & -g_x \\ v_2 & -g_x & g_0 + 2g_x & -g_x \\ v_3 & & -g_x & g_0 + g_x \end{bmatrix} \longrightarrow$$

$$\mathbf{G}: \begin{bmatrix} v_1 & v_2 & v_2' & v_3 & i_{2,2}' \\ \hline v_1 & g_0 + g_x & -g_x & & & \\ v_2 & -g_x & 2g_0 + g_x & & & +1 \\ v_2' & & & 2g_0 + g_x & -g_x & -1 \\ v_3 & & & -g_x & g_0 + g_x \\ i_{2,2}' & & -1 & +1 \end{bmatrix}$$

and

$$C:\begin{bmatrix} v_1 & v_2 & v_3 \\ v_1 & c_0 + c_x & -c_x \\ v_2 & -c_x & c_0 + 2c_x & -c_x \\ v_3 & & -c_x & c_0 + c_x \end{bmatrix} \longrightarrow$$

$$\mathbf{C}:\begin{bmatrix} v_1 & v_2 & v_2' & v_3 & i_{2,2}' \\ \hline v_1 & c_0 + c_x & -c_x & & & \\ v_2 & -c_x & 2c_0 + c_x & & & +1 \\ v_2' & & & 2c_0 + c_x & -c_x & -1 \\ v_3 & & & & -c_x & c_0 + c_x \\ i_{2,2}' & & -1 & +1 \end{bmatrix}$$

respectively, where  $g_0$  and  $c_0$  are the self-conductance and self-capacitance respectively at each node. Since the resistor and the capacitor are represented by nodal voltage, such a node splitting can be efficiently applied to decouple the RC network. The node splitting, however, cannot handle inductance or its inverse element because inductance is described by branch current. It is quite possible that two branch currents at two partitioned blocks are still coupled by mutual inductance.

#### 4.2.2 Stretching of branch currents

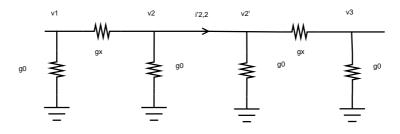

We call the entries of  $\mathbf{L}^{-1}$  the susceptor, which includes the self-susceptor  $k_0$  and the mutual susceptor  $k_x$ . To cleanly decouple the inductive couplings between two partitioned blocks, a matrix stretching of inductive-branch currents can be described by the following rule.

Rule 2: Assume that two inductive branches  $b_i$  and  $b_j$  are coupled by a mutual susceptor  $k_x$ . Branch  $b_i$  has nodal voltages  $(v_1, v_2)$  and  $b_j$  has nodal voltages  $(v_3, v_4)$ . Moreover,  $b_i$  has a branch flux  $\phi_i$  and  $b_j$  has a branch flux  $\phi_j$ . These can be decoupled by introducing an auxiliary state variable  $\phi_{ij}$  that describes the flux difference by  $\phi_{ij} = \phi_i - \phi_j$ .

Figure 5: circuit with one mutual inductance

The following transformations from the old  $\mathcal{G}$  and  $\mathcal{C}$  to the new **G** and **C** illustrates how to separate two blocks which are coupled with mutual inductance:

$$\mathcal{G}:\begin{bmatrix} \frac{v_1 \quad v_2 \quad \phi_i \quad v_3 \quad v_4 \quad \phi_j}{v_1 \quad G_1 \quad 0 \quad k_0 & & k_x} \\ v_2 \quad 0 \quad G_2 \quad -k_0 & & -k_x \\ \phi_i \quad -k_0 \quad k_0 \quad 0 \quad -k_x \quad k_x \quad 0 \\ v_3 \quad & k_x \quad G_3 \quad 0 \quad k_0 \\ v_4 \quad & -k_x \quad 0 \quad G_4 \quad -k_0 \\ \phi_j \quad -k_x \quad k_x \quad 0 \quad -k_0 \quad k_0 \quad 0 \end{bmatrix} \longrightarrow$$

$$\mathbf{G}:\begin{bmatrix} \frac{v_1 \quad v_2 \quad \phi_i \quad v_3 \quad v_4 \quad \phi_j \quad \phi_{ij}}{v_1 \quad G_1 \quad 0 \quad k'_0 & & -k_x \\ v_2 \quad 0 \quad G_2 \quad -k'_0 & & k_x \\ \phi_i \quad -k'_0 \quad k'_0 \quad 0 & & 0 \\ v_3 \quad & G_3 \quad 0 \quad k'_0 \quad k_x \\ \phi_i \quad -k'_0 \quad k'_0 \quad 0 & & 0 \\ v_4 \quad & 0 \quad G_4 \quad -k'_0 \quad -k_x \\ \phi_j \quad & -k'_0 \quad k'_0 \quad 0 & 0 \\ \phi_{ij} \quad k_x \quad -k_x \quad 0 \quad -k_x \quad k_x \quad 0 \quad 0 \end{bmatrix}$$

and

$$\mathbf{C}: \begin{bmatrix}

\frac{v_1 & v_2 & \phi_i & v_3 & v_4 & \phi_j \\

v_1 & 0 & 0 & 0 & & 0 \\

v_2 & 0 & 0 & 0 & & 0 \\

\phi_i & 0 & 0 & k_0 & 0 & 0 & k_x \\

v_3 & & 0 & 0 & 0 & 0 \\

\phi_j & 0 & 0 & k_x & 0 & 0 & k_0

\end{bmatrix} \longrightarrow \\

\mathbf{C}: \begin{bmatrix}

\frac{v_1 & v_2 & \phi_i & v_3 & v_4 & \phi_j & \phi_{ij}}{v_1 & 0 & 0 & 0 & & 0 \\

\phi_i & 0 & 0 & k'_0 & & 0 \\

\phi_i & 0 & 0 & k'_0 & & 0 \\

\psi_3 & & 0 & 0 & 0 & 0 \\

\phi_j & & 0 & 0 & k'_0 & 0 \\

\phi_{ij} & 0 & 0 & 0 & 0 & 0 & -k_x

\end{bmatrix}$$

respectively, where  $k_0'=k_0+k_x$  . Note that Rule 2 obtains an equivalent solution by finding a summed equivalent state matrix

$$\mathcal{G} + s\mathcal{C} \to \mathbf{G} + s\mathbf{C}.$$

(22)

This is due to the following node-branch relations in Eq. (14):

$$v_1{}^i - v_2{}^i = s\Phi_i, \quad v_1{}^j - v_2{}^j = s\Phi_j.$$

(23)

## 4.3 VNA matrix with BBD structure

The node splitting is applied to split the connected resistive or capacitive branches between two coupled blocks, while the branch tearing is applied to tear the coupled inductive branches between two coupled blocks. The resulting m blocks with no coupling in between are at the bottom level of the BBD, and are represented by  $\mathbf{M}_i(i = 1, ..., m)$ . The top level is the global interconnection block represented by  $\mathbf{M}_0$ , which is connected with one diagonal block  $\mathbf{M}_i(i \neq 0)$  by the corresponding connection matrix  $\mathbf{X}_{i,0}$ . The interconnection block has size  $n_0$  and contains all coupling branches between any pair of blocks at the bottom level.

Precisely, the resulting system equation is

$$(\mathbf{G} + s\mathbf{C})\mathbf{x}(s) = \mathbf{B}\mathbf{u}(s) \tag{24}$$

where

$$\mathbf{G} : \begin{bmatrix} \mathcal{G}_{1,1} & 0 & \cdots & 0 & \mathbf{X}_{1,0}^{g} \\ 0 & \mathcal{G}_{2,2} & \cdots & 0 & \mathbf{X}_{2,0}^{g} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ 0 & 0 & \cdots & \mathcal{G}_{m,m} & \mathbf{X}_{m,0}^{g} \\ -(\mathbf{X}_{1,0}^{g})^{T} & -(\mathbf{X}_{2,0}^{g})^{T} & \cdots & -(\mathbf{X}_{m,0}^{g})^{T} & \mathcal{G}_{0,0} \end{bmatrix}$$

$$\mathbf{C} : \begin{bmatrix} \mathcal{C}_{1,1} & 0 & \cdots & 0 & \mathbf{X}_{1,0}^{c} \\ 0 & \mathcal{C}_{2,2} & \cdots & 0 & \mathbf{X}_{2,0}^{c} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ 0 & 0 & \cdots & \mathcal{C}_{m,m} & \mathbf{X}_{m,0}^{c} \\ -(\mathbf{X}_{1,0}^{c})^{T} & -(\mathbf{X}_{2,0}^{c})^{T} & \cdots & -(\mathbf{X}_{m,0}^{c})^{T} & \mathcal{C}_{0,0} \end{bmatrix}$$

$$\mathbf{B} : \begin{bmatrix} 0 \\ 0 \\ \vdots \\ 0 \\ \mathcal{B}_{0} \end{bmatrix}$$

and  $\mathbf{x} = [x_1, x_2, ..., x_m, x_0]^T$ ,  $\mathbf{u} = [u_1, u_2, ..., u_m, 0]^T$ , where  $\mathbf{G}, \mathbf{C} \in \mathbb{R}^{N \times N}$ , and  $\mathbf{B} \in \mathbb{R}^{N \times n_p}$ . For each block  $\mathbf{M}_i$ , the state variable  $\mathbf{x}_i$  includes the nodal voltage  $v_n$  for the block conductance and capacitance, and the magnetic flux  $\Phi$ . Its first-order VNA admittance is  $\mathcal{G}_{ii} + s\mathcal{C}_{ii} (\in \mathbb{R}^{n_i \times n_i})$ , and  $\mathcal{B}_i$  is 0.

The diagonal blocks  $\mathbf{M}_i$  are interconnected with  $\mathbf{M}_0$  by the torn branches  $\mathbf{X}_{i0}^{q,c}$  $(\in \mathbb{R}^{n_i \times n_0})$  in the border. For the global interconnection block  $\mathbf{M}_0$  at the bottom, the state variable includes the interfacing current variables for resistive or capacitive node splitting and the new state variable describing the flux difference for inductive branch tearing. Its first-order VNA admittance is  $(\mathbf{G})_{0,0} + s(\mathbf{C})_{0,0}$  ( $\in \mathbb{R}^{n_0 \times n_0}$ ). In addition, all external sources are counted by  $\mathbf{B}_0$  for  $\mathbf{M}_0$ .

Note that  $\mathcal{B}_i$  in original method presented in Ref. [5] is different than the one described here. In original method,  $\mathcal{B}_i$   $(i \neq 0)$  are not 0, but contains port information of corresponding sub-circuit *i* and  $\mathcal{B}_0$  is 0 because all external sources are

counted by  $\mathcal{B}_i$  for block  $\mathbf{M}_i$  (i=1,...,m) and there are no external sources in  $\mathbf{M}_0$ . The **B** in original form is

$$\mathbf{B} : \begin{bmatrix} \mathcal{B}_{1} & 0 & \cdots & 0 & 0 \\ 0 & \mathcal{B}_{2} & \cdots & 0 & 0 \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ 0 & 0 & \cdots & \mathcal{B}_{m} & 0 \\ 0 & 0 & \cdots & 0 & 0 \end{bmatrix}$$

Let us take the circuit of Fig. 1 as an example. In the beginning, partition the circuit at dc into user-specified m blocks (here, for simplicity, m=2) using hypergraph and hmetis algorithm (See Section 5.2). State matrices of two blocks are generated. The node-split procedure is applied to the two blocks. Node  $v_1$  is splitted into node  $v_1$  and duplicate node  $v'_1$ , node  $v_3$  is splitted into node  $v_3$  and duplicate node  $v'_3$ . The main block contains nodes and external ports, denoted by  $\mathbf{G}_{\text{main}}, \mathbf{C}_{\text{main}}$ and  $\mathbf{B}_{\text{main}}$ ; sub block contains duplicate nodes, original nodes in the sub block and external ports, denoted by  $\mathbf{G}_{\text{sub}}, \mathbf{C}_{\text{sub}}$  and  $\mathbf{B}_{\text{sub}}$ . The main block is shown below. State matrix before arrow is the block after partition at dc, state matrix after arrow is the block applied by node split. Circuit after node splitting is illustrated in Fig. 6.

Figure 6: Two-port RLC circuit after node splitting

|                                | Γ          | $v_1$ | $v_3$ | $ext_1$ | $ext_2$ | ]          |               |

|--------------------------------|------------|-------|-------|---------|---------|------------|---------------|

|                                | $v_1$      | 0     | 0     | 1       | 0       | _          |               |

| $\mathbf{G}_{\mathrm{main}}$ : | $v_3$      | 0     | 0     | 0       | 1       | -          | $\rightarrow$ |

|                                | $ext_1$    | -1    | 0     | 0       | 0       |            |               |

|                                | $ext_2$    | 0     | -1    | 0       | 0       |            |               |

|                                | -          |       |       | ,       | ,       |            |               |

|                                |            | $v_1$ | $v_3$ | $ext_1$ | $ext_2$ | $i_{1,1'}$ | $i_{3,3'}$    |

|                                | $v_1$      | 0     | 0     | 1       | 0       | -1         | 0             |

|                                | $v_3$      | 0     | 0     | 0       | 1       | 0          | -1            |

| $G_{0,0}$ :                    | $ext_1$    | -1    | 0     | 0       | 0       | 0          | 0             |

|                                | $ext_2$    | 0     | -1    | 0       | 0       | 0          | 0             |

|                                | $i_{1,1'}$ | 1     | 0     | 0       | 0       | 0          | 0             |

|                                | $i_{3,3'}$ | 0     | 1     | 0       | 0       | 0          | 0             |

| $\mathbf{C}_{\mathrm{main}}$ : | $\begin{bmatrix} v_1 \\ v_3 \\ ext_1 \\ ext_2 \end{bmatrix}$                                  | $v_1 \\ 0 \\ 0 \\ 0 \\ 0$ |                 | $ext_1$ 0 0 0 0                                                          | $ext_2$<br>0<br>0<br>0                                                       | -]                                       | $\rightarrow$                                                          |

|--------------------------------|-----------------------------------------------------------------------------------------------|---------------------------|-----------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------|

| $\mathbf{C}_{0,0}$ :           | $\begin{bmatrix} ext_2 \\ v_1 \\ v_3 \\ ext_1 \\ ext_2 \\ i_{1,1'} \\ i_{3,3'} \end{bmatrix}$ | $\frac{v_1}{0}$           | $\frac{v_3}{0}$ | $\begin{array}{c} 0\\ \underline{ext_1}\\ 0\\ 0\\ 0\\ 0\\ 0 \end{array}$ | $\begin{array}{c} 0\\ \underline{ext_2}\\ 0\\ 0\\ 0\\ 0\\ 0 \end{array}$     |                                          | $\begin{array}{c} i_{3,3'} \\ \hline 0 \\ -1 \\ 0 \\ 0 \\ \end{array}$ |

| $\mathbf{B}_{	ext{main}}$ :    | $\begin{bmatrix} v_1 \end{bmatrix}$                                                           | $v_2$                     |                 | $\begin{array}{c} 0\\ 0\end{array}$ $\longrightarrow$ $\mathbf{B}_{0}$   | $ \begin{array}{c} 0\\ 0\\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ $ | $\begin{array}{c} 0 \\ 0 \\ \end{array}$ | $\begin{bmatrix} 0 \\ 0 \end{bmatrix}$                                 |

The block matrix of the subcircuit is:

Then arrange the main and sub block matrices in diagonal form:

|     |                                                                                 | $egin{array}{ccc} \mathbf{G}_{1,1} & \mathbf{X} \ \mathbf{X}_{1,0}^g)^T \end{array}$                  |                                                                                            |                                                                                           |                                                |                                                                        |                                                          |                                                          |                                                          |                                                          |                                                                                       |                                                                                        |  |

|-----|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| =   | $\begin{bmatrix} G_1 \\ -G_1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ -1 \\ 0 \end{bmatrix}$ | $\begin{array}{c} -G_1 \\ G_1 \\ 0 \\ -L^{-1} \\ \hline 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\$ | $\begin{array}{c} 0 \\ 0 \\ G_2 \\ L^{-1} \\ \hline 0 \\ 0 \\ 0 \\ 0 \\ -1 \\ \end{array}$ | $\begin{array}{c} 0 \\ L^{-1} \\ -L^{-} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $ | -1                                             | $ \begin{array}{c} 0 \\ 0 \\ 0 \\ 0 \\ -1 \\ 0 \\ 1 \\ 0 \end{array} $ |                                                          | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>1      | 0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0           | 0<br>0<br>0<br>0<br>1<br>0<br>0<br>0<br>0<br>0<br>0      | $ \begin{array}{c} 1 \\ 0 \\ 0 \\ -1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{array} $ | $\begin{array}{c} 0 \\ 0 \\ 1 \\ 0 \\ -1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ \end{array}$ |  |

| C = | $= \begin{bmatrix} 0\\ -(1) \end{bmatrix}$                                      | $egin{array}{ccc} { m C}_{1,1} & { m C}_{1,0} \ { m X}_{1,0}^c)^T \end{array}$                        | $\mathbf{X}_{1,0}^c$<br>$\mathbf{C}_{0,0}$                                                 |                                                                                           |                                                |                                                                        |                                                          |                                                          |                                                          |                                                          |                                                                                       |                                                                                        |  |

| —   | $\begin{bmatrix} C_1 \\ -C_1 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$  | $ \begin{array}{c} -C_{1} \\ C_{1} + C_{2} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{array} $ | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                      | $\begin{array}{c} 0 \\ 0 \\ L^{-1} \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ $      | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0               | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 | 0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0<br>0 |                                                                                       |                                                                                        |  |

| B = | $= \begin{bmatrix} \mathbf{B}_1 \\ \mathbf{B}_0 \end{bmatrix}$                  | ]                                                                                                     |                                                                                            |                                                                                           |                                                |                                                                        |                                                          |                                                          |                                                          |                                                          |                                                                                       |                                                                                        |  |

$$= \begin{bmatrix} 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ 0 & 0 \\ -1 & 0 \\ 0 & -1 \\ 0 & 0 \\ 0 & 0 \end{bmatrix}$$

## 4.4 BBD Solver

The size of the state matrix can be reduced by the model-order reduction by finding a set of orthonormalized projection vectors  $\mathbf{Q}$ . The projection is usually performed by the block Arnoldi procedure.

Directly using the block Arnoldi algorithm consumes a heavy computation to factorize the state matrix. BBD solver described below can be applied to reduce the computational cost during the block Arnoldi procedure.

Before using BBD solver, the BBD-structured state matrix  $\mathbf{G} + s\mathbf{C}$  should be decomposed into the diagonal  $\mathbf{M}$  and off-diagonal  $\mathbf{X}$  parts, where the diagonal part  $\mathbf{M}$  is

$$\mathbf{M} = \begin{bmatrix} \mathbf{M}_1 & 0 & \cdots & 0 \\ 0 & \ddots & \ddots & \vdots \\ \vdots & \ddots & \mathbf{M}_m & 0 \\ 0 & \cdots & 0 & \mathbf{M}_0 \end{bmatrix}$$

$$\mathbf{M}_i = \mathcal{G}_{i,i} + s\mathcal{C}_{i,i} \ (i = 1, ..., m)$$

and the off-diagnonal part  $\mathbf{X}$  is

$$\mathbf{X} = \begin{bmatrix} 0 & 0 & \cdots & -\mathbf{X}_1 \\ 0 & \ddots & \ddots & \vdots \\ \vdots & \ddots & 0 & -\mathbf{X}_m \\ -\mathbf{X}_1 & \cdots & -\mathbf{X}_m & 0 \end{bmatrix}$$

$$\mathbf{X}_i = \mathbf{X}_{i,0}^g + s\mathbf{X}_{i,0}^c \ (i = 1, ..., m)$$

Algorithm 2

1. Block LU-factorization to calculate  $x_k$

for every k in m(k++) do

(1.1) input:  $\mathbf{M}_k, \mathbf{X}_k, \mathcal{B}_k;$

(1.2) factor:  $\mathbf{M}_{k} = \mathbf{L}_{k}\mathbf{U}_{k}$ ; (1.3) solve:  $\mathbf{L}_{k}\Phi_{k} = \mathbf{X}_{k}$  for  $\Phi_{k}, \Psi_{k}\mathbf{U}_{k} = (\mathbf{X}_{k})^{T}$  for  $\Psi_{k}$ , and  $\mathbf{L}_{k}\xi_{k} = \mathcal{B}_{k}$  for  $\xi_{k}$ ; (1.4) form:  $\mathbf{F}_{k} = \Psi_{k}\Phi_{k}$ , and  $\mathbf{G}_{k} = \Psi_{k}\xi_{k}$ (1.5) output:  $\mathbf{F}_{k}, \mathbf{G}_{k}$ .

end for

2. Update interconnection  $\mathbf{x}_0$

(2.1) input:  $\mathbf{M}_0, \mathbf{F}_k, \mathbf{G}_k;$

- (2.2) form:  $\mathbf{F} = \mathbf{M}_0 + \sum_{k=1}^m \mathbf{F}_k, \mathbf{G} = \sum_{k=1}^m \mathbf{G}_k$

- (2.3) solve:  $\mathbf{F}\mathbf{x}_0 = \mathbf{G}$  for  $\mathbf{x}_0$ ;

(2.4) output:  $\mathbf{x}_0$ .

3. Block-backward substitution of  $x_k$

for every k in m(k - -) do

(3.1) input:  $\mathbf{x}_0, \Phi_k, \xi_k, \mathbf{U}_k$ ; (3.2) form:  $\xi_k = \xi_k - \Phi_k \mathbf{x}_0$ (3.3) solve:  $\mathbf{U}_k \mathbf{x}_k = \xi_k$  for  $\mathbf{x}_k$ (3.4) output:  $\mathbf{x}_k$

end for

The overall procedure is outlined above. Each block matrix  $\mathbf{M}_i (i = 1, ..., m)$  is first solved individually with LU factorization and substitution (1.1-1.5). The results  $\mathbf{x}_i (i = 1, ..., m)$  from each reduced block are then further used to solve the coupling block  $\mathbf{M}_0$  for  $\mathbf{x}_0$  (2.1-2.4). The final  $\mathbf{x}_i$  of each reduced block is updated (3.1-3.4) with the result from the coupling current.

### 4.5 Block Arnoldi procedure

The new block-Arnoldi orthonormalization enhanced by the BBD solver is presented below, this is also considered as another way to implement Block Arnoldi procedure comparing with PRIMA shown in Section 3.1 :

Algorithm 3

(1.1) input: **G**, **C**, **B**;

- (1.2) BBD-solve:  $(\mathbf{G} + s_0 \mathbf{C}) \mathbf{Q}^{(0)} = \mathbf{B}$  for  $\mathbf{Q}^{(0)}$

- (1.3) orthonormalize: each column in  $\mathbf{Q}^{(0)}$ ;

for every i in  $N_q - 1$  do

- (1.4) BBD-solve:  $(\mathbf{G} + s_0 \mathbf{C})\mathbf{Q}^{(i)} = \mathbf{C}\mathbf{Q}^{(i-1)}$  for  $\mathbf{Q}^{(i)}$ ;

- (1.5) orthogonalize:  $\mathbf{Q}^{(i)}$  to all  $\mathbf{Q}^{(j)}$  (j = 0, ..., i 1);

- (1.6) orthonormalize: each column in  $\mathbf{Q}^{(i)}$ ;

end for

- (1.7) compose:  $\mathbf{Q} = [\mathbf{Q}^{(0)}, \mathbf{Q}^{(1)}, ..., \mathbf{Q}^{(N_q-1)}];$

- (2.1) partition:  $\mathbf{Q} :\longrightarrow \mathbf{Q}_{0_{n_0 \times n_{p_0}}}, ..., \mathbf{Q}_{m_{n_m \times n_{p_m}}}$

for every j in m do

- (2.2) merge:  $\mathbf{Q}_i$  and  $\mathbf{Q}_{i+1}$  till a new  $\mathbf{Q}'_i$  is nonsingular;

- (2.2) orthonormalize: each column in  $\mathbf{Q}_i$ ;

end for

(2.3) compose:

$$\mathbf{Q} = diag[\mathbf{Q}_1, ..., \mathbf{Q}_m, \mathbf{Q}_0];$$

The order-reduced state matrices by  ${\bf Q}$  become

$$\widetilde{\mathbf{G}} = \mathbf{Q}^T \mathbf{G} \mathbf{Q}, \ \widetilde{\mathbf{C}} = \mathbf{Q}^T \mathbf{C} \mathbf{Q}, \ \widetilde{\mathbf{B}} = \mathbf{Q}^T \mathbf{B}$$

(25)

where

$$\widetilde{\mathbf{G}}_{i,j} = \mathbf{Q}_i^T \mathbf{G}_{i,j} \mathbf{Q}_j, \ \widetilde{\mathbf{C}}_{i,j} = \mathbf{Q}_i^T \mathbf{C}_{i,j} \mathbf{Q}_j, \ \widetilde{\mathbf{B}}_i = \mathbf{Q}_i^T \mathbf{B}_i$$

As a result, the transfer function is

$$\widetilde{\mathbf{H}}(s) = \widetilde{\mathbf{B}}^T [\widetilde{\mathbf{G}} + s\widetilde{\mathbf{C}}]^{-1} \widetilde{\mathbf{B}}.$$

We call this reduction the BVOR (BBD-based VOR) method.

### 4.6 Q constructed with individual diagonal block

The structured projection matrix  $\mathbf{Q}$  discussed in previous section is constructed with full BBD matrix as input. This section will, however, discuss another way to generate this projection matrix  $\mathbf{Q}$ , presented in Ref [9].

The structure of the  $\mathbf{Q}$  is

$$\mathbf{Q} = diag[\mathbf{Q}_1, \mathbf{Q}_2, ..., \mathbf{Q}_0] \tag{26}$$

where  $\mathbf{Q}_i \in \mathbb{R}^{n_{b_i} \times N_q}$  (1  $\leq i \leq m$ ).

Each projection block  $\mathbf{Q}_i$  is constructed from each diagonal block in  $\mathcal{G}_{i,i} + s\mathcal{C}_{i,i}$ independently, i.e.  $\mathcal{G}_{i,i} + s\mathcal{C}_{i,i} = \mathcal{B}_i$ . Note that  $\mathbf{Q}_0$  is replaced with an identity matrix  $\mathbf{I}_0 \ (\in \mathbb{R}^{n_0 \times n_0})$  to avoid the zero diagonal entries in original  $\mathbf{Q}_0$ ; and  $\mathbf{B}_i \ (i \neq 0)$  is different as the one in full BBD structure. In full BBD matrix,  $\mathbf{B}_i (i \neq 0)$  is empty, corresponding port information is deleted; here  $\mathbf{B}_i (i \neq 0)$  contains original port information of the corresponding sub-circuit i.

The main benefit of using this type of  $\mathbf{Q}$  is that only the diagonal blocks of the original BBD matrix are utilized, thus computational time is saved.

Algorithm to generate the  $\mathbf{Q}$  with individual diagonal block is presented below algorithm

Algorithm 4

for every i in m do

- (1.1) input:  $\mathbf{G}_{i,i}, \mathbf{C}_{i,i}, \mathbf{B}_i \ (i \neq 0);$

- (1.2) solve:  $(\mathbf{G}_{i,i} + s_0 \mathbf{C}_{i,i}) \mathbf{Q}^{(0)} = \mathbf{B}_i$  for  $\mathbf{Q}^{(0)}$

- (1.3) orthonormalize: each column in  $\mathbf{Q}^{(i)}$ ;

for every k in  $N_q - 1$  do

- (1.4) solve:  $(\mathbf{G}_{i,i} + s_0 \mathbf{C}_{i,i}) \mathbf{Q}^{(k)} = \mathbf{C}_{i,i} \mathbf{Q}^{(k-1)}$  for  $\mathbf{Q}^{(k)}$ ;

- (1.5) orthogonalize:  $\mathbf{Q}^{(k)}$  to all  $\mathbf{Q}^{(j)}$  (j = 0, ..., k 1);

- (1.6) orthonormalize: each column in  $\mathbf{Q}^{(k)}$ ;

end for

end for

(1.7) compose:

$$\mathbf{Q}_i = [\mathbf{Q}^{(0)}, \mathbf{Q}^{(1)}, ..., \mathbf{Q}^{(N_q-1)}] (i \neq 0);$$

(2.1) compose:  $\mathbf{Q} = diag[\mathbf{Q}_1, ..., \mathbf{Q}_m, \mathbf{Q}_0]$

## 5 Macromodel realization

The reduced state matrices are used to describe the linear RLC network in frequency domain. For the purpose of transient analysis of the whole nonlinear circuit, the reduced linear part should be linked to the whole circuit. The linkage can be done by using the macromodels realization for the reduced state matrices.

There are several macromodel realization methods: Matsumoto [6], direct stamping I [7] & II [14], transfer-function realization [1], differential-equation macromodel [1] etc. In Ref. [1] it was also found out that Matsumoto's method was the fastest equivalent circuit realization of these reduced-order interconnect macromodels studied for time-domain simulation.

At first, let us replace  $\mathcal{G}$ ,  $\mathcal{C}$  and  $\mathcal{B}$  with reduced  $\widetilde{\mathbf{G}}$ ,  $\widetilde{\mathbf{C}}$  and  $\widetilde{\mathbf{B}}$  in Eq. (1). Thus new equation is:

$$\begin{cases} \widetilde{\mathbf{C}} \frac{\mathrm{d}\widetilde{\mathbf{x}}(t)}{\mathrm{d}t} = -\widetilde{\mathbf{G}}\widetilde{\mathbf{x}}(t) + \widetilde{\mathbf{B}}\mathbf{u}(t), \\ \mathbf{i}(t) = \widetilde{\mathbf{B}}^{\mathrm{T}}\widetilde{\mathbf{x}}(t), \end{cases}$$

(27)

Before performing the actual macromodel realization, some preprocessing is needed, namely eigenvalue decomposition.

Next, the first equation of Eq. (27) is premultiplied with  $\tilde{\mathbf{G}}^{-1}$ . Assuming that a basis of eigenvectors exists for the matrix  $\tilde{\mathbf{G}}^{-1}\tilde{\mathbf{C}}$ , it can be written as  $\tilde{\mathbf{G}}^{-1}\tilde{\mathbf{C}} =$  $\mathbf{S}\mathbf{A}\mathbf{S}^{-1}$ , where  $\mathbf{\Lambda}$  is a diagonal matrix containing the eigenvalues of  $\tilde{\mathbf{G}}^{-1}\tilde{\mathbf{C}}$  as its diagonal elements and  $\mathbf{S}$  has the corresponding q eigenvectors as its columns. After premultiplying with  $\mathbf{S}^{-1}$ , Eq. (27) can be written as

$$\begin{cases} \mathbf{S}^{-1} \mathbf{S} \mathbf{\Lambda} \mathbf{S}^{-1} \frac{\mathrm{d} \tilde{\mathbf{x}}(t)}{\mathrm{d} t} = -\mathbf{S}^{-1} \tilde{\mathbf{x}}(t) + -\mathbf{S}^{-1} \widetilde{\mathbf{G}}^{-1} \widetilde{\mathbf{B}} \mathbf{u}(t), \\ \mathbf{i}(t) = \widetilde{\mathbf{B}}^{\mathrm{T}} \mathbf{S} \mathbf{S}^{-1} \tilde{\mathbf{x}}(t), \end{cases}$$

(28)

or, if a change of variables  $S^{-1}\widetilde{\mathbf{x}} \longrightarrow \widetilde{\mathbf{x}}$  (using  $\widetilde{\mathbf{x}}$  again for ease of notation) is assumeed, as

$$\begin{cases} \mathbf{\Lambda} \frac{\mathrm{d} \mathbf{\tilde{x}}(t)}{\mathrm{d} t} = -\mathbf{I} \mathbf{\tilde{x}}(t) + \mathbf{H} \mathbf{u}(t), \\ \mathbf{i}(t) = \mathbf{E}^{\mathrm{T}} \mathbf{\tilde{x}}(t), \end{cases}$$

(29)

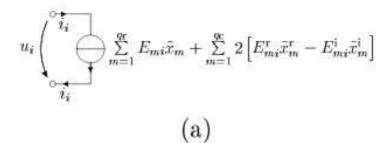

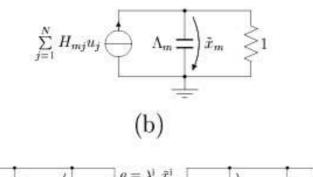

where  $\mathbf{H} = \mathbf{S}^{-1} \widetilde{\mathbf{G}}^{-1} \widetilde{\mathbf{B}}$ ,  $\mathbf{E} = \mathbf{S}^{T} \widetilde{\mathbf{B}}$ , and  $\mathbf{I}$  is the  $q \times q$  unity matrix. Note that Eq. (29) has the same dimensions as Eq. (27), but the coefficient matrices  $\boldsymbol{\Lambda}$  and  $\mathbf{I}$  are now diagonal. For the forthcoming treatment of complex eigenvalues, the m:th row in the first equation of Eq. (29) is written as

$$\Lambda_m \frac{\mathrm{d}\tilde{x}_m(t)}{\mathrm{d}t} = -\tilde{x}_m(t) + \sum_{j=1}^N H_{mj} u_j(t), \qquad (30)$$

Some of the eigenvalues of the real matrix  $\mathbf{G}^{-1}\widetilde{\mathbf{C}}$  may be complex numbers, in which case they appear in complex-conjugate pairs. Assuming that  $q_r$  of the eigenvalues are real and the rest appear in  $q_c$  conjugate pairs such that  $q = q_r + 2q_c$ .

Consider one such pair,  $\Lambda_m^r \pm j \Lambda_m^i$ . The corresponding eigenvectors, and therefore, also the corresponding rows of matrices **H** and **E** in Eq. (29) are complex conjugate. Let the corresponding elements of vector  $\tilde{\mathbf{x}}$  be  $\tilde{x}_m^r \pm j\tilde{x}_m^r$ . Inserting these into Eq. (30), and requiring the real and imaginary parts of the equation to hold independently, yields (the same pair of equations is obtained twice).

$$\begin{cases}