#### **Dmitri Leino**

# 10 Gigabit-capable Passive Optical Network Transmission Convergence layer design

#### Faculty of Electronics, Communications and Automation

Thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Technology in Espoo, 23 April 2010.

**Supervisor:**

Professor Olav Tirkkonen, Aalto University

**Instructor:**

M.Sc. Risto Soila, Tellabs Oy

AALTO UNIVERSITY SCHOOL OF SCIENCE AND TECHNOLOGY ABSTRACT OF THE MASTER'S THESIS

Author: Dmitri Leino

Title: 10 Gigabit-capable Passive Optical Network Transmission

Convergence layer design

Date: 23 April 2010 Language: English Number of pages: 12+106

Faculty of Electronics, Communications and Automation

Department of Communications and Networking

Professorship: Communications Systems Code: S-72

Supervisor: Professor Olav Tirkkonen, Aalto University

Instructor: M.Sc. Risto Soila, Tellabs Oy

With the emergence of new broadband telecommunication services and constantly increasing bandwidth demand, fixed access network infrastructure is evolving from electrical to optical. The European Commission funded research project Scalable Advanced Ring-based passive Dense Access Network Architecture (SARDANA) researches the next-generation passive optical access network technologies. The main goal of the project is to reduce expenses that are related to passive optical access networks.

This master's thesis discusses the design of the non-standardized 10 Gigabit-capable Passive Optical Network (XGPON) Transmission Convergence (TC) layer and its first implementation version for Optical Network Unit (ONU) for the SARDANA test network. The SARDANA XGPON TC (SXGTC) layer implements the Medium Access Control (MAC) protocol. The SXGTC layer is based on the standardized solution offered by the ITU-T G.984.3 Gigabit-capable Passive Optical Network (GPON) TC (GTC) layer recommendation [ITU08] but differs from it in many details. All the SXGTC layer features are compared to those of the GTC layer.

As a result, the SXGTC protocol is able to support operation on up to 9.95328 Gbps symmetrical transmission rates. The SXGTC layer is optimized for the 8-byte-word-based data processing. The first ONU SXGTC layer Field Programmable Gate Array (FPGA) implementation is presented in terms of functional blocks. The implementation supports operation on 9.95328 Gbps in the downstream offering 98 % bandwidth efficiency and on 2.48832 Gbps in the upstream offering 94.5 % bandwidth efficiency for the SARDANA test network configuration.

Keywords: Gigabit-capable passive optical network, GPON, 10 GPON, XGPON, Medium Access Control protocol, MAC, FPGA, access network

#### AALTO-YLIOPISTO TEKNILLINEN KORKEAKOULU

DIPLOMITYÖN TIIVISTELMÄ

Tekijä: Dmitri Leino

Työn nimi: 10 Gigabit-capable Passive Optical Network Transmission

Convergence kerroksen suunnittelu

Päivämäärä: 23. huhtikuuta 2010 Kieli: Englanti Sivumäärä: 12+106

Elektroniikan, tietoliikenteen ja automation tiedekunta

Tietoliikenne- ja tietoverkkotekniikan laitos

Professuuri: Tietoliikennejärjestelmät Koodi: S-72

Valvoja: Professori Olav Tirkkonen, Aalto-yliopisto

Ohjaaja: DI Risto Soila, Tellabs Oy

Uusien laajakaistaisten tietoliikennepalvelujen ja kasvavan tiedonsiirtokapasiteetin tarpeen myötä kiinteiden liityntäverkkojen infrastruktuuri on muuttumassa sähköisestä optiseksi. Euroopan komission rahoittamassa Scalable Advanced Ringbased passive Dense Access Network Architecture (SARDANA)-tutkimusprojektissa tutkitaan seuraavan sukupolven passiivisten optisten liityntäverkojen teknologioita. Projektin päätavoitteena on pienentää passiivisiin optisiin liityntäverkkoihin liittyviä kustannuksia.

Tämä diplomityö käsittelee SARDANA-testiverkon standardoimattoman 10 Gigabit-capable Passive Optical Network (XGPON) Transmission Convergence (TC)-kerroksen suunnittelua ja ensimmäistä toteutusta optisessa verkkopäätteessä (ONU:ssa). TC-kerros toteuttaa Medium Access Control (MAC)-protokollan. SARDANA XGPON TC (SXGTC)-kerros perustuu standardoituun ITU-T G.984.3 Gigabit-capable Passive Optical Network (GPON) TC (GTC)-kerroksen [ITU08] tarjoamaan ratkaisuun mutta eroaa tästä yksityiskohdiltaan. Kaikki SXGTC-kerroksen oleelliset yksityiskohdat peilataan GTC-kerrokseen.

Suunniteltu SXGTC-protokolla tukee maksimissaan 9.95328 Gbps:n symmetrisiä tiedonsiirtonopeuksia. SXGTC-protokolla on optimoitu käsittelemään dataa 8 tavun sanoissa. Ensimmäinen ONU SXGTC-kerroksen toteutus ohjelmoitavassa Field Programmable Gate Array (FPGA)-piirissä esitellään funktionaalisten lohkojen avulla. Tämän implementaation tiedonsiirtonopeus alasuunnassa on 9.95328 Gbps 98 %:n kaistatehokkuudella ja yläsuunnassa 2.48832 Gbps 94.5 %:n kaistatehokkuudella SARDANA-testiverkkokonfiguraation tapauksessa.

Avainsanat: Gigabit-capable passive optical network, GPON, 10GPON, XGPON, Medium Access Control protokolla, MAC, FPGA, SARDANA, liityntäverkko

# Acknowledgements

This thesis was written in Systems Engineering group of R&D department, Tellabs Oy, Espoo, Finland while participating in the European Commission funded research project Scalable Advanced Ring-based passive Dense Access Network Architecture (SARDANA) (proj. no. 217122).

I would like to express my gratitude to my project manager and instructor Risto Soila for his help, support, and discussions on the thesis topic. I also own great thanks to my FPGA designer colleagues in Dallas, Jim Gainer and Kerry Konecny, for valuable FPGA implementation related phone discussions and email exchange. I would also like to thank Jari Mutikainen for introducing me to Verilog HDL. Furthermore, great thanks belong to my family for their huge support.

23 April 2010, Espoo, Finland

Dmitri Leino

# **Table of contents**

| A  | bstract | of the Master's thesis                                            | ii   |

|----|---------|-------------------------------------------------------------------|------|

| D  | iplomit | yön tiivistelmä                                                   | iii  |

| A  | cknowl  | edgements                                                         | iv   |

| T  | able of | contents                                                          | v    |

| S  | ymbols  |                                                                   | viii |

| A  | bbrevia | ntions                                                            | ix   |

| 1  | Intr    | oduction                                                          | 1    |

| 2  | Pass    | sive Optical Access Networks                                      | 4    |

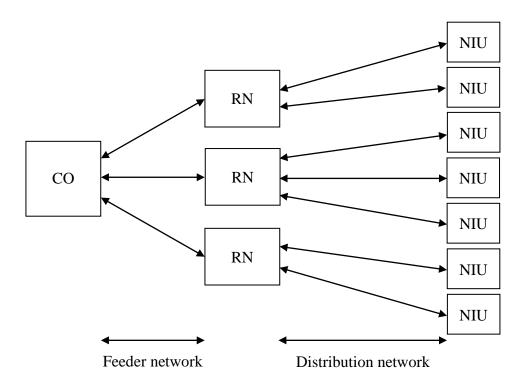

|    | 2.1     | Access network                                                    | 4    |

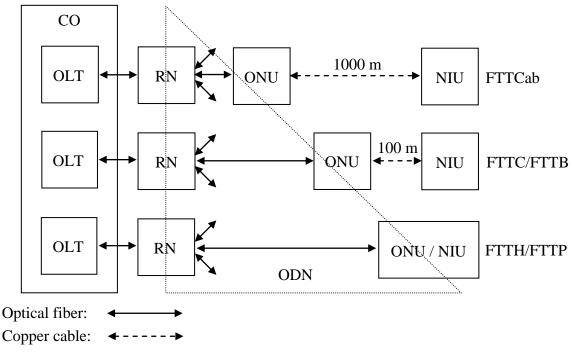

|    | 2.2     | Fiber-To-The-x (FTTx)                                             | 5    |

|    | 2.3     | Passive Optical Network (PON)                                     | 7    |

|    | 2.4     | Passive Optical Network architectures                             | 7    |

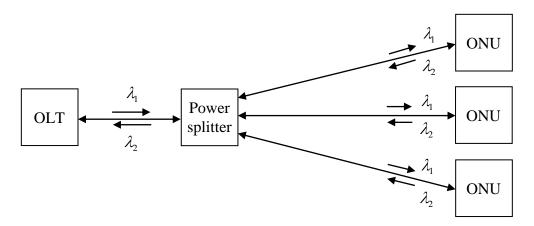

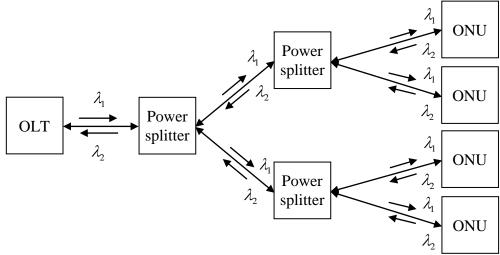

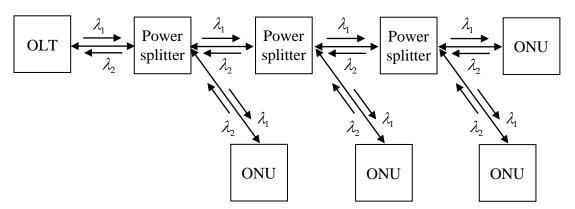

|    | 2.4.1   | Time Division Multiplexed Passive Optical Network (TDM-PON)       | 7    |

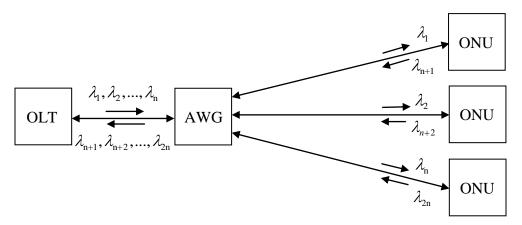

|    | 2.4.2   | Wavelength Division Multiplexed Passive Optical Network (WDM-PON) | 10   |

|    | 2.4.3   | TDM-PON vs. WDM-PON                                               | 11   |

|    | 2.5     | Passive Optical Network standards                                 | 11   |

|    | 2.5.1   | Broadband Passive Optical Network (BPON)                          | 12   |

|    | 2.5.2   | Gigabit-capable Passive Optical Network (GPON)                    | 12   |

|    | 2.5.3   | Ethernet Passive Optical Network (EPON)                           | 13   |

|    | 2.5.4   | 10 Gigabit Ethernet Passive Optical Network (10GEPON)             | 13   |

|    | 2.5.5   | 10 Gigabit-capable Passive Optical Network (XGPON)                | 13   |

|    | 2.5.6   | Commercialization of Passive Optical Networks                     | 14   |

|    | 2.6     | Evolution from TDM-PON to WDM-PON                                 | 14   |

|    | 2.7     | Summary                                                           | 15   |

|    |         | able Advanced Ring-based Passive Dense Area Network Architecture  |      |

| (2 |         | NA) Research Project                                              |      |

|    | 3.1     | SARDANA project overview                                          |      |

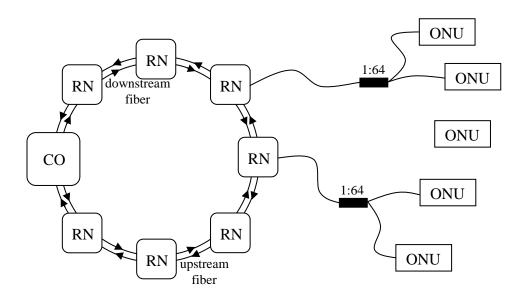

|    | 3.2     | SARDANA network architecture                                      |      |

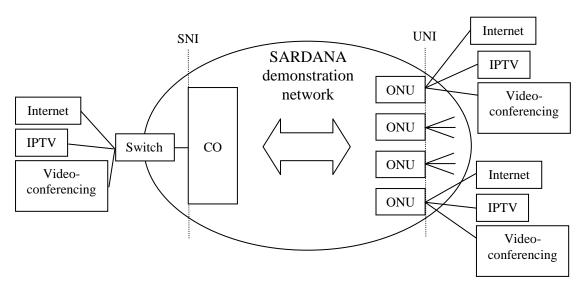

|    | 3.3     | SARDANA test and demonstration network                            |      |

|    | 3.4     | SARDANA Central Office (CO)                                       |      |

|    | 3.5     | SARDANA Optical Line Terminal (OLT)                               |      |

|    | 3.6     | SARDANA feeder and distribution networks                          |      |

|    | 37      | SARDANA Remote Node (RN)                                          | 23   |

| 3.9         Summary         25           4         FPGA-based Digital System Design         26           4.1         Complex digital system design options         26           4.2         Generic FPGA architecture         28           4.3         FPGA clock frequency and data rate         28           4.4         FPGA-based digital system design goals         30           4.5         Reprogrammable FPGA design flow         31           4.6         Summary         34           5         SARDANA 10 Gigabit-capable Passive Optical Network Transmission         36           Convergence Layer: Logical Model         35           5.1         SXGTC protocol stack         35           5.2         SXGTC layer transmission and framing mechanisms         37           5.2.1         SXGTC layer service Data Units (SDUs)         37           5.2.2         SXGEM framing principle         38           5.2.4         Upstream SXGTC framing principle         38           5.2.5         User and OMCI frame fragmentation         40           5.3.1         In the downstream         40           5.3.2         In the upstream         41           5.3.3         ONU ranging         45           5.4                                                                                                                      |   | 3.8    | SARDANA Optical Network Unit (ONU)                            | 23 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|---------------------------------------------------------------|----|

| 4.1       Complex digital system design options       .26         4.2       Generic FPGA architecture.       .28         4.3       FPGA clock frequency and data rate.       .29         4.4       FPGA-based digital system design goals.       .30         4.5       Reprogrammable FPGA design flow.       .31         4.6       Summary.       .34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission         Convergence Layer: Logical Model.       .35         5.1       SXGTC protocol stack.       .35         5.2       SXGTC layer transmission and framing mechanisms.       .37         5.2.1       SXGTC layer service Data Units (SDUs).       .37         5.2.2       SXGEM framing principle.       .38         5.2.3       Downstream SXGTC framing principle.       .38         5.2.4       Upstream SXGTC framing principle.       .39         5.2.5       User and OMCI frame fragmentation.       .40         5.3.1       In the downstream.       .40         5.3.2       In the upstream.       .40         5.3.3       In the upstream.       .40         5.3.1       In the upstream.       .41         5.3.3       ONU SXGTC layer system in Control/Management                                                                                                                                   |   | 3.9    |                                                               |    |

| 4.1       Complex digital system design options       .26         4.2       Generic FPGA architecture.       .28         4.3       FPGA clock frequency and data rate.       .29         4.4       FPGA-based digital system design goals.       .30         4.5       Reprogrammable FPGA design flow.       .31         4.6       Summary.       .34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission         Convergence Layer: Logical Model.       .35         5.1       SXGTC protocol stack.       .35         5.2       SXGTC layer transmission and framing mechanisms.       .37         5.2.1       SXGTC layer service Data Units (SDUs).       .37         5.2.2       SXGEM framing principle.       .38         5.2.3       Downstream SXGTC framing principle.       .38         5.2.4       Upstream SXGTC framing principle.       .39         5.2.5       User and OMCI frame fragmentation.       .40         5.3.1       In the downstream.       .40         5.3.2       In the upstream.       .40         5.3.3       In the upstream.       .40         5.3.1       In the upstream.       .41         5.3.3       ONU SXGTC layer system in Control/Management                                                                                                                                   |   |        | •                                                             |    |

| 4.2       Generic FPGA architecture.       28         4.3       FPGA clock frequency and data rate.       29         4.4       FPGA-based digital system design goals.       30         4.5       Reprogrammable FPGA design flow.       31         4.6       Summary.       34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission         Convergence Layer: Logical Model       35         5.1       SXGTC layer transmission and framing mechanisms       37         5.2.1       SXGTC layer Service Data Units (SDUs)       37         5.2.2       SXGEM framing principle       38         5.2.4       Upstream SXGTC framing principle       38         5.2.4       Upstream SXGTC framing principle       39         5.2.5       User and OMCI frame fragmentation       40         5.3.1       In the downstream       40         5.3.2       In the upstream       41         5.3.3       ONU ranging       45         5.4       User and Control/Management Planes of ONU SXGTC layer system       46         5.4.1       ONU SXGTC layer system in User Plane       46         5.4.2       ONU SXGTC layer system in User Plane       47         5.5       Summary of SXGPON and                                                                                                                                  | 4 | FP(    | GA-based Digital System Design                                | 26 |

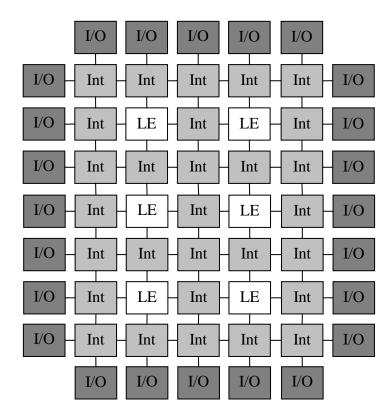

| 4.3       FPGA clock frequency and data rate       29         4.4       FPGA-based digital system design goals       30         4.5       Reprogrammable FPGA design flow       31         4.6       Summary       34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission       35         Convergence Layer: Logical Model       35         5.1       SXGTC protocol stack       35         5.2       SXGTC layer transmission and framing mechanisms       35         5.2.1       SXGTC layer service Data Units (SDUs)       37         5.2.2       SXGEM framing principle       38         5.2.3       Downstream SXGTC framing principle       38         5.2.4       Upstream SXGTC framing principle       39         5.2.5       User and OMCI frame fragmentation       40         5.3       SXGPON Medium Access Control (MAC) and flow multiplexing       40         5.3.1       In the upstream       41         5.3.2       In the upstream       41         5.3.3       ONU ranging       45         5.4       User and Control/Management Planes of ONU SXGTC layer system       46         5.4.1       ONU SXGTC layer system in User Plane       46         5.4.2       ONU S                                                                                                                               |   | 4.1    | Complex digital system design options                         | 26 |

| 4.4       FPGA-based digital system design goals.       30         4.5       Reprogrammable FPGA design flow.       31         4.6       Summary.       34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission       35         5.1       SXGTC protocol stack.       35         5.2       SXGTC layer transmission and framing mechanisms.       37         5.2.1       SXGTC layer Service Data Units (SDUs).       37         5.2.2       SXGEM framing principle.       38         5.2.3       Downstream SXGTC framing principle.       38         5.2.4       Upstream SXGTC framing principle.       39         5.2.5       User and OMCI frame fragmentation.       40         5.3.1       In the downstream.       40         5.3.2       In the upstream.       41         5.3.3       ONU ranging.       45         5.4       User and Control/Management Planes of ONU SXGTC layer system.       45         5.4.1       ONU SXGTC layer system in User Plane.       46         5.4.2       ONU SXGTC layer system in Control/Management Plane.       47         5.5       Summary of SXGPON and GPON logical model differences.       49         6       SARDANA 10 Gigabit-capable Passive Optical Network Transmissi                                                                                            |   | 4.2    |                                                               |    |

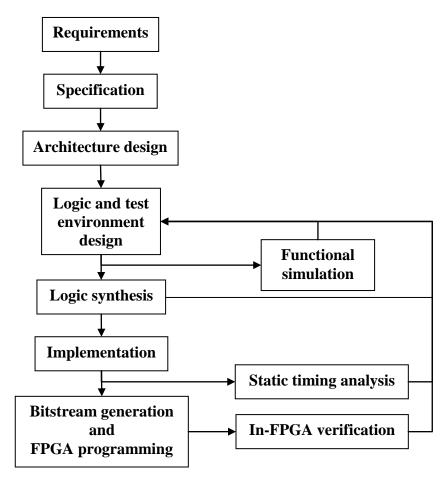

| 4.5       Reprogrammable FPGA design flow       31         4.6       Summary       34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission       35         Convergence Layer: Logical Model       35         5.1       SXGTC protocol stack       35         5.2       SXGTC layer transmission and framing mechanisms       37         5.2.1       SXGTC layer Service Data Units (SDUs)       37         5.2.2       SXGEM framing principle       37         5.2.3       Downstream SXGTC framing principle       38         5.2.4       Upstream SXGTC framing principle       39         5.2.5       User and OMCI frame fragmentation       40         5.3       SXGPON Medium Access Control (MAC) and flow multiplexing       40         5.3.1       In the downstream       40         5.3.2       In the upstream       40         5.3.3       ONU ranging       45         5.4       User and Control/Management Planes of ONU SXGTC layer system       46         5.4.1       ONU SXGTC layer system in User Plane       46         5.4.2       ONU SXGTC layer system in Control/Management Plane       47         5.5       Summary of SXGPON and GPON logical model differences       49                                                                                                                       |   | 4.3    | FPGA clock frequency and data rate                            | 29 |

| 4.5       Reprogrammable FPGA design flow       31         4.6       Summary       34         5       SARDANA 10 Gigabit-capable Passive Optical Network Transmission       35         Convergence Layer: Logical Model       35         5.1       SXGTC protocol stack       35         5.2       SXGTC layer transmission and framing mechanisms       37         5.2.1       SXGTC layer Service Data Units (SDUs)       37         5.2.2       SXGEM framing principle       37         5.2.3       Downstream SXGTC framing principle       38         5.2.4       Upstream SXGTC framing principle       39         5.2.5       User and OMCI frame fragmentation       40         5.3       SXGPON Medium Access Control (MAC) and flow multiplexing       40         5.3.1       In the downstream       40         5.3.2       In the upstream       40         5.3.3       ONU ranging       45         5.4       User and Control/Management Planes of ONU SXGTC layer system       46         5.4.1       ONU SXGTC layer system in User Plane       46         5.4.2       ONU SXGTC layer system in Control/Management Plane       47         5.5       Summary of SXGPON and GPON logical model differences       49                                                                                                                       |   | 4.4    | 1 7                                                           |    |

| 5         SARDANA 10 Gigabit-capable Passive Optical Network Transmission           Convergence Layer: Logical Model         35           5.1         SXGTC protocol stack         35           5.2         SXGTC layer transmission and framing mechanisms         37           5.2.1         SXGTC layer Service Data Units (SDUs)         37           5.2.2         SXGEM framing principle         38           5.2.3         Downstream SXGTC framing principle         38           5.2.4         Upstream SXGTC framing principle         39           5.2.5         User and OMCI frame fragmentation         40           5.3.1         In the downstream         40           5.3.2         In the upstream         40           5.3.3         ONU ranging         45           5.4         User and Control/Management Planes of ONU SXGTC layer system         46           5.4.1         ONU SXGTC layer system in User Plane         46           5.4.2         ONU SXGTC layer system in Control/Management Plane         47           5.5         Summary of SXGPON and GPON logical model differences         49           6         SARDANA 10 Gigabit-capable Passive Optical Network Transmission         51           6.1         Definition of transmission rates for SXGPON         51 <td></td> <td>4.5</td> <td></td> <td></td> |   | 4.5    |                                                               |    |

| Convergence Layer: Logical Model         35           5.1         SXGTC protocol stack         35           5.2         SXGTC layer transmission and framing mechanisms         37           5.2.1         SXGTC layer Service Data Units (SDUs)         37           5.2.2         SXGEM framing principle         38           5.2.3         Downstream SXGTC framing principle         38           5.2.4         Upstream SXGTC framing principle         39           5.2.5         User and OMCI frame fragmentation         40           5.3.1         In the downstream         40           5.3.2         In the upstream         41           5.3.3         ONU ranging         45           5.4         User and Control/Management Planes of ONU SXGTC layer system         46           5.4.1         ONU SXGTC layer system in User Plane         46           5.4.2         ONU SXGTC layer system in Control/Management Plane         47           5.5         Summary of SXGPON and GPON logical model differences         49           6         SARDANA 10 Gigabit-capable Passive Optical Network Transmission         51           6.1         Definition of transmission rates for SXGPON         51           6.2         FPGA implementation clock frequency and data path width estimation                                       |   | 4.6    | Summary                                                       | 34 |

| Convergence Layer: Logical Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |        | •                                                             |    |

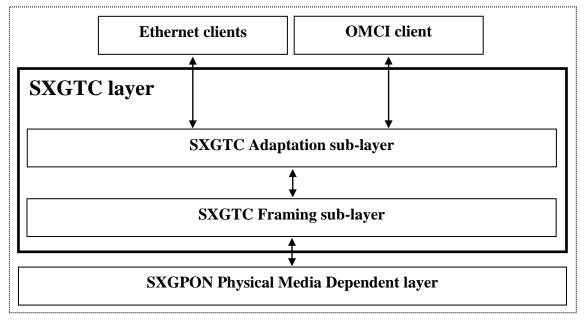

| 5.1       SXGTC protocol stack       35         5.2       SXGTC layer transmission and framing mechanisms       37         5.2.1       SXGTC layer Service Data Units (SDUs)       37         5.2.2       SXGEM framing principle       37         5.2.3       Downstream SXGTC framing principle       38         5.2.4       Upstream SXGTC framing principle       39         5.2.5       User and OMCI frame fragmentation       40         5.3.1       In the downstream       40         5.3.2       In the upstream       41         5.3.3       ONU ranging       45         5.4       User and Control/Management Planes of ONU SXGTC layer system       46         5.4.1       ONU SXGTC layer system in User Plane       46         5.4.2       ONU SXGTC layer system in Control/Management Plane       47         5.5       Summary of SXGPON and GPON logical model differences       49         6       SARDANA 10 Gigabit-capable Passive Optical Network Transmission         Convergence Layer: System Design and Optimization       51         6.1       Definition of transmission rates for SXGPON       51         6.2       FPGA implementation clock frequency and data path width estimation       52         6.3       GEM frame structure                                                                                      |   |        |                                                               |    |

| 5.2SXGTC layer transmission and framing mechanisms375.2.1SXGTC layer Service Data Units (SDUs)375.2.2SXGEM framing principle375.2.3Downstream SXGTC framing principle385.2.4Upstream SXGTC framing principle395.2.5User and OMCI frame fragmentation405.3SXGPON Medium Access Control (MAC) and flow multiplexing405.3.1In the downstream405.3.2In the upstream415.3.3ONU ranging455.4User and Control/Management Planes of ONU SXGTC layer system465.4.1ONU SXGTC layer system in User Plane465.4.2ONU SXGTC layer system in Control/Management Plane475.5Summary of SXGPON and GPON logical model differences496SARDANA 10 Gigabit-capable Passive Optical Network TransmissionConvergence Layer: System Design and Optimization516.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure576.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure <td< td=""><td>C</td><td>onverg</td><td></td><td></td></td<>                                                                                                                  | C | onverg |                                                               |    |

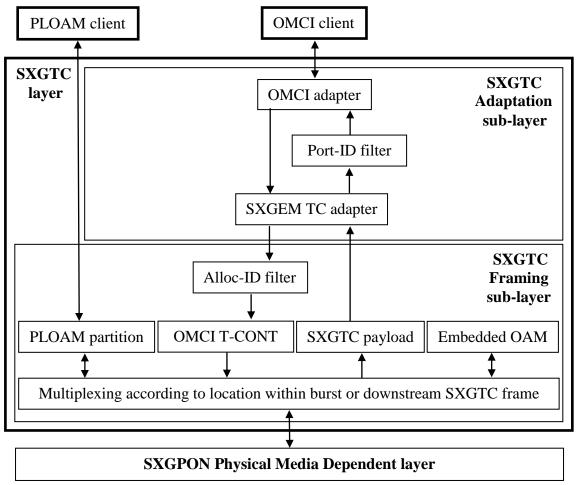

| 5.2.1       SXGTC layer Service Data Units (SDUs)       .37         5.2.2       SXGEM framing principle       .37         5.2.3       Downstream SXGTC framing principle       .38         5.2.4       Upstream SXGTC framing principle       .39         5.2.5       User and OMCI frame fragmentation       .40         5.3       SXGPON Medium Access Control (MAC) and flow multiplexing       .40         5.3.1       In the downstream       .41         5.3.2       In the upstream       .45         5.3.3       ONU ranging       .45         5.4       User and Control/Management Planes of ONU SXGTC layer system       .46         5.4.1       ONU SXGTC layer system in User Plane       .46         5.4.2       ONU SXGTC layer system in Control/Management Plane       .47         5.5       Summary of SXGPON and GPON logical model differences       .49         6       SARDANA 10 Gigabit-capable Passive Optical Network Transmission       .51         6.1       Definition of transmission rates for SXGPON       .51         6.2       FPGA implementation clock frequency and data path width estimation       .52         6.3       GEM frame structure       .53         6.4       Applicability of GEM frame structure in SXGPON       .54                                                                                  |   | 5.1    |                                                               |    |

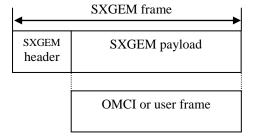

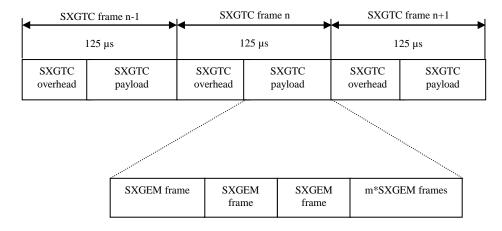

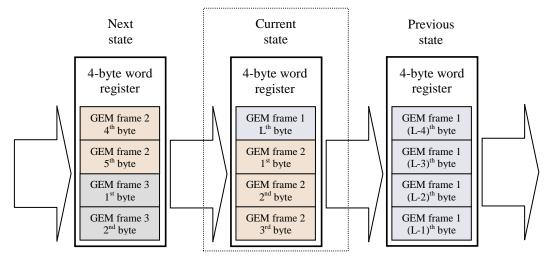

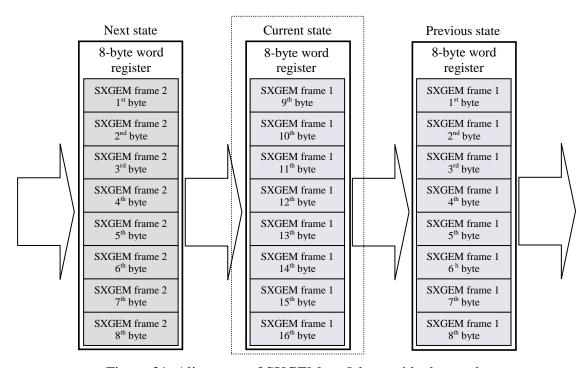

| 5.2.2       SXGEM framing principle       37         5.2.3       Downstream SXGTC framing principle       38         5.2.4       Upstream SXGTC framing principle       39         5.2.5       User and OMCI frame fragmentation       40         5.3       SXGPON Medium Access Control (MAC) and flow multiplexing       40         5.3.1       In the downstream       40         5.3.2       In the upstream       41         5.3.3       ONU ranging       45         5.4       User and Control/Management Planes of ONU SXGTC layer system       46         5.4.1       ONU SXGTC layer system in User Plane       46         5.4.2       ONU SXGTC layer system in Control/Management Plane       47         5.5       Summary of SXGPON and GPON logical model differences       49         6       SARDANA 10 Gigabit-capable Passive Optical Network Transmission       51         6.1       Definition of transmission rates for SXGPON       51         6.2       FPGA implementation clock frequency and data path width estimation       52         6.3       GEM frame structure       53         6.4       Applicability of GEM frame structure in SXGPON       54         6.5       SXGEM frame structure       57         6.6       Downstr                                                                                            |   | 5.2    | SXGTC layer transmission and framing mechanisms               | 37 |

| 5.2.3Downstream SXGTC framing principle385.2.4Upstream SXGTC framing principle395.2.5User and OMCI frame fragmentation405.3SXGPON Medium Access Control (MAC) and flow multiplexing405.3.1In the downstream405.3.2In the upstream415.3.3ONU ranging455.4User and Control/Management Planes of ONU SXGTC layer system465.4.1ONU SXGTC layer system in User Plane465.4.2ONU SXGTC layer system in Control/Management Plane475.5Summary of SXGPON and GPON logical model differences496SARDANA 10 Gigabit-capable Passive Optical Network TransmissionConvergence Layer: System Design and Optimization516.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure636.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                               |   | 5.2.1  | SXGTC layer Service Data Units (SDUs)                         | 37 |

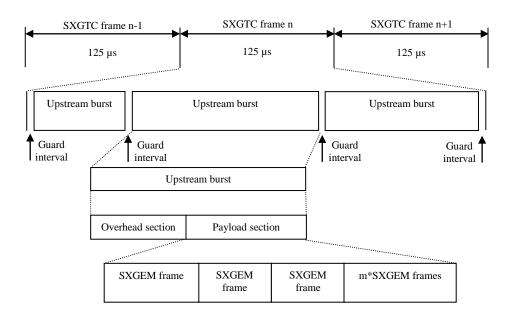

| 5.2.4Upstream SXGTC framing principle395.2.5User and OMCI frame fragmentation405.3SXGPON Medium Access Control (MAC) and flow multiplexing405.3.1In the downstream405.3.2In the upstream415.3.3ONU ranging455.4User and Control/Management Planes of ONU SXGTC layer system465.4.1ONU SXGTC layer system in User Plane465.4.2ONU SXGTC layer system in Control/Management Plane475.5Summary of SXGPON and GPON logical model differences496SARDANA 10 Gigabit-capable Passive Optical Network TransmissionConvergence Layer: System Design and Optimization516.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure in SXGPON626.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure636.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                          |   | 5.2.2  | SXGEM framing principle                                       | 37 |

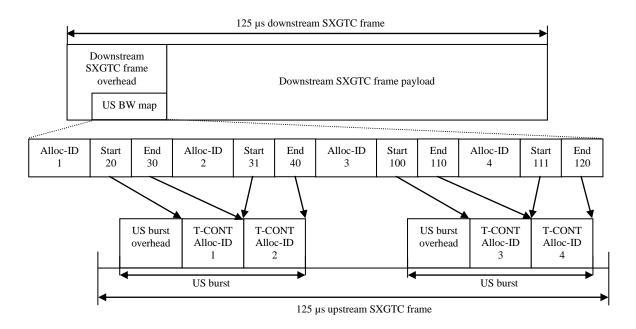

| 5.2.4Upstream SXGTC framing principle395.2.5User and OMCI frame fragmentation405.3SXGPON Medium Access Control (MAC) and flow multiplexing405.3.1In the downstream405.3.2In the upstream415.3.3ONU ranging455.4User and Control/Management Planes of ONU SXGTC layer system465.4.1ONU SXGTC layer system in User Plane465.4.2ONU SXGTC layer system in Control/Management Plane475.5Summary of SXGPON and GPON logical model differences496SARDANA 10 Gigabit-capable Passive Optical Network TransmissionConvergence Layer: System Design and Optimization516.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure in SXGPON626.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure636.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                          |   | 5.2.3  | Downstream SXGTC framing principle                            | 38 |

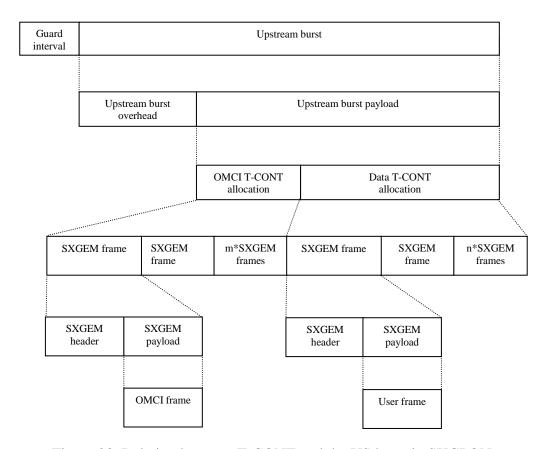

| 5.3 SXGPON Medium Access Control (MAC) and flow multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 5.2.4  |                                                               |    |

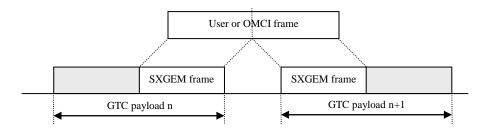

| 5.3 SXGPON Medium Access Control (MAC) and flow multiplexing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   | 5.2.5  | User and OMCI frame fragmentation                             | 40 |

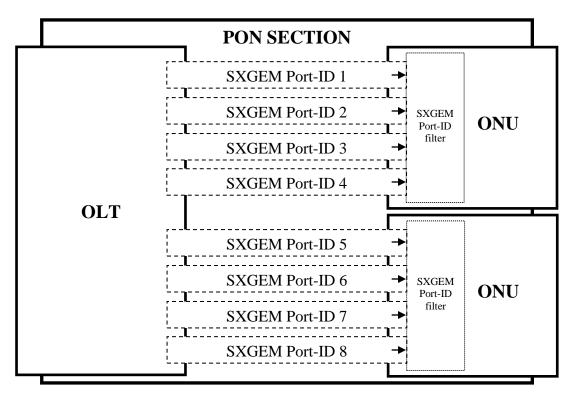

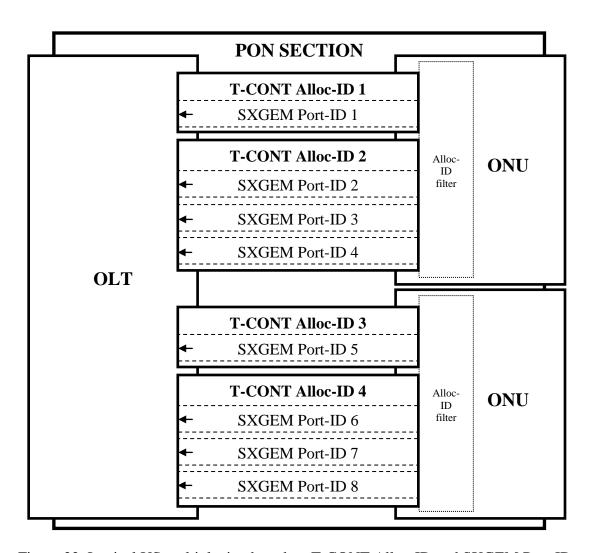

| 5.3.1 In the downstream                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 5.3    |                                                               |    |

| 5.3.3 ONU ranging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.3.1  |                                                               |    |

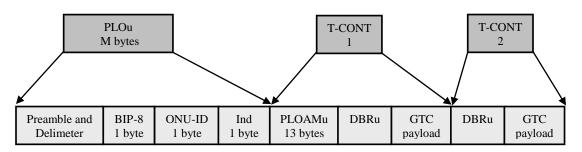

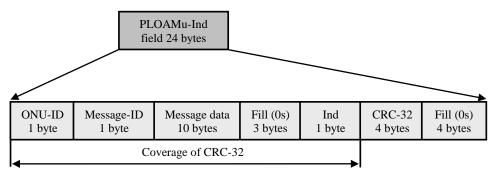

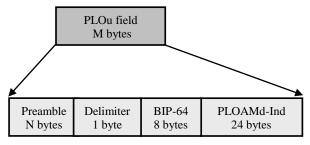

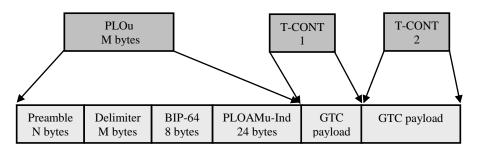

| 5.3.3 ONU ranging                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.3.2  | In the upstream                                               | 41 |

| 5.4 User and Control/Management Planes of ONU SXGTC layer system 46 5.4.1 ONU SXGTC layer system in User Plane 46 5.4.2 ONU SXGTC layer system in Control/Management Plane 47 5.5 Summary of SXGPON and GPON logical model differences 49  6 SARDANA 10 Gigabit-capable Passive Optical Network Transmission  Convergence Layer: System Design and Optimization 51 6.1 Definition of transmission rates for SXGPON 51 6.2 FPGA implementation clock frequency and data path width estimation 52 6.3 GEM frame structure 53 6.4 Applicability of GEM frame structure in SXGPON 54 6.5 SXGEM frame structure 57 6.6 Downstream GTC frame structure in SXGPON 62 6.8 Downstream GTC frame structure in SXGPON 62 6.9 GPON upstream burst structure 67 6.10 SXGPON upstream burst structure 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 5.3.3  |                                                               |    |

| 5.4.1 ONU SXGTC layer system in User Plane                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        |                                                               |    |

| 5.4.2 ONU SXGTC layer system in Control/Management Plane 47 5.5 Summary of SXGPON and GPON logical model differences 49  6 SARDANA 10 Gigabit-capable Passive Optical Network Transmission  Convergence Layer: System Design and Optimization 51 6.1 Definition of transmission rates for SXGPON 51 6.2 FPGA implementation clock frequency and data path width estimation 52 6.3 GEM frame structure 53 6.4 Applicability of GEM frame structure in SXGPON 54 6.5 SXGEM frame structure 57 6.6 Downstream GTC frame structure in SXGPON 62 6.7 Applicability of downstream GTC frame structure in SXGPON 62 6.8 Downstream SXGTC frame structure 63 6.9 GPON upstream burst structure 67 6.10 SXGPON upstream burst structure 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | 5.4.1  | • • •                                                         |    |

| 5.5 Summary of SXGPON and GPON logical model differences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |        |                                                               |    |

| 6 SARDANA 10 Gigabit-capable Passive Optical Network TransmissionConvergence Layer: System Design and Optimization516.1 Definition of transmission rates for SXGPON516.2 FPGA implementation clock frequency and data path width estimation526.3 GEM frame structure536.4 Applicability of GEM frame structure in SXGPON546.5 SXGEM frame structure576.6 Downstream GTC frame structure596.7 Applicability of downstream GTC frame structure in SXGPON626.8 Downstream SXGTC frame structure636.9 GPON upstream burst structure676.10 SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |        |                                                               |    |

| Convergence Layer: System Design and Optimization516.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |                                                               | -  |

| Convergence Layer: System Design and Optimization516.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6 | SAI    | RDANA 10 Gigabit-capable Passive Optical Network Transmission |    |

| 6.1Definition of transmission rates for SXGPON516.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | C |        |                                                               | 51 |

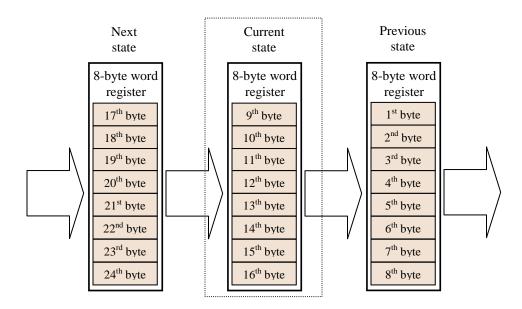

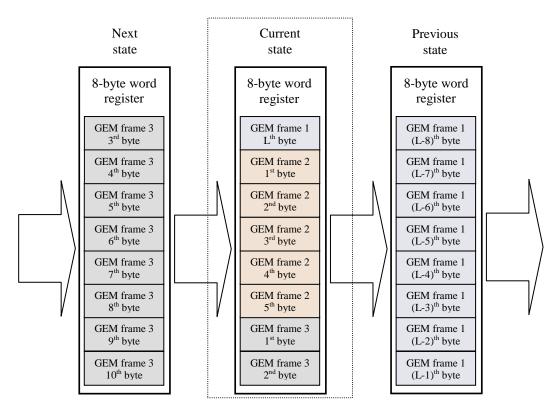

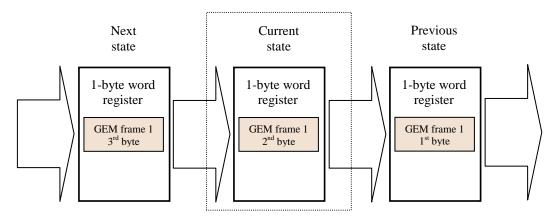

| 6.2FPGA implementation clock frequency and data path width estimation526.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | _      |                                                               |    |

| 6.3GEM frame structure536.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   | 6.2    |                                                               |    |

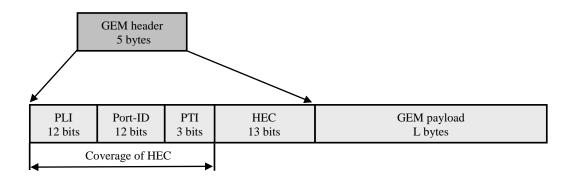

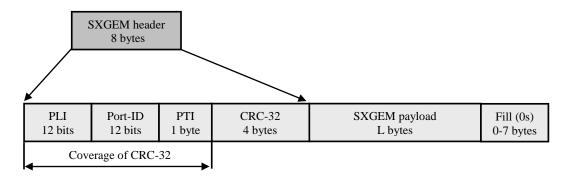

| 6.4Applicability of GEM frame structure in SXGPON546.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        |                                                               |    |

| 6.5SXGEM frame structure576.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   | 6.4    |                                                               |    |

| 6.6Downstream GTC frame structure596.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |        |                                                               |    |

| 6.7Applicability of downstream GTC frame structure in SXGPON626.8Downstream SXGTC frame structure636.9GPON upstream burst structure676.10SXGPON upstream burst structure68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        |                                                               |    |

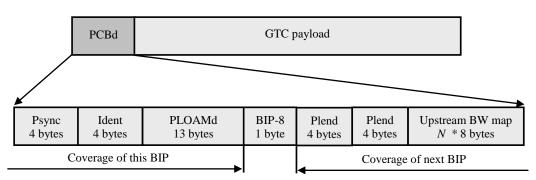

| 6.8Downstream SXGTC frame structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        |                                                               |    |

| 6.9 GPON upstream burst structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |        |                                                               |    |

| 6.10 SXGPON upstream burst structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |        |                                                               |    |

| <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |        | 1                                                             |    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 6.11   | Summary of SXGTC layer system design and optimization         |    |

| 7 SAI     | RDANA 10 Gigabit-capable Passive Optical Network Transmission  |     |

|-----------|----------------------------------------------------------------|-----|

| Converg   | ence Layer: Bandwidth Efficiency and Expected Throughput       | 71  |

| 7.1       | Upstream burst overhead                                        | 72  |

| 7.2       | Downstream GTC and SXGTC frame overhead                        | 74  |

| 7.3       | GEM and SXGEM user frame encapsulation overhead                | 75  |

| 7.3.1     |                                                                |     |

| 7.3.2     | GEM user frame encapsulation overhead                          | 77  |

| 7.3.3     | SXGEM user frame encapsulation overhead                        | 77  |

| 7.3.4     | GEM and SXGEM user frame encapsulation overhead results        | 78  |

| 7.3.5     | The effect of user frame fragmentation on SXGEM overhead       | 79  |

| 7.4       | GPON and SXGPON protocol total overhead results                | 80  |

| 7.5       | Expected throughput of SXGPON                                  | 82  |

| 7.6       | Summary of SXGPON bandwidth efficiency and throughput analysis | 84  |

| 8 SAI     | RDANA 10 Gigabit-capable Passive Optical Network Transmission  |     |

|           | ence Layer: Implementation for Optical Network Unit            | 85  |

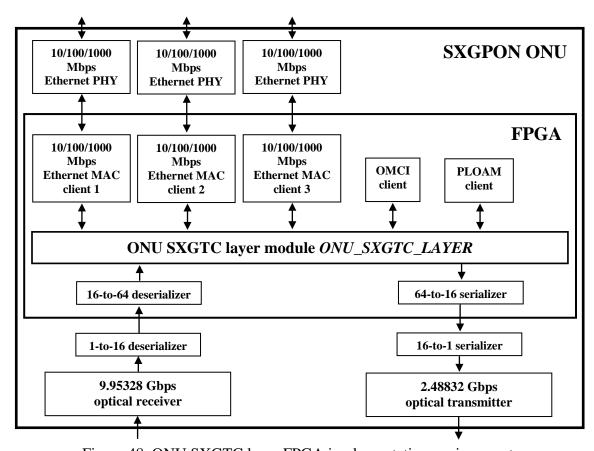

| 8.1       | ONU SXGTC implementation environment                           |     |

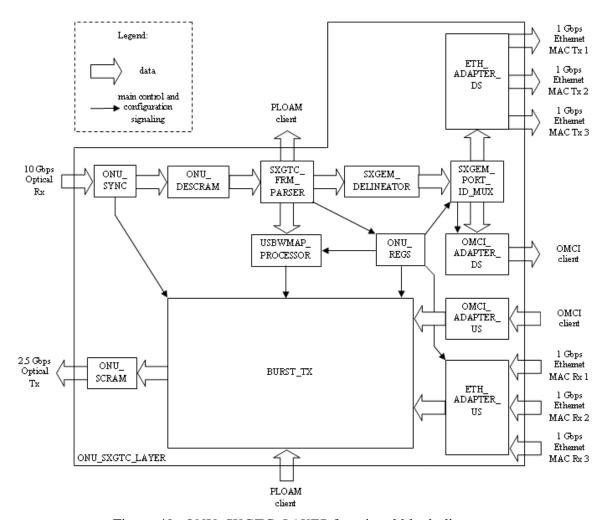

| 8.2       | ONU SXGTC layer Verilog HDL modules                            |     |

| 8.2.1     | •                                                              |     |

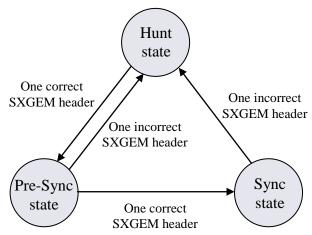

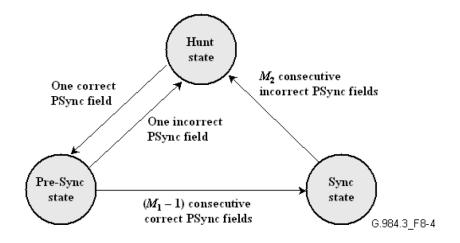

| 8.2.2     | ONU_SYNC module                                                | 87  |

| 8.2.3     | ONU_DESCRAM module                                             | 88  |

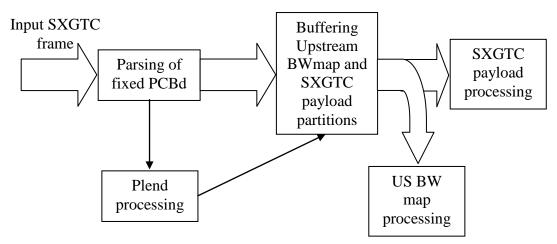

| 8.2.4     | SXGTC_FRM_PARSER module                                        | 89  |

| 8.2.5     | USBWMAP_PROCESSOR module                                       | 89  |

| 8.2.6     | SXGEM_DELINEATOR module                                        | 90  |

| 8.2.7     | SXGEM_PORT_ID_MUX module                                       | 90  |

| 8.2.8     | OMCI_ADAPTER_DS module                                         | 91  |

| 8.2.9     | ETH_ADAPTER_DS module                                          | 91  |

| 8.2.1     | 0 OMCI_ADAPTER_US module                                       | 92  |

| 8.2.1     | 1 ETH_ADAPTER_US module                                        | 92  |

| 8.2.1     | 2 BURST_TX module                                              | 93  |

| 8.2.1     | 3 ONU_SCRAM module                                             | 94  |

| 8.2.1     | 4 ONU_REGS module                                              | 94  |

| 8.2.1     | 5 ONU activation state machine module                          | 95  |

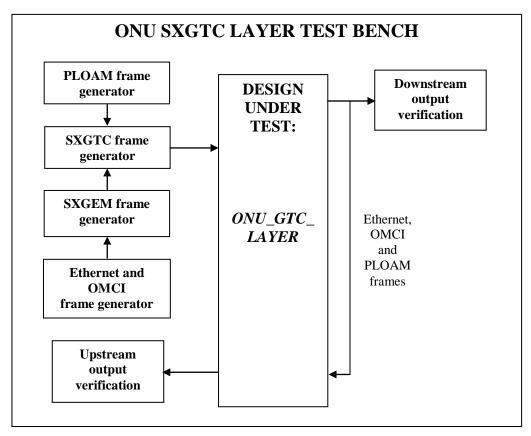

| 8.3       | ONU SXGTC layer simulation and implementation verification     | 95  |

| 8.4       | Summary of ONU SXGTC layer implementation results              | 96  |

| 9 Res     | ults and future considerations                                 | 97  |

| 9.1       | SXGTC layer design and implementation results                  |     |

| 9.2       | SXGPON future development and considerations                   |     |

| 9.3       | Commercial XGPON future development and considerations         |     |

|           | •                                                              |     |

| Reference | ces                                                            | 100 |

# **Symbols**

| E | expected value  |

|---|-----------------|

| P | probability     |

| R | frame drop rate |

#### **Abbreviations**

10GEPON

10 Gigabit Ethernet Passive Optical Network

10GPON

10 Gigabit-capable Passive Optical Network

Alen

Asynchronoud Transfer Mode partition length

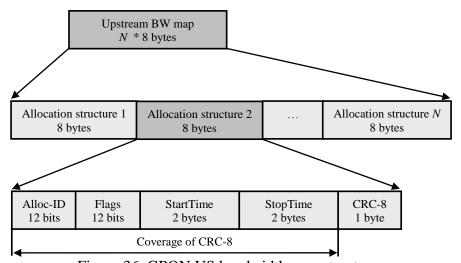

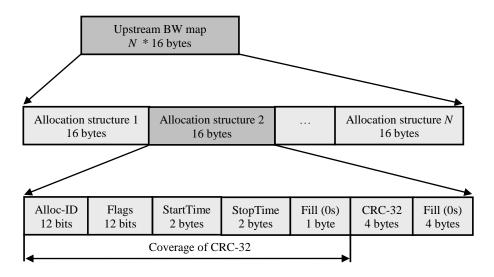

Alloc-ID Allocation Identifier

AON Active Optical Network

APON Aynchrounous Transfer Mode Passive Optical Network

ASIC Application-Specific Integrated Circuit

ATM Asynchrounous Transfer Mode

AWG Arrayed Wave Guide

BIP-8 8-bit Bit Interleaved Parity

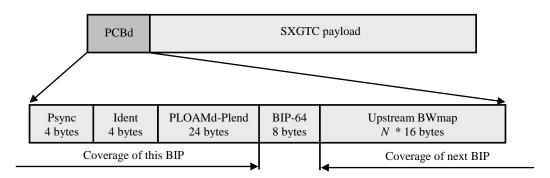

BIP-64 64-bit Bit Interleaved Parity

BCH Bose-Chaudhuri-Hocquenghem

BER Bit Error Rate

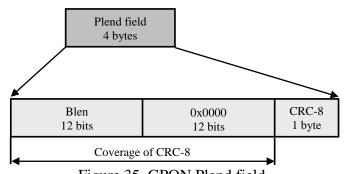

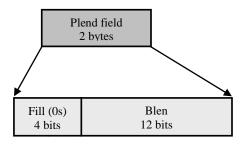

Blen Bandwidth map length

BPON Broadband Passive Optical Network

bps bits per second

BW Bandwidth

CATV Cable Television

CATVd Cable Television frame downstream

CATVu Cable Television frame upstream

C/M-Plane Control and Management Plane

CO Central Office

CRC-8 8-bit Cyclic Redundancy Check

CRC-32 32-bit Cyclic Redundancy Check

DBA Dynamic Bandwidth Allocation

DBRu Dynamic Bandwidth Report upstream

DS Downstream

DSL Digital Subscriber Line

DSP Digital Signal Processing

DWDM Dense Wavelength Division Multiplexing

EDF Erbium Doped Fiber

EPON Ethernet Passive Optical Network

FEC Forward Error Correction

FPGA Field Programmable Gate Array FSAN Full Service Access Network

FTTC Fiber-To-The-Curb

FTTCab Fiber-To-The-Cabinet

FTTB Fiber-To-The-Building

FTTH Fiber-To-The-Home

FTTH/B Fiber-To-The-Home/Building

FTTP Fiber-To-The-Premises

FTTx Fiber-To-The-x

GEM Gigabit-capable Passive Optical Network Encapsulation Method

GEPON Gigabit Ethernet Passive Optical Network

GPON Gigabit-capable Passive Optical Network

GTC Gigabit-capable Passive Optical Network Transmission Convergence

HDL Hardware Description Language

HEC Header Error Correction HFC Hybrid Fiber Coax

Ind Indication

Int Interconnect

I/O Input/Output

IEEE Institute of Electrical and Electonics Engineers

IP Intellectual Property

IPTV Internet Protocol Television

ITU-T International Telecommunication Union - Telecommunication

standardization sector

LE Logic Element LUT Look-Up Table

MAC Medium Access Control

MCI Microwave Communications, Inc

Message Identifier

MSB Most Significant Bit

MUX Multiplexer

NG-PON Next Generation Passive Optical Network

NIU Network Interface Unit

OADM Optical Add Drop Multiplexer

OAM Operations, Administration and Maintenance

OAN Optical Access Network

ODN Optical Distribution network

OLT Optical Line Terminal

OMCI Optical Network Unit Management and Control Interface

ONT Optical Network Termination

ONU Optical Network Unit

ONU-ID Optical Network Unit Identifier

OS Optical Switches

P2MP point-to-multipoint

P2P point-to-point

PCBd Physical Control Block downstream

PHY Physical layer

Plend Payload length downstream PLI Payload Length Indicator

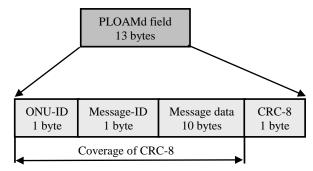

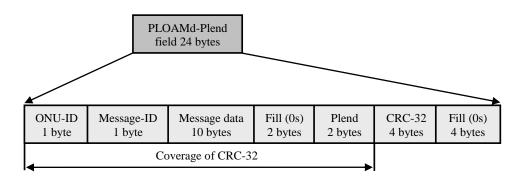

PLOAM Physical Layer Operations, Administration and Maintenance

PLOAMd Physical Layer Operations, Administration and Maintenance downstream

PLOAMu Physical Layer Operations, Administration and Maintenance upstream

PLOu Physical Layer Overhead upstream

PMD Physical Media Dependent PON Passive Optical Network

Port-ID Port Identifier

Psync Physical synchronization

PSD Packet Size Distribution

PTI Payload Type Indicator

QoS Quality of Service

RN Remote Node

RSOA Reflective Semiconductor Optical Amplifier

RTD Round Trip Delay RTL Register Transfer Level

Rx Receiver

SARDANA Scalable Advanced Ring-based passive Dense Access Network

Architecture

SBA Static Bandwidth Allocation

SDU Service Data Unit

SNI Service Network Interface

SRAM Static Random Access Memory

SXGEM Scalable Advanced Ring-based passive Dense Access Network Architecture

10 Gigabit-capable Passive Optical Network Encapsulation Method

SXGPON Scalable Advanced Ring-based passive Dense Access Network Architecture

10 Gigabit-capable Passive Optical Network

SXGTC Scalable Advanced Ring-based passive Dense Access Network Architecture

10 Gigabit-capable Passive Optical Network Transmission Convergence

TC Transmission Convergence

T-CONT Transmission Container

TDD Time Division Duplex

TDM Time Division Multiplexing

TDMA Time Division Multiple Access

TDM-PON Time Division Multiplexed Passive Optical Network

TPON Telephony on Passive Optical Network

Tx Transmitter

UNI User Network Interface

U-Plane User Plane US Upstream

VHDL Very High Speed Integrated Circuit Hardware Description Language

VLAN Virtual Local Area Network

VLSI Very Large Scale Integrated

WDD Wavelength Division Duplex

WDM Wavelength Division Multiplexing

WDM-PON Wavelength Division Multiplexed Passive Optical Network

XGPON 10 Gigabit-capable Passive Optical Network

#### 1 Introduction

Users of telecommunication access networks are today showing interest for the latest high-bandwidth demanding Internet applications and services such as on-line gaming, video telephony, video-on-demand, high-definition television and peer-to-peer applications. Furthermore, many households have multiple personal computers connected to Internet - all requiring a piece of bandwidth. The fast development of broadband telecommunication services is not only pushing the traditional copper-based access networks to the limits but requires an upgrade of access infrastructure. Fiber-To-The-Home/Building (FTTH/B) point-to-multipoint (P2MP) optical access networking is one of the most promising technological concepts that could meet this challenge, as it is evident that Digital Subscriber Line (DSL) technology is close to the end of its life cycle. [CPG<sup>+</sup>06]