HELSINKI UNIVERSITY OF TECHNOLOGY Faculty of Electronics, Communications and Automation Department of Signal Processing and Acoustics

Jouni Heinäharju

# Home Automation and Transparent Data Transmission Using Single-Medium Network Concept

Thesis submitted in partial fulfillment for the degree of Master of Science

Espoo, July 23, 2009

Supervisor

Prof. Jorma Skyttä

Instructor

Ph.D. Tapio Marttinen

#### HELSINKI UNIVERSITY OF TECHNOLOGY

#### ABSTRACT OF THE MASTER'S THESIS

| Author:<br>Name of the Thesis: |                                                                                    | Jouni Heinäharju<br>Home Automation and Transparent Data Transmission<br>Using Single-Medium Network Concept |  |

|--------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|

| Date:                          | July 23, 2009                                                                      | Number of pages: 55                                                                                          |  |

| Department:<br>Professorship:  | Department of Signal Processing and Acoustics<br>S-88 Signal Processing Laboratory |                                                                                                              |  |

| Supervisor:<br>Instructor:     | Professor Jorma Sky<br>Ph.D. Tapio Marttine                                        |                                                                                                              |  |

The purpose of this thesis is to present a new universal communication network for transparent data transmission and control applications used in home automation. The communication platform called Wiseriver is a ubiquitous wired twisted-pair network that is designed to meet all kind of individual data transmission needs in homes and buildings. The technology is based on configurable protocol-independent communication resources called virtual wires.

The thesis was started by a general survey to related technologies already existing in the market and then followed by a more specific introduction to transmission principles used in the operation of Wiseriver system. The main contribution of this thesis was to implement these Wiseriver functions with FPGA. The implementation included RTL coding using VHDL, functional simulations and logic syntheses. Two different but similar FPGA designs are used as controllers in master and access node prototype components of Wiseriver. A whole Wiseriver system prototype in turn will be used as groundwork for developing a pilot system.

The outcome of the simulation and debugging process was a base design that permits to transmit Ethernet based traffic transparently and handle a simple light control application. Simulation results and timing analyze reports indicate that the design works in completed prototype hardware. Other related developments such as PCB layout and software designs are ongoing during the prototype phase of the whole system. Also several follow-up developments have been already considered for improving the system.

Keywords:

home automation, control application, FPGA, functional simulation, logic synthesis, Ethernet

#### TEKNILLINEN KORKEAKOULU

#### DIPLOMITYÖN TIIVISTELMÄ

| Tekijä:<br>Työn nimi:          | Jouni Heinäharju<br>Taloautomaatio ja läpinäkyvä datasiirto<br>yleiskäyttöisessä tietoverkossa |               |  |

|--------------------------------|------------------------------------------------------------------------------------------------|---------------|--|

| Päivämäärä:                    | 23.7.2009                                                                                      | Sivumäärä: 55 |  |

| Osasto:<br>Professuuri:        | Signaalinkäsittelyn ja akustiikan laitos<br>S-88 Signaalinkäsittelytekniikan laboratorio       |               |  |

| Työn valvoja:<br>Työn ohjaaja: | Professori Jorma S<br>FT Tapio Marttiner                                                       |               |  |

Tämän diplomityön tarkoituksena on esitellä uusi yleiskäyttöinen tietoliikenneverkko läpinäkyvää tiedonsiirtoa ja kotiautomaation ohjaussovelluksia varten. Tietoliikennealusta nimeltään Wiseriver on ubiikki (kaikkialla läsnä oleva) langallinen parikaapeliverkko, joka on suunniteltu vastaamaan kaikenlaisiin yksittäisiin tiedonsiirtotarpeisiin kodeissa ja rakennuksissa. Teknologia perustuu konfiguroitaviin protokollariippumattomiin tiedonvälitysresursseihin, joita kutsutaan käsitteellä "virtual wire" (virtuaalinen johto).

Opinnäyte alkoi yleiskatsauksella vastaavanlaisiin jo markkinoilla oleviin teknologioihin, jonka jälkeen seurasi tarkempi perehtyminen Wiseriver-järjestelmän toiminnassa käytettäviin tiedonvälitysperiaatteisiin. Keskeisin osuus opinnäytteen tekemisessä oli näiden Wiseriver-toimintojen implementointi FPGA:lla. Implementaatio sisälsi RTL-koodausta, simulointia ja logiikkasynteesiä. Kaksi erillistä, mutta samankaltaista FPGA-toteutusta toimivat ohjaimina Wiseriverin isäntä- ja liitäntäsolmuyksiköiden prototyyppiversioissa. Kokonainen Wiseriverin järjestelmäprototyyppi puolestaan toimii perustana kehitettäessä järjestelmää edelleen pilottikohteeseen.

Simulaatio- ja testaustyön lopputuloksena syntyi perustoteutus, joka kykenee välittämään läpinäkyvästi Ethernet-pohjaista liikennettä ja hallitsemaan yksinkertaista valo-ohjaussovellusta. Simulaatiotulokset ja ajoitusraportit osoittavat että toteutus toimii myös valmisteilla olevassa prototyyppilaitteistossa. Wiseriver-järjestelmän prototyyppivaihe sisältää useita eri tahtiin eteneviä osakokonaisuuksia sisältäen esimerkiksi piirilevy- ja ohjelmistosuunnittelua. Jatkokehitystä ajatellen on myös jo olemassa suunnitelmia järjestelmän laajentamiseksi edelleen.

| Avainsanat: | kotiautomaatio, ohjaussovellus, FPGA, simulointi, |

|-------------|---------------------------------------------------|

|             | logiikkasynteesi, Ethernet                        |

## Preface

This thesis has been written for Wiseriver during the years 2008 and 2009. I am very grateful to my supervisor Prof. Jorma Skyttä and to relevant people from Wiseriver for giving me this opportunity to write this thesis of a fascinating topic.

I would like to thank my instructor Ph. D. Tapio Marttinen for enlightening conversations and helpful guidance during the challenging and instructive process. It has been a rewarding time.

Finally, I would like to take this opportunity to thank my parents for endless economical and mental support throughout my entire studies.

Helsinki, July 23, 2009

Jouni Heinäharju

# Contents

| Preface                                               | iv  |

|-------------------------------------------------------|-----|

| Contents                                              | v   |

| Terms and Abbreviations                               | vii |

| 1 Introduction                                        | 1   |

| 1.1 Purpose of Intrabuilding Network                  | 1   |

| 1.2 Properties of Intrabuilding Network               | 1   |

| 2 Available Solutions for Intrabuilding Communication | 3   |

| 2.1 Intelligent House Control (IHC)                   | 3   |

| 2.1.1 Basic Principle                                 | 3   |

| 2.1.2 Units                                           | 4   |

| 2.1.3 Programming                                     | 4   |

| 2.2 Light Control Network (Linet)                     | 5   |

| 2.2.1 General Information                             | 5   |

| 2.2.2 Nodes, Controller and Technology                | 5   |

| 2.3 LonWorks (LON)                                    | 6   |

| 2.3.1 Overview of the Network Platform                | 6   |

| 2.3.2 Network Devices and Neuron Chip                 | 7   |

| 2.3.3 LonWorks Protocol                               | 8   |

| 2.4 Konnex (KNX)                                      | 9   |

| 2.4.1 Technology Overview                             | 9   |

| 2.4.2 Communication Protocol                          | 10  |

| 2.4.3 Application and Interworking Models             | 11  |

| 2.4.4 Configuration Profiles                          | 12  |

| 2.5 Wireless Systems                                  | 12  |

| 2.5.1 ZigBee                                          | 12  |

| 2.5.2 Z-Wave                                          | 13  |

| 2.6 Digital Living Network Alliance (DLNA)            | 14  |

| 2.7 Integration Platforms                             | 15  |

| 2.7.1 Nokia Home Control Center (NHCC)                | 16  |

| 2.7.2 open Source Service Gateway (oSSG)              | 16  |

| 2.8 Summary                                           | 17  |

## Home Automation and Transparent Data Transmission Using Single-Medium Network Concept

| 3 | Wi     | seriv                                         | er Platform and Components                       | 19 |  |  |  |

|---|--------|-----------------------------------------------|--------------------------------------------------|----|--|--|--|

|   | 3.1    | Ger                                           | neral Overview                                   | 19 |  |  |  |

|   | 3.2    | Architecture, Topology and Transmission Modes |                                                  |    |  |  |  |

|   | 3.3    | Prir                                          | Principle of Transparent Data Transmission       |    |  |  |  |

|   | 3.4    | Ma                                            | nagement of Network and Control Applications     | 22 |  |  |  |

|   | 3.5    | Me                                            | chanical Implementation of Components            | 23 |  |  |  |

|   | 3.6    | Cor                                           | nparison and Summary of Wiseriver Features       | 24 |  |  |  |

| 4 | Imp    | olem                                          | entation of Wiseriver Functions with FPGA        | 26 |  |  |  |

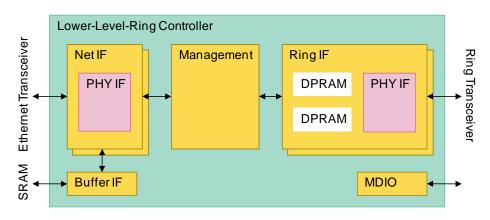

|   | 4.1    | Lov                                           | ver-Level-Ring Controller (LLRC)                 | 26 |  |  |  |

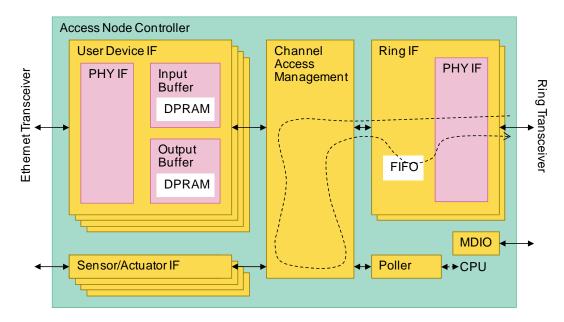

|   | 4.2    | Acc                                           | cess Node Controller (ANC)                       | 27 |  |  |  |

|   | 4.3    | Pol                                           | ling Protocol and Control Application Interfaces | 28 |  |  |  |

|   | 4.3    | .1                                            | 1-Wire                                           | 30 |  |  |  |

|   | 4.3    | .2                                            | Inter-Integrated Circuit (I <sup>2</sup> C)      | 31 |  |  |  |

|   | 4.4    | ETI                                           | H PHY Interface                                  | 33 |  |  |  |

|   | 4.4    | .1                                            | CSMA/CD and Duplex                               | 33 |  |  |  |

|   | 4.4    | .2                                            | PHY Transceiver and Media Independent Interface  | 33 |  |  |  |

|   | 4.4    | .3                                            | Data Flow Control                                | 34 |  |  |  |

|   | 4.4    | .4                                            | Management Data Input/Output (MDIO)              | 36 |  |  |  |

|   | 4.5    | Ext                                           | ernal Buffer Interface                           | 36 |  |  |  |

|   | 4.6    | Nio                                           | s II Embedded Soft Core Microprocessor           | 37 |  |  |  |

|   | 4.6    | .1                                            | Memory Subsystem                                 | 38 |  |  |  |

|   | 4.6    | .2                                            | System Interconnection Fabric (Avalon)           | 39 |  |  |  |

|   | 4.6    | .3                                            | Universal Serial Bus (USB)                       | 40 |  |  |  |

| 5 | Wi     | seriv                                         | er Prototype                                     | 41 |  |  |  |

|   | 5.1    | Fun                                           | ctional Simulation                               | 41 |  |  |  |

|   | 5.2    | Syn                                           | thesis for FPGA Design                           | 42 |  |  |  |

|   | 5.2    | .1                                            | Nios II Integration                              | 43 |  |  |  |

|   | 5.3    | Ver                                           | ification in Hardware                            | 45 |  |  |  |

| 6 | Co     | nclus                                         | sions and Future Work                            | 47 |  |  |  |

| R | eferen | ces                                           |                                                  | 49 |  |  |  |

| A | ppendi | ix                                            |                                                  | 51 |  |  |  |

# **Terms and Abbreviations**

| 100BASE-TX       | 100 Mbit/s, baseband, twisted pair based Ethernet standard |

|------------------|------------------------------------------------------------|

| 8P8C             | 8 Position 8 Contact connector                             |

| A/D              | Analog-to-digital                                          |

| AAC              | Advanced Audio Coding                                      |

| AES              | Advanced Encryption Standard                               |

| ANC              | Access Node Controller                                     |

| ANSI             | American National Standards Institute                      |

| AV               | Audio/Video                                                |

| BACnet           | Building Automation and Control networks                   |

| CAD              | Computer-Aided Design                                      |

| CE               | Consumer Electronics                                       |

| CSMA/CD          | Carrier Sense Multiple Access with Collision Detection     |

| D/A              | Digital-to-analog                                          |

| DHCP             | Dynamic Host Configuration Protocol                        |

| DLNA             | Digital Living Network Alliance                            |

| DNS              | Domain Name System                                         |

| DPRAM            | Dual-Port RAM                                              |

| DSL              | Digital Subscriber Line                                    |

| DTV              | Digital Television                                         |

| DVR              | Digital Video Recorder                                     |

| EEPROM           | Electronically Erasable Programmable ROM                   |

| EIB              | European Installation Bus                                  |

| ETH              | Ethernet                                                   |

| ETS              | Engineering Tool Software                                  |

| FIFO             | First In, First Out                                        |

| FPGA             | Field-Programmable Gate Array                              |

| FSM              | Finite State Machine                                       |

| GSM              | Global System for Mobile communications                    |

| GUI              | Graphical User Interface                                   |

| НТТР             | Hypertext Transfer Protocol                                |

| HVAC             | Heating, Ventilating and Air Conditioning                  |

| I/O              | Input/Output                                               |

| I <sup>2</sup> C | Inter-Integrated Circuit                                   |

| IC               | Integrated Circuit                                         |

| IEC              | International Electrotechnical Commission                  |

| IEEE | Institute of Electrical and Electronics Engineers |

|------|---------------------------------------------------|

| IF   | Interface                                         |

| IHC  | Intelligent House Control                         |

| IP   | Internet Protocol or Intellectual Property        |

| IPTV | IP Television                                     |

| IR   | Infrared                                          |

| ISO  | International Organization for Standardization    |

| JTAG | Joint Test Action Group                           |

| KNX  | Konnex                                            |

| LAN  | Local Area Network                                |

| LED  | Light-Emitting Diode                              |

| LLRC | Lower-Level-Ring Controller                       |

| LNS  | LonWorks Network Services                         |

| LON  | Local Operating Network                           |

| LPCM | Linear Pulse Code Modulation                      |

| LSB  | Least Significant Bit                             |

| MAC  | Media Access Control                              |

| MDIO | Management Data Input/Output                      |

| MDIX | Medium Dependent Interface crossover              |

| MII  | Media Independent Interface                       |

| MP3  | MPEG-1 Audio Layer III                            |

| MPEG | Moving Picture Experts Group                      |

| MSB  | Most Significant Bit                              |

| NAS  | Network-Attached Storage                          |

| NHCC | Nokia Home Control Center                         |

| oBIX | Open Building Information Exchange                |

| OEM  | Original Equipment Manufacturer                   |

| OHCI | Open Host Controller Interface                    |

| OSI  | Open Systems Interconnection                      |

| OS   | Operating System                                  |

| oSSG | open Source Service Gateway                       |

| P2P  | peer-to-peer or point-to-point                    |

| PC   | Personal Computer                                 |

| PCB  | Printed Circuit Board                             |

| PDA  | Personal Digital Assistant                        |

| PHY  | Physical layer                                    |

| PLL  | Phase-Locked Loop                                 |

| PoE  | Power over Ethernet                               |

| RAM    | Random-Access Memory                        |

|--------|---------------------------------------------|

| RF     | Radio Frequency                             |

| RISC   | Reduced Instruction Set Computer            |

| RJ-45  | Registered Jack                             |

| RMII   | Reduced MII                                 |

| ROM    | Read-Only Memory                            |

| RS-232 | Recommended Standard 232                    |

| RTL    | Register Transfer Level                     |

| SDRAM  | Synchronous Dynamic RAM                     |

| SMII   | Serial MII                                  |

| SMS    | Short Message Service                       |

| SMT    | Surface-Mounted Technology                  |

| SOPC   | System on a Programmable Chip               |

| S/PDIF | Sony/Philips Digital Interconnection Format |

| SRAM   | Static RAM                                  |

| UART   | Universal Asynchronous Receiver/Transmitter |

| UPnP   | Universal Plug and Play                     |

| USB    | Universal Serial Bus                        |

| UTP    | Unshielded Twisted Pair                     |

| VHDL   | VHSIC Hardware Description Language         |

| VHSIC  | Very High Speed IC                          |

| WLAN   | Wireless LAN                                |

| WWW    | World Wide Web                              |

| XML    | Extensible Markup Language                  |

#### **1** Introduction

#### 1.1 Purpose of Intrabuilding Network

A certain kind of network connecting different equipments is needed for a comprehensive automation and data transmission in a house. Different degrees of automation or intelligence can be seen in intrabuilding networks. Maximum control is achieved when all activity is integrated in one comprehensive communication system with access points to external internet or mobile lines.

Possible sub-systems to be connected are

- lighting

- HVAC

- security, surveillance & alarming

- multimedia entertainment and AV networks

- computer data network

Lighting systems can be used for automated scenarios of illumination whereas HVAC includes temperature and humidity control according to room usage. Security systems consist of sensors, detectors and alarms to report faults, burglaries or fires. Timers can be used to simulate occupied home to prevent potential intrusions. Entertainment and communication functions allow distribution of audio and video signals to multiple locations. All these applications are linked together with a control system. [1]

However, everything cannot and perhaps even should not be automated. A control device is not able, for example, to detect when certain food ingredient is cooked enough. Human consideration is still needed to estimate the cooking time. The needs of present and future house occupants are satisfied with communication and control network that has flexible functionality and appropriate architectural design. Economical cost and high comfort to user is also desirable. [2]

Basic goals of control systems and data transmission services to occupants on premises could be

- comfort and convenience

- time and energy saving

- safety and security

- ubiquitous data communication

- entertainment electronic system

#### **1.2 Properties of Intrabuilding Network**

As suggested above and by the name of this thesis a functionality of intrabuilding networks is divided to control services and data transmission. These two purposes require somewhat different technological concepts. The control network is used to govern all electrical systems in the house. The purpose of data communication is to transmit information between computers and other peripheral devices.

Control or automation nets such as IHC, LON, KNX, Linet, ZigBee and Z-Wave are used to interconnect sensors and actuators. Sensors include for example buttons, switches, thermometers, smoke detectors, moisture detectors and presence detectors. Examples of actuators are dimmers, relays, valves, sirens and buzzers. These devices are connected at a field level to the network I/Os. Interface could be a customized field level connection or a universal connection like 1-Wire, I<sup>2</sup>C or even USB. Control networks include mechanisms to create advanced automation systems from these interconnections.

Data and multimedia nets in houses are usually standard Ethernet<sup>†</sup> and WLAN<sup>††</sup> networks including upper level protocols such as DHCP and DNS. Typical data and multimedia devices are PCs, PDAs, DTVs, DVRs, home theaters and game consoles. Web cameras could be used for both surveillance and communication purposes. New DLNA and UPnP guidelines have emerged to generalize data extraction and content interchange techniques.

Most of these available intrabuilding communication solutions mentioned above are discussed and compared in this thesis. The review is followed by presentation, partial prototype implementation and some hardware verification considerations of a whole new Wiseriver platform that includes both home automation and data transmission functionality. Following phases below, not necessarily in presented order, could be completed when creating good house control and data transmission services.

- Definition of functional specification

- Selection of system architecture

- Programming of controllers

- User interface configuration

- Installation and start up

Specifications of functionalities and architecture of Wiseriver system were already made but they were refined during the thesis work. Practical section of this thesis concentrates mainly on implementation of the controller functions.

<sup>&</sup>lt;sup>†</sup> IEEE 802.3

<sup>&</sup>lt;sup>††</sup> IEEE 802.11

## 2 Available Solutions for Intrabuilding Communication

Many systems exist using various kinds of technologies and communication media. Furthermore, some systems are full monolithic platforms while others just physical layers. Advanced systems are able to provide services at higher application levels and not just at lower data and link levels. Architecturally a traditional approach would be a hierarchical design where every device is connected to a central controller. More recent trend in the industry is to move towards distributed open networks. There have been also aims to integrate these existing systems into a one universal system. This could be achieved using gateways to intermediate the communication of devices from different kinds of networks.

At first in this chapter two examples of centralized systems are discussed. Next a treatment is given to a pair of distributed systems and to a couple of wireless solutions. Finally an attention is paid on related gateway projects after reviewing an attempt to unify digital devices in homes. The emphasis is mainly on most commercial wired systems and a little less on wireless and integration systems. Power line systems such as X10, INSTEON or HomePlug have left out of the scope of this thesis but some of the systems discussed can use also power line as a communication medium.

#### 2.1 Intelligent House Control (IHC)

#### 2.1.1 Basic Principle

IHC, also known as Strömfors IHC or Schneider IHC, is principally a network of input and output units connected to a central controller. Different kinds of units are available for different purposes and when connected to controller they form a network that has a star topology. Primarily IHC is intended for on/off relay type controls and it is not able to transmit for example direct temperature information. Inputs are used for buttons and sensors, outputs for light and device control through relays. It is stated by manufactures that IHC is the most popular system of its kind in Nordic countries.

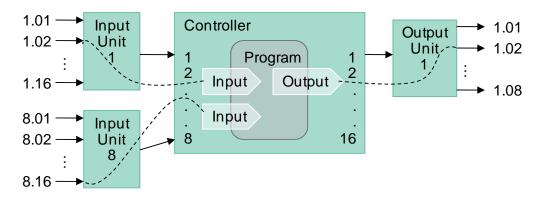

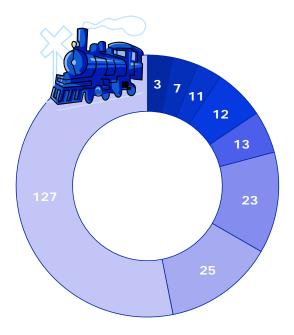

Figure 1: Principle of IHC system. Controller has 8 input ports and 16 output ports. Interface addresses are also shown.

Unique address is determined for each on/off interface and maximum number of interfaces for a single unit is 16. Also the controller has limited number of ports for input and output units resulting to a total capacity of 128 input addresses and 128 output addresses for a single controller. It is possible to chain or link several controllers together to form a larger network. [3]

#### 2.1.2 Units

Input and output units are available of few different types from which the choice is made by the required voltage. 24 V output units are used typically for LED indicators, light regulators or other low-voltage equipments. 230 V and 400 V units are utilized for bigger loads. Most common input unit is of type 24 V and it is used for push buttons, keypads and security sensors. Cabling is done with combination of control cables and UTP cables.

In addition to push buttons and relays there is a wide variety of other components that complement the functionality of the basic units. These products include light regulators, temperature controllers, IR sensors and remote controllers for achieving a more complete control. Universal light regulators have different operation modes and memory locations for used light levels. This feature is useful for example in nightlights and other lighting schemes.

Considering remote control, an interesting device called a robot phone is available. It is a voice modem that contains spoken messages and its use is based on speech menus. A network device makes remote control possible also from WWW browser. User interface is made based on blueprints saved in JPEG format. The software for this purpose is shipped with the device.

IHC is available as a complete system called ELIT IHC. The package is equipped with most common units and functions to ease the planning and installation of the system. Individual components are available also separately. [4]

#### 2.1.3 Programming

Programming of the IHC controller is done with included IHC Win software. Also firmware of the controller is upgradable which allows utilization of newly developed properties. The programming is object oriented with several ready-made object libraries. A beginner can use programs found in these libraries and hence does not necessarily have to learn actual IHC programming. Previous knowledge of any other programming language is not required.

Combining several basic operations it is possible to form more complicated control features. For instance a short push of a button may be given a different meaning than a longer press. IHC has also clock and calendar functions that may be utilized to create more complex activity. Program is transferred to controller with RS-232 cable and it remains in memory during power outages. IHC Win software also includes some simulation, debugging and documentation features.

#### 2.2 Light Control Network (Linet)

#### 2.2.1 General Information

Linet is positioned between fully wired centralized systems and advanced bus systems. It offers control unit, communication connections and essential basic functions while having the ease of installation of the bus approach. The network is intended for controlling simple devices in small applications.

The network can have up to 200 nodes and one control unit in any topology. Connecting control units together it is possible to form a larger network. Light twisted pair cabling is used to transmit information between nodes and the control unit. Linet software offers a set of functions for on/off control information, data transmission and A/D conversion to implement specific applications. Network nodes are configured to groups and only one function is active in any group. If a system is completed using just basic functions then there is no need to write software.

An example of industrial application is a set of temperature sensors attached to nodes' A/D converters. Collected data is used for a furnace control that adjusts heating elements connected to another set of nodes. In a home automation example a node could be attached to a light switch. The network will carry the on/off signal from the switch to a relay that controls a lamp. A tenant can use the control unit to arrange any switch to control any lamp without re-cabling. [5]

#### 2.2.2 Nodes, Controller and Technology

The node is a SMT packaged IC requiring network components and application specific circuitry to link simple devices into the network. Placing a microcontroller next to a node enables development of applications that demand distributed intelligence.

Linet controller provides communication and configuration services and also supplies power for nodes in the network. The controller is shipped with software that runs on RISC processor. Extensions are possible to develop by obtaining the firmware source code. Network administration is done using terminal application and the user interface can be disconnected after the configuration. The controller operates stand-alone or forms an Ethernet link to a host system for remote accessibility. [6]

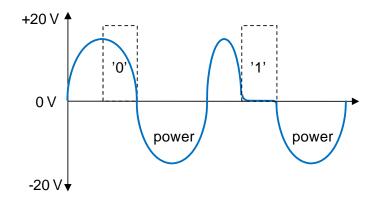

Figure 2: The carrier. Dashed line shows the area that is measured to detect the signal.

Linet network operates using time division protocol. Data and power are distributed to separate half-waves of 20 kHz sinusoidal signal as shown in figure above. Carrier frame is 253 bits long and each node has a time slot of its own and can transmit and receive 80 bits/s all the time. Synchronization and service bits are included in the beginning of the frame. Protocol and interface logic is written in the node IC's EEPROM memory. [7]

#### 2.3 LonWorks (LON)

#### 2.3.1 Overview of the Network Platform

LonWorks, or just LON, is a network platform originally created by Echelon as a generic and competitive solution to the problem of control systems. Because there are certain difficulties to install and maintain central controllers, LonWorks technology is a step away from proprietary centralized systems towards open distributed systems. Common infrastructure also prevents isolation of separate control systems. Manufacturers have a possibility to build products using off-the-shelf chips and operating systems providing improved interoperability and flexibility. Echelon itself manufactures dozens of LonWorks products with technical support and training.

Interoperability of the system is advertised as an ability to integrate products from multiple vendors. In practice, the interoperability is approached by standardizing the protocol, incorporating data and object profiles into the programming model and managing the evolution of standard conforming product certifications and interoperability guidelines. [8]

A LonWorks based control network can range in size and complexity. A network including up to 32 385 devices can be used for wide variety of applications in homes, supermarkets and skyscrapers. Nodes on the network are not just dumb I/O devices but have enough intelligence to communicate directly to each other without the need of a central controller. Communication among the nodes permits the distribution of processing loads and implementation of control functions.

A flat P2P architecture is the choice for a control device to communicate freely and efficiently with every other device on the network. The architecture is similar in some

ways as the architecture of the Internet where supervisory controller is not required to poll devices for information and then retransmit that to other devices. Software of the LonWorks requires a network database component to maintain and manage the open control system.

LonWorks is configured with LNS operating system that runs on a server. OS is not required for communication between devices during the normal operation since it just provides installation and maintenance services along with network tools. Users design a system with CAD-like environment, commit the installation to devices and generate documentation. Legacy I/O interfaces can be integrated to the system with suitable gateways.

#### 2.3.2 Network Devices and Neuron Chip

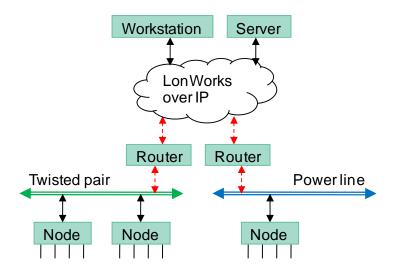

While devices on the network are called nodes, the path between them is called a channel. Each device includes also a transceiver to provide an electrical interface to physical characteristics of the channel. The media independent LonWorks allows devices to communicate over several different physical media. Twisted pair (free or bus topology) and power line are supported by Echelon's standardized signaling technology. Standards also include a tunneling method to use an IP as an envelope for LonWorks messages. Accessing and controlling LonWorks networks via web services is possible through Internet connectivity devices.

Figure 3: Devices connected to different types of channels on LonWorks network. Support for multiple media is made possible using transparent routers.

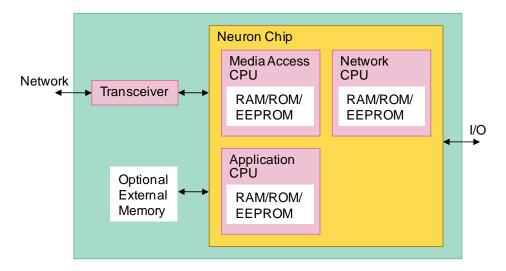

A Neuron processor is used for application execution and network communication. The chip has actually separate processors dedicated to application and protocol tasks ensuring that the complexity of applications does not affect network responsiveness. [9]

# Figure 4: Typical LonWorks device. Firmware and application code can reside in memory on the chip or in external memory attached to the chip.

ANSI C based Neuron C is used to write applications for LonWorks networks. Programming model of Neuron C is based on events occurring elsewhere on the network or at the particular node. LonWorks' low traffic feature is a result from the event triggered network. Mixture of hardware and firmware implements the protocol that is designed to follow all seven layers of the OSI model. While Neuron chip assures compatibility and is highly optimized by Echelon, the protocol can be ported also to other processors and FPGAs.

#### 2.3.3 LonWorks Protocol

Devices communicate through the network using LonWorks protocol that is ratified as a global standard<sup>†</sup>. Like Internet protocols, a packet-based LonWorks protocol is also layered as recommended by the OSI model and it handles many lower level technical details automatically. Applications can send and receive messages using a set of services provided by the protocol. Knowledge of the network topology, device addresses or functions is not needed. Some of the features of the protocol are

- P2P communication and end-to-end acknowledgement of messages

- authentication and priority transmission

- collision avoidance

- mixed data rates

- foreign frame transmission and data type identification

- unicast, multicast and broadcast

- error detection and recovery

Network management tools interact with devices through the network management services. These facilities include

• node address assignment

<sup>&</sup>lt;sup>†</sup> ISO/IEC 14908

- multicast group specification

- network traffic monitoring

- node/network diagnostics

- application code downloading

The Ethernet MAC algorithm is not well suited to control applications because it performs poorly under overload. To meet requirements during heavy loads, LonWorks uses predictive CSMA protocol that allows a channel to operate at full capacity without a lot of collisions. A specific feature is various levels of delays called Beta 2 slots that are dynamically adjusted to every device based on expected network load.

Routing of packets from a source device to destination devices is defined by addressing algorithm that support physical, device, group and broadcast address types. More than one independent LonWorks systems are able to coexist on the same physical channel. In addition to several messaging services, LonWorks offers also authentication service by 48-bit keys. This allows receivers to determine if the sender is authorized to send a message.

Yet another concept is network variables. These are particular data items that a device expects to get from other devices on the network. When the variable is received the firmware of the device passes the value to the application program. Network variables are configured during network design and installation. This process creates logical connections between certain type of output and input variables and these connections may be thought of as "virtual wires". Difference compared to the centralized system in Figure 1 is that input, output and program can now reside in any unit. A simple example of the connection is again a light bulb as an output and a switch as an input. It is more difficult to design interoperable devices to older type command-based systems than to information-based systems where the device collects information by its own about what is going on in the system. [10]

#### 2.4 Konnex (KNX)

#### 2.4.1 Technology Overview

Basic idea of KNX is fundamental as purpose is to combine all building's electrical systems to a single efficient network. KNX bus technology is intended for applications such as lighting, HVAC, security, energy management and blinds/awning control. KNX automation is suitable for new as well as existing houses and buildings of different size. Global open KNX standard<sup>†</sup> is administered by KNX Association and technology is based on several predecessor systems developed in early 1990s. Common application-independent bus solution is desired to overcome some problems of isolated devices in proprietary solutions. [11]

All control information transmitted to the bus is available everywhere in the system. Certified interoperable devices from several manufacturers can be freely added to the

<sup>&</sup>lt;sup>†</sup> ISO/IEC 14543

bus and they are compatible to communicate themselves without a central controller. Also gateways to other protocols and management-level systems are available. Cabling reinstallations are avoided because logical functionality is defined by programming. Power supply is separated from control cables to simplify installation. Commissioning of the system is designed efficiently with ETS. Access to the system is possible by touch panels or remotely through phone, SMS, LAN or Internet. [12]

KNX technology can be implemented on any processor platform either from scratch or with help of available OEM system modules like coupling units and chip sets. All products undergo a strict certification process at neutral laboratories to receive KNX compliance trademark. Product quality is ensured when the device

- can interpret signals on the medium as specified

- is configurable by manufacture independent ETS

- realizes specified interworking functions and data types

KNX specifies many essential mechanisms for manufactures to utilize

- communication messages and protocol stack for all communication requirements

- application and interworking models for various tasks

- network configuration and management schemes for linking distributed applications that run in different nodes

- device profiles for actual devices

#### 2.4.2 Communication Protocol

KNX supports several communication media. Twisted pair, power line and RF each have a slightly different bitrates but all these media implement CSMA mechanism. In IP communications LAN or Internet is used to tunnel KNX telegrams.

Logical node architecture is realized in devices connected to the bus. Device models and resources vary according to node capabilities. Devices are identified and accessed by their addresses.

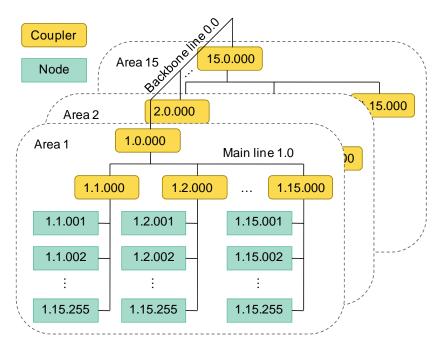

# Figure 5: The logical architecture of KNX. Couplers connect lines using bridge or router functionality.

KNX communication system is compliant to a 7 layer OSI model. Example format in table below corresponds to the interface above layer 2.

Table 1: Standard KNX frame structure, some preamble may be defined.

| Octet 0 | 12 | 34                     | 5               | 6    | 7    | 8N - 1 | N ≤ 22         |

|---------|----|------------------------|-----------------|------|------|--------|----------------|

|         |    | Destination<br>Address | Address<br>Type | TPCI | APCI | Data   | Frame<br>Check |

#### 2.4.3 Application and Interworking Models

Central concept is the data points that represent the process and control variables. Data points may be inputs, outputs, parameters or other data containers. Elements modeled as data points shall be understood as a network interface. Communication system and protocol offers an instruction set to read and write data point variables that are accessed through unicast or multicast mechanisms.

A device sends a write message when a local application writes a value to a sending data point. A receiving data point with corresponding address receives the value and its local application can now act upon this updated value. The action can be a state change, another write message or a physical output modification. Polling and call back implementations are supported by the communication stack. Local applications with linked data points form a distributed application. Address binding principles are used to establish these links.

KNX have a core set of data types to ensure interworking in multivendor networks. Interworking requires also some discovery procedures to provide essential information

about devices on the KNX network. So called KNX profiles implement a set of descriptor fields and objects that KNX configuration masters look for to manage the network. [13]

#### 2.4.4 Configuration Profiles

KNX supports System and Easy configuration modes. The difference between two modes is that S-Mode offers more flexibility with versatile configuration options whereas in E-Mode components are pre-configured to default parameters thus having more limited functionality.

Configuration features such as address binding, device parameterization and application program downloading are defined during installation. The system can be designed offline in a graphical way and download the result when components are mounted. The offline representation is a system database containing metadata of the installation. Network management in KNX identifies the different network resources within the devices in order to enable a proper interworking. Detailed descriptions of the resources, device models and other features are specified in the relevant profiles. Network management toolkit can be used for initial setup, integration of multi-mode installations, diagnostics and maintenance. [14]

#### 2.5 Wireless Systems

#### 2.5.1 ZigBee

ZigBee is a standards-based<sup>†</sup> protocol that defines network and application layers and provides infrastructure for wireless sensors. Home automation is one of the typical applications of ZigBee. Low cost, reliability, low power and easy deployment are some of the technological motivations. Evolution of the standard is maintained by ZigBee Alliance. Compatible networking capabilities can be included into products using RF modules. Hardware and software solutions are available for embedding RF into typical designs. Products are tested in certification program to ensure compatibility with the standards.

The protocol stack has several layers performing specific services for applications, devices, management, security, networking, MAC and PHY. These services provide

- standard data types and descriptions how to build a profiles onto the stack

- control for application objects and endpoints in nodes

- messages for requesting access and security

- encryption

- address handling and routing

- reliable communication

- interface to physical transmission medium

<sup>&</sup>lt;sup>†</sup> Physical and MAC layers are defined by IEEE 802.15.4

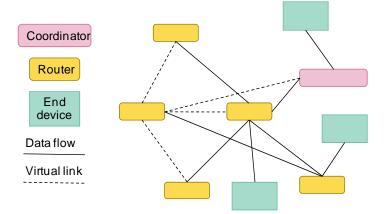

ZigBee is capable of supporting over 64 000 nodes per network and multiple networks can be linked together. Coordinators, routers and end devices are the three device types included in the networks. A coordinator device controls the network and stores information about security keys. Routers extend network area coverage whereas end devices transmit or receive messages. End devices are interconnected through P2P mesh network that contains multiple routers and a single controller. MAC association is the bare-bones default to join network.

#### Figure 6: ZigBee mesh network.

Mesh network topology supports multi-hop communication for reliability and robustness. Routers are typically connected through at least two pathways. Each router maintains a routing table where routes are established on-demand using a route discovery process.

Collection of devices employed for specific application is described by an application profile. Such application profile is defined also for home automation. Devices within an application profile communicate in clusters using specified messaging scheme. Connections between two endpoints with a specific application profile are called bindings.

Commissioning of the primary network is performed by the installer using intuitive commissioning tools running on a laptop or PDA. ZigBee security is based on a 128-bit AES algorithm and whether to allow or disallow new devices into the network is usually decided by the controller. [36]

#### 2.5.2 Z-Wave

Z-Wave protocol is a wireless RF-based communications technology designed by Zensys for control and status reading applications in residential and light commercial environments. A low-cost reliable wireless networking is delivered by substituting hardware with software solutions and focusing on narrow bandwidth applications such as on-off commands. Devices can be transformed into intelligent network nodes that can be controlled and monitored wirelessly. Remote control applications of Z-Wave include for instance lighting, HVAC and security.

The technology is available as single chip solutions that include radio transceiver, microprocessor, system interfaces and flash memory including embedded protocol stack and application software. Manufacturing blueprints of the PCB circuitry around the chip including antennas and filters are also offered. Z-Wave designs can be licensed and certified to ensure interoperability between all products. [37]

Z-Wave is an intelligent distributed mesh networking technology that has no master unit. Messages are automatically routed around household obstacles and radio dead spots in the network. Z-Wave can consist of up to 232 devices per network with the option of bridging multiple networks via gateways. Each device is identified by an individual code selected from more than 4 billion options. Devices on the network can be programmed to work singly or in groups where multiple devices are triggered by certain events

Devices are added to the network by inclusion process. Usually this is achieved by pairing a controller with the controllable device being added to the system.

#### 2.6 Digital Living Network Alliance (DLNA)

Users want devices from islands of CE, PC and mobile worlds to work together. DLNA is helping put end to frustration of difficulty to send digital content from device to another. The goal is to enable interoperability among digital devices storing and playing digital content. DLNA delivers guidelines based on open standards for achieving digital interoperability in homes. Guidelines specify network connectivity, media transport, device discovery, and media formats for building platforms and software infrastructure. [15]

Figure 7: PC, CD and mobile islands in digital home.

DLNA certified products are categorized to different DLNA device classes. PCs, video recorders and NAS devices are examples of digital media server class. These devices

store content and make it available to the network. Digital media controllers, e.g. PDAs, find content on servers and play it on digital media renderers, e.g. TVs. Digital media players are able to play media directly from servers. There are separate classes also for corresponding mobile devices, uploaders, downloaders, printers and infrastructure devices. Compatibility is tested through certification means. The certificate ensures that a device conforms to rigorous guidelines and has proven compatible.

Foundation for networking and interoperability in DLNA is IP protocol. It allows applications communicate transparently over wired and wireless media. UPnP technology enables to discover presence and capabilities of the devices based on DLNA guidelines. IP addresses along with other network properties are configured automatically.

DLNA supervises UPnP AV grouping within the UPnP standards. UPnP AV technology addresses content management and control needs to identify and distribute media content across the network. Specifications define architecture and interaction model between devices to allow content in any format over any transfer protocol. UPnP AV specifications define also services to

- enumerate the available content, e.g. videos, music, pictures

- determine how the content can be transferred

- control the flow of the content, e.g. pause, seek

- control how the content is played, e.g. volume, brightness

Media format model defines a set of media formats to content that passes over the network. LPCM is reasonable choice for audio format in wired environments. Compressed audio formats such as MP3 and AAC are more efficient for wireless devices. MPEG-2 and MPEG-4 are corresponding formats for video. [16]

#### 2.7 Integration Platforms

For communication between systems there is a standard called BACnet that includes mechanisms for information exchange. BACnet however is not discussed in further detail here. More recent solutions are NHCC and oSSG integration platforms which are based on a gateway. As already mentioned earlier a gateway could be used to allow access to legacy protocol networks. Gateways of NHCC and oSSG operate on a system level to intermediate the communication of devices from different kinds of networks

Generally the term residential gateway is used to describe home routers and modems. These devices allow connection of a LAN to an external network like Internet. The connection is usually provided through DSL, cable modem or mobile broadband network. Residential gateways are gaining capabilities of corporate gateways and may provide functions suitable also for remote house control. Some of commercial residential gateways use Linux-based firmware which requires manufacturers to publish the source code. This allows third parties to modify and change the code and thus

enhance original features and performance. One such firmware project is OpenWrt that has expanded to support chipsets from several manufacturers.

#### 2.7.1 Nokia Home Control Center (NHCC)

NHCC is an open Linux based platform for creating intelligent homes that are controlled using unified user interface. The platform supports most common technologies and it can be controlled with a mobile phone and web browser. Third parties are allowed to develop their own solutions on top of the framework and expand the system with new technologies. NHCC acts as a dictionary that translates different technological languages from different manufactures presented under the user interface. The platform relies on a partner program that offers full documentation, a library of control functions and development support for third parties. [17]

NHCC is built on top of standard gateway architecture including

- antennas for WLAN, GSM and Z-Wave

- connectors for USB and Ethernet

- CPU, RAM and internal storage

- flash card reader

Embedded open Linux firmware offers possibilities to build server functionalities for web, email and file sharing. Graphical user interface is provided for browser and mobile devices to control home appliances. Control functionality includes

- logic for simple automatic responses and events for sensor triggering, luminance levels and temperature limits

- grouping of devices for easy control

- profile support for home, away, day and night setups

- linking of different systems

#### 2.7.2 open Source Service Gateway (oSSG)

oSSG is free open source based software implementing oBIX interface which can be utilized to develop house control functions. The platform permits integration of separate technical devices and systems in a building. Electrical building services center STOK develops the software at integration laboratory that is open for research and educational purposes. [18]

So far practical implementation of oSSG has been studied with prototype server. The idea is to integrate management of automation systems using standard way to describe data and communication. Thus the question is of generally usable oBIX enabled equipment server for automation systems. oBIX has been chosen as data storing and transmission format between user interface and devices. Adapters are used to connect devices to the server by translating different protocols to standard oBIX format. The standalone server works with Windows and Linux operating systems and is independent of any specific hardware. [19]

oBIX defines web services based mechanisms for control systems. The standard is being developed under OASIS consortium in parallel with an open source Java toolkit for working with oBIX. Access to embedded control systems is the main purpose that oBIX is designed for. [20]

The groundwork for building machine-to-machine communication is laid using standard XML and HTTP network technologies. Common XML syntax is used to represent information of diverse systems as extensible object models that are called contracts. An object that uses a contract as a template or a prototype is said to be an implementation of that contract. In object-oriented terminology equivalent concepts would be a class and an instance. Objects and their state are accessed using HTTP GET, PUT and POST representational state transfer methods. [21]

oBIX system architecture is based on client-server network model. Server accepts incoming requests through a socket. oBIX does not prevent software from being both an server and a client. oSSG server includes client side functions to minimize possible overhead network traffic caused by polling of rapidly changing real-time information.

#### 2.8 Summary

Different systems are suitable for different targets. A wired system can be incorporated into a new house at the time of construction. Wireless systems may be more easily applicable to old existing houses. Although wireless systems are easy to install and expand they do not have reliability, speed and security of wired systems. The price of wireless systems is usually higher and there is also a need to take care of batteries.

As shown in this section systems may have also different capabilities. Some are more suitable for home usage and others are intended for larger buildings and even campuses. Deployment and configuration interface should be simpler and price more inexpensive in home systems when compared to high reliable industrial systems.

A hard-wired control cabling is laborious to install and modify but on the other hand a fixed high-end control network leads to a complex design in simple applications. Also a physical size of intelligent sensor and actuator units is larger because of additional distributed intelligence. Simple centralized systems are dependable on a single controller whereas complex distributed systems are more fault-tolerant and robust because intelligence is decentralized to multiple devices on the network.

|                           | LonMarks                                      | KNX                                               | IHC                          | Linet                      |

|---------------------------|-----------------------------------------------|---------------------------------------------------|------------------------------|----------------------------|

| Developer                 | Echelon, US                                   | EIBA <sup>†</sup> , Europe                        | Schneider, France            | Linet Oy, Finland          |

| Maximum<br>network size   | 32 385 nodes                                  | 65 536 devices                                    | 256 I/Os per<br>control unit | 200 nodes per control unit |

| Product<br>manufacturers  | over 200                                      | over 100                                          | few                          | few                        |

| Architecture              | distributed                                   | distributed                                       | centralized                  | centralized                |

| Topology                  | free                                          | bus, star, tree                                   | star                         | free                       |

| System license            | open standard                                 | open standard                                     | proprietary                  | proprietary                |

| Interconnection<br>medium | twisted pair,<br>power line,<br>IP and others | twisted pair,<br>power line, RF,<br>IP and others | control cables,<br>UTP       | twisted pair               |

| Programming               | event-based<br>Neuron C                       | ANSI C,<br>assembly and<br>others                 | object-oriented<br>IHC       | ANSI C, assembly           |

| Configuration             | LNS and<br>network<br>tools                   | ETS<br>toolkit                                    | IHC Win                      | terminal                   |

#### Table 2: Comparison of house control systems

Exact same properties of two wireless systems not included in the table can be found in the text on corresponding chapters. What they have in common to each other is the RF based mesh topology. Differences on the other hand can be found on maximum network size, product manufacturers and system license.

Integration platforms are attempts to connect existing one-system-approaches together. The problem with protocol translation equipment may be that all the features of some communication language cannot be supported by another language. Also there may be too many languages so that one platform could understand every one of them. Integration platforms combine the management of different subsystems together. This is done by offering common interface such as oBIX or other open framework for all home systems.

$<sup>^{\</sup>dagger}$  EIB Association, founded by Siemens, ABB, Jung and others

# **3 Wiseriver Platform and Components**

#### 3.1 General Overview

Wiseriver offers single-medium network infrastructure and communication protocol for houses and buildings. Wiseriver platform provides wire-level connections to home automation applications, entertainment systems and communication systems. Home automation, also known as domotics, includes systems such as lighting, HVAC, security and surveillance.

In addition to home automation control Wiseriver has also capacity for light to medium universal data transmission. For example signals associated to IPTV and media players can be transmitted from one source to displays and speakers in several rooms. There is enough capacity for compressed data but not for uncompressed high-definition multimedia and other hi-speed connections. Internet, IP and analog phones and PC networks can be also included in Wiseriver communications.

Wiseriver communications are based on Ethernet physical layer that inherently has certain limitations but the design of the universal Wiseriver platform is however as protocol-independent as feasible. Thus it is possible to include at least Ethernet based applications from present and future. With some modifications to the system also other kinds of applications such as USB or S/PDIF may be implemented as data is distributed transparently through the network.

The total transmission capacity of Wiseriver is divided to channels. Bandwidth and other transmission properties of each channel are configured individually. Channels are available for selected participants at the signal path endpoints in access nodes. No additional cable installations are needed after initial setup because cross-connections in the network are made electronically. A specific feature is that all channels between different access points are completely independent transmission resources separated from the total capacity. These channels are regarded as individual "virtual wires".

As a special service on top of the transparent wire-level network Wiseriver offers also processing resources for simple control applications. This service can be used to configure home automation interfaces and transfer information between them.

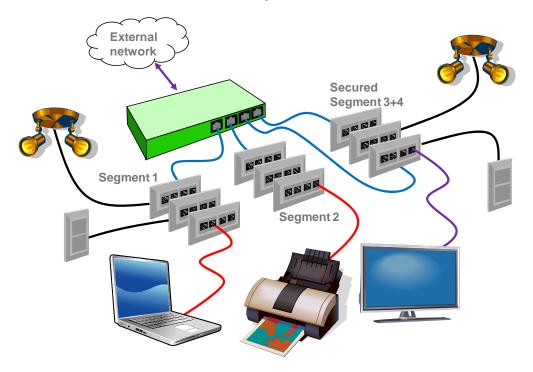

#### 3.2 Architecture, Topology and Transmission Modes

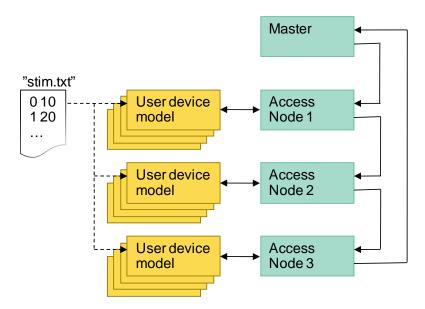

A basic Wiseriver system has two kinds of components which are master and access node. Master controls different segments of the network and cross-connections from one segment to another. Master offers also gateway to an external network. Carrier frame that constitutes the principle of the operation (see Chapter 3.3) is generated by the master. Access nodes on the other hand are able to acquire data from multiple user devices and transmit it to the network. Higher intelligence is needed especially when handling control applications and making changes to the configuration.

The overall architecture of Wiseriver is in between centralized and distributed architecture. Master is the main unit that controls the overall functionality but application programs for house control functions are distributed to access nodes. Control applications principally executed by access nodes form other logically centralized structures inside the main system.

Logically Wiseriver network is wired as a ring. Data streams flow through every access node connected to the ring. The carrier frame that constantly circulates around the ring is used to give access to a shared medium by means of channels. Access nodes acquire time division multiplexed channels from the carrier frame circulating the ring.

A ring can be wired either as a physical ring called secured segment or an unclosed wire. The latter, non-secured segment still is logically a ring since data is forwarded back from the last access node in the segment. A node failure or a cable break in a normal segment isolates every node beyond the break point. The secured segment overcomes this vulnerability by wrapping the data back before the point of failure and thus resulting to two normal non-secured segments. Master can control four segments and act as a certain kind of switch or multiport bridge between them.

Cabling for Wiseriver's infrastructure has been chosen to be 100BASE-TX which is one of Fast Ethernet standards for twisted pair. Wiseriver does not, however, utilize the data link layer (MAC) of Ethernet but only the physical layer which is used with standard connectors, wires, transducers, electrical levels and frequencies. Instead, Wiseriver's

own internal transmission protocol runs on top of the physical layer and also the frame structure is proprietary. Wiseriver protocol (Layer 2 and above in OSI) offers flow control but error checking has been left to protocols at higher levels. Flow control is based on back-pressure and it is used on demand in shared channels to avoid congestion.

The channel access method is time divided multiplexing and bandwidth of each channel is configurable. Bandwidth allocation is done in flexible way between applications in multi-purpose network while providing transparent treatment of data streams despite of the type of equipments used. Transparency and protocol independence means that the data is treated as bit streams and represented at the transmitting end exactly in same format as it was received without reading or manipulating data structures. In order to do this Wiseriver technology includes different transmission modes to specify characteristics of transmissions (shared or dedicated medium, point-to-point or broadcast, half-duplex or full-duplex, constant or variable length data structure, packet mode or isochronous).

A special transmission mode designed for control applications is based on polling messages. An access node acting as an application master polls values from specified ports and passes them to a control application. Based on input data the application program calculates suitable output values and the access node sends data again to specified ports. Program code is executed in a soft core processor or in custom hardware logic. The application program and associated input/output ports can reside anywhere on the network. Home automation devices to be integrated in control applications must be connected to control application interfaces. A control service is applied on appropriate control channels and other transmission modes use universal data transmission channels.

#### 3.3 **Principle of Transparent Data Transmission**

Basic structure in Wiseriver is the ring where the carrier frame is circulating. The carrier frame has a constant length and it is launched at  $15.6 \,\mu$ s intervals (about 64 000 times per second). If the carrier frame is illustrated as a train and the ring as a track then the track is filled entirely by the train. Cars of the train represent time multiplexed channels for user's data.

There are 128 cars and the length of the car can be modified and thus select the bandwidth of the channel. Unused cars have zero size allowing existing bandwidth to be used efficiently. Reserved channels are floating in the carrier frame. Bandwidths are reserved and released in few milliseconds for plug-and-play applications and variable bit rate applications. Bandwidth of a 1-bit wide channel is around 64 000 bits/s. Bit rate of a wider channel is simply multiple of 64 kbit/s depending on the width of the channel.

# Figure 9: Time-multiplexed bandwidth distribution with channels of different size. Unused bandwidth is located on channel #127.

At least one channel is reserved for each application and user's data is chopped to slices that fit in the car. Content of the cars are read and replaced by access nodes on the path of the train. In order to restore user's data structure some transmission modes consume additional information included in the channel. In addition to the payload for transporting user's data in up to 128 channels the carrier frame includes an overhead for frame synchronization and management.

Although Wiseriver is based on Ethernet physical layer it has constant frame rate and constant frame size which permits isochronous transfer. To summarize, key points of the operation are

- The train carrying user's data is called carrier frame and it consists of 128 numbered cars called channels.

- The carrier frame circles 64 000 times per second.

- Each channel has variable length from zero up to all bits in payload. Unit length corresponds to 64 000 bit/s.

- Each application uses a given channel in the carrier frame.

- The train fills the entire track.

#### 3.4 Management of Network and Control Applications

Definition of virtual wires, their paths, their locations, connecting ports, bandwidths and other parameters are made using graphical configuration tool. The basis is a floor plan of the apartment and an automatically generated display that shows all access nodes installed in each segment. Professional technician or advanced house owner uses the tool to drag access nodes to correct locations and adds connections to lamps, switches and transducers. In order to put intelligence to control applications an application program has to be created for manipulating data that is retrieved using polling protocol. Programs are also made using the graphical configuration tool and a result is a script or other kind of program file. Possible operations that could be used in programs are NEG, AND, OR, LSHIFT, RHIFT, ADD, SUB, MUL and DIV. The application file is transferred to Wiseriver system through configuration management interface (Ethernet or USB) or through surveillance network from remote administrator. Depending on the final runtime system the actual program is executed by soft core processor or custom hardware logic in desired access node. More detailed bit-level discussion of the polling protocol is presented on the implementation section of this thesis.

Remote surveillance is available at any time. For example it is made possible for system administrator to enquire remotely device statuses or states of the ports. oBIX is useful data format for this purpose and also for making configurations. It is uncertain however at this point whether oBIX is suitable also for uploading application program data. Certainly it would be difficult to define actual program using just oBIX alone since it is mainly just a web service protocol.

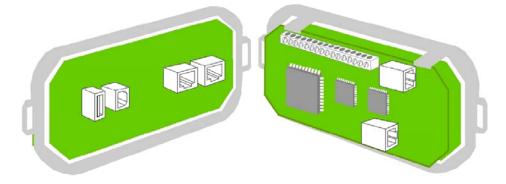

#### 3.5 Mechanical Implementation of Components

Mechanically the access node consists of a PCB and a cover frame with outlets fitting to connectors on the PCB. The size of the double-sided PCB is small enough to be mounted in a standard enclosure. Access nodes located densely around the house are equipped with most common interfaces. Each access node has four Ethernet connectors for PC, IPTV and other users' data communications equipment. Ethernet connectors are used also in the ring interface for interconnecting access nodes and master. Two 12 Mbit/s Full-Speed USB connectors are provided for PC peripherals.

Transducers and actuators of automation systems are connected directly to four-pin interfaces which can be defined to appear as  $I^2C$ , 1-Wire or digital in/out. Compatible components of lighting, ventilation, alarming and other automation systems are available off-the-shelf at low-cost. Connectors are labeled from p0 to p12 and listed in Table 3. More types of interfaces can be provided with adapters.

Table 3: List of interfaces. User data interfaces are associated with desired data channels and control interfaces are read and written using polling protocol of control application channels.

| Port           | Туре                  | Function             |

|----------------|-----------------------|----------------------|

| p0, p1, p2, p3 | RJ45 <sup>†</sup>     | user data            |

| p4             | USB A-type receptacle | peripherals          |

| p5             | USB B-type receptacle | peripherals          |

| p6, p7, p8, p9 | screw connector       | sensor and actuator  |

| p10, p11       | RJ45 <sup>†</sup>     | ring interconnection |

| p12            | RJ45 <sup>†</sup>     | management           |

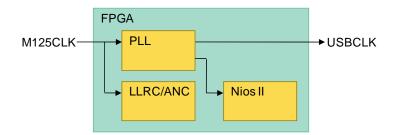

Multitude of essential electronic components that are packed to the PCB include microprocessor or soft core for management, FPGA for implementing Wiseriver functions, transceivers and magnetics for Ethernet, controller for USB, flash memory for configuration and SRAM memory for data buffering and program storage. Master is assembled on same PCB layout but with some component variations. Power is supplied using PoE or with separate 48 V line.

#### **3.6 Comparison and Summary of Wiseriver Features**

Important features of many systems like LON and KNX is openness and interoperability. Also other systems are designed to support these features as much as possible. The meaning of the open system here is that an open standard of the protocol is freely available. Devices of LON, KNX and others are not however interoperable to each other and it seems that this is not even the purpose because these systems are meant to be mostly as a one system solutions. oSSG and NHCC recognize and acknowledge the existence of different kind of systems and make them speak the same language to integrate them together. Adapters are needed if devices do not communicate in common language natively.

Wiseriver's "common language" is the polling protocol but it is not open since knowledge of the details is not required. Instead the platform just offers standard interfaces for connecting home automation equipment. Data is polled from specified devices through virtual wires and a set of simple programming operations is offered for creating control applications. Automation device manufactures do not have to go through major compatibility procedures if standard interfaces are used because control logic for these is already included in access nodes. Unlike in some open systems it is not possible for 3<sup>rd</sup> parties to design an interface unit that connects directly to Wiseriver system net via ring interfaces due to the proprietary protocol.

Wiseriver's layer 2 link technology is based on top of layer 1 physical Ethernet. Putting layer 2 Ethernet and other data communications back again on top of Wiseriver following main advantages could be seen.

<sup>&</sup>lt;sup>†</sup> formally 8P8C connector with T568A/B termination

- Easy and economical ring wiring but virtually full connectivity

- Multiple independent connections of different types in a single medium

- Definite resource sharing, guaranteed capacity for each application

Wiseriver functions are implemented using FPGA controller in master and access node components which is discussed in next chapter. Controllers are the basis on which the system architecture is defined at circuit level. FPGAs interface to the system net on one side and to user devices on the other. Also when considering the possibility to run application programs some resemblance could be seen when compared to Neuron chip of LON. Most relevant Wiseriver features are discussed in table below by summarizing comments.

| Feature                            | Comment                                                                                                                                                                                                                                                                                                                                                                                                              |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Maximum<br>network size            | 30 nodes and 128 transmission channels (virtual wires) altogether. 4 control applications in each access node as long as free channels available.                                                                                                                                                                                                                                                                    |

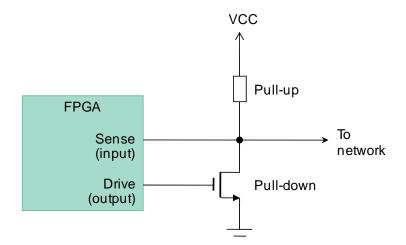

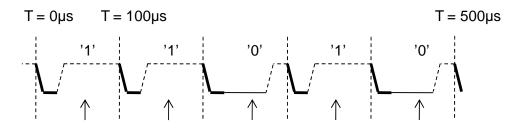

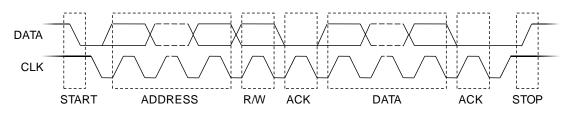

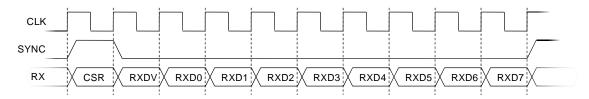

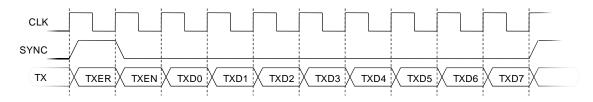

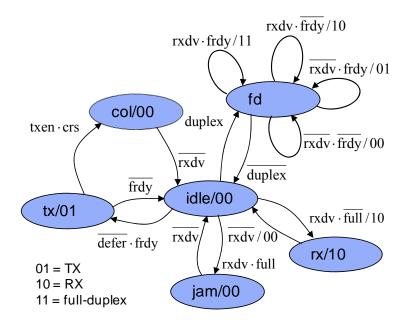

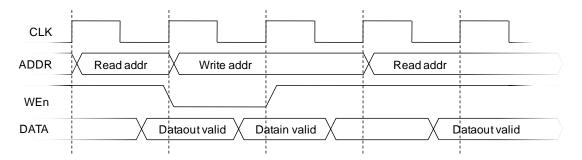

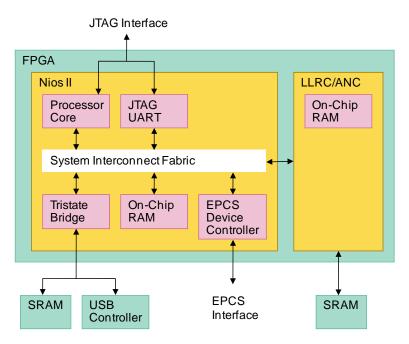

| Data<br>transmission<br>capacity   | Maximum bit rate of one data channel is almost 100 Mbit/s which is also<br>the total bit rate of each segment that all applications share. This is<br>enough for several lightweight and mediumweight data applications but<br>not for much higher speeds. Also when using hub type connection a half<br>duplex is required for back pressure and participants send one at a time<br>due to the collision avoidance. |