TKK Dissertations 76 Espoo 2007

#### TRANSMITTER ARCHITECTURES WITH DIGITAL MODULATORS, D/A CONVERTERS AND SWITCHING-MODE POWER AMPLIFIERS

**Doctoral Dissertation**

Johan Sommarek

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory TKK Dissertations 76 Espoo 2007

#### TRANSMITTER ARCHITECTURES WITH DIGITAL MODULATORS, D/A CONVERTERS AND SWITCHING-MODE POWER AMPLIFIERS

**Doctoral Dissertation**

#### Johan Sommarek

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Electrical and Communications Engineering for public examination and debate in Auditorium S4 at Helsinki University of Technology (Espoo, Finland) on the 20th of June, 2007, at 12 noon.

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory

Teknillinen korkeakoulu Sähkö- ja tietoliikennetekniikan osasto Piiritekniikan laboratorio Distribution: Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory P.O. Box 3000 FI - 02015 TKK FINLAND URL: http://www.ecdl.tkk.fi Tel. +358-9-4512271 Fax +358-9-4512269

© 2007 Johan Sommarek

ISBN 978-951-22-8808-3 ISBN 978-951-22-8809-0 (PDF) ISSN 1795-2239 ISSN 1795-4584 (PDF) URL: http://lib.tkk.fi/Diss/2007/isbn9789512288090/

TKK-DISS-2308

Multiprint Oy Espoo 2007

| ABSTRACT OF DOCTORAL DISSERTATION                                          | HELSINKI UNIVERSITY OF TECHNOLOGY<br>P.O. BOX 1000, FI-02015 TKK<br>http://www.tkk.fi |

|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| Author                                                                     | nttp://www.tkk.11                                                                     |

| Name of the dissertation                                                   |                                                                                       |

|                                                                            |                                                                                       |

| Manuscript submitted                                                       | Manuscript revised                                                                    |

| Date of the defence                                                        |                                                                                       |

| Monograph                                                                  | Article dissertation (summary + original articles)                                    |

| Department<br>Laboratory<br>Field of research<br>Opponent(s)<br>Supervisor |                                                                                       |

| Instructor                                                                 |                                                                                       |

|                                                                            |                                                                                       |

| Keywords                                                                   |                                                                                       |

| ISBN (printed)                                                             | ISSN (printed)                                                                        |

| ISBN (pdf)                                                                 | ISSN (pdf)                                                                            |

| Language                                                                   | Number of pages                                                                       |

| Publisher                                                                  |                                                                                       |

| Print distribution                                                         |                                                                                       |

| The dissertation can be read at http://lib.tkk.fi/Dis                      | ss/                                                                                   |

| VÄITÖSKIRJAN TIIVISTELMÄ                                | TEKNILLINEN KORKEAKOULU<br>PL 1000, 02015 TKK<br>http://www.tkk.fi |

|---------------------------------------------------------|--------------------------------------------------------------------|

| Tekijä                                                  |                                                                    |

| Väitöskirjan nimi                                       |                                                                    |

| Käsikirjoituksen päivämäärä                             | Variatur käsikisisituksan päivämääsä                               |

|                                                         | Korjatun käsikirjoituksen päivämäärä                               |

| Väitöstilaisuuden ajankohta                             | 1                                                                  |

| Monografia                                              | Yhdistelmäväitöskirja (yhteenveto + erillisartikkelit)             |

| Osasto                                                  |                                                                    |

| Laboratorio<br>Tutkimusala                              |                                                                    |

| Vastaväittäjä(t)                                        |                                                                    |

| Työn valvoja                                            |                                                                    |

| Työn ohjaaja                                            |                                                                    |

| Tiivistelmä                                             |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

|                                                         |                                                                    |

| Asiasanat                                               |                                                                    |

| ISBN (painettu)                                         | ISSN (painettu)                                                    |

| ISBN (pdf)                                              | ISSN (pdf)                                                         |

| Kieli                                                   | Sivumäärä                                                          |

| Julkaisija                                              |                                                                    |

| Painetun väitöskirjan jakelu                            |                                                                    |

| Luettavissa verkossa osoitteessa http://lib.tkk.fi/Diss | 5/                                                                 |

## Preface

This thesis was researched at the Electronic Circuit Design Laboratory, Helsinki University of Technology. Some of the projects that this thesis is based on were financed by TEKES and Nokia Networks. My studies were also funded by the Graduate School in Electronics, Telecommunications and Automation (GETA). So an enormous "Thank you" goes to Iiro Hartimo, the boss of GETA at TKK, for all the support he and GETA have given me.

I feel very grateful to Professor Kari Halonen for giving me the opportunity to work as part of the projects and for giving me an opportunity to write this thesis. I want to thank my instructors Jouko Vankka and Hannu Tenhunen for the guidance they have given me and also Emil Aaltosen Säätiö, Nokia Foundation, Tekniikan Edistämissäätiö and Elektroniikka Insinöörien Säätiö for the financial support they have given.

I would like to thank Jaakko Ketola, Ilari Teikari, Jonne Lindeberg, Olli Väänänen, Marko Kosunen, Antti Virtanen, Ville Saari and Pasi Juurakko for their contribution to the work. I am also grateful to my room mates Jaakko, Ilari, Olli, Lasse Aaltonen and Yang Fan and all the staff of the Electronic Circuit Design Laboratory for all the help and support they have given and for creating a stimulating working ambience.

I would also like to thank my friends, parents, sister and girlfriend for their all kind of support for my educational and non-educational activities.

Espoo, 21st May 2007

Johan Sommarek

This page is intentionally left blank.

# Contents

|   | Pref | ace                                                                       | i    |

|---|------|---------------------------------------------------------------------------|------|

|   | Sym  | bols- and abbreviations                                                   | v    |

|   | List | of Publications                                                           | xiii |

|   | Con  | tribution of the author                                                   | XV   |

| 1 | Intr | oduction                                                                  | 1    |

|   | 1.1  | Background                                                                | 1    |

|   | 1.2  | Objectives of the work                                                    | 2    |

|   | 1.3  | Contents of the thesis                                                    | 2    |

| 2 | Tra  | nsmitter architecture in wireless communication base stations             | 3    |

|   | 2.1  | Analogue Up-mixing                                                        | 3    |

|   |      | 2.1.1 Direct-Conversion Transmitters                                      | 3    |

|   |      | 2.1.2 Two-Step Transmitters                                               | 4    |

|   | 2.2  | Digital/Analogue                                                          | 4    |

|   | 2.3  | Transmitter architectures utilising non-linear                            |      |

|   |      | power amplifiers                                                          | 5    |

|   |      | 2.3.1 Envelope Elimination and Restoration                                | 5    |

|   |      | 2.3.2 Linear Amplification with Nonlinear Components                      | 6    |

|   | 2.4  | Direct Digital Conversion                                                 | 7    |

|   | 2.5  | Delta-Sigma Direct Digital Conversion                                     | 8    |

|   | 2.6  | Direct Digital RF Modulation                                              | 8    |

|   | 2.7  | Transmitter architectures researched                                      | 9    |

| 3 | Digi | tal modulator architectures for wireless communication base station trans | -    |

|   | mitt | ers                                                                       | 11   |

|   | 3.1  | Phase accumulator                                                         | 11   |

|   | 3.2  | CORDIC                                                                    | 12   |

|   | 3.3  | Direct Digital Synthesizer based on Look up Tables                        | 15   |

|   |      | 3.3.1 Sine memory compression                         | 15 |

|---|------|-------------------------------------------------------|----|

|   | 3.4  | Conclusion and implemented DDFSs                      | 19 |

|   |      | 3.4.1 Implemented DDFSs                               | 20 |

| 4 | Digi | al/Analogue Conversion in base station transmitters   | 23 |

|   | 4.1  | Performance metrics of D/A converters                 | 23 |

|   | 4.2  | Nyquist rate D/A converters                           | 23 |

|   |      | 4.2.1 Current-steering D/A converters                 | 24 |

|   |      | 4.2.2 Survey of published current-steering converters | 27 |

|   |      | 4.2.3 Implemented D/A converter                       | 27 |

|   | 4.3  | Oversampling D/A converters                           | 29 |

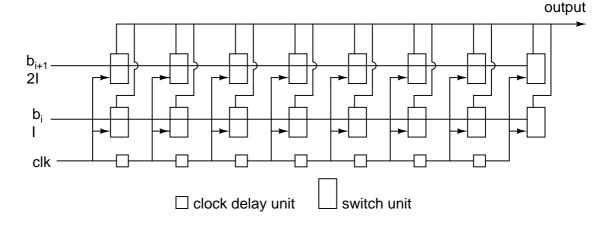

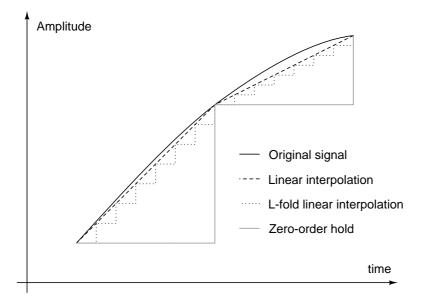

|   |      | 4.3.1 Interpolation                                   | 30 |

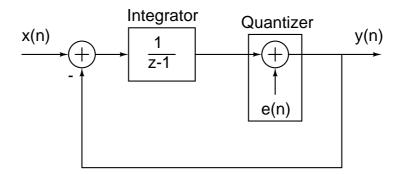

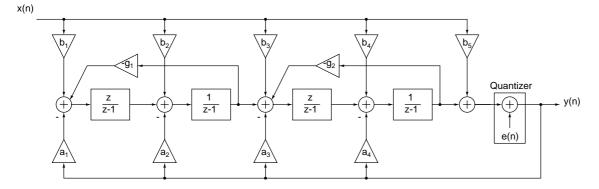

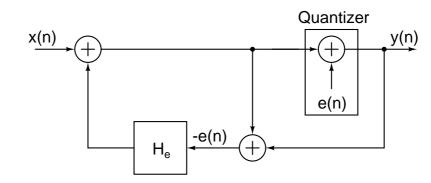

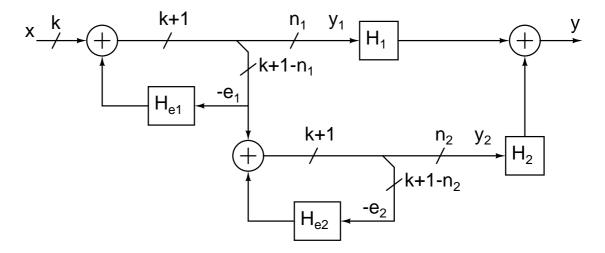

|   |      | 4.3.2 $\Delta\Sigma D/A$ converters                   | 30 |

|   |      | 4.3.3 Multi-bit quantization                          | 33 |

|   |      | 4.3.4 Problems                                        | 34 |

|   |      | 4.3.5 Bandpass and quadrature                         | 35 |

|   |      | 4.3.6 Post-filter for the out of band noise           | 35 |

|   |      | 4.3.7 Pulse-width modulation                          | 35 |

|   |      | 4.3.8 Implemented $\Delta\Sigma$ D/A-converters       | 36 |

|   | 4.4  | Summary                                               | 37 |

| 5 | Swit | ching-mode power amplifiers                           | 39 |

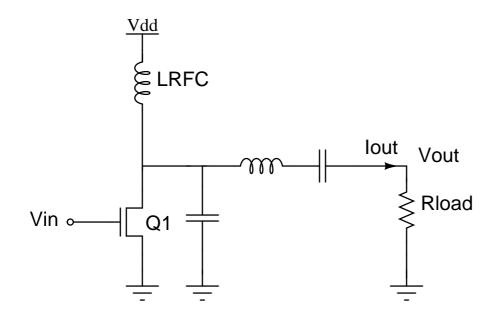

|   | 5.1  | Class-E power amplifier                               | 39 |

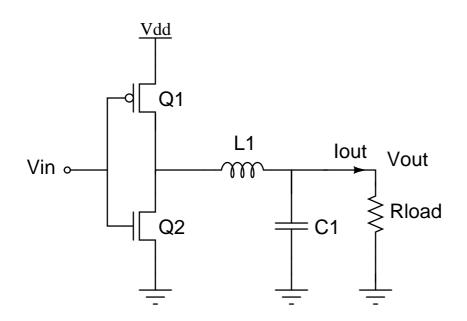

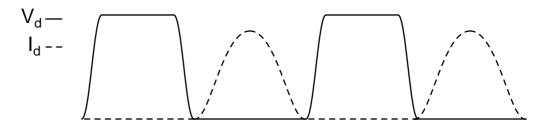

|   | 5.2  | Class-D power amplifier                               | 40 |

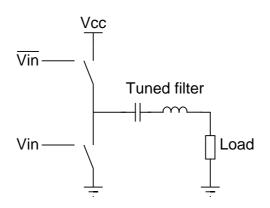

|   |      | 5.2.1 Complementary voltage-mode configuration        | 41 |

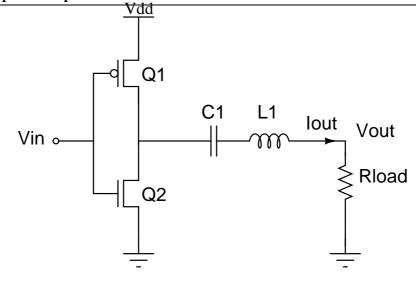

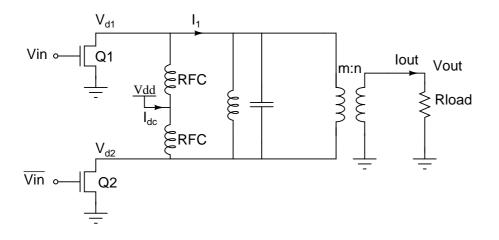

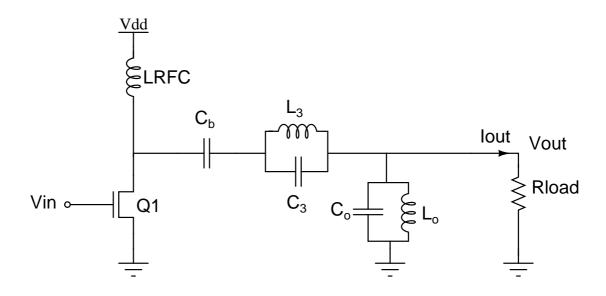

|   |      | 5.2.2 Current-mode class-D amplifier                  | 42 |

|   |      | 5.2.3 Survey of published class-D power amplifiers    | 43 |

|   | 5.3  | Class-S power amplifier                               | 44 |

|   | 5.4  | Class-F power amplifier                               | 44 |

|   | 5.5  | Losses in non-linear amplifier circuits               | 45 |

|   | 5.6  | Switching-mode power amplifiers with over-            |    |

|   |      | sampling noise-shaping D/A converters                 | 48 |

|   |      | 5.6.1 Cases researched in the papers                  | 49 |

|   | 5.7  | Comparison of the classes                             | 49 |

| 6 | Sum  | mary of Publications                                  | 51 |

| 7 | Con  | clusions                                              | 55 |

|   | 7.1  |                                                       | 56 |

# Symbols and abbreviations

| $A_{VT}$       | Threshold factor matching parameter of a transistor |

|----------------|-----------------------------------------------------|

| $A_{\beta}$    | Current factor matching parameter of a transistor   |

| В              | Bandwidth                                           |

| $C_d$          | Drain capacitance                                   |

| $C_g$          | Gate capacitance                                    |

| Ε              | Signal envelope                                     |

| $E_L$          | Inductive energy loss                               |

| $E_d$          | Capacitive energy loss                              |

| $E_g$          | Energy lost at the gate of a switching-mode PA      |

| $E_m$          | Maximum value of $E(t)$                             |

| F <sub>r</sub> | Phase increment or frequency control word           |

| G              | Gain                                                |

| Н              | Transfer function                                   |

| $H_e$          | Loop filter transfer function                       |

| $I_+$          | Output current (+ node)                             |

| <i>I_</i>      | Output current (- node)                             |

| $I_d$          | Drain current                                       |

| $I_g$          | Current to the gate of a transistor                 |

| Iout           | Output current                                      |

| L              | Interpolation factor                                |

| L                 | Phase accumulator word length                                                 |

|-------------------|-------------------------------------------------------------------------------|

| L                 | Transistor gate length                                                        |

| $L_d$             | Drain inductance                                                              |

| Ν                 | DAC resolution                                                                |

| Ν                 | Number of elementary angles                                                   |

| $N_0$             | Wordlength of input signal                                                    |

| $N_1$             | Wordlength of the output of an interpolator                                   |

| $P_L$             | Inductive power loss                                                          |

| P <sub>SAT</sub>  | Power loss due to saturation voltage                                          |

| $P_d$             | Capacitive power loss                                                         |

| $P_{g,sin}$       | Power loss at the gate of a switching-mode PA with a sinusoidal drive signal  |

| P <sub>gs</sub>   | Power loss at the gate of a switching-mode PA with a square wave drive signal |

| Pin               | Input power                                                                   |

| Pout              | Output power                                                                  |

| Q                 | Charge                                                                        |

| R                 | Oversampling ratio, resistance                                                |

| $R_g$             | Gate resistance                                                               |

| R <sub>load</sub> | Load resistance                                                               |

| $V_{GS}$          | Gate-source voltage                                                           |

| V <sub>SAT</sub>  | Saturation voltage of a switch transistor                                     |

| $V_T$             | Threshold voltage                                                             |

| V <sub>ct</sub>   | Voltage from the node between the switch transistors to ground                |

| $V_{dd}$          | Positive supply voltage                                                       |

| $V_d$             | Drain voltage                                                                 |

| $V_{gs}$          | Gate-source voltage                                                           |

| Vin         | Input voltage                                           |

|-------------|---------------------------------------------------------|

| Vout        | Output voltage                                          |

| W           | Phase accumulator output wordlength                     |

| W           | Transistor gate width                                   |

| $\delta_s$  | Skin depth                                              |

| γ           | Coarse rotation angle                                   |

| κ           | Quadrant rotation angle                                 |

| $\mu_0$     | Permeability in vacuum                                  |

| $\mu_i$     | Rotation sequence                                       |

| ω           | Fundamental frequency                                   |

| φ           | Phase                                                   |

| σ           | Conductivity                                            |

| $\sigma(I)$ | Unit current source standard variation                  |

| inv_norm    | Inverse cumulative normal distribution.                 |

| θ           | Rotation angle                                          |

| $b_l$       | Control bit of the switches of a current-steering DAC   |

| e(n)        | Error signal                                            |

| f(x)        | Approximation function in interpolation                 |

| $f_N$       | Data rate                                               |

| $f_T$       | Gain bandwidth                                          |

| $f_{clk}$   | Clock frequency                                         |

| fout        | Output frequency                                        |

| $f_s$       | Sampling frequency                                      |

| $f_{sw}$    | Switching frequency of a switching-mode power amplifier |

| $m_k$       | Slope of segment k                                      |

- $p_k$ Second order interpolation coefficient for segment ksNumber of segments $w_l$ Weight coefficient

- *x* Input signal

- $x_f$  Final x-coordinate

- y Output signal

- *y<sub>f</sub>* Final y-coordinate

- $y_k$  Initial amplitude of segment k

- ACLR Adjacent channel leakage ratio

- AM Amplitude modulation

- BP Bandpass

- BPF Bandpass filter

- BiCMOS Bipolar CMOS

- CDMA Code division multiple access

- CIFB Cascade of integrators feedback

- CIFF Cascade of integrators feedforward

- CMCD Current-mode class-D

- CMOS Complementary metal oxide semiconductor

- CORDIC Coordinate rotation digital computer

- CRFB Cascade of resonators feedback

- CRFF Cascade of resonators feedforward

- CSD Canonic signed digit

- D/A Digital-to-Analogue

- DAC D/A converter

- dBc Decibels below carrier

| DC   | Direct current                                |

|------|-----------------------------------------------|

| DDFS | Direct digital frequency synthesizer          |

| DDRM | Direct digital RF modulation                  |

| DDS  | Direct digital synthesizer                    |

| DEM  | Dynamic element matching                      |

| DNL  | Differential nonlinearity                     |

| DRFC | Direct digital RF converter                   |

| EDGE | Enhanced data rates for GSM evolution         |

| EEAS | Extended Elementary Angle Set                 |

| EER  | Envelope elimination and restoration          |

| ENOB | Effective number of bits                      |

| FET  | Field-effect transistor                       |

| FIR  | Finite impulse response                       |

| FPGA | Field programmable gate array                 |

| GSM  | Global System for Mobile Communications       |

| Ι    | In-phase                                      |

| IF   | Intermediate frequency                        |

| IF   | Interpolation filter                          |

| INL  | Integral nonlinearity                         |

| LINC | Linear amplificaton with nonlinear components |

| LO   | Local oscillator                              |

| LSB  | Least significant bit                         |

- LUT Look-up table

- MASH Multi-stage noise shaping

- MOS Metal oxide semiconductor

| MSB  | Most significant bit                 |

|------|--------------------------------------|

| MSE  | Mean square error                    |

| MTPR | Multi-tone power ratio               |

| MVR  | Modified vector rotational           |

| NL   | Noise-shaping loop                   |

| NTF  | Noise transfer function              |

| OSR  | Oversampling ratio                   |

| PA   | Power amplifier                      |

| PF   | Post-filter                          |

| PM   | Phase modulation                     |

| PWM  | Pulse-width modulation               |

| Q    | Quadrature                           |

| QAM  | Quadrature amplitude modulation      |

| R    | Resistor                             |

| RAM  | Random access memory                 |

| RF   | Radio frequency                      |

| ROM  | Read-only memory                     |

| SFDR | Spurious-free dynamic range          |

| SNDR | Signal-to-noise-and-distortion ratio |

| SNR  | Signal-to-noise ratio                |

| STF  | Signal transfer function             |

| VCO  | Voltage controlled oscillator        |

| VDD  | Positive supply voltage              |

| VHDL | VHSIC Hardware Description Language  |

| VMCD | Voltage-mode class-D                 |

WCDMA Wideband CDMA

ZCS Zero-current-switching

ZVS Zero-voltage-switching

This page is intentionally left blank.

# **List of Publications**

| P1 | J. Vankka, J. Pyykönen, J. Sommarek, M. Honkanen and K. Halonen, A<br>Multicarrier GMSK Modulator for Base Station, IEEE Journal of Solid-State<br>Circuits, Vol. 37, No 10, pp. 1226-1234 October 2002.                                                             |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2 | J. Vankka, J. Ketola, O. Väänänen, J. Sommarek, M. Kosunen and K. Halonen<br>'A GSM/EDGE/WCDMA Modulator With On-chip D/A Converter for base<br>station,' IEEE Trans. on Circuits and Systems Part II, Vol 49, No.10, pp:<br>645-655, Oct. 2002                      |

| Р3 | J. Sommarek, M. Kosunen, J. Vankka, K. Halonen, '14-bit 110 MHz CMOS D/A Converter', Proc. 21st Norchip Conference, Nov. 10 - 11, 2003, Riga, Latvia, pp. 104-107.                                                                                                   |

| P4 | J. Vankka, J. Sommarek, J. Ketola, I. Teikari and K. A. I. Halonen, 'A Di-<br>gital Quadrature Modulator With On-Chip D/A Converter', IEEE Journal Of<br>Solid-State Circuits, Vol. 38, No 10, October 2003, pp. 1635-1642                                           |

| Р5 | J. Sommarek, J. Vankka, J. Ketola, J. Lindeberg and K. Halonen, 'A Digital<br>Modulator with Bandpass Delta-Sigma Modulator', Springer Science + Busi-<br>ness Media Inc., Analog Integrated Circuits and Signal Processing, Vol. 43,<br>No 1, pp. 81-86, April 2005 |

| P6 | J. Lindeberg, J. Sommarek, J. Vankka and K. Halonen, 'A 1.5V direct digital synthesizer with tunable Delta-Sigma modulator in 0.13 $\mu$ m CMOS,' IEEE Journal of Solid-State Circuits Vol. 40, No 9, pp. 1978-1982 September 2005                                   |

| Р7 | J. Sommarek, A. Virtanen, J. Vankka and K. Halonen, 'Comparison of Dif-<br>ferent Class-D Power Amplifier Topologies for 1-bit RF Band-Pass Delta-<br>Sigma D/A Converters', International Symposium on Signals Systems and<br>Electronics, ISSSE 2004               |

| Р8 | J. Sommarek, A. Virtanen, J. Vankka and K. Halonen, 'Comparison of Dif-<br>ferent Class-D Power Amplifier Topologies for 1-bit Band-Pass Delta-Sigma<br>D/A Converters, Proceedings of 22nd Norchip Conference, November 8-9,<br>2004, Oslo, Norway, pp. 115-118.    |

P9 J. Sommarek, V. Saari, J. Lindeberg, J. Vankka and K. Halonen, 'A 20 MHz

BP-PWM and BP-DSM Class-D PA in 0.18 μm CMOS', Proc. of International Conference on Electronics, Circuits and Systems, December 11 - 14, 2005, Gammarth, Tunisia

## **Contribution of the author**

As a general guideline, the first author of each publication carries the main responsibility for the manuscript.

In paper P1, I carried out the circuit design, analysis and measurements. Jouko Vankka was involved as instructor and in system and architecture design and was behind the idea of the ramp generator. Jaakko Pyykönen designed the D/A converter and Mauri Honkanen was involved in the system specification.

In paper P2, I designed the ramp generator and the D/A converter, which is presented in more detail in paper P3, Jaakko Ketola designed the digital part of the circuit and Olli Väänänen and Jouko Vankka were involved in system and architecture design.

I designed the D/A converter presented in P3, Marko Kosunen instructed me in the design and performed the SFDR measurements with the cascade transistors by-passed.

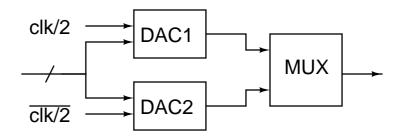

In paper P4, I designed the digital part, including VHDL code and circuit design, but excluding the multiplexer at the digital-analogue interface, which was designed by Jaakko Ketola. Ilari Teikari designed the D/A converter. I performed the measurements related to the digital part of the circuit. Jouko Vankka was involved in system and architecture design and as instructor.

In paper P5, I designed the VHDL code of the upconverter and performed the measurements of the circuit. Jaakko Ketola designed the  $\Delta\Sigma$ -modulator and performed the integrated circuit of the digital part. Jonne Lindeberg designed the D/A converter. Jouko Vankka was involved as instructor and in system and architecture design.

I designed the digital part of the circuit presented in paper P6, while Jonne Lindeberg designed the D/A converter and measured the circuit. Jonne Lindeberg and Jouko Vankka were involved in system and architecture design and Jouko Vankka as instructor.

In paper P7, I performed the simulations and was the instructor of Antti Virtanen, who wrote the APLAC code that I developed further for the simulations. The introduction was written by Antti Virtanen. Jouko Vankka was involved as instructor.

In paper P8, I performed the simulations, the circuit design and all the measurements. I developed further the APLAC code that had originally been designed by Antti Virtanen in paper P7. Jouko Vankka was involved as instructor.

In paper P9, I made the simulations, and all the measurements. In the simulations of the  $\Delta\Sigma$ -modulator I utilized Matlab code originally written by Jonne Lindeberg. Ville

Saari designed the integrated power amplifier. Jouko Vankka was involved as instructor.

## **Chapter 1**

## Introduction

#### 1.1 Background

Mobile communication systems had gained high market penetration by the time of writing this thesis. Competition has forced the price of mobile communication down, thereby forcing the system manufacturers to cut costs in order to gain higher profit margins. In particular, mobile telephony has seen fierce competition; not only does this competition put pressure on the prices of mobile phones and calls, but also on the prices of the hardware used in the base stations. In addition to mobile telephony, the newest generations of mobile communications also provide mobile internet services where the clients tend to demand higher and higher bandwidths all the time. Thus the development is towards reduced cost and higher bandwidths.

Also, the transition from older to newer generations sets demand for support of multiple standards as the generation shift is not instantaneous; also, integration of several standards into a single chip involves higher volumes for the chip and thereby aids the reduction of its unit cost. Thus the pressure is on to demand flexibility from the base station to accommodate transmission of multiple standard communication signals and to be able to service an increasing number of clients simultaneously. Moreover, the cost pressure motivates a movement towards the digitalization and higher integration level of the transmitters as the analogue parts tend to be more costly, less flexible and require more tuning.

The switching-mode power amplifiers have theoretically superior efficiencies compared to those of linear power amplifiers. Also, in practice, in many applications they attain significantly higher efficiencies than linear power amplifiers.

Therefore, this thesis contributes to this digitalization effort by presenting research on multicarrier, multimode digital modulators and digital quadrature modulators. At the digital-analogue interface both Nyquist-rate D/A converters and oversampling  $\Delta\Sigma$ modulation based D/A converters are researched. Finally switching-mode power amplifiers are studied in combination with  $\Delta\Sigma$ -D/A converters.

#### **1.2** Objectives of the work

The research described in this thesis focuses on the design of digital modulators based on direct digital frequency synthesis, digital quadrature modulator based upconversion of the digital baseband signal to IF, D/A conversion using a Nyquist-rate current-steering D/A converter and  $\Delta\Sigma$ -modulator-based D/A conversion at IF. Another objective was to investigate the suitabilities of a 1-bit bandpass  $\Delta\Sigma$ -modulator and a bandpass pulse-width modulator to drive a Class-D power amplifier.

#### **1.3** Contents of the thesis

The thesis is organised into two parts. In the first part, an overview of the design issues related to the digital modulation, upconversion, D/A conversion and power amplification in wireless communication base station transmitters is given to put into context and summarize the technical work that has been carried out. First, Chapter 2 reviews transmitter architectures for wireless communication base station applications. In Chapter 3, issues related to the design of digital modulators for wireless communication base station transmitter systems are discussed and CORDIC and LUT-based direct digital synthesizers are reviewed. Chapter 4 summarizes different digital-analogue conversion methods for wireless communication base station transmitter systems, concentrating on current-steering D/A converters and D/A converters utilising  $\Delta\Sigma$  modulation. In Chapter 5, switching-mode power amplifier topologies are briefly reviewed and the theory and fundamental concepts behind Class-D power amplifiers are introduced. The second part of this thesis is composed of the published papers.

### Chapter 2

# Transmitter architecture in wireless communication base stations

Conventionally, the signal processing in wireless communication takes place in the digital domain with signal frequencies significantly lower than the radio frequency (RF) that is needed for transmission. Thus, in order to perform the transmission, an upconversion of the baseband signal is needed. This upconversion can be accomplished in various manners including analogue mixing, direct digital conversion and combined digital/analogue upconversion.

#### 2.1 Analogue Up-mixing

In a fully analogue upconversion the digital baseband signal is converted into an analogue signal and then upconverted into a radio frequency signal in the analogue domain. The upconversion chain can consist of one, two or more mixer stages.

#### 2.1.1 Direct-Conversion Transmitters

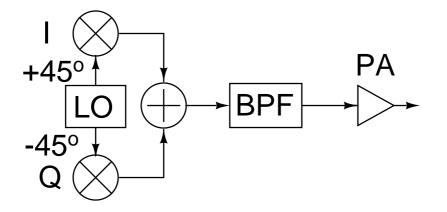

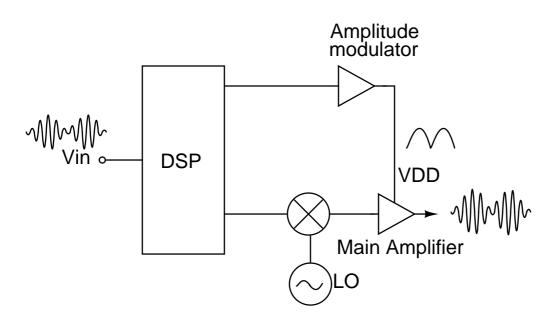

If the transmitted carrier frequency equals the local oscillator frequency, the architecture is called direct conversion. In this case, the modulation and upconversion coincide [Razavi 98]. A block diagram of the architecture is shown in Figure 2.1. In this architecture, the power amplifier may disturb the transmit local oscillator; this is because the output of the power amplifier is a modulated high-power signal centred at the LO frequency. Despite the existence of difference shielding techniques employed to isolate the VCO, it is still difficult the avoid the problem completely [Razavi 98].

Figure 2.1 Direct conversion transmitter

Figure 2.2 Two-step transmitter

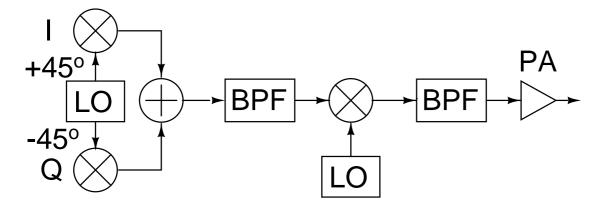

#### 2.1.2 **Two-Step Transmitters**

One approach to circumventing the LO pulling problem is to upconvert the baseband signal in two or more steps so that the power amplifier output spectrum is far from the frequency of the VCOs. For example, the architecture could look as in Figure 2.2, where the baseband I and Q channels are quadrature modulated at a lower frequency  $\omega_1$  and the result is upconverted to  $\omega_1 + \omega_2$  by mixing and bandpass filtering. The first bandpass filter suppresses the harmonics of the IF signal, whilst the second one removes the undesired sideband around  $\omega_1 - \omega_2$  [Razavi 98].

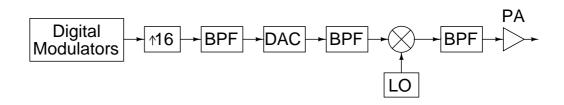

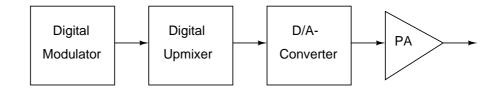

#### 2.2 Digital/Analogue

In digital/analogue upconversion, the signal is first upconverted digitally into an intermediate frequency (IF) signal using a digital quadrature modulator and then mixed up to the radio frequency using analogue techniques. This decreases the need for analogue components in the system. In addition, performing the quadrature modulation digitally yields high precision and a perfect I/Q-channel matching. Figure 2.3 shows an example block

Figure 2.3 Block diagram of a digital/analogue upconversion chain

Figure 2.4 EER system block diagram

diagram of the system.

# 2.3 Transmitter architectures utilising non-linear power amplifiers

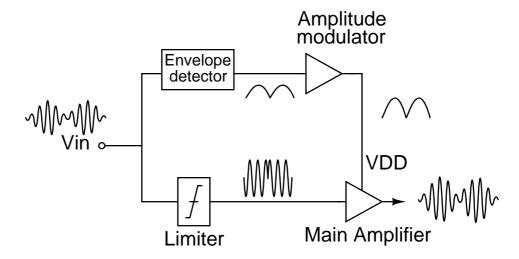

#### 2.3.1 Envelope Elimination and Restoration

An envelope elimination and restoration (EER) architecture endeavours to achieve high efficiency on non-constant envelope signals by feeding in the envelope of the transmitted signal to a non-linear, i.e. Class-E [Funk 96, Saari 05], Class-D [Raab 94b, Raab 94a] or Class-F [Weiss 01], power amplifier through its supply voltage, whilst the power amplifier is driven with a phase modulated signal. The idea is based on the fact that any narrow-band signal is equivalent to simultaneous amplitude and phase modulated (AM) and a phase modulated (PM) signal, which are then processed separately before combining them at the non-linear power amplifier, as shown in Figure 2.4. The amplitude and phase modulated signals can be generated with analogue circuitry or by digital signal processing [Saari 05], in which case it can also be called polar modulation. Polar modulation can also be used to create multimode operation in a transmitter [Heinbach 01]. This

Figure 2.5 EER with digital generation of the PM and AM signals

Figure 2.6 LINC amplifier system

kind of system is illustrated in Figure 2.5.

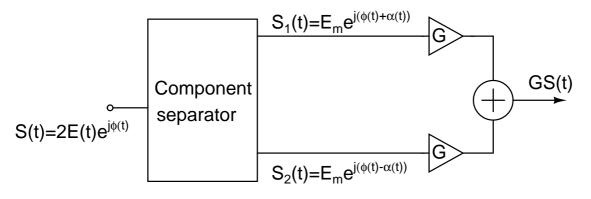

#### 2.3.2 Linear Amplification with Nonlinear Components

Linear amplification with non-linear components (LINC), which is also known as Chireix outphasing, is based on the idea of separating the signal to be amplified in two constant amplitude signals, whose phases are modulated in such a way that their sum after amplification is the desired amplified signal. A block diagram of a LINC system is depicted in Figure 2.6.

The incoming signal (S(t)), which may be both amplitude and phase modulated, can be expressed as

$$S(t) = 2E(t)e^{j\phi(t)},$$

(2.1)

where E(t) represents the envelope of the signal. If we denote the maximum value of E(t)

Figure 2.7 Direct Digital Conversion Architecture

as  $E_m$ , then the signal S(t) can be separated into two constant envelope signals,  $S_1(t)$  and  $S_2(t)$ , as follows [Cox 74, Zhang 01].

$$S_1(t) = E_m e^{j(\phi(t) + \alpha(t))}$$

$$S_2(t) = E_m e^{j(\phi(t) - \alpha(t))}$$

(2.2)

where

$$\alpha(t) = \arccos\left(\frac{E(t)}{E_m}\right) \tag{2.3}$$

Both the constant envelope signals are then amplified with two nonlinear PAs with the same gain G, which yields:

$$G(S_1(t) + S_2(t)) = GS(t).$$

(2.4)

The resulting signal is a linearly amplified version of the incoming signal. The system has potential for higher efficiency than a system utilising a linear PA, since it employs high-efficiency non-linear amplifiers [Raab 85]. The system is vulnerable to the mismatch either in the phases of the branches or in the gains of the amplifiers, which cause distortion. In an endeavour to quit the phase mismatch problems, both analogue [Shi 00] and digital [Zhang 01,Zhang 00,Gerhard 05] component separators have been developed.

#### 2.4 Direct Digital Conversion

In direct digital conversion, the baseband signal is generated with a digital modulator using a Direct Digital Frequency Synthesizer (DDFS). Then it is upconverted with a digital upmixer to radio frequency. The D/A conversion is performed at RF and the D/A converter is followed by a power amplifier. However, a multi-bit D/A converter is susceptible to glitches and spurious noise (as the output frequency increases), which is difficult to remove by filtering. Moreover parts of the digital circuitry are processing RF frequency signals, therefore their sampling frequency needs to be very high. This causes high power dissipation. Figure 2.7 illustrates the architecture.

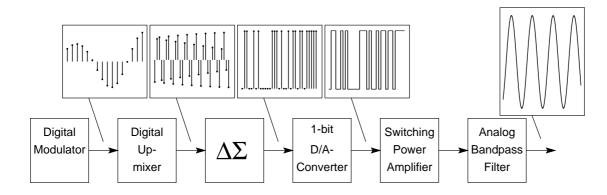

Figure 2.8 Block diagram of a digital upconversion chain using a Delta-Sigma DAC [Ketola 04]

#### 2.5 Delta-Sigma Direct Digital Conversion

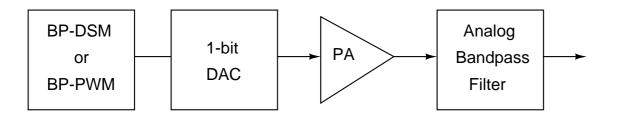

A transmitter architecture based on Delta-Sigma Direct Digital Conversion is similar to the aforementioned Direct Digital Conversion, but the multi-bit D/A converter is replaced with a 1-bit  $\Delta\Sigma$  D/A converter, which, due to its noise shaping, is suitable only for relatively narrowband signals. However, in many wireless communication standards, the signal bands are relatively narrow compared to the RF carrier frequency and therefore the narrowband nature of the  $\Delta\Sigma$  D/A converter does not impede its application in them.

The 1-bit  $\Delta\Sigma$  D/A converter overcomes some of the problems related to the multi-bit D/A converter. Since the output of the 1-bit  $\Delta\Sigma$  D/A only has two levels, any misplacement of the levels results only in gain error or offset. Neither of those is of great importance in many transmitter applications. The 1-bit  $\Delta\Sigma$  D/A converter is an all-digital circuit, which has several advantages over analogue signal processing, such as flexibility, noise immunity, reliability and potential improvements in performance and power consumption, because of the scaling of the technology. In addition, the design, synthesis, layout and testing of digital systems can be highly automated [Lindeberg 05]. The combination of a Direct Digital Frequency Synthesizer (DDFS) with a 1-bit  $\Delta\Sigma$ -D/A converter is attractive in digital transmitters, since it allows the power amplifier to be a switching-mode power amplifier, which may thus attain a high efficiency [Norsworthy 97].

#### 2.6 Direct Digital RF Modulation

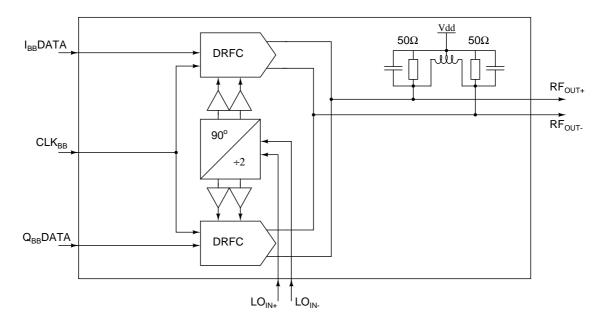

Direct Digital RF Modulation (DDRM) architecture is depicted in Figure 2.9. It is built around a Direct Digital RF Converter (DRFC) that combines the functionalities of a D/A converter and mixer [Eloranta 05]. The DRFC is based on a conversion cell of a current-steering D/A converter such that the current source and the current switches have been replaced with a mixer structure. The output currents from the conversion cells are summed at the output. The architecture is reminiscent of the Direct Conversion Transmitter of Section 2.1.1, but uses fewer analogue circuit blocks.

Figure 2.9 Direct Digital RF Modulator Architecture [Eloranta 05]

#### 2.7 Transmitter architectures researched

The digital modulators presented in papers P1 and P2 have their output signals centered between (11 and 16.5) and 19.2 MHz respectively. Therefore they are meant for the twostep transmitter architecture presented in Subsection 2.1.2. The architecture-level novelty of paper P1 is the multicarrier modulator that combines the carriers in the digital domain, whilst paper P2 presents a novel multimode modulator with GSM, EDGE, and WCDMA realised with the same modulator circuitry.

Paper P4 presents an upconverter for the Digital/Analogue architecture described in Section 2.2. The concept would also be applicable for a direct digital conversion architecture (Section 2.4), either when the transmitted RF frequency is low enough or if the digital circuits and D/A converter could be operated at a higher frequency.

The architecture-level novelty of the implementation is the multiplier-free digital quadrature modulation at a quarter or half of the sampling frequency. The circuit was one of the first digital quadrature modulators operating at 500 MHz. In the state of the art found in the literature the implementation of paper P4 is best compared with the hybrid CORDICbased implementations in [Wu 03] and [Caro 07] or the multiplier-free implementation based on circular shift registers in [Lin 97].

Paper P5 presents a digital quadrature modulator with a 1-bit bandpass  $\Delta\Sigma$  D/A converter, which could be used as part of a Delta-Sigma direct digital conversion architecture as described in Section 2.5. However, as in Paper P4, the circuit implemented did not reach operation at a high enough RF frequency for GSM, EDGE, or WCDMA, although the concept worked at a sampling frequency of 700 MHz and a signal frequency of 175 MHz in the VHF band.

The novelty is the combination of a multiplier-free digital quadrature modulator with a bandpass Delta-Sigma D/A converter. Therefore it is best compared to the same state of the art as paper P4. A similar architecture with a multi-bit  $\Delta\Sigma$  modulator is discussed in [Neitola 01].

Paper P6 presents a DDFS combined with a tunable  $\Delta\Sigma$  D/A converter capable of phase, amplitude, and quadrature amplitude modulation, which could be used as part of a transmitter architecture such as the  $\Delta\Sigma$  direct digital conversion architecture. The architecture is general-purpose in that it allows the IF to be selected freely within the Nyquist range. In the implemented circuit the maximum output frequency was 100 MHz, in the VHF band.

Papers P7-P9 present research on the switching mode power amplifier part of the Delta-Sigma direct digital conversion architecture described in Section 2.5. The architecture is best compared with those presented in the literature in [Jayaraman 98, Midya 02] and [Larson 05]. The state of the art is extended by simulations and measurements on topologies not found in prior art encountered in the literature. Experimental research on the transformer coupled voltage mode Class-D topology with  $\Delta\Sigma$ -modulated input is presented in paper P8 and research into the bandpass PWM-controlled Class-D power amplifier presented in [Midya 02] is extended to measurements in paper P9.

## Chapter 3

# Digital modulator architectures for wireless communication base station transmitters

In this chapter, the most prominent methods of digital modulation based on direct digital frequency synthesis are concisely reviewed. The perspective is that of a wireless communication base station transmitter. The two most important direct digital frequency synthesis methods are based on the use of a coordinate rotation digital computer (CORDIC) or look-up tables (LUT).

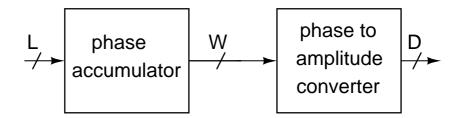

A direct digital frequency synthesizer is composed of a phase accumulator followed by a phase-to-amplitude converter, as illustrated in Figure 3.1.

#### **3.1** Phase accumulator

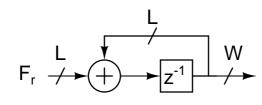

An operational block diagram of phase accumulator is depicted in Figure 3.2. The phase accumulator calculates the phase of the sine wave to be generated by adding a phase increment to the phase in an accumulator each clock cycle. The rate of the overflows of the accumulator gives the output frequency

Figure 3.1 Direct digital frequency synthesizer

Figure 3.2 Phase accumulator

$$f_{out} = \frac{F_r}{2^L} f_{clk} \tag{3.1}$$

where  $F_r$  is the phase increment (which is also called *frequency control word*), *L* the phase accumulator word length and *W* the word length of the output of the phase accumulator, which is usually truncated.  $F_r$  is an integer, hence the frequency resolution is obtained by substituting  $F_r = 1$ :

$$\Delta f = \frac{f_{clk}}{2^L} \tag{3.2}$$

The maximum output frequency is limited by the sampling theorem to  $f_{out} = f_{clk}/2$ .

Phase truncation to *W*-bits causes spurs in the output spectrum of the DDS. The effects of the phase truncation have been analyzed in [Nicholas 87, Cheng 04]. Modified phase accumulator structures that reduce the worst-case spur levels exist [Nicholas 87].

#### 3.2 CORDIC

The coordinate rotation digital computer (CORDIC) algorithm was introduced in [Volder 59]. It is a simple and efficient algorithm used to calculate hyperbolic, trigonometric and linear functions. CORDIC is based on the idea of decomposition of the desired rotation angle into the weighted sum of a set of predefined elementary rotation angles with the purpose of enabling the rotation without a multiplier, with shift and add operations [Hu 92b] and small LUT [Walther 71]. Therefore, it is found in applications such as simple microcontrollers and FPGAs. The algorithm is suitable for pipelining.

The tasks in the CORDIC algorithm are formulated as rotations of a  $2 \times 1$  vector. The rotations can be performed in three different coordinate systems, i.e. hyperbolic, linear and circular coordinate systems, and can be used for the calculation of hyperbolic and trigonometric functions, amongst others.

There are two modes in which a CORDIC algorithm can be operated:

- *Rotation mode* [Valls 06, Timmermann 92], which has also been called *vector ro-tation mode*, [Hu 92b] or *forward rotation mode*. The desired rotation angle θ is given. The objective is to compute the final coordinate [x<sub>f</sub> y<sub>f</sub>]<sup>t</sup> [Hu 92b].

- *Vectoring mode* [Valls 06, Timmermann 92], which has also been called *angle accumulation mode* [Hu 92b] or *backward rotation mode*. The desired rotation angle

$\theta$  is not given. The objective is to rotate the given initial vector  $[x(0) y(0)]^t$  to the *x*-axis so that the angle between them can be accrued [Hu 92b].

#### **CORDIC** in circular coordinate system

The circular variant is of interest in this chapter since it can be used for direct digital frequency synthesis [Kang 06, Yang 03, Kang 02]. Therefore rest of the section concentrates on it. The rotation angle  $\theta$  is decomposed into the weighted sum of the elementary rotation angles as follows [Hu 92b].

$$\theta = \sum_{i=0}^{N-1} \mu_i a_i \tag{3.3}$$

where N is the number of elementary angles,  $\mu_i \in -1, 1$  is the rotation sequence and  $a_i = \arctan(2^{-i})$  [Wu 01].

The inputs to the algorithm are  $x_0, y_0, z_0$ . The algorithm executes the following loop from i = 0 through *N*.

$$\begin{pmatrix} x_{i+1} \\ y_{i+1} \end{pmatrix} = \begin{pmatrix} 1 & -\mu_i 2^{-i} \\ \mu_i 2^{-i} & 1 \end{pmatrix} \begin{pmatrix} x_i \\ y_i \end{pmatrix} = k_i \begin{pmatrix} \cos(a_i) & \mu_i \sin(a_i) \\ -\mu_i \sin(a_i) & \cos(a_i) \end{pmatrix} \begin{pmatrix} x_i \\ y_i \end{pmatrix}_i$$

$$z_{i+1} = z_i - \mu_i a_i$$

(3.4)

where  $\mu_i = \operatorname{sign}(z_i)$  in rotation mode (in vectoring mode  $\mu_i = -\operatorname{sign}(x_i y_i)$ ) and  $a_i = \arctan 2^{-i}$ , i = 0, 1, 2, ..., N - 1 [Kang 06, Wu 01] and  $k_i = \sqrt{1 + 2^{-2i}}$ . The algorithm has a gain of  $\prod_{i=0}^{N-1} k_i$ . In order to maintain the norm the same as that of the input vector, scaling is needed:

$$\begin{pmatrix} x_f \\ y_f \end{pmatrix} = \frac{1}{\prod_{i=0}^{N-1} k_i} \begin{pmatrix} x_N \\ y_N \end{pmatrix} = \frac{1}{\prod_{i=0}^{N-1} \sqrt{1+2^{-2i}}} \begin{pmatrix} x_N \\ y_N \end{pmatrix}$$

(3.5)

where  $[x_f y_f]^t$  is the final output vector and  $z_N$  is the output phase [Wu 01]. When the gain can be tolerated, the scaling can be omitted and  $[x_N y_N]^t$  and  $z_N$  can be output instead. In a hardware realisation of the CORDIC algorithm, the loop is replaced by consecutive micro-rotation stages, each realising Equation (3.4). The quantization errors due to the finite word lengths of  $x_i, y_i$  and  $z_i$  and the number of iterations N determine the accuracy of the algorithm; the effect of these parameters have been studied in [Kota 93, Hu 92a, Vankka 00].

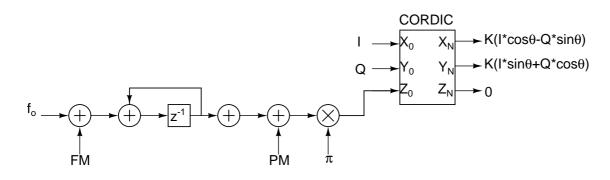

CORDIC can be used in polar-to-cartesian conversion [Gielis 91] for high-speed waveform synthesis. Here, its rotation mode is used in a circular coordinate system by setting  $y_0 = 0$ . CORDIC has also been used for cartesian-to-polar conversion, as in [Gerhard 05], where it operates as a LINC digital component separator in a WCDMA transmitter. Here

Figure 3.3 Rotation-mode CORDIC used for digital modulation [Valls 06]

the vectoring mode is employed in a circular coordinate system.

Rotation-mode CORDIC can be operated as a phase-to-amplitude converter of a direct digital frequency synthesizer (DDFS) [Kang 02]. The use of CORDIC as part of a direct digital synthesizer is explained in detail in [Valls 06]. A recent implementation of DDFS using differential CORDIC is reported in [Kang 06].

The rotation-mode CORDIC has also been used to perform quadrature modulation; e.g. in [Kosunen 01], it has been used in a QAM-modulator for a WCDMA base station and in [Vankka 02a] for a multimode base station. In both, the quadrature modulation has been accomplished by feeding the baseband I and Q data, as in Figure 3.3, and taking the quadrature modulated signal output from  $X_N$ .

#### **Modified CORDIC algorithms**

Latency time reduction and chip area savings have been sought in [Timmermann 89] by use of a modified CORDIC algorithm that employs multiplication and division operations in order to decrease the number of iterations. In [Wang 97], a hybrid CORDIC algorithm for rotation mode that replaces the least significant rotation angles with radix-2 coefficients is introduced.

Angle recoding is a modified CORDIC algorithm for vector rotation that is based on the idea of introducing a null rotation in the set of possible operations in the CORDIC iteration stages, i.e.  $\mu_i \in -1, 0, 1$  in (3.4) [Hu 93, Wu 02]. This can be interpreted as adding flexibility to the conventional CORDIC algorithm with an intention of making it faster and more accurate. A similar approach is that of the modified vector rotational (MVR) CORDIC [Wu 01]. In Extended Elementary Angle Set (EEAS)-based CORDIC in addition to relaxed  $\mu_i$  as above, the elementary angle set is extended [Wu 00].

A differential CORDIC algorithm utilizing redundant arithmetic [Dawid 96] has been used in [Kang 06] to realise a digit-pipelined DDFS where the phase-accumulator has been incorporated in the digit-level pipelining framework.

Hybrid LUT/CORDIC algorithms presented in [Janiszewski 01b,Janiszewski 01a,Janiszewski 04, Janiszewski 02] that combine the speed of LUTs and precision of CORDIC have been developed for direct digital frequency synthesis applications, which are suitable especially when quadrature modulation is not needed.

#### **Fine/coarse coordinate rotation**

In fine/coarse coordinate rotation, the rotation is decomposed in three parts as follows [Song 04]:

$$\theta = \frac{\pi}{2}\kappa + \frac{\pi}{16}\gamma + \frac{\pi}{128}\eta + \delta \tag{3.6}$$

The components are called quadrant, coarse and fine rotation  $(\frac{\pi}{128}\eta + \delta)$ , respectively.  $\kappa, \gamma$  and  $\eta$  are integers and  $\gamma, \eta \in [0, 7]$ . The quadrant rotation only needs interchange and/or negation operations. For the coarse rotation, the values of  $\cos(\frac{\pi}{16}\gamma)$  and  $\sin(\frac{\pi}{16}\gamma)$  are stored in LUT and for the fine rotation the  $\cos(\frac{\pi}{128}\eta + \delta)$  and  $\sin(\frac{\pi}{128}\eta + \delta)$  are calculated utilizing linear interpolation. The fine and coarse rotations are performed by complex multipliers. The fine/coarse approach results in a LUT size that increases polynomially with the resolution, whilst, in a pure LUT DDFS the dependence is exponential [Song 04]. This method has been used in [Torosyan 03, Song 04] for implementation of a Quadrature Direct Digital Synthesizer/Mixer with an output resolution of 13 and 15 bits and a sampling frequency of 300 and 330 MHz, respectively.

### **3.3** Direct Digital Synthesizer based on Look up Tables

In Direct Digital Frequency Synthesizers (DDFS) based on Look-up Tables (LUTs) the phase-to-amplitude converter of Figure 3.1 is realised with a random access memory (RAM), often mostly a read-only memory (ROM), since, in most DDFSs found in the literature, no remapping of the phase-to-amplitude characteristic have been needed as in [Gotoh 94, Prasad 06].

#### 3.3.1 Sine memory compression

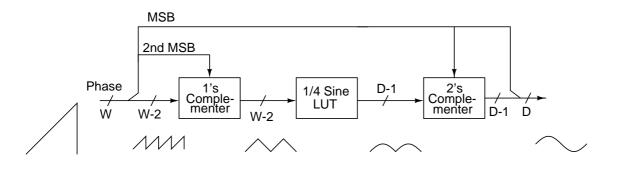

The most elementary technique of sine memory compression is to utilise the quarter wave symmetry of the sine function for memory compression and store only one quarter of the full period of the sine function in the memory and generate the rest from it as presented in Figure 3.4.

Further methods of compressing the quarter wave memory can be divided into three categories, angular decomposition, amplitude compression and interpolation, which, in turn, can be categorized by the order of the approximation polynomial.

Figure 3.4 Sine memory compression by quarter wave symmetry

Figure 3.5 Sunderland architecture

#### **Compression by angular decomposition**

The compression of quarter sine memory through angular decomposition is based on the idea of splitting the phase into smaller fractions and using these fractions to address two or more smaller LUTs, such that the total amount of LUT memory is decreased.

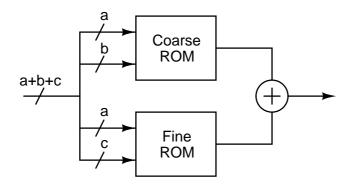

Sunderland architecture [Sunderland 84] (illustrated in Figure 3.5) is based on splitting the argument of sine function into three fractions:  $\phi = \alpha + \beta + \gamma$ , where the word lengths of the terms are *a*, *b* and *c*, respectively.  $\alpha$ ,  $\beta$  and  $\gamma$  are such that [Sunderland 84, Goldberg 96].

$$\alpha < \frac{\pi}{2}, \ \beta < \frac{\pi}{2} 2^{-a}, \ \gamma < \frac{\pi}{2} 2^{-(a+b)}.$$

(3.7)

Thus, using trigonometric identities, we have

$$\sin(\alpha + \beta + \gamma) = \sin(\alpha + \beta)\cos(\gamma) + \cos(\alpha)\cos(\beta)\sin(\gamma) - \sin(\alpha)\sin(\beta)\sin(\gamma) \quad (3.8)$$

This can be approximated as

$$\sin(\alpha + \beta + \gamma) \approx \sin(\alpha + \beta) + \cos(\alpha)\sin(\gamma)$$

(3.9)

The values of the first term of (3.9) are stored in the coarse ROM and the values of

Figure 3.6 Trigonometric approximations: sine-phase difference (dashed) and double trigonometric (dotted)

Figure 3.7 Amplitude compression circuit for memory compression in DDFS [Langlois 01]

the second term are stored in the fine ROM. A similar technique is presented in [Curticapean 01].

An improvement to the Sunderland method is to calculate the values of coarse and fine ROM such that either the mean square error (MSE) or the maximum error is minimized [Nicholas 88, Tang 02].

#### Amplitude compression

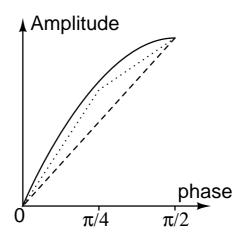

The amplitude compression techniques for sine memory exploit the redundancy between the value of the phase angle and the corresponding sine amplitude [Langlois 01]. The sine-phase difference algorithm is the simplest of these techniques. It approximates the sine function as a straight line, as shown in Figure 3.6. Only the approximation error is stored in a LUT. A generic block diagram of the amplitude compression method is shown in Figure 3.7. The double trigonometric approximation architecture [Yamagishi 98] combines the sine-phase difference algorithm with the subtraction of another triangular waveform, as shown in Figure 3.7. The implementation of this algorithm requires an additional complementer as additional logic hardware. More sophisticated amplitude compression methods have been presented in [Kim 03, Langlois 01, Yang 04], and [Sodagar 00]. The

Figure 3.8 Linear interpolation [Langlois 03b]

latter approximates the sine function with a parabolic function, therefore the implementation requires a multiplier. Second-order polynomial approximation with fixed coefficients utilizing canonic signed digit (CSD) hyperfolding has been presented in [Caro 04].

#### Linear interpolation

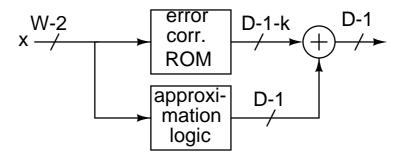

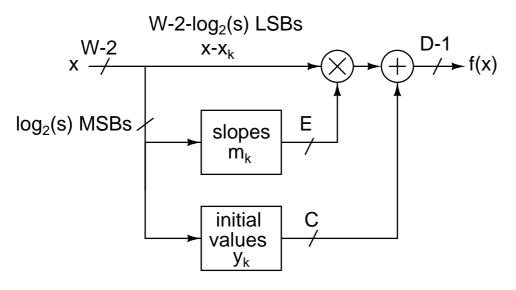

In a DDFS based on linear interpolation, the first quadrant of the sine function is divided into segments that are approximated with a piecewise linear function f(x) in (3.10) [Langlois 03a, Langlois 03b, Bellaouar 00]

$$f(x) = y_k + m_k(x - x_k), \text{ for } x \in [x_k, x_{k+1}), \text{ for all } k \in \mathbb{Z}, \ 0 \le k \le s - 1, x_0 = 0, x_s = 1,$$

(3.10)

where *s* is the number of segments and  $m_k$  and  $y_k$  are the slope and initial amplitude of each segment, respectively. The values of  $m_k$  and  $y_k$  are stored in LUTs. Figure 3.8 shows a block diagram of an implementation of a quadrant phase to amplitude converter of a DDFS based on linear interpolation. It needs two smaller LUTs and a multiplier to replace the 1/4 sine LUT of a pure LUT-based DDFS, as shown in Figure 3.4.

The dual slope approach [Strollo 03, Strollo 04] is a variation of the linear interpolation concept in that, instead of one slope per segment it utilizes two slopes per segment. Linear and nonlinear addressing schemes for the LUTs in a linear interpolation DDFS have been studied and implemented in [Chimakurthy 06].

#### Second-order polynomial interpolation

In a DDFS based on second-order polynomial interpolation. the first quadrant of the sine function is divided into segments that are approximated with a piecewise polynomial

function f(x) of second order as follows:

$$f(x) = y_k + m_k(x - x_k) - p_k(x - x_k)^2$$

(3.11)

where the interpolation coefficients:  $y_k, m_k, p_k$  are stored in LUTs. The implementation requires 2 multipliers. The compression method is also called *parabolic interpolation* [Fanucci 01] or *piecewise polynomial approximation* [Caro 05].

Quasi-linear interpolation [Ashrafi 05] is a hybrid between linear and second-order polynomial interpolation using parabolic interpolation for the more curved part and linear interpolation for the more linear part of the quadrant.

Other variations of the concept involve multi-stage linear interpolation [Hikawa 04] and piecewise parabolic interpolation using a Farrow structure [Eltawil 02b, Eltawil 02a].

#### **Conclusion of compression methods**

The sine memory compression methods trade computational complexity for memory. The key is to find a balance between performance in terms of SFDR and area and power consumption [Langlois 03a]. A study of this balance for an FPGA realisation is presented in [Cardells-Tormo 03]. The different methods of memory compression can be combined in order to find a balance for design as has been done in [Yang 04], which uses a quad-line approximation method for amplitude compression and Sunderland architecture for angle decomposition with fine and coarse ROMs and quantization and error ROM technique for additional ROM compression [Yang 04]. Comparisons of the compression ratios, SFDRs, memory sizes etc. of different compression methods have been reported in, for example, [Vankka 00, Yang 04, Kim 03, Chimakurthy 06, Langlois 03a] and [Said 03].

#### Finite Word Length Effects in LUT based DDFSs

The phase-to-amplitude converter introduces two different types of errors to the signal: the error due to memory compression nonlinearity and the error due to the amplitude quantization of the sine samples [Nicholas 88]. The deterioration of the SFDR of the signal caused by these errors has been studied in, for example, [Nicholas 88, Cheng 04, Vankka 00].

## **3.4** Conclusion and implemented DDFSs

Direct Digital Frequency Synthesizers can be realised using a variety of methods and architectures that can be divided into two categories, i.e. CORDIC based and LUT based. The computational complexity of CORDIC involves higher circuit complexity compared to a pure LUT-based DDFS with no computational complexity and high requirement of memory. Between these two extremes, there is a trade-off with multiple solutions of CORDIC that utilize LUTs and LUT-based DDFSs that utilize adders and multipliers to save memory. One prominent difference between CORDIC and LUT-based DDFS is, however, found in their application in QAM modulation, where an LUT-based DDFS requires 2 multipliers [Vankka 01] and complex QAM 4 multipliers [Valls 06], but no multipliers are needed in CORDIC-based implementation [Valls 06]. However, CORDIC requires higher datapath precision than LUT, in order to attain the same spectral purity [Song 04]. CORDIC and LUT-based DDFSs have been further compared in [Janiszewski 02]. Table 3.1 compares various implemented DDFSs.

#### 3.4.1 Implemented DDFSs

Papers P1 and P6 present LUT-based DDFS designs. The DDFS in paper P6 employs second-order polynomial interpolation for sine memory compression, achieving an SFDR of 87.09 dBc with an  $f_{clk}$  of 200 MHz. The total ROM size was 1600 bits, resulting in a high compression ratio of 123. The phase resolution (W) 14 and the output resolution (D) of the DDFS was 12. The chip was fabricated on a CMOS technology of 0.13  $\mu$ m with a total chip area of 2.02 mm<sup>2</sup>.

The DDFS in paper P1 employs an angular decomposition method for sine memory compression called the modified Nicholas architecture, attaining an SFDR of 87 dBc with an  $f_{clk}$  of 52 MHz. The phase resolution (W) was 14 and the output resolution (D) of the DDFS was 12. The total ROM size was 3840 bits, resulting in a compression ratio of 51:1. The chip was fabricated on a BiCMOS technology of 0.35  $\mu$ m. The paper demonstrates the use of LUT-based DDFS for a multicarrier modulator architecture.

Paper P2 presents a CORDIC-based DDFS design. The resolution of the CORDIC is 18 bits, attaining an SFDR of 90 dBc with an  $f_{clk}$  of 76.8 MHz. The paper demonstrates the use of CORDIC for the realisation of a multimode GSM/EDGE/WCDMA modulator. The implementation was the first published multimode GSM/EDGE/WCDMA modulator with an on-chip D/A converter.

Paper P1 introduces a novel digital power ramping and control unit based on a recursive digital sinusoidal oscillator and an enhanced version with more configurability is presented in paper P2. Conventionally, LUT- or FIR-based units were used.

| Ref.             | Туре        | ROM  | comp. | SFDR | Area            | fclk | resol. | Tech | com-    |

|------------------|-------------|------|-------|------|-----------------|------|--------|------|---------|

|                  | J1 *        | size | ratio | dBc  | mm <sup>2</sup> | MHz  | W,D    | μm   | ments   |

| [Caro 05]        | Polyn.      | _    | _     | 84   | 0.05            | 526  | 15     | 0.25 | IQ      |

|                  | Interp.     |      |       | -    |                 |      | 12     |      |         |

| [Sunderland 84]  | Angular     | 3840 | 51.2  | 65   | 48              | 7.5  | 14     | 3.5  | DAC     |

|                  | decomp.     |      |       |      |                 |      | 12     |      |         |

| [Langlois 03a]   | Linear      | 448  | 402:1 | 84   | 0.28            | 320  | 16     | 0.35 |         |

|                  | interp.     |      |       |      |                 |      | 11     |      |         |

| [Yang 04]        | Amplit.     | 368  | 200:1 | 55   | 1.47            | 800  | 32     | 0.35 | DAC     |

|                  | compr.      |      |       |      |                 |      | 9      |      |         |

| [Caro 04]        | Amplit.     | 0    | 0     | 80   | 0.22            | 98   | 14     | 0.35 | IQ      |

|                  | compr.      |      |       |      |                 |      | 12     |      |         |

| [Strollo 04]     | Linear      | -    | -     | 80   | 0.09            | 600  | 24     | 0.25 | IQ      |

|                  | interp.     |      |       |      |                 |      | 12     |      |         |

| [Curticapean 01] | Angular     | 576  | 455:1 | 96   | 0.23            | 100  | 16     | 0.35 | IQ      |

|                  | decomp.     |      |       |      |                 |      | 16     |      | 2 mults |

| [Tang 02]        | Angular     | 3840 | 51:1  | 83   | 2               | 200  | 14     | 0.35 | IQ      |

|                  | decomp.     |      |       |      |                 |      | 12     |      | mixer   |

| [Nicholas 91]    | Angular     | 3072 | 128:1 | 90   | 24              | 100  | 15     | 1.25 |         |

|                  | decomp.     |      |       |      |                 |      | 12     |      |         |

| [Chimakurthy 06] | Interp.     | 1216 | 404:1 | 90   | -               | 25   | 15     | FPGA |         |

|                  |             |      |       |      |                 |      | 15     |      |         |

| [Song 04]        | CORDIC      | -    | -     | 100  | 0.51            | 330  | 18     | 0.25 | IQ      |

|                  | fine/coarse |      |       |      |                 |      | 15     |      | mixer   |

| [Torosyan 03]    | CORDIC      | 442  | -     | 90   | 0.36            | 300  | 15     | 0.25 | IQ      |

|                  | fine/coarse |      |       |      |                 |      | 13     |      | mixer   |

| [Gielis 91]      | CORDIC      | -    | -     | 60   | 25              | 540  | 12     | 1    | IQ      |

|                  |             |      |       |      |                 |      | 10     |      | mixer   |

| Paper P1         | Angular     | 3840 | 51:1  | 87   |                 | 52   | 14     | 0.35 |         |

|                  | decomp.     |      |       |      |                 |      | 12     |      |         |

| Paper P2         | CORDIC      |      |       | 90   |                 | 76.8 | 18     | 0.35 | IQ      |

|                  |             |      |       |      |                 |      | 18     |      |         |

| Paper P6         | Interp.     | 1600 | 123:1 | 87   | 2.02            | 200  | 14     | 0.13 |         |

|                  |             |      |       |      |                 |      | 12     |      |         |

Table 3.1 Comparison of implemented DDFSs.

This page is intentionally left blank.

## **Chapter 4**

# **Digital/Analogue Conversion in base station transmitters**

As expressed in the chapter that discusses the transmitter and upconversion architectures, the final output signal from the antenna is analogue, whilst, at baseband, digital signal processing is utilised. Thus, conversion from digital to analogue is needed at some point of the transmitter chain. There is a wide range of alternative D/A conversion architectures available for this purpose, and they can be divided into three subcategories: Nyquist rate D/A converters, oversampling D/A converters and undersampling D/A converters.

## 4.1 Performance metrics of D/A converters

The most important performance metrics for D/A converters in wireless communications transmitters can be divided into two classes: static metrics and dynamic metrics. The most important static metrics are differential nonlinearity (DNL) [Razavi 95] and integral nonlinearity (INL) [Razavi 95].

The most important dynamic metrics are signal-to-noise ratio (SNR) [Andersson 05], signal-to-noise-and-distortion ratio (SNDR) [Andersson 05], spurious-free dynamic range (SFDR) [Andersson 05], effective number of bits (ENOB) [Andersson 05] and multi-tone power ratio (MTPR) [Andersson 05].

## 4.2 Nyquist rate D/A converters

A Nyquist rate D/A converter samples the input data with a rate that is slightly higher than twice the bandwidth, as required by the sampling theorem [Shannon 49]. The most important Nyquist rate D/A converter architectures are current-steering, charge-redistribution, R-2R ladder and resistor-string D/A converters. Out of these only current-steering has been found suitable for the transmitter applications.

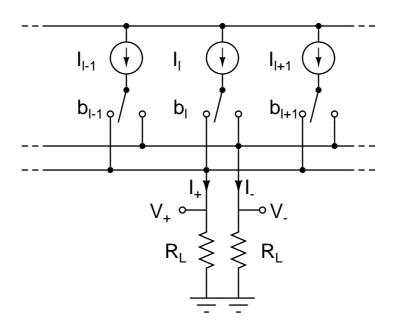

Figure 4.1 Current-steering D/A converter [Andersson 05]

#### 4.2.1 Current-steering D/A converters

A current-steering D/A converter is based on switched current technique. Figure 4.1 depicts the structure of a differential current-steering D/A converter. It is composed of weighted current sources, switches and two load resistors.

The weighted currents are summed in the outputs. Depending on the control bits  $b_l$ , the current  $I_l$  is steered either in the positive or negative load resistor. So the output currents are [Andersson 05]

$$I_+ = \sum_l b_l I_l$$

$I_- = \sum_l \overline{b_l} I_l.$

The currents  $I_l$  may or may not vary, depending on the weighting scheme employed. In general, the weighting of the current sources can be expressed as follows

$$I_l = w_l I_{unit}$$

The most common current steering D/A converter architectures are binary, thermometer (also called unary [van den Bosch 01a]) and segmented. In a binary weighting

$$w_l = 2^l$$

,

whilst in a thermometer-coded architecture, the weights are

$$w_l = 1.$$

Segmented architecture is a hybrid of the above, i.e. some of the current sources are binary weighted, while the others are thermometer-coded.

The binary weighted architecture is more vulnerable to glitches than the thermometercoded architecture, because a small change in the value of the input signal can trigger a state transition in many (or all in the worst case) of the binary weighted bits. For example, a transition from '100000' to '011111' can cause a glitch if the MSB transition is slower than the LSB transitions [Kosunen 06]. In a segmented architecture, the glitches due to the use of a binary weighted LSB end are small, therefore is common that the MSB bits are thermometer coded and the LSB bits are binary weighted [Razavi 95].

#### Static performance limitations

Static non-linearities that deteriorate INL and DNL emanate from two categories of nonidealities: random process variations and gradient process variations.

To enable the prediction of INL variation due to the random variation, the concept of INL yield has been defined as the percentage of the functional D/A converters with an INL specification of less than half an LSB [van den Bosch 01b]. This parameter has the following relationship with the relative unit current source standard variation  $\sigma(I)/I$  and DAC resolution N [van den Bosch 01b, van den Bosch 01a].

$$\frac{\sigma(I)}{I} = \frac{1}{2C\sqrt{2^N}} \text{ with } C = \text{inv\_norm}(0.5 + \frac{\text{yield}}{2})$$

(4.1)

where inv\_norm stands for inverse cumulative normal distribution. Based on (4.1) and the relation between the size and matching of MOS transistors [Pelgrom 89], the dimensions of the current sources can be calculated in the case of MOS current sources [van den Bosch 01c]:

$$WL = \frac{1}{2\left(\frac{\sigma_{I}}{T}\right)^{2}} \left[ A_{\beta}^{2} + \frac{4A_{VT}^{2}}{\left(V_{GS} - V_{T}\right)^{2}} \right]$$

(4.2)

where  $A_{\beta}$  and  $A_{VT}$  are technological parameters and  $(V_{GS} - V_T)$  is the gate overdrive voltage of the current source transistors. This relationship between mismatch and area imposes a minimum constraint on the area of the D/A converter, depending on the resolution.

Gradient variations mainly emanate from the variation of the oxide thickness on the wafer and die stress gradients. There are layout design techniques the purpose of which is to mitigate the effects of gradient process variations that result in static nonlinearity. Two categories of these techniques can be identified as heuristic [Bastos 98, Deveugele 04] and analytic [van der Plas 99, Cong 00] methods that require a priori cognizance of the gradients [Kosunen 06].

Loss of resolution emanating from matching errors such as gradient and random errors can be compensated for using calibration techniques, two main categories of which can

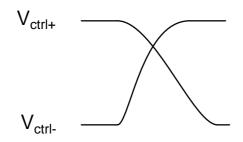

Figure 4.2 Switch control signal intersection point

be identified as [Kosunen 06] continuous [Groeneveld 89] and quantized [Manoli 89, Cong 03, Schofield 03, Tiilikainen 01].

Another way to tackle the problem is to use dynamic element matching (DEM) to convert spurious tones caused by matching errors into white or shaped noise [Andersson 05, O'Sullivan 04].

#### **Dynamic performance limitations**

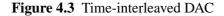

The dynamic performance of a current-steering D/A converter is principally limited by the imperfect synchronization of the control signals of the switches, drain voltage variation of the current-source transistors and feedthrough of the control signals to the output of the switches [van den Bosch 01a].