TKK Dissertations 56 Espoo 2006

#### INTEGRATION OF BROADBAND DIRECT-CONVERSION QUADRATURE MODULATORS

**Doctoral Dissertation**

Esa Tiiliharju

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory TKK Dissertations 56 Espoo 2006

#### INTEGRATION OF BROADBAND DIRECT-CONVERSION QUADRATURE MODULATORS

**Doctoral Dissertation**

#### Esa Tiiliharju

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Electrical and Communications Engineering for public examination and debate in Auditorium S5 at Helsinki University of Technology (Espoo, Finland) on the 8th of December, 2006, at 12 noon.

Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory

Teknillinen korkeakoulu Sähkö- ja tietoliikennetekniikan osasto Piiritekniikan laboratorio Distribution: Helsinki University of Technology Department of Electrical and Communications Engineering Electronic Circuit Design Laboratory P.O. Box 3000 FI - 02015 TKK FINLAND URL: http://www.ecdl.tkk.fi/ Tel. +358-9-4512271 Fax. +358-9-4512269 E-mail: esatii@utu.fi

© 2006 Esa Tiiliharju

ISBN-13 978-951-22-8521-1 ISBN-10 951-22-8521-5 ISBN-13 978-951-22-8522-8 (PDF) ISBN-10 951-22-8522-3 (PDF) ISSN 1795-2239 ISSN 1795-4584 (PDF) URL: http://lib.tkk.fi/Diss/2006/isbn9512285223/

TKK-DISS-2233

Otamedia Oy Espoo 2006

## Abstract

To increase spectral efficiency, transmitters usually send only one of the information carrying sidebands centered around a single radio-frequency carrier. The close-lying mirror, or image, sideband will be eliminated either by the filtering method or by the phasing method. Since filter Q-values rise in direct relation to the transmitted frequencies, the filtering method is generally not feasible for integrated microwave transmitters. A quadrature modulator realizes the phasing method by combining signals phased at quadrature (i.e. at 90° offsets) to produce a single-sideband (SSB) output. In this way output filtering can be removed or its specifications greatly relieved so as to produce an economical microwave transmitter. The proliferation of integrated circuit (IC) technologies since the 1980s has further boosted the popularity of quadrature modulator as an IC realization makes possible the economical production of two closely matched doubly balanced mixers, which suppress carrier and even-order spurious leakage to circuit output. Another strength of IC is its ability to perform microwave quadrature generation accurately on-chip, and thereby to avoid most of the interconnect parasitics which could ruin high-frequency quadrature signaling.

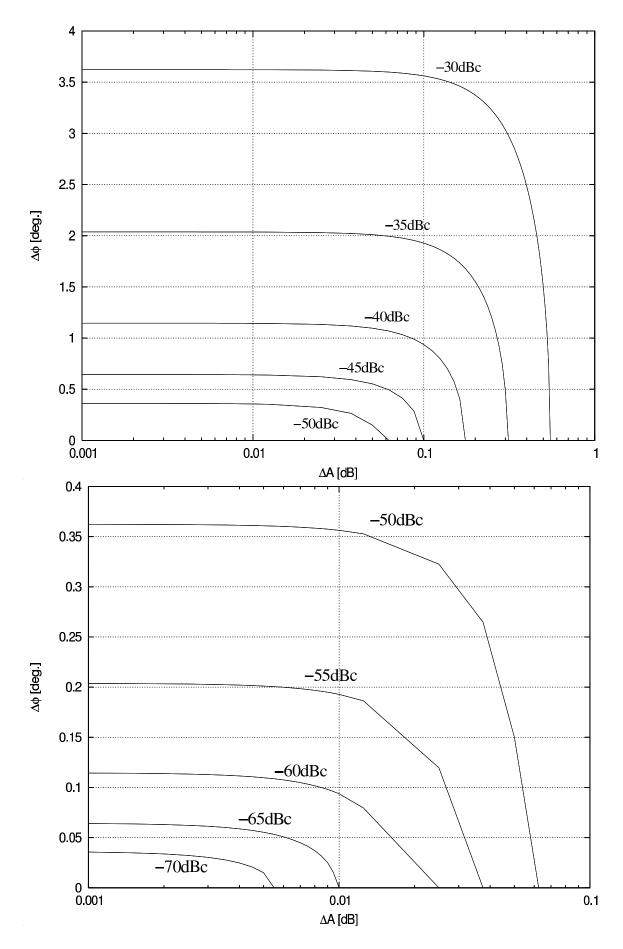

Nevertheless, all quadrature modulator implementations are sensitive to phasing and amplitude errors, which are born as a result of mismatches, from the use of inaccurate differential signaling, and from inadequacies in the phasing circuitry itself. A 2° phase error is easily produced, and it reduces the image-rejection ratio (IRR) to -30 dBc. Therefore, as baseband signals synthesized by digital signal processing (DSP) are sufficiently accurate, this thesis concentrates on analyzing and producing the microwave signal path of a direct-conversion quadrature modulator with special emphasis on broadband, multimode radio-compatible operation.

A model of the direct-conversion quadrature modulator operation has been developed, which reveals the effect the circuit non-linearities and mismatch-related offsets have on available performance. Further, theoretical proof is given of the well-known property of improving differential signal balance that cascaded differential pairs exhibit. Among the practical results, a current reuse mixer has been developed, which improves the transmitted signal-to-noise-ratio (SNR) by 3 dB, with a maximum measured dynamic range of +158 dB. The complementary bipolar process was further used to extend the bipolar push-pull stage bandwidth to 9.5 GHz. At the core of this work is the parallel switchable polyphase (PP) filter quadrature generator that was developed, since it makes possible accurate broadband IQ generation without the high loss that usually results from the application of PP filtering. Two IQ modulator prototypes were realized to test simulated and theoretically derived data: the 0.8  $\mu$ m SiGe IC achieves an IRR better than -40 dBc over 0.75-3.6 GHz, while the 0.13  $\mu$ m digital bulk CMOS IC achieves better than -37 dBc over 0.56-4.76 GHz. For this IRR performance the SiGe prototype boasts the inexpensive solution of integrated baluns, while the CMOS one utilizes a coil-transmission line hybrid transformer at its LO input to drive the switchable PP filters.

**Keywords:** SSB transmitter, direct-conversion quadrature modulator, SiGe, digital CMOS, microwave frequencies.

## Tiivistelmä

Taajuuksien käytön tehostamiseksi lähettimet lähettävät yleensä vain toisen informaatiota sisältävistä sivukaistoistaan yhdelle radiotaajuuksiselle kantoaallolle keskitettynä. Viereinen peilitaajuus eli sivukaista vaimennetaan joko suodattamalla tai vaiheistamalla signalointia sopivasti. Koska suodattimen hyvyysluvut nousevat suorassa suhteessa käytettyyn taajuuteen, ei suodatusmenetelmä ole yleensä mahdollinen mikroaaltotaajuusalueen lähettimissä. Kvadratuurimodulaattori toteuttaa vaiheistusmenetelmän yhdistämällä 90-asteen vaihesiirroksin vaiheistetut signaalit yksisivukaistaisen lähetteen tuottamiseksi. Näin voidaan korvata lähdön suodatus joko kokonaan tai lieventämällä vaadittavia suoritusarvoja, jolloin mikroaaltoalueen lähetin voidaan tuottaa taloudellisesti. Integroitujen piiriratkaisujen yleistyminen 1980-luvulta lähtien on edesauttanut kvadratuurimodulaattorin suosiota, koska integroidulle piirille voidaan taloudellisesti tuottaa kaksi hyvin ominaisuuksiltaan toisiaan vastaavaa kaksoisbalansoitua sekoitinta, ja nämä tunnetusti vaimentavat kantoaaltovuotoa ja parillisia harmoonisia piirin lähdössä. Toinen integroitujen piirien vahvuus on kyky tarkkaan mikroaaltoalueen kvadratuurisignalointiin samalla piirillä, jolloin vältetään suurin osa kytkentöjen parasiittisista jotka muutoin voisivat tuhota korkeataajuuksisen 90-asteen vaiheistuksen.

Kaikki kvadratuurimodulaattorit ovat joka tapauksessa herkkiä vaiheistus- ja amplitudieroille, joita syntyy komponenttiarvojen satunnaishajonnasta, epätarkan differentiaalisen signaloinnin käytöstä, ja itse vaiheistuspiiristön puutteellisuuksista. Kahden asteen vaihevirhe syntyy helposti, ja tällöin sivukaistavaimennus heikkenee -30 dBc:n tasolle. Tämänvuoksi, ja olettaen että digitaalisella signaaliprosessorilla luotu kantataajuuksinen signalointi on riittävän tarkkaa, tämä väitöskirja keskittyy kvadratuurimodulaattorin mikroaaltotaajuuksisen signaalipolun analysointiin ja tuottamiseen painottaen erityisesti laajakaistaista, monisovellusradioiden kanssa yhteensopivaa toimivuutta.

Kvadratuurimodulaattorin toimintamallia on kehitetty siten, että mallissa huomioidaan epälineaarisuuksien ja piirielementtien satunnaishajontojen vaikutus saavutettavalle suorituskyvylle. Lisäksi on teoreettisesti todistettu sinänsä hyvin tunnettu peräkkäin kytkettyjen vahvistinasteiden differentiaalisen signaloinnin symmetrisyyttä parantava vaikutus. Käytännön tuloksista voidaan mainita kehitetty virtaakierrättävä sekoitin, joka parantaa signaali-kohinasuhdetta +3 dB, suurimman mitatun dynaamisen alueen ollessa +158 dB. Samaa komplementaarista bipolaariprosessia käytettiin edelleen bipolaarisen vuorovaihe-asteen kaistan levittämisessä 9.5 GHz:iin. Yhtenä tämän työn tärkeimmistä tuloksista on kehitetty kytkimin valittavista rinnakkaisista monivaihesuodattimista koostuva kvadratuurigeneraattori, jolla on mahdollista tuottaa laajakaistaista IQ-signalointia ilman suurta häviötä joka yleensä liittyy monivaihesuodattimien käyttöön. Kaksi IQ-modulaattoriprototyyppiä toteutettiin simuloitujen ja teoreettisesti mallinnettujen tulosten testaamiseksi: 0.8  $\mu$ m SiGe integroitu piiri saavuttaa paremman sivukaistavaimennuksen kuin -40 dBc yli 0.75-3.6 GHz, kun taas 0.13  $\mu$ m digitaalipiirien tuottamiseen tarkoitetulla CMOS prosessilla toteutettu integroitu piiri saavuttaa paremman sivukaistavaimennuksen kuin -37 dBc taajuusalueella 0.56-4.76 GHz. Näihin sivukaistavaimennuksiin SiGe prototyyppi pääsee edullisesti integroiduin symmetrointimuuntajin, kun taas CMOS piirillä käytetään kela-siirtojohtotyyppistä yhdistelmämuuntajaa LO-sisääntulossa josta ajetaan erikseen kytkettäviä monivaihesuodattimia.

Asiasanat: yksisivukaistainen lähetin, suoramuunnos kvadratuurimodulaattori, SiGe, digitaali-CMOS, mikroaaltotaajuusalue.

## Preface

This work was started as the result of an initiative on the part of MICRO ANALOG SYSTEMS OY as part of the TEKES ORAVAT-program in 1998-2002, continued with support from the Academy of Finland, and finally concluded as part of the TEKES ELMO program in 2004-2006 for Nokia Telecommunications. Texas Instruments is acknowledged for the fabrication of the CMOS and the complementary SiGe prototype ICs, with special thanks to Tuomas Hollman and Jaakko Ketola for fabrication support.

Additional funding from the J&A Wihuri Foundation, the Finnish Society of Electronics Engineers Foundation, the Ulla Tuominen Foundation, the Finnish Cultural Foundation, and Kaute is gratefully acknowledged.

I would like to thank my supervisor, Professor Kari Halonen, for the possibility to work on this thesis independently. I want to thank the pre-examiners, Prof. Håkan Olsson of the Royal Institute of Technology (KTH) and Prof. Robert Weigel of the University of Erlangen, for their contribution to the completion of this thesis. Marko Kosunen, Kari Stadius, and Jouko Vankka well deserve my sincere gratitude for their solid professional advice. ECDL secretary, Helena Yllö, Lauri Koskinen, Mika Laiho, Mika Länsirinne, Kimmo Koli, Ari Paasio, Tero Wahlroos, and all other past and current members of the laboratory staff should be mentioned also.

Finally, I would like to thank my parents for their exceptional support, and I would also like to mention my in-laws for their efforts for us, and all my other friends and relatives for their encouragement.

Above all, this book is dedicated to Kirsi, Taru, Säde, Kati, Pia, and Leo.

Esa Tiiliharju Helsinki, December 2006

# **Symbols and Abbreviations**

### Symbols

| $A_{\rm v}$                                     | voltage gain                                          |  |  |  |  |

|-------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| $\Delta A$                                      | amplitude error of differential signals               |  |  |  |  |

| $\Delta \phi$                                   | phase error of differential signals                   |  |  |  |  |

| $\mathbf{f}_{\mathrm{MAX}}$                     | maximum oscillation frequency                         |  |  |  |  |

| $f_{\mathrm{T}}$                                | unity gain frequency                                  |  |  |  |  |

| $g_{\mathrm{m}}$                                | transconductance                                      |  |  |  |  |

| $I_{\rm DD}$                                    | current dissipated from the voltage supply            |  |  |  |  |

| $3^{\mathrm{RD}}$                               | third-order harmonic product                          |  |  |  |  |

| 3RD-rej                                         | third-order harmonic products rejection               |  |  |  |  |

| $2^{\mathrm{ND}}$                               | second-order harmonic product                         |  |  |  |  |

| IIP <sub>3</sub>                                | input-referred third-order intercept point            |  |  |  |  |

| 2ND-rej                                         | second-order harmonic products rejection              |  |  |  |  |

| $P_{1dB}$ input-referred 1 dB compression point |                                                       |  |  |  |  |

| $N_{\rm BW}$ noise bandwidth                    |                                                       |  |  |  |  |

| $\mathrm{N}_{\mathrm{floor}}$                   | noise floor                                           |  |  |  |  |

| $\mathrm{N}_{+20\mathrm{MHz}}$                  | noise floor at a +20 MHz offset from the wanted tone  |  |  |  |  |

| $\mathrm{N}_{+190\mathrm{MHz}}$                 | noise floor at a +190 MHz offset from the wanted tone |  |  |  |  |

| $OIP_3$                                         | output-referred third-order intercept point           |  |  |  |  |

| $\omega_{\mathrm{BB}}$                          | baseband signal angular frequency                     |  |  |  |  |

| $\omega_{ m LO}$                                | local tone angular frequency                          |  |  |  |  |

| $OP_{1\mathrm{dB}}$                             | output-referred 1 dB compression point                |  |  |  |  |

| lpha,eta                                        | differential pair small-signal coefficients           |  |  |  |  |

| eta                         | transistor forward current gain                                 |

|-----------------------------|-----------------------------------------------------------------|

| $\Delta \mathrm{DR}$        | dynamic range improvement                                       |

| $\epsilon$                  | measure of imbalance for cascaded differential pairs            |

| $\gamma, \delta$            | small-signal model coefficients for cascaded differential pairs |

| E                           | part-of                                                         |

| $\pm 2$ ND                  | up-converted second harmonics products                          |

| $\pm 3$ RD                  | up-converted third harmonics products                           |

| $\Re^+$                     | positive real                                                   |

| σ                           | linearization factor                                            |

| $\theta$                    | phase-error factor                                              |

| $P_{\rm DD}$                | power dissipated from the voltage supply                        |

| $\phi$                      | phase difference of signals                                     |

| $\mathbf{P}_{\mathrm{OUT}}$ | output power                                                    |

| <b>S</b> <sub>11</sub>      | two-port reflection coefficient, a.k.a. input return loss       |

| $S_{22}$                    | two-port reflection coefficient, a.k.a. output return loss      |

| $S_{21}$                    | forward transmission coefficient (gain)                         |

| $V_{\mathrm{DD}}$           | voltage supply                                                  |

| А                           | baseband signal amplitude                                       |

| a <sub>0</sub>              | offset factor                                                   |

| $a_1, b_1$                  | linear baseband gain factors                                    |

| $a_2, b_2$                  | second-order baseband distortion factors                        |

| $a_3, b_3$                  | third-order baseband distortion factors                         |

| $A_{\rm c}, A_{\rm s}$      | linear LO tone gain factors                                     |

| $A_{\rm i}, A_{\rm q}$      | linear baseband gain factors                                    |

| adBx                        | local common-mode gain factor                                   |

| adBx1                       | local gain factor for the linear term                           |

| adBx3                       | local gain factor for the third-order term                      |

| В                           | local signal amplitude                                          |

| $c_1, d_1$                  | linear LO tone gain factors                                     |

| $c_2, d_2$                  | second-order LO tone distortion factors                         |

| $c_3, d_3$                            | third-order LO tone distortion factors             |  |  |  |  |  |

|---------------------------------------|----------------------------------------------------|--|--|--|--|--|

| СМ                                    | M baseband common-mode gain factor                 |  |  |  |  |  |

| go                                    | bipolar small-signal model channel conductance     |  |  |  |  |  |

| i(t)                                  | time-dependent in-phase signal                     |  |  |  |  |  |

| $\mathrm{K}_{\mathrm{BB}}$            | baseband gain to mixer load                        |  |  |  |  |  |

| loi(t)                                | time-dependent in-phase local tone                 |  |  |  |  |  |

| loq(t)                                | time-dependent quadrature-phased local tone        |  |  |  |  |  |

| Nx noise sources as x=i, q, xi, or xq |                                                    |  |  |  |  |  |

| Oc                                    | offset of the in-phase local input                 |  |  |  |  |  |

| Oi                                    | offset of the in-phase baseband input              |  |  |  |  |  |

| Oq                                    | offset of the quadrature-phase baseband input      |  |  |  |  |  |

| Os                                    | offset of the quadrature-phase local input         |  |  |  |  |  |

| q(t)                                  | time-dependent quadrature-phased signal            |  |  |  |  |  |

| $r_{\pi}$                             | bipolar small-signal model base-emitter resistance |  |  |  |  |  |

| r <sub>o</sub>                        | bipolar small-signal model channel resistance      |  |  |  |  |  |

| s(t)                                  | time-dependent quadrature modulator output signal  |  |  |  |  |  |

|                                       |                                                    |  |  |  |  |  |

### Abbreviations

| 16-QAM | QAM with 16 constellation points                           |  |  |  |

|--------|------------------------------------------------------------|--|--|--|

| 2.5G   | second-and-a-half-generation wireless telephone technology |  |  |  |

| 2G     | second-generation wireless telephone technology            |  |  |  |

| 3G     | third-generation wireless telephone technology             |  |  |  |

| 64-QAM | QAM with 64 constellation points                           |  |  |  |

| DEV    | relative element value tolerances                          |  |  |  |

| LOT    | absolute element value tolerances                          |  |  |  |

| ACPR   | adjacent channel power ratio                               |  |  |  |

| BB     | baseband                                                   |  |  |  |

| BER    | Bit-error rate                                             |  |  |  |

| BiCMOS | bipolar process with CMOS components                       |  |  |  |

| CDMA                                   | code division multiple access                        |  |  |  |  |

|----------------------------------------|------------------------------------------------------|--|--|--|--|

| CGCS                                   | common-gate common-source transistor connection      |  |  |  |  |

| CMOS                                   | complementary metal oxide semiconductor              |  |  |  |  |

| CMRR                                   | common-mode rejection ratio                          |  |  |  |  |

| DA digital-to-analog                   |                                                      |  |  |  |  |

| DC                                     | direct current                                       |  |  |  |  |

| DR                                     | dynamic range                                        |  |  |  |  |

| DSP                                    | digital signal processing                            |  |  |  |  |

| EDGE                                   | enhanced data-rate for gsm evolution                 |  |  |  |  |

| EER                                    | envelope elimination and restoration                 |  |  |  |  |

| EVM                                    | error-vector-magnitude                               |  |  |  |  |

| FET                                    | field-effect transistor                              |  |  |  |  |

| GMSK gaussian minimum shift keying     |                                                      |  |  |  |  |

| GPRS general Packet Radio Service      |                                                      |  |  |  |  |

| GSM                                    | obal system for mobile communications                |  |  |  |  |

| gsm                                    | global System for Mobile communications              |  |  |  |  |

| Ι                                      | in-phase                                             |  |  |  |  |

| IC                                     | integrated circuit                                   |  |  |  |  |

| $\text{ideal}_{\mathrm{x},\mathrm{y}}$ | ideal output rotating phasor x- and y components     |  |  |  |  |

| IF                                     | intermediate frequency                               |  |  |  |  |

| IQ                                     | in- and quadrature phased                            |  |  |  |  |

| IRR                                    | image-rejection ratio                                |  |  |  |  |

| LCR                                    | inductor-capacitor-resistor resonant circuit         |  |  |  |  |

| LO                                     | Local tone, i.e. synthesized microwave carrier       |  |  |  |  |

| LSB                                    | lower sideband                                       |  |  |  |  |

| MB-OFDM                                | multiband OFDM                                       |  |  |  |  |

| MIM                                    | metal-insulator-metal semiconductor structure        |  |  |  |  |

| MOS(FET)                               | metal-oxide-semiconductor (field-effect)) transistor |  |  |  |  |

| NMOS                                   | n-channel MOSFET                                     |  |  |  |  |

| NPN                                    | bipolar transistor with P-doped base                 |  |  |  |  |

| OFDM                          | orthogonal frequency-division multiplexing             |  |  |  |  |  |

|-------------------------------|--------------------------------------------------------|--|--|--|--|--|

| OPLL                          | offset phase-locked loop                               |  |  |  |  |  |

| PA                            | power amplifier                                        |  |  |  |  |  |

| PAR                           | peak-to-average ratio                                  |  |  |  |  |  |

| PLL                           | phase-locked loop                                      |  |  |  |  |  |

| PMOS                          | p-channel MOSFET                                       |  |  |  |  |  |

| PNP                           | bipolar transistor with N-doped base                   |  |  |  |  |  |

| PP                            | polyphase                                              |  |  |  |  |  |

| Q                             | filter quality factor                                  |  |  |  |  |  |

| Q                             | quadrature-phased                                      |  |  |  |  |  |

| QAM                           | quadrature amplitude modulation                        |  |  |  |  |  |

| QPSK                          | quadrature phase-shift keying                          |  |  |  |  |  |

| QVCO                          | voltage-controlled oscillator with quadrature outputs  |  |  |  |  |  |

| RC resistor-capacitor circuit |                                                        |  |  |  |  |  |

| $real_{\rm x,y}$              | realized output rotating phasor x- and y components    |  |  |  |  |  |

| RF                            | radio frequency                                        |  |  |  |  |  |

| RFIC                          | radio frequency integrated circuit                     |  |  |  |  |  |

| SAW                           | surface Acoustic Wave                                  |  |  |  |  |  |

| SDR                           | software-defined radio                                 |  |  |  |  |  |

| SFG                           | signal-flow-graph                                      |  |  |  |  |  |

| SiGe                          | silicon bipolars with germanium-doped transistor bases |  |  |  |  |  |

| SMA                           | Sub-Miniature A Connector                              |  |  |  |  |  |

| SNR                           | signal-to-noise ratio                                  |  |  |  |  |  |

| SSB                           | single-sideband                                        |  |  |  |  |  |

| TDR                           | transmitted dynamic range                              |  |  |  |  |  |

| UMTS                          | universal Mobile Telecommunications System             |  |  |  |  |  |

| USB                           | apper sideband                                         |  |  |  |  |  |

| UWB                           | ultra-wideband                                         |  |  |  |  |  |

| VCO                           | voltage-controlled oscillator                          |  |  |  |  |  |

| VNA                           | vector network analyzer                                |  |  |  |  |  |

| W-CDMA                        | wideband CDMA                                          |  |  |  |  |  |

| WLAN                          | wireless local-area network                            |  |  |  |  |  |

## Contents

| 1.1.1Two-step transmitter11.1.2Polar loop transmitters31.1.3Direct-conversion quadrature modulator31.2Research contribution51.3Organization of the thesis62Quadrature modulator theory72.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.1The first-order error model102.2.2Operation in the presence of distortion142.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of OP <sub>1dB</sub> 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303ILO buffer specifications333.1LO buffer specifications333.2Differential pair phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.5.1Implementation of the cascade433.5.2Process variations43                                        | 1 | Intro | oduction 1                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|--------------------------------------------------------|

| 1.1.2Polar loop transmitters31.1.3Direct-conversion quadrature modulator31.2Research contribution51.3Organization of the thesis62Quadrature modulator theory72.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.1The first-order error model102.2.2Operation in the presence of distortion142.3.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303.1LO buffer specifications333.2Differential pair phase-splitting333.3Differential pair phase-splitting363.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5.1Implementation of the cascade433.5.2Process variations43                                                     |   | 1.1   | Linear transmitters                                    |

| 1.1.3Direct-conversion quadrature modulator31.2Research contribution51.3Organization of the thesis51.3Organization of the thesis62Quadrature modulator theory72.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.1The first-order error model102.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of OP <sub>1dB</sub> 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303I.O buffer specifications333.1LO buffer specifications333.3Differential pair phase-splitting353.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.2Process variations43                             |   |       | 1.1.1 Two-step transmitter                             |

| 1.2Research contribution51.3Organization of the thesis51.3Organization of the thesis62Quadrature modulator theory72.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.2.1The first-order error model102.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of OP <sub>1dB</sub> 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.2Process variations43                                                                                    |   |       | 1.1.2 Polar loop transmitters                          |

| 1.3Organization of the thesis62Quadrature modulator theory72.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.1The first-order error model102.2.2Operation in the presence of distortion142.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                     |   |       | 1.1.3 Direct-conversion quadrature modulator           |

| 2Quadrature modulator theory72.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.2.1The first-order error model102.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory3031LO buffer specifications333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                          |   | 1.2   | Research contribution                                  |

| 2.1The ideal quadrature modulator82.2The non-ideal quadrature modulator82.2.1The first-order error model102.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting363.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                        |   | 1.3   | Organization of the thesis                             |

| 2.2The non-ideal quadrature modulator82.2.1The first-order error model102.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.2Process variations43                                                                                                                                                                                                                                        | 2 | Qua   | drature modulator theory 7                             |

| 2.2.1The first-order error model102.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.2Process variations43                                                                                                                                                                                                                                                                              |   | 2.1   | The ideal quadrature modulator    8                    |

| 2.2.2Operation in the presence of distortion142.2.3The simplified distortion model172.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory3031LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized $0.8  \mu$ m SiGe balun413.5.2Process variations43                                                                                                                                                                                                                                                         |   | 2.2   | The non-ideal quadrature modulator                     |

| 2.2.3 The simplified distortion model172.3 Quadrature modulator characteristics232.3.1 SSB performance232.3.2 Calculation of $OP_{1dB}$ 242.3.3 Operation in the presence of noise262.3.4 Transmitted dynamic range272.4 ACPR and EVM282.5 Evaluation of theory303 LO buffering333.1 LO buffer specifications333.2 Differential pair phase-splitting333.3 Cascaded phase-splitting363.4.1 Single-transistor phase-splitters383.4.2 Modified CGCS topology383.4.4 Monolithic transformers413.5 The realized 0.8 $\mu$ m SiGe balun413.5.1 Implementation of the cascade433.5.2 Process variations43                                                                                                                                                                                                                                                                                                        |   |       | 2.2.1 The first-order error model                      |

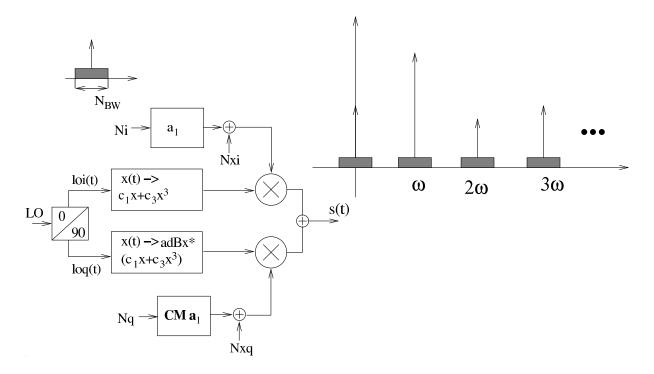

| 2.3Quadrature modulator characteristics232.3.1SSB performance232.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting333.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                          |   |       | 2.2.2 Operation in the presence of distortion          |

| 2.3.1       SSB performance       23         2.3.2       Calculation of $OP_{1dB}$ 24         2.3.3       Operation in the presence of noise       26         2.3.4       Transmitted dynamic range       27         2.4       ACPR and EVM       28         2.5       Evaluation of theory       30         3       LO buffering       33         3.1       LO buffer specifications       33         3.2       Differential pair phase-splitting       35         3.3       Cascaded phase-splitting       36         3.4       Integrated baluns       38         3.4.1       Single-transistor phase-splitters       38         3.4.2       Modified CGCS topology       38         3.4.3       Differential pair baluns       38         3.4.4       Monolithic transformers       41         3.5       The realized 0.8 $\mu$ m SiGe balun       41         3.5.2       Process variations       43 |   |       | 2.2.3 The simplified distortion model                  |

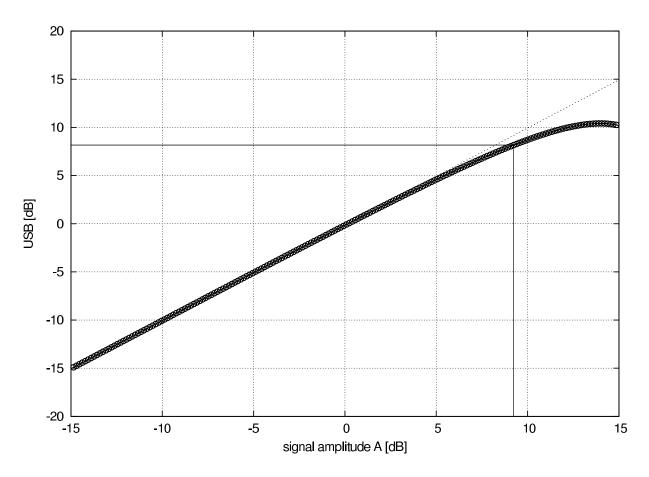

| 2.3.2Calculation of $OP_{1dB}$ 242.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                         |   | 2.3   | Quadrature modulator characteristics                   |

| 2.3.3Operation in the presence of noise262.3.4Transmitted dynamic range272.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |       | 2.3.1 SSB performance                                  |

| 2.3.3 Operation in the presence of noise262.3.4 Transmitted dynamic range272.4 ACPR and EVM282.5 Evaluation of theory30 <b>3 LO buffering</b> 333.1 LO buffer specifications333.2 Differential pair phase-splitting353.3 Cascaded phase-splitting363.4 Integrated baluns383.4.1 Single-transistor phase-splitters383.4.2 Modified CGCS topology383.4.3 Differential pair baluns383.4.4 Monolithic transformers383.4.5 The realized 0.8 $\mu$ m SiGe balun413.5.1 Implementation of the cascade433.5.2 Process variations43                                                                                                                                                                                                                                                                                                                                                                                |   |       | 2.3.2 Calculation of $OP_{1dB}$                        |

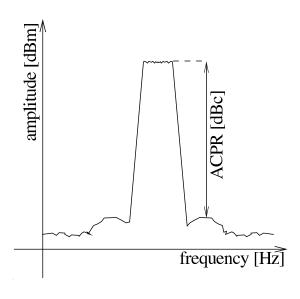

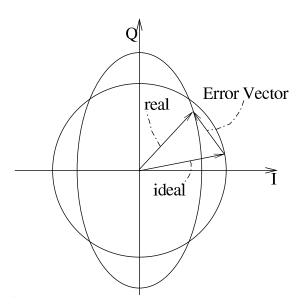

| 2.4ACPR and EVM282.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers383.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |       |                                                        |

| 2.5Evaluation of theory303LO buffering333.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |       | 2.3.4 Transmitted dynamic range                        |

| 3LO buffering33 $3.1$ LO buffer specifications33 $3.2$ Differential pair phase-splitting35 $3.3$ Cascaded phase-splitting36 $3.4$ Integrated baluns38 $3.4.1$ Single-transistor phase-splitters38 $3.4.2$ Modified CGCS topology38 $3.4.3$ Differential pair baluns38 $3.4.4$ Monolithic transformers38 $3.4.1$ Single baluns38 $3.4.2$ Modified CGCS topology38 $3.4.3$ Differential pair baluns41 $3.5$ The realized $0.8 \ \mu m$ SiGe balun41 $3.5.1$ Implementation of the cascade43 $3.5.2$ Process variations43                                                                                                                                                                                                                                                                                                                                                                                    |   | 2.4   | ACPR and EVM                                           |

| 3.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers383.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 2.5   | Evaluation of theory    30                             |

| 3.1LO buffer specifications333.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers383.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 3 | LOI   | buffering 33                                           |

| 3.2Differential pair phase-splitting353.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized $0.8 \ \mu m$ SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |       |                                                        |

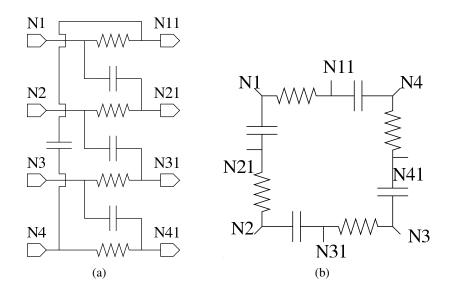

| 3.3Cascaded phase-splitting363.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 3.2   | -                                                      |

| 3.4Integrated baluns383.4.1Single-transistor phase-splitters383.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 3.3   |                                                        |

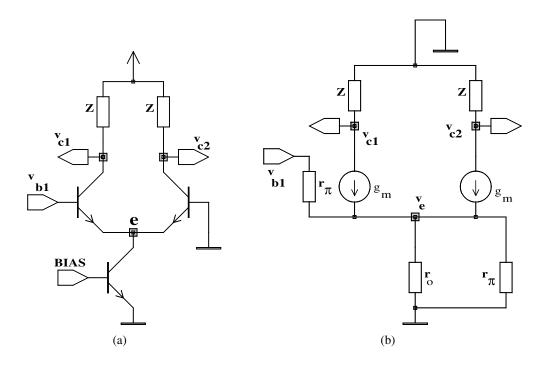

| 3.4.1       Single-transistor phase-splitters       38         3.4.2       Modified CGCS topology       38         3.4.3       Differential pair baluns       38         3.4.4       Monolithic transformers       41         3.5       The realized 0.8 µm SiGe balun       41         3.5.1       Implementation of the cascade       43         3.5.2       Process variations       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   | 3.4   |                                                        |

| 3.4.2Modified CGCS topology383.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized $0.8 \ \mu m$ SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |       | -                                                      |

| 3.4.3Differential pair baluns383.4.4Monolithic transformers413.5The realized 0.8 $\mu$ m SiGe balun413.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |       | • • •                                                  |

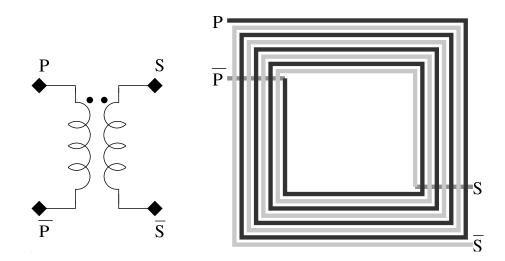

| 3.4.4 Monolithic transformers413.5 The realized 0.8 $\mu$ m SiGe balun413.5.1 Implementation of the cascade433.5.2 Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |       |                                                        |

| 3.5       The realized 0.8 μm SiGe balun       41         3.5.1       Implementation of the cascade       43         3.5.2       Process variations       43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |       |                                                        |

| 3.5.1Implementation of the cascade433.5.2Process variations43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 3.5   |                                                        |

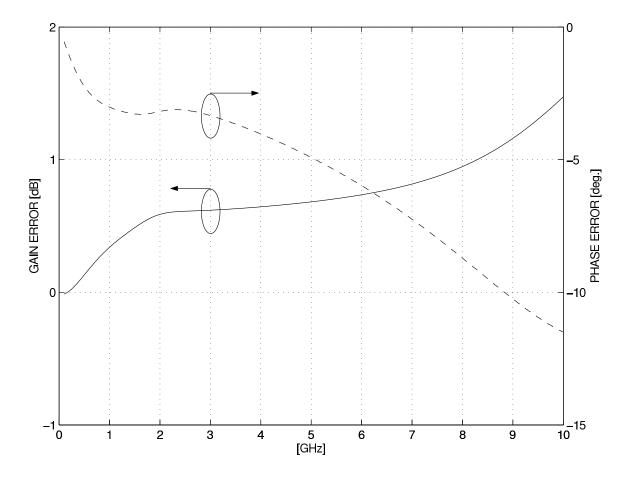

| 3.5.2 Process variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |       |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       | 1                                                      |

| 3.5.3 Matching to 50 W with integrated passives                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       | 3.5.3 Matching to 50 $\Omega$ with integrated passives |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |       |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 3.6   |                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | -     | •                                                      |

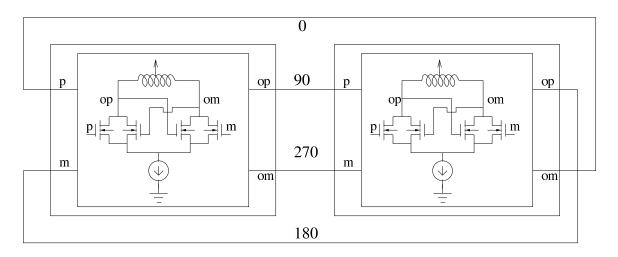

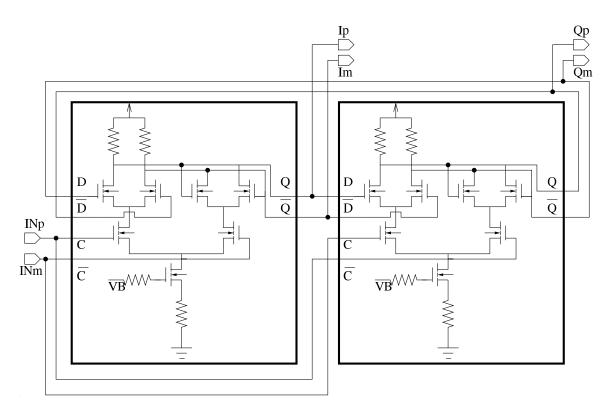

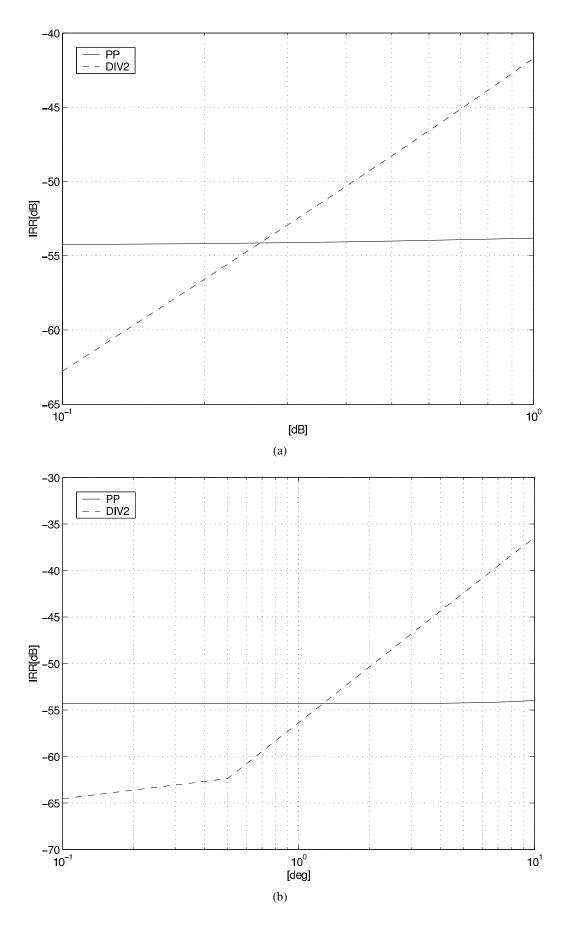

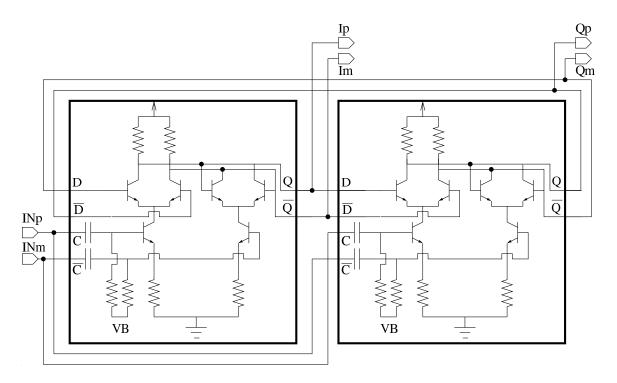

|   |      | 3.6.2 Application to a broadband quadrature modulator | 2 |

|---|------|-------------------------------------------------------|---|

|   | 3.7  | Summary                                               | 3 |

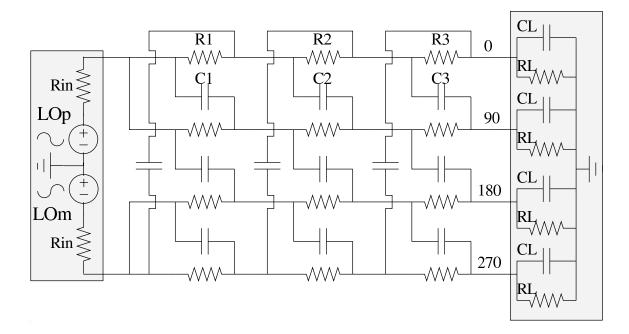

| 4 | Broa | adband quadrature generation 5                        | 4 |

|   | 4.1  | Quadrature generator specifications                   |   |

|   | 4.2  | Integrated quadrature generators                      |   |

|   |      | 4.2.1 RC-CR quadrature generation networks            |   |

|   |      | 4.2.2       Allpass RC networks       5               |   |

|   |      | 4.2.3 Feedback RC networks                            |   |

|   |      | 4.2.4 Polyphase quadrature generation                 |   |

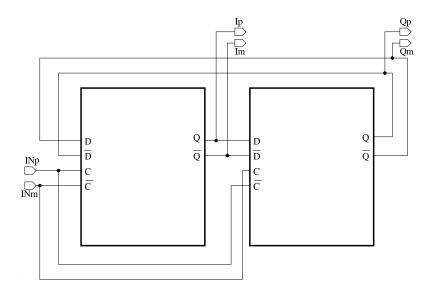

|   |      | 4.2.5 The div-by-2 quadrature generator               |   |

|   |      | 4.2.6       Quadrature VCOs       6                   |   |

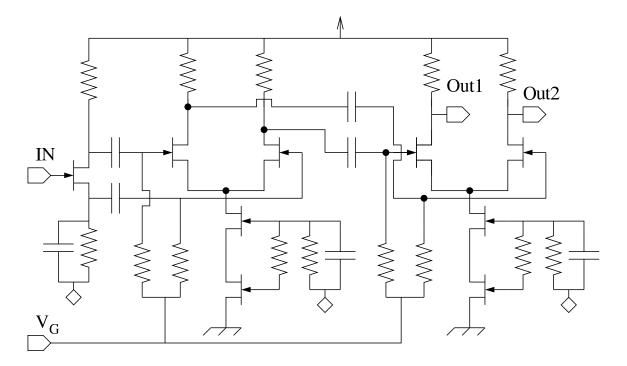

|   | 4.3  | The tested 0.13 $\mu$ m CMOS divider                  |   |

|   | 4.4  | The tested 0.19 $\mu$ m complementary SiGe dividers   |   |

|   | 4.5  | The realized 0.8 $\mu$ m SiGe polyphase network       |   |

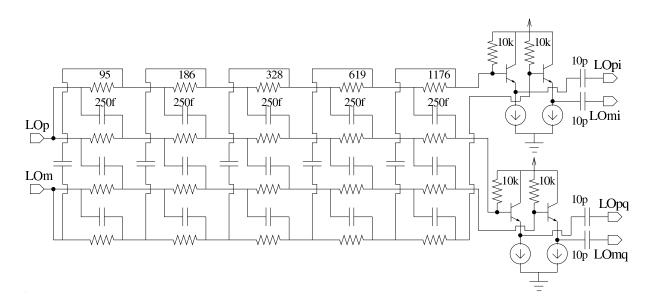

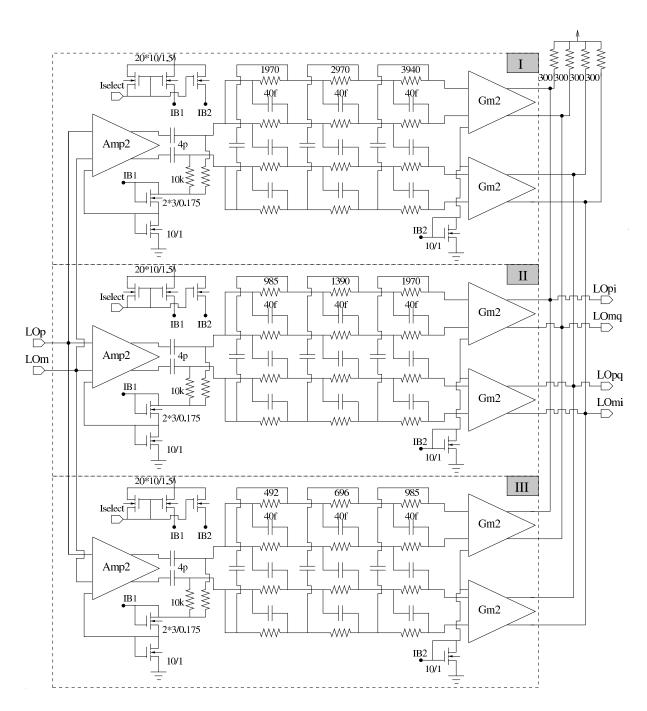

|   | 4.6  | The realized 0.13 $\mu$ m CMOS switchable PP          |   |

|   | 4.7  | Summary                                               |   |

|   | 4.7  | Summary                                               | / |

| 5 | -    | conversion mixers 6                                   | - |

|   | 5.1  | Mixer specifications                                  |   |

|   |      | 5.1.1 Gilbert mixer operation                         |   |

|   |      | 5.1.2 Linearity and noise                             | 0 |

|   |      | 5.1.3 Low supply voltage limitations                  | 1 |

|   | 5.2  | Integrated up-conversion mixers                       | 3 |

|   |      | 5.2.1 Gilbert mixers                                  | 3 |

|   |      | 5.2.2 Resistive mixers                                | 3 |

|   |      | 5.2.3 Digital-to-RF mixer                             | 4 |

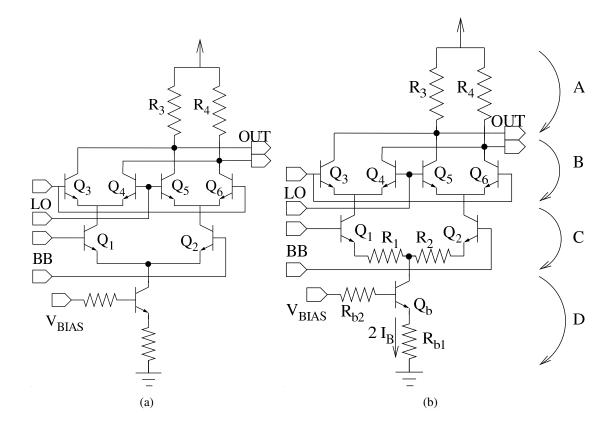

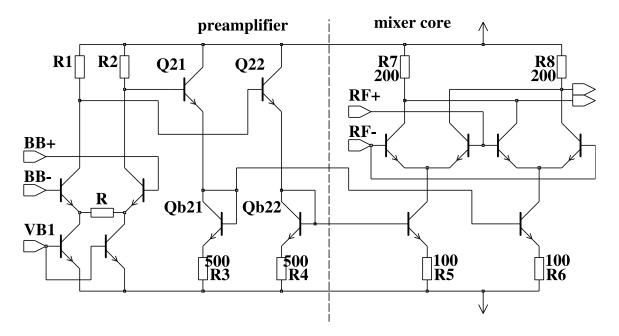

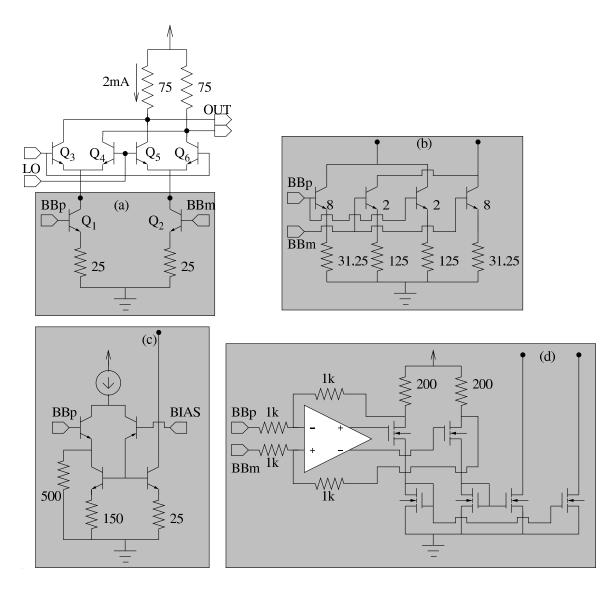

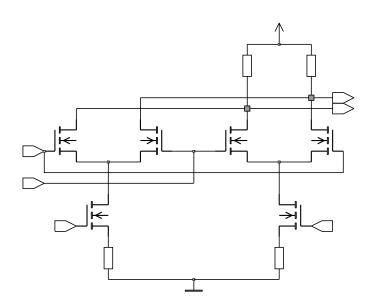

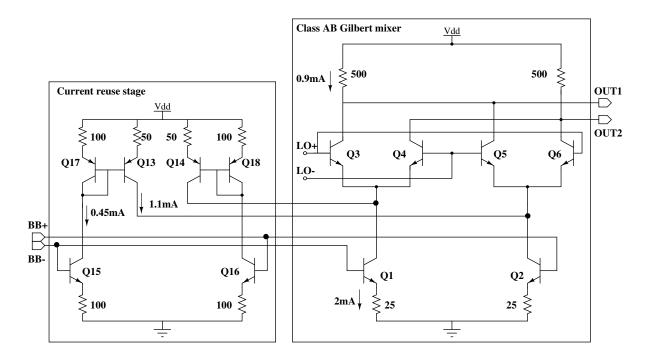

|   | 5.3  | The realized 0.8 $\mu$ m BiCMOS mixer                 | 6 |

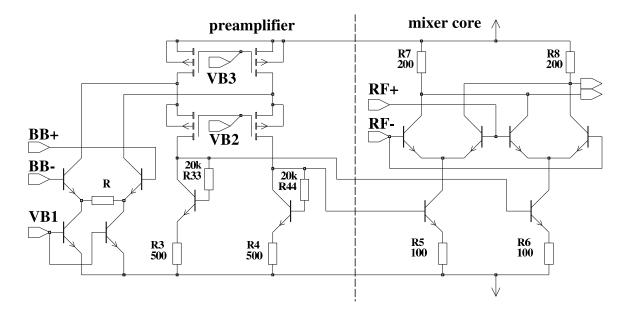

|   | 5.4  | The realized 0.8 $\mu$ m SiGe mixer                   | 7 |

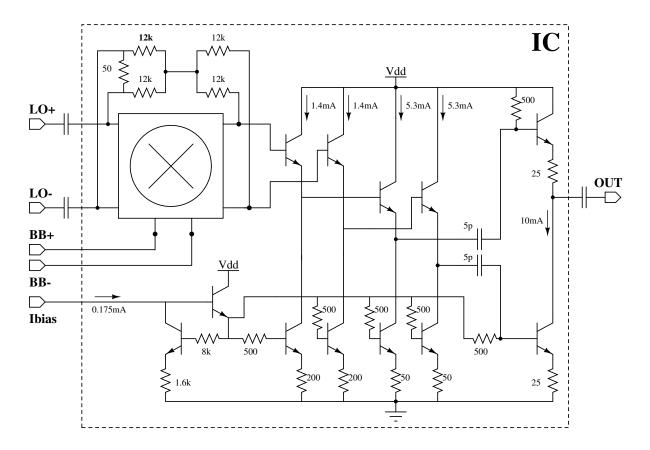

|   | 5.5  | The realized 0.13 $\mu$ m CMOS mixer                  | 0 |

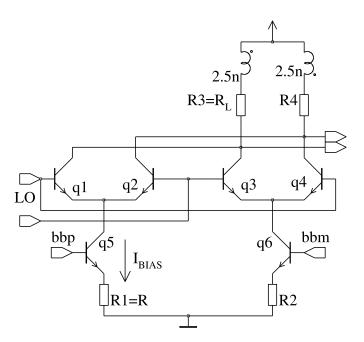

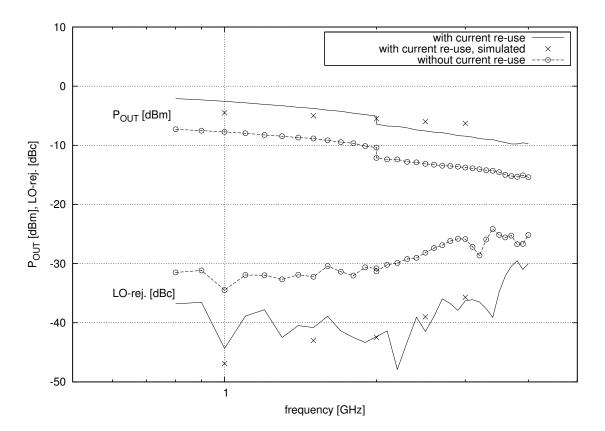

|   | 5.6  | The realized 0.4 $\mu$ m complementary SiGe mixer     | 3 |

|   |      | 5.6.1 Comparison to a class AB Gilbert cell           | 6 |

|   | 5.7  | Summary                                               | 6 |

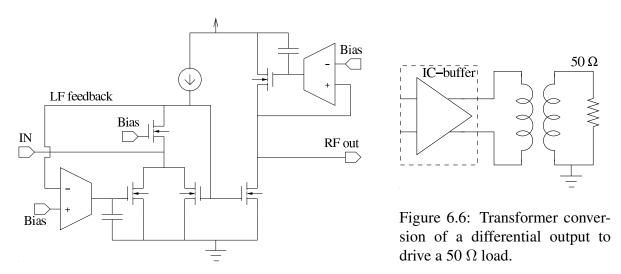

| 6 | Out  | out buffering 8                                       | 7 |

| U | 6.1  | Buffer specifications                                 |   |

|   | 0.1  | -                                                     |   |

|   |      | 5                                                     |   |

|   | 60   |                                                       |   |

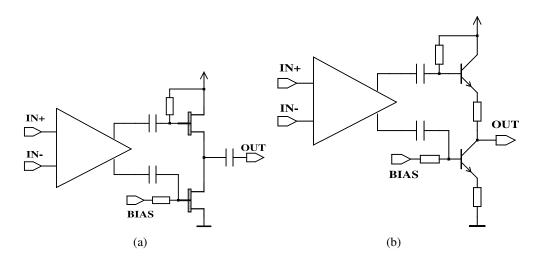

|   | 6.2  | Integrated buffers                                    |   |

|   |      | 6.2.1 Balun buffers                                   |   |

|   |      | 6.2.2 Single-ended buffers                            |   |

|   |      | 6.2.3 Differential buffers                            |   |

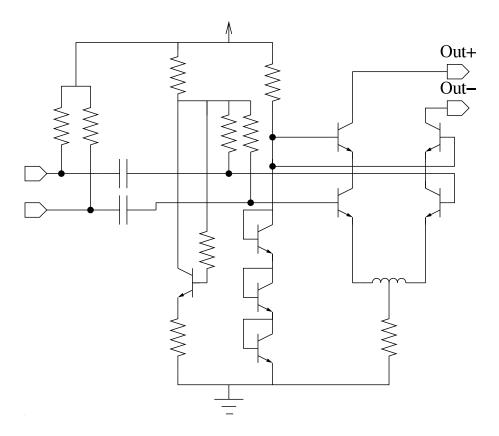

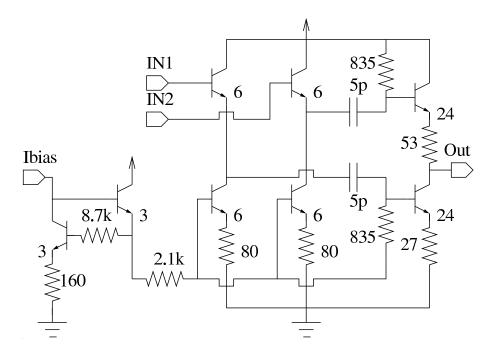

|   | 6.3  | The realized 0.8 $\mu$ m SiGe buffer                  |   |

|   | 6.4  | The realized 0.13 $\mu$ m CMOS buffer                 |   |

|   | 6.5  | The realized 0.4 $\mu$ m complementary SiGe buffer    |   |

|   | 6.6  | Summary                                               | 6 |

| 7  | Broa                                                    | dband quadrature modulators                               | 97  |  |  |

|----|---------------------------------------------------------|-----------------------------------------------------------|-----|--|--|

|    | 7.1                                                     | Integrated direct-conversion quadrature modulators        | 97  |  |  |

|    |                                                         | 7.1.1 Modulators with tunable RC-CR quadrature generation | 97  |  |  |

|    |                                                         | 7.1.2 Modulators with PP quadrature generation            | 98  |  |  |

|    |                                                         | 7.1.3 Modulators with div-by-2 quadrature generation      | 99  |  |  |

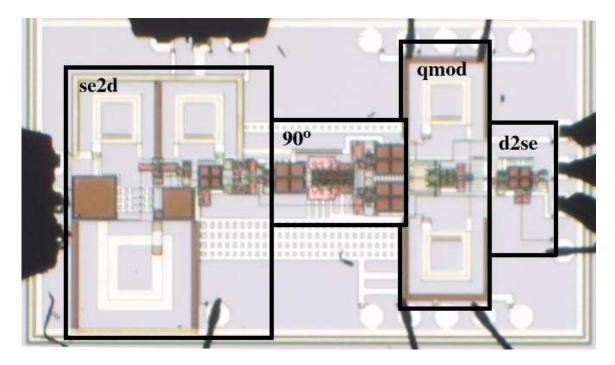

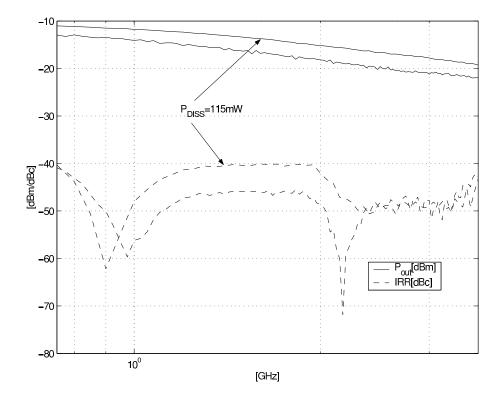

|    | 7.2                                                     | The realized 0.8 $\mu$ m SiGe quadrature modulator        | 99  |  |  |

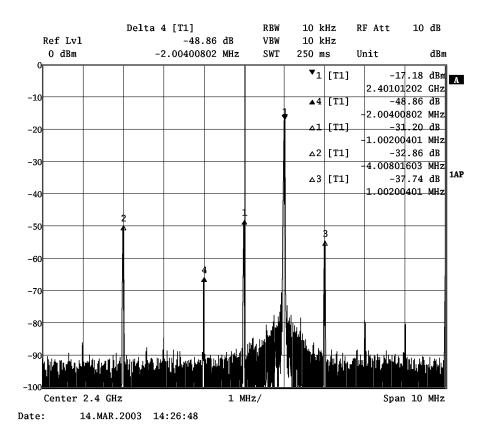

|    |                                                         | 7.2.1 Measurement setup                                   | 100 |  |  |

|    |                                                         | 7.2.2 Experimental Results                                | 100 |  |  |

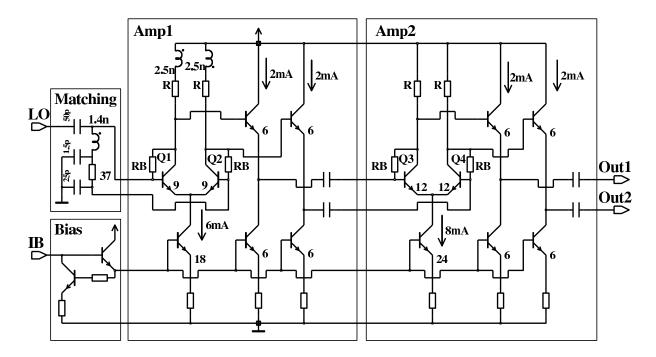

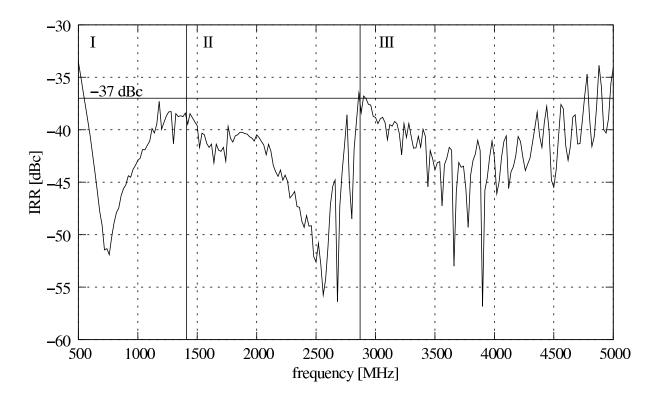

|    | 7.3 The realized 0.13 $\mu$ m CMOS quadrature modulator |                                                           |     |  |  |

|    |                                                         | 7.3.1 Measurement setup                                   | 103 |  |  |

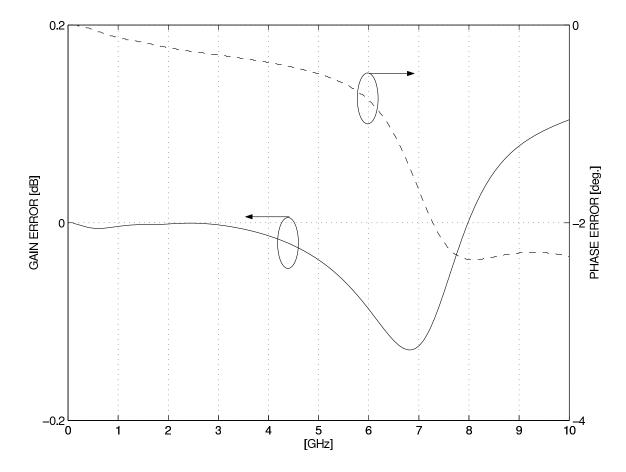

|    |                                                         | 7.3.2 Experimental Results                                | 105 |  |  |

|    | 7.4                                                     | Benchmark                                                 | 107 |  |  |

| 8  | Con                                                     | clusions                                                  | 111 |  |  |

| Re | References 112                                          |                                                           |     |  |  |

### 1. Introduction

A wireless radio transmitter applies a coded and modulated signal on a radio frequency carrier wave for subsequent transmission and reception. Ideally, transmission does not add noise and/or distort the transmitted signal, but this is hardly ever the case. Distortion spreads the transmitted signaling to interfere with other users, and transmitted noise might desensitize the user's own receiver block. Therefore, the use of radio frequencies is tightly controlled, i.e. regulated, by government agencies such as ETSI in Europe and FCC in the USA.

Different modulation schemes are used, according to desired power and spectral efficiencies [1]: 2G cellular services use power-efficient phase modulation schemes such as GMSK, used to build gsm-services. This makes possible perfect audio transmission, but offers very limited data capabilities in the range of 60 kbit/s. As the emerging 2.5 and 3G services (EDGE, UMTS) target much higher data transmission rates at a minimum of several hundred kilobits per second, this reflects on the chosen modulations as well. Accordingly, the predominant spectrally efficient modulation formats (QPSK, 16-QAM, 64-QAM, OFDM) manipulate both the amplitude and phase of the transmitted signal so as to pack several bits into each transmitted symbol. In fact, the hugely successful wireless local area networks (WLANs) have recently introduced OFDM in a 55 Mbit/s system operating in the 2.4 GHz frequency band (802.11g).

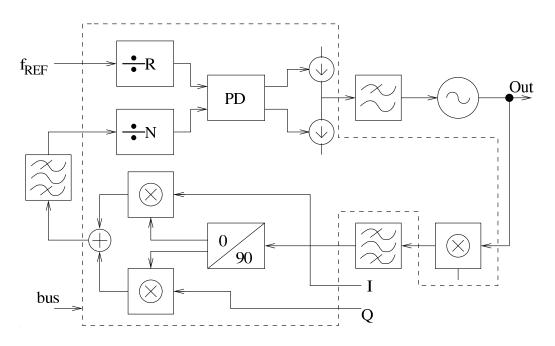

The penalty for the increased data rates is that the simultaneous manipulation of amplitude and phase results in variable envelope signaling; for OFDM peak-to-average-ratios (PAR) in the range 8-13 dB are commonplace. To maintain reasonable power amplifier (PA) efficiencies, transmitter linearity and spectral purity now have increased significance: a spectrally pure transmitter makes possible the application of a non-linear efficient PA. Transmitters can thus be classified into non-linear (constant envelope) and linear (variable envelope) transmitters [2, 3]. One of the most successful non-linear transmitters is the offset phase-locked loop (OPLL), which utilizes the PLL filtering action to fulfill tight GSM noise specifications [4]. This dominant 2G transmitter is shown in Fig. 1.1.

#### **1.1** Linear transmitters

To assess different linear transmitter types, the software-defined radio (SDR), or at least the multistandard radio requirements of broadband, linear, and low-noise radio transmissions, have to be considered in a world of radio standards rapidly evolving towards higher bitrate operation.

#### **1.1.1** Two-step transmitter

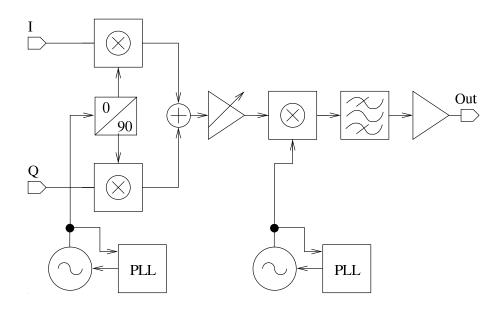

The two-step, or super-heterodyne, transmitter can also be described as the filtering method of frequency translation; one or more intermediate frequencies (IFs) are used in order to relax the specifications of individual circuit blocks. In particular, this approach yields high-quality receivers which are immune to the PA pulling of the frequency synthesizers and exhibit low-noise signal transmission. The complexity of the resulting hardware is high and the use of off-chip SAW-filters is costly and should be avoided, especially since lead-free soldering will

Figure 1.1: The OPLL up-conversion loop for GSM transmitters [4].

Figure 1.2: The two-step or super-heterodyne transmitter.

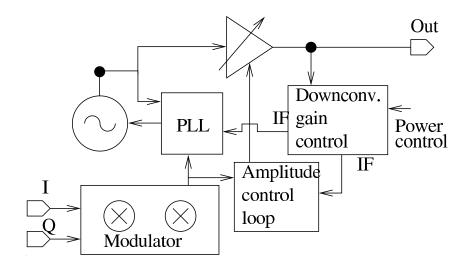

Figure 1.3: The polar loop transmitter with closed-loop PA-control [6].

become globally mandatory in the near future. The complexity of the hardware is evident from the block diagram of a typical two-step transmitter in Fig. 1.2. In fact, filters with no (or limited) tuning range and complex frequency planning involved severely restrict the application of this topology in multi-mode radios.

#### **1.1.2** Polar loop transmitters

Recently, envelope elimination and restoration (EER), or the Kahn method of transmission [5], have been used to realize multimode GSM/EDGE transmitters [6, 7]. The one in [6] is also GPRS-compatible with the PA inside its amplitude and phase control feedback loops; the use of the topology in Fig. 1.3 results in a measured PA efficiency of 35% while fulfilling EDGE-specifications with +27 dBm at the antenna. The polar loop approach, however, results in complex hardware with the need for custom PA to accommodate amplitude control. Amplitude and phase control loop bandwidths need to be carefully matched so as to prevent spectral re-growth and instability. Since both realizations [6,7] include phase-locked loops, their usability for wider signal bandwidth system (e.g. W-CDMA) up-conversion is questionable.

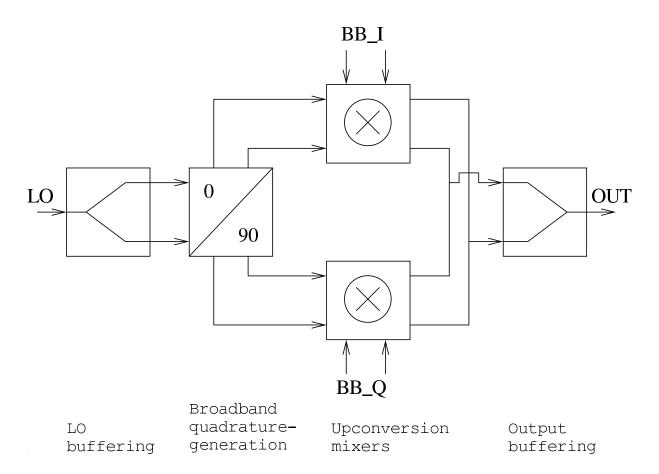

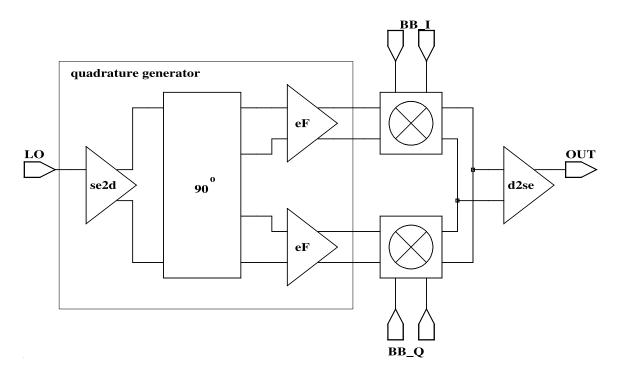

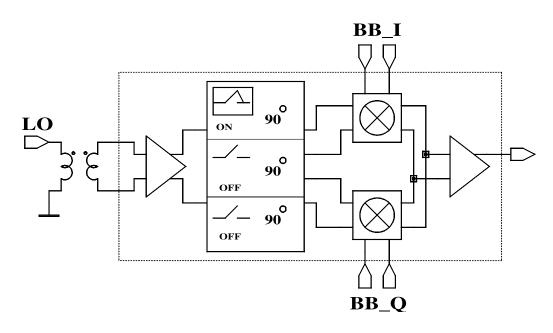

#### 1.1.3 Direct-conversion quadrature modulator

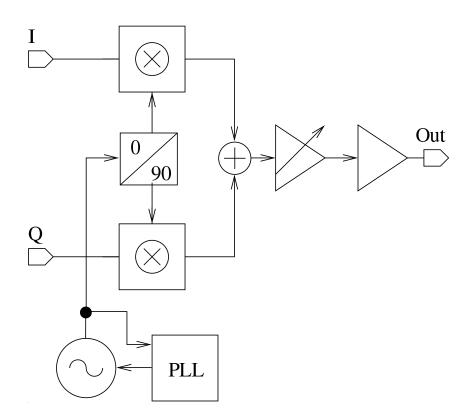

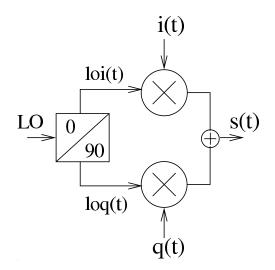

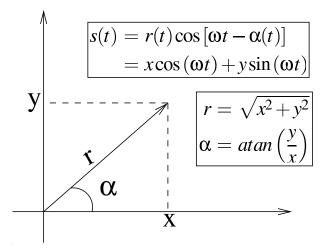

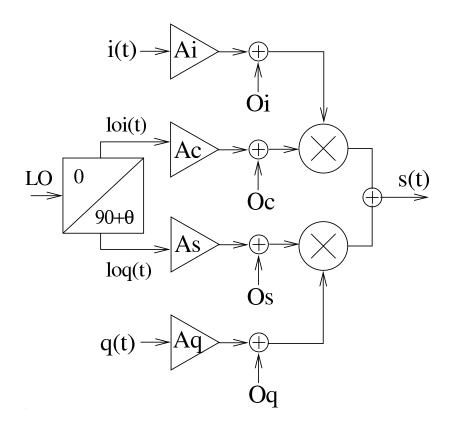

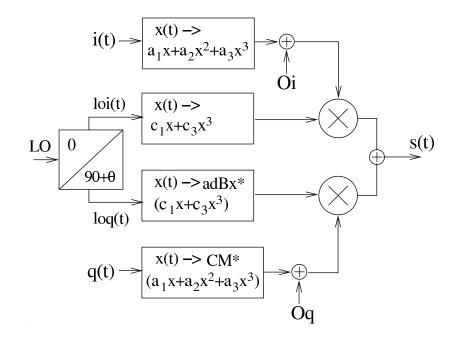

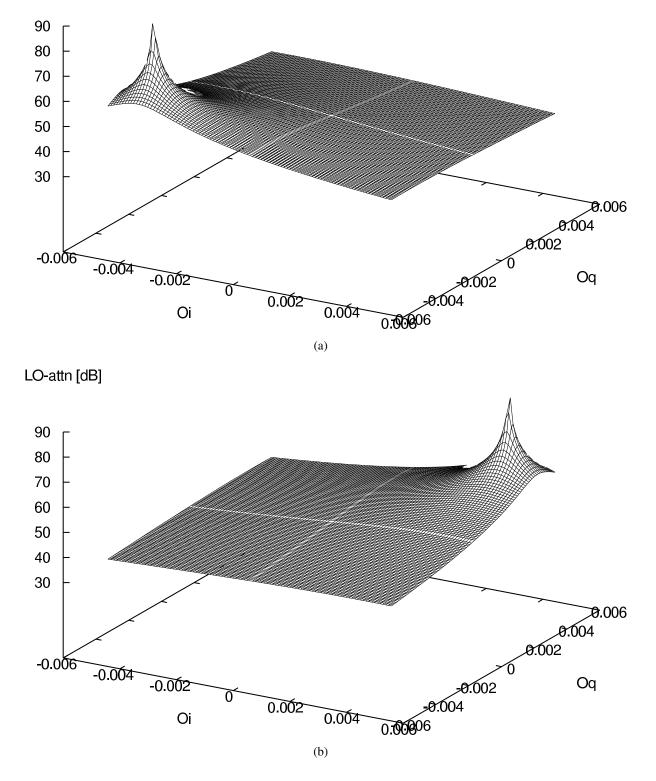

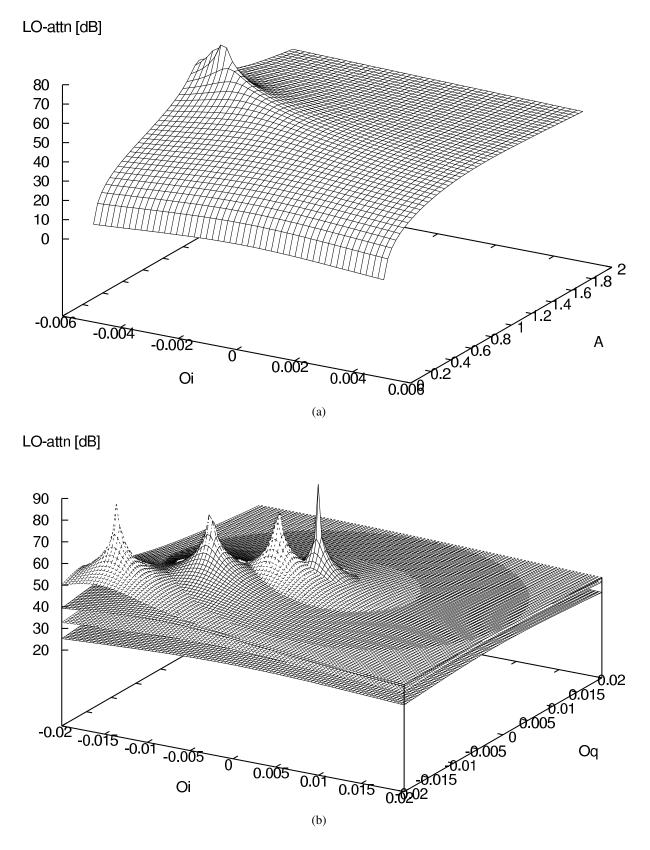

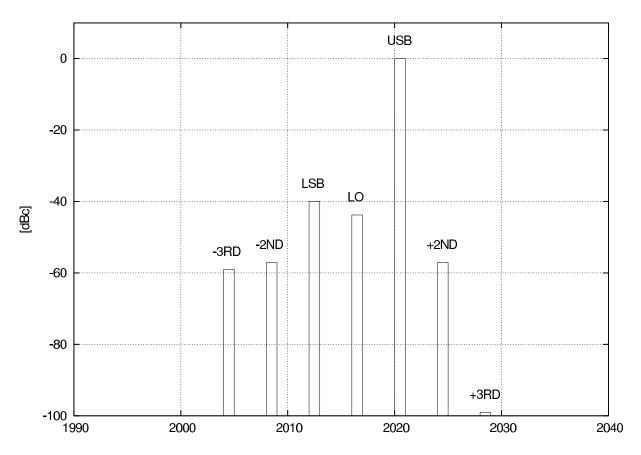

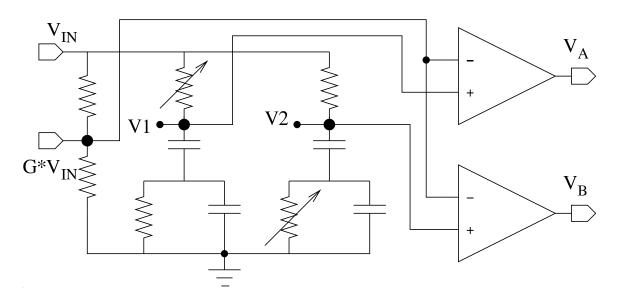

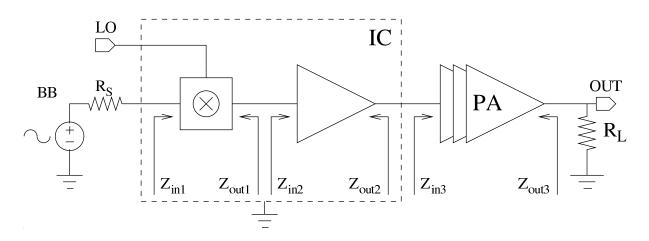

Since both polar loop transmitters and two-step transmitters include a quadrature modulator for I/Q up-conversion, it has the least hardware complexity and is the most integrable transmitter type. This simplicity is also evident in the direct-conversion quadrature modulator block diagram shown in Fig. 1.4, where only one frequency synthesizer is used. Such an IQ modulator is also compatible with broadband signaling, such as MB-OFDM for ultra-wideband (UWB physical layer proposal in [8]), and, as third-party vendors can be used, decades of PA research can be tapped for linearized or linear PAs so as to rapidly attain acceptable system performance. Alas, a good quadrature modulator performance is sensitive to DC offsets, signaling accuracy, noise, and distortion. Deviations from exact quadrature signaling (signals at 90° offsets) give rise to an unwanted sideband. The microwave carrier or local (LO) may leak to the output and destroy signal integrity through several mechanisms, such as: baseband offset; LO phasing errors, and package/bonding wire antenna effects. Different control circuits or direct digital up-conversion have been suggested as remedies for better signal quality. However, although impressive, both approaches fail to offer broadband drop-in functionality, and their performance is limited to either

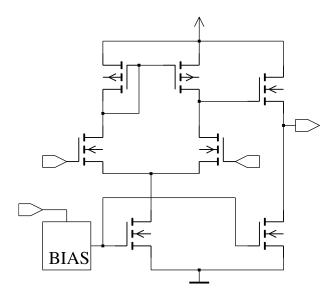

Figure 1.4: A direct-conversion quadrature modulator with high power amplifier (HPA) buffering.

spot-frequency operation [9] or sinc-effect baseband oversampling [10, 11]. Both approaches share the microwave LO phasing to quadrature (IQ-signaling) as the performance limiting factor.

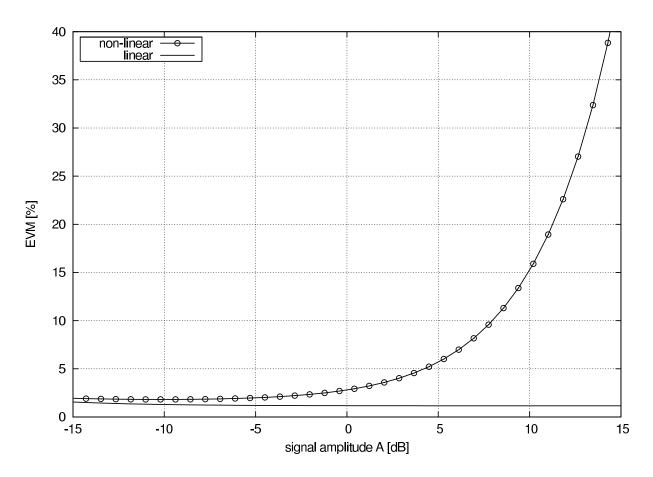

To illustrate how the IQ modulator specifications differ depending on the specific application, the published performance for a 3G basestation transmitter [12] and for a multistandard WLAN (802.11a/b/g) application [13] are shown in Table 1.1. The 3G basestation application is a good example of the need to minimize modulator error-vector-magnitude (EVM), as the total system EVM specification is 17.5% (QPSK) but still only a maximum EVM of 5% (max) has been specified to the modulator. This has been done to increase PA efficiency with the variable-envelope modulation, since a high EVM margin allows the PA to be used deeper in its non-linear, efficient mode of operation.

| IIIi | mance for 50 and wLAN applications. |       |     |         |                |  |  |

|------|-------------------------------------|-------|-----|---------|----------------|--|--|

|      |                                     |       | 3G  | WLA     | WLAN           |  |  |

|      |                                     |       |     | 2.4 GHz | 5 GHz          |  |  |

|      | POUT                                | [dBm] | +41 | -4      | -4             |  |  |

|      | IRR                                 | [dBc] | -30 | -40     | -40            |  |  |

|      | $OP_{1\mathrm{dB}}$                 | [dBm] | +3  |         | —              |  |  |

|      | $OIP_3$                             | [dBm] | +13 | +17     | +13            |  |  |

|      | EVM                                 | [%]   | 5   | 3.2     | 3.6            |  |  |

|      | I <sub>DD</sub>                     | mA    |     | 13      | 137<br>1.6-3.6 |  |  |

|      | $V_{\mathrm{DD}}$                   | V     | —   | 1.8/1.6 |                |  |  |

|      |                                     |       |     |         |                |  |  |

Table 1.1: Published buffered quadrature modulator performance for 3G and WLAN applications.

The set of WLAN specifications is another good example of high bitrate wireless communications, but targeted to be used at a much shorter range than the 3G device. For the 3G device a higher transmitted power is needed to keep the basestation geographical cell size economically feasible, whereas a high power WLAN transmission could be detrimental to other applications roaming in the same unlicensed frequency bands. Use of the higher bitrate WLAN modes of operation (55 Mbit/s) dictates that a minimum IRR performance of -40 dBc has to be achieved [14]. The reason for the increased IRR specification is that the OFDM modulation used for the high bitrates needs accurate phasing, unless it starts to fold its subcarriers onto each other.

#### **1.2 Research contribution**

This thesis work concentrates on microwave signal integrity in the context of direct-conversion quadrature modulators: integrated balun and quadrature signaling accuracy and mismatch evaluation are at the core of this work. LO frequency synthesis, and power amplifier design are extensive topics in their own right, but they have been treated as being outside the scope of this thesis work. Reference to these issues is only made where it is helpful in defining practical available broadband performance from a quadrature modulator.

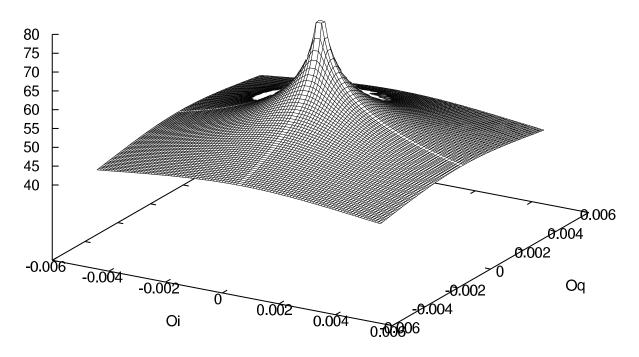

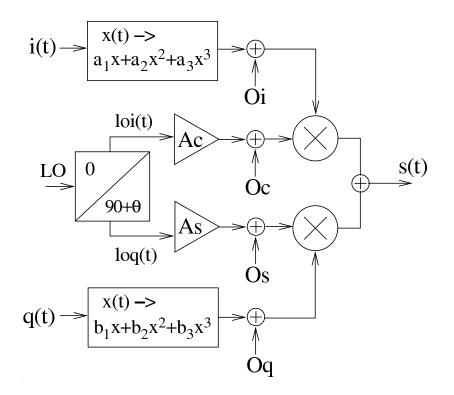

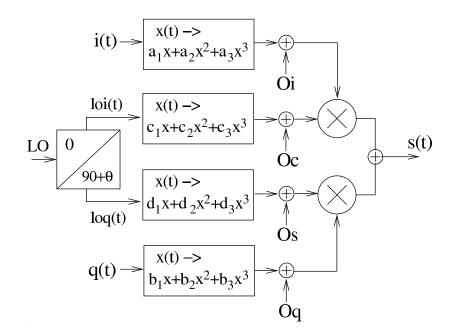

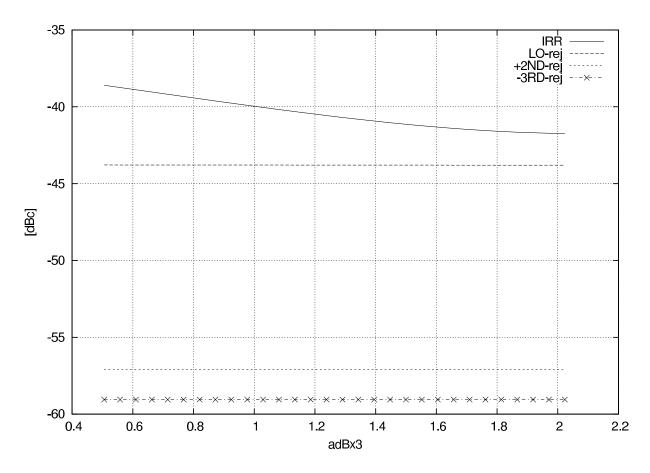

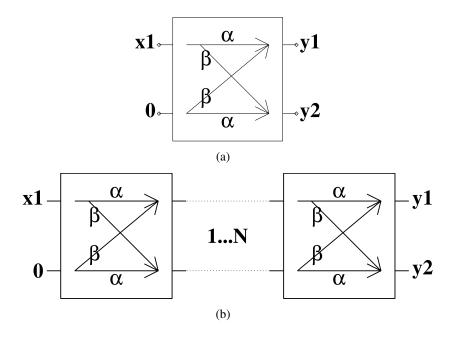

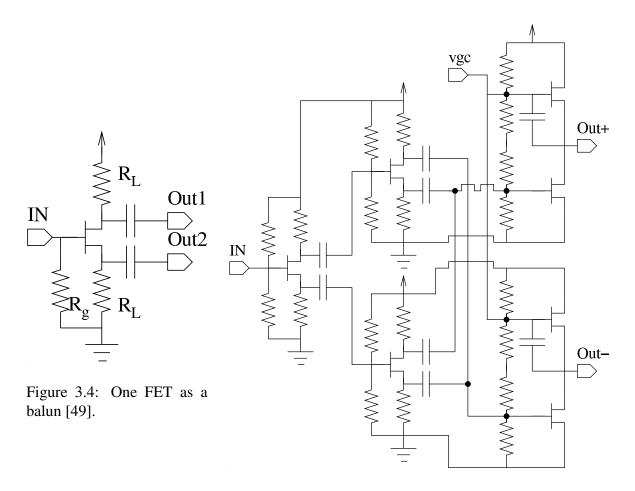

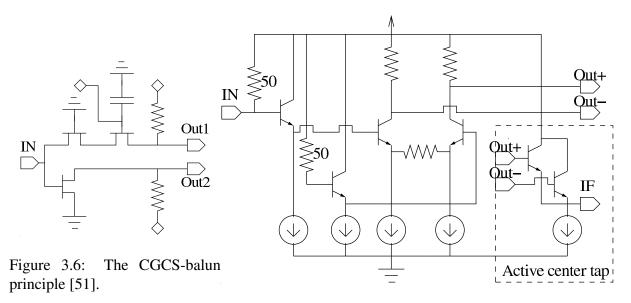

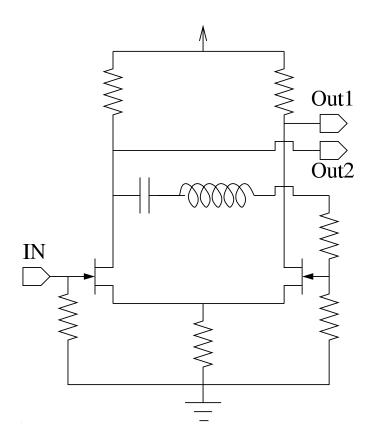

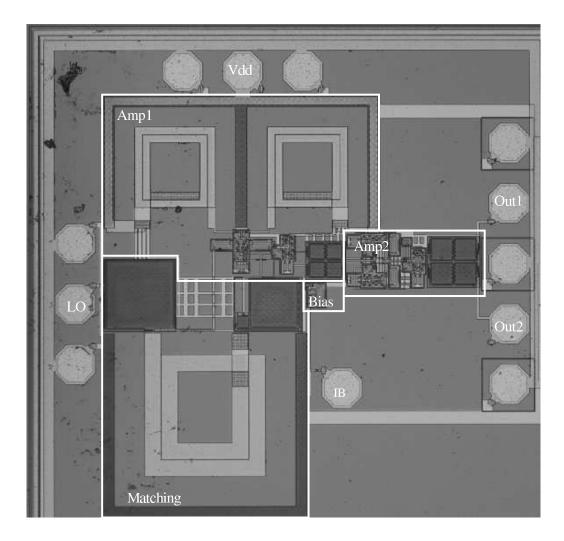

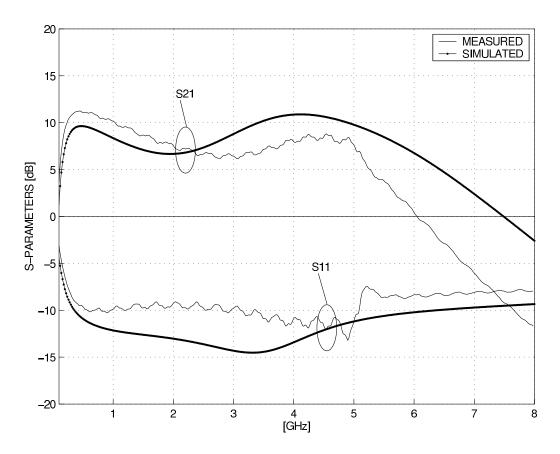

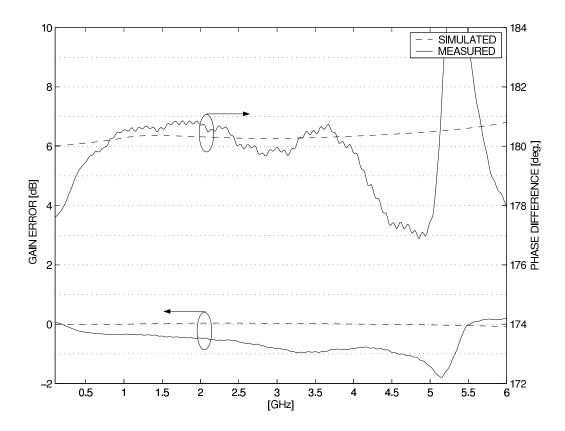

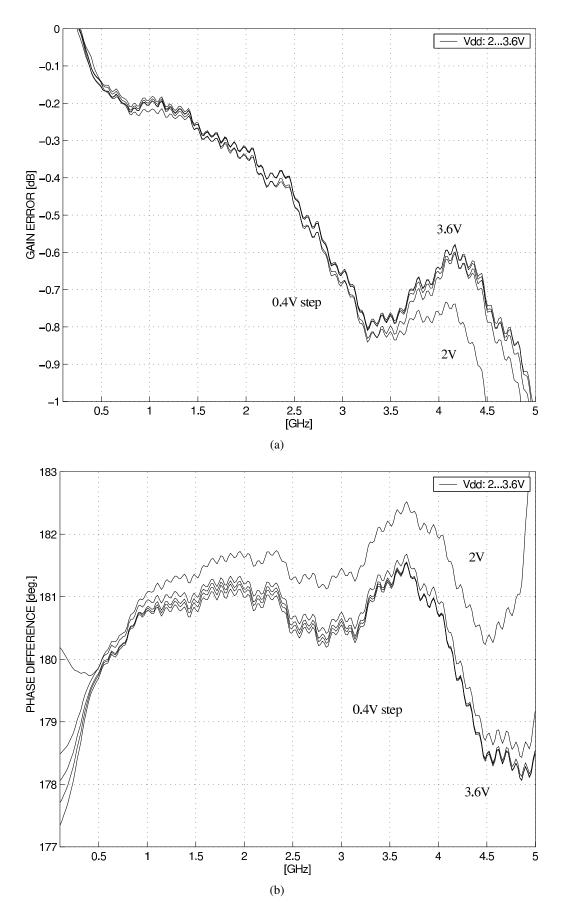

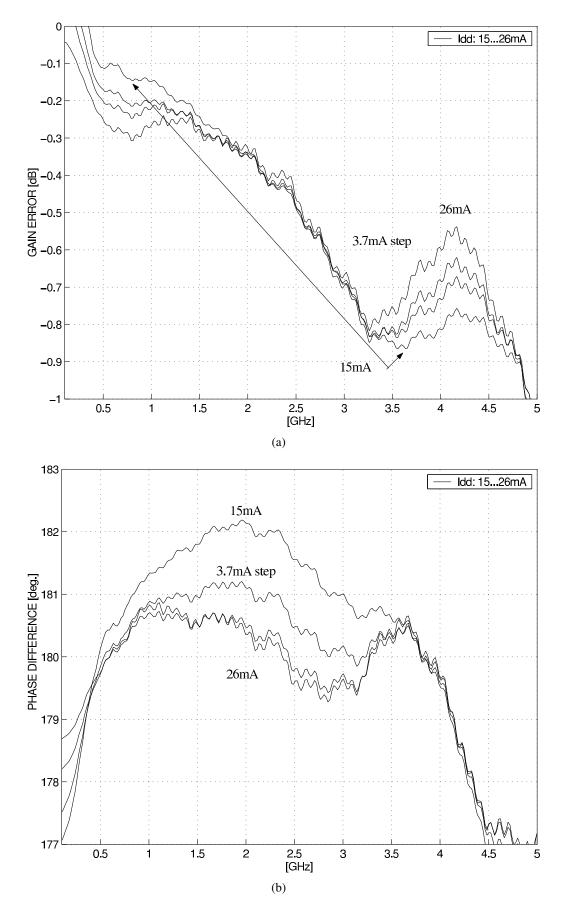

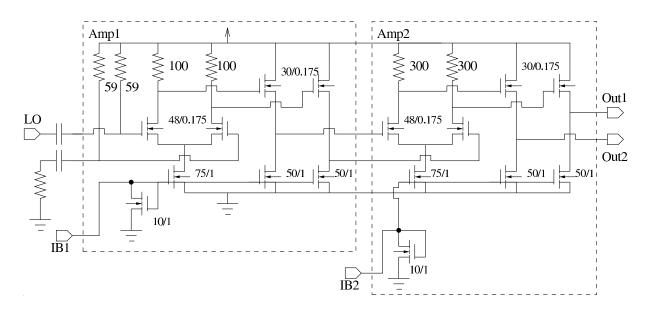

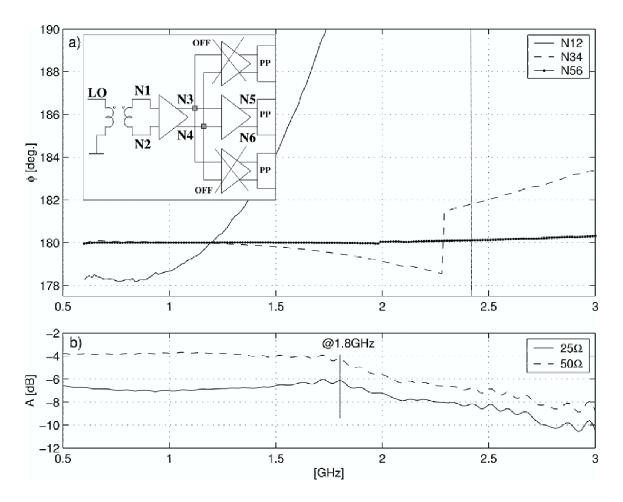

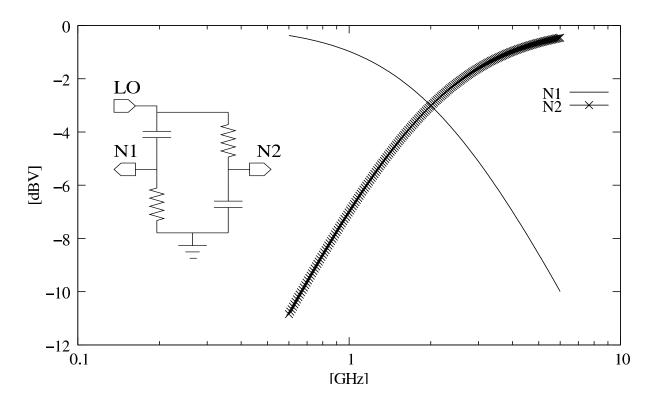

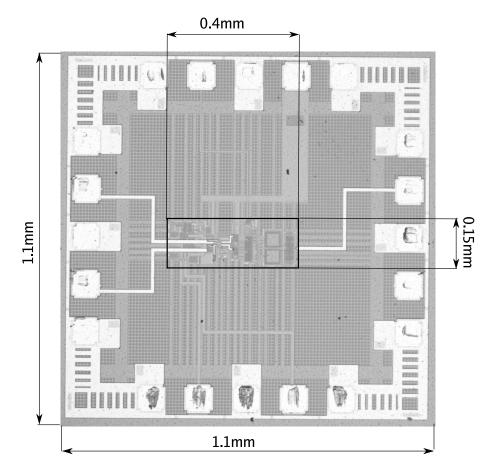

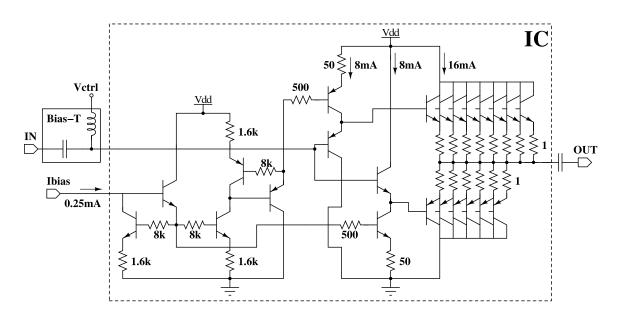

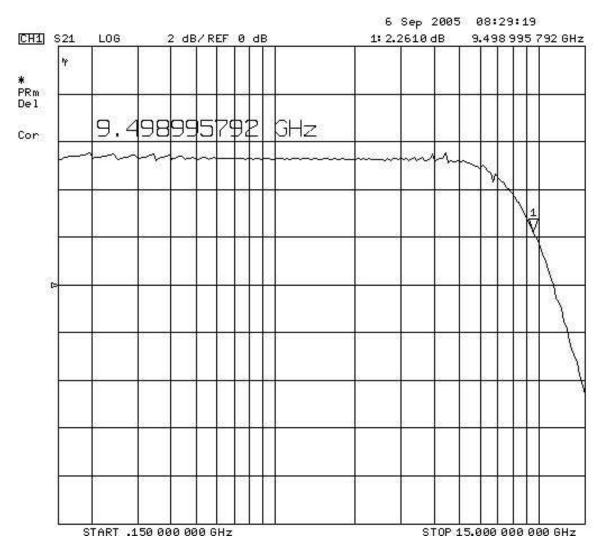

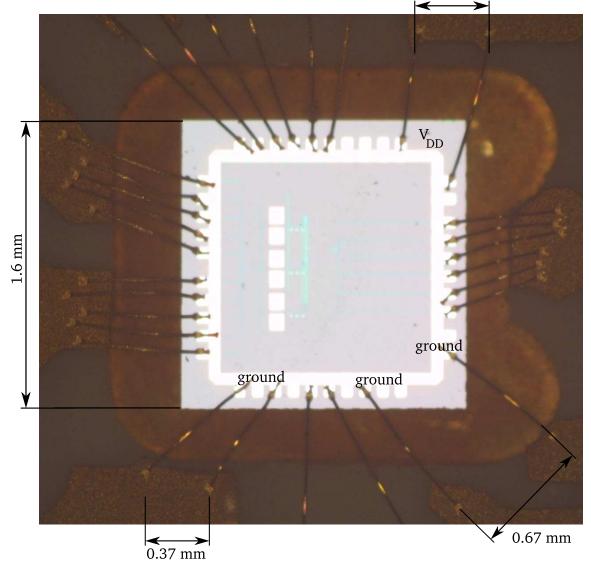

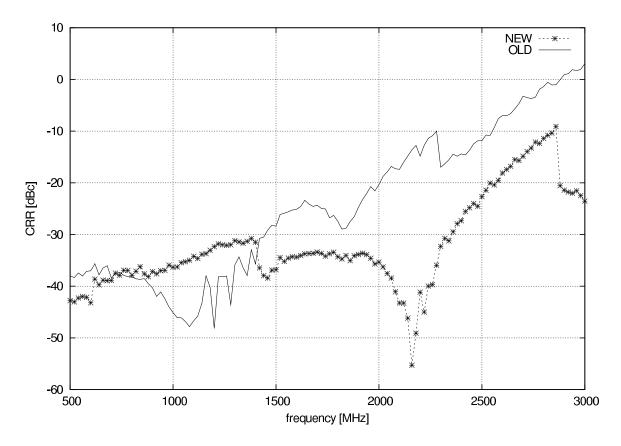

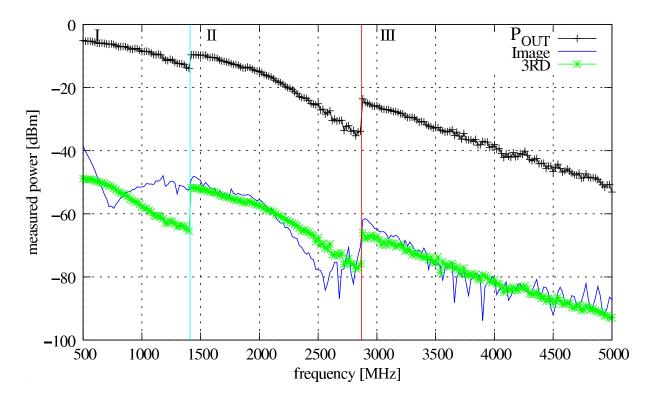

Four radio frequency integrated circuits (RFICs) were fabricated in support of this thesis. The technologies used for the first three prototypes are illustrative of underlying development trends in 2000-2004, as linewidths dropped from 0.8  $\mu$ m to 0.13  $\mu$ m while processes varied from BiCMOS, through SiGe, to a digital CMOS process. The fourth prototype was implemented in an experimental 0.4  $\mu$ m complementary SiGe process with an emphasis on finding improved mixer and buffer structures.