| Helsinki University of Technology Reports in Electron Physics 2001/28<br>Espoo, October 2001                                                        |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                     |

|                                                                                                                                                     |

|                                                                                                                                                     |

|                                                                                                                                                     |

| PROCESSING OF HIGH EFFICIENCY SILICON SOLAR CELLS                                                                                                   |

| Jaakko Härkönen                                                                                                                                     |

| Dissertation for the degree of Doctor of Science in Technology to be presented with due permission                                                  |

| for public examination and debate in Auditorium S4 at Helsinki University of Technology on the 9 <sup>th</sup> of November 2001 at 12 o'clock noon. |

|                                                                                                                                                     |

|                                                                                                                                                     |

|                                                                                                                                                     |

|                                                                                                                                                     |

|                                                                                                                                                     |

| Helsinki University of Technology<br>Department of Electrical and Communications Engineering<br>Electron Physics Laboratory                         |

| Teknillinen korkeakoulu                                                                                                                             |

Sähkö- ja tietoliikennetekniikan osasto Elektronifysiikan laboratorio Distribution:

Helsinki University of Technology

Electron Physics Laboratory

P.O.Box 3000

FIN-02015 HUT

Tel. +358-9-451 2322

Fax. +358-9-451 5008

http://www.hut.fi/Units/Electron/

ISBN 951-22-5680-0 ISSN 0781-4984

Otamedia Oy Espoo 2001

#### HELSINKI UNIVERSITY OF TECHNOLOGY

**Author:** Jaakko Härkönen

**Title:** Processing of silicon solar cells

**Date:** 20.3.2001 **Number of pages: 106**

**Department:** Department of Electrical and Communications Engineering

**Professorship:** Microelectronics (semiconductor technology) Code: S-69

**Supervisor:** Professor Pekka Kuivalainen

### **Abstract:**

Fabrication technology of high efficiency silicon solar cells has been studied in this work. Process development work has been carried out since 1997 within a project "Development of high -efficiency low -cost silicon solar cells", which was funded by TEKES, Fortum Advanced Energy Systems and Okmetic Ltd. Co –operation with photovoltaic research group of Fortum Surface Chemistry has been very close during the project. Target of this project is to demonstrate by low cost processing technologies, the feasibility of the fabrication of solar cells with a conversion efficiency as high as possible.

Three different solar cell configurations and their processing technologies are discussed in this content. The solar cells processed by industrially feasible methods on the low cost multicrystalline silicon wafers are the main focus of this work. Solar cells made of single crystalline silicon are studied in order to reveal the capability of the fabrication process in scope of the conversion efficiency. The third cell technology is the devices made by Rapid Thermal Processing of silicon wafers. That topic has been studied because of its possible potential for excellent manufacturability.

Processing of the solar cells has been carried out in the clean room facilities of Microelectronics Center at HUT. In addition to device processing, a special issue in this project has been characterization of metallic impurities and defects in multicrystalline silicon material.

Minimization of unwanted impurities and defects as well as understanding their interactions is necessary when processing high performance devices. Process induced contamination sources has been charted by  $\mu PCD$  ( microwave Photoconductive Decay ) and SPV ( Surface Photovoltage ) measurements.

Other special issues in this thesis are investigation of passivation properties of PECVD grown Si<sub>3</sub>N<sub>4</sub> films, optimization of emitter diffusion and Cr/Cu front contact metallization.

During three years, several hundreds of single and multicrystalline silicon wafers have been processed to solar cells. Best conversion efficiencies were 15,1 % ( mc-Si ), 16,4 % ( c-Si ) and 14,5% ( RTP mc-Si ).

**Keywords**: Solar cells, Multicrystalline silicon, Silicon processing, Lifetime.

### **Preface**

I would like to thank professor Juha Sinkkonen for possibility to carry out the research for this work at the Electron Physics Laboratory. Professor Pekka Kuivalainen deserves a big thanks for being my supervisor.

This Doctoral Thesis is a result of project which has been funded by TEKES, Fortum Advanced Energy Systems and Okmetic Ltd. I would like to warmly thank these instances for their funding and sympathy for photovoltaic research at the Electron Physics Laboratory. Among the steering group of the project, I would especially like to thank Dr. Emmanuel Fabre and Dr. Tuomo Suntola for many fruitful discussions and advices.

The results presented in this work would not have been possible without very close cooperation between the photovoltaic research groups of HUT and Fortum. The cooperation used to be unusual informal, flexible and constructive. In other words, it was a pleasure to make solar cells together with Dr. Pentti Passiniemi, M.Sc. Markko Rajatora and M.Sc. Teemu Marjamäki.

The experimental research on the semiconductor devices is a team work. The results to be presented in this work are results of the team. I warmly thank all the members of the photovoltaic research group of the Electron Physics Laboratory that have given their contributions to this work. Especially, it was my privilegde to conduct the research for the Master's Thesis of Tuuli Juvonen and Kimmo Solehmainen. The results of their studies are referred in Chapters 10 and 11.

The process development of semiconductor devices requires a great number of samples to be processed. The clean room work was mostly done by skillfull professionals. I would like to thank the laboratory technicians Janne Kylmäluoma and Helena Karppinen for their very important work that made us possible to demonstrate high efficiency silicon solar cells.

M.Sc. Kukka Banzuzi corrected my English which is far away from perfect. I appreciate very much her efforts.

I thank my colleagues at the Electron Physics Laboratory for the good athmosphere and "Jenny ja Antti Wihurin säätiö", "Väisälän säätiö" and "Ulla Tuomisen säätiö" for the economical support. I would also like to thank my family for the encouragment during my studies. This work is dedicated to memory of my mother.

Jaakko Härkönen Geneve 22.03.2001

# **List of Symbols**

A Area of the solar cell

AFM Atomic Force Microscope

AM1.5G Air Mass 1.5 Global

ARC Antireflection Coating

α Absorption coefficent

$\alpha_{v}$  Coefficient of thermal expansion

BSF Back Surface Field GaAs Gallium Arsenide

C(z) Spatial collection efficiency function of the solar cell

σ Capture cross sections

CdTe Cadmium Telluride

CIS Copper Indium diSelenide

DI Deionized water CH<sub>3</sub>COOH Acetic acid CO<sub>2</sub> Carbon dioxide

CVD Chemical Vapor phase Deposition

Cu Copper Cr Chromium

Cz-Si Czochralski silicon

$D_{n,p}$  Diffusion constant of electrons and holes

DS Direct solidification

d Strain rate EElectric field  $E_a$ Activation energy  $E_i$ Intrinsic Fermi level  $E^{'}$ Young's modulus eV Electron volt 3 Dielectric constant Fe -B Iron boron pair Fz-Si Float Zone silicon

$F(\lambda), \Phi(\lambda)$  Flux of the incident light

FF Fill factor

G Generation rate

HF Hydrofluoric acid

$I_s$  Diode saturation current  $I_{sc}$  Short circuit current  $I_L$  Light generated current IQE Internal Quantum Efficiency

J Current density  $k_B$  Bolzmann's constant L Diffusion constants

$\lambda$  Wavelength

LBIC Laser Beam Induced Current

MW<sub>p</sub> Mega Watt Peak, nominal output power of the solar cell

mc-Si Multicrystalline silicon NaOH Sodium hydroxide

NH<sub>4</sub>OH Nitric acid

$N_A$  Acceptor doping density  $N_D$  Donor doping density  $N_{it}$  Interface trap density

*n<sub>i</sub>* Intrinsic doping concentration*n* Concentration of electrons

OH Hydroxide ion

$\Omega$  Ohm

PECVD Plasma Enhanced Chemical Vapour Deposition

p Concentration of holesPCD Photoconductivity Decay

PC1D Device simulator

$\eta$  Conversion efficiency of the solar cell

RRecombination rate $R(\lambda)$ Reflection coefficentRIEReactive Ion EtchingRTORapid Thermal Oxidation

$\rho$  Charge density

$\mu_{n,p}$  Mobility of electrons and holes

$\sigma_{rr,\theta\theta}$  Thermoelastic stress

$S_{n,p}$  Surface recombination velocity for electrons and holes

SC Standard Cleaning

SEM Scanning Electron Microscope

SF<sub>6</sub> Sulphurichexafluoride

SiO<sub>2</sub> Silicon dioxide SOD Spin –on Dopant

$SR(\lambda)$  Spectral response of the solar cell

Si<sub>3</sub>N<sub>4</sub> Silicon Nitride

SiN<sub>x</sub> Non –stoichiometric silicon nitride

SPV Surface Photovoltage

au Lifetime

$au_{eff}$  Effective lifetime  $au_{B}$  Bulk lifetime

T Absolute temperature

V Voltage

$V_{oc}$  Open circuit voltage of the solar cell

v<sub>th</sub> Thermal velocity v Poisson's ratio

W<sub>scr</sub> Width of the space charge region

$W_B$  Width of the base region  $W_E$  Thickness of the emitter

z,x Distance

# **Contents**

| 1. Introduction                                                                                                                       | 1        |

|---------------------------------------------------------------------------------------------------------------------------------------|----------|

| 2. Physics of pn –junction solar cells                                                                                                | 5        |

| 3. Lifetime characterization                                                                                                          | 17       |

| 3.1 Photoconductivity Decay ( PCD ) method<br>3.2 Surface Photovoltage measurement                                                    | 18<br>21 |

| 4. Efficiency losses                                                                                                                  | 25       |

| 5. Multicrystalline silicon                                                                                                           | 28       |

| 6. Wafer cleaning and wet etching                                                                                                     | 35       |

| 7. High temperature processing of solar cells                                                                                         | 41       |

| 7.1 Lifetime characterization of high temperature processing 7.1.1 Experimental procedure                                             | 49<br>51 |

| 8. Antireflection coating                                                                                                             | 55       |

| 8.1 Properties of silicon nitride thin films grown by PECVD 8.2 Characterization of PECVD grown Si <sub>3</sub> N <sub>4</sub>        | 55<br>57 |

| 9. Contacts of solar cells                                                                                                            | 63       |

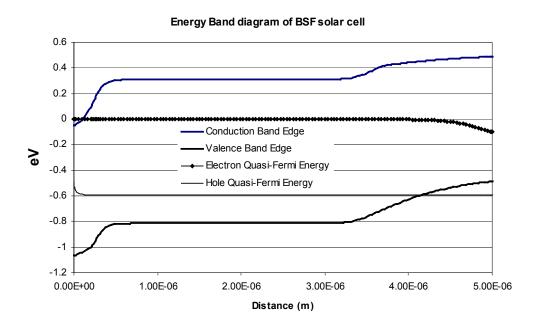

| <ul><li>9.1 Processing of the front contact</li><li>9.2 Processing of the back contact and</li><li>Back Surface Field (BSF)</li></ul> | 66<br>68 |

| 10. Rapid Thermal Processing (RTP) of solar cells                                                                                     | 71       |

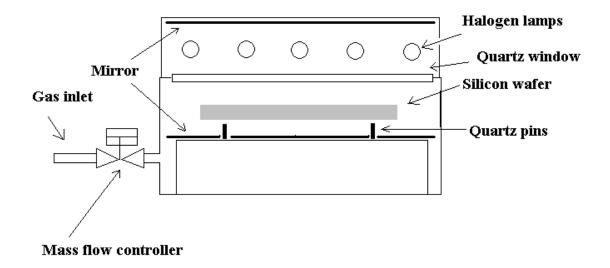

| 10.1 Experimental                                                                                                                     | 75       |

| 11. Processing of single crystalline silicon solar cells                                                                              | 77       |

| 11.1 Substrate technology 11.2 Processing of high efficiency single crystalline silicon solar cells                                   | 77<br>81 |

|                                                                                                                                       |          |

| 12.Characterization of solar cells                                                                                                    | 87       |

| 13. Results                                                                                                                           | 90       |

| 13.1 Comparison of measured and simulated parameters                                                                                  | 91       |

| 14. Conclusions | 98  |

|-----------------|-----|

| References      | 103 |

## 1. Introduction

Environmental awareness has traditionally motivated the research of renewable energy sources. Solar cells convert sunlight directly to electrical power without any pollution, exhaust, fuel, noise or moving parts. Benefits of this elegant form of the energy conversion from cost free solar radiation to the most usable form of the energy, electrical current, have been recognized decades ago. However, despite of three decades of intensive research, photovoltaic devices correspond today only to a very small amount of the global energy production, and it has been widely accepted that solar cells cannot be implemented as a primary energy source in the industrialized countries. This is mainly due to the lack of methods to store electricity and the high expenses of solar energy system components. There can still be, however, a great environmental impact if solar cells reduce effectively the use of fossil fuels in developing countries, which are predicted to be responsible for a major part of global CO<sub>2</sub> emissions in the future.

Solar energy markets show significant annual growth numbers. Renewable energies oriented business seems to have reached a certain degree of maturity, i.e. moving from governmentally subsidized activity towards a truly market steered industry.

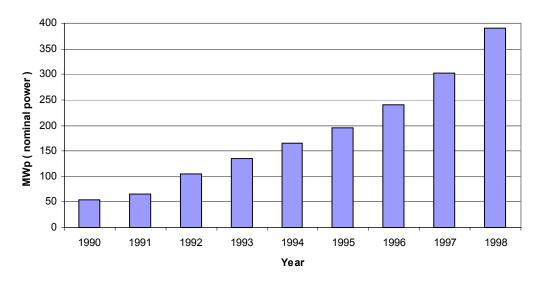

# Cumulation of installed photovoltaic energy production capacity

**Figure 1.**Annual installed PV power according to the Reference [1].

Photovoltaic markets clearly have two mainstreams. One is to produce electricity as cheaply as possible and the other one is to maximize the performance of the solar energy system at the moderate level of costs. Statistics of the solar energy system production is shown in Table 1.

**Table 1.** Production of solar cells and photovoltaic modules in 1997 [1]. Numbers correspond to nominal output power in  $MW_p$ . Other module production consists of CIS ( Copper Indium Diselenide ), CdTe and GaAs solar cells. GaAs solar cells are used within space industry. Although their contribution in nominal output power is small, space solar cells play a significant role in turn – over of photovoltaic markets.

|        | Cell<br>Productio<br>n | Module<br>Productio<br>n | Module<br>Productio<br>n<br>capacity | a-Si<br>productio<br>n | c-Si<br>module<br>productio<br>n | Other<br>module<br>productio<br>n |

|--------|------------------------|--------------------------|--------------------------------------|------------------------|----------------------------------|-----------------------------------|

| USA    | 51                     | 36                       | 72                                   | 2,5                    | 29                               | 4,4                               |

| Japan  | 29                     | 34                       | 81                                   | 2,4                    | 32                               | 0                                 |

| Europe | 15                     | 22                       | 48                                   | 0,9                    | 21                               | 0                                 |

| Rest   | 8                      | 8                        | 8                                    | 0                      | 8                                | 0                                 |

| Totals | 103                    | 100                      | 209                                  | 5,8                    | 90                               | 4,4                               |

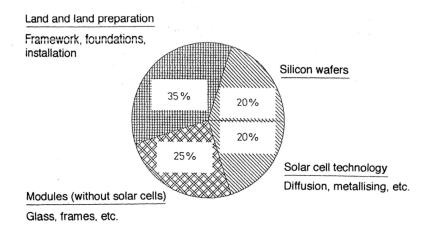

Photovoltaic devices have found a great variety of applications outside of the primary energy production, like transportable electronics, remote telecommunication systems, rural electrification etc. These new applications have created a need for solar cells with higher conversion efficiency. Costs of the solar energy system can be roughly divided into the following categories as shown in Figure 2.

**Figure 2.**Cost distribution of solar energy system [2].

According to Fig. 2 , about one fifth of the total costs of a photovoltaic module is attributed to the silicon substrate. One multicrystalline wafer (  $100 cm^2$  ), costed about 1,8 USD in 1999. If a conversion efficiency of 14% is assumed a total number of 37 mc –Si solar cells are required for a 50  $W_p$  ( nominal output power under AM1.5G illumination conditions ) module. Total costs of the module would then be 333 USD . According to the Reference [3], daily solar radiation in Southern Finland in September is about 3 kWh/m² . The photovoltaic module would therefore produce 3 kWh/m² \* 0,37m² \* 14% of electrical energy which is about 0,15 kWh. In photovoltaic costs analysis, the lifetime of solar energy system is usually assumed to be 30 years. If average solar radiation in September is assumed to be the same as average radiation throughout the year, the module would produce about 1700 kWh in 30 years. That would lead to a price of 5 USD / kWh which is at least 50 times more than the price of electricity in Finland in 1999.

Wide utilization of solar electricity is apparently not economically competitive at the moment in Finland. It is, however, difficult to predict the future of solar energy from the global point of view. Obviously most of the world's population could be regarded as potential users of photovoltaic energy. It is characteristic that in densely populated areas, for example India or China, energy consumption per capita is much less than in the industrialized countries. Also, in these areas the power density of solar radiation is typically larger by a factor of two compared to Finland. It is definitely not insignificant

whether the energy demand in developing areas is fulfilled by burning fossil fuels or by renewables.

# 2. Physics of pn -junction solar cell

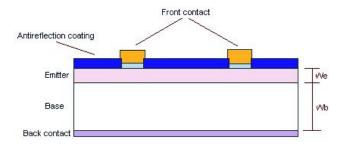

In principle, a silicon solar cell is a large area pn-junction diode processed on a single or multicrystalline silicon wafer. Fabrication of such a device in its simplest form requires only formation of an  $n^+$ -emitter on the p-type substrate, deposition of an antireflection coating (ARC) and contacting the device on the front and back sides.

Figure 3. Schematic cross section of the pn –junction solar cell.  $W_e$  is the width of the emitter and  $W_b$  is the width of the base region of the solar cell.

When sunlight is absorbed in a solar cell, the photons generate electron -hole pairs that contribute to the electrical current if they are successfully collected to the electrodes. Dynamical behavior of electrons and holes is described with continuity equations [4].

$$\frac{\partial n}{\partial t} = G_n - R_n + \frac{1}{q} \nabla \bullet J_n

\frac{\partial p}{\partial t} = G_p - R_p - \frac{1}{q} \nabla \bullet J_p$$

(1)

where subscribes n and p refer to electrons and holes, respectively. G is the generation rate, R is the recombination rate and J is current density. In order to derive the current -

voltage relationship of semiconductor devices, three more equations are needed. The Poisson equation is a special case of the Maxwell's equations when no magnetic field is present. The Poisson equation gives the relationship between charge density and electric field.

$$\nabla \bullet E = \frac{1}{\varepsilon} \rho \quad , \tag{2}$$

where E is the electric field,  $\varepsilon$  is the dielectric constant of the semiconductor and  $\rho$  is the charge density. Current in a semiconductor device is a result of the flow of electrons and holes which is caused by the electric field and the gradient of the carrier density.

$$J_{n} = q\mu_{n}nE + qD_{n}\nabla n$$

$$J_{p} = q\mu_{p}nE - qD_{p}\nabla p$$

, (3)

where  $D_{n,p}$  is the diffusion constant of the given semiconductor. The first component of the current density is the so called drift current and second term is the diffusion current. The diffusion constant depends on the temperature and mobility of the charge carriers and can be expressed with the so called Einstein's relation.

$$D_{n,p} = \frac{k_B T}{q} \mu_{n,p} \qquad , \tag{4}$$

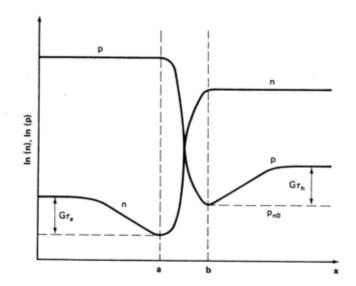

where  $\mu_{n,p}$  is the mobility of electrons and holes and  $k_B$  is the Boltzmann's constant. The mobility of the charge carriers in silicon is a well-known material parameter and it is affected by different scattering processes. Schematic illustration of charge carrier densities in an illuminated pn—junction structure is shown in Figure 4.

**Figure 4.**Distribution of charge carriers in an illuminated, infinite pn –junction. Edges of space charge regions are marked with *a* and *b*. Generation of charge carriers is assumed to be homogenous in the entire device [5].

When a pn –junction diode is illuminated, photons having a higher energy than the band gap of the semiconductor, create electron hole pairs. Minority carriers which are generated within the diffusion length are swept by the electric field of the space charge region to their respective majority carrier side of the junction. Light generated current in quasi –neutral regions is therefore diffusion of minority carriers and the current flows to the opposite direction compared to a current flowing in a forward biased pn- junction without illumination.

The current transport mechanism offers also a convenient way to distinguish the different solar cell categories. The operation of silicon solar cells is based on diffusion of minority carriers, whereas thin film cells as well as compound semiconductor solar cell structures utilize electric field assisted transport of the light generated charge carriers. In the case of the III-V materials, the semiconductors band gap is direct, which in turn means that the lifetime of minority carriers is too short for the electron –hole pairs be collected efficiently by diffusion. Compound semiconductor solar cell structures are designed so that there are doping or band gap gradients that create an electric field through the active device regions. Amorphous silicon thin film (a-Si) cells are *pin* –

diodes where the electron -hole pairs are collected from the intrinsic layer by drift current. It is possible to make efficient solar cells of materials having a non –orientated crystallographic structure or a direct band gap, because the absorption of light is significantly stronger in these material systems. Detrimental high recombination rate can be circumvented by using the drift current transportation provided by the internal electric fields that penetrate through the relatively thin device regions.

In a simple analysis of the ideal pn –junction diode, recombination in the space charge region as well as the drift –current component in Eq (3) are neglected. For minority carriers in the n- side of the illuminated pn -junction

$$D_{p} \frac{d^{2} \Delta p}{dx^{2}} = \frac{\Delta p}{\tau_{p}} - G$$

$$p_{n} = \Delta p + p_{n0}$$

(5)

where  $\tau_p$  is the lifetime of holes and  $p_{n0}$  is the minority carrier concentration at the thermal equilibrium. General solution of this differential equation is

$$\Delta p = G\tau_p + Ae^{\frac{x}{L_p}} + Be^{-\frac{x}{L_p}} \quad , \tag{6}$$

where  $L_p$  is the diffusion constant for holes. The diffusion constant connects diffusion length to another important parameter, the lifetime, with the following relation

$$L_{n,p} = \sqrt{\tau_{n,p} D_{n,p}} \qquad . \tag{7}$$

A and B in Eq (6) are constants which are determined from boundary conditions. Constant A is zero because there must be some finite concentration of holes when x approaches infinity in the given geometry. In order to find out the constant B, it is necessary to find out the hole concentration at the edge of the space charge region at the n –side of the diode which is marked with b in Figure 4. According to [3], concentration of holes depends exponentially on the voltage across the diode at x=0.

$$p_{n,b} = p_{n0}e^{\frac{qV_a}{k_BT}} \qquad , \tag{8}$$

where T is temperature,  $V_a$  is the voltage over the diode and the subscribe b refers to Figure 4. Solution of Eq (5) with the above mentioned boundary conditions is

$$p_{n} = p_{n0} + G\tau_{p} + \left[ p_{n0} \left( e^{\frac{qV_{a}}{k_{b}T}} - 1 \right) - G\tau_{p} \right] e^{-\frac{x}{L_{p}}} , \qquad (9)$$

If the minority carrier distributions on both sides of the junction are known as in Eq (9), the total diffusion current can be calculated.

$$J_{p}(x) = \frac{qD_{p}p_{n0}}{L_{p}} \left(e^{\frac{qV_{a}}{k_{B}T}} - 1\right) e^{-\frac{x}{L_{p}}} - qGL_{n}e^{-\frac{x}{L_{p}}}$$

$$J_{n}(x) = \frac{qD_{n}n_{p0}}{L_{n}} \left(e^{\frac{qV_{a}}{k_{B}T}} - 1\right) e^{-\frac{x}{L_{n}}} - qGL_{n}e^{-\frac{x}{L_{n}}}$$

$$(10)$$

The total current density is uniform through the entire diode. In the space charge region recombination is neglected, but generation is included and it is given by

$$J_{scr} = qW_{scr}G (11)$$

where  $W_{scr}$  is the width of the space charge region. Current density in the diode can be obtained by adding the minority carrier current densities at x=0 to the current density generated in the space charge region. The relationship between current and voltage in a solar cell under illumination can be now written as

$$I = I_s \left( e^{\frac{qV_a}{k_B T}} - 1 \right) - I_L$$

$$I_L = qG(L_n + W_{scr} + L_p)$$

(12)

where  $I_s$  is a so called diode saturation current which is caused by different recombination mechanisms. This can be obtained from Eq (10) and it is given by

$$I_{s} = A \left( \frac{q D_{n} n_{i}^{2}}{L_{n} N_{A}} + \frac{q D_{p} n_{i}^{2}}{L_{p} N_{D}} \right)$$

(13)

where  $N_A$  is the acceptor doping density,  $N_D$  is the donor doping density, A is the area of the solar cell and  $n_i$  is the intrinsic carrier concentration of silicon given by

$$n_i^2 = N_C N_V e^{-\frac{E_g}{kT}} (14)$$

where  $N_{C,V}$  are the densities of states in the conduction and valence bands, respectively.  $E_g$  is the band gap of the semiconductor in electron volts. It can be seen that there is an exponential dependence of the intrinsic carrier concentration on the temperature. Consequently there is a similar dependence of diode saturation current i.e leakage current. This, in turn, leads to the fact that the conversion efficiency of solar cells is sensitive to temperature. The problematics related with the temperature dependence is discussed in Chapter 12, where the measurement technology of solar cells is described.

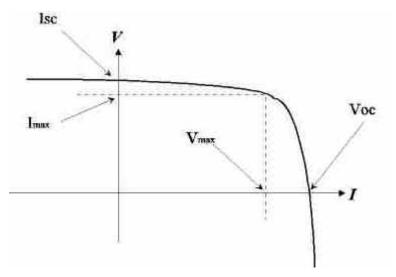

Efficiency of a solar cell is the ratio of electrical output power and incident optical power. It is usually expressed in terms of short circuit current, open circuit voltage and fill factor.

$$\eta = \frac{P_{out}}{P_{in}} = \frac{I_{\text{max}} V_{\text{max}}}{P_{in}} = \frac{I_{sc} V_{oc} FF}{P_{in}}$$

$$FF = \frac{I_{\text{max}} V_{\text{max}}}{I_{sc} V_{oc}}$$

(15)

As shown in Eq (22), fill factor FF is defined to be the ratio between maximum operation points and short circuit current and open circuit voltage. Fill factor is reduced by series resistance, leakage current over the edges of the solar cell or leakage current caused by recombination. The electrical parameters of the solar cell are visualized in a schematic current-voltage characteristics shown in Figure 5.

Figure 5. Schematic IV –curve of the solar cell under illumination. The parameters  $V_{oc}$ ,  $I_{sc}$ ,  $V_{max}$  and  $I_{max}$  are defined in Equations (12) and (15).

The above analysis of the current –voltage characteristic of the illuminated pn – junction diode is based on a very simple model and several approximations. More detailed analysis, which takes into account an important device parameter, namely the surface recombination velocity, is carried out in the Appendixes of Reference [3], and only the results are presented here. A more realistic picture of solar cell operation is obtained if the first term on the right hand side in Eq (13) is multiplied by constant  $F_N$  and second term is multiplied by  $F_P$ .

$$F_{N} = \frac{S_{p} \cosh(\frac{W_{E}}{L_{p}}) + \frac{D_{p}}{L_{p}} \sinh(\frac{W_{E}}{L_{p}})}{\frac{D_{h}}{L_{p}} \cosh(\frac{W_{E}}{L_{p}}) + S_{p} \sinh(\frac{W_{E}}{L_{p}})}, \quad (16)$$

and

$$F_{P} = \frac{S_{n} \cosh(\frac{W_{B}}{L_{n}}) + \frac{D_{n}}{L_{n}} \sinh(\frac{W_{B}}{L_{n}})}{\frac{D_{n}}{L_{n}} \cosh(\frac{W_{B}}{L_{n}}) + S_{n} \sinh(\frac{W_{B}}{L_{n}})}, \quad (17)$$

where  $W_B$  is the width of the base region of the diode i.e. the thickness of the silicon wafer and  $W_E$  is the thickness of the emitter as presented in Figure 2. In practice,  $W_B$  is several hundreds of micrometers and  $W_E$  is essentially the same as the depth of the diffused pn -junction.  $S_{n,p}$  is the surface recombination velocity for electrons and holes, respectively.

The  $I_L$  in Eq (12) is current generated by incident light. In addition to carrier generation rate, it can be also expressed in terms of Spectral Response (SR).

$$I_{L} = Aq \int_{\lambda_{0}}^{\lambda_{1}} SR(\lambda) (1 - R(\lambda)) F(\lambda) d\lambda \qquad , \tag{18}$$

where A is the area of the solar cell,  $\lambda$  is the wavelength of light,  $SR(\lambda)$  is the spectral response of the solar cell,  $F(\lambda)$  is the flux of the incident light and  $R(\lambda)$  is the reflection coefficient of the solar cell. The output current of the solar cell as a function of the wavelength of light is called spectral response. Internal spectral response can be expressed with [6]

$$SR(\alpha) = \int_{0}^{\infty} \alpha \exp(-\alpha z)C(z)dz$$

, (19)

where  $\alpha$  is the absorption coefficient of silicon and it can be expressed in terms of wavelength of the light, C(z) is spatial collection efficiency function of the solar cell and z is the distance. The collection efficiency function describes solar cells ability to generate electrical current from the absorbed sunlight. The function is defined separately for different regions of the solar cell

$$C(z) = \frac{K_{p} \exp(z / L_{p}) + \exp(-z / L_{p})}{K_{p} \exp(W_{E} / L_{p}) + \exp(-W_{E} / L_{p})}, \qquad 0 \le z \le W_{E}$$

$$C(z) = 1, \qquad W_{E} \le z \le L - W_{B}$$

$$C(z) = \frac{K_{n} \exp[(L - z) / L_{n}] + \exp[-(L - z) / L_{n}]}{K_{n} \exp(W_{B} / L_{n}) + \exp(-W_{B} / L_{n})}, \qquad L - W_{B} \le z \le L.$$

(20)

where  $K_n$  and  $K_p$  are constants, defined by

$$K_{n,p} = \frac{1 + S_{n,p} L_{n,p} / D_{n,p}}{1 - S_{n,p} L_{n,p} / D_{n,p}}.$$

(21)

In Equations (12)-(19) there are four parameters that can be influenced by device processing. These parameters are the reflection properties of the front surface, the diffusion length in the silicon material, the geometrical dimensions of the solar cell and the surface recombination velocity.

The open circuit voltage of the solar cell is obtained by setting the current I in Eq.(12) to zero and solving the voltage.

$$V_{oc} = \frac{kT}{q} \ln \left( \frac{I_L}{I_s} + 1 \right) \tag{22}$$

This equation implies that the open circuit voltage is determined by logarithmic ratio of light generated current and diode saturation current. Diffusion length and surface recombination velocities are present in Equations (12),(13),(15) and (16). These equations determine the diode saturation current as well as the light generated current. Therefore in order to maximize the voltage of the solar cell, recombination in the bulk and at both surfaces need to be minimized. Apparently, an important material parameter determining the conversion efficiency of the solar cell is the diffusion length in processed silicon wafer.

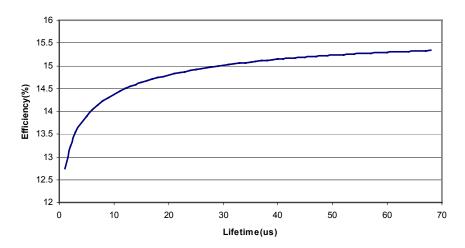

As it can be seen in Equations (16) and (17), the dependence of the efficiency on the lifetime is not linear. Apparently, numerical methods need to be utilized in order to reveal a reliable prediction of the lifetime versus efficiency relationship. At the given substrate resistivity, diffusion length is related to the minority carrier lifetime which is a measure of silicon material quality. Figure 6 presents the simulated dependence between minority carrier lifetime and conversion efficiency of a solar cell. The simulation has been carried out with the one -dimensional device simulator PC1D. The relevant simulation parameters are the same as the ones used for simulation of 15% efficient mc-Si solar sell in Chapter 12. The parameters are listed in Table 6.

#### Simulated efficiency vs. bulk lifetime

**Figure 6.**Simulated dependence between minority carrier lifetime and conversion efficiency of a solar cell.

It can be seen in Figure 6. that the efficiency of a solar cell is a strong function of the lifetime in the 1-30μs range. This range of the lifetime, expressed in terms of diffusion length, corresponds to the thickness of the solar cell or less. Within this range of deviation, the efficiency varies from 12,7% to 15%. On the other hand, within the range of lifetime from 30μs to 70μs, the efficiency is improved only about 0,6% and the increase in the efficiency seems to saturate towards the higher lifetime values. The conclusion is that, when the diffusion length of the minority carriers approaches the wafer thickness, the efficiency of the solar cell becomes more and more limited by the recombination at the back and front surfaces instead of the bulk recombination.

These notifications are fundamentally important when thinking of a *low -cost* concept for solar cells. The efficiency gap between world record solar cells and commercially available cells is about 9-10%. The material as well as the processing cost can be kept on a reasonable level in scope of solar energy production when a lower class, i.e. lifetime between 1-30µs, material quality is accepted. It is still possible to achieve a relatively high efficiency, e.g. 15%. In other words, the production cost can be manifold, for instance, eight to ten times higher if an efficiency as high as e.g. 16% is urgently wanted. The challenging task trying to increase the utilization of the solar energy is to

push the efficiency of economically produced solar cell up to the limits, near the 15%. That requires expertise on semiconductor processing technologies and a knowledge of lifetime behavior in low cost silicon. This work is mainly focused on these topics. Unless otherwise mentioned, all processes or process recipes, presented in this work are developed by the author.

### 3. Lifetime characterization

High minority carrier lifetime is the key factor when striving for a good operational performance of solar cells. Lifetime influences the open circuit voltage, the short circuit current as well as the fill factor. Despite of the lifetime's apparent importance, measurement of the minority carrier lifetime is very seldom straightforward. In this chapter, two common measurement technologies are shortly presented. A comprehensive overview of different minority carrier lifetime measurement techniques and detailed analysis of measurement physics can be found in references [7] and [8]. Contents of this Chapter is based mainly on these two sources.

Recombination lifetime is a time constant that corresponds to the average decay time of the excess carriers to be captured by some recombination centers. Recombination can take place due to impurity atoms in the semiconductors crystal lattice, lattice defects or surfaces. An excess of minority carriers can be generated by absorption of light or by a forward biased pn -junction.

All semiconductors contain impurities. As a matter of fact, every foreign atom but the host atom of the perfect periodic crystal can be considered as an impurity. The crystallographic point defects and structural defects can be also regarded as impurities. Impurities can be added to semiconductors in order to change the electrical properties of the material in different ways, such as diffusion or ion implantation. Doping is a crucial part of semiconductor processing. On the other hand, a large part of the impurities are unwanted in the semiconductor material. These impurities are incorporated during the crystal growth or device processing.

The dopant impurities, usually phosphorous, boron, antimony or arsenide, form so called *shallow -levels* to semiconductors band gap. In contrast to dopant atoms, the other impurities usually form *deep -levels* to the band gap. In some applications deep -level impurities are added in a controlled way to the base region of the bipolar devices in order to decrease the base transit time. Semi -insulating compound semiconductor substrates are also fabricated by adding some deep -level impurities to the substrate. Excluding these two applications, deep -level impurities are generally unwanted. In addition to the

crystal imperfections, the deep -level impurities in semiconductors include e.g. transition or refractory metals like copper, iron, gold or chromium. According to the Shockley – Read –Hall recombination statistics, most efficient recombination centers are the ones that form deep levels near the mid band gap and have large capture cross sections.

## 3.1 Photoconductivity Decay (PCD) method

In the Photoconductivity Decay method, effective lifetime is measured by illuminating the wafer by laser pulse, the transient of the decaying minority carrier is monitored and effective lifetime is extracted from the conductivity transient.

When a silicon wafer is illuminated by monochromatic light having an energy larger than the band gap, the absorbed photons generate a three dimensional cloud of electron -hole pairs which decays exponentially within the lifetime.

$$\Delta n(t) = \Delta n(0)e^{-\frac{t}{\tau_{eff}}} \qquad , \tag{23}$$

where

$$\frac{1}{\tau_{eff}} = \frac{1}{\tau_B} + D\beta^2 \tag{24}$$

where  $\tau_{eff}$  is the effective lifetime and  $\tau_B$  is the bulk lifetime. Measurement of the conductive decay therefore gives the value of the effective lifetime. Effective lifetime is a quantity which depends on the bulk lifetime and parameter  $\beta$  which is defined as

$$\beta \tan(\frac{\beta T}{2}) = \frac{s_r}{D} \tag{25}$$

where D is the so called ambipolar diffusion coefficient and it is given by

$$D = \frac{D_n D_p (n+p)}{n D_n + p D_n} \qquad , \tag{26}$$

and  $s_r$  is the surface recombination velocity. Surface recombination is caused by the interruptions in the periodic lattice structure at the end of the wafer or at different silicon / thin film interfaces which are constantly added to the wafer because of different device processing purposes. In addition to the interface properties, surface recombination velocity is also affected by the number of charge carriers in the vicinity of the surface. In other words, surface recombination velocity is an illumination level dependent quantity.

$$s_{r} = \frac{s_{n}s_{p}(p_{s0} + n_{s0} + \Delta n_{s})}{s_{n}(n_{s0} + n_{1s} + \Delta n_{s}) + s_{p}(p_{s0} + p_{1s} + \Delta p_{s})}, \qquad (27)$$

where

$$S_n = \sigma_{ns} v_{th} N_{it} \qquad , \tag{28}$$

$$S_p = \sigma_{ps} V_{th} N_{it} \qquad , \tag{29}$$

where  $\sigma_{ns}$  and  $\sigma_{ps}$  are capture cross sections of the interface traps,  $v_{th}$  is thermal velocity of charge carriers and  $N_{it}$  is the interface trap density. The  $n_{Is}$  and  $p_{Is}$  are defined as

$$n_{1s} = n_i e^{\frac{E_T - E_i}{kT}} \qquad , \tag{30}$$

$$p_{1s} = n_i e^{-\frac{E_T - E_i}{kT}} (31)$$

where  $E_T$  is the energy level of the surface trap and  $E_i$  is an intrinsic Fermi level. Number of charge carriers in the vicinity of the surface can be reduced by introducing a depletion region close to the surface. Silicon surfaces can be depleted for example by certain

chemical treatments, corona charging the surface or by providing a fixed charge to a dielectric film next to the silicon. The latter method is called field-effect passivation. Commonly used dielectric thin films used in silicon processing are  $SiO_2$  and  $Si_3N_4$ , but basically all dielectric films have some fixed charge that can be usually tuned by changing the deposition conditions.

Recombination lifetime of the silicon wafer is a good measure of the material quality and an important parameter in device modeling of solar cells. Therefore accurate determination of the bulk lifetime from the PCD measurement data is of special interest. However, as shown in Eq. (24), the measured lifetime is a combination of bulk lifetime and a time constant which is determined by surface recombination velocity. There are only two special cases where bulk lifetime of commercial silicon wafers can easily be measured with PCD method. This occurs when the bulk lifetime is so short that the corresponding diffusion length does not exceed the penetration depth of the exciting laser pulse or when the surface recombination velocity is negligibly small. In the first case, all the excess carriers have been recombined in the bulk before reaching the front or back surface of the silicon wafer. The second case is due to the elimination of the surface recombination, which can only be achieved by very high quality silicon dioxide passivation that can be obtained by thermal dry oxidation process at high temperatures. Unfortunately, high temperature processing changes the properties of the silicon wafer and the measured lifetime is not anymore the original bulk lifetime.

One way to measure lifetimes that give higher diffusion lengths than sample thickness is to passivate wafer surfaces chemically. In practice, during the PCD measurement the wafer is placed in a plastic envelope containing a passivation solution. Iodine in ethanol and HF are commonly used chemical passivators that keep silicon surfaces terminated by hydrogen. Drawback of the chemical passivation concept is the questionable stability and reproducibility of this passivation method. Additionally, it can be inconvenient to return the chemically passivated samples back to a process having high temperature treatments.

In a lifetime mapping measurement systems, conductivity transient is usually detected by measuring the reflection of microwave signal. Resistivity of the silicon wafer must then be more than 1  $\Omega$ \*cm before PCD measurement can be carried out by

commercially available equipment's. This serious drawback of the PCD method is due to the detection limits of available microwave antennas and the finite power of exciting laser pulse.

### 3.2 Surface Photovoltage measurement

Solar cell substrates have often lower resistivity than 1  $\Omega$ \*cm. In these cases, PCD measurements produce lifetime maps which are corrupted by noise because the amplitude of the conductivity transient is below the detection limit of the measurement system. In contrast to PCD measurements, Surface Photovoltage (SPV) is a steady state method which allows the measurement of low resistivity samples.

SPV measurement directly gives a value for the diffusion length. The difference between injection levels in PCD and SPV are around five to six orders of magnitude. Many metallic impurities in silicon show some characteristic illumination level behavior. Therefore the comparison of measurement data obtained by both of these two methods may give valuable information of the origin of the contamination in solar cells.

If the silicon wafer is continuously illuminated with monochromatic light having energy larger than band gap, the charge carriers that have diffused to the illuminated surface are separated by space charge region which is present close to the wafers surface. The separated carriers create a surface potential  $V_{SPV}$  which is within certain limits linearly proportional to the number of the excess carriers at the space charge regions edge. The number of the excess carriers at the space charge regions edge can be solved from the one dimensional continuity equation

$$D\frac{d^2\Delta n(x)}{dx^2} - \frac{\Delta n(x)}{\tau} + G(x) = 0 \quad , \tag{32}$$

with the boundary conditions determined by surface recombination

$$\frac{d\Delta n(x)}{dx} = s_1 \frac{\Delta n(0)}{D} \qquad \text{at } x = 0$$

$$\frac{d\Delta n(x)}{dx} = -s_2 \frac{\Delta n(t)}{D} \qquad \text{at } x = t \qquad .$$

(33)

The generation rate depends on the photon flux of the incident light, the reflectance of the wafer surface and the wavelength of the light. It is a good assumption that every photon creates an electron -hole pair. Generation rate in terms of position x and wavelength  $\lambda$  is then given by

$$G(x,\lambda) = \Phi(\lambda)\alpha(\lambda)[1-R]e^{-\alpha(\lambda)x} \qquad , \tag{34}$$

where  $\Phi(\lambda)$  is the flux of the incident light. The solution of Eq. 31 with the given boundary conditions is

$$\Delta n(x) = \frac{(1-R)\Phi\alpha\tau}{(\alpha^2 L^2 - 1)} \left[ \frac{A_1}{D_1} + e^{-\alpha t} \frac{B_1}{D_1} - e^{-\alpha t} \right] , \qquad (35)$$

where

$$A_{1} = \left(\frac{s_{1}s_{2}L}{D} + s_{2}\alpha L\right) \sinh\left[\frac{t-x}{L}\right] + (s_{1} + \alpha D) \cosh\left[\frac{t-x}{L}\right]$$

$$B_{1} = \left(\frac{s_{1}s_{2}L}{D} - s_{1}\alpha L\right) \sinh\left[\frac{x}{L}\right] + (s_{2} - \alpha D) \cosh\left[\frac{x}{L}\right]$$

(36)

$$D_{1} = \left(\frac{s_{1}s_{2}L}{D} + \frac{D}{L}\right) \sinh\left[\frac{t}{L}\right] + (s_{1} + s_{2}) \cosh\left[\frac{t}{L}\right]$$

The Eq. (35) is non-linear and therefore quite impractical for extraction of diffusion length. However, in order to make successful estimations of the diffusion length only a linear relationship between the surface photovoltage and the number of excited charge carriers at the edge of the surface space charge region need to be known. In this analysis, diffusion length is assumed to be smaller than wafer thickness, and exciting wavelength is chosen in such a way that the photons are not absorbed within the surface space charge region nor near of the back side of the wafer. With these assumptions quite complicated Eq. (35) can be simplified and a linear relationship between surface photovoltage and carrier concentration can be found.

$$V_{SPV} = C_1 \frac{(1 - R)\Phi L_n}{(s_1 + \frac{D_n}{L_n})(L_n + \frac{1}{\alpha})},$$

(37)

where  $C_I$  is a constant. Equation (37) is valid for quite restricted values of  $V_{SPV}$ . Linear relationship between the photon flux and surface photovoltage needs to be examined separately for every sample.

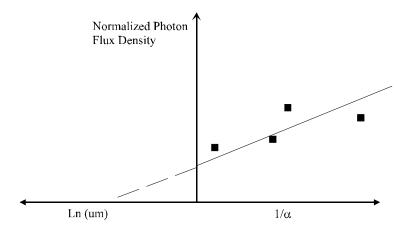

Surface photovoltage is a steady state measurement method. During one SPV measurement, the surface voltage is kept constant which leaves the photon flux and absorption coefficient to be the only variables in Eq. 38.

$$\Phi = C_2 \left( L + \frac{1}{\alpha} \right) \tag{38}$$

where  $C_2$  is a constant. When the sample is illuminated by at least two monochromatic light sources while the surface voltage is kept constant, the diffusion length can be extracted from interception of the x-axis of the photon flux -absorption coefficient graph as shown in Fig. 7.

**Figure 7.**Principle of diffusion length extraction by four laser SPV measurement.

If the resistivity of the sample is known, the minority carrier lifetime can easily be calculated from the measurement data.

# 4. Efficiency losses

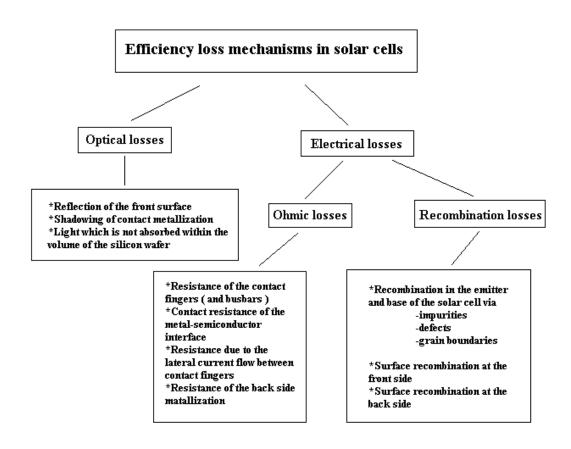

In order to experimentally demonstrate high efficiency devices, optical and electrical losses in silicon material need to be minimized by using semiconductor processing technologies available. Schematic presentation of the relevant loss mechanism in solar cells is presented in Figure 8.

Figure 8

Different loss mechanisms in a solar cell [5].

Optical losses in silicon solar cells consist of reflection of light at the front surface of the solar cell and finite ability of silicon to utilize the radiation spectrum of sunlight. The latter is caused by the fact that photons having lower energy than silicon's band gap

basically pass through the solar cell. Threshold wavelength of the photons to be absorbed is 1107 nm.

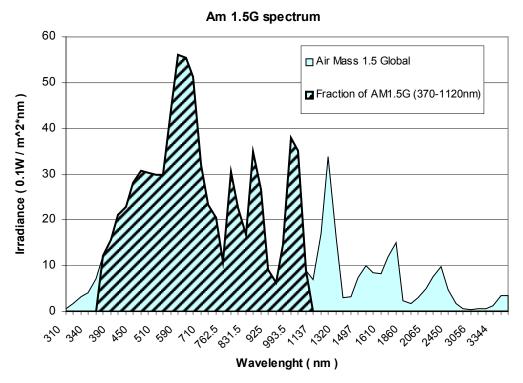

**Figure 9.**AM1.5 Global spectrum. The portion of the light that silicon solar cells are able to convert into electricity is dashed.

Some absorption may also take place at longer wavelengths but its contribution to the output current is negligibly small. Generation of electron –hole pairs by light having an energy lower than the band gap requires energy levels to be present between the conduction and valence bands. Although such levels usually exist in large densities in non –ideal solar cells, the charge collection properties are so degraded in these cases badly that sub band gap generation cannot be measured electrically.

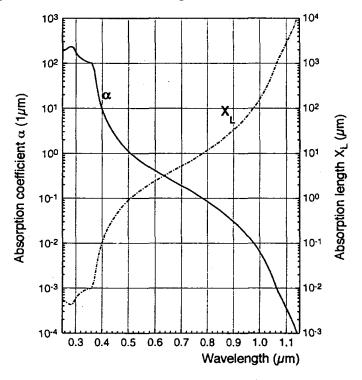

The lowest usable wavelength of light for silicon solar cells is about 350-370nm. The lower limit is set by the fact that short wavelength photons are absorbed very close to the front surface. As shown in Figure 10, the absorption length, reciprocal of the absorption coefficient, is only about 10nm for photons at 370nm. Instead of excited

carrier pair collection, recombination to the surface states is a more likely process this close to the front surface. Additionally, the reflectance of the silicon surface starts to increase sharply towards the short wavelengths.

**Figure 10.**The absorption coefficient of the silicon according to the Reference [6]

Reflection losses can be minimized by using an anti –reflection coating and by etching to the flat wafer surface objects that scatter the incident light. Electrical losses in solar cells occur basically in metal contacts and by recombination. The solar cell is a high current density device and therefore great deal of output power can be lost by resistive losses in the front contact fingers. Recombination in solar cells occurs in bulk (inside the silicon wafer) or at the front and back surfaces. Bulk and surface recombination reduce the number of light generated charge carriers which are meant to be collected by the electrical contacts. Therefore, in order to create as high an output current as possible, recombination in the bulk and at the surfaces need to be eliminated effectively. Processing techniques used to minimize losses in pn –junction mc-Si solar cells are described in detail in the following chapters, together with their limitations.

## 5. Multicrystalline silicon

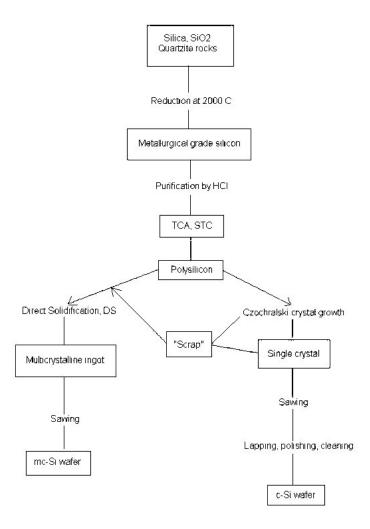

Multicrystalline silicon (mc-Si) wafers consist of single crystalline grains having different crystallographic orientations separated by grain boundaries. Approximately one third of the commercial photovoltaic cells are made of mc –Si [9]. Mc –Si has been predicted in many contents to become the dominant substrate material in the future. That is mainly due to significantly lower price of the mc-Si compared to the single crystalline material. Availability of solar grade silicon may also play a crucial role in the future because the markets of photovoltaic energy systems have been predicted to grow more than 20% annually. Solar grade silicon has been traditionally fabricated from the "scrap" of the electronics grade silicon. In order to meet the frequently presented predictions about solar cell production, there is simply not enough available waste silicon from the microelectronics industry.

The raw material of the mc –Si and single crystalline silicon (c-Si) is basically similar, semiconductor –grade polysilicon which costs approximately 14-15 USD / kg in 1999 [10]. Mc –Si wafers of 100 cm² typically cost about ten times less than four inch wafers manufactured by the Czochralski method. The cost reduction of mc –Si wafers is obtained by direct solidification (DS) process which is simply block casting of polysilicon to a quartz crucible. This method is naturally less expensive than Czochralski ingot pulling.

**Figure 11.** Photograph of multicrystalline silicon blocks.

A desired property of the multicrystalline block is a grain size as large as possible. Commercially available mc –Si wafers consist of grains that usually are two orders of magnitude larger than average minority carrier diffusion lengths in grains. The multicrystalline silicon blocks are cut by wire saw to wafers having thickness of about 300µm. In addition to simple fabrication process, the low price of mc –Si wafers is consequence of fact that the solar cell substrates do not need to be polished. Schematic flow chart of mc-Si and Cz-Si wafer processes are shown in Fig 12.

**Figure 12.**Simple process flow chart of the fabrication sequence of solar cells substrates and silicon wafers used for microelectronics [11].

The cost reduction of the starting material is obtained at the cost of material quality which has a strong influence on the electrical characteristics of the solar cells. Concentrations of different impurities in multicrystalline materials are much higher than in Czochralski silicon, because almost all of the polysilicon raw material, including its impurities, is transferred to block casts during the solidification. In contrast to direct solidification, Czochralski process utilizes the advantageous property of silicon melt enrichment through the impurity segregation during the ingot pulling process. Example of lifetime distribution in a multicrystalline silicon block is shown in Figure 13.

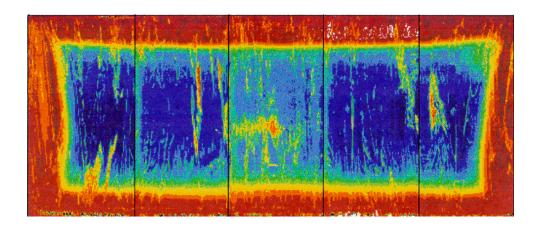

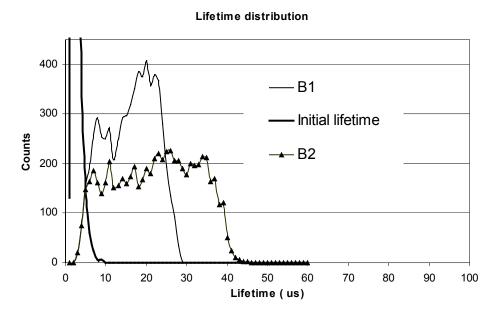

**Figure 13.**Example of lifetime distribution in silicon block cast. Picture is from application notes of Semilab R.T.

It can clearly be seen in Fig 13. that lower lifetime regions are found near the edges of the ingot. It is obvious that the defected outer edge of the ingot is the result of interaction between quartz crucible and silicon melt during the solidification. Prior to wafering, the edge regions are typically removed from the ingot which naturally means lower process yield. Therefore the optimization of the DS thermal budget and crucible design are subject of intensive research [11].

Solar cell substrates are boron doped with resistivity of typically 0,5 – 1,0  $\Omega$ \*cm which corresponds to doping density of about  $10^{16}$  cm<sup>-3</sup>. Value of base resistivity is a

trade off between diffusion length and open circuit voltage and typically needs to be optimized for each fabrication process. The open circuit voltage increases with decreasing base resistivity whereas the lifetime tend to decrease drastically when doping density exceeds  $10^{16}~\rm cm^{-3}$ . In low cost production of solar cells, the processing is not carried out in clean rooms and consumption of wet chemicals used for substrate cleaning is minimized. In such an environment, long diffusion lengths cannot be achieved and therefore the process is optimized to maximize the open circuit voltage by employing heavy emitter doping and low base resistivity.

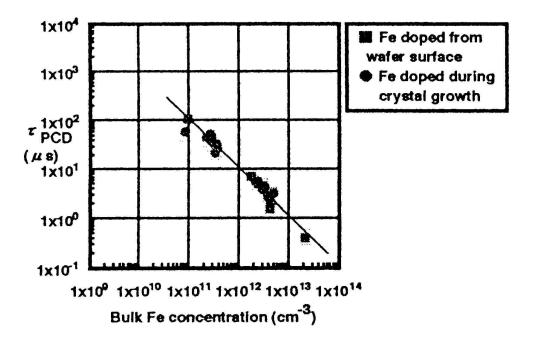

Average  $\mu$ PCD lifetime in non –processed mc-Si wafers is typically about 5 $\mu$ s which corresponds to about 70 $\mu$ m in diffusion length. Iron has been commonly recognized to be a lifetime dominant metallic contaminant in solar grade silicon. The relationship between iron concentration and bulk lifetime has been extensively studied. A widely accepted experimental relationship between iron concentration and minority carrier lifetime is presented in Figure 14 [12].

Figure 14. Experimentally found relationship between iron concentration and  $\mu PCD$  lifetime.  $10^{11} cm^{-3}$  is the lowest limit of intentionally introduced iron contamination. Therefore, the influence of iron to long lifetimes remains therefore to some extent unclear.

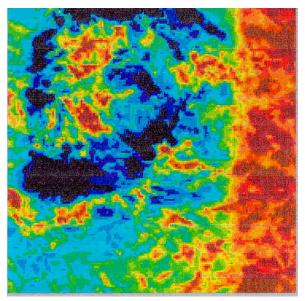

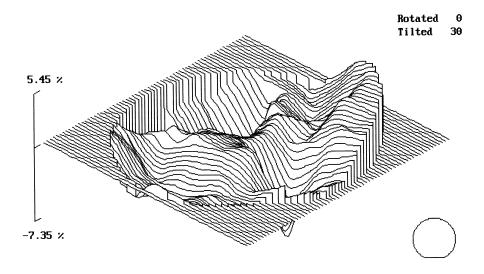

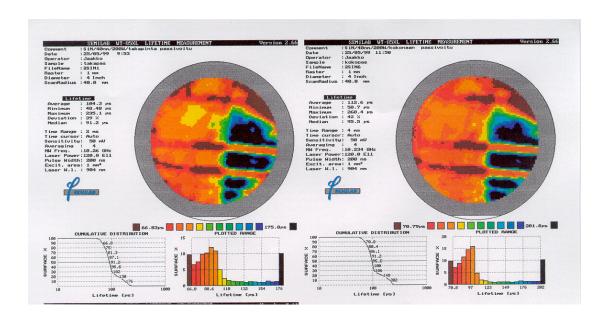

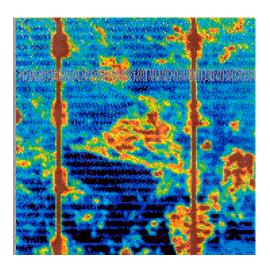

Typical  $\mu$ PCD lifetime map of a non –processed mc –Si wafer is shown in Figure 15. This particular wafer has been wire sawed so that the DS process induced crucible contamination is apparent in the right edge of the wafer.

Figure 15.

$\mu PCD$  lifetime map of a non –processed Scanwafer mc –Si wafer. Lifetime in the contaminated areas are about  $1\mu s$  which, according to the graph in Figure 14., corresponds to iron concentration exceeding  $10^{13}$  cm<sup>-3</sup>.

Iron is present in p-type silicon in two forms. It can be paired with boron atom or it can be present in an interstitial place in the silicon lattice. The latter form is metastable because iron tends to form Fe –B pairs even at room temperature. Iron boron pair limited minority carrier lifetime has been reported to be only slightly dependent on injection level compared to other metallic contaminants.

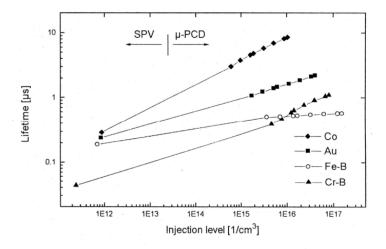

**Figure 16.**Injection level dependence for different contaminants, according to reference [14]

Injection level dependence similar to Fe-B pairs presented in Figure 17 is found from SPV and  $\mu$ PCD measurements carried out for the mc-Si wafers used for solar cell processing.

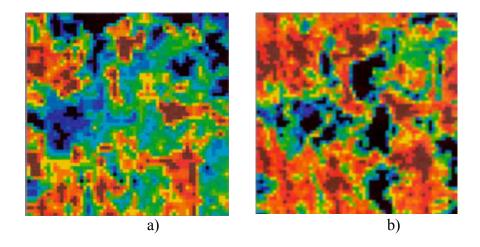

Figure 17. SPV lifetime map of an unprocessed mc-Si wafer a) and  $\mu PCD$  map of the same wafer. Average lifetime in the SPV map is 0,9  $\mu s$  and in the  $\mu PCD$  chart 4,6  $\mu s$ . The wafer resistivity is about 1  $\Omega^*cm$ . Therefore the  $\mu PCD$  measurement has been carried out at highest possible injection level

in order to achieve an acceptable signal to noise ratio of the reflected microwave signal.

The measurement results presented in the above figure support strongly the conclusion that the dominant lifetime killer in solar cell substrates is iron.

It is evident that high conversion efficiency cannot be obtained if the diffusion length in the solar cell is less than 100μm. Lifetime can be improved by correct device processing. This technique is called gettering which means removing the unwanted impurities to non -active device regions or outside the substrate. It is well known that a heavily phosphorous doped layer works as a sink for many metallic impurities in silicon. At high temperatures metallic impurities diffuse fast in the silicon lattice, but very slowly in the phosphorous doped regions. Therefore during the emitter diffusion process unwanted lifetime killers are effectively collected to the emitter region and an increase in bulk lifetime can be observed by μPCD or SPV measurements.

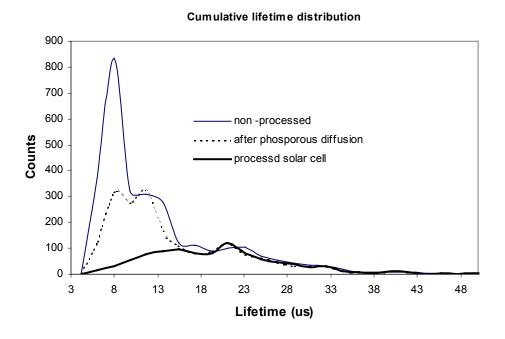

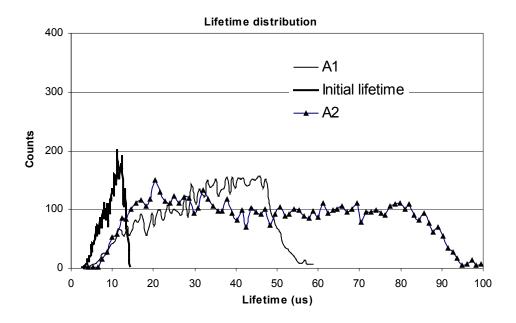

**Figure 18.** Cumulative lifetime distributions in mc-Si material after different processing steps. Average minority carrier lifetime after processing (  $n^+$ -diffusion, PECVD silicon nitride deposition, sputtering and aluminum sintering ) is about 20 $\mu$ s which corresponds to a diffusion length equal or higher than the thickness of the solar cell.

## 6. Wafer cleaning and wet etching

In order to obtain a high conversion efficiency, minority carrier lifetime in multicrystalline silicon wafers must be as high as possible. Bulk lifetime in starting wafers varies typically from 1µs to 10µs which correspond to diffusion lengths less than the solar cells thickness. With correct device processing, however, lifetime can be increased by an order of magnitude, which is mainly due to the phosphorous and aluminum gettering that automatically occur during the processing. Lifetime improvement is directly related to the reduction of metallic impurities in silicon. Concentration of iron in solar grade mc –Si is typically  $10^{11} - 10^{13}$  atoms per cubic centimeter. In other words, less than one part per billion. It is obvious that when processing solar cells having a high minority carrier lifetime, extreme cleanliness must be maintained throughout the device processing. Annual worldwide production of silicon wafers was estimated to be about 10 000 tons in 1992 [15]. For example, one metal coin would therefore contain enough impurity atoms to contaminate the whole of world's silicon production for one year.

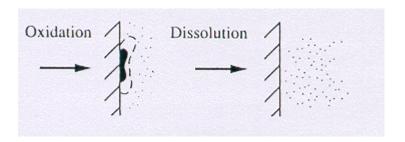

The fabrication process described in this thesis has two high temperature furnace steps, emitter diffusion and aluminum drive –in . Minority carrier lifetime can basically be degraded during only these two process steps which are carried out at the temperature high enough for diffusion of solid substances into silicon. Possible sources of unwanted impurities are naturally numerous, e.g. process equipment, chemicals, DI water, wafer carriers and wafer handling tools. During device processing, wafer contamination can never be totally avoided, and proper cleaning process needs to be implemented prior to the furnace steps. In the fabrication process of mc-Si solar cells, there are three different mechanism used for wafer cleaning: chemical dissolution of metallic impurities, chemical oxidation of silicon followed by oxide removal and wet etching of silicon.

The first process step is the anisotropic wet etching of *as -cut* mc-Si wafers. After wafering of mc -Si block cast, a damage etching needs to be carried out in order to remove crystallographic damages which are produced by the wafer saw. Sawing damages can be as deep as 10µm, and if they are not removed, this results a significant leakage current. Surface of the wafer is also contaminated by oil and metallic residuals from the

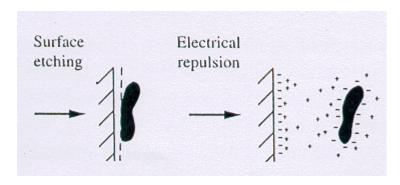

wafer saw. Sawing damages, as well as contamination, can effectively be removed simply by etching enough silicon from both surfaces. During the alkaline etching, OH ions provide a significant negative charge to the silicon surface. Cleaning of the wafer occurs when particles are removed from the surface electrostatically. The principle is illustrated in Figure 19.

**Figure 19.**The principle of particle removal during alkaline etching. Picture is from Reference [16].

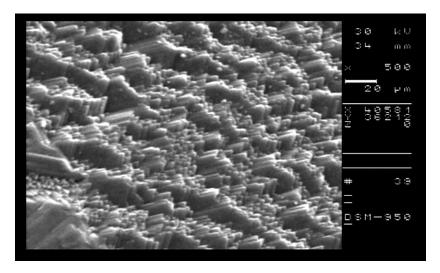

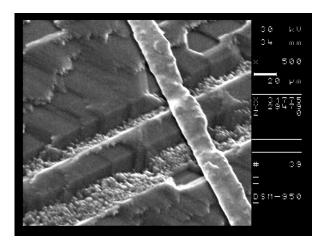

Damage etching has been carried out by a weak alkaline solution. The etching recipe has been developed by Fortum Surface Chemistry and it is based on NaOH –isopropanol – DI water solution. In this etching procedure only a few micrometers of silicon is removed from the wafer surfaces at a relatively low etching rate. This results in randomized pyramids to be created in the grains which have (100) or (111) crystal orientations. About 30 - 40 % of the wafer surface becomes effectively textured. SEM picture of randomized pyramids created by NaOH texturation is shown in Figure 20.

**Figure 20.**NaOH wet etch textured mc-Si surface.

In addition to surface texturation, significant cost savings are obtained if an alkaline damage etch is used instead of an acidic etch. Solution containing HF , HNO<sub>3</sub> and CH<sub>3</sub>COOH is usually called as "acid etchant". Acid etchant planarizes the silicon surface and it generally results in lower surface recombination velocities, but unfortunately it is also about ten times more expensive than alkaline based solutions [17].

After the damage etch and prior to the emitter diffusion mc-Si wafers need to be cleaned, because the sodium containing etch solution is an extremely harmful contaminant itself. Sodium is a slow diffusant in silicon and silicon dioxide if compared to trace metals (Cu, Ni, Cr, Zn, Au etc). It means that in addition to reduced lifetime, once the alkaline metals have entered for example into the quartz parts of the diffusion system they are difficult to get rid of by any cleaning or gettering process. A RCA cleaning process is carried out on regular basis before the first high temperature process step in order to remove alkaline residuals left from the damage etching as well as trace metals which are probably still present in harmful quantities on the wafer surface. RCA cleaning, also known as Standard Cleaning (SC), has been widely used in semiconductor industry for more than twenty years. RCA cleaning consists of three steps and it is carried out in the heated quartz containers. There are many versions of RCA cleaning. The following recipe has been used at the Electron Physics Laboratory.

#### **RCA 1:**

6 l DI water

1,2 1 NH<sub>4</sub>OH

$1,21 H_2 O_2$

$80^{0}$ C / 10min

DI water rinse 10min

### HF-dip:

3.5 l DI-water

70 ml HF (aqueous 50%)

RT / 30s

DI water rinse 10min

#### **RCA 2:**

6,2 1 DI water

1,1 1 HCl

$1,11H_2O_2$

$80^{0}$ C / 15min

DI water rinse 10min

RCA 1 clean removes organic contamination and dissolves particles by chemical oxidation of the silicon. It is important to remove any organic contamination in the beginning of the cleaning cycle, because some types of organic contamination cause incomplete oxidation of silicon and therefore lead to partial contamination. In a RCA 1 bath, hydrogen peroxide acts as an oxidizing agent and OH<sup>-</sup> ions from NH<sub>4</sub>OH leave a negative surface charge which repulses particles [18]. Some ion exchange processes between metals and ammonia can also take place during RCA 1. For example, RCA 1 has

been reported to remove copper contamination effectively [19]. The principle of the particle removal by chemical oxidation is presented in Figure 21.

**Figure 21.**Particle removal by chemical oxidation.

Next, chemical oxide formed during RCA 1 is removed by a short HF dip. After rinsing in DI water, the wafers are placed in RCA 2 bath. Cleaning mechanism of RCA 2 is based on Cl<sup>-</sup> ions which form volatile metal chlorides that are desorbed from the wafer surface

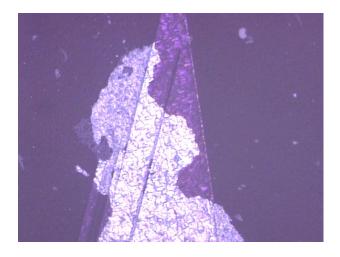

After cleaning, the wafers are ready for emitter diffusion which is described in Chapter 7. Spin –on Dopant (SOD) is basically phosphorous doped silicon dioxide dissolved in liquid, but despite of baking the SOD at 120°C for 30 minutes, all organic solvents that are incorporated into the SOD for adjusting the viscosity are not totally evaporated. During the high temperature treatment, organic residuals adhere strongly to the silicon surface and as a result, the SOD is very difficult to remove after the diffusion. Most of the SOD is first removed by buffered HF (BHF) which is typically aqueous NH<sub>4</sub>F (40%) and HF (49%) with a ratio of 7:1 [16]. Buffered HF removes silicon dioxide at the rate of about 100nm / min, but does not etch any organic residuals. The duration of the BHF treatment depends on the thickness of the SOD layer and flatness of the surface. Removal of spinned SOD from a planar (acid etched) mc-Si surface takes about 10 minutes, whereas sprayed SOD removal from a textured surface may take up to one hour. Optical microscope picture of SOD residuals is shown in Figure 22.

**Figure 22.**Figure of phosphorous glass residuals on mc-Si wafer. Wafer has been coated with silicon nitride in order to make the residuals visible. Glass residuals can be seen as bright areas.

The spin –on glass residuals, presented in the figure above, are unacceptable because they shadow light, prevent contact formation and increase leakage current significantly. RCA 1 clean is an effective method for SOD residual removal, because of its ability to strip away organic contamination. Hydroxide ions, however, provide a negative surface potential which is unfortunately opposite to what is needed for field effect passivation of solar cells. Therefore the SOD removal is finished with a RCA 2 clean.

An alternative method for SOD stripping is oxygen plasma treatment. Plasma stripping can, however, cause some surface damage because of ion bombardment. Glass residuals are typically very undefined structures which may create reproducibility problems in terms of the RIE macro loading effect.

## 7. High temperature processing of solar cells

Fabrication process of multicrystalline silicon solar cells described in this thesis contains two high temperature furnace steps. The first furnace step is carried out in order to create a phosphorous doped emitter and the second one is needed for sintering sputtered aluminum to the back side of solar cells. Emitter diffusion process plays a crucial role determining the conversion efficiency mainly because of the following reasons: first, if the emitter doping is too low, good front ohmic contacts are not formed. This is especially true in the case of screen printed solar cells which require a phosphorous concentration in the emitter region well above of 10<sup>20</sup> cm<sup>-3</sup> to achieve a contact resistance between silicon and thick film paste which is acceptably low. Additionally, an important component of the series resistance of a solar cell is caused by the lateral carrier flow in the emitter region. Naturally it depends on the distance between the contact fingers and on the sheet resistance of the emitter which is in turn a function of the doping concentration and depth of the diffusion. Effects caused by lateral carrier flow in the emitter region are very difficult to predict because of lack of two dimensional modeling tools. Optimization of the emitter diffusion gets even more difficult if the front surface is textured. On the other hand, too high a concentration of phosphorous leads to many unwanted effects, such as an increased photon absorption near the front surface due to band gap narrowing.

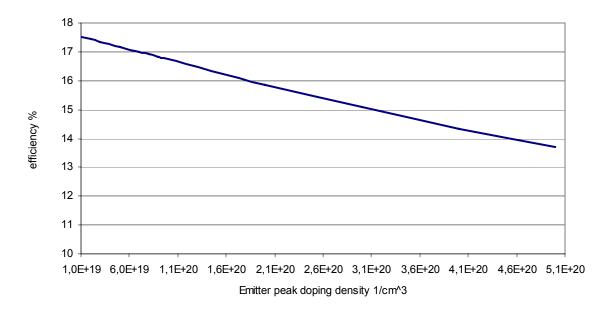

There is in Figure 22. an illustrative example of PC1D simulation showing a linear relationship between the emitter doping density and the conversion efficiency. Efficiency is higher at lower doping densities because of the decreased minority carrier recombination in the emitter region [20]. In other words, in an emitter having a high sheet resistance, diffusion length of holes exceeds several times the depth of the pn-junction.

Figure 23.

One dimensional simulation of conversion efficiency dependence on emitter doping density.

Increased resistive losses which occur at the lower doping densities are neglected from this simulation.

Phosphorous atoms can be transported to silicon wafers in gaseous or in liquid phase. Gas phase diffusion is carried out in quartz tube furnaces by leading phosphine or phosphorous oxycloride to the furnace tube. An alternative method is to use solid phosphorous source wafers which are stacked between the silicon wafers. At high temperatures phosphorous is transported to silicon wafers with the help of inert carrier gas. The advantage of gas phase diffusion is the homogeneous doping profile it gives, and the cleanliness of the diffusion sources compared to the liquid phase diffusion. In a tube furnace, filled with a gas containing phosphorous, doping takes place on both sides of the wafers resulting in a parasitic npn –structure. Parasitic junction on the back side of the solar cell can be tolerated under some circumstances. First, an appropriate edge isolation needs to be applied in order to prevent the pn –junction to be shunted to the back contact of the solar cell. Edge isolation can be carried out simultaneously for a large number of

solar cells by plasma etching. Solar cells are stacked tightly against each other in a vacuum chamber, and a couple of micrometers of silicon is etched in fluorine containing plasma. The parasitic pn –junction on the back side is punched through by sintering or alloying aluminum. There is currently at least one commercial manufacturer who uses a fabrication process based on combination of gas phase diffusion of both sides of the solar cells and edge isolation [21]. Floating junction passivation of the rear side of the solar cell is a novel application of parasitic phosphorous diffusion. However, this concept requires photolithography and is therefore excluded from commercial production. A detailed description of this device concept is given in Reference [22]

In the scope of processing low cost photovoltaic devices, use of liquid phase dopant sources is more common than gas phase diffusion. All of the solar cells described in this thesis have been diffused by using Spin-on –Dopant (SOD) sources. Diffusion of solid material in silicon lattice can be described by one dimensional differential equation which is known as Fick's second law.

$$\frac{\partial N(x,t)}{\partial t} = D \frac{\partial^2 N(x,t)}{\partial x^2} \tag{39}$$

Where N(x,t) is the concentration of the diffusion as a function of time and position, and D is the diffusion constant which depends strongly on temperature and to some extent on the concentration of diffusing species.

$$D = D_0 e^{-\frac{E_a}{kT}} \tag{40}$$

Where  $E_a$  is the activation energy and  $D_0$  is a constant.  $D_0$  and  $E_a$  are characteristic for each diffusing species and host material. Since the dopant source in the case of mc-Si solar cells is a relatively thick phosphorous doped silicon dioxide glass layer, the surface concentration of phosphorous,  $N_s$  can be assumed to be constant during the diffusion. In this case, the solution of Fick's second law takes the following form.

$$N(x,t) = N_s \left( 1 - \frac{2}{\sqrt{\pi}} \int_0^{\frac{x}{2\sqrt{Dt}}} e^{-\alpha^2} d\alpha \right)$$

(41)

The bracketed expression above is the so called complementary error function and it can be appreviated by letters.

$$N(x,t) = N_s erfc \frac{x}{2\sqrt{Dt}}$$

(42)

In practical case, however, phosphorous diffusion does not follow this simple model accurately. This phenomena has been extensively studied and it has been explained to be a consequence of concentration dependence of the diffusion coefficient. With high phosphorous concentrations, the diffusion coefficient increases rapidly [23].

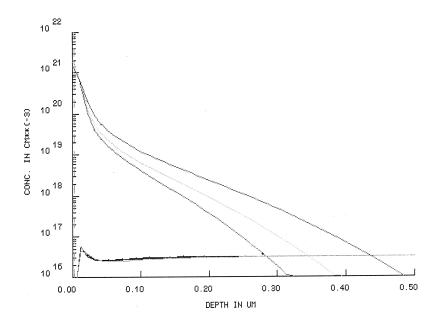

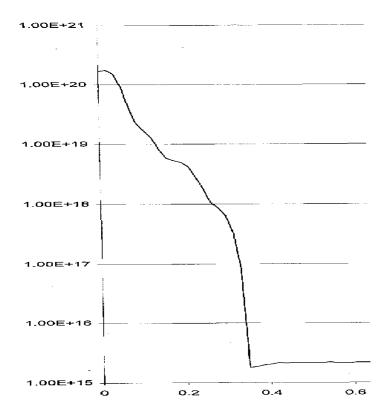

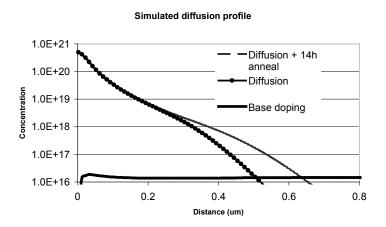

Emitter diffusion with SOD is carried out in the temperature range from  $840^{0}$ C to  $870^{0}$ C. Sheet resistivities of the mc-Si solar cells are typically varied from  $30 \Omega$ / sqr to  $100 \Omega$ / sqr, yielding diffusion times at the peak temperature from  $30 \min$  to  $60 \min$ . Figure 23 shows simulated (ICECREM process simulator) diffusion profiles of typical solar cells emitters.

**Figure 24.**Simulated diffusion profiles when a diffusion source has been a  $10^{21}$  cm<sup>-3</sup> phosphorous doped silicon dioxide film. Curves represent from left to right  $840^{0}$ C / 35min ,  $840^{0}$ C / 60min and  $870^{0}$ C / 60min. Simulated thermal cycle starts at  $750^{0}$ C and it is followed by a ramp up with a rate of  $15^{0}$ C / min. Cooling is simulated to occur at a rate of  $5^{0}$ C / min.

The spin –on dopant used in this process has been supplied by Filmtronics Inc. The concentration of phosphorous in SOD (product code P509) is 2,0 \*10<sup>21</sup> cm<sup>-3</sup>. Prior to the diffusion SOD is spinned or sprayed on the RCA cleaned mc –Si wafers. Spraying is the preferred deposition method because of better step coverage on textured wafers. It is also very difficult to spin films on the square substrates without special equipment. Some portion of the rear of the wafer tend to be coated while corners on the front side may remain partially uncoated resulting a leaking pn –junction. Harmful drawback of the spray technique is the slightly acidic nature of the SOD which may corrode metallic parts of the spray equipment. After SOD coating wafers are baked in an air convection oven for 30min at 120<sup>0</sup>C. During the baking, liquid solvents in SOD are evaporated and SOD takes the form of a solid film. The temperature profiles of the furnace recipes used in this work are summarized in Table 2.

**Table 2.**The diffusion profiles and corresponding recipe names used in this work.

| Diffusion/Al-                                           | Push in T      | Ramp up rate.  | Peak T | Ramp down rate                                                                         | Pull out T     |

|---------------------------------------------------------|----------------|----------------|--------|----------------------------------------------------------------------------------------|----------------|

| sintering recipes                                       | <sup>0</sup> С | <sup>0</sup> С | °C     | <sup>0</sup> C/min                                                                     | <sup>0</sup> C |

| D2GET                                                   | 750            | 8              | 860    | 1) $2^{0}C/min(\rightarrow 800^{0} C)$<br>2) $1^{0}C/min(\rightarrow 700^{0} C)$       | 700            |

| D3GET                                                   | 750            | 8              | 850    | 3) $2^{0}C/min(\rightarrow 800^{0}$<br>C)<br>4) $1^{0}C/min(\rightarrow 700^{0}$<br>C) | 700            |

| D4GET                                                   | 750            | 8              | 870    | 5) $2^{0}C/min(\rightarrow 800^{0}$<br>C)<br>6) $1^{0}C/min(\rightarrow 700^{0}$<br>C) | 700            |

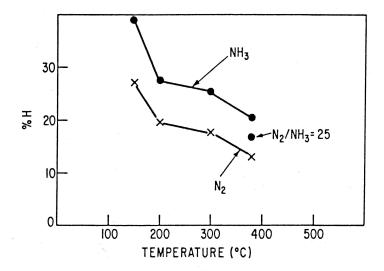

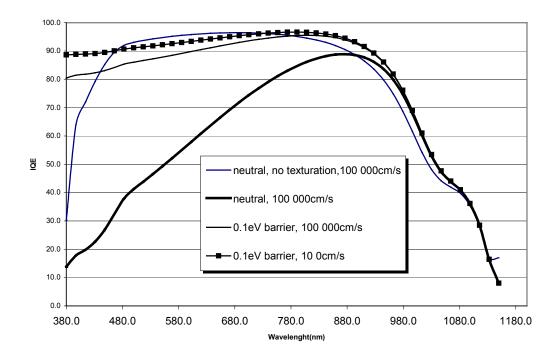

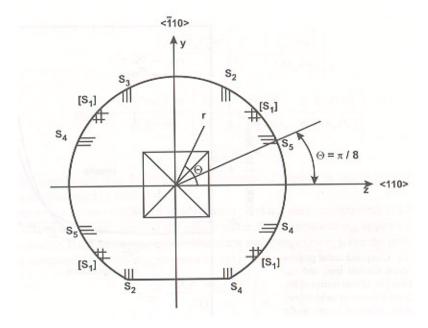

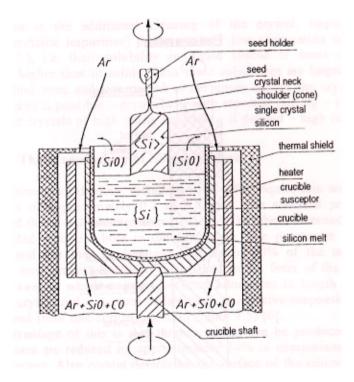

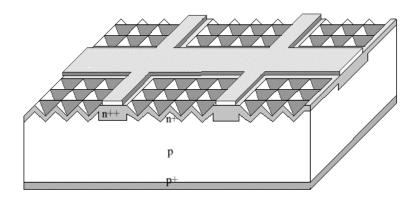

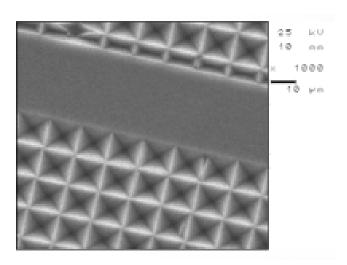

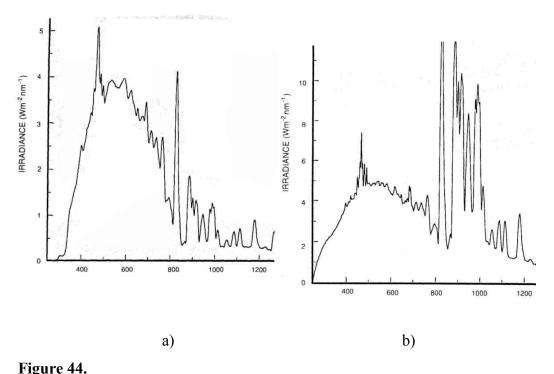

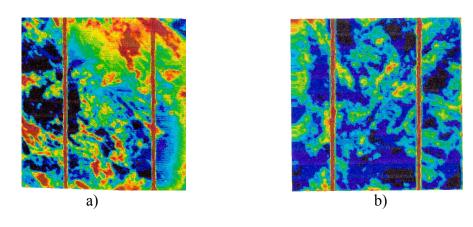

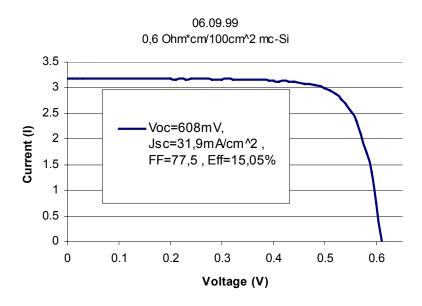

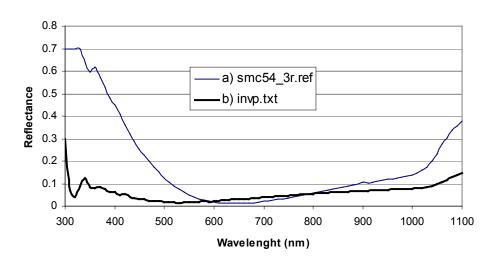

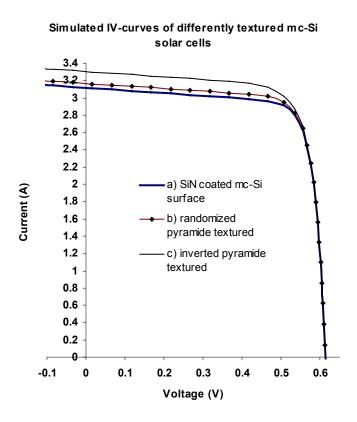

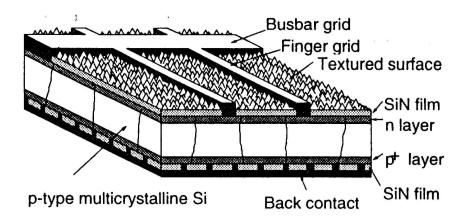

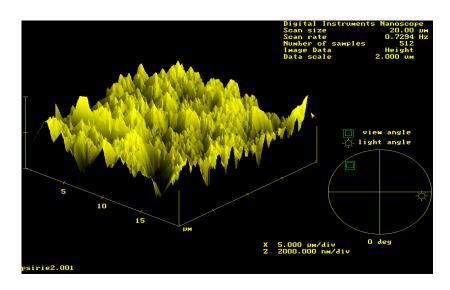

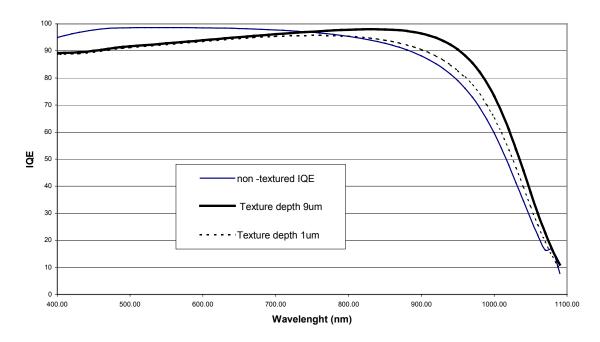

| DTUULI                                                  | 750            | 8              | 820    | 7) $3^{0}C/min(\rightarrow 800^{0}$<br>C)<br>8) $2^{0}C/min(\rightarrow 700^{0}$<br>C) | 700            |