Helsinki University of Technology Laboratory for Theoretical Computer Science Research Reports 71 Teknillisen korkeakoulun tietojenkäsittelyteorian laboratorion tutkimusraportti 71 Espoo 2002 HUT-TCS-A71

# COMBINING SYMBOLIC AND PARTIAL ORDER METHODS FOR MODEL CHECKING 1-SAFE PETRI NETS

Keijo Heljanko

TEKNILLINEN KORKEAKOULU TEKNISKA HÖGSKOLAN HELSINKI UNIVERSITY OF TECHNOLOGY TECHNISCHE UNIVERSITÄT HELSINKI UNIVERSITE DE TECHNOLOGIE D'HELSINKI

Helsinki University of Technology Laboratory for Theoretical Computer Science Research Reports 71 Teknillisen korkeakoulun tietojenkäsittelyteorian laboratorion tutkimusraportti 71 Espoo 2002 HUT-TCS-A71

## COMBINING SYMBOLIC AND PARTIAL ORDER METHODS FOR MODEL CHECKING 1-SAFE PETRI NETS

### Keijo Heljanko

Dissertation for the degree of Doctor of Science in Technology to be presented with due permission of the Department of Computer Science and Engineering, for public examination and debate in Auditorium T2 at Helsinki University of Technology (HUT CS building, Espoo, Finland) on the 22nd of March, 2002, at 12 noon.

Helsinki University of Technology Department of Computer Science and Engineering Laboratory for Theoretical Computer Science

Teknillinen korkeakoulu Tietotekniikan osasto Tietojenkäsittelyteorian laboratorio Distribution: Helsinki University of Technology Laboratory for Theoretical Computer Science P.O.Box 5400 FIN-02015 HUT Tel. +358-0-451 1 Fax. +358-0-451 3369 E-mail: lab@tcs.hut.fi

© Keijo Heljanko Original publications © IOS Press, Springer-Verlag

ISBN 951-22-5886-2 ISSN 1457-7615

Picaset Oy Helsinki 2002 **ABSTRACT:** In this work, methods are presented for model checking finite state asynchronous systems, more specifically 1-safe Petri nets, with the aim of alleviating the state explosion problem. Symbolic model checking techniques are used, combined with two partial order semantics known as net unfoldings and processes.

We start with net unfoldings and study deadlock and reachability checking problems, using complete finite prefixes of net unfoldings introduced by McMillan. It is shown how these problems can be translated compactly into the problem of finding a stable model of a logic program. This combined with an efficient procedure for finding stable models of a logic program, the Smodels system, provides the basis of a prefix based model checking procedure for deadlock and reachability properties, which is competitive with previously published procedures using prefixes.

This work shows that, if the only thing one can assume from a prefix is that it is complete, nested reachability properties are relatively hard. Namely, for several widely used temporal logics which can express a violation of a certain fixed safety property, model checking is PSPACE-complete in the size of the complete finite prefix.

A model checking approach is devised for the linear temporal logic LTL-X using complete finite prefixes. The approach makes the complete finite prefix generation formula specific, and the prefix completeness notion application specific. Using these ideas, an LTL-X model checker has been implemented as a variant of a prefix generation algorithm.

The use of bounded model checking for asynchronous systems is studied. A method to express the process semantics of a 1-safe Petri net in symbolic form as a set of satisfying truth assignments of a constrained Boolean circuit is presented. In the experiments the BCSat system is used as a circuit satisfiability checker. Another contribution employs logic programs with stable model semantics to develop a new linear size bounded LTL-X model checking translation that can be used with step semantics of 1-safe Petri nets.

**KEYWORDS:** Verification, Model Checking, Petri nets, Complete Finite Prefixes, Partial Order Methods, Symbolic Methods, Bounded Model Checking

### CONTENTS

| Pro                  | eface                                                                                       | 1                     |

|----------------------|---------------------------------------------------------------------------------------------|-----------------------|

| List of Publications |                                                                                             | 2                     |

| 1                    | Introduction 1.1 Contributions                                                              | <b>4</b><br>8         |

| 2                    | Petri Nets                                                                                  | 10                    |

| 3                    | Net Unfoldings3.1Complete Finite Prefixes                                                   | <b>12</b><br>15       |

| 4                    | Rule-Based Constraint Programming4.1The Smodels System4.2Motivation for Using Stable Models | <b>22</b><br>24<br>25 |

| 5                    | Verification with Prefixes5.1Computational Complexity Issues                                | 28<br>29              |

| 6                    | Bounded Model Checking                                                                      | 32                    |

| 7                    | Conclusions7.1Topics for Further Research                                                   | <b>36</b><br>37       |

| A                    | Corrections and Additions to Publications                                                   | 38                    |

| Re                   | References                                                                                  |                       |

| Or                   | Original Publications                                                                       |                       |

#### PREFACE

This dissertation is the result of studies and research at the Laboratory for Theoretical Computer Science of Helsinki University of Technology from 1997 to 2002. I'm grateful to my supervisor Prof. Ilkka Niemelä, for frequent advice and great support. I'm also grateful to Prof. Emeritus Leo Ojala who deserves a large credit for supervising me until his retirement in the year 2000, and for creating a good research oriented laboratory.

People at the laboratory deserve credit for a good research atmosphere. A list of people to thank would be too long, however, I would like to especially thank Tommi Junttila for his comments on numerous research ideas and issues.

During 1999 and 2000 I visited Prof. Javier Esparza's research group at Technische Universität München for a total of 8 months. I would like to thank for the visit opportunity, as these visits were vital for creating a major part of this dissertation.

My co-authors J. Esparza and I. Niemelä significantly contributed to the joint publications and deserve credit for their excellent work. They also gave me a much needed insight into their fields of expertise.

The following people directly contributed software or examples used in the experiments of this dissertation: Patrik Simons (Smodels), Tommi Junttila (BCSat), Gerard Holzmann (SPIN tool LTL to Büchi automata translator [44]), Frank Wallner (qq tool for synchronizing Petri nets and Büchi automata), Stefan Schwoon (qq tool support), Burkhard Graves and Bernd Grahlmann (C code to read PEP prefix files), Stefan Römer (ERVunfold binaries and example nets), Stephan Melzer (example nets), Claus Schröter (example nets and formulas). I would also like to thank Victor Khomenko for interesting discussions on the net unfolding method.

The work was funded by Helsinki Graduate School on Computer Science and Engineering (HeCSE) and by the Academy of Finland (projects 43963 and 47754). The financial support of the following institutions is gratefully acknowledged: Support Foundation of Helsinki University of Technology, Emil Aaltonen Foundation, Nokia Oyj Foundation, Helsinki University of Technology grant fund, and Foundation of Technology (Tekniikan Edistämissäätiö). The grants of these institutions were of great importance as they made full-time studies and international visits possible.

I would like to thank my parents for their support and encouragement. Last but not least I would like to thank my love Virpi for her love and support.

Otaniemi, February 28th, 2002

Keijo Heljanko

#### LIST OF PUBLICATIONS

The dissertation consists of 6 publications listed below, and a dissertation summary. Publications [P1]-[P4] are on model checking using complete finite prefixes, and [P5]-[P6] are on bounded model checking.

- [P1] K. Heljanko, Using logic programs with stable model semantics to solve deadlock and reachability problems for 1-safe Petri nets, Fundamenta Informaticae, 37(3):247–268, 1999, IOS Press.

- [P2] K. Heljanko, Model checking with finite complete prefixes is PSPACEcomplete, in Proceedings of the 11th International Conference on Concurrency Theory (CONCUR'2000), State College, Pennsylvania, USA, August 2000, volume 1877 of Lecture Notes in Computer Science, pages 108–122, Springer-Verlag.

- [P3] J. Esparza and K. Heljanko, A new unfolding approach to LTL model checking, in Proceedings of 27th International Colloquium on Automata, Languages and Programming (ICALP'2000), Geneva, Switzerland, July 2000, volume 1853 of Lecture Notes in Computer Science, pages 475–486, Springer-Verlag.

- [P4] J. Esparza and K. Heljanko, Implementing LTL model checking with net unfoldings, in Proceedings of the 8th International SPIN Workshop on Model Checking of Software (SPIN'2001), Toronto, Canada, May 2001, volume 2057 of Lecture Notes in Computer Science, pages 37– 56, Springer-Verlag.

- [P5] K. Heljanko, Bounded reachability checking with process semantics, in Proceedings of the 12th International Conference on Concurrency Theory (CONCUR'2001), Aalborg, Denmark, August 2001, volume 2154 of Lecture Notes in Computer Science, pages 218–232, Springer-Verlag.

- [P6] K. Heljanko and I. Niemelä, Bounded LTL model checking with stable models, in Proceedings of the 6th International Conference on Logic Programming and Nonmonotonic Reasoning (LPNMR'2001), Vienna, Austria, September 2001. volume 2173 of Lecture Notes in Artificial Intelligence, pages 200–212, Springer-Verlag.

The current author is the only author of publications [P1], [P2], and [P5].

The publication [**P3**] (as well as the extended version [20]) is co-authored by J. Esparza. The key ideas of the publication [**P3**] were jointly developed while the current author was visiting Technische Universität München. Some key proof ideas on the tableaux side of [20] are due to J. Esparza, whereas the proofs of the used synchronization construction are by current author.

The publication [P4] (as well as the extended version [22]) is co-authored by J. Esparza. The paper was jointly written, with the current author designing the presented algorithms, implementing the unfsmodels prototype tool, and performing the experiments. J. Esparza contributed to simplifying the theory behind the used approach, as well as coming up with simpler proofs in [22].

The publication [P6] is co-authored by I. Niemelä. The basic translation was jointly developed. The current author's contribution is a new succinct LTL translation, implementation of the translations, and the experimental work.

#### **1** INTRODUCTION

It is a widely recognized fact that the complexity of systems containing software or hardware components is increasing at a high rate. Furthermore, we as a society are increasingly more dependent on e.g., the correct functioning of communication infrastructure. Therefore, computer scientists are faced with the problem of designing safety or business critical systems of large complexity.

The traditional way of ensuring the correctness of of such systems has relied on two main techniques of *testing* and *simulation*. However, when the systems contain concurrent and/or reactive components, these techniques frequently do not scale at the rate of the system complexity growth. The use of *computer aided verification* has been suggested as an aid to supplement these methods. These methods are based on the observation that we should use the increasing computational capacity we have at our disposal to ease the design of complex systems.

One of the most promising methods for computer aided verification is *model checking*. The basic principles of model checking were developed in the early 1980's independently by two different groups with the earliest publications being [12, 64]. The basic idea is to model the system of interest so as to allow the generation of a graph that contains the reachable states of the system as nodes and the state transitions between them as edges. When a labeling of the nodes with *atomic propositions* which hold at each state is added, this graph is known as a *Kripke structure* of the system (see e.g., [11]). The specification of the property we are interested in is given by a *temporal logic formula*. After this, one can check with a *model checking algorithm* whether the system meets its specification, i.e., by checking if the Kripke structure of the system is a model of the specification.

The system under model checking can be described in several different ways. In case of synchronous digital hardware the description language is frequently a hardware description language. In the case of asynchronous systems, there is a variety of different formalisms. In this work, a model called (1-safe) Petri nets [15] will be used as a system description formalism. Other choices of asynchronous system models could include process algebras [43, 57], extended finite state machines as supported by the SPIN tool [44], high-level Petri nets as supported by tools like Maria and PROD [53, 73], protocol specification languages such as SDL [45], and various programming languages such as Java [2]. We selected 1-safe Petri nets mainly because of their simplicity and the fact that there is an extensive body of research on their analysis methods. We believe that most of the methods developed in this work can also be applied to other asynchronous system description formalisms.

The use of temporal logics to specify properties of concurrent programs was first suggested by Pnueli in the late 1970's [63]. Several temporal logics can be used as specification languages. Two of the most prominent are the computation tree logic (CTL), and linear temporal logic (LTL); for the semantics of the logics and a discussion of their features see e.g., [11]. This work will concentrate mainly on LTL, particularly on its subset LTL-X, in which the so called *next-time* operator has been removed. The LTL-X logic

is probably the most widely used linear time temporal logic used to specify properties of asynchronous systems.

After the system model is described, and the specifications are developed, model checking is (ideally at least) a fully automated procedure. A model checker will either output that the system corresponds to the specification or that the specified property does not hold. The *executions* of a system are the finite and infinite paths in the Kripke structure that start from some initial state of the system. If the specified property does not hold, the model checker outputs a *counterexample* execution which violates the property. This frequently facilitates in the location of errors. These features have made model checking an appealing alternative for industrial use.

The main obstacle in applying model checking is the *state explosion problem.* For example, if the system is described as a composition of n finite state machines, then the Kripke structure of the system can be of exponential size in the number of components. Some sources of state explosion are concurrency of components mentioned above, and combinatorial explosion due to combinations of different data values in data variables.

In this work, methods for alleviating the state explosion problem in model checking of 1-safe Petri nets are developed. The two main techniques employed in this work are the use of symbolic and partial order methods. There is a large body of work dedicated to making model checking more efficient in different domains; for an overview see e.g., [11, 70].

In symbolic model checking the main idea is to represent the behavior of the system in a symbolic form rather than explicitly constructing a Kripke structure as a graph. There are several variations to symbolic methods. Their common feature is the use of representations of sets of states of the system in implicit form rather than having each global state of a system explicitly represented, e.g., as a node of the Kripke structure.

There are a large number of symbolic methods available. The most wellknown is the use of data structure called ordered binary decision diagrams (OBDDs), which are a canonical form of Boolean functions [9]. The method was developed by McMillan for the verification of synchronous digital circuits [10, 55]. The main idea is to represent the transition relation and sets of reachable states as Boolean functions represented by OBDDs. The OBDDs have efficient algorithms for basic Boolean operations, and are frequently very compact exploiting regularities in the digital circuits to represent large sets of states of synchronous hardware designs very compactly.

Recently, several suggestions have been made to replace OBDDs with methods based on propositional satisfiability (SAT) procedures [1, 6] to further improve the scalability of symbolic model checking. The bounded model checking method was introduced in [6]. The main idea in bounded model checking is to look for counterexamples that are shorter than some fixed length n for a given property. If a counterexample can be found which is at most of length n, the property does not hold for the system. Otherwise the result is inconclusive, and the bound must be increased or proved sufficient to cover all possible counterexamples by other means. The implementation ideas are very similar to procedures used in SAT-based artificial intelligence (AI) planning [47, 59].

It seems that the bounded model checking procedures can currently chal-

lenge OBDD based methods on digital hardware designs both in terms of memory and time required to find counterexamples [7, 8, 13]. The weakness of bounded model checking is that if no counterexample can be found using a bound, the result is in general inconclusive. In certain favorable cases, it can be proved that e.g., all reachable states of a system are reachable within some bound n. In this case the bounded model checking is able to show the non-existence of counterexamples for reachability properties; for more discussion see [6]. Another way of ensuring completeness is to use a SAT procedure inside a "classical" symbolic model checker, as presented in [1, 76], to replace an OBDD based procedure. It has also been observed that the performance of a SAT based procedure is frequently more predictable than the performance of an OBDD based procedure, which depends on the so called variable ordering that can dramatically affect the OBDD sizes during model checking, see e.g., [13]. This variable ordering is frequently hard to generate automatically using heuristics, and generally more human interaction is needed when using OBDDs instead of SAT procedures [13].

Partial order methods are a collection of methods to alleviate the state explosion problem during the verification of asynchronous systems. Most of the communication protocol and software verification work has used some kind of asynchronous system model, in which there are a set of different "modules" in the system that can each operate independently of each other without a global synchronization clock. The modules can communicate with each other through such communication mechanisms as shared variables, message queues, or synchronization primitives. In partial order methods the goal is to use the independence between the modules of the system to alleviate the state explosion problem. This independence arises from the fact that frequently two modules of the system do not interact with each other and e.g., changes made to local variables in two different modules of the system can frequently be executed in any order (or event concurrently) without affecting the outcome (the reached global state of the system). The partial order methods can be divided into two subclasses: partial order reduction and partial order semantics methods.

The first class of partial order methods includes the so called partial order reduction methods, which use the independence between transitions of the system to generate a subset of the Kripke structure of the system, which still preserves the model checking outcome of the specification we are interested in. The methods thus use the independence information to prune the Kripke structure, but still operate on interleaving executions of the system. As noted in Section 10 of [11] this set of methods could be better described as model checking using representatives, since the verification is performed using representative executions from suitably defined (using a notion of independence) equivalence classes of behaviors.<sup>1</sup> Methods of this class include stubborn sets, persistent sets, and ample sets. Also closely related to these methods is the sleep set method. For more information on this class of methods, see e.g., [11, 30, 70, 72].

This work will concentrate on the second subclass of partial order methods

<sup>&</sup>lt;sup>1</sup>Rather than being based on a partial order model of program execution, the methods use commutativity of (some) transitions to generate only part of the Kripke structure. This commutativity might not even arise from concurrency.

which will be referred to as partial order semantics methods. Namely, these methods take a partial order view of the behavior of asynchronous systems. In this view, two concurrent (and thus also independent) events are executed concurrently, and not in any fixed order. There is an order between events that are dependent on each other; however, as noted before, this order need not be a total order, but only a partial one. For Petri nets, there are two main partial order semantics, known as *net unfoldings* and *processes*. Roughly speaking, a net unfolding can be seen as a partial order branching time model of computation, while processes are a linear time view of the partial order behavior of the system.

Net unfoldings were introduced in [58] as a partial order semantics for Petri nets. Intuitively, they can be seen as a partial order version of an infinite computation tree. They were later more extensively researched under the name of branching processes by Engelfriet [16]. McMillan was the first to show how to use net unfoldings as a basis for a verification method [55] for finite state systems. He provided an algorithm to compute a *complete finite prefix* of the unfolding, which contained full information about the behavior of the Petri net system in symbolic form. The finite prefix can sometimes be exponentially more succinct than the Kripke structure of the system, which makes them interesting symbolic representations for model checking work. The net unfoldings have been a base of several model checking approaches in the past, some of which are mentioned in this work. Section 3 contains more information on the net unfolding method. In addition, publications [**P1**]-[**P4**] are on net unfolding based methods.

Processes were introduced to give partial order semantics to Petri nets [4, 5, 29, 31]. Intuitively, a process can be seen as the partial order version of an execution. However, it is actually the case that even a single process can correspond to exponentially many interleaving executions, and thus can sometimes also be exponentially more succinct than the Kripke structure. The partial order behavior of the system can now be described as a set of processes it induces. A net unfolding can be intuitively seen as the union of all the processes of the Petri net system, with maximal prefix sharing. The term "branching processes" refers to this fact. The only process based verification method we know of is presented in publication [P5], which contains a process based bounded model checking procedure. It can be seen as a symbolic representation of all the processes of the 1-safe Petri net in question, which have a depth equal to a user specified value n. An extensive treatment of Petri net processes can be found in [4, 5].

For computational complexity of Petri net related verification problems, see e.g., [18]. More information on the state explosion problem and methods to alleviate it can be found in [70]. For a longer introduction to model checking, including other related techniques, see e.g., [11].

Our research goal has been the development of efficient model checking methods for 1-safe Petri nets. The main problem facing us is the state explosion problem. We have chosen to concentrate on using a combination of symbolic methods and partial order semantics to alleviate this problem. A major part of the work focuses on developing a better understanding of complete finite prefix based verification methods.

### 1.1 Contributions

The main contributions of each of the publications are the following:

- [P1]: Linear size translations are devised from the deadlock and reachability problems of 1-safe Petri nets using complete finite prefixes into finding a stable model of a logic program. For deadlock checking, the translation can be seen as an adaptation of the mixed integer programming translation of [56] to the used logic programming framework, while the reachability checking version is new. Experimental results from the deadlock detection problem show the method to be competitive with alternative net unfolding based deadlock checking approaches. This publication is an extended version of [37].

- **[P2]**: Model checking several temporal logics is shown to be PSPACEcomplete in the size of a complete finite prefix of a 1-safe Petri net system for fixed size formulas. The proof employs a class of net systems for which it is easy to generate a complete finite prefix in polynomial time. This class is also shown to contain net systems for which classical prefix generation algorithms [24, 25, 55] generate exponentially larger prefixes than required to satisfy the prefix completeness criterion.

- **[P3]**: A new net unfolding based model checking procedure for an action based linear temporal logic is presented. This procedure solves the model checking problem by direct inspection of a prefix instead of requiring the running of an elaborate algorithm on the prefix, as is the case in previous approaches [75]. The report version [20] is an extended version that contains proofs and examples not contained in the conference version **[P3]** due to length constraints.

- [P4]: An implementation of a net unfolding based linear temporal logic model checker is presented. The tableau procedure of [P3] is applied to a state based temporal logic LTL-X, and developed further to be more easily implementable as a modification of a conventional prefix generation procedure. Experimental results from a prototype implementation are presented. Again, the report version [22] contains proofs omitted from the conference version [P4] due to length constraints.

- [P5]: Bounded model checking is applied to checking reachability properties of asynchronous systems, specifically 1-safe Petri nets. We consider three different semantics: interleaving, step, and process semantics. The reachability checking problems are translated into constrained Boolean circuit satisfiability, and experimental results on a set of deadlock checking problems are obtained. The main contribution is the translation for the process semantics, which frequently performs best of the three semantics considered.

- [P6]: We present how to use logic programs with stable model semantics to solve bounded model checking problems of 1-safe Petri nets.

8

In this work, two semantics are considered: interleaving and step semantics. As properties, reachability and also linear time temporal logic LTL-X are used, both with parametric initial markings. The main contribution of the paper is a new, more succinct bounded LTL-X model checking translation that allows for concurrency of invisible transitions in generated counterexamples. This frequently allows counterexamples to be found with smaller bounds. This publication is an extended version of [41].

**Structure of the Dissertation.** The dissertations consists of 6 publications and a dissertation summary.

The structure of the dissertation summary is as follows. First we introduce basic notation used for Petri nets. In Section 3 we define net unfoldings. The discussion of different notions of prefix completeness in Section 3.1 is a subject that is presented only in the dissertation summary. We will continue with the definition of logic programs with stable model semantics, and the motivation for using them in Section 4. Verification with prefixes is the topic of Section 5, parts of which are new to this work. In Section 6, we introduce bounded model checking. The conclusions are in Section 7. The Appendix A contains corrections and additions to the publications.

#### 2 PETRI NETS

This section summarizes the basic Petri net notation used throughout the work. All of the material is also presented in the publications.

Petri nets are a widely used model of concurrent and reactive systems. In this work we discuss verification methods for Petri nets used to model asynchronous finite state systems. More specifically, we limit ourselves to the so-called 1-safe Petri nets, which can be seen as an interesting generalization of communicating automata, see e.g., [15].

A net is a triple  $N = \langle P, T, F \rangle$ , where P and T are disjoint sets of places and transitions, respectively, and F is a function  $(P \times T) \cup (T \times P) \rightarrow \{0, 1\}$ . Places and transitions are generically called nodes. If F(x, y) = 1 then we say that there is an arc from x to y. The places are represented in graphical notation by circles, transitions by squares, and the flow relation F with arcs.

The preset of a node  $x \in P \cup T$ , denoted by  $\bullet x$ , is the set  $\{y \in P \cup T \mid F(y, x) = 1\}$ . The postset of a node  $x \in P \cup T$ , denoted by  $x^{\bullet}$ , is the set  $\{y \in P \cup T \mid F(x, y) = 1\}$ . Their generalizations on sets of nodes  $X \subseteq P \cup T$  are defined as  $\bullet X = \bigcup_{x \in X} \bullet x$ , and  $X^{\bullet} = \bigcup_{x \in X} x^{\bullet}$ , respectively. In this work we consider only nets in which every transition has a nonempty preset and a nonempty postset.

A marking of a net  $\langle P, T, F \rangle$  is a mapping  $P \to \mathbb{N}$  (where  $\mathbb{N}$  denotes the set of natural numbers including 0). We identify a marking M with the multiset containing M(p) copies of p for every  $p \in P$ . For instance, if  $P = \{p_1, p_2\}$  and  $M(p_1) = 1$ ,  $M(p_2) = 2$ , we write  $M = \{p_1, p_2, p_2\}$ . A marking is graphically denoted by a distribution of tokens on the places of the net.

A marking M enables a transition t if it marks each place  $p \in {}^{\bullet}t$  with a token, i.e., if M(p) > 0 for each  $p \in {}^{\bullet}t$ . If t is enabled at M, then it can fire or occur, and its occurrence leads to a new marking M', obtained by removing a token from each place in the preset of t, and adding a token to each place in its postset; formally, M'(p) = M(p) - F(p,t) + F(t,p) for every place p. For each transition t the relation  $\xrightarrow{t}$  is defined as follows:  $M \xrightarrow{t} M'$  if t is enabled at M and its occurrence leads to M'.

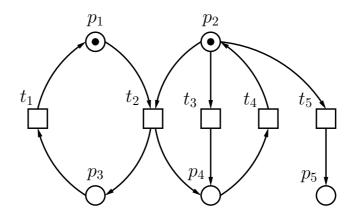

A 4-tuple  $\Sigma = \langle P, T, F, M_0 \rangle$  is a net system if  $\langle P, T, F \rangle$  is a net and  $M_0$  is a marking of  $\langle P, T, F \rangle$  (called the *initial marking* of  $\Sigma$ ). We will use as a running example the net system in Figure 1.

A sequence of transitions  $\sigma = t_1 t_2 \dots t_n$  is an occurrence sequence if there exist markings  $M_1, M_2, \dots, M_n$  such that

$$M_0 \xrightarrow{t_1} M_1 \xrightarrow{t_2} \dots M_{n-1} \xrightarrow{t_n} M_n.$$

$M_n$  is the marking reached by the occurrence of  $\sigma$ , which is also denoted by  $M_0 \xrightarrow{\sigma} M_n$ . A marking M is a reachable marking if there exists an occurrence sequence  $\sigma$  such that  $M_0 \xrightarrow{\sigma} M$ . The reachability graph of a net system  $\Sigma$  is the labelled graph having the reachable markings of  $\Sigma$  as nodes, and the  $\xrightarrow{t}$  relations (more precisely, their restriction to the set of reachable markings) as edges. In this work we only consider net systems with finite reachability graphs.

Figure 1: A running example, net system  $\Sigma$ .

A marking M of a net is *n*-safe if  $M(p) \le n$  for every place p. A net system  $\Sigma$  is *n*-safe if all its reachable markings are *n*-safe. In this work we mainly consider net systems which are 1-safe. The only exception to this rule is the publication [**P3**], where we also consider *n*-safe net systems for a fixed integer  $n \ge 1$ .

**Labelled Nets.** Let  $\mathcal{L}$  be a finite alphabet. A *labelled net* is a pair  $\langle N, l \rangle$  (also represented as 4-tuple  $\langle P, T, F, l \rangle$ ), where N is a net and  $l: P \cup T \to \mathcal{L}$  is a labelling function. Notice that different nodes of the net can carry the same label. We extend l to multisets of  $P \cup T$  in the obvious way.

For each label  $a \in \mathcal{L}$  we define the relation  $\xrightarrow{a}$  between markings as follows:  $M \xrightarrow{a} M'$  if  $M \xrightarrow{t} M'$  for some transition t such that l(t) = a.

The reachability graph of a labelled net system  $\langle N, l, M_0 \rangle$  is obtained by applying *l* to the reachability graph of  $\langle N, M_0 \rangle$ . In other words, its nodes are the set

$\{l(M) \mid M \text{ is a reachable marking}\}$

and its edges are the set

$$\{l(M_1) \xrightarrow{l(t)} l(M_2) \mid M_1 \text{ is reachable and } M_1 \xrightarrow{t} M_2\}.$$

It should be noted that in this dissertation summary only labelled net systems of a very restricted form are used. Namely, for any two reachable marking  $M_1, M_2$  of the underlying net system  $\langle N, M_0 \rangle$  such that  $l(M_1) = l(M_2)$  it holds that if  $M_1 \xrightarrow{t} M'_1$  then there exist  $t', M'_2$  such that  $M_2 \xrightarrow{t'} M'_2$ , l(t') = l(t), and  $l(M'_2) = l(M'_1)$ .

#### **3 NET UNFOLDINGS**

This section introduces net unfoldings and complete finite prefixes more throughly than the presentation in the publications [**P1**]-[**P4**]. The discussion of different notions of prefix completeness in Sect. 3.1 is a subject which is new to the dissertation summary. The presentation of this section is heavily influenced by the presentation of [23, 24, 25].

Net unfoldings were introduced in [58] as a partial order semantics for Petri nets. They were later more extensively researched under the name of branching processes by Engelfriet [16]. McMillan was the first to show how to use net unfoldings as a basis for a verification method [55]. This method has since its publication been the basis of several model checking approaches, some of which we will discuss in this dissertation.

In this section we introduce the definitions needed to describe the unfolding approach. More details can be found in [23, 24, 25, 65, 74].

**Occurrence Nets.** We use  $\langle F (\leq_F)$  to denote the (reflexive) transitive closure of a flow relation F. We say that two distinct nodes x, y are causally related, if  $x \leq_F y$  or  $y \leq_F x$  holds. The nodes x and y are in conflict, denoted by x # y, if there exist  $t_1, t_2 \in T$  such that  $t_1 \neq t_2$ ,  $\bullet t_1 \cap \bullet t_2 \neq \emptyset$ ,  $t_1 \leq_F x$ , and  $t_2 \leq_F y$ . The nodes x and y are concurrent, denoted by  $x \operatorname{col} y$ , if neither  $x \leq_F y$  nor  $y \leq_F x$  nor x # y.

Occurrence nets are nets which have the following special properties. An occurrence net is a net  $N = \langle B, E, G \rangle$  such that

- $\forall b \in B : |\bullet b| \le 1$ ,

- *G* is acyclic, or equivalently, <<sub>*G*</sub> is a strict partial order (a transitive and irreflexive relation),

- *N* is finitely preceded, i.e., for any node *x* of the net, the set of nodes *y* such that *y* <<sub>*G*</sub> *x* is finite, and

- $\forall x \in B \cup E : \neg(x \# x).$

The elements of *B* and *E* are called *conditions* and *events*, respectively. We also use *G* instead of *F* to denote the flow relation of an occurrence net in order to not to cause confusion when the occurrence nets are used later in this section. Let Min(N) denote the set of minimal elements of the strict partial order  $<_G$  restricted to the set of conditions. In this work the minimal elements will all be conditions, and thus the set Min(N) can be intuitively seen as an initial marking, called the *default initial marking*. A set of conditions of an occurrence net is a *co-set* iff all the conditions of the set are pairwise is the *co* relation.

**Branching Processes.** We associate to a net system  $\Sigma$  a set of *labelled* occurrence nets, called the *branching processes* of  $\Sigma$ . For technical reasons we require that the initial marking  $M_0$  of  $\Sigma$  is 1-safe. The conditions and events of branching processes are labelled with places and transitions of  $\Sigma$ ,

respectively. The conditions and events of the branching processes are subsets from two sets  $\mathcal{B}$  and  $\mathcal{E}$ , inductively defined as the smallest sets satisfying the following conditions

- $\perp \in \mathcal{E}$ , where  $\perp$  is an special symbol,

- if  $e \in \mathcal{E}$ , then  $(p, e) \in \mathcal{B}$  for every  $p \in P$ , and

- if  $\emptyset \subset X \subseteq \mathcal{B}$ , then  $(t, X) \in \mathcal{E}$  for every  $t \in T$ .

In our definitions of branching process (see below) we make consistent use of these names: The label of a condition (p, e) is p, and its unique input event is e. Conditions  $(p, \perp)$  have no input event, i.e., the special symbol  $\perp$ is used for the minimal conditions of the occurrence net. Similarly, the label of an event (t, X) is t, and its set of input conditions is X. The advantage of this scheme is that a branching process is completely determined by its sets of conditions and events. This labelling scheme was first introduced by Engelfriet [16].

We will define branching processes inductively in what follows as pairs (B, E) where  $B \subseteq \mathcal{B}$  and  $E \subseteq \mathcal{E}$ . A pair (B, E) can now be alternatively seen as a labelled net system  $N = \langle N, l, Min(N) \rangle$  with  $N = \langle B, E, G \rangle$  as follows. The labelling l is the one described above, conditions B and events E are as given, and the flow relation G being

- if  $e = (t, X) \in E$  and  $b \in (X \cap B)$ , then  $(b, e) \in G$ , and

- if  $b = (p, e) \in B$  such that  $e \in E$ , then  $(e, b) \in G$ .

Note that the definition above does not assume anything about the "consistency" of the labelling, i.e., an edge can only exist if both its endpoints exists. This complicates the definition somewhat but makes it applicable to any pair (B, E) instead of only branching processes. For branching processes the net system as defined above are occurrence net systems, as expected.

We will now inductively define the set of finite branching process of a net system  $\Sigma$  as a pairs (B, E).

**Definition 1** The set of finite branching processes of a net system  $\Sigma$  with the (1-safe) initial marking  $M_0 = \{p_1, \ldots, p_n\}$  is inductively defined as follows:

- $(\{(p_1, \bot), \ldots, (p_n, \bot)\}, \emptyset)$  is a branching process of  $\Sigma$ .

- If (B, E) is a branching process of Σ, t ∈ T, and X ⊆ B is a coset labelled by •t, then (B ∪ {(p, e) | p ∈ t•}, E ∪ {e}) is also a branching process of Σ, where e = (t, X). If e ∉ E, then e is called a possible extension of (B, E).

The set of branching processes of  $\Sigma$  is obtained by declaring that the union of any finite or infinite set of branching processes is also a branching process, where union of branching processes is defined componentwise on conditions and events. Since branching processes are closed under union, there is a unique maximal branching process, called the *unfolding* of  $\Sigma$ . This result is due to Engelfriet [16]. We will often use the term *prefix* as a synonym for

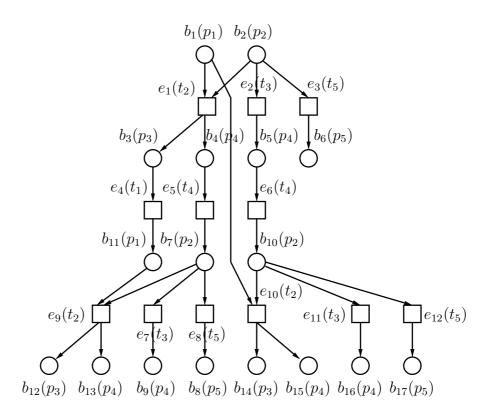

Figure 2: An initial part of the unfolding of  $\Sigma$ .

a branching process of a net system, as any finite branching process can be seen as a prefix of the unfolding of the same net system.

As an example of the unfolding, look at our running example, the 1-safe net system  $\Sigma$  in Figure 1. An initial part of the (infinite) unfolding of  $\Sigma$  is presented in Figure 2. The labelling *l* is given by the labels in the parentheses.

We take as partial order semantics of  $\Sigma$  its unfolding. This is justified, because it can be easily shown the reachability graphs of  $\Sigma$  and of its unfolding coincide. (Notice that the unfolding of  $\Sigma$  is a *labelled* net system, and so its reachability graph is defined as the *image* under the labelling function of the reachability graph of the *unlabelled* system.) It is possible to show an even stronger correspondence between the behavior of the original net system and the unfolding. Namely, also the partial order behavior of the net system is preserved by unfolding [24, 25].

We often use  $\beta$  to refer to a branching process. Because it is easy to obtain either presentation  $\beta = (B, E)$  or  $\beta = \langle N, l, Min(N) \rangle$  with  $N = \langle B, E, G \rangle$ of the branching process from each other, we use them interchangeably all through this work.

**Configurations.** A configuration of an occurrence net is a set of events C satisfying the two following properties: C is causally closed, i.e., if  $e \in C$  and  $e' <_G e$  then  $e' \in C$ , and C is conflict-free, i.e., no two events of C are in conflict. Note that configurations can correspond to several occurrence sequences of the underlying net system. In our running example in Figure 2 the configuration  $C = \{e_1, e_4, e_5\}$  corresponds to the occurrence

sequences  $t_2$ ,  $t_1$ ,  $t_4$  and  $t_2$ ,  $t_4$ ,  $t_1$  of the net system  $\Sigma$  in Figure 1. We call these occurrence sequences *linearisations* of the configuration.

A configuration C of a branching process is associated with a reachable marking of  $\Sigma$  denoted by  $Mark(C) = l((Min(N) \cup C^{\bullet}) \setminus {}^{\bullet}C)$ . The corresponding set of conditions associated with a configuration is called a *cut*, and is defined as  $Cut(C) = ((Min(N) \cup C^{\bullet}) \setminus {}^{\bullet}C)$ . Given an event *e*, we call  $[e] = \{e' \in E \mid e' \leq_G e\}$  the local configuration of *e*.

Another way of specifying the unfolding is that it is the output of an unfolding algorithm, Algorithm 1, which was first presented in this form in [24]. We denote by PE(Unf) the set of possible extension e = (t, X) of a branching process Unf = (B, E). For the algorithm to work, we require the following notion of fairness: Whenever an event is added to the set pe of possible extensions, it is also eventually selected to be removed from the set. One possibility to guarantee this is to require that the unfolding algorithm proceeds, e.g., in breadth-first order in generating the unfolding.

#### Algorithm 1 The unfolding algorithm

input: A net system  $\Sigma = \langle P, T, F, M_0 \rangle$ , where  $M_0 = \{p_1, \dots, p_n\}$ . output: The unfolding Unf = (B, E) of  $\Sigma$ . begin  $Unf := (\{(p_1, \bot), \dots, (p_n, \bot)\}, \emptyset);$  pe := PE(Unf);while  $pe \neq \emptyset$  do append to Unf an event e = (t, X) of pe and a condition (p, e)for every place  $p \in t^{\bullet};$  pe := PE(Unf);endwhile end

Note that the unfolding algorithm might not terminate because the unfolding can be an infinite object.

#### 3.1 Complete Finite Prefixes

When we are interested in Petri nets which have only a finite number of reachable states, then the net unfolding will contain a finite initial part, which contains full information about the net unfolding. This observation was first made by McMillan [55], who developed an algorithm to obtain such complete finite prefix of the unfolding.

Later Esparza et al. [24, 25] improved McMillan's construction to guarantee that for 1-safe net systems one can obtain a prefix which represents all reachable markings and whose size is bound by the number of reachable states of the original net system. A prefix can in some cases be exponentially smaller than the reachability graph of the system, which makes them interesting for verification purposes.

**Marking Completeness.** We begin by giving a notion of prefix completeness sufficient to check reachability properties using net unfoldings.

**Definition 2** A branching process  $\beta$  of a net system  $\Sigma$  is marking complete if for each reachable marking M of  $\Sigma$  there exists a configuration C of  $\beta$  such that Mark(C) = M.

Esparza et al. have shown that for 1-safe Petri nets it is always possible to create a marking complete prefix which has at most as many events as the net system has reachable markings [24, 25]. (Use for example the prefix generation algorithm of [24, 25] and throw away the so called "cut-off events" as soon as they are encountered.)

**Net Structure Completeness.** We have defined marking completeness in a way which does not require that each enabled transition of the net system is presented as an event in the prefix. To require this, we define the following (incomparable) notion of completeness.

**Definition 3** A branching process  $\beta$  of a net system  $\Sigma$  is net structure complete if for each transition t enabled by some reachable marking M of  $\Sigma$  there exists an event e of  $\beta$  such that l(e) = t.

Usually net structure completeness on its own is not a very interesting property, as it only allows one to recreate all the transitions (which are enabled by some reachable marking) of the net system  $\Sigma$  from the prefix  $\beta$ . However, if one creates a prefix which is marking complete, and then adds one event for each enabled transition not existing in the prefix so far, it is possible to obtain a marking and net structure complete prefix whose number of events is bound by the sum of reachable markings and the number of transitions of the net system  $\Sigma$ .

**Completeness.** Esparza et.al were the first to define a semantic prefix completeness criterion. We will thus simply refer to it as completeness [24, 25].

**Definition 4** A branching process  $\beta$  of a net system  $\Sigma$  is complete if for each reachable marking M of  $\Sigma$  there exists a configuration C of  $\beta$  such that:

- Mark(C) = M, and

- for every transition t enabled in M there exists a configuration  $C \cup \{e\}$  such that  $e \notin C$  and l(e) = t.

Clearly the unfolding of a net system is always complete. If a finite prefix of the unfolding is complete we call it a *complete finite prefix*. Intuitively if a prefix is complete then the unfolding can be "easily" reconstructed from it. (Of course the unfolding could be also obtained from a net structure complete prefix by e.g., recreating the original net system and then unfolding it. However, we do not consider such and indirect way of constructing an unfolding from a prefix "easy".) A complete finite prefix also contains all the information about the reachability graph of the net system, and thus can be seen as a symbolic representation of the reachability graph. A slightly weaker definition of completeness is presented in [50]. It does also allow the unfolding to be "easily" generated from the prefix if needed.

**Strong Completeness.** The traditional prefix generation algorithms and some of the model checking algorithms use the notion of a set of *cut-off* events  $E_{cut}$ . Recently Vogler et al. [74] have added cut-off events into a notion of prefix completeness in an algorithm independent fashion. Their notion of prefix completeness can be parameterized in several different ways. For simplicity we will fix a set of parameters, and obtain an instance of their notion which can be defined as follows.

**Definition 5** A branching process  $\beta$  of a net system  $\Sigma$  is strongly complete if there is a set  $E_{cut} \subseteq E$  such that:

- for each reachable marking M of  $\Sigma$  there is a configuration  $C \subseteq (E \setminus E_{cut})$  of  $\beta$  such that Mark(C) = M, and

- for each configuration C' ⊆ (E \ E<sub>cut</sub>) of β and for each transition t enabled by Mark(C') in Σ, there is an event e of β such that e ∉ C', l(e) = t, and such that C' ∪ {e} is a configuration of β (e may be in E<sub>cut</sub>).

We call an event *e* redundant if there exists an event  $e' \in E_{cut}$  such that  $e' <_G e$ . It is easy to see that all redundant events can be removed and the branching process still stays strongly complete. We will in the following assume that a strongly complete branching process does not contain any redundant events.

Note that this definition requires each configuration C' without cut-off events to be fully extended by all the transitions enabled by the corresponding marking, not just one representative configuration to be fully extended (compare to Def. 4).

The intuition is that  $E_{cut}$  contains a set of events, which do not need to be fired to reach any of the reachable markings of  $\Sigma$ , and thus the prefix can be truncated at any event in the set of cut-off events without losing any reachable markings. However, in a strongly complete prefix this truncation should always manifest itself as a cut-off event left in the prefix. This notion of completeness is strongest of all the notion of completeness discussed in this work. Thus if a prefix is strongly complete it is also complete, marking complete, and net structure complete. Clearly, if we remove all the cutoff events from a strongly complete prefix, we will end up with a marking complete prefix which might no longer be net structure complete.

Because strong completeness criterion implies completeness, it might require more events to be present in the prefix than just ordinary completeness. The drawback of these notions of prefix completeness which require more events to be added to the prefix than just plain marking completeness is that the prefix may need to have also a large number of (usually cut-off) events included to satisfy the additional parts of the used completeness requirement. We do not know of an upper bound on the number of such additional events which would be linearly bounded by the number of markings in the reachability graph.

The McMillan's deadlock checking algorithm [55], Esparza's branching time model checker [17, 32], as well as the deadlock checkers of [48, 56] and [**P1**] rely on having a complete set of cut-off events available and thus require

strong completeness. However, the reachability translation of [P1] works for any marking complete prefix.

The work of Khomenko and Koutny in [49] presents two different deadlock checking procedures. The first one requires strong completeness, while the the second one works for any marking complete prefix. The intuition behind this translation is to express the deadlock as a reachability of a marking satisfying the formula  $dead = \neg \bigvee_{t \in T} \bigwedge_{p \in \bullet_t} p$ . The latest implementation of the reachability checking procedure described in [**P1**] supports a large variety of formulas to be given as input, including the formula *dead*. The details of the improved implementation have been described in [34]. The main feature of the used translation is that it is linear in the input formula size for all supported formulas. We would like to use marking completeness for all reachability properties in the future, as that enables one to generates smaller prefixes than e.g., strong completeness. We need to experiment with this alternative deadlock checking approach to see whether it is a viable solution when e.g., using the approach of [**P1**].

The complexity results of publication [P2] were done for the notion of completeness (Def. 4), however, the prefixes used in the proofs are also strongly complete (Def. 5) and thus the results also hold for this stronger notion of prefix completeness.

We believe that also other, more application specific, notions of prefix completeness will be useful in the design of efficient model checking algorithms with prefixes. Instances of this can be found in the publications **[P3]** and **[P4]**.

**Prefix generation.** We will now describe one algorithm which constructs a complete finite prefix of the unfolding of a bounded Petri net. Actually the generated prefix will also be complete with respect to the strong completeness criterion of Def. 5, see [74]. In this form the algorithm was first presented in [24]. First we will introduce some additional notation.

Given a configuration C, we denote by  $\uparrow C$  the set of events of the unfolding given by  $\{e \mid e \notin C \land \forall e' \in C : \neg(e\#e')\}$ . Intuitively,  $\uparrow C$  corresponds to the behavior of  $\Sigma$  from the marking reached after executing the events in C. We call  $\uparrow C$  the continuation after C of the unfolding of  $\Sigma$ . If  $C_1$  and  $C_2$  are two finite configurations leading to the same marking, i.e.,  $Mark(C_1) = M = Mark(C_2)$ , then  $\uparrow C_1$  and  $\uparrow C_2$  are isomorphic, i.e., there is a bijection between them which preserves the labelling of events and the causal, conflict, and concurrency relations (see [24, 25]). The basic idea of the unfolding algorithm is to avoid the construction of such redundant isomorphic copies of the same behavior by truncating the unfolding when possible.

Adequate orders. To implement a complete finite prefix generation algorithm we use the notion of *adequate order* on configurations [24, 25]. Given a configuration C of the unfolding of  $\Sigma$ , we denote by  $C \oplus E$  the set  $C \cup E$ , under the condition that  $C \cup E$  is a configuration satisfying  $C \cap E = \emptyset$ . We say that  $C \oplus E$  is an extension of C. Now, let  $C_1$  and  $C_2$  be two finite configurations leading to the same marking. Then  $\uparrow C_1$  and  $\uparrow C_2$  are isomorphic, as was noted above. This isomorphism, say f, induces a mapping from the

extensions of  $C_1$  onto the extensions of  $C_2$ ; the image of  $C_1 \oplus E$  under this mapping is  $C_2 \oplus f(E)$ .

**Definition 6** A strict partial order  $\prec$  on finite configurations of the unfolding of a net system is an adequate order if:

- $\prec$  is well-founded,

- $C_1 \subset C_2$  implies  $C_1 \prec C_2$ , and

- $\prec$  is preserved by finite extensions; if  $C_1 \prec C_2$  and  $Mark(C_1) = Mark(C_2)$ , then the isomorphism f from above satisfies  $C_1 \oplus E \prec C_2 \oplus f(E)$  for all finite extensions  $C_1 \oplus E$  of  $C_1$ .

Note the requirement that  $\prec$  is a strict partial order (a transitive and irreflexive relation), as this part is sometimes overlooked in the definition.

Total adequate orders have been presented for 1-safe Petri nets in [24, 25] and for synchronous products of transition systems in [23]. The approach has also been adapted for process algebras in [52], where the authors also define an adequate order. The exact definitions adequate orders for 1-safe Petri nets are somewhat involved and left out of this work, the details can be found in [24, 25, 65].

Unlike the semantic definition of strong completeness, Def. 5, the presented algorithm uses an algorithmic way of computing a set of cut-off events. They are identified as follows.

**Definition** 7 An event e of a prefix of the unfolding is a cut-off event if the already constructed part of the prefix contains an event e', such that Mark([e']) = Mark([e]) and  $[e'] \prec [e]$ .

We call the configuration [e'] the corresponding configuration. The intuition behind cut-off events is the following. Because Mark([e']) = Mark([e]) we know that their continuations  $\uparrow [e']$  and  $\uparrow [e]$  are isomorphic. Because [e'] was already added to the prefix, we don't have to duplicate the same (isomorphic) behavior after [e] but can safely truncate that branch of the prefix without loosing any information. For the correctness proof of the algorithm, see [24, 25].

It is also possible to use non-local corresponding configurations when finding cut-off events of a prefix. This more refined cut-off criterion was first proposed in [35]. Non-local cut-off criteria have not been implemented in currently available prefix generation tools due to high costs of computing them in an implementation.

A Complete Prefix Generation Algorithm. We can now preset the complete prefix generation algorithm of Esparza et al., Algorithm 2. It is an improved version of the first complete prefix generation algorithm developed by McMillan [55].

The algorithm works as follows. First possible extensions are calculated. Then the algorithm adds events to the prefix in increasing adequate order of their local configurations. It adds to the prefix all events which do not have a cut-off in their local configuration, updating the sets of of possible extensions Algorithm 2 A (strongly) complete finite prefix algorithm

**input:** A *n*-safe net system  $\Sigma = \langle P, T, F, M_0 \rangle$ , where  $M_0 = \{p_1, \ldots, p_n\}$ . output: A complete finite prefix Fin = (B, E) of Unf. begin  $Fin := (\{(p_1, \bot), \ldots, (p_n, \bot)\}, \emptyset);$ pe := PE(Fin); $cut\_off := \emptyset;$ while  $pe \neq \emptyset$  do choose an event e = (t, X) in pe such that [e] is minimal with respect to  $\prec$ ; if  $[e] \cap cut\_off = \emptyset$  then append to *Fin* the event e and a condition (p, e)for every place  $p \in t^{\bullet}$ ; pe := PE(Fin);if e is a cut-off event for Fin then  $cut_off := cut_off \cup \{e\}$ ; else  $pe := pe \setminus \{e\};$ endif endwhile end

and cut-off events accordingly. For 1-safe nets the number of non-cut-off event generated by the algorithm is bounded by the number of reachable markings when using the adequate order of [24].

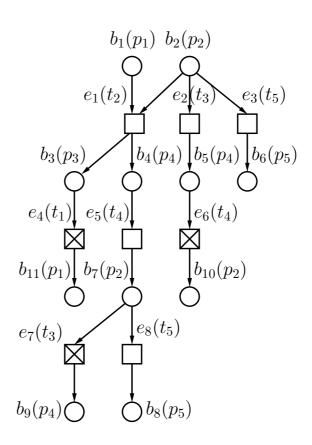

The (strongly) complete prefix generated by the algorithm for our running example is presented in Figure 3. In the figures the cut-off events are marked with crosses. We can obtain a smaller marking complete prefix by just removing all the cut-off events from the prefix of Figure 3.

We refer the reader interested in prefix generation algorithms to [23, 24, 25, 50, 65]. The latest development in them is the use of parallel algorithms [40, 74] for prefix generation.

Figure 3: A strongly complete finite prefix of  $\Sigma$ .

#### 4 RULE-BASED CONSTRAINT PROGRAMMING

This section introduces logic programs with stable model semantics in more detail than the publications [P1] and [P6]. The presentation of this section is based on [67], [P1] and slightly extended here. The motivation for using stable models in Section 4.2 is new to this dissertation summary.

We will use normal logic programs with stable model semantics [28] as the underlying formalism into which several verification problems in this work are translated. To be more explicit, the tools developed in publications [P1], [P4], and [P6] employ logic programs with stable model semantics. For a longer introduction to the stable model semantics, and its relation to propositional satisfiability, we refer the interested reader to [59].

The stable model semantics is one of the main declarative semantics for normal logic programs. However, here we use logic programming in a way that is different from the typical PROLOG style paradigm, which is based on the idea of evaluating a given query. Instead, we employ logic programs as a *constraint programming framework* [59], where stable models are the solutions of the program rules seen as constraints.

We consider normal logic programs that consist a set of of rules of the form

$$\mathbf{h} \leftarrow \mathbf{a_1}, \dots, \mathbf{a_n}, not \, (\mathbf{b_1}), \dots, not \, (\mathbf{b_m}) \tag{1}$$

where  $a_1, \ldots, a_n, b_1, \ldots, b_m$  and h are propositional atoms. Such a rule can be seen as a constraint saying that if atoms  $a_1, \ldots, a_n$  are in a model and atoms  $b_1, \ldots, b_m$  are not in a model, then the atom h is in a model. The atom h is called the *head* of the rule, while the atoms  $a_1, \ldots, a_n$  and the *not-atoms*  $b_1, \ldots, b_m$  are jointly called the *body* of the rule.

The stable model semantics also enforces minimality and groundedness of models. This makes many combinatorial problems easily and succinctly describable using logic programming with stable model semantics.

The stable model semantics for a normal logic program P is defined as follows [28]. (See also an alternative definition after examples below.)

**Definition 8** The reduct  $P^A$  of P with respect to a set of atoms A is obtained by

- (i) deleting each rule in P that has a not-atom not (x) in its body such that x ∈ A, and

- (ii) by deleting all not-atoms in the remaining rules.

The deductive closure of  $P^A$  is the smallest set of atoms that is closed under  $P^A$  when the rules in  $P^A$  are seen as inference rules. A set of atoms A is a stable model of P iff A is the deductive closure of  $P^A$  when the rules in  $P^A$  are seen as inference rules.

The problem of deciding whether a program has a stable model is NPcomplete [54]. The definition above gives a way non-deterministic way of constructing stable models. We will demonstrate the basic behavior of the semantics using programs P1-P4 below:

Program P1 has two stable models: {a} and {b}. For example if we guess  $A = \{a\}$  we obtain the reduct program  $P^{\{a\}} = \{a \leftarrow\}$ , whose deductive closure is {a} and thus A is a stable model. The {b} case is symmetric. If we guess  $A = \{a, b\}$  we obtain the reduct program  $P^{\{a,b\}} = \emptyset$ , whose deductive closure is  $\emptyset$  and thus A is not a stable model. If we guess  $A = \emptyset$  we obtain the reduct program  $P^{\{a,b\}} = \emptyset$ , whose deductive closure is  $\emptyset$  and thus A is not a stable model. If we guess  $A = \emptyset$  we obtain the reduct program  $P^{\emptyset} = \{a \leftarrow, b \leftarrow\}$ , whose deductive closure is {a, b} and thus A is not a stable model.

Program P2 has the empty set as its unique stable model. This exposes the fact that the deductive closure of  $P^{\emptyset} = \{a \leftarrow a\}$  is the empty set. Also the deductive closure of  $P^{\{a\}} = \{a \leftarrow a\}$  is the empty set, and thus  $A = \{a\}$  is not a stable model.

Program P3 is an example of a program which has no stable models. If we guess  $A = \emptyset$ , then we will deduce {a}, which will contradict with our assumption  $A = \emptyset$ , and symmetrically for  $A = \{a\}$ .

Program P4 has one stable model  $\{b, d\}$ . If we guess  $A = \{b, d\}$  we will get the reduct program  $P^{\{b,d\}} = \{b \leftarrow, d \leftarrow b\}$  whose deductive closure is  $\{b, d\}$ . If we guess  $A = \{a, c\}$  we will get the reduct  $P^{\{a,c\}} = \{a \leftarrow c, d \leftarrow b\}$  whose deductive closure is  $\emptyset$  which does not agree with our guess. Other cases are similar.

Next we proceed to give an alternative definition of the stable model semantics using slightly different notation.

**Definition 9** Let *A* be a set of atoms, we define  $not(A) = \{not(a) | a \in A\}$ .

For a set of atoms and not-atoms B we denote the atoms in B by  $B^+$  and the set of not-atoms by  $B^-$ . Atoms and not-atoms are also called *literals*. We denote with Atoms(P) the set of all propositional atoms which appear in the logic program P as literals. We use the notation  $\overline{\Delta}$  to denote the set  $Atoms(P) \setminus \Delta$ .

**Definition 10** The deductive closure of a set of rules P and a set of literals B is denoted by Dcl(P, B), where Dcl(P, B) is the smallest set of atoms that contains  $B^+$  and is closed under R(P, B) when

$$R(P,B) = \{\mathbf{h} \leftarrow \mathbf{a_1}, \dots, \mathbf{a_n} \mid \\ \mathbf{h} \leftarrow \mathbf{a_1}, \dots, \mathbf{a_n}, not (\mathbf{b_1}), \dots, not (\mathbf{b_m}) \in P \text{ and} \\ not (\mathbf{b_i}) \in B^-, \text{ for } i = 1, \dots, m\}$$

is seen as a set of inference rules.<sup>2</sup>

The deductive closure gives us a fixpoint characterization of the stable models.

<sup>&</sup>lt;sup>2</sup>This could alternatively be defined as computing the least fixpoint of a suitably defined monotone predicate transformer over the atoms of the program, see e.g., page 6 of [68].

**Proposition 1** The set of atoms  $\Delta$  is a stable model of a set of rules P iff  $\Delta = Dcl(P, not(\overline{\Delta})).$

The proof is immediate by noting that the reduct  $P^{\Delta} = R(P, not(\overline{\Delta}))$ .

We explain the notation of the definition above with a non-deterministic algorithm for computing stable models which uses this notation. First one guesses a set of atoms  $\Delta$ , then computes all atoms of the program not in  $\Delta$ , i.e.,  $\overline{\Delta}$ . Then all these atoms not in  $\Delta$  are used as "negative assumptions"<sup>3</sup>  $B = not(\overline{\Delta})$  to compute the reduct program  $P^{\Delta} = R(P, B)$ . This reduct program does not contain any not-atoms, and it is thus easy to compute the deductive closure  $\Delta'$  in polynomial time. If the result is the same as our guess, i.e.,  $\Delta = \Delta'$  we have found a stable model.

There is another way of looking at reducts and deductive closures. Note that the reduct program only contains rules without not-atoms. Therefore the program can be seen as a conjunction of propositional Horn clauses [59]. For example in P4 above one of the reduct programs was  $P^{\{b,d\}} = \{b \leftarrow, d \leftarrow b\}$  which can be seen as the propositional formula  $((b) \land (d \lor \neg b))$ . Now the deductive closure of the program is the (unique) subset minimal model of this propositional formula, in this case  $\{b, d\}$ . As there are linear time algorithms to obtain subset minimal models for Horn clauses, their implementation techniques can be applied to computing deductive closures.

Logic programs with stable model semantics has been used to encode several NP-complete problems including combinatorial graph problems such as Hamiltonian circuits and 3-coloring, propositional satisfiability (both conjunctive normal form *CNF* and non-CNF expressions), product configuration, AI planning, and computer aided verification problems as presented in this work, for references see e.g., [59, 61, 68].

#### 4.1 The Smodels System

There is a tool, the Smodels system [60, 68], which provides an implementation of logic programs as a rule-based constraint programming framework. It finds stable models of a logic program, and can also tell when the program has no stable models.

The implementation is based on backtracking search technique similar to the Davis Putnam method (see e.g., [27]), and it uses a generalization of the well-founded semantics [71] to approximate the stable models and to prune the search space. The Smodels implementation needs space linear in the size of the input program [68]. The Smodels seems to be the most efficient implementation of the stable model semantics currently available and it has been applied successfully in a number of areas, for references see e.g., [68].

The stable model semantics is defined using rules of the form (1) above. We employ some extensions, called *extended rules*, which can be seen as compact shorthands for a set of basic rules. The **Smodels** version 2 handles these extended rules directly [61, 68]. We will now discuss these extensions and their semantics. For an alternative discussion, see Section 3 of [P6].

First of the extended rules are *conflict rules*, which are rules of the form:  $h \leftarrow 2\{a_1, \ldots, a_n\}$ . The semantics of this rule is that if two or more atoms

<sup>3</sup>Note that in our use here  $B^+ = \emptyset$ .

from the set  $a_1, \ldots, a_n$  belong to the model, then also the atom h will be in the model. It is easy to see that this rule can be encoded by using  $\frac{N^2-N}{2}$  basic rules of the form:  $h \leftarrow a_i, a_j$ .

There is also a linear translation for conflict rules based on adding  $\mathcal{O}(N)$  (short, constant size) new rules and  $\mathcal{O}(N)$  new atoms to the program. The intuition behind this translation is that it is possible to implement a ripple-carry adder style Boolean circuit which outputs true iff less than two of the inputs are true, and the added rules simulate the behavior of this circuit. For a more general way of handling these constraints see Sect. 2.2 of [68].

The conflict rules are very useful for encoding conflict relations between transitions of a Petri net. Having them directly supported by Smodels improved the performance in many cases. This was observed during preliminary experimental work for the publication [P1]. When conflict rules were replaced by the  $\frac{N^2-N}{2}$  basic rules as described above, Smodels running times were significantly increased.

We also use the so called *integrity rules* in the programs. They are rules with no head, i.e., of the form:  $\leftarrow a_1, \ldots, a_n, not(b_1), \ldots, not(b_m)$ . The semantics is given by the following<sup>4</sup>: First we add two new atoms to the program, call them contradiction and bad. Next we add new rule to the program: contradiction  $\leftarrow$  bad, not (contradiction). It is easy to see that any model containing bad is not a stable model when this rule has been added. Now we can replace each integrity rule with a rule having bad as the head, i.e., the rule becomes: bad  $\leftarrow a_1, \ldots, a_n, not(b_1), \ldots, not(b_m)$ . It is easy to see that any set of atoms, such that  $a_1, \ldots, a_n$  are in a model and atoms  $b_1, \ldots, b_m$  are not in a model, is not a stable model. It is also easy to see that adding one integrity rule to a program does not create any new stable models, and neither does adding any set of integrity rules.

The last extended rule we use is called a choice rule and is of the following form:  $\{h\} \leftarrow a_1, \ldots, a_n, not (b_1), \ldots, not (b_m)$ . The semantics is the following: A new atom h' is introduced to the program, and the rule is replaced by two rules:  $h \leftarrow a_1, \ldots, a_n, not (b_1), \ldots, not (b_m), not (h')$ , and  $h' \leftarrow not (h)$ . The atom h' is removed from any stable models it appears in, and the rest of the model gives the semantics for the extended rule.

#### 4.2 Motivation for Using Stable Models

In this work logic programs with stable models are used as a formalism into which several NP-complete problems have been mapped into. Here we briefly discuss our motivation for using stable models over other formalisms for solving NP-complete problems like e.g., propositional satisfiability (SAT) or mixed integer programming (MIP).

Our motivations for using logic programs with stable model semantics could be summed up as follows (in no particular order). Some of them are scientific, while others are more of a social nature.

We needed to efficiently encode conflicts using logic program rules of the form ← 2{a<sub>1</sub>,..., a<sub>n</sub>} and a similar construct was not supported by academic SAT systems without a substantial blow-up in formula size

<sup>&</sup>lt;sup>4</sup>For a 3-SAT translation using this technique, see page 6 of [68].

at the time this work began [33]. Also at that time to our knowledge there were no academic satisfiability checkers which would handle non-CNF formulas.<sup>5</sup> The Smodels could handle both these features nicely. To our knowledge the first academic SAT checker supporting both these features is BCSat [46] which was not yet available when the first publications were created. We also did not have access to the commercial Prover satisfiability checker [66], which has these features.

- While the MIP approach could handle the constraints of the form

← 2{a<sub>1</sub>,..., a<sub>n</sub>} we could not find an academic MIP solver with

performance approaching that of Smodels. The special purpose MIP

solver of [48, 49] does do much better than general purpose solvers but

was not available when our work began. Moreover, their algorithms

are specific to complete finite prefixes which limits their applicability

to other domains.

- The Smodels system has linear memory requirements in the input program size, and combined with our linear size translations of different problems in [P1], [P4], and [P6], we got methods to solve these problems in linear space.

- In the publication [P6] the LTL-X translation uses logic programs with stable model semantics in a way which is difficult to translate automatically in a succinct way to SAT.<sup>6</sup> For example, the translation for until formulas contains cyclic dependencies. The fact that the deductive closure of a reduct program is the least fixpoint of a (suitably defined) monotone predicate transformer perfectly matches the fact that the truth value of an until formula can also be defined as a least fixpoint of a monotone predicate transformer. (See also Appendix A, additions to publication [P6].) With propositional logic it is easy to express any fixpoint of a monotone predicate transformer, but ensuring that the fixpoint is the least fixpoint is more involved.

- The author was familiar with the stable model semantics and Smodels system already before work on [33] (finally leading to publication [P1]) began. Also substantial local knowledge and help was available when using this formalism and the Smodels system.

- The Smodels system was freely available as a C++ library under GPL license, which made it easy to integrate to other tools.

The experience gained from working with Smodels system have resulted in a constrained Boolean circuit satisfiability system BCSat first presented in [46].

With the notable exception of the LTL-X translation part of publication [P6] all the logic program translations we have presented can be converted

<sup>&</sup>lt;sup>5</sup>While not absolutely necessary, we find it easier to use non-CNF satisfiability procedure instead of a CNF one. Of course it is straightforward to translate a constrained Boolean circuits to CNF, but it increases the implementation effort.

<sup>&</sup>lt;sup>6</sup>Best automatic translations are at least quadratic from logic programs with stable model semantics to SAT in the general case [3].

into constrained Boolean circuits of the same size by simple syntactic translation (and thus also to CNF formulas if need be), for more discussion see Section 3.3 of publication [P6]. We believe that such a propositional translation will have slightly better performance due to lower overhead in the solvers used. Starting from scratch we would probably take this route and use, e.g., constrained Boolean circuits with a SAT solver supporting the gate selection used by publication [P5].

#### 5 VERIFICATION WITH PREFIXES

This section is a collection of observations about model checking algorithms using complete finite prefixes, and their relation to the research done in the publications [P1]-[P4]. Most of the presentation in this section is new to the dissertation summary.

Complete finite prefixes can be seen as a symbolic representation of the reachability graph which can sometimes be exponentially more succinct that the reachability graph. This makes it interesting to develop model checking procedures based on complete finite prefixes.

Complete finite prefixes have been used in several different verification tools. McMillan was the first to introduce a deadlock checking procedure using prefixes [55] in a form of a branch-and-bound algorithm. Esparza introduced an branching time logic model checker [17]. An erratum was found in this procedure, which was fixed by Graves [32].

Melzer and Römer in [56] introduced mixed-integer-programming (MIP) as a solution method for deadlock detection using prefixes. We adapt their deadlock checking procedure in publication [P1] to logic programs with stable model semantics, and also show how to do reachability checking using the same logic programming methodology. Experimental results can be found in publication [P1], and they are quite competitive to both the MIP approach of [56] as well as an implementation of McMillan's deadlock checker described in [56]. Later in experiments of [34] we found out that by enabling the "no-lookahead" option of the underlying logic programming system we could often obtain further (sometimes quite substantial) improvements in deadlock and reachability checking running times. This new improved set of options were also used in the comparisons published in [26, 49]. All the experiments in these publications were obtained by invoking the mcsmodels tool using the option "-n" which enables the "no-lookahead" option in underlying Smodels solver.

In [48] another mixed integer programming approach was given for deadlock checking. It obtains better performance than the authors of [56] by using an application specific search procedure to solve the generated MIP instances. This procedure has been extended to handle also some reachability properties, and in [49] the authors compare against the latest implementation of our deadlock procedure described in [P1], [34]. They conclude that even though the two procedures are based on different principles, the performance of the tools are comparable on deadlock checking examples.