Espoo 2008

TKK-ICS-R3

# MODEL CHECKING TIMED SAFETY INSTRUMENTED SYSTEMS

Jussi Lahtinen

TEKNILLINEN KORKEAKOULU TEKNISKA HÖGSKOLAN HELSINKI UNIVERSITY OF TECHNOLOGY TECHNISCHE UNIVERSITÄT HELSINKI UNIVERSITE DE TECHNOLOGIE D'HELSINKI

# MODEL CHECKING TIMED SAFETY INSTRUMENTED SYSTEMS

Jussi Lahtinen

Helsinki University of Technology Faculty of Information and Natural Sciences Department of Information and Computer Science

Teknillinen korkeakoulu Informaatio- ja luonnontieteiden tiedekunta Tietojenkäsittelytieteen laitos Distribution: Helsinki University of Technology Faculty of Information and Natural Sciences Department of Information and Computer Science P.O.Box 5400 FI-02015 TKK FINLAND URL: http://ics.tkk.fi Tel. +358 9 451 1 Fax +358 9 451 3369 E-mail: series@ics.tkk.fi

© Jussi Lahtinen

ISBN 978-951-22-9444-2 (Print) ISBN 978-951-22-9445-9 (Online) ISSN 1797-5034 (Print) ISSN 1797-5042 (Online) URL: http://www.otalib.fi/tkk/edoc/

TKK ICS Espoo 2008 **ABSTRACT:** Defects in safety-critical software systems can cause large economical and other losses. Often these systems are far too complex to be tested extensively. In this work a formal verification technique called model checking is utilized. In the technique, a mathematical model is created that captures the essential behaviour of the system. The specifications of the system are stated in some formal language, usually temporal logic. The behaviour of the model can then be checked exhaustively against a given specification.

This report studies the Falcon arc protection system engineered by UTU Oy, which is controlled by a single programmable logic controller (PLC). Two separate models of the arc protection system are created. Both models consist of a network of timed automata. In the first model, the controller operates in discrete time steps at a specific rate. In the second model, the controller operates at varying frequency in continuous time. Five system specifications were formulated in timed computation tree logic (TCTL). Using the model checking tool Uppaal both models were verified against all five specifications.

The processing times of the verification are measured and presented. The discrete-time model has to be abstracted a lot before it can be verified in a reasonable time. The continuous-time model, however, covered more behaviour than the system to be modelled, and could still be verified in a moderate time period. In that sense, the continuous-time model is better than the discrete-time model.

The main contributions of this report are the model checking of a safety instrumented system controlled by a PLC, and the techniques used to describe various TCTL specifications in Uppaal. The conclusion of the work is that model checking of timed systems can be used in the verification of safety instrumented systems.

**KEYWORDS:** safety instrumented systems, model checking, real-time, Uppaal

# CONTENTS

| Li | st of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | vii                                                                              |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 1  | Introduction1.1Model Checking1.2Work Description1.3Outline of the Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1<br>1<br>2<br>2                                                                 |

| 2  | Model Checking of Timed Systems         2.1       Timed Automata       .         2.1.1       Formal Semantics       .         2.1.2       Decision Problems in Timed Automata       .         2.1.3       Parallel Composition of Timed Automata       .         2.1.4       Symbolic Semantics, Regions and Zones       .         2.1.5       Difference Bound Matrices       .         2.1.2       Temporal Logic with Real Time       .         2.2.1       Computation Tree Logic       .         2.2.2       Timed Computation Tree Logic       .         2.3       Model Checking Tool Uppaal       .       .         2.3.1       Modelling in Uppaal       .       . | 2<br>4<br>5<br>7<br>8<br>10<br>12<br>13<br>14<br>15<br>16<br>17<br>18            |

| 3  | Timed Safety Instrumented Systems3.1Programmable Logic Controller3.2Safety Instrumented Systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | <b>19</b><br>19<br>20                                                            |

| 4  | Modelling Systems with Timed Automata4.1Modelling Real-Time Communication Protocols4.2Modelling Real-Time Controllers4.3Other Real-Time Research                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | <b>21</b><br>21<br>23<br>24                                                      |

| 5  | Case Study: Falcon5.1The Falcon Arc Protection System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 24<br>24<br>25<br>27<br>28<br>29<br>30<br>30<br>31<br>31<br>32<br>33<br>34<br>36 |

| 6  | Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37                                                                               |

| 7  | Conclusions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 40                                                                               |

|    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                  |

| Re         | References 4                                      |    |  |

|------------|---------------------------------------------------|----|--|

| Appendices |                                                   | 46 |  |

| A          | Falcon case: Discrete-time Model Related Code     | 46 |  |

| B          | Falcon case: Continuous-time Model Related Code   | 50 |  |

| С          | Falcon Case: The Discrete-time Simplified Model   | 52 |  |

| D          | Falcon Case: The Continuous-time Simplified Model | 55 |  |

# LIST OF FIGURES

| 1  | A finite state automaton                                      | 3  |  |

|----|---------------------------------------------------------------|----|--|

| 2  | A timed automaton                                             | 5  |  |

| 3  | A timed automaton with invariant constraints                  | 5  |  |

| 4  | Regions of a system                                           | 11 |  |

| 5  | The zone graph of the timed automaton in Figure 3             | 12 |  |

| 6  | An observer automaton in Uppaal                               | 18 |  |

| 7  | A TON timer with inputs IN and PT, and outputs Q and ET.      | 20 |  |

| 8  | Functionality of a TON timer                                  | 20 |  |

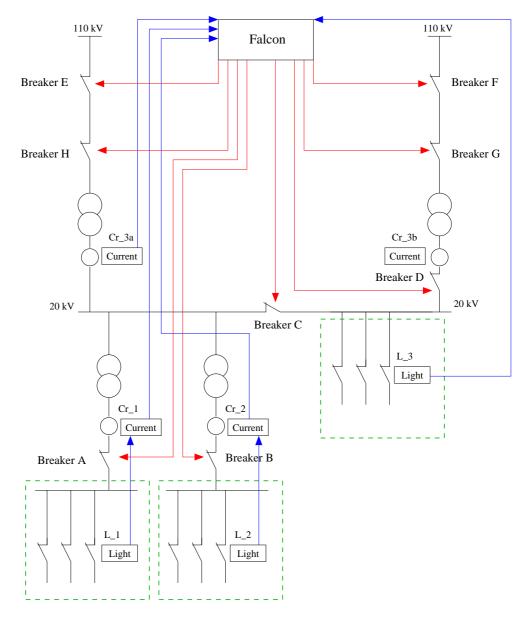

| 9  | The Falcon architecture                                       | 26 |  |

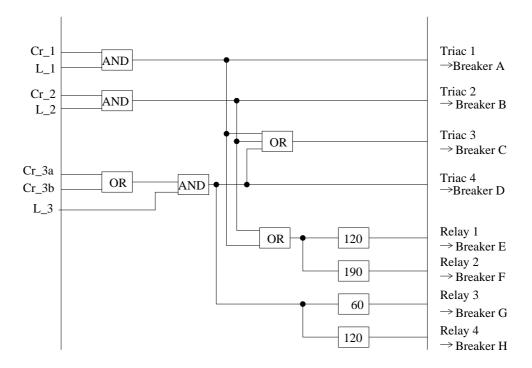

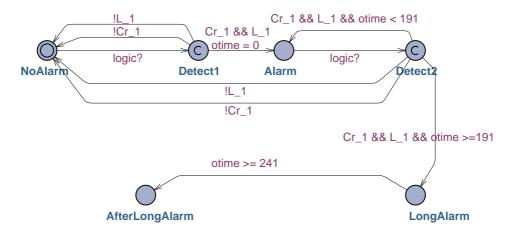

| 10 | Falcon master unit logic of the example case                  | 27 |  |

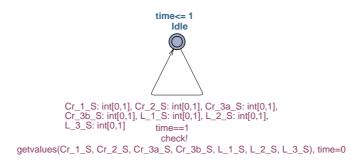

| 11 | The Falcon system model with discrete time                    | 28 |  |

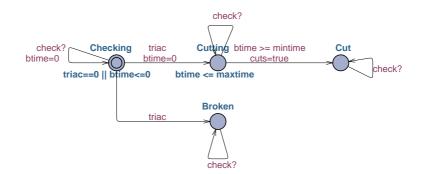

| 12 | The discrete-time breaker model                               | 30 |  |

| 13 | The discrete-time secondary breaker model                     | 30 |  |

| 14 | The falcon system of the continuous-time model                | 31 |  |

| 15 | The continuous-time model of the breaker                      | 32 |  |

| 16 | The secondary breaker model in continuous-time                | 32 |  |

| 17 | The continuous-time environment model                         | 33 |  |

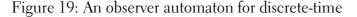

| 18 | The observer automaton used in property 3 in the continuous-  |    |  |

|    | time case                                                     | 35 |  |

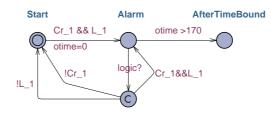

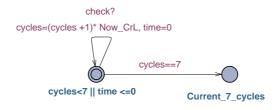

| 19 | An observer automaton for discrete-time                       | 35 |  |

| 20 | An observer automaton for continuous-time model               | 36 |  |

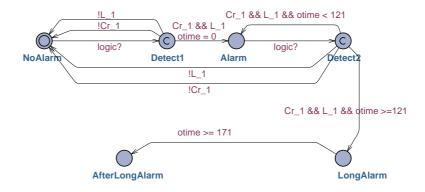

| 21 | The observer automaton used in Property 5                     | 37 |  |

| 22 | The Falcon control unit of the simplified discrete-time model | 52 |  |

| 23 | The Falcon control unit of the simplified continuous-time     |    |  |

|    | model                                                         | 55 |  |

# LIST OF SYMBOLS AND ABBREVIATIONS

| $\{d\}$                           | The fractional part of <i>d</i>                           |

|-----------------------------------|-----------------------------------------------------------|

| $\begin{bmatrix} d \end{bmatrix}$ | The integer part of d                                     |

| N                                 | The set of natural numbers                                |

| $\mathbb{R}_+$                    | The set of non-negative real numbers                      |

| $\mathbb{R}^{\dot{C}}$            | The set of clock valuations                               |

| А                                 | Temporal logic path quantifier: for all computation paths |

| Е                                 | Temporal logic path quantifier: for some computation path |

| U                                 | Temporal logic operator: until                            |

| Х                                 | Temporal logic operator: next time                        |

| BDD                               | Binary decision diagram                                   |

| CCS                               | Calculus of Communicating Systems                         |

| CTL                               | Computation tree logic                                    |

| DBM                               | Difference bound matrix                                   |

| FBD                               | Function block diagram                                    |

| IEC                               | International Electrotechnical Commission                 |

| IL                                | Instruction list                                          |

| LD                                | Ladder diagram                                            |

| PLC                               | Programmable logic controller                             |

| SFC                               | Structured function chart                                 |

| SIS                               | Safety instrumented system                                |

| ST                                | Structured text                                           |

| TCTL                              | Timed computation tree logic                              |

| TON                               | Timer on delay                                            |

| UTU                               | Urho Tuominen Oy                                          |

|                                   |                                                           |

# **1** INTRODUCTION

Software plays an increasing role in safety-critical applications where an incorrect behaviour could lead to significant economical, environmental or personnel losses. Thus, it is imperative that these safety-critical systems conform to their functional requirements. Testing is regularly used to ensure that the requirements are met. Testing can not, however, show the absence of software bugs, only their presence. If the system functionality has to be verified, some much more powerful method is needed.

### 1.1 Model Checking

Model checking [20] is an automatic technique for verifying hardware and software designs. Other, more traditional system verification techniques include simulation, testing, and deductive reasoning [20]. Deductive reasoning normally means the use of axioms and proof rules to prove the correctness of systems. Deductive reasoning techniques are often difficult and require a lot of manual intervention. On the other hand, validation techniques based on extensive testing or simulation can easily miss errors when the number of possible states of the system is very large. Model checking requires no user supervision and always produces a counterexample when the design fails to satisfy some checked property.

Model checking consists of modeling, specification, and verification. Firstly, the design under investigation has to be converted into a formalism understood by the used model checking tool. This means that the system behaviour is depicted in a modeling language. The model should comprise the essential properties of the system, and at the same time abstract away from unimportant details that only complicate the verification process [20].

Secondly, the system has some properties it must satisfy. These properties, also called specifications, are usually given in some logical formalism. For hardware and software designs, it is typical to use temporal logic [20], which can express the requirements for system behaviour over time.

After modeling and specification, only the fully automatic model checker part remains. If the design meets the desired properties, the verification tool will state that the specification is true. In case of a design flaw or an incorrect modeling or specification, a counterexample will be generated. A counterexample presents a legal execution sequence in the model that is not allowed by a specification. The analysis of the counterexample is usually impossible to do automatically and thus involves human assistance. For example, it is impossible for a computer program to decide whether the model or the specification is incorrect. The counterexample can help the designer find the errors in the specifications, in the design or in the model.

There are several model checking techniques. Many of them suffer from the state explosion problem [46]. State explosion results from the fact that the number of states in a system grows exponentially as the size of the model increases. Although the system is still finite, model checking might be too complex for even state-of-the-art computers. No fully satisfactory solution to this problem has yet been found, although symbolic representation of the state space using BDDs or reducing the needed state space using abstraction have been found useful [17, 46]. Partial order reduction [24, 46, 20] is also a typical state space reduction method. Bounded model checking [9, 10] attempts to avoid the state explosion problem by bounding the counterexample length. Nevertheless, model checking is likely to prove an invaluable tool to verify system requirements or design.

# 1.2 Work Description

In this work, a real-time safety-critical system is modelled as a network of timed automata [8]. Furthermore, the model is verified against five properties using the model checking tool Uppaal. Timed automata are chosen as the basis of the model, since the system is very dependent on correct timing. The theory of timed automata provides a framework to model and verify realtime systems.

The checked system is a safety instrumented system (SIS) that is controlled by a single programmable logic controller (PLC). The purpose of the system is to cut electricity from a protected area, if an electric arc is observed. Because of the complexity of the system, standard testing can not guarantee the correct functioning.

# 1.3 Outline of the Work

The rest of this work is organized as follows. In Section 2 timed automata are introduced and the model checking methodology of this work is presented. In Section 3 the use of programmable logic controllers in timed safety instrumented systems is discussed. A survey of related research is in Section 4. The case study of this work is presented in Section 5, where two different models of the system are shown. The results of the verification of the models are in Section 6. Finally, the conclusions of the work are in Section 7.

# 2 MODEL CHECKING OF TIMED SYSTEMS

Model checking methods often use automata as their primary modelling structure. The automata can be finite state automata, timed automata, Büchi automata or of some other automata class depending on the employed model checking method. Automata provide a way to describe the behaviour of the modelled system efficiently and precisely. Also, the modelling of specifications by automata is possible. This provides a useful model checking approach of a system. The specification automaton and the automaton of the system can be run in parallel. Usually model checking tools create a parallel composition of the system automaton and the negation of the specification automaton. If the created automaton is not empty, the specification is not met by the system. A counterexample can be easily extracted from the parallel composition.

A finite automaton [20] is a mathematical model of a system that has a constant amount of memory that does not depend on the size of the input. Automata can operate on finite or infinite words depending on definition.

**Definition 2.1 (Finite Automata)** A finite automaton over finite words A is a five tuple  $\langle \Sigma, Q, \Delta, Q^0, F \rangle$  such that

- $\Sigma$  is the finite alphabet,

- Q is the finite set of states,

- $\Delta \subseteq Q \times \Sigma \times Q$  is the transition relation,

- $Q^0 \subseteq Q$  is the set of initial states, and

- $F \subseteq Q$  is the set of final states.

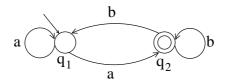

Usually automata are depicted as graphs with labeled transitions, where the set of states Q is represented by the nodes and the transition relation  $\Delta$ is transformed to the edges of the graph. An example of a finite automaton is in Figure 1.

Figure 1: A finite state automaton

In the example automaton  $\Sigma = \{a, b\}$ , the set of states  $Q = \{q1, q2\}$ ,  $Q^0 = \{q1\}$  and  $F = \{q2\}$ . Initial states are marked with an incoming arrow. Final states are the ones with a double circle. In the example the transition relation is such that  $\Delta = \{(q1, a, q1), (q1, a, q2), (q2, b, q2), (q2, b, q1)\}$ .

The following definitions follow closely [20]. A word v is a sequence of  $\Sigma^*$  whose length is denoted by |v|. The *i*th input letter of the word v is denoted by v(i). A run  $\rho$  over v is a path in the automaton graph from an initial state  $\rho(0)$  to a state  $\rho(|v|)$ . Formally, a run  $\rho$  of an automaton A over v is a mapping  $\rho : \{0, 1, ..., |v|\} \mapsto Q$  such that:

- The first state is an initial state,  $\rho(0) \in Q^0$ .

- Moving from ρ(i) to ρ(i + 1) upon reading the *i*th input letter v(i) is consistent with the transition relation. For every i, 0 ≤ i < |v|(ρ(i), v(i), ρ(i + 1)) ∈ Δ.</li>

A run  $\rho$  over a word v is accepting if it ends in a final state,  $\rho(|v|) \in F$ . The language of an automaton A, L(A) is the set of words accepted by A.

# 2.1 Timed Automata

Timed automata [3, 8] are used in the model checking of real time systems. Alternative methods with the same goal are e.g., Petri Nets, timed process algebras, and real time logics [16, 40, 42, 50]. Timed automata are especially needed when the correct functioning depends fundamentally upon real time considerations. Such a situation is typical when the system must interact with a physical process.

Modal logic [21] considers only the ordering of sequential events, i.e., it abstracts away from time. However, in the linear time model an execution of a system can be modelled as a timed trace, in which the events and their actual time points are denoted. The behaviour of a system is a set of these timed traces. A set of timed traces can be thought of as a set of sequences that form a language. If the language is regular, it is possible to use finite automata in the process of specification and verification of the system.

In the original theory [3] timed automata are essentially finite state automata extended with real valued clock variables and infinite input. The functionality of the automaton can be restricted by the conditions set to the clocks.

A timed automaton is an abstraction of a real time system. It is basically a finite state automaton with a set of clock variables. The variables model the logical clocks of the system, and they are initialized with zero when the system is started. After this, all the clock variables are increased at the same rate. In addition to the clocks, a timed automaton also has guard constraints on its transitions. A transition can be taken, when the guard constraint on the edge of the automaton evaluates to true. These guards restrict the behaviour of the automaton by constraining the values of the clocks allowed for the transition to be enabled.

Finally, the clock variables can also be reset. This can only happen when a transition is taken. Multiple clocks can be reset at once. The clock variables are reset after the guard constraint has been evaluated as true.

The problem with the original timed automaton is that the guards only enable the transitions. The automaton can not be forced to make transitions. This leads to a possible situation where the automaton stays forever in some state [8].

A simplified version of a timed automaton, a timed safety automaton [29] is a timed automaton with local state invariants. A timed safety automaton may stay in a node only as long as the clocks satisfy the invariant of the node. These invariant conditions can eliminate the problem because they can force the automaton to make a transition. Because of its simple structure, the timed safety automaton has been adopted in many timed automata verification tools including Uppaal [34] and Kronos [51].

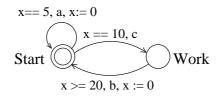

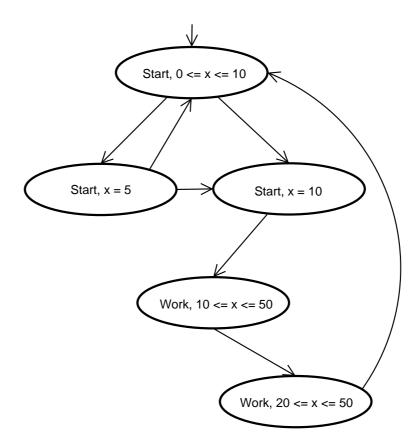

Figure 2: A timed automaton

An example of a timed automaton is in Figure 2. The timed automaton in Figure 2 has two locations: *Start* and *Work*, and a clock variable x. *Start* has a double circle surrounding it indicating the initial location insted of the incoming arrow in Figure 1. The automaton has three transitions. Each transition has a guard and an action. There is a transition from *Start* to itself. The guard of this transition states that the transition can only be taken, when the clock variable has value 5 (x == 5). The action related to this transition is a. The clock is reset after the transition (x := 0). The transition from *Start* to *Work* has a guard x == 10 and an action c. This transition does not reset the clock variable. The third transition from *Work* to *Start* has a guard  $x \ge 20$  and an action b. The guard states that the transition can not be taken unless x is at least 20. The transition also resets the clock x. It is also possible to remain in either one of the locations forever. The automaton has no location invariants.

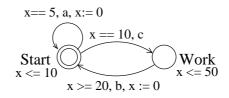

When location invariants are added to the example automaton, the result is a timed safety automaton (Figure 3). It has an invariant in both locations. The invariants specify a local condition that *Start* must be left before x becomes greater than 10, and *Work* must be left before x becomes greater than 50.

Figure 3: A timed automaton with invariant constraints

This work concentrates on timed safety automata, and will herefrom refer to them as timed automata or automata.

#### 2.1.1 Formal Semantics

Basic definitions of the syntax and semantics of timed automata are given. The definitions follow the semantics in [8]. The following notations are used:  $\mathbb{N}$  is the set of natural numbers, C is the set of clocks, B(C) is a set of simple conjunctions of the form  $x \bowtie c$  or  $x - y \bowtie c$ , where  $x, y \in C, c \in \mathbb{N}$  and  $\bowtie \in \{<, \leq, =, \geq, >\}$ . A timed automaton is a finite graph, with transitions labelled with conditions over and resets of non-negative real valued clock variables. **Definition 2.2 (Timed Automata)** A timed automaton A is defined as a tuple  $\langle L, l_0, C, \Sigma, E, I \rangle$ , where

- *L* is a finite set of locations (or nodes),

- $l_0 \in L$  is the initial location,

- *C* is the finite set of clocks,

- $\Sigma$  is the finite set of actions,

- E ⊆ L×Σ×B(C)×2<sup>C</sup>×L is the finite set of edges between locations with an action, a guard, and a set of clocks to be reset; and

- $I: L \longrightarrow B(C)$  assigns invariants to locations.

Next the semantics of a timed automaton is defined. A clock valuation is a function  $u : C \to \mathbb{R}_+$  from the set of clocks to the non-negative reals. Let  $\mathbb{R}^C$  be the set of clock valuations. Let  $u_0(x) = 0$  for all  $x \in C$ . In our notation guards and invariants can be considered as sets of clock valuations.  $u \in I(l)$  means that the clock valuation u satisfies all the constraints in I(l).

For  $d \in \mathbb{R}_+$ , let u + d denote the clock assignment that maps all  $x \in C$  to u(x) + d, and for  $r \subseteq C$ , let  $[r \mapsto 0]u$  denote the clock assignment that maps all clocks in r to 0 and agree with u for the other clocks in  $C \setminus r$ .

The semantics of a timed automaton is defined as a labelled transition system where a state consists of the current location, and the current values of the clock variables. Thus, there are two types of transitions between states. In a delay transition the automaton delays for some time (denoted  $\stackrel{d}{\rightarrow}$ , where d is a non-negative real). In an action transition an enabled edge is followed (denoted  $\stackrel{a}{\rightarrow}$ , where a is an action). Consecutive delay-action transitions can be denoted as  $\stackrel{d}{\rightarrow}$ .

**Definition 2.3 (Semantics of Timed Automata)** Let  $(L, l_0, C, \Sigma, E, I)$  be a timed automaton. The semantics is defined as a labelled transition system  $\langle S, s_0, \rightarrow \rangle$ , where  $S \subseteq L \times \mathbb{R}^C$  is the set of states,  $s_0 = (l_0, u_0)$  is the initial state, and  $\rightarrow \subseteq S \times \{\mathbb{R}_+ \cup \Sigma\} \times S$  is the transition relation such that:

- $(l, u) \xrightarrow{d} (l, u + d)$  if  $\forall d' : 0 \le d' \le d \Longrightarrow u + d' \in I(l)$ , and

- $(l, u) \xrightarrow{a} (l', u')$  if there exists  $e = (l, a, g, r, l') \in E$  such that  $u \in g, u' = [r \mapsto 0]u$ , and  $u' \in I(l)$ .

The transition relation is intuitively such that it allows two kind of transitions. Either all the clock values of the automata are increased by some positive value, or time does not advance at all while an edge of the automaton is taken. In the first case the transition must be allowed by the location invariants. In the second case the transition can only be taken if the guards

6

evaluate to true, and the invariant constraints are not violated after the transition's reset phase. As an example of the semantics, the timed automata in Figure 3 could have the following reachable states:

$$(Start, x = 0) \xrightarrow{5} (Start, x = 5) \xrightarrow{a} (Start, x = 0) \xrightarrow{10} (Start, x = 10) \xrightarrow{c} (Work, x = 10) \xrightarrow{38} (Work, x = 48) \xrightarrow{b} (Start, x = 0)...$$

## 2.1.2 Decision Problems in Timed Automata

In model checking, we need to be able to ask questions about the functioning of the automaton used as a model. Operational semantics is the basis for verification of timed automata [8]. An important question to ask about a timed automaton is the reachability of a certain state in the automaton. These kind of questions are used to formalize safety properties of the system. It is also important to know how to compare the functioning of two independent automata. Two main indications of similarity are language inclusion and bisimilarity. Language inclusion means that the set of traces produced by an automaton A is a subset of the set of traces produced by a different automaton B. Bisimilarity is a stronger measure of similarity than language inclusion. A formal definition of bisimulation is presented in what follows. Next, some definitions for language inclusion, bisimulation and reachability in timed automata are given. The definitions in [8] are closely followed.

A timed action (t, a) is a pair, where  $a \in \Sigma$  is an action performed by the automaton A at time point  $t \in \mathbb{R}_+$ . The absolute time t is called the time-stamp of the action a. A timed trace  $\xi = (t_1, a_1)(t_2, a_2)(t_3, a_3)...$  is a sequence of timed actions where  $t_i \leq t_{i+1}$  for all  $i \geq 1$ .

**Definition 2.4** A Run of a Timed Automaton  $A = \langle L, l_0, C, \Sigma, E, I \rangle$  with initial state  $\langle l_0, u_0 \rangle$  over a timed trace  $\xi = (t_1, a_1)(t_2, a_2)(t_3, a_3)...$  is a sequence of transitions:  $\langle l_0, u_0 \rangle \xrightarrow{d_1 a_1} \langle l_1, u_1 \rangle \xrightarrow{d_2 a_2} \langle l_2, u_2 \rangle \cdots$  satisfying the condition  $t_i = t_{i-1} + d_i$  for all  $i \ge 1$ .

The timed language L(A) is the set of all timed traces  $\xi$  for which there exists a run of A over  $\xi$ .

Language inclusion problem is undecidable for timed automata [3]. This is because timed automata are not determinizable in general. If the time stamps of the traces are not taken into consideration, we can define the untimed language  $L_{untimed}(A)$  as the set of all traces in the form:  $a_1a_2a_3...$  for which there exists a timed trace  $\xi = (t_1, a_1)(t_2, a_2)(t_3, a_3)... \in A$ . The language inclusion problem for these untimed languages is decidable [3].

It has been shown that timed bisimulation is decidable [15]. Timed bisimulation is introduced for timed process algebras in [50], and can be extended to timed automata [8].

$\Sigma, E^2, I^2$  is a symmetrical binary relation satisfying the following condition:

for all  $(s_1, s_2) \in R$ ,

if  $s_1 \xrightarrow{\sigma} s'_1 \in E^1$  for some  $\sigma \in \Sigma$  and  $s_1, s'_1 \in L^1$ , then  $s_2 \xrightarrow{\sigma} s'_2 \in E^2$  and  $(s'_1, s'_2) \in R$  for some  $s_2, s'_2 \in L^2$ .

if  $s_2 \xrightarrow{\sigma} s'_2 \in E^2$  for some  $\sigma \in \Sigma$  and  $s_2, s'_2 \in L^2$ , then  $s_1 \xrightarrow{\sigma} s'_1 \in E^1$  and  $(s'_1, s'_2) \in R$  for some  $s_1, s'_1 \in L^1$ .

Two automata are timed bisimilar iff there is a bisimulation containing the initial states of the automata.

In the case of bisimulation, an untimed version is also decidable [35]. We just consider a timed transition  $s_1 \xrightarrow{d} s_2$  as an empty transition  $s_1 \xrightarrow{\varepsilon} s_2$ . The alphabet of the automaton is the replaced with  $\Sigma \cup \{\varepsilon\}$ .

#### Definition 2.6 (Reachability Analysis of Timed Automata)

Let  $\langle l, u \rangle \to \langle l', u' \rangle$  if  $\langle l, u \rangle \xrightarrow{\sigma} \langle l', u' \rangle$  for some  $\sigma \in \Sigma \cup \mathbb{R}_+$ . Let  $\to^*$  denote *n* consecutive transitions, where  $n \in \mathbb{N}$ . For an automaton with initial state  $\langle l_0, u_0 \rangle$ ,  $\langle l, u \rangle$  is reachable iff  $\langle l_0, u_0 \rangle \to^* \langle l, u \rangle$ . More generally, given a constraint  $\phi \in B(C)$  we say that the configuration  $\langle l, \phi \rangle$  is reachable if  $\langle l, u \rangle$  is reachable for some *u* satisfying  $\phi$ .

Reachability analysis offers a lot of model checking properties. Negations of reachability properties can be used to express invariant properties. For example, a system is always in a safe state if the failure states of the system are not reachable. In addition, reachability analysis of timed automata offers a way to examine bounded liveness properties. These properties state that some state will be reached within a given time. The property can be transformed into an invariant property using an additional automaton.

#### 2.1.3 Parallel Composition of Timed Automata

A parallel composition of timed automata [3] is an operation used to describe complex systems using simpler subsystems. A parallel composition describes the joint functioning of several automata concurrently.

In an untimed version of the parallel composition, it can be defined using the traces of the automata. An untimed automaton is totally determined by the set of its traces. A parallel composition of these trace sets is the set of traces such that for each automaton the relevant projection is possible in the automaton. If the event sets of the automata are distinct, the parallel composition is just the union of the trace sets. If the event sets of the automata are identical, the parallel composition is the set theoretic intersection of the trace sets.

Next, the parallel composition of timed automata is defined. The definitions in [3] are closely followed. The projection of an untimed trace  $\xi = a_1 a_2 a_3 \dots$  onto an automaton  $A_i$ , written  $\xi \lceil A_i$  is formed by taking only

the events of the trace  $\xi$  that are in the event set of the automaton  $A_i$ . The projection is only considered when the intersection  $\xi \cap A_i$  is nonempty. The parallel composition  $||_i A_i$  for a set of untimed automata  $A_i$  is thus an untimed automaton with the event set of  $\bigcup_i A_i$ . The trace set of the parallel composition is the set of traces that exist in at least one of the component automata, and can be projected to all of the component automata.

The parallel composition operator can be extended to timed automata as well. The projection operator is changed so that in the parallel composition of two processes the common events should always happen at the same time. A composition of two traces with common events will always result in either an empty set or a single trace.

If, for example, automaton  $A_1$  with an event set  $\{a, b\}$  has only a single trace

$$\xi_1 = (a, 1)(b, 2)(a, 4)(b, 5)(a, 7)(b, 8)\dots$$

and an automaton  $A_2$  with an event set  $\{a, c\}$  has three possible traces:

$\begin{aligned} \xi_2 &= (a, 1)(a, 4)(a, 7) \dots \\ \xi_3 &= (a, 1)(a, 2)(a, 3) \dots \\ \xi_4 &= (c, 3)(c, 6)(c, 9) \dots \end{aligned}$

The resulting parallel composition  $A_1 || A_2$  would have an event set of  $\{a, b, c\}$  and a set of traces:

$\xi_{C1} = (a, 1)(b, 2)(a, 4)(b, 5)(a, 7)(b, 8)...$  $\xi_{C2} = (a, 1)(b, 2)(c, 3)(a, 4)(b, 5)(c, 6)(a, 7)(b, 8)...$

These are the compositions of trace pairs  $(\xi_1, \xi_2)$  and  $(\xi_1, \xi_4)$ . The trace pair  $(\xi_1, \xi_3)$  results in an empty trace because the common event *a* takes place at different time stamps in the traces.

Following the definitions in [20], the actual timed automaton that represents the parallel composition of two automata  $A_1 = \langle L_1, l_0^1, C_1, \Sigma_1, E_1, I_1 \rangle$ and  $A_2 = \langle L_2, l_0^2, C_2, \Sigma_2, E_2, I_2 \rangle$  is the timed automaton:

$$A_1 \| A_2 = \langle L_1 \times L_2, l_0^1 \times l_0^2, C_1 \cup C_2, \Sigma_1 \cup \Sigma_2, E, I \rangle$$

where  $I(s_1, s_2) = I_1(s_1) \wedge I_2(s_2)$  and the transition relation E is given by the following rules:

- For  $a \in \Sigma_1 \cup \Sigma_2$ , if  $\langle s_1, a, \phi_1, \lambda_1, s'_1 \rangle \in E_1$  and  $\langle s_2, a, \phi_2, \lambda_2, s'_2 \rangle \in E_2$ , then *E* will contain the transition  $\langle (s_1, s_2), a, \phi_1 \land \phi_2, \lambda_1 \cup \lambda_2, (s'_1, s'_2) \rangle$ .

- For  $a \in \Sigma_1 \Sigma_2$  if  $\langle s, a, \phi, \lambda, s' \rangle \in E_1$  and  $t \in L_2$ , then *E* will contain the transition  $\langle (s, t), a, \phi, \lambda, (s', t) \rangle$ .

- For  $a \in \Sigma_2 \Sigma_1$  if  $\langle s, a, \phi, \lambda, s' \rangle \in E_2$  and  $t \in L_1$ , then *E* will contain the transition  $\langle (t, s), a, \phi, \lambda, (t, s') \rangle$ .

The locations of the parallel composition automaton are pairs of locations from the component automata. Invariants are conjunctions of the invariants in the component automata. For each pair of transitions from the component automata with the same action, there will be a transition in the composite automaton. The transition source state is a pair in the composition that consists of the source states of the individual automata. The transition target location is such a pair that is formed from the target locations of the individual transitions. If an action only exists in one of the automata, the composition transition will be such that the other automaton remains unchanged. Such a transition is created for each location of the other automaton.

#### 2.1.4 Symbolic Semantics, Regions and Zones

A timed automaton with real-valued clocks leads to an infinite transition system. In order to perform efficient verification of timed automata, a finite transition system must be acquired. The basis of decidability results in timed automata comes from the concept of region equivalence over clock assignments [3]. The next section follows closely the definitions in [8].

**Definition 2.7 (Region Equivalence)** Let k be a function, called a clock ceiling, mapping each clock  $x \in C$  to a natural number k(x) (i.e. the ceiling of x). For a real number d, let  $\{d\}$  denote the fractional part of d, and let  $\lfloor d \rfloor$  denote its integer part. Two clock assignments u, v are region-equivalent, denoted  $u \sim_k v$ , iff

- for all x, either  $\lfloor u(x) \rfloor = \lfloor v(x) \rfloor$  or both u(x) > k(x) and v(x) > k(x),

- for all x, if  $u(x) \le k(x)$  then  $\{u(x)\} = 0$  iff  $\{v(x)\} = 0$ ; and

- for all x, y if  $u(x) \le k(x)$  and  $u(y) \le k(y)$  then  $\{u(x)\} \le \{u(y)\}$  iff  $\{v(x)\} \le \{v(y)\}.$

A region is an equivalence class denoted [u] that is the set of regionequivalent clock assignments with u. Using the region construction, a finite partitioning of the state space is possible. This is because each clock has a maximal constant value k(x) which makes the number of regions finite. The constant value k(x) is the highest value, against which the clock is compared.

Also,  $u \sim v$  implies that the states of the timed automaton (l, u) and (l, v) are bisimilar with regard to the untimed bisimulation for any location  $l \in L$ . The equivalence classes can be used to create a finite-state region automaton. Using a region automaton, many of the decision problems of timed automata become decidable. The transition relation between symbolic states of a region automaton is the following:

- $\langle l, [u] \rangle \Rightarrow \langle l, [v] \rangle$  if  $\langle l, u \rangle \xrightarrow{d} \langle l, v \rangle$  for a positive real number d, and

- $\langle l, [u] \rangle \Rightarrow \langle l', [v] \rangle$  if  $\langle l, u \rangle \xrightarrow{a} \langle l', v \rangle$  for an action a.

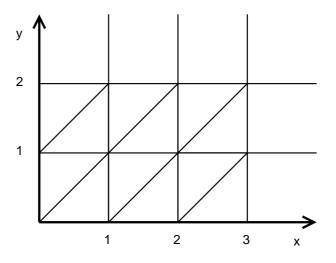

Figure 4: Regions of a system

An example of the regions of an automaton with two clocks x and y is in Figure 4. The maximal comparison constants of x and y are 3 and 2, respectively. The example has 60 different time regions. All open areas, lines and intersections count as a region. Possible regions of the example are (x = 1, y = 1) (a corner point), (x = 2, y < 1) (a line segment),  $\{(1 < x < 2) \land (y < x)\}$  (an open area).

The intuitive idea of using regions is the following: if two states, which correspond to the same location of a timed automaton, have clock values with the same integral parts and the ordering of the fractional parts, the two states will behave similarly.

The problem of the region automata is the exponential growth in the number of regions as the number of clocks or the maximal constants increase. Clock zones [1] can represent the state space of a timed automaton more efficiently. [19, 29]

The idea of clock zones is that most of the time regions are not needed, and some of them can be united. A clock zone is a set of clock assignments i.e. a conjunction of inequalities or a convex union of clock regions, that compare a clock value or the difference between two clock values against an integer. The following types of inequalities are allowed:

$$x < c, x \le c, c < x, c \le x, x - y < c, x - y \le c$$

where c is an integer, x, y are clocks. For a clock zone  $\phi$ , the set of clock values satisfying  $\phi$  will also be denoted  $\phi$ . If an automaton A has k clocks, then a clock zone  $\phi$  expressed in terms of these clocks is a convex subset in k-dimensional Euclidean space [20].

For example, one possible zone graph of the timed automaton in Figure 3 is in Figure 5.

Figure 5: The zone graph of the timed automaton in Figure 3

## 2.1.5 Difference Bound Matrices

Difference bound matrix (DBM) [19] is a way to represent a clock zone in a compact form. We define a difference bound matrix following the definition in [20]. Its definition requires the use of a special clock  $c_0$  that always has value 0. The difference bounded matrix is indexed by the set of clocks  $C_0 = C \cup \{c_0\}$ . The special clock  $c_0$  has the index 0. The entries of the matrix  $D_{i,j}$  have the form  $(d_{i,j}, \prec_{i,j})$  that expresses a comparison of two clock values  $c_i$  and  $c_j$  with an integer  $d_{i,j}$ . The comparison operator  $\prec_{i,j}$  is either <or  $\leq$ . The matrix entries represent inequalities  $c_i - c_j \prec d_{i,j}$ , where  $d_{i,j}$  is either integer or  $\infty$ . The special clock  $c_0$  can be used to represent inequalities that only concern one clock variable. As an example, consider the following clock zone:

$$c_2 - c_1 < -2 \land c_2 \le 1 \land c_1 \le 3$$

The difference bounded matrix is:

$$D = \begin{pmatrix} (0, \le) & (0, \le) & (0, \le) \\ (3, \le) & (0, \le) & (\infty, <) \\ (1, \le) & (-2, <) & (0, \le) \end{pmatrix}$$

A zone can be represented by  $|C_0|^2$  atomic constraints of the form  $c_1 - c_2 \prec n$ . Each pair is used only once. In the case of two constraints on the same pair of variables, the intersection of these constraints is mean-

ingful. These zones can be stored in  $|C_0| \times |C_0|$  sized matrices called difference bound matrices.

The zone representation is not unique. The same zone can be represented by several different matrices. In our example  $c_1 - c_0 \leq 3$  and  $c_0 - c_2 \leq 0$ implies  $c_1 - c_2 \leq 3$ . We can change  $D_{1,2}$  to  $(3, \leq)$  and obtain an alternative DBM. Generally, the sum of the upper bounds  $c_i - c_j$  and  $c_j - c_k$  is an upper bound on the clock difference  $c_i - c_k$ . Reducing the clock differences to tighten the difference bound matrix is done as follows:

If  $c_i - c_j \prec_{i,j} d_{i,j}$  and  $c_j - c_k \prec_{j,k} d_{j,k}$ , then  $c_i - c_k \prec'_{i,k} d'_{i,k}$  where  $d'_{i,k} = d_{i,j} + d_{j,k}$  and

$$\prec_{i,k}' = \begin{cases} \leq & \text{if } \prec_{i,j} = \leq \text{ and } \prec_{j,k} = \leq \\ < & \text{otherwise} \end{cases}$$

If  $(d'_{i,k}, \prec'_{i,k})$  is a tighter bound than  $(d_{i,k}, \prec_{i,k})$ , the original bound can be replaced by the new one. The operation is called tightening. The DBM is in a canonical form when no further tightening is possible. The canonical form of the DBM in our example is:

$$D = \begin{pmatrix} (0, \le) & (-2, <) & (1, <) \\ (3, \le) & (0, \le) & (3, \le) \\ (1, <) & (-2, <) & (0, \le) \end{pmatrix}$$

#### 2.2 Temporal Logic with Real Time

Temporal logic is an extension of classical logic that can be used to create formal system specifications. These formal specifications can then be checked using some model checking method. With temporal logic unambiguous descriptions such as "The system never reaches an erroneous state." or "This action always leads to the resetting of the system." can be written.

Temporal logics can be classified according to the assumed structure of time. Some temporal logics assume linear time structure, some assume a branching time structure. Computation tree logic (CTL) [20] is a branching time logic. It is used when the models that are verified are finite state systems that abstract away from time. It is assumed that an execution can be modelled as a linear sequence of system events.

Timed computation tree logic (TCTL) [2] is an extension of CTL to real time systems. For real time systems ordinary CTL is not sufficient, since a system's correctness depends on the values of the timing delays. Sometimes it is not enough if a function is known to eventually happen. In real time systems we need to know whether the action takes place within a certain time period.

In order to create real time models and specifications, using event sequences is not sufficient and therefore timed traces are needed. Timed traces associate with each state the time of the occurrence of the event. The concept of time can be modelled in different ways. In the case of timed computation tree logic a dense-time model is preferred. In a dense-time model the times of events are real numbers, that increase monotonically without a bound [3]. TCTL was created to describe CTL specifications in real time.

In TCTL, quantitative temporal operators are introduced to describe timed properties. First, the syntax and semantics of the branching-time logic CTL are reviewed. Next, the TCTL extensions to the CTL syntax are defined. TCTL semantics is also represented.

#### 2.2.1 Computation Tree Logic

In CTL time is seen as a tree-like structure in which the future in not determined. Different possible futures exist, and any of these is possible. The following section follows the notations in [20].

CTL formulas consist of logical operators, path quantifiers and temporal operators. Path quantifiers (A("for all computation paths") and E("for some computation path")) are used in a state to specify that all of the paths (A) or some of the paths (E) starting from that state have some property. The temporal operators describe properties of a path of the tree. Several temporal operators exist. Here, only some are defined, since others can be defined using them.

- X ("next") requires that the property holds at the next state of the path.

- U ("until") is a binary operator. Formula *P* U *Q* holds when *P* is true until *Q* becomes true. Also, the second argument must become true at some point.

Given a finite set of atomic propositions  $\{AP\}$ , the CTL formulas can be inductively defined as follows:

$$\begin{array}{lll} \phi & ::= & p \mid false \mid \phi_1 \to \phi_2 \mid \\ & & \mid \mathbf{EX}\phi_1 \mid \mathbf{E} \left[\phi_1 \mathbf{U} \, \phi_2\right] \mid \mathbf{A} \left[\phi_1 \mathbf{U} \, \phi_2\right] \end{array}$$

where  $p \in AP$  is an atomic proposition and  $\phi_1, \phi_2$  are CTL formulas.  $\mathbf{EX}\phi_1$  means that there is an immediate successor state that is reachable in one step, in which  $\phi_1$  is true.  $\mathbf{E} [\phi_1 \mathbf{U} \phi_2]$  requires that there is a path in which  $\phi_2$  becomes true at some time point t. Also,  $\phi_1$  must be true on that path until t.  $\mathbf{A} [\phi_1 \mathbf{U} \phi_2]$  means that for every computation path, the previous condition holds.

Other often used temporal operators are for example:  $\mathbf{EF}\phi$  for  $\mathbf{E}[true \mathbf{U}\phi]$ ,  $\mathbf{AF}\phi$  for  $\mathbf{A}[true \mathbf{U}\phi]$ ,  $\mathbf{EG}\phi$  for  $\neg \mathbf{AF}\neg\phi$  and  $\mathbf{AG}\phi$  for  $\neg \mathbf{EF}\neg\phi$ .

The semantics of CTL is defined with respect to a Kripke structure  $M = \langle S, R, L \rangle$ , where S is the set of states,  $R \subseteq S \times S$  is the total transition relation, and  $L : S \to 2^{AP}$  is the labelling function. A path in M is an infinite

sequence of states,  $\pi = s_0, s_1, s_2, ...$  such that for every  $i \ge 0, (s_i, s_{i+1}) \in R$ . We denote with  $\pi^i$  the suffix of  $\pi$  starting at  $s_i$ . Notation  $M, s \models f$  means that f holds at a state s in a structure M. Let  $Tr(s) = \{\pi = s_0, s_1, ... \mid s_0 = s\}$  be the set of possible paths starting from the state s. The satisfaction relation  $\models$  is defined inductively:

$$\begin{split} M,s &\models p \quad i\!f\!f \quad p \in L(s) \\ M,s &\models \neg \phi \quad i\!f\!f \quad M,s \nvDash \phi \\ M,s &\models \phi_1 \to \phi_2 \quad i\!f\!f \quad M,s \nvDash \phi_1 \text{ or } M,s \models \phi_2 \\ M,s &\models EX\phi \quad i\!f\!f \quad \exists s_1 \in S, \text{ s.t. } , (s,s_1) \in R \text{ and } M, s_1 \models \phi \\ M,s &\models A[\phi_1 U \phi_2] \quad i\!f\!f \quad \forall \pi = s_0, s_1, s_2 \dots \in Tr(s) : \\ &= i((M,s_i \models \phi_2) \land (\forall (j < i)M, s_j \models \phi_1)) \\ M,s &\models E[\phi_1 U \phi_2] \quad i\!f\!f \quad \exists \pi = s_0, s_1, s_2 \dots \in Tr(s) : \\ &= i((M,s_i \models \phi_2) \land (\forall (j < i)M, s_j \models \phi_1)) \end{split}$$

#### 2.2.2 Timed Computation Tree Logic

It is possible to write properties like  $\mathbf{EF}p$  in CTL. However, CTL does not provide a way to bound the time at which p happens. TCTL extends the temporal operators so that it is possible to limit their scope in time. It is possible to write for example  $\mathbf{EF}_{<5}p$  meaning that at some computation path p will become true within 5 time units. TCTL syntax is shortly:

$$\begin{array}{lll} \phi & ::= & p \mid false \mid \phi_1 \to \phi_2 \mid \\ & & \mid \mathbf{E} \left[ \phi_1 \mathbf{U}_{\sim c} \, \phi_2 \right] \mid \mathbf{A} \left[ \phi_1 \mathbf{U}_{\sim c} \, \phi_2 \right] \end{array}$$

where  $p \in AP$  is an atomic proposition,  $c \in N$ ,  $\phi_1$  and  $\phi_2$  are TCTL formulas and  $\sim \in \{<, \leq, =, \geq, >\}$ .

$\mathbf{E} \left[\phi_1 \mathbf{U}_{< c} \phi_2\right]$  means that for some computation path there exists a prefix of time length less than *c* time steps, such that at the last state of the prefix  $\phi_2$  holds, and  $\phi_1$  is true in all the states in the path until the last state.  $\mathbf{A} \left[\phi_1 \mathbf{U}_{< c} \phi_2\right]$  means that the above condition holds on every computation path. It is also possible to create TCTL formulas for time intervals. For example a formula  $\mathbf{EF}_{(a,b)}\phi$  meaning " $\phi$  holds at least once between time steps *a* and *b*" can be written  $\mathbf{EF}_{=a}\mathbf{EF}_{<(b-a)}\phi$ .

Since TCTL operates in a dense time domain and not in a discrete time domain like CTL, the next-time operator can not be used. By definition, there is no unique next time point. The computation paths in TCTL with dense time domain are maps from the real valued time domain R to states of the system. There is a unique state at every real valued time instant. For a set of states S and a state  $s \in S$  an s-path through S is a map p from R to S satisfying p(0) = s. The computation tree in dense time is a map from every

state to a set of paths starting at that state. The prefix of an *s*-path up to time t is denoted  $p_t$ . The concatenation of two *s*-paths  $p_1$  and  $p_2$  is denoted  $p_1 \cdot p_2$ .

The structure that TCTL can be defined against can not be exactly the same as in the of CTL. The TCTL structure is a triple  $M = \langle S, f, L \rangle$  where S is the set of states,  $L : S \to 2^{AP}$  is the labelling function, and f is a map giving for each  $s \in S$  a set of s-paths through S. f satisfies the tree constraint:

$$\forall s \in S. \forall p \in f(s). \forall t \in R. p_t \cdot f[p(t)] \subseteq f(s).$$

The satisfaction relation  $\models$  for TCTL is defined inductively:

$$\begin{split} M,s &\models p \quad i\!f\!f \quad p \in L(s) \\ M,s &\models \neg \phi \quad i\!f\!f \quad M,s \nvDash \phi \\ M,s &\models \phi_1 \to \phi_2 \quad i\!f\!f \quad M,s \nvDash \phi_1 \text{ or } M,s \models \phi_2 \\ M,s &\models A[\phi_1 U_{\sim c} \phi_2] \quad i\!f\!f \quad \forall p \in f(s) : \exists t \sim c, p(t) \models \phi_2 \land \\ (\forall (0 < t' < t)p(t') \models \phi_1) \\ M,s &\models E[\phi_1 U_{\sim c} \phi_2] \quad i\!f\!f \quad \exists p \in f(s) : \exists t \sim c, p(t) \models \phi_2 \land \\ (\forall (0 < t' < t)p(t') \models \phi_1) \\ \end{split}$$

#### 2.3 Model Checking Tool Uppaal

Uppaal is a tool for model checking of timed systems. Other tools for modelling and verification based on timed automata are e.g., Kronos [51] and RED [48].

The Uppaal modelling language [34] is based on networks of timed automata. A network of timed automata is a parallel composition  $A_1 | \cdots | A_n$ of timed automata  $A_1, \dots A_n$ , referred to as processes. The definition of a parallel composition varies depending on the used process calculi. In Uppaal the parallel composition operator of Calculus of Communicating Systems (CCS) [39] is used. Hand-shake synchronization with input and output actions is used for synchronous communication. Asynchronous communication happens through shared variables. For hand-shake synchronization purposes the action alphabet  $\Sigma$  in Uppaal consist of symbols *a*? for input actions and *a*! for output actions. Internal actions are represented by a distinct symbol  $\tau$ . Next we define a network of timed automata formally.

A network of timed automata has a common set of clocks and actions. The network consists of n timed automata  $A_i = (L_i, l_i^0, C, \Sigma, E_i, I_i), 1 \le i \le n$ . A location vector is  $\overline{l} = (l_1, ..., l_n)$ . We write  $I(\overline{l}) = \bigwedge_i I_i(l_i)$  as a composition of the invariant functions. Let  $\overline{l}[l'_i/l_i]$  mark the vector  $\overline{l}$  with the *i*th element  $l_i$  replaced by  $l'_i$ .

**Definition 2.8 (Semantics of a network Timed Automata)** Let  $A_i = (L_i, l_i^0, C, \Sigma, E_i, I_i), 1 \le i \le n$ . be a network of timed automata. Let  $\overline{l}_0 =$

$(l_1^0, ..., l_n^0)$  be the initial location vector. The semantics is defined as a labelled transition system  $\langle S, s_0, \rightarrow \rangle$ , where  $S = (L_1 \times \cdots \times L_n) \times \mathbb{R}^C$  is the set of states,  $s_0 = (\overline{l}_0, u_0)$  is the initial state, and  $\rightarrow \subseteq S \times \{\mathbb{R}_+ \cup \Sigma\} \times S$  is the transition relation defined by:

- $(\overline{l}, u) \to (\overline{l}, u+d)$  if  $\forall d': 0 \le d' \le d \Longrightarrow u+d' \in I(\overline{l})$

- $(\overline{l}, u) \rightarrow (\overline{l}[l'_i/l_i], u')$  if there exists  $l_i \xrightarrow{agr} l'_i$  such that  $u \in g, u' = [r \mapsto 0]u$ , and  $u' \in I(\overline{l})$ ; and

- $(\overline{l}, u) \to (\overline{l}[l'_j/l_j, l'_i/l_i], u')$  if there exists  $l_i \xrightarrow{c^2 g_i r_i} l'_i$  and  $l_j \xrightarrow{c! g_j r_j} l'_j$  such that  $u \in (g_i \land g_j), u' = [r_i \cup r_j \mapsto 0]u$  and  $u' \in I(\overline{l})$ .

# 2.3.1 Modelling in Uppaal

Modelling in Uppaal is done via a graphical user interface. Timed automaton templates can be created with the Uppaal modelling tool. Every template has its own local declaration section, where local variables and functions can be introduced. There is also a global declarations' section for global variables and functions. Finally, a section for process declaration is needed. In this part the automaton instances are created from the templates, and the parallel composition of these is declared for property checking and simulation.

In addition to creating networks of timed automata, the Uppaal modelling language is extended with several modelling features:

- Templates of automata can be defined with a set of parameters. The parameters are substituted in the process declaration part.

- Integer constants can be defined.

- Bounded integer variables (int[min, max]) can be defined.

- Binary synchronization channels can be declared.

- Broadcast channels can be declared. In broadcast synchronization one transition labelled with an output action can synchronize with several transitions labelled with an input action.

- Synchronization channels can be declared urgent by prefixing the channel declaration with the keyword urgent. When a transition labelled with an urgent synchronization is enabled (i.e., it can be taken), time is not allowed to pass. However, the synchronization transition need not be taken if other transitions are possible.

- Locations can be declared urgent. When a system is in an urgent location, no time is allowed to pass.

- Locations can be declared committed. A state is committed if one or more locations in the state are committed. When a system state is committed, no time is allowed to pass. Also, the next transition must be such that an outgoing edge of at least one of the committed locations is involved.

- Arrays of clocks, channels, constants or integers can be declared.

- Integer variables and arrays can be initialized.

#### 2.3.2 Verification in Uppaal

As specifications, Uppaal accepts a subset of TCTL formulas. In general, Uppaal does not allow nesting of temporal operators, or bounded specifications. In Uppaal syntax [] is equivalent to the TCTL **G**, or "globally".  $\langle \rangle$  is equivalent to the TCTL **F**, or "finally". The notation p - - > q (p leads to q) is an abbreviation of A[](p imply A <> q).

In Uppaal specifications, the dot character (.) is used to reference the variables and states of a particular timed automaton. For example A.l references to the location or variable l of automaton A.

In the verification process, Uppaal uses symbolic states of the timed automata  $\langle l, D \rangle$  where *l* is a location of the automaton, and *D* is a zone stored in memory as a DBM [5]. The Uppaal tool calculates the parallel composition of the timed automata in the model, and performs reachability analysis on the structure in order to verify it against a property. In other words, the tool goes through the state space, and tries to find a state, in which the property is false.

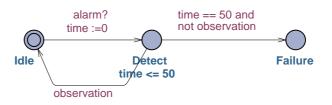

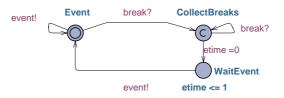

Not all specifications can be stated in TCTL as supported by Uppaal. In these cases some modelling tricks can be used. Often it is possible to create an additional observer automaton that observes the behaviour of some other automata. For instance, bounded liveness properties of TCTL can be checked using an observer automaton.

An example of an observer automaton is in Figure 6. Using the observer automaton, a bounded liveness property:

#### AG alarm imply AF $_{<50}$ observation

that can not be checked as such with Uppaal, can be stated differently as:

#### A[] not Observer.Failure

Observer automata can be used in many ways and with various properties.

Figure 6: An observer automaton in Uppaal

# **3 TIMED SAFETY INSTRUMENTED SYSTEMS**

#### 3.1 Programmable Logic Controller

A programmable logic controller (PLC) defined in IEC 1131-3 is a digital computer that can be used in automation control and safety instrumentation control.

PLCs have evolved from simple logic controllers used to control physical processes that have a number of inputs, outputs, relays and timers. PLCs were designed as a replacement to logic controllers with relays [23]. PLCs, however, can be modified to work like different logic controllers. The IEC standard describes five different programming language standards for PLCs:

- Ladder diagram (LD),

- Function block diagram (FBD),

- Structured text (ST),

- Instruction list (IL), and

- Sequential function chart (SFC).

Structured text and instruction list are textual PLC programming languages. The other three are graphical diagram based languages. PLCs support complex features such as multi-tasking and interrupts, but these are not necessary, and will only make the verification difficult. Therefore, a simple version of a PLC is used throughout this work. The characterization follows.

A PLC program uses two memory areas reserved for input and output signal values. Before each execution cycle the sensors of the PLC are polled and the values are copied to the memory area reserved for the input signals. This part of memory contains the snapshot of the input values at the time of the polling. After the PLC program has been executed, the output values are updated. A well written PLC program terminates within a bounded amount of time which is less than the cycle time of the PLC. The PLC program will initiate the next cycle after some fixed amount of time.

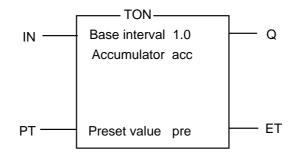

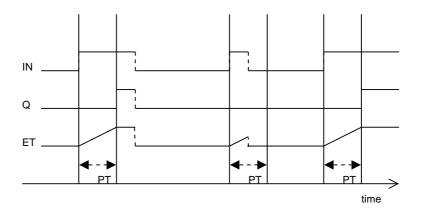

Timers are pieces of programs used with systems that need real-time features. The timers used in our simple version of a PLC are of type TON (Timer On Delay). A TON timer has some signal as an input IN, a preset integer value PT, an internal accumulator variable, timers base interval value, and two output signals Q and ET. The timer records the number of base intervals the input signal has been true, and increases the accumulator value accordingly. When the accumulator value is greater than or equal to the preset value PT, the output signal Q is turned on. ET is an integer output that has an initial value of 0. In every cycle the value of ET is increased by 1, if the IN is true, and the current value of ET is not increased. When the input IN is false, both outputs are reset to zero. The preset value PT can also be seen as an integer input. A TON timer is represented in Figure 7.

Figure 7: A TON timer with inputs IN and PT, and outputs Q and ET

The functionality of a TON timer is in Figure 8.

Figure 8: Functionality of a TON timer

#### 3.2 Safety Instrumented Systems

Industrial processes involve great risks because of dangerous temperatures, pressures and materials. Therefore, separate systems to protect environment, personnel and equipment are needed. In the ANSI/ISA-84.00.01-2004 (IEC 61511) standard a safety instrumented system (SIS) [23] is defined as an "instrumented system used to implement one or more safety instrumented functions. A SIS is composed of any combination of sensor(s), logic solver(s), and final element(s)". The purpose of a SIS is to either automatically take an industrial process to a safe state, when predetermined conditions are true; or mitigate the consequences of an industrial hazard. A SIS is designed to always work in a risk reducing manner. [23]

The sensors of a SIS collect information of the state of the process. Sensors can measure temperature, pressure, flow or other process parameters. The logic solver makes decisions of the actions taken based on the sensors' signals. A typical action is a signal sent to the final elements. Final elements are usually valves or electrical switches that have some risk reducing effect on the process.

An example of a SIS is an emergency cooling system of a reactor. The SIS has heat sensors, and a logic, which determines when the safety instrumented function is initiated. In this case the safety instrumented function is the opening of a coolant valve. Similarly, a SIS observing the pressure of a tank, initiates an open action of a pressure releasing valve.

As mentioned earlier, PLCs can be used as the logic solvers of safety instrumented systems. Since, PLCs are increasingly used in safety critical systems, testing and verification of PLC applications has become very important [23].

# **4 MODELLING SYSTEMS WITH TIMED AUTOMATA**

In this section, some research in the area of model checking with timed automata is surveyed. The research can be roughly divided into model checking of real-time communication protocols, and model checking of real-time controllers. Most of the surveyed case studies use the model checking tool Uppaal. A comprehensive tutorial on Uppaal is in [6]. In this paper the tool itself and its use is described. In addition, two extensive examples and some modelling conventions are given.

#### 4.1 Modelling Real-Time Communication Protocols

Protocol verification has been of interest to many research groups. Network and other communication protocols have been modelled and verified using Uppaal, and other modelling tools. Several protocols that have been commonly in use have been found erroneous, and corrected using Uppaal.

In [44] and [43] a fault tolerant clock synchronization mechanism for a Controller Area Network (CAN) was modelled and verified. The modelling was done using the Uppaal tool. The goal of the work was to formally verify the precision that could be achieved, and the effects of faults to the precision. In their system, master nodes regularly transfer clock synchronization messages to the slave nodes. As an essential part of this research, clock drifting was modelled using clock automata where the clocks operated in variable length cycles. In their model the clock rate could change dynamically. The clock synchronization system corrected both the offset and the drift error of the clocks. A certain precision was verified using an observer automaton that compared the clocks of the nodes.

In [7] the correctness of the Philips Audio Control Protocol was verified using the Uppaal tool. The analysis was performed on a system with two senders. Consequently, the bus collision problem was present. In addition, for an incorrect implementation of the protocol, a counterexample was found. An important observation of the paper was the usefulness of the committed locations in Uppaal. The Uppaal tool was extended to include these features. In this research, clocks with drifting timespeeds were used. The system was verified for an error tolerance of 5 % on the timing.

In [33] a Collision Avoidance Protocol was studied. The protocol was modelled and verified using two tools SPIN [31] and Uppaal. The timed aspects were easy to model with Uppaal. It was also noticed that the notion of committed locations in Uppaal supported the modelling of broadcast communication, and yielded significant reductions in time- and space-usages.

An Audio/Video protocol by Bang & Olufsen (B&O) was studied in [27]. The protocol controls the transmission of messages over a single bus, and detects collisions. The protocol was known to be faulty, although the cause of the fault could not have been pinpointed before. Using the Uppaal tool, an error trace was extracted. This led to the detection of the error in the implementation. The corrected implementation was successfully verified.

As a continuation to [27] a different Power Down protocol by Bang & Olufsen was studied in [26]. The modelling of the system resulted in the discovery of three design errors that were identified and corrected. In this paper, modelling techniques for time slicing problems with interruptions are introduced. In addition, three observer automaton techniques for property verification are introduced.

A bounded retransmission protocol is studied in [18]. In the paper a file transfer service is first specified by stating several logical properties. The bounded retransmission protocol's conformance to these properties is then checked using Uppaal and SPIN. The timed properties are checked using Uppaal.

The Pragmatic General Multicast (PGM) protocol is analyzed in [12]. The protocol intends to guarantee a reliability property: "a receiver either receives all data packets from transmissions and repairs or is able to detect unrecoverable data packet loss" A simplified model of the protocol is built and two reliability properties are checked with Uppaal. The properties were verified only with some parameter values, which the paper presents.

In [36] a method for modelling and verifying of the LEGO RCX programs is introduced. A tool is developed, which can automatically translate RCX programs into Uppaal models. Also, a system of two RCX units communicating through an infrared channel is built. In their research their IR protocol and Fischer's mutual exclusion protocol are verified. Their experiments with an actual system of two communicating RCX units showed that an Uppaal model could be created using their tool, but the model could not be verified because of its complexity.

## 4.2 Modelling Real-Time Controllers

Controllers have also been of interest to many researchers. Programmable logic controllers (PLCs) that are also analyzed in this work are analyzed in [32], [49], [4] and [38].

In [32] software analysis techniques for PLCs are developed. Various verification techniques are considered for two PLC programming languages: instruction list (IL) and sequential function charts (SFCs). In this work a formal semantics is created for both languages. A model checking method for the untimed version of a SFC program is presented. The analysis techniques are also implemented in industrial size case studies.

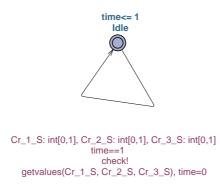

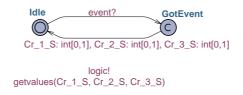

In [49] a method is developed to analyze simple PLCs written in the instruction list (IL) language. The PLCs are converted into timed automata that can be verified using Uppaal. The simple PLCs discussed in this paper use the TON timers discussed in Section 3.1.

In [4], PLCs designed graphically using Sequential Function Charts (SFCs) are converted into models that can be analyzed using model checking techniques. Two approaches are introduced. Both Cadence SMV and Uppaal are applied.

In [38], two examples of analyzing PLC applications with Uppaal are presented. The PLC timing is modelled in detail. Especially the reaction time of the PLC to a signal is observed. In the first example the PLC just reads input and writes output. The second example utilizes a TON timer: the timer is set when the PLC receives input. PLC output is set when the timer's timeout is recognized.

A distributed lift system was re-examined in [41]. The lift system was previously found faulty in [25], but the errors were fixed in an *ad hoc* manner by the system developers. In this paper the developers' solutions are analyzed using Uppaal. The solutions are shown to be incorrect. A different solution is proposed and proven to be correct.

In [28] it is shown how model checking can be used in the designing process of a deadlock free wafer scanner controller with an optimized throughput. Deadlock situations are possible, since the wafers are handled by robots that work independently. In their work a deadlock avoidance policy is first analyzed based on a finite state model using the SMV model checker. A throughput analysis can then be performed on a more detailed timed automaton model using the Uppaal tool. The two models (the SMV model and the Uppaal model) are formally related through the notion of a stuttering bisimulation introduced by Browne et al. [14]. In the throughput optimization part an observer automaton is used to measure the progress of the system. It observes the unload events of wafers that had already been scanned. The observer is used to find an infinite schedule that takes at most H time units until the first unload event, and that has at most S time units between two unload events.

In [13] a wafer scanner system is analyzed using model-based techniques. As a part of their analysis the system is modelled with the process algebraic language  $\chi$  (Chi) [47]. The model is then translated into Uppaal timed automata. Some properties are then verified using the Uppaal model.

In [11] a turntable system is analyzed using various model checking tools. A  $\chi$  (Chi) [47] simulation model is translated into model written in the input languages of CADP [22], SPIN and Uppaal. They concluded that Uppaal is the easiest to translate to. Verification of properties with fairness constraints [20] can be done in CADP and SPIN but is impossible in Uppaal.

In [37] a prototype gear controller is designed and analyzed. Uppaal is used to verify the design. The paper also introduces a method to verify bounded response time properties in Uppaal without an observer automaton. Extra variables (boolean variables and clock variables) are used instead.

# 4.3 Other Real-Time Research

In [30], techniques for generating timed test cases are introduced. In the paper the examined environment and the system under test are both modelled as timed automata. Using the presented techniques, both single purpose, and coverage based test cases are then obtained as counterexamples given by Uppaal.

# 5 CASE STUDY: FALCON

#### 5.1 The Falcon Arc Protection System

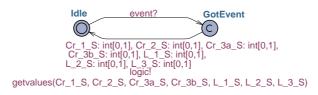

The Falcon arc protection system is designed by the engineering company Urho Tuominen Oy (UTU). The system is designed to increase personnel safety and minimize material damages in case of an electric arc, e.g., in switchgear. This is accomplished by cutting off the electricity, when an electric arc is observed. The Falcon system consists of the UTU-Falcon master unit, several light sensors and several current sensors. The master unit is implemented as a programmable logic controller (PLC). It is possible to design new logical protection architectures that can be uploaded to the master unit. An example of such a logic is in Figure 10.

The devices used to cut electricity are circuit breakers. Circuit breakers are automatically-operated switches that operate in a matter of milliseconds. Their operation is somewhat similar to fuses, but circuit breakers can be reset either automatically or manually.

The master unit operates in cycles. On each cycle, the master unit reads the inputs from its sensors and sends output signals according to its programmed logic. Typically the master unit reacts to simultaneous light and current alarms by giving a tripping command to the circuit breakers.

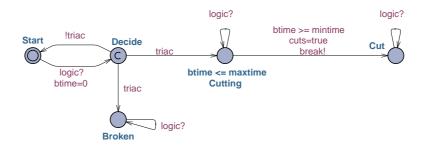

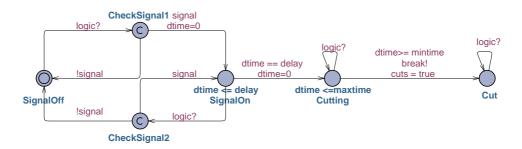

The arc protection system can also be designed to work selectively. This means that electricity is not cut off in every part of the protected area. Instead, only the affected areas are cut off. If the electrical arc does not disappear, an even larger area must be shut down. This kind of selective behaviour is created by placement of the breakers, and the delay components inside the Falcon master unit. The delay components are TON timers introduced in Section 3.1. Intuitively, as soon as an alarm is detected, it is responded to. If the alarm does not disappear, the TON timers in the master unit logic receive continuous input. After some preprogrammed number of cycles, the TON timers give out a signal to some secondary breakers. The secondary breakers will cut off the electricity more extensively.