# A STUDY OF THE SCALING AND ADVANCED FUNCTIONALITY POTENTIAL OF PHASE CHANGE MEMORY DEVICES

## Submitted by

## **Hasan Hayat**

to the University of Exeter as a thesis for the degree of Doctor of Philosophy (PhD) in Engineering, November 2016.

This thesis is available for Library use on the understanding that it is copyright material and that no quotation from the thesis may be published without proper acknowledgement.

I certify that all material in this thesis which is not my work has been identified and that no material is included for which a degree has previously been conferred upon me.

Hasan Hayat

#### Abstract

As traditional volatile and non-volatile data storage and memory technologies such as SRAM, DRAM, Flash and HDD face fundamental scaling challenges, scientists and engineers are forced to search for and develop alternative technologies for future electronic and computing systems that are relatively free from scaling issues, have lower power consumptions, higher storage densities, faster speeds, and can be easily integrated on-chip with microprocessor cores. This thesis focuses on the scaling and advanced functionality potential of one such memory technology i.e. Phase Change Memory (PCM), which is a leading contender to complement or even replace the above mentioned traditional technologies.

In the first part of the thesis, a physically-realistic Multiphysics Cellular Automata PCM device modelling approach was used to the study the scaling potential of conventional and commercially-viable PCM devices. It was demonstrated that mushroom-type and patterned probe PCM devices can indeed be scaled down to ultrasmall (single-nanometer) dimensions, and in doing so, ultralow programming currents (sub-20 µA) and ultrahigh storage densities (~10 Tb/in²) can be achieved via such a scaling process. Our sophisticated modelling approach also provided a detailed insight into some key PCM device characteristics, such as amorphization (Reset) and crystallization (Set) kinetics, thermal confinement, and the important resistance window i.e. difference in resistances between the Reset and Set states. In the second part of the thesis, the aforementioned modelling approach was used to assess the feasibility of some advanced functionalities of PCM devices, such as

assess the feasibility of some advanced functionalities of PCM devices, such as neuromorphic computing and phase change metadevices. It was demonstrated that by utilizing the accumulation mode of operation inherent to phase change materials, we can combine a physical PCM device with an external comparator-type circuit to deliver a 'self-resetting spiking phase change neuron', which when combined with phase change synapses can potentially open a new route for the realization of all-phase change neuromorphic computers. It was further shown that it is indeed feasible to design and 'electrically' switch practicable phase change metadevices (for absorber and modulator applications, and suited to operation in the technologically important near-infrared range of the spectrum).

Finally, it was demonstrated that the Gillespie Cellular Automata (GCA) phase change model is capable of exhibiting 'non-Arrhenius kinetics of crystallization', which were found to be in good agreement with reported experimental studies.

#### **List of Publications**

#### **Book Chapters**

(1) H. Hayat, K. Kohary and C. D. Wright, "Scaling of Phase Change Materials and Memory Devices", (Invited Book Chapter). To be published in *Phase Change Memory: Device Physics, Reliability and Applications*. Chapter 9. (2016). Editor: Andrea Redaelli. Springer Publishing Group. Accepted

# **Review Papers**

(2) H. Hayat, K. Kohary and C. D. Wright, "Emerging Nanoscale Phase-Change Memories: A Summary of Device Scaling Studies", *Electronic Materials*, Elsevier Reference Module in Materials Science and Materials Engineering, 04144, (2016).

#### **Research Papers**

- (3) **H. Hayat**, K. Kohary and C. D. Wright, "Can conventional phase-change memory devices be scaled down to single-nanometre dimensions?", *Nanotechnology*, 28, 3, (2016).

- (4) **H. Hayat**, K. Kohary and C. D. Wright, "Ultrahigh Storage Densities via the Scaling of Patterned Probe Phase-Change Memories", *IEEE Transactions on Nanotechnology*, (2017). Accepted

- (5) S. G-C. Carrillo, G. R. Nash, **H. Hayat**, M. J. Cryan, M. Klemm, H. Bhaskaran and C. D. Wright, "Design of practicable phase-change metadevices for near-infrared absorber and modulator applications", *Optics Express*, 24, 12, (2016).

- (6) R. Cobley, **H. Hayat**, and C. D. Wright, "A self-resetting spiking phase-change neuron", *European Phase Change and Ovonics Symposium (EPCOS)*, Cambridge, (2016).

- (7) **H. Hayat**, K. Kohary and C. D. Wright, "Size Scaling in Phase-Change Memory Cells: From Traditional to Emerging Device Structures", *European Phase Change and Ovonics Symposium (EPCOS)*, Cambridge, (2016).

- (8) **H. Hayat**, K. Kohary and C. D. Wright, "Simulation of Ultrahigh Storage Densities in Nanoscale Patterned Probe Phase-Change Memories", *IEEE Nanotechnology Materials and Devices Conference*, Toulouse, pp. 1-2, October, (2016).

- (9) H. Hayat, K. Kohary and C. D. Wright, "A theoretical study of the scaling behaviour of mushroom PCRAM devices using the Gillespie Cellular Automata Approach", European Phase Change and Ovonics Symposium (EPCOS), Amsterdam, (2015).

- (10) R. Cobley, H. Hayat, and C. D. Wright, "Self-resetting Spiking Neurons for Neuromorphic Computing Applications using Nanoscale Phase-Change Memory Devices", <u>Submitted to Nanotechnology</u>

- (11) **H. Hayat**, K. Kohary and C. D. Wright, "Modelling the Non-Arrhenius Kinetics of Crystallization in Phase-Change Materials using the Gillespie Cellular Automata Approach", *Manuscript in preparation*

# **Attended Conferences and Events**

- (1) *IEEE Nanotechnology Materials and Devices*, Toulouse, France. October 2016 (Oral presentation).

- (2) European Phase Change and Ovonics Symposium (EPCOS), Cambridge, UK. September 2016 (Poster presentation).

- (3) European Phase Change and Ovonics Symposium (EPCOS), Amsterdam, Netherlands. September 2015 (Poster presentation).

- (4) Chalcogenide Advanced Manufacturing Partnership (ChAMP), University of Southampton, UK. March 2015.

- (5) Defence Materials Forum (DMF), University of Exeter, UK. May 2016 (Poster presentation).

- (6) Early Career Researcher Networking (ECRN) Sessions, University of Exeter, UK. 2016 (Poster presentation).

# **Table of Contents**

| Abstract     |                                                          | 2     |

|--------------|----------------------------------------------------------|-------|

| List of Pub  | lications                                                | 3     |

| Table of Co  | ontents                                                  | 5     |

| List of Figu | ıres                                                     | 8     |

| List of Tabl | les                                                      | 17    |

| Acknowled    | gements                                                  | 18    |

| Chapter 1    | Introduction and Motivation                              | 19    |

| 1.1          | Overview of Data Storage and Memory Technologies         | 20    |

|              | 1.1.1 Traditional Memory Technologies                    | 21    |

|              | 1.1.2 Emerging Memory Technologies                       | 26    |

| 1.2          | Phase Change Memory (PCM)                                | 31    |

|              | 1.2.1 Background and Commercialization of PCM            | 31    |

|              | 1.2.2 Phase Change Memory: Operation Principle           | 33    |

|              | 1.2.3 Threshold Switching                                | 34    |

|              | 1.2.4 PCM Device Structures and Scaling Characteristics  | 35    |

| 1.3          | Phase Change Materials: Characteristics and Properties   | 36    |

|              | 1.3.1 Key Features of Phase Change Materials             | 37    |

|              | 1.3.2 Key Properties of Phase Change Materials           | 38    |

|              | 1.3.3 Scaling of Phase Change Materials                  | 38    |

| 1.4          | Advanced Functionalities of Phase Change Materials and   |       |

|              | Memory Devices                                           | 39    |

|              | 1.4.1 Neuromorphic (Brain-inspired Computing)            | 39    |

|              | 1.4.2 In-Memory Processing: Beyond Von-Neumann Computing | ng 40 |

|              | 1.4.3 Phase Change Metamaterials and Metadevices         | 41    |

| 1.5          | Project Aim and Contribution to Knowledge                | 44    |

| 1.6          | Thesis synopsis                                          | 46    |

| Chapter 2    | A Review of Scaling in Phase Change Memory Materials     |       |

|              | and Devices                                              | 49    |

| 2.1          | Scaling of Phase Change Materials                        | 51    |

|              | 2.1.1 Material Scaling in One Dimension                  | 52    |

|              | 2.1.2 Material Scaling in Two Dimensions                 | 55    |

|           | 2.1.3 Material Scaling in Three Dimensions                    | 58  |

|-----------|---------------------------------------------------------------|-----|

| 2.2       | Scaling of Phase Change Memory Devices                        | 61  |

|           | 2.2.1 The 'Mushroom' Cell                                     | 61  |

|           | 2.2.2 The μTrench and Dash-type Cell                          | 69  |

|           | 2.2.3 The Pore Cell                                           | 70  |

|           | 2.2.4 Crossbar Cells                                          | 73  |

|           | 2.2.5 Probe-based Phase Change Memory Cells                   | 74  |

|           | 2.2.6 Carbon Nanotube-based Cells                             | 79  |

| 2.3       | The Role of Thermal Engineering in Scaling                    | 80  |

| 2.4       | Chapter Summary                                               | 82  |

| Chapter 3 | Simulation of Phase Change Devices using a Multiphysics       |     |

|           | Cellular Automata Approach                                    | 84  |

| 3.1       | Electrical Model                                              | 85  |

| 3.2       | Thermal Model                                                 | 87  |

| 3.3       | A Review of Phase Change Models                               | 88  |

|           | 3.3.1 Classical Nucleation-Growth Theory                      | 88  |

|           | 3.3.2 Johnson-Mehl-Avrami-Kolmogorov (JMAK) Model             | 90  |

|           | 3.3.3 Rate Equation-based Methods                             | 91  |

|           | 3.3.4 Atomistic Modelling                                     | 93  |

|           | 3.3.5 Gillespie Cellular Automata (GCA) Model                 | 94  |

|           | 3.3.6 Summary and Comparison of Phase Change Models           | 101 |

| 3.4       | Implementation of the Multiphysics Cellular Automata Approach | for |

|           | PCM Device Simulations                                        | 102 |

| 3.5       | Chapter Summary                                               | 107 |

| Chapter 4 | The Scaling Characteristics of Conventional Mushroom-type     | €   |

|           | Phase Change Memory Devices                                   | 108 |

| 4.1       | Introduction                                                  | 108 |

| 4.2       | Methodology                                                   | 110 |

| 4.3       | Results                                                       | 113 |

|           | 4.3.1 The Reset process in nanoscaled PCM cells               | 113 |

|           | 4.3.2 The Set process in nanoscaled PCM cells                 | 121 |

| 4.4       | Resistance Window and Reset Current                           | 127 |

| 4.5       | Chapter Summary and Conclusions                               | 132 |

| Chapter 5                                                  | Ultrahigh Storage Densities via the Scaling of Patterned                                                                                                                                                                                                                          |

|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                            | Probe Phase Change Memories 134                                                                                                                                                                                                                                                   |

| 5.1                                                        | Introduction                                                                                                                                                                                                                                                                      |

| 5.2                                                        | Methodology                                                                                                                                                                                                                                                                       |

| 5.3                                                        | Results and Discussion                                                                                                                                                                                                                                                            |

|                                                            | 5.3.1 Comparison of PP-PCM Cell Structures                                                                                                                                                                                                                                        |

|                                                            | 5.3.2 Scaling Characteristics of PP-PCM Cells                                                                                                                                                                                                                                     |

|                                                            | 5.3.3 Storage Densities in PP-PCM Cells                                                                                                                                                                                                                                           |

| 5.4                                                        | Chapter Summary and Conclusions                                                                                                                                                                                                                                                   |

| Chapter 6                                                  | Self-Resetting Spiking Phase Change Neurons for                                                                                                                                                                                                                                   |

|                                                            | Neuromorphic Computing Applications 157                                                                                                                                                                                                                                           |

| 6.1                                                        | Introduction                                                                                                                                                                                                                                                                      |

| 6.2                                                        | Methodology                                                                                                                                                                                                                                                                       |

| 6.3                                                        | Results and Discussion                                                                                                                                                                                                                                                            |

| 6.4                                                        | Chapter Summary and Conclusions                                                                                                                                                                                                                                                   |

| Chapter 7                                                  | Electrical Switching in Phase Change Metadevices for                                                                                                                                                                                                                              |

|                                                            |                                                                                                                                                                                                                                                                                   |

|                                                            | Near-infrared Absorber and Modulator Applications 174                                                                                                                                                                                                                             |

| 7.1                                                        | Near-infrared Absorber and Modulator Applications                                                                                                                                                                                                                                 |

| 7.1<br>7.2                                                 | • •                                                                                                                                                                                                                                                                               |

|                                                            | Introduction                                                                                                                                                                                                                                                                      |

| 7.2                                                        | Introduction                                                                                                                                                                                                                                                                      |

| 7.2                                                        | Introduction.175Methodology.176Results and Discussion.178                                                                                                                                                                                                                         |

| 7.2                                                        | Introduction                                                                                                                                                                                                                                                                      |

| 7.2<br>7.3                                                 | Introduction                                                                                                                                                                                                                                                                      |

| 7.2<br>7.3<br>7.4                                          | Introduction                                                                                                                                                                                                                                                                      |

| 7.2<br>7.3<br>7.4                                          | Introduction                                                                                                                                                                                                                                                                      |

| 7.2<br>7.3<br>7.4<br><b>Chapter 8</b>                      | Introduction                                                                                                                                                                                                                                                                      |

| 7.2<br>7.3<br>7.4<br><b>Chapter 8</b><br>8.1               | Introduction                                                                                                                                                                                                                                                                      |

| 7.2<br>7.3<br>7.4<br><b>Chapter 8</b><br>8.1<br>8.2        | Introduction175Methodology176Results and Discussion1787.3.1 Choice of Material Layers for Modulator structure1787.3.2 Electrical Switching180Chapter Summary and Conclusions184Non-Arrhenius Kinetics of Crystallization in Phase ChangeMaterials185Introduction185Methodology188 |

| 7.2<br>7.3<br>7.4<br><b>Chapter 8</b><br>8.1<br>8.2<br>8.3 | Introduction                                                                                                                                                                                                                                                                      |

# List of Figures

| 1.1  | The growth rate of global digital data per year                          | 19 |

|------|--------------------------------------------------------------------------|----|

| 1.2  | Memory taxonomy showing various memory technologies                      | 20 |

| 1.3  | (a) Physical distribution and hierarchy of memory in a computer.         |    |

|      | (b) Schematic of a circuit of a SRAM cell consisting of six transistors. |    |

|      | (c-d) Schematics of DRAM and Flash memories.                             |    |

|      | (e) Schematic of a typical hard disk                                     | 23 |

| 1.4  | FeRAM schematic cross-section and basic working principle                | 27 |

| 1.5  | (a) Basic functioning of MRAM. (b) Conventional MRAM                     |    |

|      | device structure vs STT-RAM device structure                             | 28 |

| 1.6  | (a) Schematic of a RRAM cell. (b) RRAM switching mechanism               | 29 |

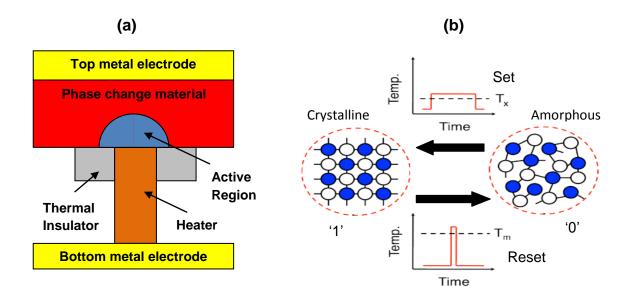

| 1.7  | (a) Schematic of a typical PCM 'mushroom' cell.                          |    |

|      | (b) Reversible switching in PCM between an 'orderly' crystalline         |    |

|      | phase, and 'disorderly' amorphous phase using Set and Reset              |    |

|      | pulses respectively                                                      | 33 |

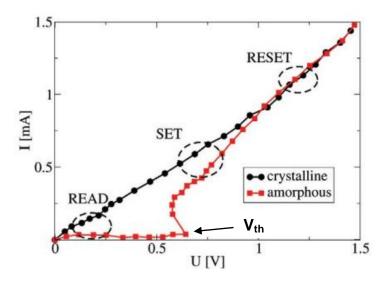

| 1.8  | Typical current-voltage (I-V) curve for a PCM cell                       |    |

|      | showing the threshold voltage (V <sub>th</sub> )                         | 34 |

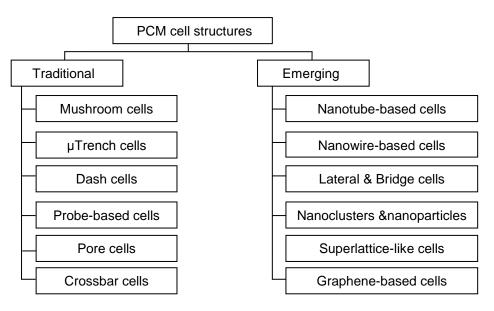

| 1.9  | Taxonomy of various 'Traditional' and 'Emerging' PCM                     |    |

|      | cell structures                                                          | 36 |

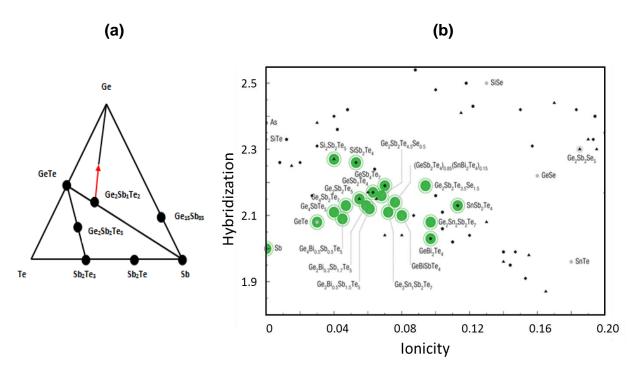

| 1.10 | (a) The ternary Ge-Sb-Te phase diagram with some popular                 |    |

|      | phase change alloys highlighted. (b) A map of Te-based phase             |    |

|      | change materials as a function of material ionicity & hybridization      | 37 |

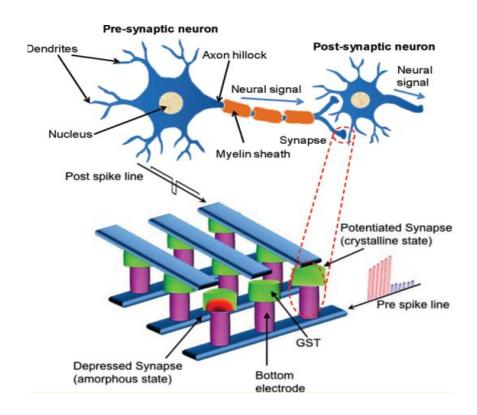

| 1.11 | Bioinspired electronic synapses                                          | 40 |

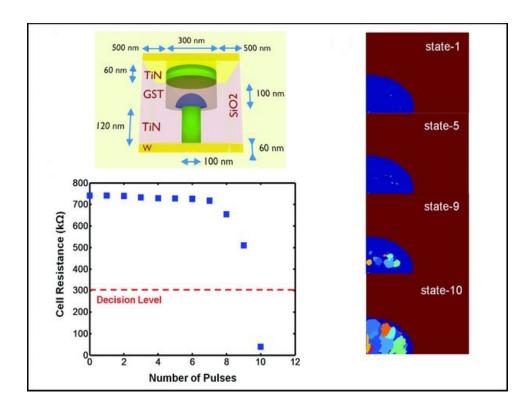

| 1.12 | Schematic of the PCM mushroom cell used by Wright et al for              |    |

|      | simulations of the phase-change base-10 accumulator response             | 42 |

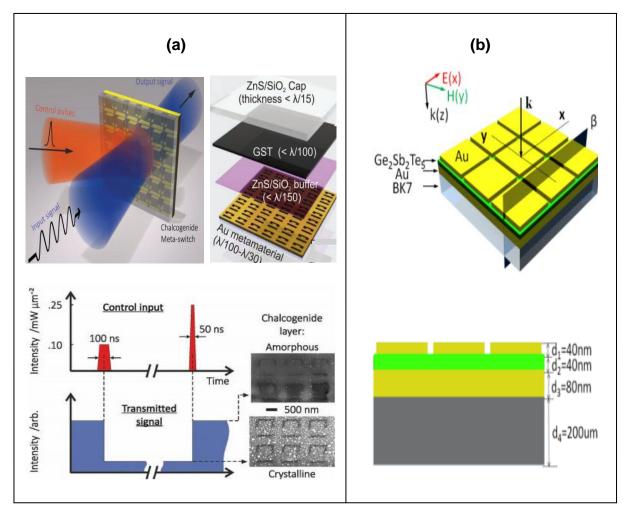

| 1.13 | (a) All-optical non-volatile, chalcogenide metamaterial switch           |    |

|      | reported by Gholipour et al. (b) Schematic of the phase                  |    |

|      | change metamaterial absorber structure presented by Cao et al            | 43 |

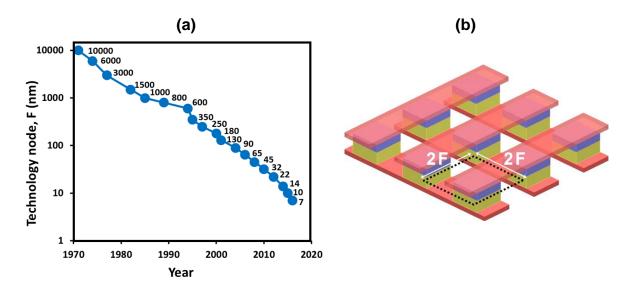

| 2.1  | (a) Historic trend in the semiconductor device technology                |    |

|      | node F (numbers on the plot refer to F value in nanometres).             |    |

|      | (b) Schematic of a generic device layout showing device pitch of         |    |

|      | F, and so smallest device area at node F equal to $4F^2$                 | 50 |

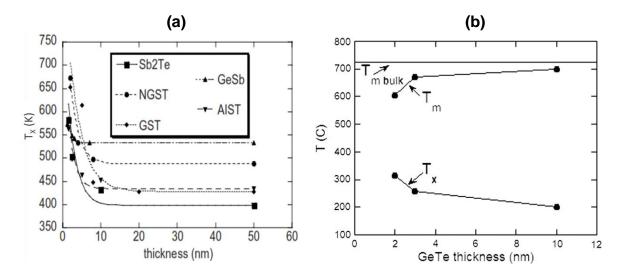

| 2.2  | (a) Variation of crystallization temperature as a function of film                                               |

|------|------------------------------------------------------------------------------------------------------------------|

|      | thickness for various phase change materials.                                                                    |

|      | (b) Variation of crystallization and melting temperatures                                                        |

|      | $(T_x$ and $T_m)$ versus film thickness for GeTe films                                                           |

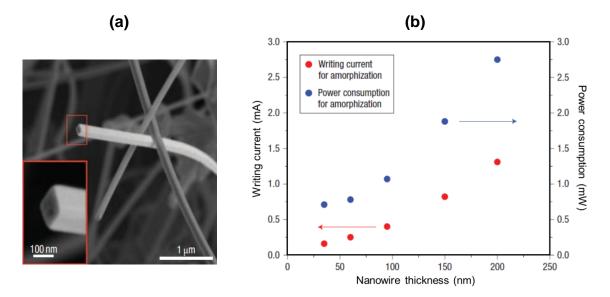

| 2.3  | (a) SEM image of as-grown Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> nanowires. (b) The                     |

|      | variation in amorphization current and power as a function                                                       |

|      | of Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> nanowire diameter                                             |

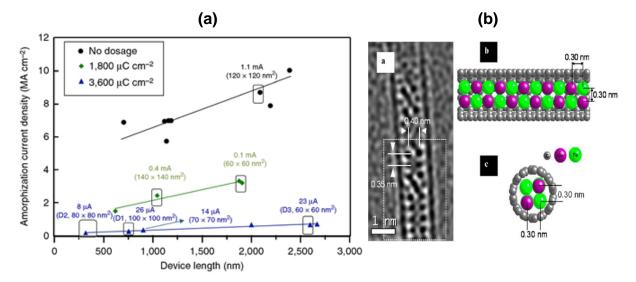

| 2.4  | (a) Amorphization current densities in GeTe nanowires. (b) GeTe                                                  |

|      | nanowires grown inside a 1.3 nm CNT template                                                                     |

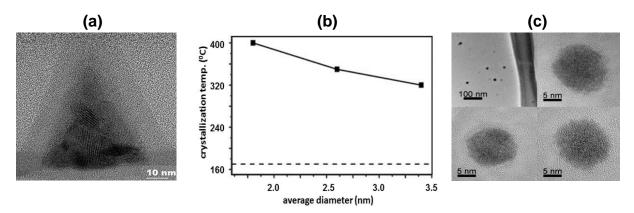

| 2.5  | (a) TEM image of an annealed (crystallized) GeSb nanoparticle.                                                   |

|      | (b) Variation of crystallization temperature as a function of                                                    |

|      | nanoparticle diameter for ultra-small GeTe nanoparticles. (c) TEM                                                |

|      | images of as-deposited amorphous and spherical nanoclusters 58                                                   |

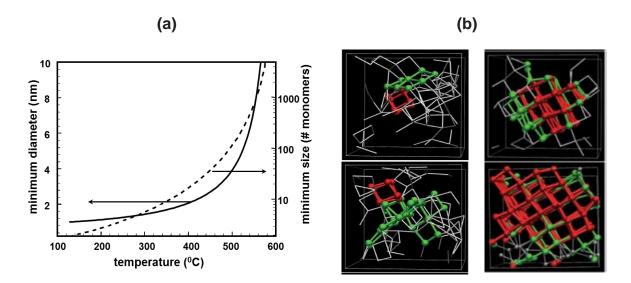

| 2.6  | (a) Predicted (via classical nucleation-growth theory the minimum                                                |

|      | stable crystallite cluster size for Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> as a function of temperature |

|      | (b) Atomic configurations during the crystallization process in                                                  |

|      | amorphous Ge <sub>2</sub> Sb <sub>2</sub> Te <sub>5</sub> and the evolution of structural units on               |

|      | annealing at 600 K 60                                                                                            |

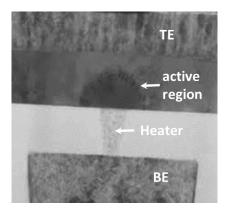

| 2.7  | TEM Cross-section of a mushroom type PCM cell showing the                                                        |

|      | rounded amorphous dome formed above the heater                                                                   |

| 2.8  | Schematic of a PCM cell showing key geometrical and physical                                                     |

|      | parameters used in the analytical study of Russo et al                                                           |

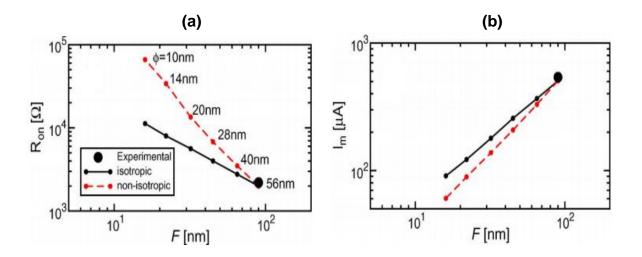

| 2.9  | (a) Variation of PCM mushroom-type cell ON resistance as a function                                              |

|      | of the technology node size (F). (b) Variation in the melting (Reset)                                            |

|      | current as a function of the technology node (F)                                                                 |

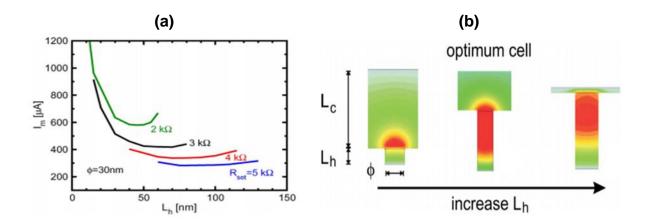

| 2.10 | (a) The variation of melting current, $I_{m}$ , as a function of heater length, $L_{h}$ .                        |

|      | (b) Simulated temperature distributions in mushroom-type PCM cells                                               |

|      | (each subject to their own individual melting current) with different                                            |

|      | L <sub>c</sub> and L <sub>h</sub> sizes67                                                                        |

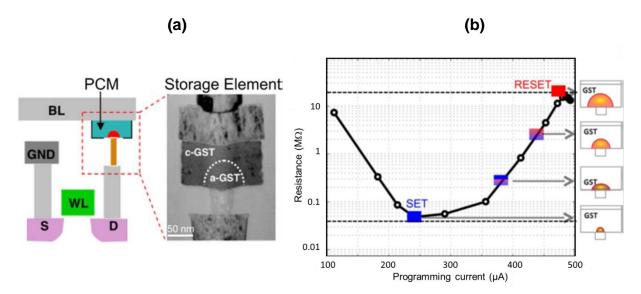

| 2.11 | (a) A 90 nm node mushroom-type PCM as developed by IBM to deliver                                                |

|      | multi-level storage capability of up to 3-bits per cell. (b) Programming                                         |

|      | current versus resistance curve for multi-level operation showing use of                                         |

|      | partial Reset to provide multiple resistance levels                                                              |

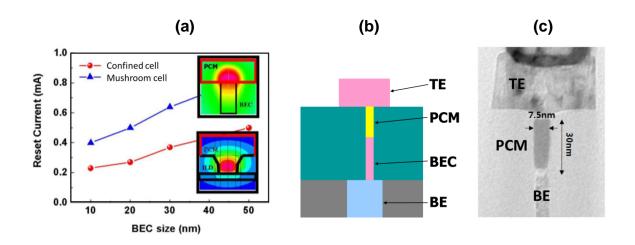

| 2.12 | (a) Simulated Reset current amplitude as a function of the size of            |      |

|------|-------------------------------------------------------------------------------|------|

|      | the bottom electrical contact (BEC) for a mushroom-type cell                  |      |

|      | (planar structure) and a confined cell, showing expected reduction            |      |

|      | in Reset current for the latter. (b) Schematic of the dash-type version       |      |

|      | of the confined cell as developed by Samsung. (c) TEM cross-                  |      |

|      | sectional image of a dash-type cell                                           | 70   |

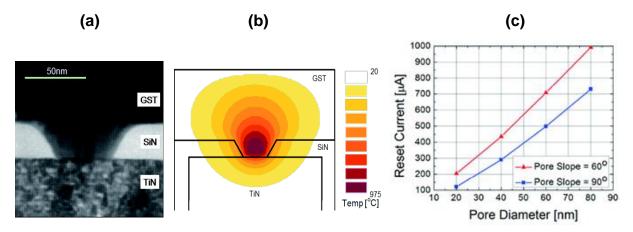

| 2.13 | (a) TEM cross-sectional image of a GST pore-type cell. (b) Simulation         |      |

|      | of temperature distribution in GST layer during RESET process,                |      |

|      | showing successful confinement of the heated volume. (c) Simulated            |      |

|      | effect of pore diameter and slope of SiN sidewall on Reset current            | 71   |

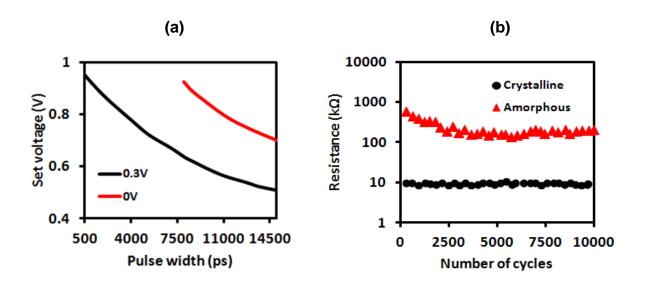

| 2.14 | (a) Set voltage versus pulse width for pore-type cells of 50 nm in            |      |

|      | diameter with and without the aid of a 0.3 V "incubation-field".              |      |

|      | (b) Shows successful repeated switching of the cell in (a) with 500 ps        |      |

|      | pulses for both Set and Reset                                                 | . 72 |

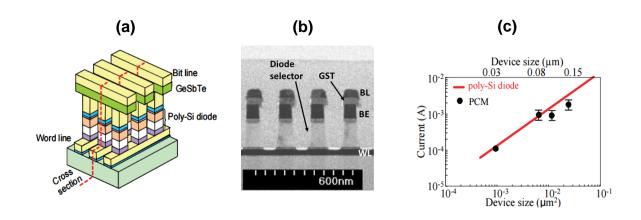

| 2.15 | (a) Schematic of a crossbar type PCM structure with integrated Si-diode       |      |

|      | selector. (b) TEM cross-sectional image of a crossbar device.                 |      |

|      | (c) Reset current scaling characteristics of a PCM crossbar device            |      |

|      | showing a ten-fold reduction in current as the contact size shrinks           |      |

|      | from 150 nm to 30 nm                                                          | . 73 |

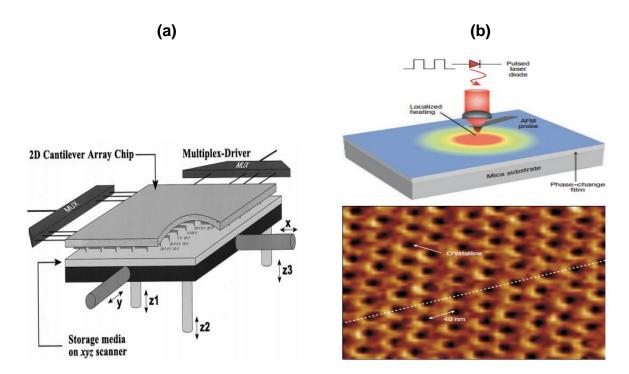

| 2.16 | (a) The IBM 'Millipede' concept consisting of a 2-D array of probes           |      |

|      | used to write, read and erase indentations in polymer media                   |      |

|      | (b) Experimental setup by Hamann et al for phase change thermal               |      |

|      | recording (top), and crystalline bits written in an amorphous GST film        |      |

|      | using a heated AFM tip (bottom), achieving storage densities of up            |      |

|      | to 3.3. Tb/in <sup>2</sup>                                                    | 75   |

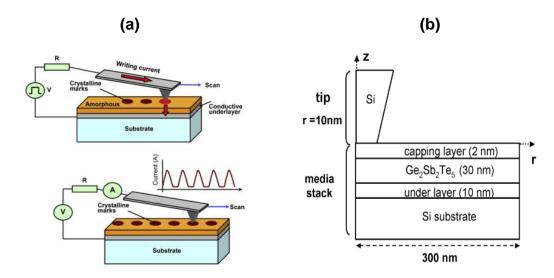

| 2.17 | (a) Schematic of the write (top) and read (bottom) processes in phase         |      |

|      | change probe storage. (b) Phase change probe memory cell structure            |      |

|      | used by Wright et al. to demonstrate 1.5 Tb/in <sup>2</sup> storage densities | 75   |

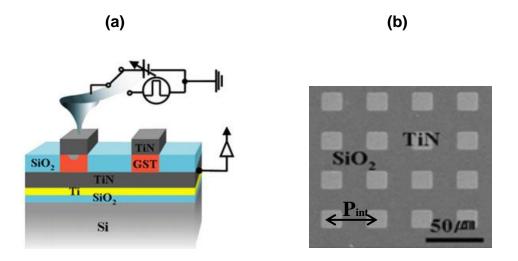

| 2.18 | (a) Schematic diagram of patterned probe PCM (PP-PCM) cells                   |      |

|      | proposed by Kim et al. to demonstrate electrical switching on the             |      |

|      | micrometer scale. (b) SEM image of the 2D-arrayed PP-PCM cells                | 77   |

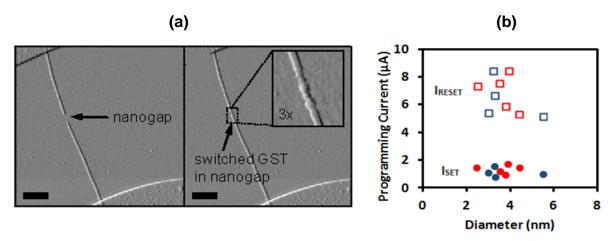

| 2.19 | (a) AFM images of a CNT-based nanogap PCM cell before and after                |    |

|------|--------------------------------------------------------------------------------|----|

|      | filling with GST (the scale bars are 500 nm). (b) Ultra-low programming        |    |

|      | currents achieved for several CNT-based nanogap PCM devices                    |    |

|      | having ultra-small contact diameters                                           | 79 |

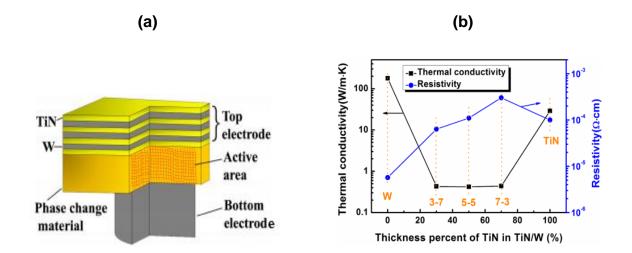

| 2.20 | (a) Stacked TiN/W electrode structure used by Lu et al to enhance              |    |

|      | thermal confinement in 190nm sized PCM cells. (b) Thermal                      |    |

|      | conductivities and resistivities of 3-7, 5-5, 7-3 (nm) TiN-W electrode         |    |

|      | layers. Much lower thermal conductivities were observed for stacked            |    |

|      | electrodes in comparison to single layer TiN and W electrodes                  | 82 |

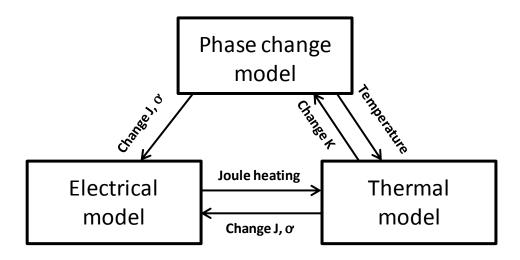

| 3.1  | Block diagram of a physical model for the simulations of electrical            |    |

|      | PCM devices. J, K, and $\sigma$ are the current density, thermal conductivity, |    |

|      | and electrical conductivity in the phase change material, respectively         | 85 |

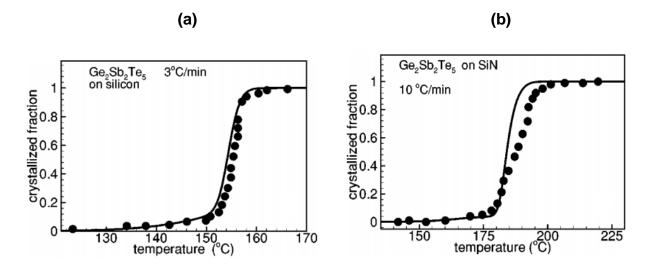

| 3.2  | Experimental (symbols) and calculated (lines) results of crystallized          |    |

|      | fraction of GST as a function of temperature during ramped anneals             |    |

|      | for (a) GST on silicon for 3°C / min ramp rate, and (b) GST on SiN for         |    |

|      | 3 <sup>o</sup> C / min ramp rate                                               | 93 |

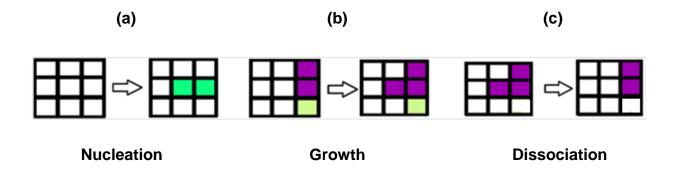

| 3.3  | Possible events in the GCA approach: (a) Nucleation, (b) Growth,               |    |

|      | and (c) Dissociation                                                           | 95 |

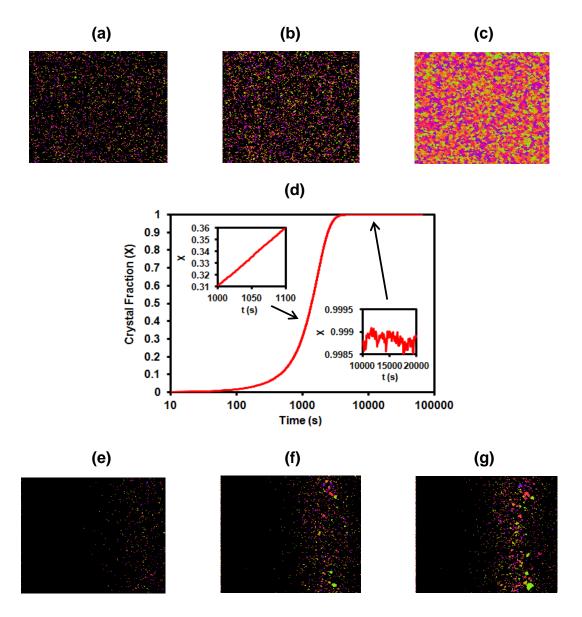

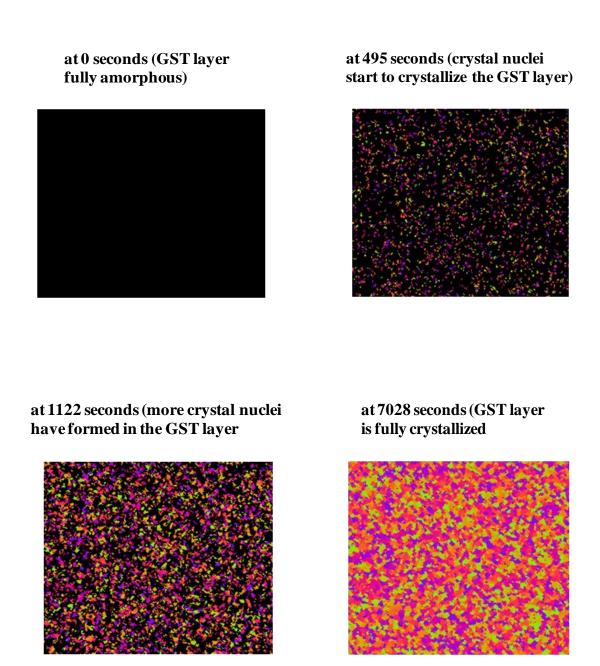

| 3.4  | (a-c) Images showing the GST crystallization evolution (starting with          |    |

|      | a pure amorphous material (black)) for temperature T=131°C using the           |    |

|      | GCA code. Figures were obtained at (a) 5000 steps (X=0.112, t=495s),           |    |

|      | (b) 20000 steps (X=0.371, t=1122s), and (c) 10 <sup>5</sup> steps              |    |

|      | (X=0.995, t=7028s) of the algorithm. (d) Crystal fraction, X versus            |    |

|      | time, t during low temperature annealings at 131°C. Details of the             |    |

|      | progress of the annealing is shown during the growth phase and when            |    |

|      | the crystal fraction saturates near X=1. (e-g) Images showing the              |    |

|      | GST crystallization evolution for different left and right boundary            |    |

|      | temperatures of 227°C and 477°C respectively. Figures were obtained            |    |

|      | after (e) 18ns, (f) 300ns, and (g) 554ns, respectively                         | 00 |

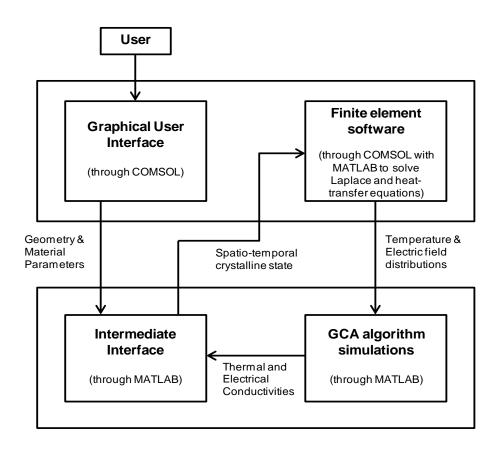

| 3.5  | Block diagram showing the implementation of the fully coupled                  |    |

|      | Multiphysics Cellular Automata approach for PCM device simulations 1           | 04 |

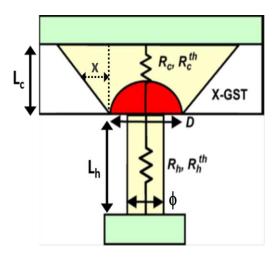

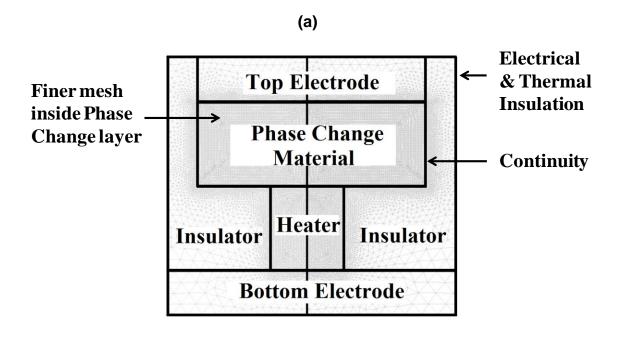

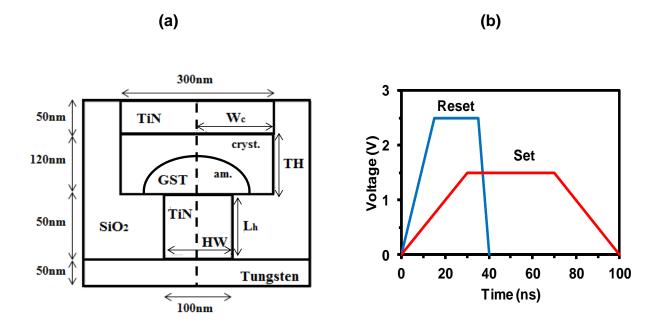

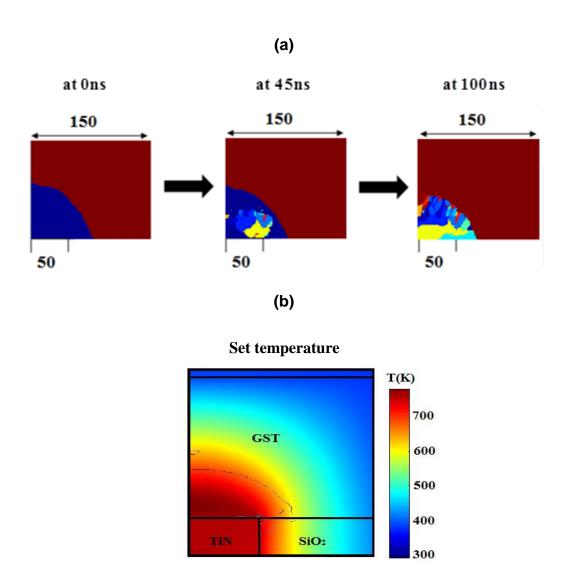

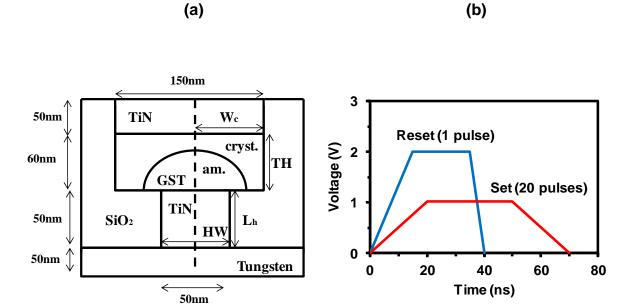

| 3.6 | (a) Schematic of the mushroom-type PCM cell used for device                        |

|-----|------------------------------------------------------------------------------------|

|     | simulations.(b)Typical test system for PCM device switching                        |

|     | consisting of an electrical pulse generator and a series load                      |

|     | resistor R <sub>L</sub> in series with the PCM device                              |

| 4.1 | (a) Schematic of the PCM simulation cell showing the key scaled                    |

|     | features of heater width, HW, GST layer thickness, TH, and GST layer               |

|     | (half) width, $W_{\text{c}}$ . (b) A commonly used trapezoidal Reset and Set       |

|     | voltage pulse for the simulations in this study. The pulse amplitudes              |

|     | and durations were varied from (1.3V - 3V) and (20 - 100ns)                        |

|     | respectively to switch the mushroom-type PCM cell                                  |

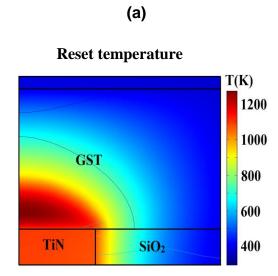

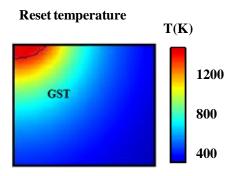

| 4.2 | (a) Temperature distribution (at 35ns i.e. the time of occurrence of               |

|     | maximum temperature) during the Reset process (2.5 V, 40 ns pulse)                 |

|     | in a large PCM cell having heater width of 100 nm (it is clear that the            |

|     | melting temperature of GST is exceeded in a dome-like region above                 |

|     | the heater contact). (b) Evolution of the amorphous dome (blue)                    |

|     | formation on a fully crystalline GST layer (red) during the Reset                  |

|     | process (plots show one half of the GST layer and numbers at the                   |

|     | top and bottom of plots show the GST width $W_{\rm c}$ = 150nm and the             |

|     | heater half-width, HW/2 = 50nm respectively)                                       |

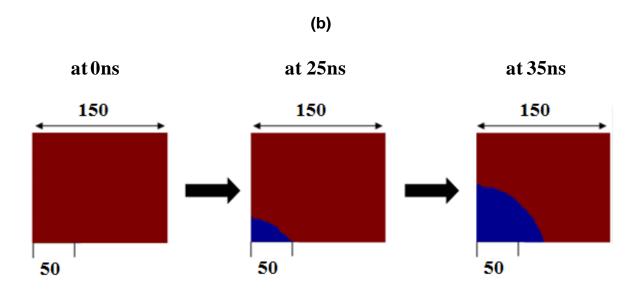

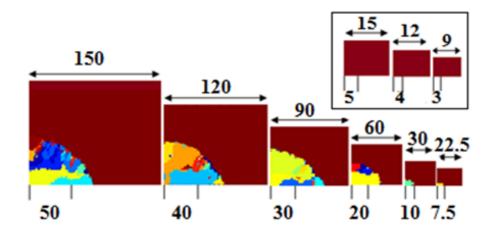

| 4.3 | Successful formation of amorphous regions (shown in blue) at the                   |

|     | end of the Reset process as cells are scaled down in size and for                  |

|     | heater widths down to 15 nm (plots show one half of the GST layer                  |

|     | and numbers at the top and bottom of plots show the GST width $\ensuremath{W_{c}}$ |

|     | and the heater half-width, HW/2 respectively, both in nanometers) 115              |

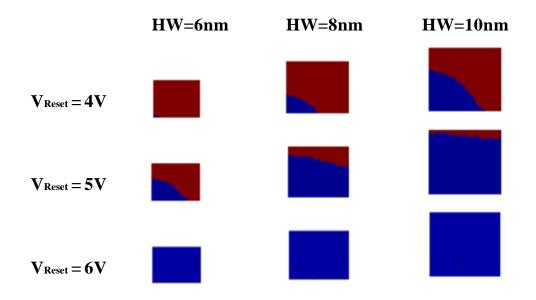

| 4.4 | Amorphous domes for HW = 10, 8 and 6nm using larger Reset                          |

|     | voltage amplitudes i.e. $V_{RESET} = 4 - 6 \text{ V}$ . A 6 V Reset pulse          |

|     | amplitude is large enough to completely amorphize the GST material                 |

|     | for all three heater widths117                                                     |

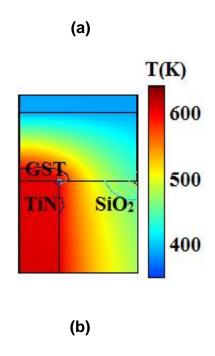

| 4.5 | (a) Temperature distribution (at the time of occurrence of                         |

|     | maximum temperature) during the Reset process (2.5 V, 40 ns pulse)                 |

|     | in small PCM cell having heater width of 10 nm. (b) Maximum                        |

|     | temperature reached in the GST layer during a 2.5 V, 40 ns Reset                   |

|     | process for a single layer TiN top electrode and a multi-layered                   |

|     | TiN/W top electrode119                                                             |

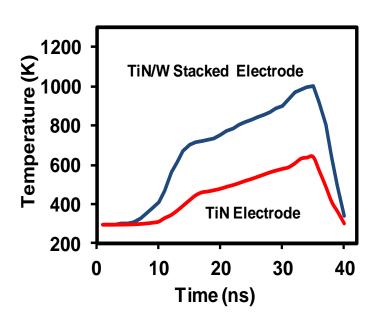

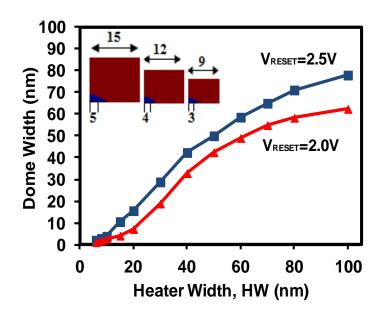

| 4.5  | (c) The width of the amorphized dome as a function of cell size (heater         |     |

|------|---------------------------------------------------------------------------------|-----|

|      | width) for 40 ns Reset pulses of 2.5 V and 2.0 V. Successful Reset              |     |

|      | is achieved in all cases (dome width > heater width), but for the               |     |

|      | smallest cells (heater widths ≤ 10 nm) a stacked TiN/W top electrode            |     |

|      | had to be used. Inset shows amorphous regions (blue) at the end of              |     |

|      | the Reset process for the smallest cells (numbers at the top and                |     |

|      | bottom of plots show the GST width, $W_{\text{c}}$ , and the heater half-width, |     |

|      | HW/2 respectively, both in nanometers)                                          | 120 |

| 4.6  | (a) Evolution of the re-crystallization (Set) of the amorphous dome             |     |

|      | (blue) shown in Figure 4.2 (b), using a 1.5V, 100ns Set pulse.                  |     |

|      | (b) Corresponding Set temperature distribution (at 70ns i.e. the time           |     |

|      | of occurrence of maximum temperature) during the Set process                    | 122 |

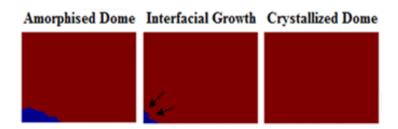

| 4.7  | (a) Re-crystallization of the amorphous domes shown in Figure 4.3 and           |     |

|      | 4.5 (c) using a Set pulse of 1.5 V and 100 ns duration. (b)                     |     |

|      | Evidence of interfacial growth initiated from the amorphous-crystalline         |     |

|      | interface for HW ≤ 10 nm (inset of Fig. 4.7 (a))                                | 124 |

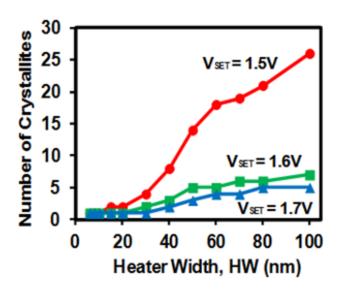

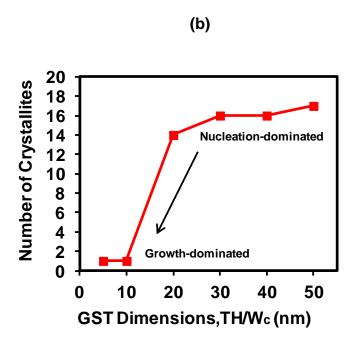

| 4.8  | (a) The number of crystallites formed during the Set process as a               |     |

|      | function of cell size (shown as heater width) and for different Set             |     |

|      | pulse amplitudes                                                                | 125 |

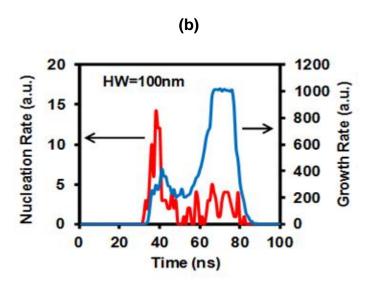

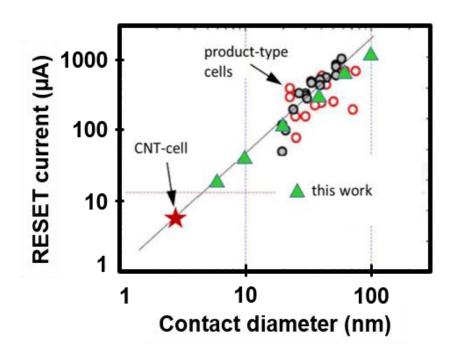

| 4.8  | (b) and (c) The nucleation and growth rates during the                          |     |

|      | Set process (1.5 V, 100 ns pulse) for a 100 nm (heater width)                   |     |

|      | cell (b) and a 10 nm cell (c)                                                   | 126 |

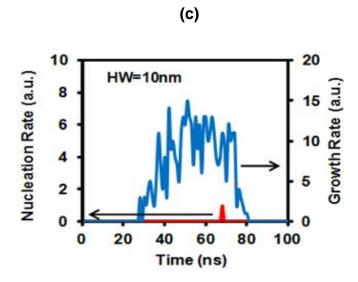

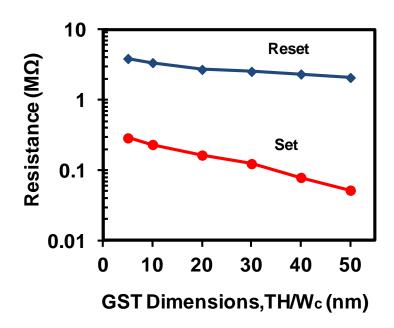

| 4.9  | Cell resistance in Set and Reset states as a function of heater                 |     |

|      | contact size                                                                    | 128 |

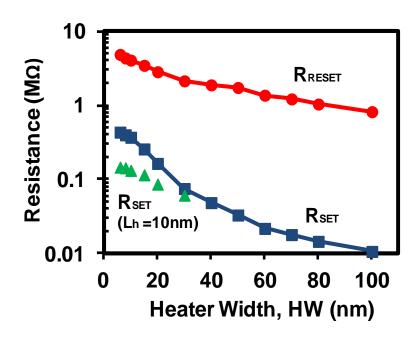

| 4.10 | Reset current amplitude as a function of contact size for the                   |     |

|      | mushroom-type cells of this work (triangles), for various product-type          |     |

|      | cells reported in the literature (circles) and for the CNT-contact cell         |     |

|      | (star) reported by Xiong et al                                                  | 130 |

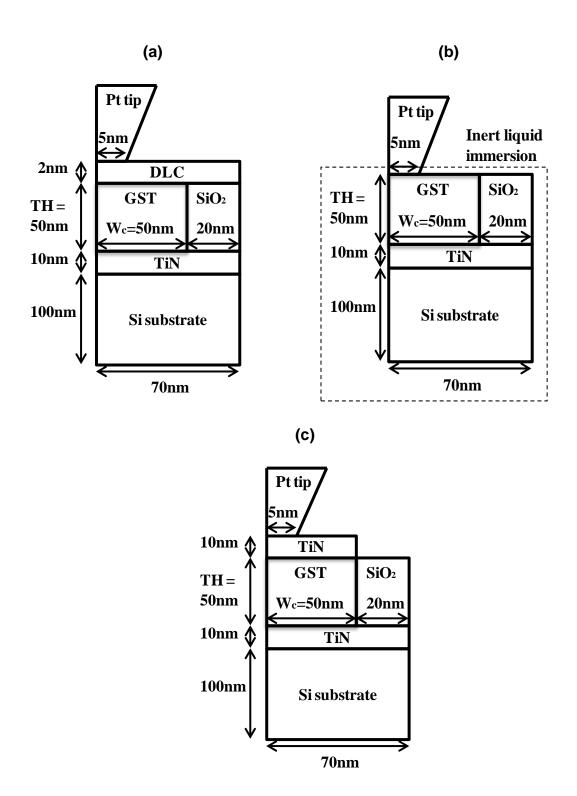

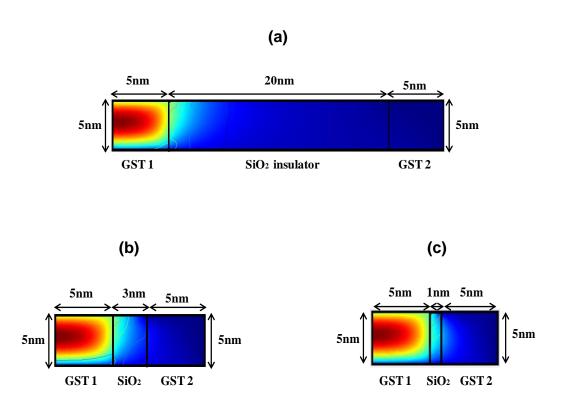

| 5.1  | Potential PP-PCM cell structures: (a) trilayer DLC/GST/TiN cell structure.      |     |

|      | (b) probe direct contact with GST layer by immersing sample in an inert         |     |

|      | liquid to prevent oxidation. (3) trilayer TiN/GST/TiN cell structure            | 136 |

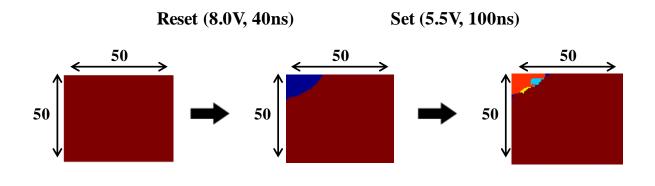

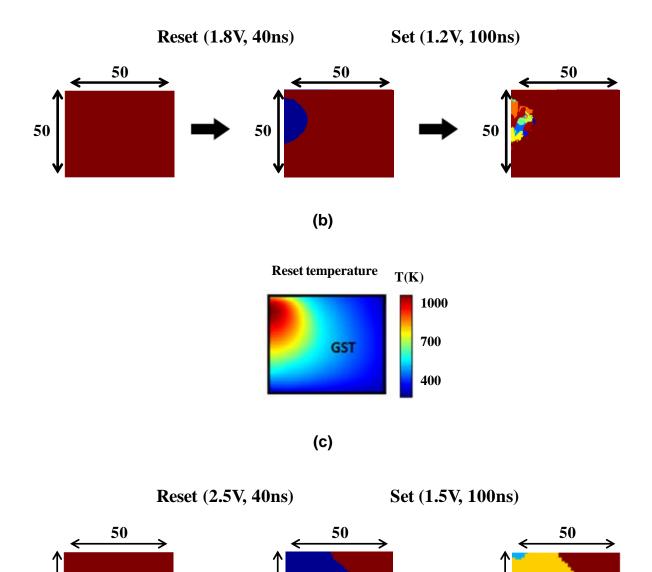

| 5.2  | (a) Reset and Set processes for Cell Structure 1: DLC/GST/TiN.                  |     |

|      | Successful Reset and Set achieved using 8.0V / 40ns and 5.5V / 100ns            |     |

|      | pulses respectively. (b) Reset temperature distribution inside GST layer        |     |

|      | using an 8.0V / 40ns Reset pulse                                       | 141   |

|------|------------------------------------------------------------------------|-------|

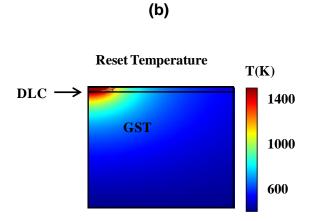

| 5.3  | (a) Reset and Set processes for Cell Structure 2: GST/TiN.             |       |

|      | Successful Reset and Set achieved using 1.8V / 40ns and 1.2V /         |       |

|      | 100ns pulses respectively, which are much lower in amplitude           |       |

|      | compared to the pulses used to switch Cell Structure 1.                |       |

|      | (b) Reset temperature distribution inside GST layer using a 1.8V /     |       |

|      | 40ns Reset pulse                                                       | 143   |

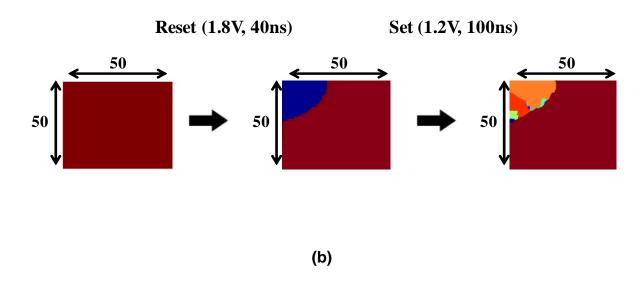

| 5.4  | (a) Reset and Set processes for Cell Structure 3: TiN/GST/TiN with     |       |

|      | successful Reset and Set achieved using 1.8V / 40ns and 1.2V /         |       |

|      | 100ns pulses respectively. A rounded amorphous bit is formed a few     |       |

|      | nm below the top of the GST layer in this case. (b) Reset temperature  |       |

|      | distribution inside GST layer using a 1.8V, 40ns Reset pulse (c) Reset |       |

|      | and Set processes in Cell Structure 3 using larger amplitude Reset     |       |

|      | and Set pulses of 2.5V, 40ns and 1.5V, 100ns respectively              | 145   |

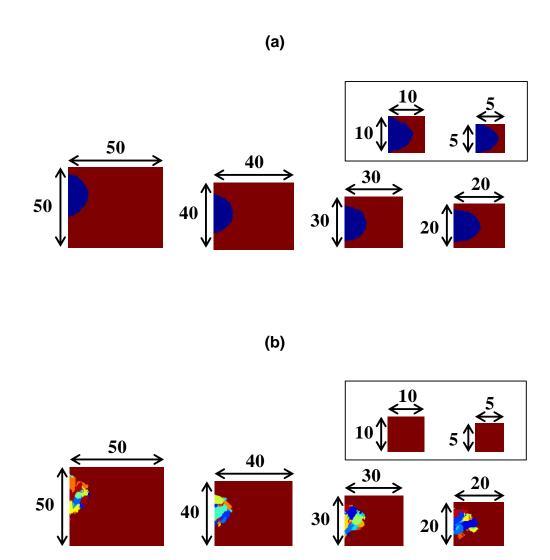

| 5.5  | (a) Successful formation of amorphous bits (shown in blue) at the end  |       |

|      | of the Reset process as GST dimensions are scaled down in size         |       |

|      | (b) Re-crystallization of the amorphous bits shown in Figure 5.5 (a)   | 148   |

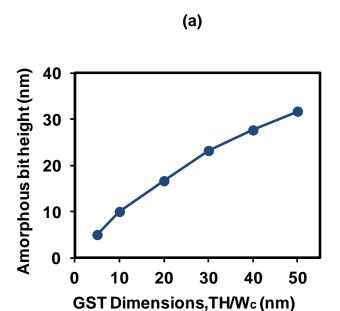

| 5.6  | The variation in the height of the amorphous bit as a function of      |       |

|      | GST dimensions                                                         | 149   |

| 5.7  | The number of crystallites formed during the Set process as a          |       |

|      | function of GST size                                                   | 149   |

| 5.8  | Cell resistance in the Reset and Set states as a function of the       |       |

|      | GST dimensions                                                         | 150   |

| 5.9  | Electro-thermal simulations used to determine the ultimate insulator   |       |

|      | width between GST cells before thermal interference (between cells)    |       |

|      | starts taking place                                                    | 152   |

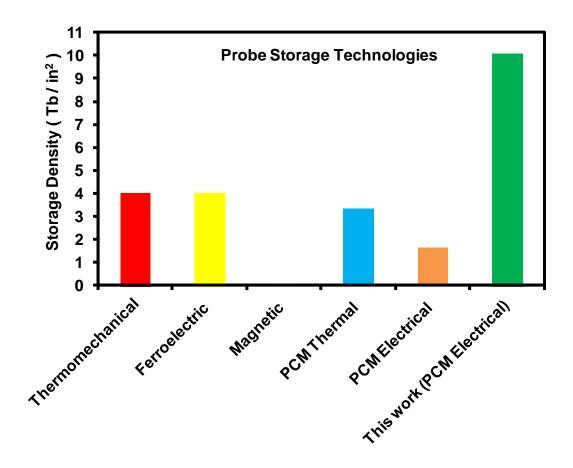

| 5.10 | Comparison of storage density in this work (green bar) compared        |       |

|      | to other reported probe-based technologies                             | . 154 |

| 6.1  | (a) Schematic of the PCM simulation cell used for the physical         |       |

|      | device simulations with dimensions: HW=50nm, TH=60nm and               |       |

|      | $W_c$ =75nm. (b) Trapezoidal Reset and Set pulses used to amorphize    |       |

|      | and crystallize the PCM cell. One Reset pulse (2.0V, 40ns), and 20     |       |

|      | Set pulses (1.025V, 70ns each) are applied for this study. (c) Block   |       |

|      | diagram for the self-resetting neuron SPICE circuit implementation     | 160   |

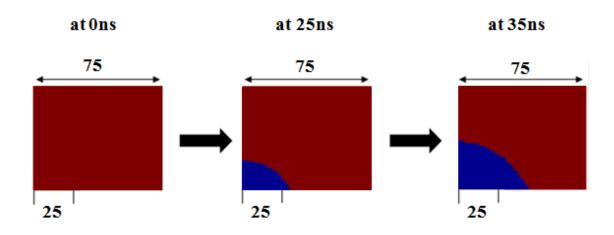

| 6.2 | Evolution of the amorphous dome (blue) formation on a fully crystalline      |

|-----|------------------------------------------------------------------------------|

|     | GST layer (red) during the Reset process                                     |

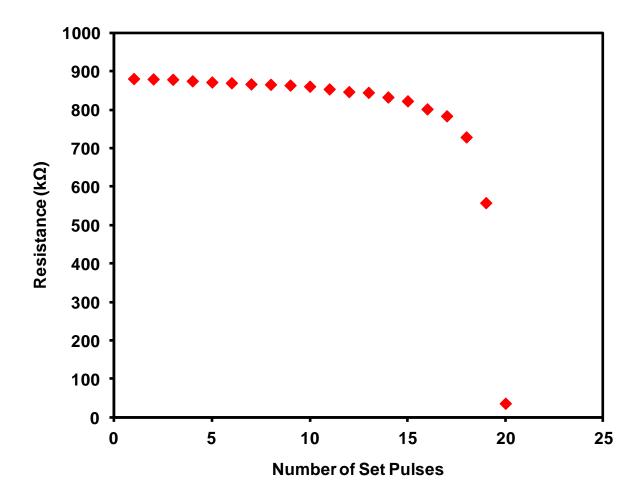

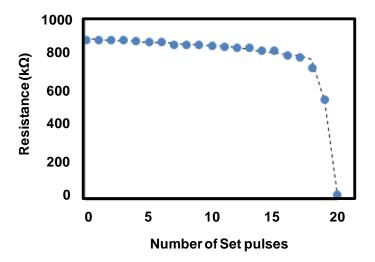

| 6.3 | The resistance of the PCM mushroom cell (shown in Figure 6.1 (a))            |

|     | after the application of each of 20 Set input pulses having an               |

|     | amplitude of 1.025V and being of 70ns duration (with 20ns rise and           |

|     | 20ns fall times)                                                             |

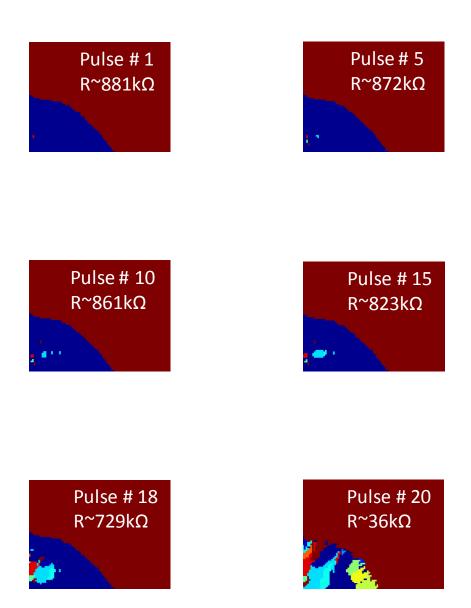

| 6.4 | Phase diagrams showing the crystal structures of the active region           |

|     | of the PCM cell for states 1, 5, 10, 15, 18 and 20                           |

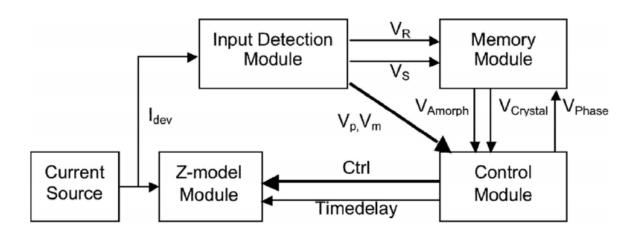

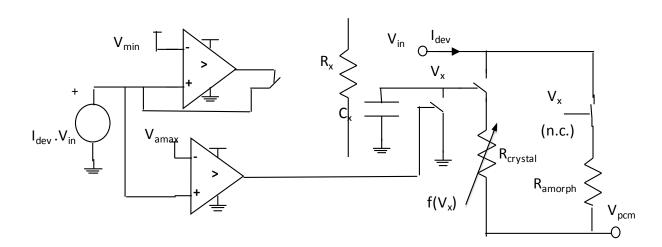

| 6.5 | (a) Block diagram of the SPICE circuit model presented by Cobley and         |

|     | Wright. (b) Circuit diagram of the neuron SPICE / PCM model 168              |

| 6.6 | Calibration (dotted line) of the SPICE circuit model with the PCM            |

|     | device results from Figure 6.3                                               |

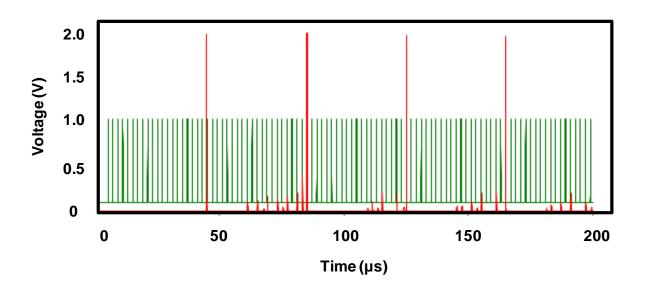

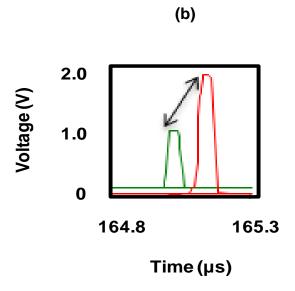

| 6.7 | (a) Simulated response for the self-resetting spiking phase change           |

|     | neuron implementation. Input spikes are shown in green and output            |

|     | spikes are shown in red. (b) Simulated response showing the worst            |

|     | case 'recovery period' (black arrow). During this period subsequent          |

|     | spikes are not detected at the neuron                                        |

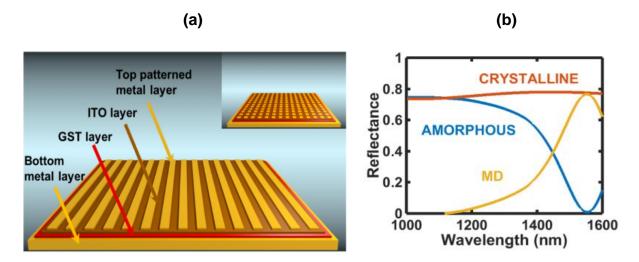

| 7.1 | (a) Schematic of a GST-based thin film phase change                          |

|     | metamaterial absorber/modulator structure (inset shows the top metal         |

|     | layer patterned into squares). (b) Simulated reflectance spectrum for        |

|     | the design in Fig. 7.1 (a) with Au top and bottom metal layers and with      |

|     | the phase change GST layer in both crystalline and amorphous states.         |

|     | The design was optimized for maximum modulation depth of 1550nm 176          |

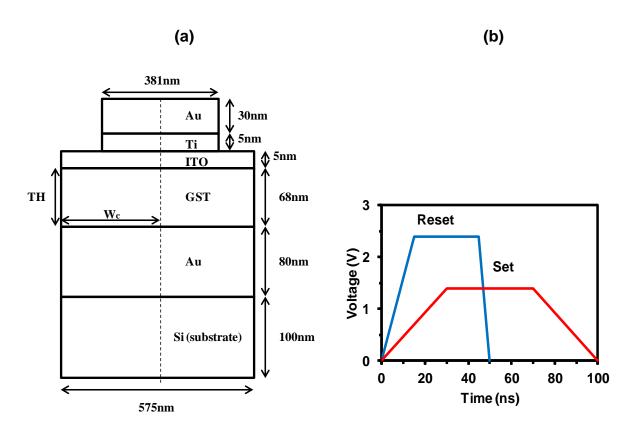

| 7.2 | (a) Schematic of the phase change metamaterial absorber /                    |

|     | modulator structure showing the dimensions of each material. A GST           |

|     | layer with thickness, TH = 68nm, and width, $W_c$ = 287.5nm is used.         |

|     | (b) Trapezoidal Reset and Set pulses of 2.4V, 50ns and 1.4V, 100ns           |

|     | are applied to switch the GST layer between the amorphous and                |

|     | crystalline phases177                                                        |

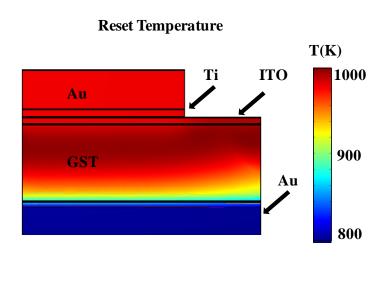

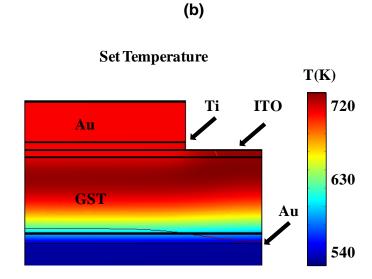

| 7.3 | Simulated temperature distribution in the structure of Figure 7.2 (a) for    |

|     | the case of electrical excitation (assuming an electrically pixelated        |

|     | structure with pixel size equal to the unit-cell size) for (a) a Reset pulse |

|     | of 2.4V, 50ns and (b) a Set pulse of 1.4V, 100ns respectively                |

| 7.4   | The starting and finishing phase states of the GST layer after a                           |       |

|-------|--------------------------------------------------------------------------------------------|-------|

|       | sequence of Reset / Set / Reset electrical pulses                                          | 183   |

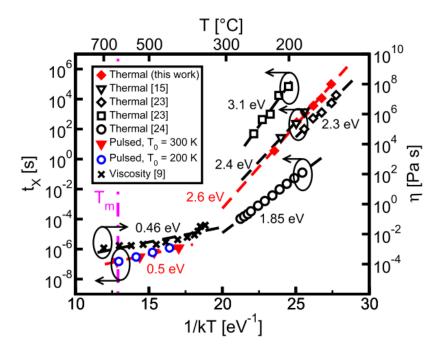

| 8.1   | Arrhenius plot by Ciocchini et al. showing measured crystallization                        |       |

|       | speed, $t_x$ (in seconds), as a function of 1 / $k_B T$ (where T is the                    |       |

|       | crystallization temperature in ${}^{\circ}\text{C}$ and $k_B$ is the Boltzmann constant).  |       |

|       | Values from other studies e.g. Orava et al (denoted by x in figure)                        |       |

|       | have also been shown. Data clearly shows different Ea values at                            |       |

|       | different crystallization temperatures, thus evidencing                                    |       |

|       | non-Arrhenius crystallization in PCM                                                       | . 187 |

| . 8.2 | GCA model simulations: Evolution of the crystallization of the GST                         |       |

|       | layer for a temperature of 131°C (404 K) on both left and right                            |       |

|       | boundaries. At 0 seconds ( $t_x = 0s$ ) the GST layer is amorphous, and                    |       |

|       | at $t = 7028$ seconds ( $t_x = 7028$ s) the GST layer is crystallized                      | 190   |

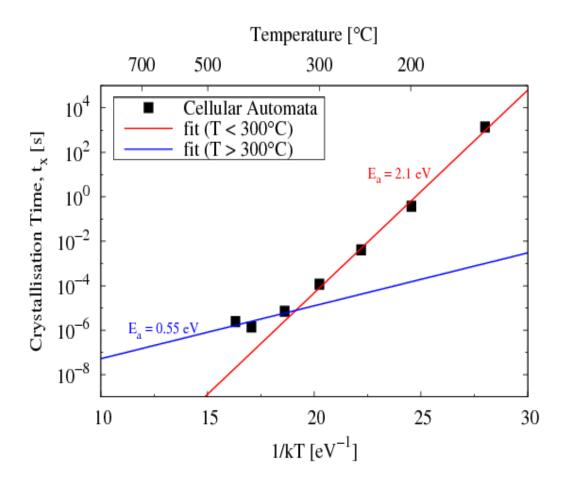

| 8.3   | Arrhenius plot of crystallization times versus the crystallization                         |       |

|       | temperature (in °C) and 1/k <sub>B</sub> T (eV <sup>-1</sup> ), using our GCA phase change |       |

|       | model (black squares)                                                                      | 192   |

# **List of Tables**

| 1.1 | Comparison of various traditional memory technologies                    |

|-----|--------------------------------------------------------------------------|

| 1.2 | Comparison of various emerging memory technologies 30                    |

| 1.3 | Timeline of PCM products demonstrated and commercialized after           |

|     | 2003                                                                     |

| 2.1 | Scaling of PCM device operating parameters as the device is              |

|     | scaled isotropically in size by the factor k (for k > 1)                 |

| 2.2 | Storage density comparison of various probe-based                        |

|     | memory technologies                                                      |

| 3.1 | Thermodynamic and kinetic parameters used in the Gillespie               |

|     | Cellular Automata (GCA) model                                            |

| 3.2 | Comparison of different phase change modelling approaches 101            |

| 3.3 | Continuation of the comparison of different phase change                 |

|     | modelling approaches                                                     |

| 4.1 | Material parameters used for the electro-thermal and phase               |

|     | change simulations112                                                    |

| 4.2 | A comparison of the Reset current (and power) scaling performance of     |

|     | mushroom-type cells (this work) versus other reported traditional and    |

|     | emerging PCM cells reviewed in Chapter 2                                 |

| 5.1 | Material parameters used for the electro-thermal and phase               |

|     | change simulations                                                       |

| 5.2 | Summary of the comparison of three potential PP-PCM cell                 |

|     | structures discussed in section 5.3.1                                    |

| 5.3 | Storage densities as the PP-PCM cell dimensions are scaled               |

|     | down to sub-10nm dimensions                                              |

| 6.1 | Key parameters used for the self-resetting spiking phase change          |

|     | neuron simulations using the SPICE / PCM model (shown in Figures         |

|     | 6.1 (c) and 6.5 (b))                                                     |

| 7.1 | Material parameters for the electro-thermal/phase change simulations 178 |

.

# Acknowledgements

First and foremost, I am heartily thankful to my beloved parents Dr. Nabeel and Dr. Tanzila, and siblings Usama, Sabah and Sarah. Words cannot express how grateful I am for the endless love, support, and sacrifices they have made throughout my education and professional career, and I will be forever grateful for their presence in my life through thick and thin.

I would like to express my deepest gratitude to my PhD Supervisors, Prof. C. David Wright (University of Exeter, UK) and Dr. Krisztian Kohary (Obuda University, Hungary) for giving me the opportunity to work on this very exciting PhD project, and for their guidance, support, enthusiasm and patience. I am sincerely grateful to them for making my PhD journey a great learning and fulfilling experience.

The present and past members of Prof. Wright's group have contributed immensely to my personal and professional time at Exeter. The group has been a source of friendships, as well as help, advice and collaboration, and I look forward to working with them in the future. I would like to thank Dr. Karthik Nagareddy, Dr. Arseny Alexeev and Toby Bachmann for helpful discussions regarding COMSOL modelling, experimental work and publications. I would also like to thank Prof. Gino Hrkac for his advice and support as a mentor throughout the last 3 years. With regards to the research on neuromorphic computing and phase change metadevices in this thesis, I would also like to acknowledge fellow group members Dr. Rosie Cobley for the SPICE simulations in Chapter 6, and Santiago Garcia-Cuevas Carrillo for the modulator reflectance simulations in Chapter 7.

Last but not least, a special thanks to all my dear friends here in Exeter, in other parts of the UK and abroad, for the moral support, motivation, and the great memories we have shared. I am blessed to have friends like them in my life and the completion of this thesis would not have been possible without them.

Yours Sincerely,

Hasan

# **Chapter 1**

# **Introduction and Motivation**

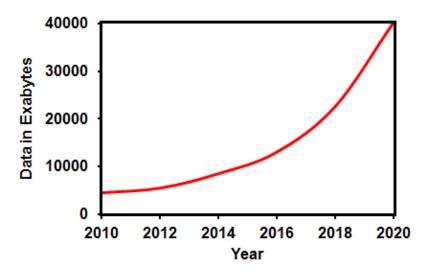

Digital data, obtained from the digitization of various forms of information such as text, image or voice, and sound, plays a vital role in different aspects of our daily lives including business, education, entertainment and communication. The last few decades have seen an extraordinary shift in the usage and value of data storage and memory technologies, driven mainly by the advancements of three particular applications. The first and most significant shift has been the increased usage of modern electronic devices, such as tablets and mobile phones. The second trend has been the shift of focus from individual electronic components to the ability to integrate an increasingly larger volume of elements into subsystems rather than as discrete components on a processor. The third trend has been the increase in the amount of information created and reproduced in digital form, which surpassed the Zettabyte barrier in 2010 [1, 2], and is predicted to increase up to 40 Zettabytes by 2020 [1] (the equivalent of 5200 Gigabytes (GB) per human being), as shown in Figure 1.1. This exponential increase in digital data can be fathomed by the fact that the total storage of personal information uploaded by users to the Facebook server by the end of 2014 exceeded 500 Petabytes. At the same time Google handled more than 7300 Petabytes during that year alone [3, 11].

**Figure 1.1** The growth rate of global digital data per year (adapted from Ref. [1]).

## 1.1 Overview of Data Storage and Memory Technologies

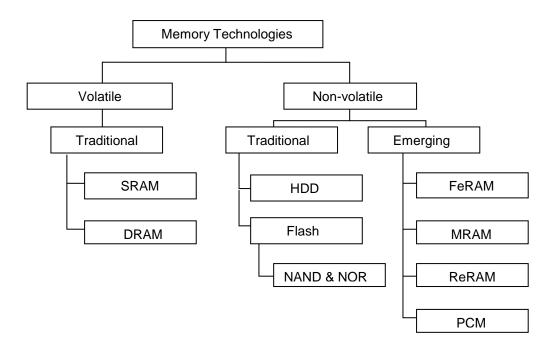

Today's electronic and computing systems use a hierarchy of data storage devices to achieve an optimal trade-off between cost and performance. These devices can be divided into two main categories: (1) volatile memories, and (2) non-volatile memories, as shown in the memory taxonomy in Figure 1.2. In volatile memories, the conservation of data with time (data retention) requires a constant power supply (SRAM, Static Random Access Memory) or periodical refreshing (DRAM, Dynamic Random Access Memory), both of which can be costly in terms of energy, and are consequently expensive. However, volatile memories have very short execution times (~µs-ns), and are used to complete the main tasks in the central processing unit (CPU) such as logic operations [4]. On the other hand, non-volatile memories such as Flash memories and Hard Disk Drives (HDDs) retain data even when the power supply is turned off. These memories have slower processing times, and hence are used mainly for data storage purposes [4]. Section 1.1.1 discusses the characteristics and limitations of some of the currently used volatile and non-volatile memories in further detail.

**Figure 1.2** Memory taxonomy showing various Traditional and Emerging Memory Technologies (adapted from the International Technology Roadmap for Semiconductors (ITRS) 2013 [7]).

# 1.1.1 Traditional Memory Technologies

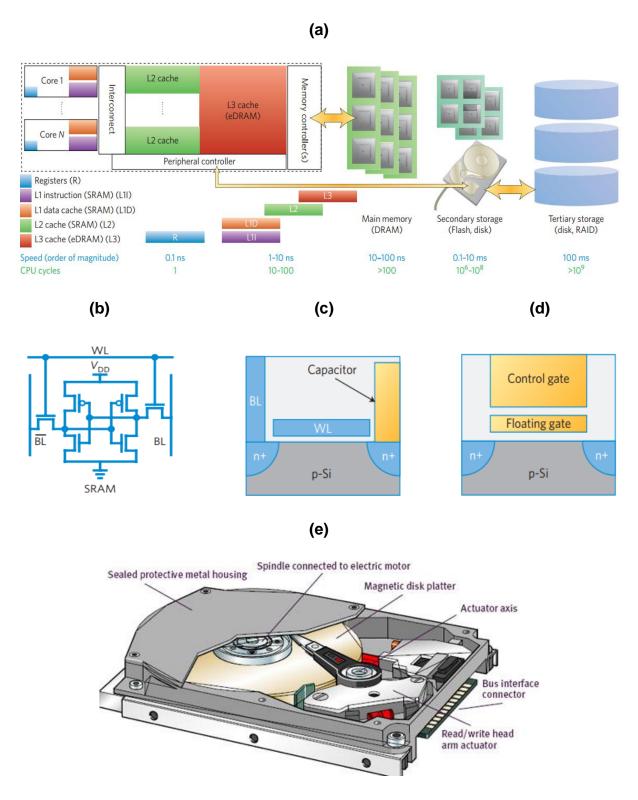

The general technology requirements of memories in modern computing systems are size scalability, high storage density, high endurance, fast speed, low power consumption, low cost, and compatibility and integration with the complementary metal oxide semiconductor (CMOS) platform [5]. For decades, SRAM and DRAM (volatile), and Flash and HDD (non-volatile) have been the workhorses of the memory hierarchy (shown in Figure 1.3 (a)), and hence are classified as traditional (or established) memory technologies.

# 1.1.1.1 Static Random Access Memory (SRAM)

SRAM gains its name from the fact that data is held in a 'static' manner, and does not need to be dynamically refreshed (updated) as in the case of DRAM (Section 1.1.1.2). It is also 'random' which means individual bits in the memory can be accessed rather than being processed sequentially. Whilst the data in SRAM memory does not need dynamic refreshing (making it faster than DRAM), it is still volatile, and as a result data is not held when the power supply is turned off.

The SRAM memory cell typically consists of four transistors configured as two cross coupled inverters, and has two stable states equating to logical '1' and '0' states. In addition to the four transistors, an additional two transistors are also required to control access to the memory cell during read and write processes making a total of six transistors, hence termed as a 6T memory cell (circuitry shown in Figure 1.3 (b)). At present, SRAMs in computer systems are embedded within the CPU and act as Level 1 (L1) and Level 2 (L2) cache memories [6].

Despite SRAM being a well established technology, its (1) large cell size (due to the 6 transistors translating to an 84F<sup>2</sup> size, with F being the smallest feature possible with a chosen lithography technology), and (2) high energy consumption (due to the requirement of a constant power supply) are major limiting factors in the development of this technology. At present it is not clear whether scaling beyond the 16nm node will be possible at all in SRAM [7], hence new alternative memory technologies will be required in order for memories to further scale down to smaller (sub-10nm) dimensions.

# 1.1.1.2 Dynamic Random Access Memory (DRAM)

DRAM stores each data bit on a capacitor within the memory cell which is consistently charged and discharged to provide logical '1' and '0' states. Due to charge leakage of the capacitor, it is necessary to refresh the memory cell periodically, which gives rise to the term 'dynamic'. In contrast, SRAMs do not have to be refreshed. However, DRAM is also volatile, and data is not held when the power supply is disconnected.

DRAM cells consist of one capacitor and one transistor (shown in Figure 1.3 (c)), where the capacitor is used to store charge, and the transistor acts as a switch which enables the control circuitry on the memory chip to read the capacitor or change its state. One of the advantages of DRAM over SRAM is the simplicity of the cell i.e. in DRAMs a single transistor is required for its operation in comparison to SRAMs which require 6 transistors, making its cell size much smaller (6F²). This simplicity also means lower production costs and higher storage densities [9]. However, constant refresh cycles required for the recharging of the capacitor leads to extra power consumption, and processing speeds slower than those in SRAMs. Similar to SRAM, it is not clear whether DRAM cells of the future will be scalable beyond the 16nm node [7], affirming the need for alternative memory technologies which can scale down to single nanometer dimensions.

## 1.1.1.3 Flash Memory

Flash memory was first developed by Toshiba in 1980 and is currently the most widely used technology for electronic non-volatile storage. A typical Flash memory cell (shown in Figure 1.3 (d)) consists of a storage transistor with a control gate and a floating gate. A thin dielectric material or oxide layer is used to insulate the floating gate from the rest of the transistor, and is responsible for storing electrical charge and controlling the flow of current. The transfer of charge (electrons) comes from Fowler- Nordheim tunnelling (a process in which electrons tunnel through a barrier in the presence of a high electric field), or hot electron injection (a process in which an electron gains sufficient kinetic energy to overcome a barrier necessary to break an interface state) which traps the charge in the floating gate, and once stored, charge

**Figure 1.3** (a) Physical distribution and hierarchy of memory in a computer (reprinted from [8]), (b) Schematic of a circuit of a SRAM cell consisting of six transistors. BL, bit line;  $\overline{BL}$ , logic complement of BL; WL, word line;  $V_{DD}$ , supply voltage (reprinted from [8]), (c-d) Schematics of DRAM and Flash memories (reprinted from [8]), (e) Schematic of a typical hard disk (reprinted from [12]).

can remain stored at detectable levels for up to 10 years. As the floating gate is surrounded by an insulator, no refresh cycles are needed as in the case of DRAM [4]. Flash memory is further divided into two main categories: (1) NOR Flash, which uses no shared components and enables random access to data by connecting individual memory cells in parallel, and (2) NAND Flash, which is more compact in size, with a lesser number of bit lines, and connects floating-gate transistors together to achieve greater storage. Hence, NAND Flash is better suited to serial data, whereas NOR Flash is better suited to random access data [4].

Flash memories can be seen in many forms today such as USB memory sticks, digital camera memory cards in the form of Compact Flash, SD cards, mobile phones, laptops, tablets, MP3 players and many more. In comparison to SRAM and DRAM, Flash is much cheaper, retains data even when the power supply is disconnected (non-volatility), and has storage capacities now exceeding Terabytes on a single drive. However, similar to SRAM and DRAM, Flash suffers from some fundamental drawbacks that limit its future potential. In particular, as the technology node continues to scale down, the tunnelling of charge from the floating gate, leading to data loss, becomes a significant problem, and as the cell density increases, the parasitic effect [10] of one cell on adjacent cells becomes prominent. Hence, scaling Flash memories beyond 16nm will be exceedingly difficult without a significant increase in manufacturing costs [4]. In addition, Flash has much slower writing speed ( $\mu$ s-ms) and a seriously limited endurance ( $\sim$ 10<sup>4-5</sup> cycles) [11]. Hence, an alternative memory technology, free from scaling issues with non-volatile data retention, is very much desired.

#### 1.1.1.4 Limitations of Traditional Memory Technologies

The characteristics and limitations of the three main volatile and non-volatile memories in use today (SRAM, DRAM and Flash) have been discussed in Sections 1.1.1.1 – 1.1.1.3. In addition to these technologies, the other main non-volatile storage technology is HDD (Hard Disk Drives, in which reversible magnetic microdomains are created and erased for data storage (shown in Figure 1.3 (e)). The limitations of various traditional memory technologies are listed below and their operational characteristics are summarized in Table 1.1.

- SRAMs and DRAMs are volatile memory technologies; hence a constant power supply or constant refreshing is required for data retention leading to an increase in power consumption. In addition, SRAM and DRAM cells are large in size, and scaling beyond 16nm is challenging for both SRAM and DRAM.

- Flash memories have higher storage capacities, are cheaper, and are non-volatile; therefore no refresh cycles or constant power supply is needed. However, Flash memories are slower (μs-ms), have limited endurance (~10<sup>4-5</sup> cycles), and it is challenging to scale them down to sub-10nm dimensions at present.

- HDDs are non-volatile and have been in use since the 1950s. However, they are much larger in size, slow, and can suffer from head 'crashes' which damage the disk surface resulting in loss of data in that sector.

**Table 1.1** Comparison of various traditional memory technologies [4, 7, 13].

|                             | SRAM                    | DRAM                                                      | Flash                | HDD                   |

|-----------------------------|-------------------------|-----------------------------------------------------------|----------------------|-----------------------|

| Cell Area (F <sup>2</sup> ) | 80-140                  | 6-12                                                      | 4                    | 2/3                   |

| Non-volatility              | No                      | No                                                        | Yes                  | Yes                   |

| Endurance (cycles)          | 10 <sup>16</sup>        | 10 <sup>16</sup>                                          | 10 <sup>4-5</sup>    | 10 <sup>4-5</sup>     |

| Energy per bit (pJ)         | 5 x 10 <sup>-4</sup>    | 5 x 10 <sup>-3</sup>                                      | 2 x 10 <sup>-4</sup> | 5 x 10 <sup>3-4</sup> |

| Speed                       | <1ns                    | 10ns                                                      | 1-10ms               | 5-8 ms                |

| Retention                   | as long as V<br>applied | < <seconds< th=""><th>years</th><th>years</th></seconds<> | years                | years                 |

The limitations and challenges summarized above have led researchers to develop alternative (emerging) non-volatile memory technologies that are relatively free from scaling issues, have lower power consumptions, higher storage densities, faster speeds, can be easily integrated on-chip with the microprocessor cores, and store information using new types of physics that do not rely on storing charge on a capacitor like in DRAM and Flash [8, 9, 11]. Section 1.1.2 discusses some of these emerging memory technologies in further detail.

# 1.1.2 Emerging Memory Technologies

In recent years, emerging memory technologies (shown in Figure 1.2) such as Ferroelectric RAM (FeRAM), Magnetic RAM (MRAM), Resistive RAM (RRAM), and Phase Change Memory (PCM) have been proposed to complement or even replace in some environments, the traditional memory technologies discussed in Section 1.1.1. These emerging technologies are also termed as "universal" memory technologies, where the term "universal" generally refers to technologies that can substitute both primary (SRAM and DRAM), and secondary (Flash and HDD) technologies without losing any of their respective advantages. The following sections discuss and compare the characteristics of some of the leading emerging technologies in use today.

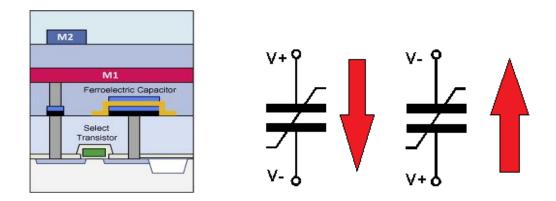

## 1.1.2.1 Ferroelectric RAM (FeRAM)

FeRAM is a type of non-volatile memory based on the permanent polarization of a ferroelectric material (a material that exhibits, over some range of temperature, a spontaneous electric polarization which can be reversed or reoriented by applying an electric field), and has a similar one-transistor/one-capacitor cell structure to DRAM (shown in Figure 1.4). However, the capacitor typically uses a ferroelectric material such as PZT (Pb<sub>x</sub>Zr<sub>1-x</sub>TiO<sub>3</sub>) as the dielectric layer [13], and when charged or discharged (logical '0' and '1' states), a polarization is encoded in the material caused by the change in the positions of the atoms under the application of an electric field. A read is performed by forcing the cell into a particular (known) state, and depending on the polarization of the ferroelectric material, a current spike occurs on the output terminal, allowing the prior polarization to be determined.

FeRAMs have considerable advantages over DRAM and Flash, such as lower power consumption, faster write speeds and no need for constant refresh cycles [4]. However, scalability of FeRAMs is a major drawback at present, mainly due to the signal being proportional to the area of the ferroelectric capacitor, and inversely proportional to thickness, which is limited in scaling by the interaction of the ferroelectric material with the electrodes, hence giving rise to a 'dead zone' [13]. In addition, limited endurance, an intrinsically large cell size, and data loss during the read operation, are all limiting factors in the development of FeRAMs. To overcome

**Figure 1.4** FeRAM schematic cross-section (left) (reprinted from [13]), and FeRAM basic working principle (right) showing that the ferroelectric capacitor can be polarised either up or down by applying the relevant electric field.

these challenges, Ferroelectric Field Effect Transistors (Fe-FETs) and Ferroelectric Polarization RAMs (Fe-PRAMs) have been proposed as potential solutions [13, 14]. In addition, SBT (SrB<sub>2</sub>Ta<sub>2</sub>O<sub>9</sub>) has also been proposed as a replacement for the more widely used PZT material to improve scalability [11]. Despite FeRAMs being trialled in automobile equipment, railway passes, and other electronic appliances in recent years [15], further research on the mentioned limitations is required before FeRAMs can become a dominant and more commercially-viable memory technology.

#### 1.1.2.2 Magnetic RAM (MRAM) and Spin Torque Transfer MRAM (STT-MRAM)

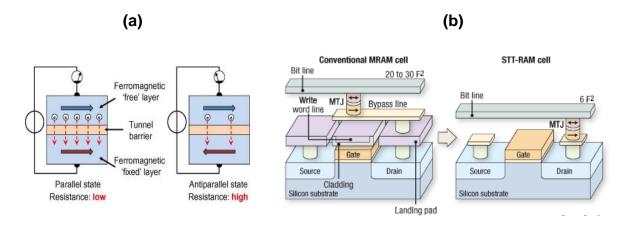

MRAM, first developed by IBM in the 1970s [16], is a form of non-volatile memory that uses magnetic charge to store data instead of electric charge used in DRAM and SRAM technologies. The basic cell structure of MRAM is based on a magnetic tunnel junction (MTJ) which consists of a conducting layer sandwiched between two ferromagnetic layers, with one layer having a fixed magnetization, and the other being a free layer (with a weak coercive field) which can be switched. Data bits are stored as the orientation of the magnetism in the variable layer, and are read from the cell resistivity. When the two layers are parallel, electrons with opposite spin pass without any hindrance allowing the flow of current, resulting in a low resistance ON state (logical '1'). On the other hand, when the layers are not parallel, electrons are scattered strongly, resulting in a high resistance OFF state (logical '0'), as shown in Figure 1.5 (a).

**Figure 1.5** (a) Basic functioning of MRAM (reprinted from [13]). (b) Conventional MRAM device structure vs STT-RAM device structure (Reprinted from [18]).

MRAM magnetic memories present considerable advantages over traditional memory technologies, such as fast speeds (<20ns) and high endurance cycles (>10<sup>12</sup> cycles) along with non-volatility [4, 9]. However, MRAMs at present have a small ON/OFF current ratio (in the order of 30%), high programming currents, complex structure for fabrication, and problems with write operations disturbing neighbouring cells which limit the storage density [13, 14]. Also, similar to FeRAMs, MRAMs have a serious handicap in terms of scaling due to the fact that a degradation of the write, read and retention properties is observed, which is due to the thermal instability of the magnetization in the free (weak coercive field) layer [4].

To overcome the limitations of conventional MRAMs, several improvements have been proposed, such as the introduction of Magnesium Oxide (MgO) as a dielectric material (which was shown to increase the ON/OFF current ratio by more than 300% [13]), and the invention of STT-MRAMs (Spin Torque Transfer MRAMs, cell structure shown in Figure 1.5 (b)) as a potential replacement for existing memory technologies. STT-MRAMs exploit the spin torque transfer phenomenon of magnetic materials (an electromagnetic effect that makes it possible to reverse the magnetization by using spin-polarized electric current), and in comparison to conventional MRAMs, have shown lower switching currents ( $\sim \mu$ A), faster speeds ( $\sim t$ ens of ns), and better scalability (tefF) [11]. In addition, an industrial prototype of 1Gb STT-MRAM at the 54nm node (tefF) has also been presented by Hynix Semiconductor [17].

## 1.1.2.3 Resistive RAM (RRAM)

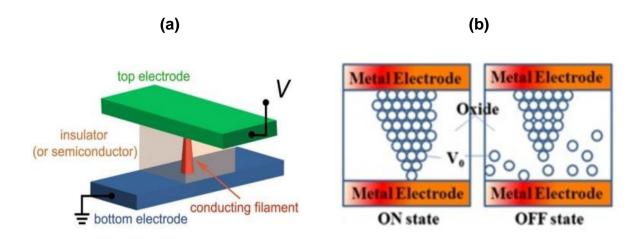

RRAMs are non-volatile memories that store data via the electrical switching between distinct resistance states observed in numerous metal oxides (such as NiO<sub>x</sub>, TiO<sub>x</sub>, and TaO<sub>x</sub>). A typical RRAM cell consists of a resistance-changeable material sandwiched between two metal electrodes, and the change in resistance is achieved by applying controlled current or voltage pulses between the electrodes which typically forms a conductive filament (as shown in Figure 1.6 (a)). The transition from a high resistance OFF state to a low resistance ON state (Set process, Figure 1.6 (b), left), and the reverse transformation from the low resistance ON state to high resistance OFF state (Reset process, Figure 1.6 (b), right) are obtained using different voltage polarities. If the polarities of the Reset and Set states are of the same sign, the RRAM system is termed as 'unipolar', and if the polarities are of the opposite sign, the system is 'bipolar'.

Oxide-based RRAMs are currently one of the most competitive candidates for future non-volatile memory applications due to their simple cell structure, fast switching speeds (~10ns), compatibility with CMOS, and good scalability (<30nm) [19, 20]. In addition, further variations of RRAMs such as CBRAM (Conductive Bridge RAM, a type of RRAM which uses a reactive electrode that supplies mobile ions (e.g. Cu<sup>+</sup>,

**Figure 1.6** (a) Schematic of a RRAM cell with insulator (or semiconductor) sandwiched between metal electrodes. (b) RRAM switching mechanism showing the transition between a low resistance ON state, and high resistance OFF state (reprinted from [9]).

Ag<sup>+</sup>) to move through insulating dielectrics (known as solid-state electrolytes) to form conducting filaments in the ON state) have demonstrated a large ON/OFF ratio, fast speed, and long endurance [14], along with a 16Gb CBRAM test chip presented recently [21]. However, a major challenge in oxide-based RRAMs at present is reliability, mainly variability and failure. In RRAMs the switching (formation and rupture of filaments) is not controlled microscopically, and is intrinsically stochastic, which is reflected in a large variation of device resistance and switching voltage from cycle to cycle and device to device [14]. In addition, the failure mechanisms in RRAMs are not well understood at present. Hence, further research is required to address reliability and power consumption challenges before RRAMs can become a leading memory technology of the future [14, 20].

**Table 1.2** Comparison of various emerging memory technologies [4, 9, 19, 22].