Fayyaz, Asad and Castellazzi, Alberto and Romano, Gianpaolo and Riccio, Michele and Urresti, J. and Wright, Nick (2016) UIS failure mechanism of SiC power MOSFETs. In: 4th IEEE Workshop on Wide Bandgap Power Devices and Applications (WiPDA 2016), 7-9 November 2016, Fayetteville, Arkansas, USA.

## Access from the University of Nottingham repository:

http://eprints.nottingham.ac.uk/41655/1/UIS%20failure%20mechanism%20of%20SiC %20power%20MOSFETs.pdf

## Copyright and reuse:

The Nottingham ePrints service makes this work by researchers of the University of Nottingham available open access under the following conditions.

This article is made available under the University of Nottingham End User licence and may be reused according to the conditions of the licence. For more details see: http://eprints.nottingham.ac.uk/end\_user\_agreement.pdf

## A note on versions:

The version presented here may differ from the published version or from the version of record. If you wish to cite this item you are advised to consult the publisher's version. Please see the repository url above for details on accessing the published version and note that access may require a subscription.

For more information, please contact eprints@nottingham.ac.uk

# UIS failure mechanism of SiC power MOSFETs

Asad Fayyaz, Alberto Castellazzi

Power Electronics, Machines and Control (PEMC) Group, University of Nottingham, Nottingham, UK Gianpaolo Romano, Michele Riccio, Andrea Irace Dept. of Electrical Engineering and Information Technologies, University of Naples Federico II, Naples, Italy

Source

N+

P- Body

Jesus Urresti, Nick Wright

Emerging Technologies and Materials (ETM) Group, Newcastle University, Newcastle Upon Tyne, UK

Source

N+

P- Body

Abstract—This paper investigates the failure mechanism of SiC power MOSFETs during avalanche breakdown under unclamped inductive switching (UIS) test regime. Switches deployed within motor drive applications could experience undesired avalanche breakdown events. Therefore, avalanche ruggedness is an important feature of power devices enabling snubber-less converter design and is also a desired feature in certain applications such as automotive. It is essential to thoroughly characterize SiC power MOSFETs for better understanding of their robustness and more importantly of their corresponding underling physical mechanisms responsible for failure in order to inform device design and technology evolution. Experimental results during UIS at failure and 2D TCAD simulation results are presented in this study.

Keywords—Silicon carbide; MOSFET; Avalanche breakdown; Avalanche ruggedness; Unclamped inductive switching

#### I. INTRODUCTION

Silicon carbide (SiC) power MOEFETs offer impeccable device features for power electronics applications. As compared to Silicon (Si), features such as faster switching speeds, lower on-state losses, lower off-state leakage currents, higher power density per unit area, higher thermal conductivity and smaller die sizes are some of the exciting benefits of SiC which could not be realized using the existing Si device technology [1, 2]. SiC power MOSFETs are relatively newer in device manufacturing technology than its well established Si counterparts. They require extensive characterization comprising of experiments and advanced TCAD simulations assessing their robustness under different unintended test conditions such as UIS (Unclamped inductive switching) and SC (short circuit) for better in-depth understanding into physics of failure mechanism and to facilitate future device technology advancements.

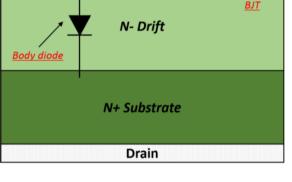

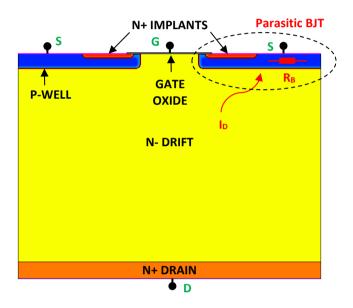

Under UIS, the failure of Si power MOSFETs is linked to the activation of parasitic bipolar junction transistor (BJT) [3]. Fig. 1 illustrates the structure of a power MOSFET. The  $V_{BE}$  of parasitic NPN BJT for Si is around 0.6-0.7V which decreases with temperature at a rate of 2mV/K and on the other hand, the base resistance (R<sub>B</sub>) of the p-well increases with temperature [4]. For parasitic BJT activation, the voltage across both ends of R<sub>B</sub> of the p-well, should be higher than the built-in

Gate

Gate oxide Channel

Layer

Fig. 1: Power MOSFET structure

voltage of the base-emitter junction. Indeed, evolution of Si MOSFET design has targeted substantially the improvement of the parasitic BJT structure to enhance robustness against activation. However, it is expected that the wide bandgap and low intrinsic carrier concentration of SiC makes it very unlikely for the intrinsic BJT to be activated during typical UIS events (i.e. with typical values of switched currents and ensuing temperature evolution). Not only that, the built-in voltage at the base-emitter junction in SiC is also higher (around ~ 2-3V) than in Si [5].

### II. SILICON CARBIDE MOSFET AVALANCHE RUGGEDNESS AND ANALYSIS METHODOLOGY

Avalanche ruggedness is a useful feature of power devices. Ability of power devices to dissipate energy during avalanche breakdown results in convertor designs without snubbers. Also, systems such as engine control units (ECUs) and anti-lock braking systems in automotive applications require power devices to dissipate more consistent overload transient energy release from inductive loads, typically motors and actuator controlled solenoids. Previous publications have shown that commercially available SiC MOSFETs exhibit

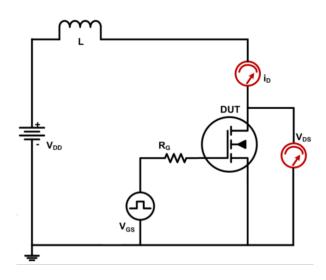

Fig. 2: UIS test circuit schematic

significant intrinsic avalanche ruggedness and could dissipate avalanche energy  $(E_{AV})$  above 1 J, depending on the test conditions [6–8].

UIS test circuit, as illustrated in Fig. 2, is widely used for assessment of avalanche ruggedness of power devices. Here, the device under test (DUT) is turned ON using a single gate pulse ( $t_{ON}$ ) to ramp up the inductor current to the desired value. When the device turns OFF, the device enters avalanche breakdown since current in the inductor cannot immediately go to zero due to the current continuity condition. Parameters such as  $t_{ON}$ , L and  $V_{DD}$  are normally altered to move outside of the device's safe operating area (SOA) until failure is obtained during avalanche breakdown. The self-heating of the DUT during  $t_{ON}$  was simulated and was found to be significantly lower than the temperature levels experienced during avalanche breakdown; therefore, the self-heating of the device is considered here to be negligible.

In order to get more insight into device internal phenomena and the actual failure mechanism during avalanche breakdown, here, experimental results showing failure were reproduced with the aid of 2D TCAD physical simulations. UIS measures were also performed on bare dies where thermal imaging using infrared IR camera was performed to obtain the temperature distribution of the DUT's surface.

### III. EXPERIMENTAL RESULTS

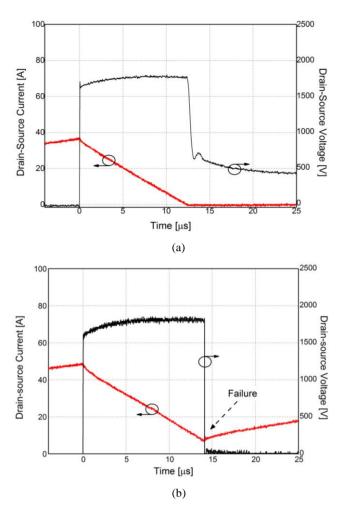

Experimental results showing drain current  $(I_D)$  and voltage  $(V_{DS})$  for UIS test for discrete second generation 1.2kV 36A SiC power MOSFET manufactured by CREE [9] are shown in Fig. 3.

For test condition without failure, Fig. 3(a), the inductor current goes to zero as the avalanche time is lapsed and the drain source voltage goes to  $V_{DD}$ ; therefore, the device still withstands voltage and is hence functional. The peak current (I<sub>0</sub>) and time in avalanche (t<sub>AV</sub>) was increased to dissipate higher

$$E_{AV} = \frac{1}{2} I_0 V_{BD(eff)} t_{AV} \tag{1}$$

Fig. 3: Experimental UIS I<sub>D</sub> and V<sub>DS</sub> failure waveforms; (a) – Before failure; (b) – At failure;  $V_{DD} = 400V$ ;  $T_{CASE} = 25^{\circ}C$ ; L =  $500\mu$ H;

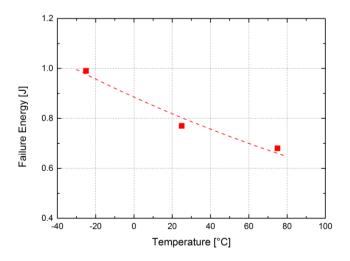

Fig. 4: Critical E<sub>AV</sub> versus temperature (T<sub>CASE</sub>) [10]

avalanche energy ( $E_{AV}$ ) and thus moving out of the safe operating area (SOA) until failure was obtained as reported in Fig. 3(b). At failure, a short was observed between all three terminals of the MOSFET (gate, drain and source) as the voltage comes down sharply and the current starts to increase again linearly as dictated by the inductor alone. Equation (1) dictates the energy dissipated during avalanche breakdown ( $E_{AV}$ ). The critical avalanche energy ( $E_{AV\_CRITICAL}$ ) versus case temperature ( $T_{CASE}$ ) has been plotted in Fig. 4 and it clearly indicates that the critical  $E_{AV}$  decreases for higher  $T_{CASE}$ . Several previous studies have presented the relationship between different I<sub>0</sub> and  $t_{AV}$  values for UIS test on SiC power MOSFETs with an aim to determine the critical  $E_{AV}$  as well as the SOA boundary conditions [10, 11].

#### IV. TCAD SIMULATIONS

TCAD Synopsys Suite was used to investigate the insight physics of the device at failure and give interpretation of experimental results. Fig. 5 shows the full planar cell

Fig. 5: TCAD MOSFET full cell structure (Not to scale)

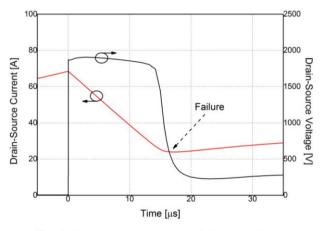

structure which was used to perform 2D electro-thermal device simulations. Cell bulk doping was carefully chosen (N<sub>DRIFT</sub> = 9 x 10<sup>15</sup> cm<sup>-3</sup>) to obtain breakdown voltage (V<sub>BD</sub>) close to the experimental value (V<sub>BD</sub> ~ 1900V) as shown in Fig. 3. The P-body and the N+ source terminals of the simulated device structure were separated (both terminals set to same bias voltage of 0V). Relevant physical models representing interface traps and degradation of mobility were also included into the simulation.

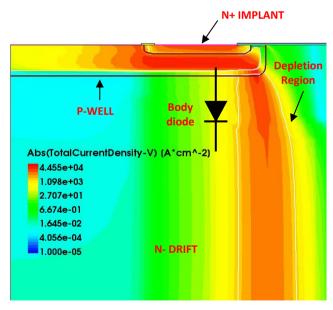

Fig. 7: Total Current Density during avalanche breakdown (<u>Far away from failure</u>)

Fig. 8: Total Current Density; (Zoomed in view of Fig. 7)

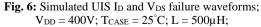

Fig. 6 shows mixed mode TCAD simulation results showing drain current ( $I_D$ ) and voltage ( $V_{DS}$ ) at failure. The total current density distribution within the cell immediately after device enters breakdown is shown in Fig. 7. During avalanche breakdown, the current flows through the intrinsic body diode and the base resistance ( $R_B$ ). Since the electrical field during avalanche breakdown is maximum at the edge of the p-well / ndrift, the current is therefore saturated close to the edge of the pn junction as could be seen in Fig. 7 and Fig. 8. As a result of that, the lattice temperature of the device close to the edge of the pn junction increases rapidly to really high values, raising well above 1000K, as the failure intervenes.

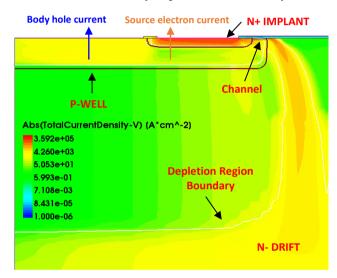

It was observed that as the device temperature increases, current starts flowing in the channel and in the p-well region immediately underneath the channel (Fig. 9) indicating a concurrent decrease of threshold voltage ( $V_{TH}$ ) and an increase of the device leakage current due to such elevated temperatures. This results in a thermally unstable operational condition characterized by rapid thermal runaway. Indeed,

Fig. 9: Total Current Density; (Zoomed in – After failure)

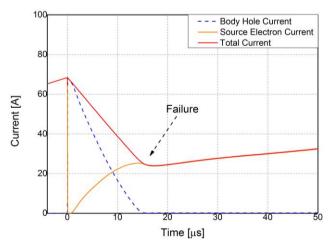

Fig. 10: Different current components

even if channel is activated, bias conditions correspond to a thermally unstable region of operation, characterized by increasing  $I_D$  with temperature [12]. The inability of the device to further withstand voltage after failure is also confirmed as the depletion region shrinks in Fig. 9 suggesting that the device would be no more functional and therefore classed as failed.

The electron and hole current components of the device's total drain-source current are shown in Fig. 10. The source electron current due to majority carriers (orange solid line) is the main current component when the device is ON (channel is activated) to ramp up the inductor current. The source electron current component ideally should be negligible during avalanche breakdown as the device is no more in the ON-state. During avalanche breakdown, holes (dotted blue line) and electrons (red solid line) flow out of p-body and n+ drain terminals respectively as the body diode of a power MOSFET is eventually a PiN diode. But due to reported elevated device lattice temperature in excess of 1000K during avalanche breakdown, V<sub>TH</sub> significantly decreases below zero which results in activation of the channel (increase of source electron current) as well as increase of the drain leakage current underneath the channel leading to thermal runaway and eventually causing device failure as can be better understood from Fig. 9 and Fig. 10.

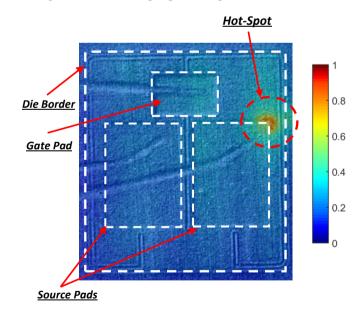

### V. THERMAL MAPPING

To complement the experimental results and the TCAD simulation results, infrared thermal mapping system (as described in [13]) was used to acquire temperature distribution of bare die devices during UIS tests. A localized hot-spot formation due to current crowding over a small number of cells within the total active area of the device was observed as shown in Fig. 11. Thermal map reports temperature normalized to the

Fig. 11: Hot-spot formation during UIS on bare die device (Normalized);  $V_{DD} = 400V$ ;  $T_{CASE} = 75^{\circ}C$

calibration range of camera. Equation (2) was used for temperature normalization during post processing of the thermal map where  $T_{max}$  is the maximum measured temperature of the thermal map and  $T_{REF}$  is the DUT's case temperature. During failure, estimated surface temperature during avalanche breakdown were well in excess of 500°C. The topographic image of the bare die was superimposed onto the thermal map to clearly show the bare die device boundary.

$$T_n = \frac{T - T_{REF}}{T_{\max} - T_{REF}} \tag{2}$$

Further TCAD simulations are required with more cells in parallel in order to investigate the role of device design parameter mismatch in enhancing the occurrence of hot-spots and thermal runaway with highly localized current crowding phenomena. It is really important to ensure uniformities among all cells in the device to avoid weak spots inside the device. By doing this, nonlinearities between cells are kept minimal thus ensuring that the failure occurs randomly in the device's active area [14].

#### VI. CONCLUSION

UIS tests were performed on commercial SiC power MOSFET to assess their avalanche ruggedness. Failure obtained in UIS were reproduced using 2D TCAD electro-thermal simulations showing the physics leading to failure due to a significant decrease in the threshold voltage ( $V_{TH}$ ) and increase in the drain leakage current leading to flow of electron current into the source terminal during avalanche breakdown. Thermal imaging of bare die devices under UIS conditions were also performed and a localized hot-spot due to focalization of current in a small area was observed on the device during failure. It is also needed that investigations assessing device's avalanche breakdown capability should be coupled with body diode forward voltage stability [15] to give a better understanding and characterization of the body diode feature of SiC power MOSFETs.

#### REFERENCES

A. Elasser and T. P. Chow, "Silicon carbide benefits and advantages for power electronics circuits and systems," in *Proceedings of the IEEE*, vol. 90, no. 6, pp. 969-986, Jun 2002.

- [2] J. Rabkowski, D. Peftitsis and H. P. Nee, "Silicon Carbide Power Transistors: A New Era in Power Electronics Is Initiated," in *IEEE Industrial Electronics Magazine*, vol. 6, no. 2, pp. 17-26, June 2012.

- [3] K. Fischer and K. Shenai, "Dynamics of power MOSFET switching under unclamped inductive loading conditions," in *IEEE Transactions on Electron Devices*, vol. 43, no. 6, pp. 1007-1015, Jun 1996.

- [4] A. Castellazzi, V. Kartal, R. Kraus, N. Seliger, M. Honsberg-Riedl, D. Schmitt-Landsiedel, Hot-Spot Meaurements and Analysis of Electro-Thermal Effects in Low-Voltage Power-MOSFET's, Microelectronics Reliability, Volume 43, Issue 9, 2003, Pages 1877-1882.

- [5] B.J. Baliga, Silicon Carbide Power Devices, River Edge, NJ, USA: World Scientific, 2012.

- [6] A. Fayyaz, L. Yang, M. Riccio, A. Castellazzi, A. Irace, Single pulse avalanche robustness and repetitive stress ageing of SiC power MOSFETs, Microelectronics Reliability, Volume 54, Issues 9–10, September–October 2014, Pages 2185-2190.

- [7] A. Fayyaz, L. Yang and A. Castellazzi, "Transient robustness testing of silicon carbide (SiC) power MOSFETs," *Power Electronics and Applications (EPE), 2013 15th European Conference on*, Lille, 2013, pp. 1-10.

- [8] P. Losee et al., "1.2kV class SiC MOSFETs with improved performance over wide operating temperature," 2014 IEEE 26th International Symposium on Power Semiconductor Devices & IC's (ISPSD), Waikoloa, HI, 2014, pp. 297-300.

- [9] C2M0080120D Datasheet, Wolfspeed, Durham, NC, USA, 2015.

- [10] A. Fayyaz, G. Romano, A. Castellazzi and A. Irace, "Robustness investigation of SiC Power MOSFETs under negative temperature," *Power Electronics and Applications (EPE), 2016 18th European Conference on*, Karlsruhe, 2016, pp. 1-8. (In press)

- [11] C. DiMarino and B. Hull, "Characterization and prediction of the avalanche performance of 1.2 kV SiC MOSFETs," *Wide Bandgap Power Devices and Applications (WiPDA), 2015 IEEE 3rd Workshop on*, Blacksburg, VA, 2015, pp. 263-267.

- [12] M. Riccio, A. Castellazzi, G. De Falco, A. Irace, Experimental analysis of electro-thermal instability in SiC Power MOSFETs, Microelectronics Reliability, Volume 53, Issues 9–11, September–November 2013, Pages 1739-1744.

- [13] G. Romano, M. Riccio, G. De Falco, L. Maresca, A. Irace and G. Breglio, "An ultrafast IR thermography system for transient temperature detection on electronic devices," 2014 Semiconductor Thermal Measurement and Management Symposium (SEMI-THERM), San Jose, CA, 2014, pp. 80-84.

- [14] Muhammad Nawaz, Evaluation of SiC MOSFET power modules under unclamped inductive switching test environment, Microelectronics Reliability, Volume 63, August 2016, Pages 97-103.

- [15] A. Fayyaz, G. Romano, A. Castellazzi, Body diode reliability investigation of SiC power MOSFETs, Microelectronics Reliability, Available online 18 September 2016. (*In press*)