# Non-Destructive Evaluation of Solder Joint Reliability

Derek Richard Braden B.Eng., M.Sc.

Ph.D. Thesis

April 2012

# THESIS CONTAINS CD/DVD

# The following figures and tables have been omitted on request of the university –

| Fig 1.1 (p.2)            | Fig 3.6 (p.36)              |

|--------------------------|-----------------------------|

| Fig 2.1 (p.8)            | Table 3.1 (p.39)            |

| Fig 2.2 (p.9)            | Table 3.3 (p.42)            |

| Fig 2.4 (p.10)           | Fig 3.7 (p.43)              |

| Fig 2.5 & Fig 2.6 (p.11) | Fig 3.9 (p.46)              |

| Fig 2.8 (p.12)           | Table 3.5 (p.47)            |

| Fig 2.9 & Fig 2.10 (p13) | Fig 3.10 (p.48)             |

| Fig 2.13 (p.15)          | Fig 3.11 & Fig 3.12 (p.49)  |

| Fig 2.14 (p.17)          | Fig 3.14 (p.52)             |

| Fig 2.15 (p.18)          | Fig 3.34 (p.69)             |

| Fig 2.17 (p.20)          | Fig 5.18 & Fig 5.19 (p.110) |

| Fig 2.19 (p.22)          |                             |

| Fig 3.2 & Fig 3.3 (p.30) |                             |

| Fig 3.4 (p.32)           |                             |

| Fig 3.5 (p.35)           |                             |

# Non-Destructive Evaluation of Solder Joint Reliability

### Derek Richard Braden B.Eng., M.Sc.

A thesis submitted in partial fulfillment of the requirements of Liverpool John Moores University for the degree of Doctor of Philosophy

> General Engineering Research Institute Liverpool John Moores University

> > April 2012

### Abstract

A through life non-destructive evaluation technique is presented in which a key solder joint feature, nucleating at the bump to silicon interface and propagating across a laminar crack plane is captured and tracked using acoustic microscopy imaging (AMI). The feasibility of this concept was successfully demonstrated by employing the measurement technique in combination with Finite Element Analysis (FEA) to study the impact of component floor plan layout on the reliability of electronics systems subjected to thermal cycling.

A comprehensive review of current and emerging packaging and interconnect technologies has shown increasingly a move from conventional 2D to 3D packaging. These present new challenges for reliability and Non Destructive Evaluation (NDE) due to solder joints being hidden beneath the packaging, and not ordinarily visible or accessible for inspection.

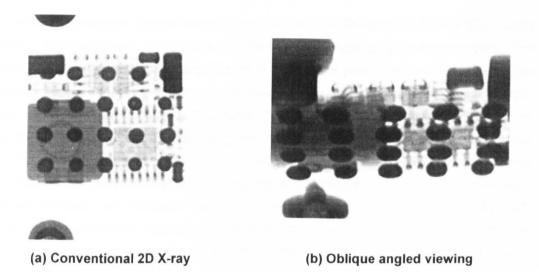

Solutions are developed using non-destructive testing (NDT) techniques that have the potential to detect and locate defects in microelectronic devices. This thesis reports on X-ray and Acoustic Micro Imaging (AMI) which have complementary image discriminating features. Gap type defects are hard to find using X-ray alone due to low contrast and spot size resolution, whereas AMI having better axial resolution has allowed cracks and delamination at closely spaced interfaces to be investigated. The application of AMI to the study of through life solder joint behaviour has been achieved for the first time.

Finite Element Analysis and AMI performance were compared to measure solder joint reliability for several realistic test cases. AMI images were taken at regular intervals to monitor throughlife behaviour. Image processing techniques were used to extract a diameter measurement for a laminar crack plane, within a solder joint damage region occurring at the bump to silicon interface. FEA solder joint reliability simulations for flip-chip and micro-BGA (mBGA) packages placed on FR4 PCB's were compared to the AMI measurement performance, with a reasonable level of correlation observed. Both techniques clearly showed significant reliability degradation of the critical solder joints located furthest from the neutral axis of the package, typically residing at the package corners. The technique also confirmed that circuit board thickness can affect interconnect reliability, as can floor plan. Improved correlation to the real world environment was achieved when simulation models considered the entire floor plan layout and constraints imposed on the circuit board assembly.

This thesis established a novel through life solder joint evaluation method crucial to the development of better physics of failure models and the advancement of model based prognostics in electronics systems.

ii

### Acknowledgements

I would like to acknowledge and thank the following people and companies for their generous support and help. Without them I would not have been able to complete this work.

Firstly I would like to thank my employers Delphi Electronics and Safety for providing the required financial and technical support to enable this research to be brought to fruition. I would particularly like thank Dr Marek Wojcik and Janusz Duralek for providing simulation support and a practical introduction to FEA, Pam Williamson for micro-sectioning of test samples and obtaining subsequent SEM images. Steve Graham for ensuring ECAD resource was available for test board design, and thanks also to David Parry for designing the layout of the test board and supervising its manufacture. Thanks also to Bob Schofield, for checking through my thesis and making recommendations for improvement. There are many people throughout Delphi who have contributed or supported in some way to the success of this work. Unfortunately I cannot list you all, but you know who you are and I sincerely thank you for giving freely your time for technical discussions or making available services at your disposal.

I would particularly like to thank Dr Scott Popelar for generously taking the time to discuss his original papers with me, providing encouraging advice and additional modelling information.

The seed of undertaking a PhD was planted in my mind by my good friend Dr Adrian Craven, the seed would never have taken root without the persuasive nature of Professor David Harvey, I thank you both for your enlightened views of my ability.

To my esteemed academic supervisors Professor David Harvey and Dr Guang-Ming Zhang, I sincerely thank you for your guidance, support and enthusiasm throughout my research, and in particular the final preparation of this thesis. I would also like to thank Ryan Yang for his assistance with AMI and X-ray imaging of test samples, sense of humour, and encouraging advice at critical times during my writing up. This thesis, and friendships developed would not have been possible without the many entertaining and inspirational discussions we have held in Dr Zhang's 'office'. I truly thank them for the inspiration, fun and sanity these discussions provided.

Also, I would like to thank my longstanding friends Steve Jeffries and John McColl for providing encouragement, humour and sense of perspective throughout this marathon project. We can now get back out on the mountains again! I also thank them for their thorough review of my written work.

Finally, undertaking and completing this work would not have been possible without the unconditional love and support from my wonderful wife, Angela. Her willingness to sacrifice so much, in order for me to complete this work is incalculable. As a sign of my love and gratitude I dedicate this work to Angela and my young son Samuel, for whom the adventure and wonders of the world are merely beginning. His daddy has now finished writing "his book" it's now time to play!

iii

# **Table of Contents**

| ABSTRACT             |             |

|----------------------|-------------|

| ACKNOWLEDGEMENTS     |             |

| TABLE OF CONTENTS    | IV          |

| LIST OF PUBLICATIONS | <b>vi</b> i |

| LIST OF FIGURES      | IX          |

| LIST OF TABLES       | XIII        |

| GLOSSARY OF TERMS    | XIV         |

#### **CHAPTER 1**

| INTROD | UCTION 1                                  |

|--------|-------------------------------------------|

| 1.1    | Background to Project1                    |

| 1.3    | Motivation and Contribution to Knowledge5 |

| 1.4    | Thesis Outline                            |

#### **CHAPTER 2**

| AR | EA A | RRAY I | PACKAGING TECHNOLOGIES                               | 7  |

|----|------|--------|------------------------------------------------------|----|

|    | 2.1  | Introd | uction                                               | 7  |

|    | 2.2  | A Brie | f Review of Packaging                                | 7  |

|    | 2.3  | Next G | eneration Packaging                                  | 9  |

|    | 2.4  | Levels | of Interconnection Technology for Area Array Devices | 14 |

|    |      | 2.4.1  | Solder ball (bump) interconnect                      | 15 |

|    |      | 2.4.2  | Through silicon vias (TSV)                           | 18 |

|    | 2.5  | Packa  | ging Substrate Technology                            | 19 |

|    | 2.6  | Packa  | ge Overmoulding Technology                           | 22 |

|    |      | 2.6.1  | Dam and fill encapsulation.                          | 22 |

|    |      | 2.6.2  | Transfer moulding encapsulation                      | 23 |

|    | 2.7  | Summa  | ary of Packaging Issues Affecting Reliability        | 23 |

#### CHAPTER 3

| RE | LIABI |         | SSESSMENT OF SOLDER JOINTS                       | 25 |

|----|-------|---------|--------------------------------------------------|----|

|    | 3.1   | Introdu | uction                                           | 25 |

|    | 3.2   | Funda   | mentals of Reliability and Environmental Testing | 26 |

|    |       | 3.2.1   | Probability                                      |    |

|    |       | 3.2.2   | Time period                                      | 27 |

|    |       |         |                                                  |    |

|     | 3.2.4   | Failure life distribution                                     | 28 |

|-----|---------|---------------------------------------------------------------|----|

| 3.3 | Fatigu  | e Failure Models, Acceleration Models and Accelerated Testing | 31 |

|     | 3.3.1   | Plastic and creep strain based fatigue model approach         | 32 |

|     | 3.3.2   | Energy-based models                                           | 35 |

|     | 3.3.3   | Fracture mechanics-based models                               | 37 |

|     | 3.3.4   | Accelerated test models                                       | 37 |

| 3.4 | Non-D   | estructive Inspection Methodologies                           | 42 |

|     | 3.4.1   | X-ray                                                         | 43 |

|     | 3.4.2   | Acoustic micro imaging (AMI)                                  | 45 |

|     | 3.4.3   | Acoustic micro imaging and X-ray inspection comparison study  | 51 |

|     | 3.4.4   | Development of advanced acoustic micro imaging techniques     | 55 |

| 3.5 | Experi  | mental Design and NDE of Solder Joints                        | 56 |

|     | 3.5.1   | Floor plan layout test board design and construction          | 56 |

|     | 3.5.2   | Test regime / setup                                           | 58 |

| 3.6 | AMI ins | spection of Test Samples                                      | 60 |

| 3.7 | X-ray a | nd Microsectioned Inspection of Test Samples                  | 65 |

| 3.8 | Summa   | ary of Testing Results                                        | 69 |

#### CHAPTER 4

| SOLDER  | JOIN      | T FAILURE          | ANALYSIS           | USING          | FINITE        | ELEMENT          |

|---------|-----------|--------------------|--------------------|----------------|---------------|------------------|

| MODELLI | NG        |                    |                    |                |               |                  |

| 4.1     | Introduc  | tion               |                    |                | •••••         |                  |

| 4.2     | Solder J  | oint Fatigue Mode  | el                 |                |               |                  |

| 4.3     | Fatigue   | Life Prediction Mo | odel               |                | ••••••        |                  |

| 4.4     | Bounda    | ry and Model Con   | straints           |                |               |                  |

| 4.5     | Flip Chij | o Modelling and S  | imulation Case     | Studies        |               |                  |

|         | 4.5.1     | Single component   | , single side plac | ement (M1)     |               |                  |

|         | 4.5.2     | Flip chip compone  | ents mirrored on a | a substrate (I | M2)           |                  |

|         | 4.5.3     | Mirrored packages  | s modelled using   | a global PCI   | B approach    | ( <b>M</b> 3) 80 |

| 4.6     | Simulati  | on Results         |                    |                |               | 81               |

|         | 4.6.1     | Single side placen | nent 0.8mm and     | 1.6mm subst    | trate thickne | ss (M1) 82       |

|         | 4.6.2     | 'Mirrored' placeme | ent 0.8mm and 1.   | 6mm substra    | ate thickness | s (M2) 82        |

|         | 4.6.3     | Global model appr  | roach applied to r | nirrored plac  | ement (M3)    |                  |

| 4.7     | Inter-cas | e Study Comparis   | sons               |                |               | 85               |

|         | 4.7.1     | Organic substrate  | thickness 0.8 mr   | n vs. 1.6 mm   | (M4)          | 85               |

|         | 4.7.2     | Single side compo  | nent vs. mirrored  | l configuratio | n (M5)        |                  |

|        | 4.7.3   | Single & mirrored configuration vs. global model approach (N | <i>I</i> 6) 87 |

|--------|---------|--------------------------------------------------------------|----------------|

| 4.8    | mBGA    | Modelling and Simulation Case Studies                        | 88             |

| 4.9    |         | ary and Discussion of the Results                            |                |

|        |         |                                                              |                |

| CHAPTE | R 5     |                                                              |                |

| SOLDER | JOINT   | THROUGH LIFE MONITORING                                      |                |

| 5.1    | Measu   | rement of Crack Plane Diameters of the Solder Joints         |                |

| 5.2    | Ultrase | ound Imaging and Crack Plane Results                         |                |

|        | 5.2.1   | Ultrasound images of bumps                                   |                |

|        | 5.2.2   | Correlation of simulated and measured results                | 104            |

| 5.3    | Throug  | gh Life Measurement Summary                                  | 108            |

| CHAPTE | R 6     |                                                              |                |

| CONCLU | ISIONS  | ·                                                            | 112            |

| 6.1    |         | ary of Achievements                                          |                |

| 6.2    |         | stions for Further Work                                      |                |

|        |         |                                                              |                |

| REFERE | NCES.   |                                                              | 117            |

|        |         |                                                              |                |

| APPEND | IX A    | TEST BOARD CONFIGURATIONS                                    | 124            |

| APPEND | IX B    | MODELLING PARAMETER DETAILS                                  | 125            |

| APPEND | IX C    | ADVANCED ACOUSTIC IMAGING TECHNIQUES                         | 127            |

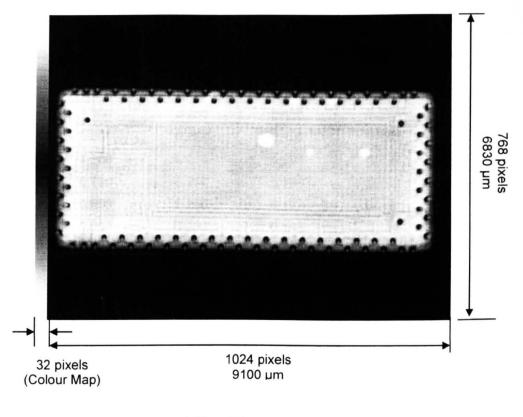

| APPEND | IX D    | DETERMINATION OF PIXEL DIMENSIONS                            | 132            |

| APPEND | IX E    | COMMON TRANSDUCER SPECIFICATIONS                             | 133            |

| APPEND | IX F    | DVD DATA ARCHIVE                                             | 134            |

# List of Publications

#### **Referred Journal Papers**

- 1. Ryan S.H. Yang, Derek R. Braden, Guang-Ming Zhang and David M. Harvey, "Through lifetime monitoring of solder joints using Acoustic Micro Imaging": Soldering & Surface Mount Technology (SSMT), 24(1):30-37, 2012.

- Yang, R.S.H., Braden, D.R., Zhang, G.-M. and Harvey, D.M. An automated ultrasound inspection approach for solder joint assessment. Submitted to Microelectronics Reliability, 2011. (Under review process)

- G.-M. Zhang, D.M. Harvey, and D.R. Braden, "Signal de-noising and ultrasonic flaw detection via overcomplete and sparse representations," J. Acoustic Society of America, 124(5):2963-2972, 2008

- 4. G.-M. Zhang, D.M. Harvey, and D.R. Braden, "Microelectronic package characterisation using scanning acoustic microscopy," NDT&E International, 40(8):609-617, 2007

- 5. G.-M. Zhang, D.M. Harvey, and D.R. Braden, "Effect of sparse basis selection on ultrasonic signal representation," Ultrasonics, 45:82-91, 2006.

- 6. G.-M. Zhang, D.M. Harvey, and D.R. Braden, "Adaptive sparse representations of ultrasonic signals for acoustic micro-imaging," J. Acoustic Society of America, 120(2): 862-869, 2006

- G.-M. Zhang, D.M. Harvey, and D.R. Braden, "Advanced acoustic micro-imaging using sparse signal representation for the evaluation of microelectronic packages," IEEE Trans Advanced Packaging, 29(2):271-283, 2006.

- G.-M. Zhang, D.M. Harvey, and D.R. Braden, "Resolution improvement of acoustic micro-imaging by continuous wavelet transform for semiconductor inspection," Microelectronics Reliability, 46(5-6):811-821, 2006.

- 9. G.-M. Zhang, D.M. Harvey, and D.R. Braden, An improved acoustic micro-imaging technique with learning overcomplete representation, J. Acoustic Society of America, 118(6): 3706-3720, 2005.

- **10. G.-M. Zhang, D.M. Harvey and D.R. Braden**, High resolution AMI technique for the evaluation of microelectronic packages, IEE Electronics Letters, 40(6): 399-400, 2004.

#### Conference Papers

- 11. Ryan S.H. Yang, Derek R. Braden, Guang-Ming Zhang, and David M. Harvey, Through Lifetime Solder Joint Reliability: Prediction and Monitoring 12th International Conference on Electronics Materials and Packaging (EMAP) 2010, Singapore, October 25th-27th 2010.

- Derek R. Braden, Ryan S.H. Yang, Janusz Duralek, Guang-Ming Zhang and David M. Harvey, Investigation into the impact of component floor plan layout on the overall reliability of electronics systems in harsh environments.

3rd Electronics System Technology Conference (ESTC), 13<sup>th</sup>-16<sup>th</sup> September, Berlin, 2010.

- 13. Ryan S.H. Yang, David M. Harvey, Guang-Ming Zhang, and Derek R. Braden, Reliability of Solder Joints Assessed by Acoustic Imaging during Accelerated Cycling, 3rd Electronics System Technology Conference (ESTC), 13<sup>th</sup>-16<sup>th</sup> September, Berlin, 2010.

- 14. Ryan S.H. Yang, David M. Harvey, Guang-Ming Zhang, and Derek R. Braden Feature Extraction of Acoustic Images for Reliability Testing of Solder Joints, GERI Annual Research Symposium (GARS), Liverpool John Moores University, UK, June 2010.

- **15.** Derek R. Braden, Ryan S.H. Yang, Janusz Duralek, Guang-Ming Zhang and David M Harvey, Monitoring through life behaviour of solder joints subjected to thermal cycling using AMI GERI Annual Research Symposium (GARS), Liverpool John Moores University, UK, June 2010.

- 16. Guang-Ming Zhang, Ryan S.H. Yang, Derek R. Braden, and David M.Harvey Sparse representation Methods for Ultrasonic NDE Signal processing, 10<sup>th</sup> western Pacific Acoustics Conference, 21<sup>st</sup>-23<sup>rd</sup> September 2009, Beijing, China.

- 17. D.R. Braden. D.M. Harvey, and G.-M. Zhang, A novel approach to accelerated thermal testing of electronic products using self-heating and thermal profiling GERI Annual Research Symposium, 23rd June 2009, LJMU, Liverpool, UK.

- 18. G.-M. Zhang, D.M. Harvey, and D.R. Braden, Ultrasonic Flaw Detection using Sparse Representation for Failure Analysis of Next Generation Microelectronic Packages, 2nd Electronics System-Integration Technology Conference, 1st-4th September 2008, Greenwich, London, UK, accepted, 2008

- G.-M. Zhang, D.M. Harvey, D.R. Braden, Sparse Deconvolution of Ultrasonic NDE Traces - A Preliminary Study, IEEE International Ultrasonics Symposium, 2-5 November 2008, Beijing, China.

- 20. D.M. Harvey, G.-M. Zhang, and D.R. Braden, Sensor requirements for modern circuit board inspection IOP Sensors & their Applications XIV, Liverpool, 2007.

- 21. G.-M. Zhang, D.M. Harvey, and D.R. Braden, Ultrasonic signal inspection improvement for detection of defects in microelectronic packages, IMAPS- 38th International Symposium on Microelectronics, 2005.

- 22. G.-M. Zhang, D.M. Harvey, and D.R. Braden, X-ray inspection and acoustic micro imaging applied to quality testing of BGA solder joints a comparative study, Proc. IEEE 6th International Conference on Electronic Materials and Packaging, pp.361-366, 2004.

- 23. G.-M. Zhang, D.M. Harvey, and D.R. Braden, Acoustic time-frequency domain imaging for the evaluation of microelectronic packages, Proc. IEEE 6th International Conference on Electronic Materials and Packaging, pp.355-360, 2004.

# List of Figures

| Figure 1-1: Example of Package-on-Package (PoP) (Statschippac)                                                                                                 | 2  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-1: Cross section of Plastic Ball Grid Array (PBGA) (ETAC data sheet)                                                                                  | 8  |

| Figure 2-2: Pyramid stack configuration (i2a Technologies website)                                                                                             | 9  |

| Figure 2-3: Same-die stack configuration (i2a Technologies website)                                                                                            | 10 |

| Figure 2-4: Overhang cross stack configuration (i2a Technologies website)                                                                                      | 10 |

| Figure 2-5: PoP packaging variations (INEMI, 2007)                                                                                                             | 11 |

| Figure 2-6: PiP packaging variations (INEMI, 2007)                                                                                                             | 11 |

| Figure 2-7: Example of a Fan-In Chip PoP (FiPoP)                                                                                                               | 12 |

| Figure 2-8: TSV usage and via critical dimensions (CD) (Lassig, 2007)                                                                                          | 12 |

| Figure 2-9: Typical SiP packaging technology in 2010 (INEMI, 2007)                                                                                             | 13 |

| Figure 2-10: Four silicon die stacked in polymer PCB (INEMI, 2007)                                                                                             | 13 |

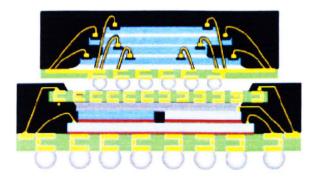

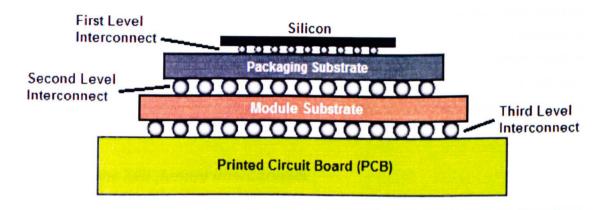

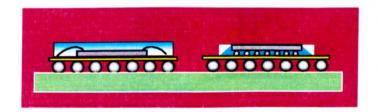

| Figure 2-11: Hierarchical interconnect level structure                                                                                                         | 14 |

| Figure 2-12: Die face up (left) or face down (right)                                                                                                           | 14 |

| Figure 2-13: Pictorial of solder ball and solder column interconnections (Fillion, 2006).                                                                      | 15 |

| Figure 2-14: Reflowed printed bumps onto UBM (Courtesy of Pac Tech)                                                                                            | 17 |

| Figure 2-15: Micro-section of TSV interposer (Institute of Microelectronics (IME),<br>Singapore)                                                               | 18 |

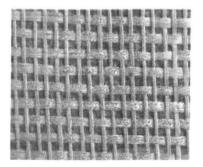

| Figure 2-16: Standard industry laminate pre-preg weaves                                                                                                        | 19 |

| Figure 2-17: Glass transition temperature (T <sub>g</sub> ) curves for various laminates<br>(Ritchey, 1999)                                                    | 20 |

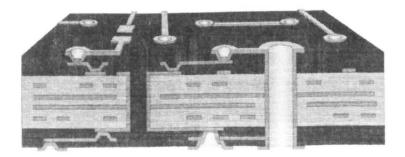

| Figure 2-18: Illustration showing microvias used in combination with standard through and buried vias to interconnect multiple layers in interposer substrate. | 21 |

| Figure 2-19: Warpage of un-encapsulated package (Fielstad, et al., 2003).                                                                                      | 22 |

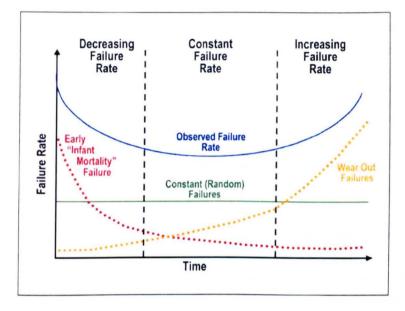

| Figure 3-1: Reliability bathtub curve                                                                                                                          | 28 |

| Figure 3-2: The effect of $\beta$ on the Weibull failure rate function (Reliasoft, 2010)                                                                       | 30 |

| Figure 3-3: The effects of $\eta$ on the Welbull pdf for a common $\beta$ (Reliasoft, 2010)                                                                    | 30 |

| Figure 3-4: Strain v time graph, indicating the stages of creep (Plumbridge, et al.,<br>2003)                                                                  | 32 |

| Figure 3-5: Hysteresis loop showing stress-strain relationship during a mechanical<br>fatigue cycle (Plumbridge, et al., 2003)        | 35 |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3-6: Thermo-mechanical hysteresis loop response (Plumbridge, et al., 2003)                                                     | 36 |

| Figure 3-7: Diagram of 2D X-ray imaging principle (Focalspot, Inc.)                                                                   | 43 |

| Figure 3-8: Gap type features imaged using scanning acoustic microscopy (Sonix<br>Inc.)                                               | 45 |

| Figure 3-9: Diagram showing reflections through a material boundary and also when encountering an air gap (Courtesy of Sonoscan Inc.) | 46 |

| Figure 3-10: Illustration of the two main AMI techniques (Courtesy of Sonoscan Inc.)                                                  | 48 |

| Figure 3-11: Gating at various depths within a sample (Courtesy of Sonoscan Inc.)                                                     | 49 |

| Figure 3-12: Gating at various depths within a sample (Courtesy of Sonoscan Inc.)                                                     | 49 |

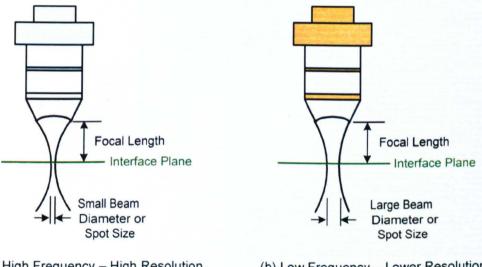

| Figure 3-13: Diagram illustrating influence of transducer frequency on resolution                                                     | 50 |

| Figure 3-14: X-ray and AMI images Flip-Chip on Ceramic substrate (Zhang, et al., 2004)                                                | 52 |

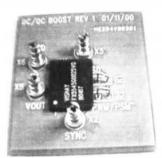

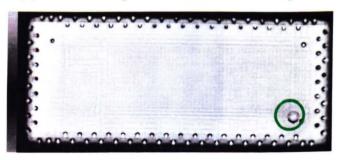

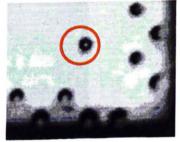

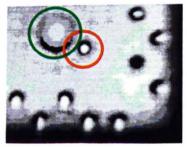

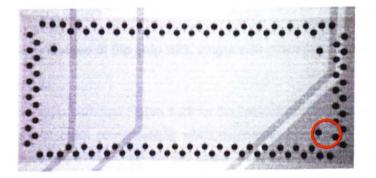

| Figure 3-15: Vishay FunctionPAK® Power BGA DC-DC converter demonstration board                                                        | 52 |

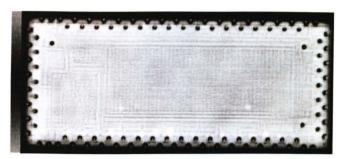

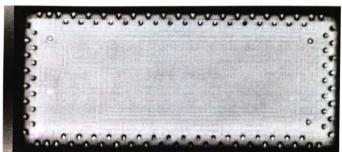

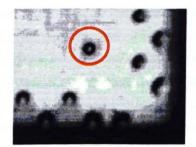

| Figure 3-16: Imaging of PowerBGA™ using 5MHz acoustic transducer                                                                      | 53 |

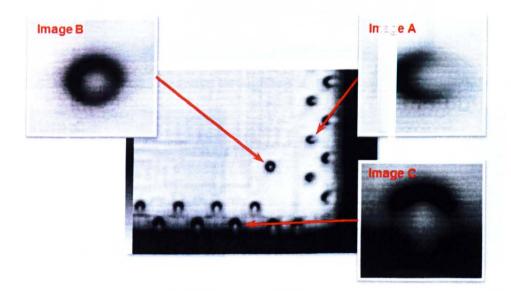

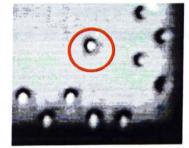

| Figure 3-17 X-ray imaging of PowerBGA™ after environmental testing                                                                    | 55 |

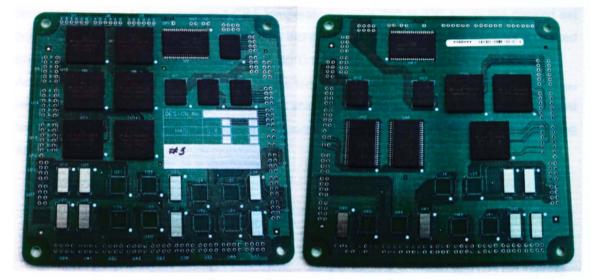

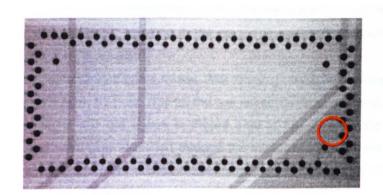

| Figure 3-18: Photograph of completed circuit board (RSS1 and RSS2)                                                                    | 57 |

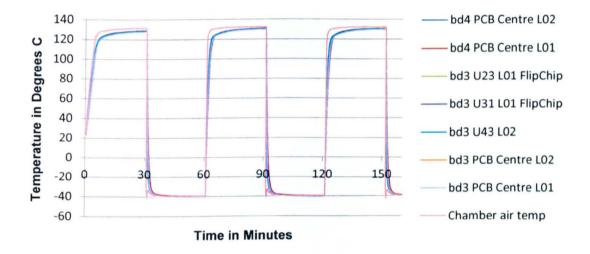

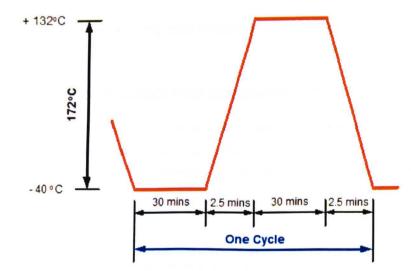

| Figure 3-19: Test thermal profile - chamber set point -40°C to +134°C                                                                 | 58 |

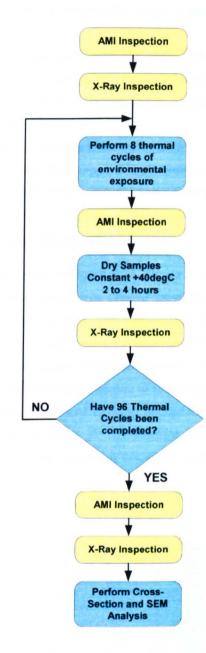

| Figure 3-20: Flow Chart of Test and Inspection Regime                                                                                 | 59 |

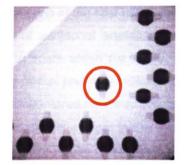

| Figure 3-21: Solder joints at different locations on the Flip- Chip                                                                   | 60 |

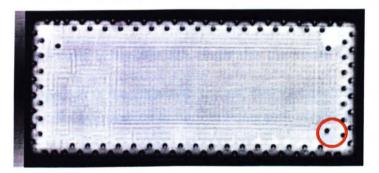

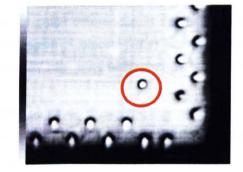

| Figure 3-22: AMI images of flip chip U23, single side placement 0.8mm substrate                                                       | 61 |

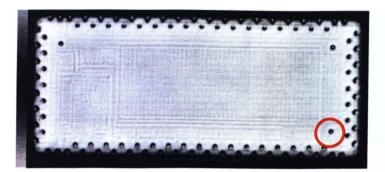

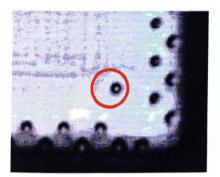

| Figure 3-23: AMI images of flip chip U23, single side placement 1.6mm substrate                                                       | 62 |

| Figure 3-24: Mirrored Component Placement U31 reflow side 1, 0.8mm substrate                                                          | 63 |

| Figure 3-25: Mirrored Component Placement U43 reflow side 2, 0.8mm substrate                                                          | 63 |

| Figure 3-26: Mirrored Component Placement U31 reflow side 1, 1.6mm substrate                                                          | 64 |

| Figure 3-27: Mirrored Component Placement U43 reflow side 2, 1.6mm substrate                                                          | 64 |

| Figure 3-28: X-ray images of flip chip U23, single side placement 0.8mm substrate                                                     | 65 |

| Figure 3-29: X-ray images of flip chip U23, single side placement 1.6mm substrate                                                     | 66 |

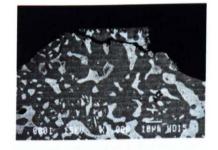

| Figure 3-30: Micro sections of flip chip U23, single side placement 0.8mm substrate                                                   | 67 |

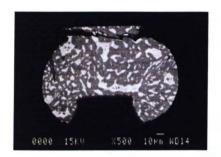

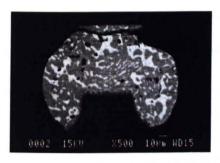

| Figure 3-31: Microsection of flip chip U23, single side placement 1.6mm substrate                                                               | 68 |

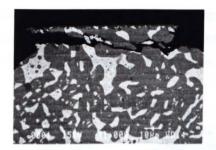

|-------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3-32: Microsection of U31 and U43, mirrored placement 0.8mm substrate                                                                    | 68 |

| Figure 3-33: Microsection of U31 and U43, mirrored placement 1.6mm substrate                                                                    | 68 |

| Figure 3-34: Accumulation effects of fatigue damage in solder joints (Werner, 1997)                                                             | 69 |

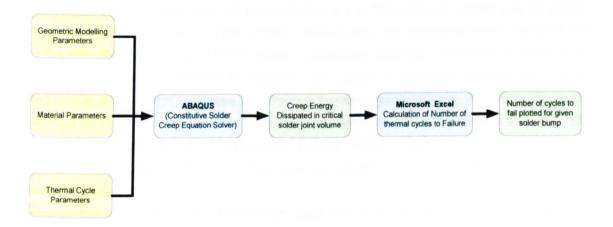

| Figure 4-1: Block diagram showing the simulation process                                                                                        | 71 |

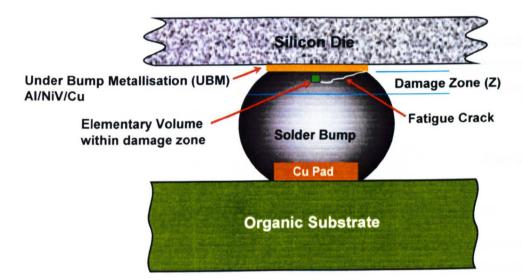

| Figure 4-2: Pictorial representation of flip chip interconnection                                                                               | 73 |

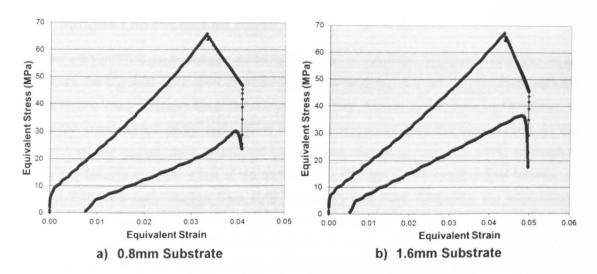

| Figure 4-3: Flip chip hysteresis curves calculated for organic substrates. (single<br>thermal cycle) (Popelar – Braden personal communications) | 75 |

| Figure 4-4: Simulation Thermal Profile                                                                                                          | 77 |

| Figure 4-5: Single side, single chip placement model                                                                                            | 79 |

| Figure 4-6: Single chips placed either side of substrate                                                                                        | 79 |

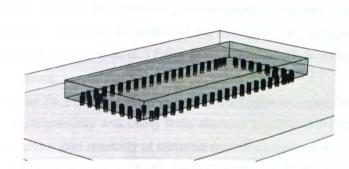

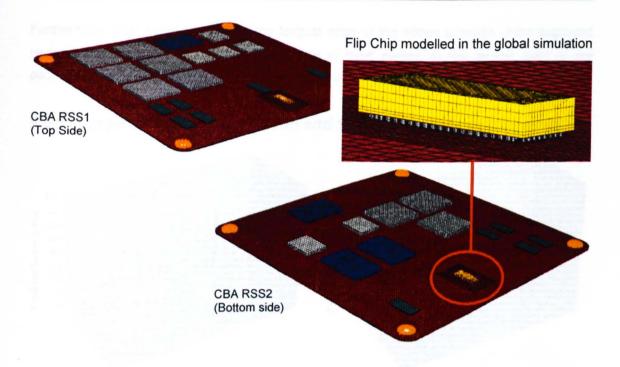

| Figure 4-7: Modelling of CBA using global approach.                                                                                             | 81 |

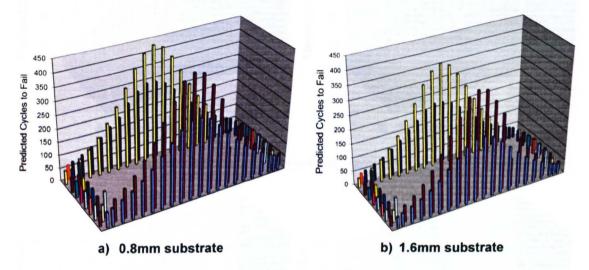

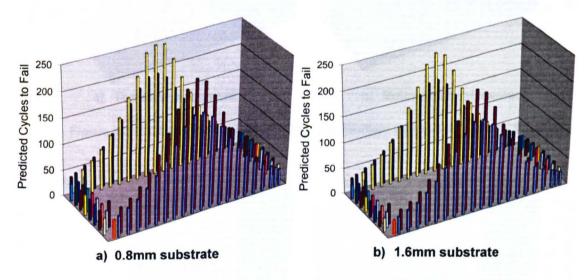

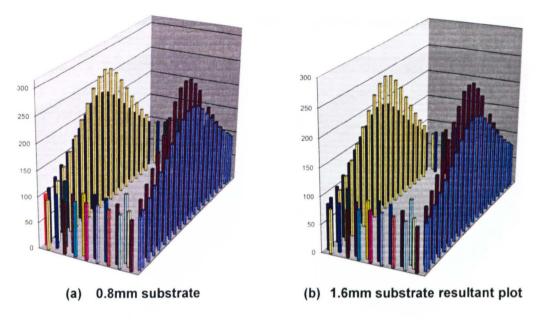

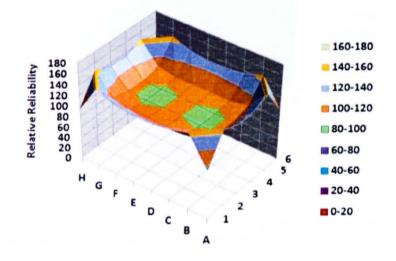

| Figure 4-8: Graphical results for 0.8mm and 1.6mm PCB, U23 single side placement                                                                | 82 |

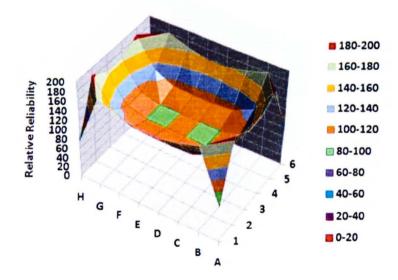

| Figure 4-9: Results for 0.8mm and 1.6mm PCB, mirrored, U31 topside placement                                                                    | 83 |

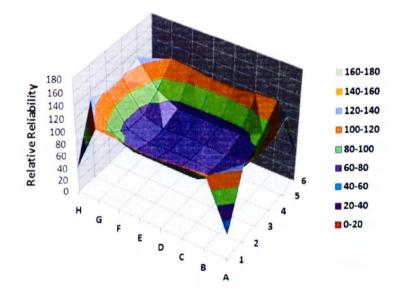

| Figure 4-10: Results for 0.8mm and 1.6mm PCB, mirrored, U34 bottom side placement                                                               | 83 |

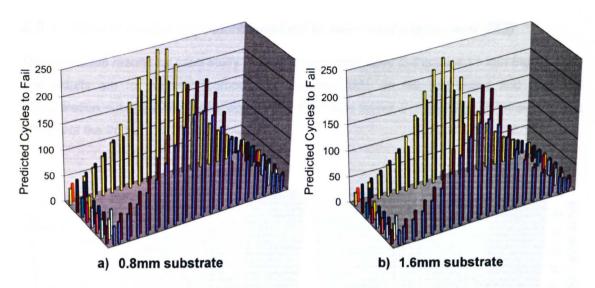

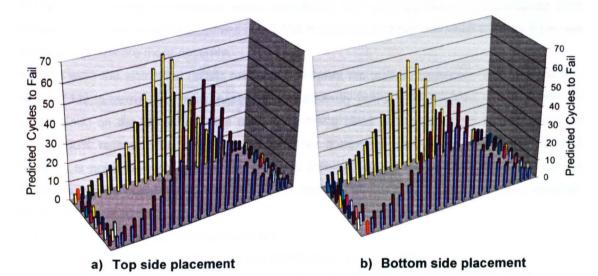

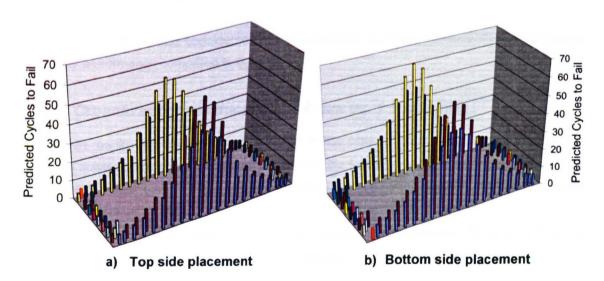

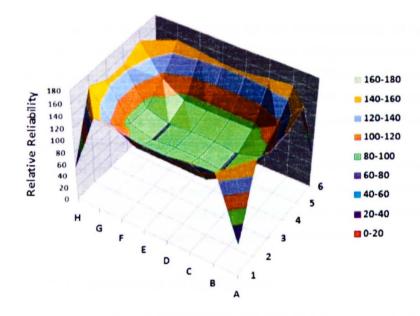

| Figure 4-11: Global Model Results, Top and Bottom placement, 0.8mm Substrate                                                                    | 84 |

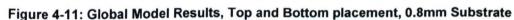

| Figure 4-12: Global Model Results, Top and Bottom placement, 1.6mm Substrate                                                                    | 84 |

| Figure 4-13: Graphical results comparing 0.8mm and 1.6mm PCB, single side placement                                                             | 86 |

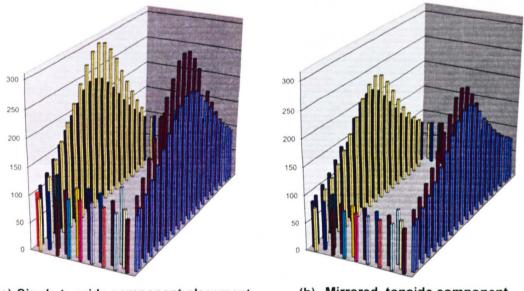

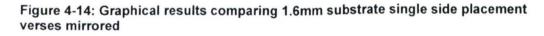

| Figure 4-14: Graphical results comparing 1.6mm substrate single side placement verses mirrored                                                  | 86 |

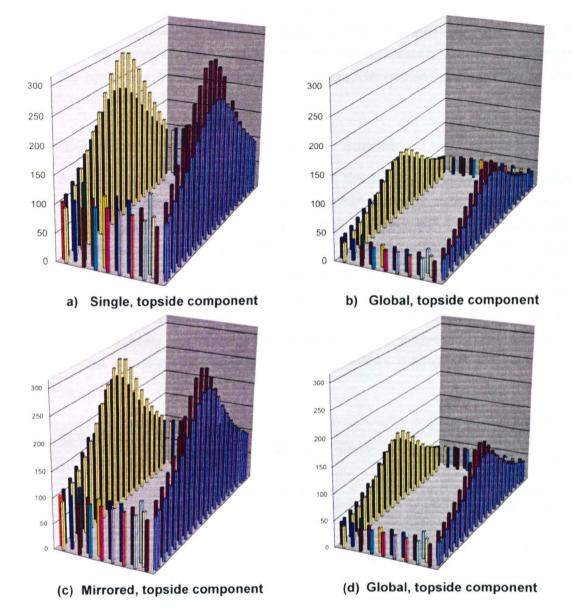

| Figure 4-15: Global relative reliability comparisons for 1.6mm substrate                                                                        | 87 |

| Figure 4-16: Simulation results for mBGA single side placement, board thickness<br>0.8mm                                                        | 89 |

| Figure 4-17: Simulation results for mBGA single side placement, board thickness<br>1.6mm                                                        | 89 |

| Figure 4-18: Simulation results for mBGA single side vs back to back placement,<br>board thickness 0.8mm (considering topside package only)     | 90 |

| Figure 4-19: Modelling results for mBGA single side vs back to back placement,<br>board thickness 1.6mm (considering topside package only)      | 90 |

| Figure 4-20: Modelling results for mBGA comparing single side placement 0.8mm<br>PCB to 1.6mm PCB thickness.                                    | 91 |

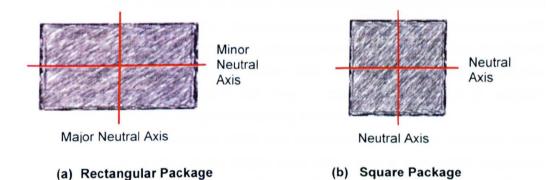

| Figure 4-21: Example of package neutral axes                                        | 92  |

|-------------------------------------------------------------------------------------|-----|

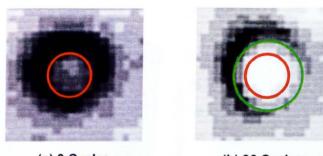

| Figure 5-1: CSAM image including radial gradient based region growing segmentation. | 95  |

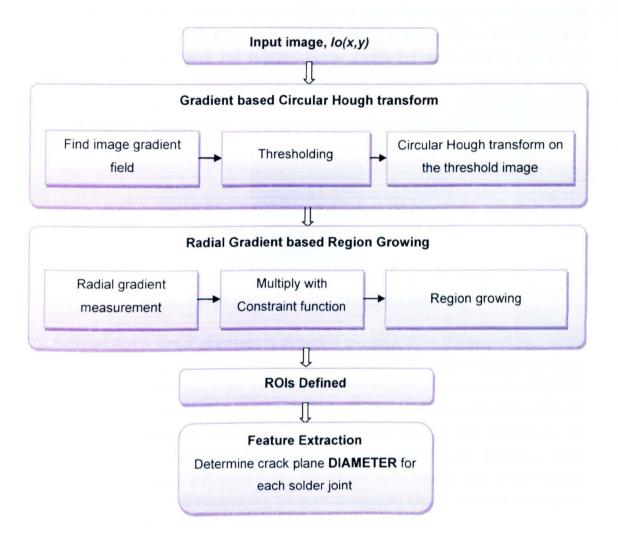

| Figure 5-2: Feature extraction flowchart (LJMU EUE research Group)                  | 96  |

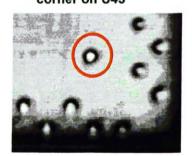

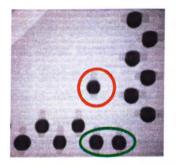

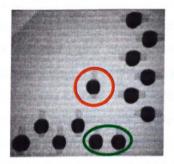

| Figure 5-3: Edge bump showing fractional black ring                                 | 97  |

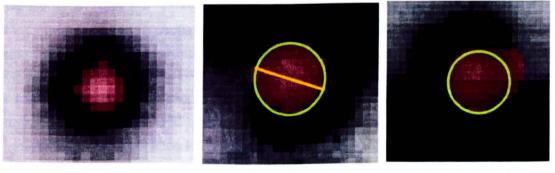

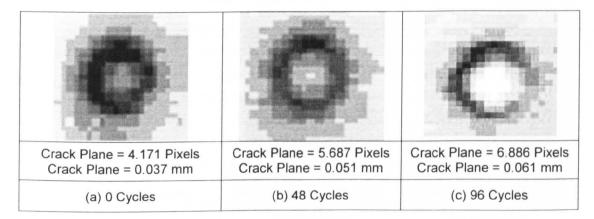

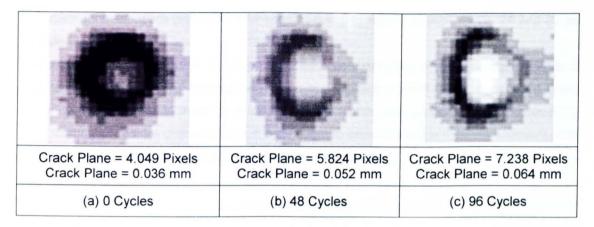

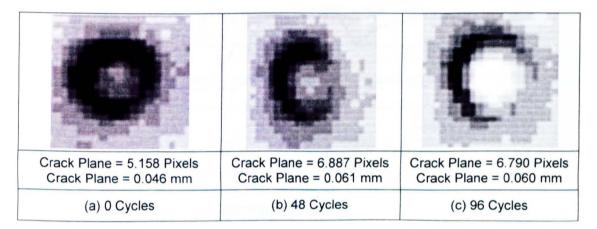

| Figure 5-4: Magnified images of crack plane measurement of individual bumps         | 97  |

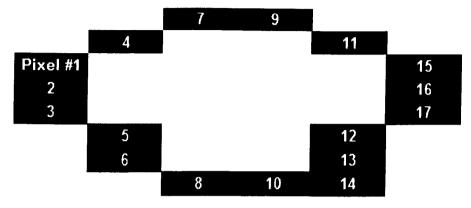

| Figure 5-5: Diagram of a pixelated region of interest (ROI)                         | 98  |

| Figure 5-6: U23 single side placement, bump 107, 0.8mm organic substrate            | 100 |

| Figure 5-7: U23 single side placement, bump 107, 1.6mm organic substrate            | 100 |

| Figure 5-8: U31 top side placement, bump 107, 0.8mm organic substrate               | 101 |

| Figure 5-9: U31 top side placement, bump 107, 1.6mm organic substrate               | 101 |

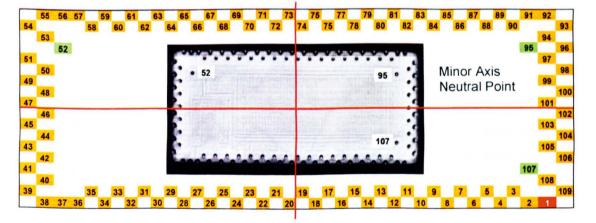

| Figure 5-10: Bump labelling and package neutral points                              | 101 |

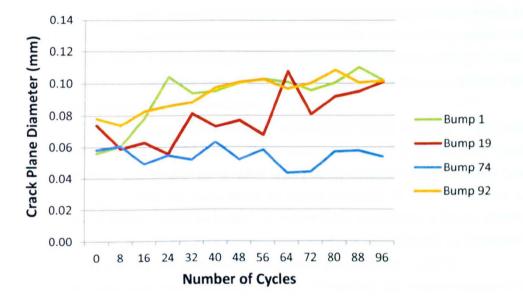

| Figure 5-11: Bump characteristics for U23 0.8mm substrate.                          | 102 |

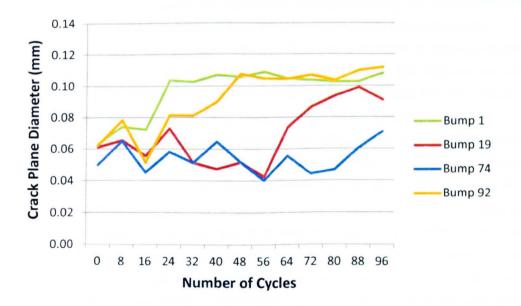

| Figure 5-12: Bump characteristics for U23 1.6mm substrate                           | 102 |

| Figure 5-13: U31, bump 107, 1.6mm organic substrate                                 | 104 |

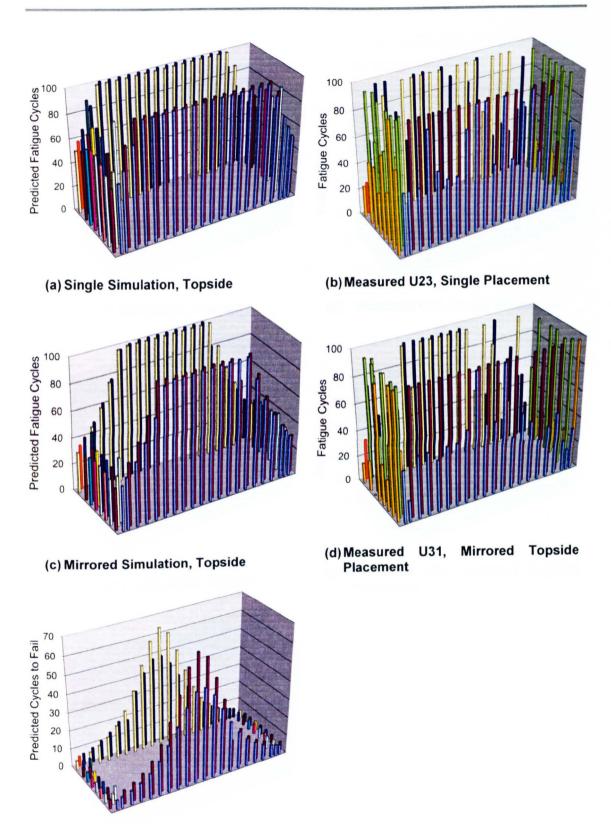

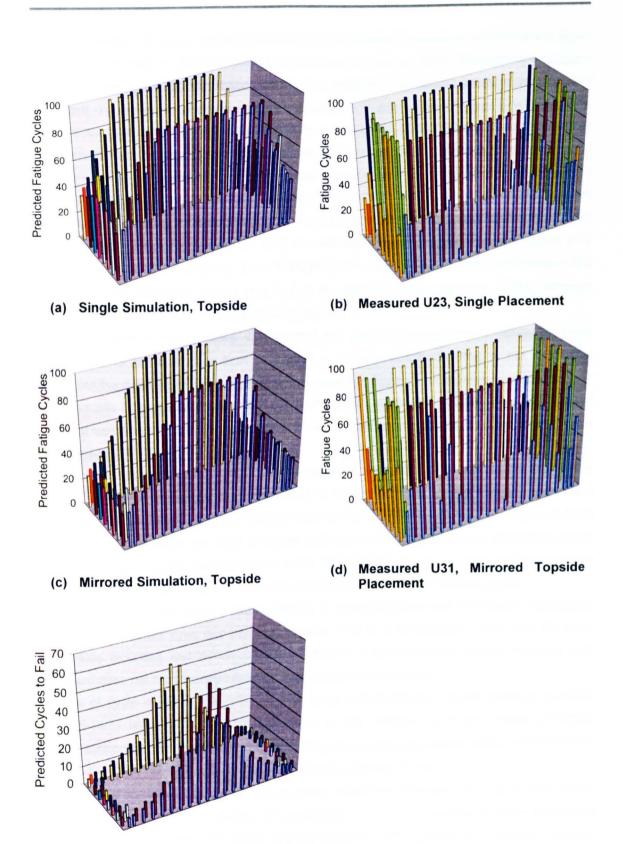

| Figure 5-14: Comparison simulation and measured results – 0.8mm substrate           | 105 |

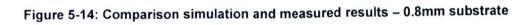

| Figure 5-15: Comparison simulation and measured Results - 1.6mm substrate           | 106 |

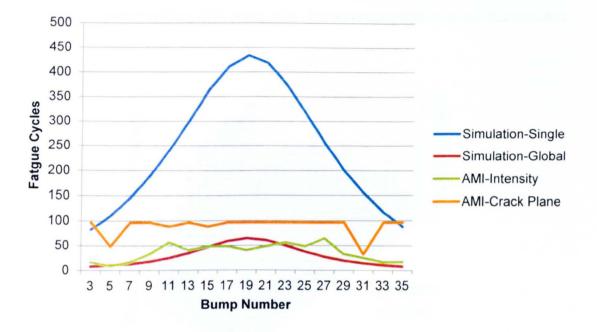

| Figure 5-16: U26 outer row, 0.8mm substrate bumps 1 to 38                           | 108 |

| Figure 5-17: U26 inner row, 0.8mm substrate bumps 3 to 35                           | 109 |

| Figure 5-18: 3D AMI intensity plot for flip chip U26 (Yang, et al., 2010c)          | 110 |

| Figure 5-19: Rotated 3D fatigue cycles plot for flip chip U26 – crack plane method  | 110 |

# List of Tables

| Table 3-1: Empirically derived ductility constants (Source GMW3172 Handbook)                                                                       | 39  |

|----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 3-2: Comparison of acceleration factor models                                                                                                | 41  |

| Table 3-3: Current and future state inspection requirements for next generationpackaging, updated from original table by Dias (Dias, et al., 2005) | 42  |

| Table 3-4: Acoustic impedance of common electronics packaging materials                                                                            | 46  |

| Table 3-5: Impact of impedance on return pulse polarity (Courtesy of Sonoscan Inc.)                                                                | 47  |

| Table 4-1: Flip chip modelling case studies                                                                                                        | 78  |

| Table 4-2: mBGA Modelling case studies                                                                                                             | 88  |

| Table A-1: Configuration of test boards                                                                                                            | 124 |

| Table B-1: Summary of principle materials properties of test CBA                                                                                   | 125 |

| Table B-2: Flip chip simulation data form                                                                                                          | 125 |

| Table B-3: Printed Circuit Board material characteristics                                                                                          | 126 |

| Table C-1: The AMI results of simulated A-scans by different AMI techniques                                                                        | 131 |

| Table E-1: Resolution Data for Common Transducers (Courtesy of Sonoscan Inc.)                                                                      | 133 |

# **Glossary of Terms**

| 2D                       | Two dimensional                                                                                                                          |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| 3D                       | Three dimensional                                                                                                                        |

| Ar                       | Acceleration Factor                                                                                                                      |

| AI                       | Aluminium                                                                                                                                |

| AMI                      | Acoustic Micro Imaging                                                                                                                   |

| β                        | Shape parameter term in Weibull distribution function                                                                                    |

| BD                       | Beam diameter                                                                                                                            |

| BGA                      | Ball Grid Array                                                                                                                          |

| BT                       | Bismaleimide-Triazine – A resin based laminate material used in the construction of the interposer within an area array packaged device. |

| СВА                      | Circuit Board Assembly                                                                                                                   |

| CD                       | Compact Disc                                                                                                                             |

| cdf                      | Cumulative distribution function                                                                                                         |

| CGA                      | Column Grid Array                                                                                                                        |

| CIP                      | Chip In Polymer technology                                                                                                               |

| C-SAM                    | C-mode Scanning Acoustic Microscopy                                                                                                      |

| CSP                      | Chip Scale Package                                                                                                                       |

| CTE                      | Coefficient of Thermal Expansion                                                                                                         |

| DIP                      | Dual Inline Package                                                                                                                      |

| DNP                      | Distance from neutral point                                                                                                              |

| DVD                      | Digital Versatile Disc                                                                                                                   |

| η                        | Scale parameter in Weibull distribution where the bulk of the distribution lies                                                          |

| ε                        | Strain                                                                                                                                   |

| $\mathcal{E}_{o}$        | Initial strain                                                                                                                           |

| $\dot{arepsilon}_i$      | Initial creep strain rate                                                                                                                |

| έ <sub>m</sub>           | Minimum creep strain rate                                                                                                                |

| $\dot{arepsilon}_{ m f}$ | Material ductility coefficient                                                                                                           |

| $\Delta \varepsilon_{P}$ | Plastic strain range                                                                                                                     |

| $\Delta \varepsilon_c$   | Elastic strain range                                                                                                                     |

| EUE                      | Electronic and Ultrasonic Engineering (Research Group at LJMU)                                                                           |

| EDS                      | Energy Dispersive Spectroscopy                                                                                                           |

| EEPROM                   | Electrically Erasable Programmable Read Only Memory                                                                                      |

| ESTC                     | Electronics Systems integration Technology Conference                                                                                    |

| ENIG              | Electroless Nickel Immersion Gold                                                                                                        |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| <i>F(t)</i>       | Cumulative failure distribution function                                                                                                 |

| FAMI              | Frequency domain Acoustic Micro Imaging                                                                                                  |

| fcBGA             | Flip chip Ball Grid Array                                                                                                                |

| FEA               | Finite Element Analysis                                                                                                                  |

| FEM               | Finite Element Modelling                                                                                                                 |

| FFT               | Fast Fourier Transform                                                                                                                   |

| FiPoP             | Fan-In PoP                                                                                                                               |

| FR-4              | "FR" stands for Flame Retardant and "4" means woven glass reinforced epoxy resin. The most commonly used printed circuit board material. |

| FR-5              | High temperature versions of FR-4 epoxy laminate with glass fibre reinforcement.                                                         |

| γ                 | Defines the location of the Weibull distribution in time                                                                                 |

| GERI              | General Engineering Research Council                                                                                                     |

| GBS               | Grain Boundary Sliding                                                                                                                   |

| HASL              | Hot Air Solder Levelling, involves coating the conductors with molten solder then blowing off the excess with a hot air knife            |

| Hz                | Hertz, the unit of cyclic frequency in cycles per second                                                                                 |

| IBM               | International Business Machines                                                                                                          |

| IC                | Integrated Circuit                                                                                                                       |

| IET               | Institute of Engineering and Technology, formally known as IEE                                                                           |

| IEEE              | Institute of Electrical and Electronics Engineers                                                                                        |

| I/O               | Input/Output                                                                                                                             |

| INEMI             | International Electronics Manufacturing Initiative                                                                                       |

| IMC               | Intermetallic Compound                                                                                                                   |

| ITRS              | International Technology Roadmap for Semiconductors                                                                                      |

| k                 | Boltzmann's constant - 1.3806503 × 10 <sup>-23</sup> Joules per Kelvin                                                                   |

| $^{1}/_{\lambda}$ | Reliability – Average operation time per single failure                                                                                  |

| λ(t)              | Instantaneous failure rate                                                                                                               |

| LJMU              | Liverpool John Moores University                                                                                                         |

| m                 | Fatigue ductility exponent empirically derived and used in Coffin Manson acceleration equation.                                          |

| Matlab™           | Mathematical Computer Software Analysis Package from Mathworks                                                                           |

| MC                | Material Creep                                                                                                                           |

| MEMS              | Micro-electromechanical Systems                                                                                                          |

| Microns           | Micrometres or 10 <sup>-6</sup> Metres                                                                                                   |

| Microvias         | Terminology describing through holes or circuit board layer interconnects of <150µm diameter.                                            |

| MHz            | One Million Hertz                                                                                                      |

|----------------|------------------------------------------------------------------------------------------------------------------------|

| mils           | A US distance unit equal to 0.001 inch. One mil is exactly 25.4 microns, just as one inch is exactly 25.4 millimetres. |

| MPa            | Mega Pascal                                                                                                            |

| N <sub>f</sub> | Number of stress cycle reversals or Cycles to fail in the field                                                        |

| N <sub>t</sub> | Cycles to fail in the test environment or cycles to first failure                                                      |

| NDT            | Non-Destructive Testing                                                                                                |

| NDE            | Non Destructive Evaluation                                                                                             |

| P <sub>r</sub> | Probability                                                                                                            |

| Pb             | Lead                                                                                                                   |

| PBGA           | Plastic Ball Grid Array                                                                                                |

| PCB            | Printed Circuit Board                                                                                                  |

| PGA            | Pin Grid Array – Precursor to BGA and CSP                                                                              |

| PiP            | Package in Package                                                                                                     |

| PoP            | Package on Package                                                                                                     |

| ppm            | Parts Per Million                                                                                                      |

| Pre-Preg       | Epoxy impregnated glass fibre matting                                                                                  |

| psi            | Pounds per square Inch                                                                                                 |

| Q              | Relative activation energy for creep                                                                                   |

| QFP            | Quad Flat Pack                                                                                                         |

| ρ              | Density of material                                                                                                    |

| RGI            | Radial Gradient Index                                                                                                  |

| R              | Acoustic energy reflection coefficient                                                                                 |

| RAM            | Random Access Memory                                                                                                   |

| ROI            | Region of Interest                                                                                                     |

| RSS1           | Reflow Solder Side 1                                                                                                   |

| RSS2           | Reflow Solder Side 2                                                                                                   |

| 7              | Stress or applied load stress                                                                                          |

| SAC            | Lead free solder comprising tin(Sn), silver(Ag) and copper(Cu).                                                        |

| SAC305         | Lead free solder comprising of 96.5% tin(Sn), 3% silver(Ag) and 0.5% copper(Cu).                                       |

| SAM            | Scanning Acoustic Microscopy                                                                                           |

| SCSP           | Stacked Chip Scale Packages                                                                                            |

| SEM            | Scanning Electron Microscope                                                                                           |

| SiP            | System in Package                                                                                                      |

| SLAM           | Scanning Laser Acoustic Microscope                                                                                     |

| Sn             | Tin                                                                                                                    |

| SoC                | System-on-Chip                                                                                                                              |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Т                  | Temperature                                                                                                                                 |

| T                  | Relative acoustic energy transmission.                                                                                                      |

| t <sub>r</sub>     | Time to fail in field                                                                                                                       |

| Tg                 | Glass transition temperature of a material                                                                                                  |

| t <sub>r</sub>     | Time to rupture or failure in the Monkman-Grant equation                                                                                    |

| t,                 | Time to fail in test                                                                                                                        |

| $\Delta T_{Field}$ | Thermal range in field environment                                                                                                          |

| $\Delta T_{Test}$  | Thermal range in test environment                                                                                                           |

| TAMI               | Time domain Acoustic Micro Imaging                                                                                                          |

| TSOP               | Thin small-outline package                                                                                                                  |

| TSV                | Through Silicon Via – Interconnection technology                                                                                            |

| UBM                | Under Bump Metallisation                                                                                                                    |

| V                  | Velocity of sound in metres per second                                                                                                      |

| Via                | Small plated through hole in a printed circuit board used solely to interconnect tracks on different layers of the circuit board.           |

| W                  | Inelastic strain energy density in MPa or psi                                                                                               |

| W <sub>CR</sub>    | Creep strain energy dissipated per thermal cycle in mJ/mm <sup>3</sup> .<br>Note: 1mJ/mm <sup>3</sup> = 1MPa. Can also be expressed in psi. |

| WLCSP              | Wafer Level Chip Scale Packaging                                                                                                            |

| Z                  | Acoustic Impedance                                                                                                                          |

# **Chapter 1**

#### Introduction

This research, supported by Delphi Electronics Group, Liverpool, investigates solder joint reliability of area array parts using Non Destructive Evaluation methods. The methods developed aim to enable through life condition monitoring of modern manufactured electronic systems. A further extension of the work is to examine the influence on reliability of component layout or placement on a printed circuit board.

Although this research has been focused on high reliability automotive applications, the knowledge gained can be used by many industry sectors using electronics in their products or which have complex interdependent material structures e.g. composite materials.

#### 1.1 Background to Project

Electronics is used extensively across many different market sectors to-day to deliver advanced technology features and functionality expected by consumers.

For many high volume markets such as automotive, the increased level of functionality must be delivered at the lowest possible cost and work in extremely harsh environments whilst achieving the highest levels of reliability. In such automotive applications reliability expectations of 98.5% is not unusual.

The use of electronics in modern vehicles is extensive and continues to increase. In 2002, it was estimated that some 25% of a vehicle's manufacturing cost was due to electronic systems (Braden, 2000). By 2010 Donovan (Donovan, 2007) predicted this to increase to account for some 40% of a vehicle's overall cost base. To-day, electric and hybrid motor vehicles push this figure substantially higher.

As the electronic content in a motor vehicle continues to increase, so also does the complexity of the vehicle embedded systems. Likewise, the reliability expectation of both the customer and vehicle manufacturer has also increased. In the first twelve months of a vehicle's life electrical problems account for up to 70% of customer complaints and warranty problems (MIRA (Motor Industry Research Association)). This is a generalised figure that includes all electrical and electronic equipment. No figures were presented for the proportion of failures within the quoted percentage that were attributed to either Ball Grid Array (BGA) or Chip Scale Packaged (CSP) devices. To put this in context, within Delphi Corporation as a whole it is estimated that the daily production of solder joints is approximately 1 billion. This represents some 1 billion or more failure site opportunities at the component to circuit board assembly interface.

Ever growing consumer expectations are driving manufacturers of electronic products to increased levels of functionality and miniaturisation in their products. This in turn has

accelerated the use of densely packaged electronic components in new designs (Braden, 2000). Consequently increased use is being made of Area Array packaged devices such as Ball Grid Array and Chip Scale Packaged components.

Such packaging technologies offer input/output connection pitches in the range 1.50mm to 0.5mm (BGA) and 1.0mm to 0.5mm (CSP). The benefit of using such technologies is not just seen in terms of bottom line product cost and circuit board real estate savings; it can impact on both product yield and quality. It also has the advantage that it may be processed using existing surface mount manufacturing techniques (Di Giacomo, 1997) (Fielstad, et al., 2003) (Viswanadham, et al., 1998).

Inside the semiconductor industry, Moore's law is driving significant changes in packaging technologies of electronic devices. Increasing transistor count relates directly to an increase in the number of interconnections emerging from the package (Perkins, 2007). As a result, packaging-interconnect density has experienced a six fold increase over the last five years. Subsequently designing 2D or 3D area array packaging is the future trend of electronics, leading to the development of further variations of BGA and CSP packaging; System-on-Chip (SoC), System in Package (SiP), Package on Package (PoP), Stacked Chip Scale Packages (SCSP) (Tyndall National Institute, 2006) and Chip In Polymer technology (CIP) (Ostmann, et al.).

Given that many complex silicon designs are realised using SoC or PoP, a point has now been reached where the decision to integrate on silicon is no longer an easy one (Edwards, 2010). In order to readily adapt to market trends and cost, it is considered beneficial to use multiple chips in the realisation of a design by deploying scalable 2D or 3D area array packaging concepts as illustrated in Figure 1-1.

#### Figure 1-1: Example of Package-on-Package (PoP) (Statschippac)

Moreover, this is driving development of increasingly detailed non-destructive failure analysis tools in order to understand the reliability of micro and nanometric components subjected to

environmental testing (Krastev, 2007) (Dias, et al., 2005). This is particularly true of the automotive, avionics and defence industries due to reliability concerns. Automotive electronics systems operate in harsh environments, particularly those located under the bonnet or on the engine, where thermal cycling, vibration and high levels of moisture are present.

The package to printed circuit board (PCB) solder joint interconnections are extremely important since it represents, in many cases, the weakest link in terms of product reliability. Solder joints however do not solely perform the job of providing an electrical connection; they mechanically affix the component to the PCB, provide thermal conduits for heat dissipation into the circuit board and help match expansion differences between printed circuit boards and components.

The continued 'up integration' of electronics functions into single silicon building blocks offers significant advantages in automotive applications, allowing complex products to be produced at low cost whilst achieving high levels of reliability. Unlike the 'white goods' market, which performs primarily regulatory and compliance testing, automotive applications additionally require extensive reliability life tests to be performed, thus assuring design reliability, safety and robustness. This subsequent testing and product validation adds considerable cost to the finished product. The design of these tests is based on a 'physics of failure' approach in which the application of thermal or mechanical energy is used to initiate a defect and then propagate the defect until a failure occurs in the product or an individual component.

For electronics applications solder joint failures are the most commonly experienced and of these the majority can be can be attributed to three main factors:

#### 1) Fracture - Tensile rupture/fracture through mechanical overloading.

In this type of failure, the shear strength of the solder has been exceeded either as a result of design, for example fixing a warped PCB into an enclosure, or as a result of an accident or abuse such as dropping a product or knocking a component during the manufacturing process.

#### 2) Creep - Long lasting permanent loading

The solder joint or joints are subjected to continuous stress loading which results in degradation of the joint over time. Although such failures are more prominent through exposure to high temperature, solder joint cracks can occur at room temperature. Stress figures are of the order of <1N/mm<sup>2</sup> at 20°C and preferably  $\leq 0.1$ N/mm<sup>2</sup>.

#### 3) Low Cyclic Fatigue – Cyclic loading

Cyclic fatigue induced failures are the result of the deformation of solder joints or component materials. This in turn may be due to a combination of coefficient of thermal expansion (CTE) mismatch differences in materials and cycling between temperature extremes. Deformation in solder joints is typically larger than with other material systems used in the manufacture of

electronics products. Solder joint cracking forms in all solder joints that are subjected to low cycle fatigue stress over long periods of time.

For large BGA, CSP or SiP packaged components, thermal cycling in conjunction with selfheating introduces thermal gradients across the component. Thermal gradients interacting with the CTE of various materials used in the fabrication of a component produces stress and strain. Accumulated stress and strain over time giving rise to fatigue failures.

Many physics of failure models exist that describe how the operating environment induces a given failure mode within the electronic devices and their packaging. Such models are not only used to predict operating performance and theoretical life expectancy but they are also used by reliability engineers to determine test durations and sample sizes. This is particularly important in the automotive industry. Products typically have an expected life of 600,000km or 15 years in the case of light duty applications such as cars and vans.

The models in many cases are verified through laboratory testing of Circuit Board Assemblies (CBA) which are not fully representative of the characteristics and dynamics of the actual boards used in production.

In order to detect solder joint degradation or joint failure over a period of time, samples are either removed from the test at various points during the test cycle for micro-sectioning or are monitored for signs of deterioration throughout the test using electrical resistance measurement. Destruction of the test sample is inherent with micro-sectioning. Thus samples removed from an environmental test and subsequently micro-sectioned cannot be returned for further exposure. There are further unwanted issues with this technique. Firstly, it is assumed that all generated defects behave consistently and occur across the entire sample batch in the same manner. Secondly, by destroying the sample, the technique does not allow for a detailed investigation of solder crack initiation or how the environmental exposure affects crack propagation. Finally, any defects of interest and solder joint cracks irrespective of size can easily be missed due to the 2D nature of micro-sectioning and is very reliant on selecting the correct sectioning plane.

Such detailed failure site information is core to understanding component/product reliability. Clearly it is difficult in a non-destructive manner to visually inspect hidden solder joints on area array type packages. As device features and packaging get ever smaller, traditional non-destructive failure analysis tools such as X-ray and Acoustic Microscopy are becoming increasingly less effective. Furthermore, 3D structures that include stacked die packages and SiP, with associated heat sinks and thermal dissipation solutions present further challenges for non-destructive evaluation techniques.

#### 1.3 Motivation and Contribution to Knowledge

Several non-destructive testing (NDT) techniques have been proposed to investigate, detect and locate defects in microelectronic devices, their associated packaging and their interconnection to a substrate, which for this research is an organic printed circuit board (PCB). These include optical inspection using microscopes, X-ray microscopy (Moore, et al., 2002), acoustic micro imaging (AMI)/scanning acoustic microscopy (SAM) (Pahl, et al., 2004), electronic speckle pattern interferometry (Lee, et al., 2004), scanning electron microscopy (SEM) and laser ultrasound coupled to interferometry (Liu, et al., 2004). No single method has been able to satisfy present NDT requirements, so this work is motivated at advancing techniques to measure and extend product reliability knowledge for current and future products. The work presented in this thesis follows a multidisciplinary approach to gain better understanding of the interconnect behaviour of area array packaged devices populated on organic substrates.

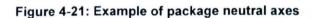

Comparison is made between Finite Element Analysis and AMI techniques as applied to the measurement of the reliability performance of solder joints for the test cases studied. Test cases were carefully designed to investigate the influence on joint reliability of floor plan layout and substrate thickness. AMI has not previously been used to perform through life monitoring and study the effects of thermal cycling on crack growth through a solder joint. In the proposed method AMI images taken at regular intervals throughout the environmental exposure are post processed to measure the diameter of a 2D plane (termed crack plane) within a damage region of the solder joint occurring at the bump to silicon interface. Subsequently testing the hypothesis that crack plane diameter is related to fatigue cycle exposure and joint degradation can be monitored for the first time, using AMI to assess lifetime performance.

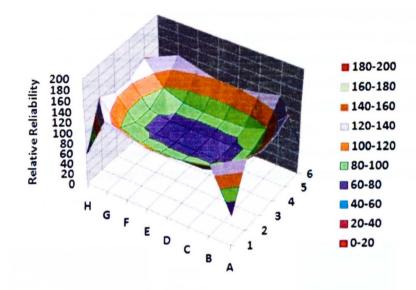

The crack plane diameter values for each bump, recorded at regular intervals throughout the testing were used to generate a 3D graphical representation of the reliability of the package interconnections. Interconnection reliability graphs obtained from measurement and simulation results were subsequently used to study the influence of floor plan layout and substrate thickness on joint reliability. Component layout influence on solder joint reliability has been studied by Ye (Ye, et al., 2007) and Primavera (Primavera, et al., 2004) for BGA packaged components. In their work no through life monitoring was deployed and destructive testing techniques were used to evaluate joint degradation only at the end of the environmental test exposure. This subsequently gave limited information regarding healthy and failed joints, with no intermediate data available for monitoring through life performance.

As joint geometries and packaging dimensions reduce it is suggested that the influence of floor plan layout, PCB constraint points and substrate thickness will significantly influence solder joint reliability (Braden, et al., 2010). The new metrology method proposed in this work will be crucial to the study of this emerging area of interest and may ultimately lead to better physics of failure models and prognostics in electronics systems.

#### 1.4 Thesis Outline

The thesis is divided into six chapters and five appendices.

**Chapter 1** outlines the background to the research, identifying the key problems encountered along with motivation and contribution to knowledge and a thesis overview.

**Chapter 2** presents a detailed review of area array packaging technology to develop an understanding of the packaging roadmap and the need to develop new improved metrology to inspect hidden joints. The chapter also develops understanding of package interconnection techniques, structures, materials deployed in their fabrication and the likely interconnect reliability problems which will be encountered. This underpinning information is required in order to assess the difficulties of deploying Non Destructive Evaluation methods to the inspection of solder joints, and as an aid to the specifications required to develop and run Finite Element Analysis (FEA) simulations.

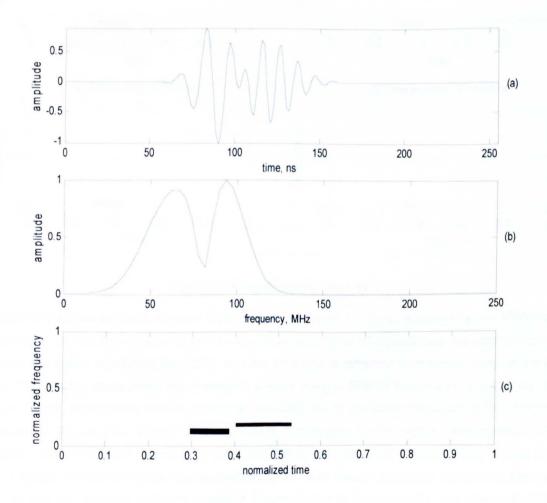

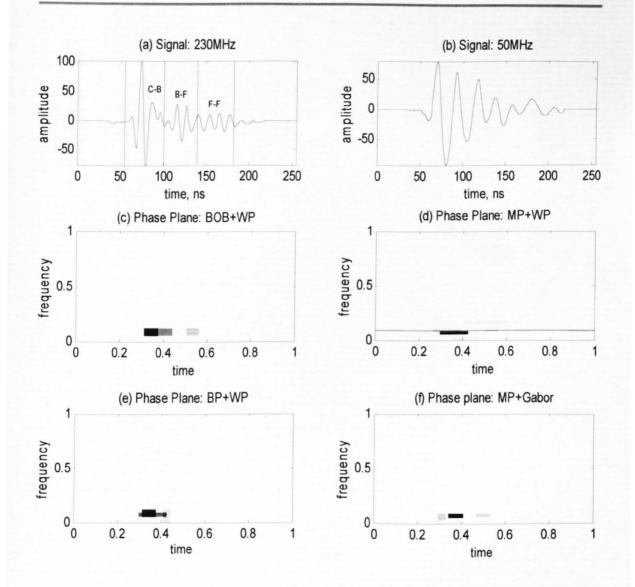

**Chapter 3** studies the application of AMI and X-ray NDT techniques to the through life assessment of solder joints. The two contrasting methods are compared for their ability to resolve component features. Reliability and experimental testing setups are compared, including a discussion of common acceleration factors and how they are derived. Advanced signal processing and novel acoustic time-frequency domain imaging techniques were developed to improve the resolution of conventional AMI.

**Chapter 4** designs the modelling methodology used in the evaluation of flip chip solder joint reliability performance. Specific modelling scenarios were developed that would investigate the influence of substrate thickness and component floor plan layout on joint reliability.

**Chapter 5** develops an innovative through life measurement method for post processing the AMI image in order to non-destructively obtain the bump crack plane diameter and hence produce a thermal cycle's exposure estimate.

Chapter 6 Presents the conclusions from the work and suggestions for future studies are identified.

# Chapter 2

#### Area Array Packaging Technologies

#### 2.1 Introduction

It is projected that worldwide, advanced electronic packaging will account for revenue streams exceeding \$42 billion by the end of 2012. The fastest growth being experienced in Chip Scale Packaging with the United Kingdom being poised to emerge as the second largest European market by 2012, with revenues projected to exceed \$1.52 billion (Sadanaga, 2009).

In order to be world class in the field of microelectronics and packaging requires a detailed understanding of the reliability of emerging packaging technologies and the development of metrology and forensic inspection techniques in order to examine the interconnection and packaging performance.

#### 2.2 A Brief Review of Packaging

The term packaging describes the process of mounting, interconnecting and encapsulation of microelectronic parts which increasingly includes combinations of passive parts in a compact and efficient manner.

It is this ability to package complex electronic functionality into a compact footprint which enables many modern day size constrained products to be realised and which provides increased available circuit board real estate.

Often packaging is considered as the low technology part of the semiconductor device manufacturing process. However, within packaging lies a multitude of materials technology and engineering problems (Grovenor, 1989) which can limit the overall performance of the device in its application. Electronics packaging provides four main functions:-

- 1. Provision of electrical interconnection between semiconductor die and/or passive components within the packaging and the outside world.

- 2. Provides thermal management for the silicon through power distribution and heat dissipation from the active regions of the silicon.

- 3. Provides protection of the silicon and their interconnections from harsh chemical and moisture laden environments.

- Provides mechanical protection of the silicon and interconnections as well as providing a way of physically being able to handle the device during automated manufacturing processes.

Modern area array packaging such as Ball Grid Array (BGA) (introduced primarily by Motorola in the late 1980's) and Chip Scale Packaging (CSP) offers high packing density, better heat

dissipation and higher I/O count at lower cost and better reliability. BGAs have small conductive solder balls or columns that are soldered directly onto the surface of printed circuit boards as illustrated in Figure 2-1.

#### Figure 2-1: Cross section of Plastic Ball Grid Array (PBGA) (ETAC data sheet)

Unsurprisingly this makes it difficult to inspect the connections between the package and the PCB because the solder balls are located underneath the package. Consequently, special microscopes and micro-focus X-ray systems have been developed for joint inspection but are expensive and not useful as a 100% inspection tool. Therefore ensuring quality of the assembly process for products using BGA technology must be precise, having the minimum of tolerance errors (Denning, 2001).

Area array packaging covers a wide variety of packaging styles, types and configurations, however in all cases the principle interconnection techniques between the device package and the printed circuit board remain the same; each variation addressing a particular technology or packaging need.

The basic construction of an area array device is illustrated in Figure 2-1. The base material of the package is formed from substrates such as alumina (ceramic material), glass reinforced epoxy based laminate such as FR-4 or FR-5 or polyimide flex-film. The substrate which provides a mounting structure for die attachment also functions as a compliant interposer between the silicon die in the package and the printed circuit board onto which the package is soldered.

The electrical connection between the interposer and silicon is made either through wire bonding or reflow of high temperature solder balls attached to 'flip chips'. To protect the interconnections and silicon from the harsh environments to which it will be exposed the entire configuration is encapsulated or over-moulded with plastic.

#### 2.3 Next Generation Packaging

The continual trend to increase functionality and pursuit of extreme miniaturisation within a single integrated circuit package, combined with dramatic increases in interconnection density is driving the development of next generation packaging.