#### **Aalborg Universitet**

#### Performance Analysis of Video PHY Controller Using Unidirection and Bi-directional IO Standard via 7 Series FPGA

Das, Bhagwan; Abdullah, M F L; Hussain, Dil muhammed Akbar; Pandey, Nisha; Verma, Gaurav

Published in:

Gyancity Journal of Electronics & Computer Science

DOI (link to publication from Publisher): 10.21058/gjecs.2017.21003

Creative Commons License CC BY 4.0

Publication date: 2017

Document Version Publisher's PDF, also known as Version of record

Link to publication from Aalborg University

Citation for published version (APA):

Das, B., Abdullah, M. F. L., Hussain, D. M. A., Pandey, N., & Verma, G. (2017). Performance Analysis of Video PHY Controller Using Unidirection and Bi-directional IO Standard via 7 Series FPGA. *Gyancity Journal of* Electronics & Computer Science, 2(1), 22 - 30. https://doi.org/10.21058/gjecs.2017.21003

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- ? Users may download and print one copy of any publication from the public portal for the purpose of private study or research. ? You may not further distribute the material or use it for any profit-making activity or commercial gain ? You may freely distribute the URL identifying the publication in the public portal ?

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

## Performance Analysis of Video PHY Controller Using Unidirection and Bidirectional IO Standard via 7 Series FPGA

# Bhagwan Das<sup>1,a</sup>, M.F.L Abdullah<sup>1,b</sup>, DMA Hussain<sup>2,c</sup>, Nisha Pandey<sup>3,d</sup>, Gaurav Verma<sup>3,d</sup>

<sup>1</sup>Faculty of Electrical & Electronic Engineering, Universiti Tun Hussein Onn Malaysia (UTHM), Malaysia

> <sup>2</sup>Department of Energy Technology, Aalborg University, Esbjerg, Denmark <sup>3</sup>Gyancity Research Lab, India.

<sup>a</sup>engr.bhagwandas@hotmail.com, <sup>b</sup>faiz@uthm.edu.my; <sup>c</sup>akh@et.aau.dk, <sup>d</sup>gyancity@gyancity.com

Abstract—The Video PHY controller offers an interface between transmitters/receivers and video ports. These video ports are categorized in HDMI or Displayport. HDMI Video PHY controller are mostly used for their high speed operation for high resolution graphics. However, the execution of high resolution graphics consumes more power, this creates a need of designing the low power design for Video PHY controller. In this paper, the performance of Video PHY controller is analyzed by comparing the power consumption of unidirectional and bi-directional IO Standard over 7 series FPGA. It is determined that total on-chip power is reduced for unidirectional IO Standard based Video PHY controller compared to bidirectional IO Standard based Video PHY controller. The most significant achievement of this work is that it is concluded that unidirectional IO Standard based Video PHY controller consume least standby power compared to bidirectional IO Standard based Video PHY controller. It is defined that for 6 GHz operated frequency Video PHY controller, the 32% total on-chip power is reduced using unidirectional IO Standard based Video PHY controller is less compared to bidirectional IO Standard based Video PHY controller. It is also demonstrated that 97% device static power i.e. standby mode power consumption is reduced using unidirectional IO Standard based Video PHY controller is less compared to bidirectional IO Standard based Video PHY controller. The proposed design will be to provide high resolution video processing at low standby power consumption using unidirectional IO Standard based Video PHY controller is less compared to bidirectional IO Standard based Video PHY controller.

Keywords- Power Consumption, Static Power Consumption, Standby Power Consumption, Unidirectional and Bidirectional IO Standard, Video PHY Controller, 7 Series Field Programing Gate Array.

#### I. Introduction

The Video PHY controller is used to organize, the PHY layer with video controllers. The Video PHY controller offers the processing of high resolution video data. It is reported that the processing of high resolution video consumes high power for operating frequencies of 2.0 GHz to 6.25 GHz [1-2]. There are several techniques are utilized in order to control or reduce the power consumption of different devices such as; optical transmitter [3], energy efficient laser driver [4], Ethernet [5], filters [6]. These techniques include; these techniques include; clock gating, voltage scaling [7], variable frequency and etc. However, each techniques has its own advantages and disadvantages. It has been demonstrated in [8-9] that for different variation in suitable IO Standard the power consumption of device can be reduced depend upon the core voltage of Field Programming Gate Array (FPGA), operating voltage of the device and IO Standard voltage selected for particular device. There are different types of IO Standard. The unidirectional and bi-directional IO Standard are categorized for their signal termination. The unidirectional signaling defines IO pins are assigned for signal transferring via input to output or vice versa. In the IO Standard description, the DCI versions of class-I

SSTL and HSTL I/O standards only have internal split-termination resistors present on inputs (not outputs). The DCI versions of class-II SSTL and HSTL I/O standards always have internal split-termination resistors present on input, outputs, or bidirectional pins. There are different IO Standard are available in 7 series FPGA, such as; unidirectional IO Standard, bidirectional IO Standard and also some of the both unidirectional and bi-directional IO Standard [11]. In this paper, the power analysis for low power consumption is demonstrated for Video PHY controller for high frequency using unidirectional and bi-directional IO Standard via 7 series Field Programming Gate Array. It is important to note that unidirectional and bi-directional IO Standard are of many types, the selection of particular IO Standard depends upon the specific circuit and the core voltage of FPGA.

#### II. METHODOLOGY

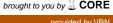

The power analysis for Video PHY controller at high frequency using unidirectional and bidirectional IO Standard is designed using different design steps as demonstrated in Figure 1. It is illustrated in Figure 1 that in first design step, Video PHY controller is designed using Vivado design suite via vhdl coding by defining the different parameters and configuration of transmitter and receiver. In the second design step, the vhdl based Video PHY controller is designed using unidirectional and bi-directional IO Standard. The IO Standard are selected based upon the core voltage of FPGA, and operating voltage of Video PHY controller. In the third design step, the vhdl Video PHY controller using unidirectional and bi-directional IO Standard is tested for different high frequencies in order to analyze the performance of the designed low power Video PHY controller.

Figure 1. Design steps for performance analysis of Video PHY controller using unidirectional and bi-directional IO Standard

#### A. Design Step 1: vhdl based HDMI based Video PHY controller

The HDMI based Video PHY controller is designed in Xilinx Vivado Suite using vhdl. The elaborated/schematic design of Video PHY controller is shown in Figure 2.

Figure 2. Schematic design of Video PHY controller

The Video PHY controller in Figure 2 is designed using different protocols parameters as illustrated in Table 1.

| NAME OF<br>PARAMETER   | PARAMETER<br>CONFIGURATION |  |

|------------------------|----------------------------|--|

| Tx Protocol            | DP                         |  |

| Tx Max GT line rate    | 5.4 Gb/s                   |  |

| Tx channels            | 2                          |  |

| Tx PLL type            | QPLL 0/2                   |  |

| Tx Ref Clock           | GTREFCLK1                  |  |

| Rx Protocol            | HDMI                       |  |

| Rx Max GT line rate    | 5.4 Gb/s                   |  |

| Rx channels            | 3                          |  |

| Rx PLL type            | CPLL                       |  |

| Rx Ref Clock           | GTREFCLK0                  |  |

| No of pixels per clock | 8                          |  |

| Clock Frequency        | 60 MHz                     |  |

Table 1. Protocol parameters for HDMI based Video PHY controller

Table 1 describes the different protocols parameters for HDMI based Video PHY controller. The interface for the Video controller is HDMI. There different clock signals are utilized to synchronize the transmitter and receiver data rate. In 7 series FPGA, an I/O tile is defined with I/O buffers, I/O logics and I/O delays. Each IOB contains both input and output logic and IO drivers. These drivers can be configured to various I/O standards [9]. The IO Standard based schematic diagram of Video PHY controller is demonstrated using Figure 3. It is defined in Figure 2 device configuration has been changed by adding the IO Standard and its related operating voltage in VHLD based HDMI based Video PHY controller. Virtex 7 series FPGA support many IO Standard a long list is available in [11]. In this research, authors have selected the unidirectional and bi-directional IO Standards that meet the requirements for Video PHY controller. These IO Standards are specified in the Electronic Industry Alliance JEDEC [10]. The reason for selecting the unidirectional and bi-directional IO Standards for Video PHY controller is that to compare the performance of Video PHY controller at unidirectional and bi-directional IO Standards. Both unidirectional and bi-directional IO Standards has there own characteristics. It is advisable to verify the power

consumption of Video PHY controller at unidirectional and bi-directional IO Standards. In the IO Standard description, the DCI versions of class-I SSTL and HSTL I/O standards only have internal split-termination resistors present on inputs (not outputs). The DCI versions of class-II SSTL and HSTL I/O standards always have internal split-termination resistors present on input, outputs, or bidirectional pins. In the next section, the unidirectional and bidirectional Io Standard specification are discussed.

### 1) Unidirectional and Bi-directional IO Standard Specification

It is defined in [11] that class-I SSTL and HSTL I/O standards are only supported for unidirectional. In this work, the class-I HSTL is considered because the video controller need a high speed buffering for video processing. HSTL (High-Speed Transceiver Logic) is the IO Standard for high-speed bus standard is defined by JEDEC (JESD8-6). The HSTL standards have four variations (classes), to support clocking high-speed memory interfaces. 7 series FPGA I/O supports class-I for the 1.2V version of HSTL (in HP banks), and class-I and II for the 1.5V and 1.8V versions, including the differential versions. HSTL\_I use VCCO/2 as a parallel-termination voltage (VTT) and are intended for use in unidirectional links. HSTL\_II use VCCO/2 as a parallel-termination voltage (VTT) and are intended for use in bidirectional links. This HSTL IO Standard is also configured for different other Io Standards such as; DCI (Digital Controlled Impedance), DIFF (Differential Impedance) [11]. In this paper, only the HSTL IO Standard with Class I and II are utilized for developing the unidirectional and bidirectional IO Standard base design for Video PHY controller. The syntax for changing the IO Standards from default to user defined unidirectional and bidirectional IO Standard is mentioned as following manner:

a) For HSTL\_IIO Standard

attribute IOSTANDARD: string; attribute IOSTANDARD of IDIOA0: label is- "HSTL I";

b) For HSTL II IO Standard

attribute IOSTANDARD: string; attribute IOSTANDARD of IDIOA0: label is-"HSTL II";

In the above discussion, unidirectional and bidirectional IO Standard section and syntax to choose the unidirectional and bidirectional IO Standard for Video PHY controller is demonstrated in the next, the performance of the Video PHY controller is analyzed for aforementioned Io Standards.

B. Design Step 3: Performance Analysis of IO Standard based HDMI based Video PHY controller using power analysis

The performance of the unidirectional and bidirectional IO Standard based Video PHY controller IO Standard based HDMI Video PHY controller is analyzed for high frequency operation of 6 GHz. The power analysis is performed for these high frequencies using HSTL\_II O Standard, and HSTL\_II IO Standard, and HSTL\_II\_18 IO Standard. The power analysis for Video PHY controller in 7 series FPGA power is comprises of sum of device static power, design static power and design dynamic power presented in equation (1) [9].

$Total\ FPGA\ power = Design\ Dynamic\ Power + Device\ Static\ Power + Design\ Static\ Power$ (1)

Device static power characterizes the transistor leakage power when devices is powered and not configured. Design Dynamic power epitomizes the power associated with design activity and switching events in the core or I/O of the device. Dynamic power is determined by node capacitance, supply voltage, and switching frequency. Design static power denotes the power consumption when the device is configured with no switching activates. The power consume by clock manager. In the next section, the power analysis is performed for Video PHY controller IO Standard for different IO Standards.

## 1) Performance Analysis of Video PHY controller for 6 GHz frequency via Unidirectional IO Standard

The performance of the Video PHY controller is analyzed for 6 GHz for Unidirectional IO Standard by measuring the on-chip power. The unidirectional IO Standards is selected for performance analysis is HSTL\_ I IO Standard. The on-chip power consumption for HSTL\_ I IO Standard at 6 GHz for Video PHY controller is illustrated in Table 1.

Table 1. Power Consumption in W for Video PHY controller using HSTL\_ I IO Standard at 6 GHz

| Design<br>Dynamic | Device<br>Static Power | Design<br>Static Power | Total<br>Power |

|-------------------|------------------------|------------------------|----------------|

| Power             |                        |                        |                |

| 3.4               | 0.001                  | 0.6                    | 4.001          |

It is illustrated in Table 1 that when vhdl based design of Video PHY controller is operated at 6 GHz using HSTL\_ I IO Standard. The total on-chip power consumption is 4.001 W. In this, the maximum power consumption is 3.4 W. The device static power consumption is recorded as 0.001 W. The design static power consumption is 0.6 W. In the next, the power consumption of vhdl based design of Video PHY controller is operated at 6 GHz is analyzed for bidirectional IO Standard.

## 2) Performance Analysis of Video PHY controller for 6 GHz frequency via Bidirectional IO Standard

The performance of the Video PHY controller is analyzed for 6 GHz for bidirectional IO Standard by measuring the on-chip power. The bidirectional IO Standards is selected for performance analysis is HSTL\_ II IO Standard. The on-chip power consumption for HSTL\_ I IO Standard at 6 GHz for Video PHY controller is illustrated in Table 2.

Table 2. Power Consumption in W for Video PHY controller using HSTL\_ II IO Standard at 6 GHz

| Design     | Device       | Design       | Total |

|------------|--------------|--------------|-------|

| Dynamic    | Static Power | Static Power | Power |

| Power 4.67 | 0.045        | 1.25         | 5.965 |

Table 2 shows the on-chip power consumption for vhdl based design of Video PHY controller operated at 6 GHz using HSTL\_II IO Standard. The total on-chip power consumption is 5.965 W. It can be analyzed that design dynamic power is increased compared to unidirectional IO Standard design for vhdl based design of Video PHY controller is operated at 6 GHz. The most important thing to note that standby mode power

i.e. device static power is increased to 0.045 W for vhdl based design of Video PHY controller operated at 6 GHz using HSTL\_II IO Standard compared to vhdl based design of Video PHY controller operated at 6 GHz using HSTL\_I IO Standard. In this section, the power analysis is discussed for Video PHY controller operated at 6 GHz for unidirectional and bidirectional IO Standards. In the next section, the results attained are discussed for Video PHY controller operated at 6 GHz for unidirectional and bidirectional IO Standards.

#### III. RESULTS AND DISCUSSION

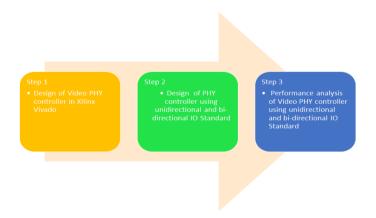

In this paper, power analysis for Video PHY controller is proposed using unidirectional and bidirectional IO Standard. The IO Standard are selected according to specification of for Video PHY controller and 7 series FPGA. It is determined that for Video PHY controller is tested 6 GHz using unidirectional and bidirectional IO Standards. The power consumption analysis for Video PHY controller is proposed using unidirectional and bidirectional IO Standard is demonstrated in Figure 3.

Figure 3. Design dynamic power analysis for Video PHY controller using unidirectional and bidirectional IO Standard

It can be analyzed from Figure 3 that when Video PHY controller is designed using unidirectional the design dynamic power consumption is 3.4 W. However, when Video PHY controller is designed using bidirectional IO Standard, the design dynamic power recorded is 4.67 W. It is determined that unidirectional IO Standard based design consumes less power than bidirectional IO Standard for Video PHY controller. The reason for this less power consumption is that HSTL\_I which is unidirectional IO Standard has operating voltage of 1.5 V and HSTL\_II which is bidirectional IO Standard has operating voltage of 1.8 V. The operating voltage of Video PHY controller is 1.5 V. The difference between core voltage of series 7 FPGA and bidirectional IO Standard based design of Video PHY controller is consume more power compared to unidirectional IO Standard based design of Video PHY controller. It can defined as 27% power reduction is achieved using unidirectional IO Standard based design of Video PHY controller. The device static power consumption analysis for Video PHY controller using unidirectional and bidirectional IO Standard is demonstrated in Figure 4.

ISSN: 2446-2918 DOI: 10.21058/gjecs.2017.21003

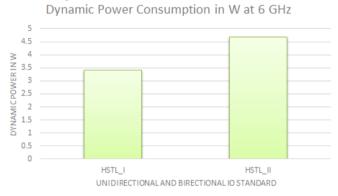

Figure 4. Device Static power analysis for Video PHY controller using unidirectional and bidirectional IO Standard

Figure 4 demonstrates the device static power consumption for Video PHY controller is designed using unidirectional and bidirectional IO Standard. It is illustrated that for unidirectional IO Standard based design of Video PHY controller device static power is 0.001 W. For bidirectional IO Standard based design of Video PHY controller device static power is 0.045 W. The device static power is more for bidirectional IO Standard based design of Video PHY controller. It is calculated that power reduction in device static power is attained for unidirectional IO Standard based design of Video PHY controller compared to bidirectional IO Standard based design of Video PHY controller. The power reduction is of 97%. It means the unidirectional IO Standard based design of Video PHY controller consumes very less power in standby mode. The reason for this less power consumption is the difference between the core voltage of 7 series FPGA and IO Standard based design of Video PHY controller. The difference between core voltage of 7 series FPGA and bidirectional IO Standard based design of Video PHY controller is high, due to this leakage current is increased and this cause to increase the device static power. Similarly, the power reduction of design static power of Video PHY controller is achieved for unidirectional Io Standard compared to bidirectional IO Standard based design of Video PHY controller. This power consumption is demonstrated in Figure 5.

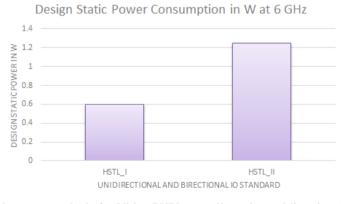

Figure 5. Design Static power analysis for Video PHY controller using unidirectional and bidirectional IO Standard

It can be analyzed from Figure 5 that when Video PHY controller is designed using unidirectional the design static power consumption is 0.6 W. However, when Video PHY controller is designed using bidirectional IO Standard, the design dynamic power recorded is 1.2 W. It is determined that unidirectional IO Standard based design consumes less power than bidirectional IO Standard for Video PHY controller. It is illustrated that 50% design

static power reduction is achieved using unidirectional IO Standard based design of Video PHY controller compared to bidirectional IO Standard based design of Video PHY controller. The power consumption analysis for Video PHY controller is proposed using unidirectional and bidirectional IO Standard is demonstrated in Figure 3. The total on-chip power analysis is also performed for Video PHY controller using unidirectional and bidirectional IO Standard. It is shown in Figure 6 that total on-chip power of Video PHY controller is less for unidirectional IO Standard design for Video PHY controller compared to directional IO Standard based of Video PHY controller.

Figure 6. Total on-chip power analysis for Video PHY controller using unidirectional and bidirectional IO

Standard

Figure 6 demonstrates the total on-chip power consumption for Video PHY controller for both unidirectional and bidirectional IO Standards. It can be analyzed that total power consumption of unidirectional IO Standard based Video PHY controller is less compared to bidirectional IO Standard based Video PHY controller. It can observed that total on-chip power for unidirectional IO Standard based Video PHY controller is 4.001 W and total on-chip power for bidirectional IO Standard based Video PHY controller is 5.965 W. It is determined that overall, 33% power reduction is achieved for unidirectional IO Standard based Video PHY controller compared to bidirectional IO Standard based Video PHY controller for 6 GHz operating frequency. The reason for this less power consumption for unidirectional IO Standard based Video PHY controller is that it has same operating voltage for Video PHY controller and for core voltage of 7 series FPGA. The unidirectional IO Standard based Video PHY controller also has less termination impedance compared to bidirectional IO Standard based Video PHY controller. It is therefore defined that Video PHY controller operated at 6 GHz, the unidirectional IO Standard based Video PHY controller consume less power compared to bidirectional IO Standard based Video PHY controller.

#### IV. CONCLUSION AND FUTURE WORK

The power performance analysis for Video PHY controller is proposed in this work using unidirectional and bidirectional IO Standard for high performance. The Video PHY controller is tested for high frequency operation of 6 GHz and 6 GHz unidirectional IO Standard based Video PHY controller and bidirectional IO Standard based Video PHY controller. The total on-chip power is calculated for Video PHY controller using unidirectional IO Standard and bidirectional IO Standard. It is defined that total 33% power consumption is reduced for based Video PHY controller using unidirectional IO Standard based Video PHY controller is less compared to bidirectional IO. It also defined using unidirectional IO Standard based Video PHY controller 95% standby power is saved compared to bidirectional IO Standard

ISSN: 2446-2918 DOI: 10.21058/gjecs.2017.21003

based Video PHY controller. It is therefore, concluded that unidirectional IO Standard based Video PHY controller offers the least power consumption for standby mode. The unidirectional IO Standard based Video PHY controller will be supportive to produce high resolution video and will provide minimum standby power consumption. In the future, the resolution for the Video PHY controller can be improved using proposed technique at lowes standby power consumption.

#### V. ACKNOWLEDGEMENT

This work is supported in collaboration with Gyancity Research Lab, India and Universiti Tun Hussein Onn Malaysia, Malaysia. We are thankful to both organization for encouraging us to contribute in knowledge.

#### REFERENCES

- [1]. Xilinx Inc, "Video PHY Controller v2.0" in Product Guide, June 8, 2016. Available: <a href="https://www.xilinx.com/support/...phy">https://www.xilinx.com/support/...phy</a> controller/v2 0/pg230-vid-phy-controller.pdf [Accessed: Mar 17, 2017].

- [2]. Bonatto, A. C., Soares, A. B., & Susin, A. A. (2011, April). Multichannel SDRAM controller design for H. 264/AVC video decoder. *In 2011 IEEE VII Southern Conference on Programmable Logic (SPL)*, 2011, pp. 137-142).

- [3]. B. Das, M. F. L. Abdullah, N. S. M. Shah, and B. Pandey, "Energy-efficient Pseudo Noise generator based optical transmitter for Ethernet(IEEE 802.3az)," *In 2015 International Conference on Computer, Communications, and Control Technology (I4CT)*, 2015, pp. 142-146.

- [4]. M. F. L. Abdullah. Bhagwan Das, Mohd. Shah Nor Shahida, Qadir Bakhsh, "Current Mode Logic based Semiconductor Laser Driver Design for Optical Communication System," *Indian Journal of Science & Technology*, vol. 9, pp. 1-6, 2016.

- [5]. B. Pandey, M. A. Rahman, A. Saxena, and B. Das, "Leakage Power Reduction with Various IO Standards and Dynamic Voltage Scaling in Vedic Multiplier on Virtex-6 FPGA," *Indian Journal of Science and Technology*, vol. 9, pp. 1-12, 2016.

- [6]. B. Pandey, B. Das, A. Kaur, T. Kumar, A. M. Khan, D. M. Akbar Hussain, et al., "Performance Evaluation of FIR Filter After Implementation on Different FPGA and SOC and Its Utilization in Communication and Network," *Wireless Personal Communications*, pp. 1-15, 2016.

- [7]. M. F. L. Abdullah, Mohd Shah Nor Shahida, Qadir Bakhsh, Bishwajeet Pandey, "Energy Efficient Design Of Laser Driver Using Field Programming Gate Array," ARPN Journal of Engineering and Applied Sciences, vol. 11, pp. 3796-3804, 2016.

- [8]. B. Das, A. Kiyani, V. Kumar, M. F. L. Abdullah, and B. Pandey, "Power optimization of Pseudo Noise based optical transmitter using LVCMOS IO standard," *In 2015 Power Generation System and Renewable Energy Technologies (PGSRET)*, 2015, pp. 1-7.

- [9]. B. Das, and M.F.L Abdullah. "Low Power Design of High Speed Communication System Using IO Standard Technique over 28 nm Chip" in *Design and Modeling of Low Power VLSI Systems*, M. Sharma, R.Gautam, M.A. Khan, Eds. USA: IGI publisher, June 2016, ISSN No. 2327-039X.

- [10]. Electronic Industry Alliance, "IO Standards". [Online]. Available: https://www.coursehero.com [Accessed: Mar 17, 2017].

- [11]. Xilinx Inc, "7 Series FPGAs SelectIO Resources" in User Guide, SEP 27, 2016. Available: https://www.xilinx.com/support/documentation/user\_guides/ug471\_7Series\_SelectIO.pdf [Accessed: Mar 17, 2017].