# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2016

# Enabling Runtime Profiling to Hide and Exploit Heterogeneity within Chip Heterogeneous Multiprocessor Systems (CHMPS)

Eugene Cartwright University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Software Engineering Commons, and the Systems Architecture Commons

## Recommended Citation

Cartwright, Eugene, "Enabling Runtime Profiling to Hide and Exploit Heterogeneity within Chip Heterogeneous Multiprocessor Systems (CHMPS)" (2016). Theses and Dissertations. 1571. http://scholarworks.uark.edu/etd/1571

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu.

# Enabling Runtime Profiling to Hide and Exploit Heterogeneity within Chip Heterogeneous Multiprocessor Systems (CHMPS)

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Computer Engineering

by

Eugene Cartwright

University of Arkansas

Bachelor of Science in Computer Engineering, 2009

University of Arkansas

Master of Science in Computer Engineering, 2012

# May 2016 University of Arkansas

| This dissertation is approved for recommendation to the Graduate Council |                                     |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------|--|--|--|

| Dr. David Andrews<br>Dissertation Director                               |                                     |  |  |  |

| Dr. John Gauch<br>Committee Member                                       |                                     |  |  |  |

| Dr. Jackson Cothren Committee Member                                     | Dr. Miaoqing Huang Committee Member |  |  |  |

#### Abstract

The heterogeneity of multiprocessor systems on chip (MPSoC) has presented unique opportunities for furthering today's diverse application needs. FPGA-based MPSoCs have the potential of bridging the gap between generality and specialization but has traditionally been limited to device experts. The flexibility of these systems can enable computation without compromise but can only be realized if this flexibility extends throughout the software stack. At the top of this stack, there has been significant effort for leveraging the heterogeneity of the architecture. However, the betterment of these abstractions are limited to what the bottom of the stack exposes: the runtime system.

The runtime system is conveniently positioned between the heterogeneity of the hardware, and the diverse mix of both programming languages and applications. As a result, it is an important enabler of realizing the flexibility of an FPGA-base MPSoC. The runtime system can provide the abstractions of how to make use of the hardware. However, it is also important to know *when* and *which* hardware to use. This is a non-issue for a homogeneous system, but is an important challenge to overcome for heterogeneous systems.

This thesis presents a self-aware runtime system that is able to adapt to the application's hardware needs with a runtime overhead that is comparable to a naive approach. It achieves this through a combination of pre-generated offline data, and the utilization of runtime data. For systems with diminishing hardware, the results confirmed that the runtime system provided high resource efficiency. This thesis also explored different runtime metrics that can affect the application on a heterogeneous system and offers concluding remarks on future work.

©2016 by Eugene Cartwright

All Rights Reserved

# Acknowledgements

I would like to extend my thanks to my thesis committee, especially my advisor Dr. David Andrews for providing the tools necessary for my research.

# Contents

| 1 | Intro | oduction           | n                                                 |  | 1  |  |

|---|-------|--------------------|---------------------------------------------------|--|----|--|

|   | 1.1   | Why Heterogeneity? |                                                   |  |    |  |

|   | 1.2   | Issues of          | of Heterogeneity                                  |  |    |  |

|   |       | 1.2.1              | Application portability and complexity            |  |    |  |

|   |       | 1.2.2              | Dynamic Mapping                                   |  | 7  |  |

|   |       | 1.2.3              | Interoperability                                  |  | 9  |  |

|   | 1.3   | Thesis             | Statement                                         |  | 9  |  |

|   |       | 1.3.1              | Thesis Contributions and Organization             |  | 10 |  |

| 2 | Bacl  | kground            | 1                                                 |  | 12 |  |

|   | 2.1   | Prograr            | mming Languages and tools                         |  | 12 |  |

|   |       | 2.1.1              | C++ AMP:                                          |  | 13 |  |

|   |       | 2.1.2              | Bolt:                                             |  | 13 |  |

|   |       | 2.1.3              | Intel Thread Building Blocks:                     |  | 14 |  |

|   |       | 2.1.4              | OpenMP:                                           |  | 14 |  |

|   |       | 2.1.5              | Cilk/Cilk Plus:                                   |  | 15 |  |

|   | 2.2   | Progran            | mming Frameworks                                  |  | 15 |  |

|   |       | 2.2.1              | OpenCL:                                           |  | 16 |  |

|   |       | 2.2.2              | Heterogeneous System Architecture:                |  | 17 |  |

|   |       | 2.2.3              | PLASMA:                                           |  | 18 |  |

|   |       | 2.2.4              | Dandelion:                                        |  | 19 |  |

|   |       | 2.2.5              | OpenCPI:                                          |  | 19 |  |

|   | 2.3   | Runtim             | ne Systems                                        |  | 20 |  |

|   |       | 2.3.1              | Elastic Computing:                                |  | 20 |  |

|   |       | 2.3.2              | Harmony:                                          |  |    |  |

|   |       | 2.3.3              | Qilin:                                            |  |    |  |

|   | 2.4   | Reconfi            | figurable Systems                                 |  | 26 |  |

|   |       | 2.4.1              | AMAP:                                             |  |    |  |

|   |       | 2.4.2              | SPREAD:                                           |  | 27 |  |

|   |       | 2.4.3              | StarPU:                                           |  | 27 |  |

|   |       | 2.4.4              | CaaS:                                             |  | 29 |  |

|   |       | 2.4.5              | CAP-OS:                                           |  | 30 |  |

| 3 | Imp   | lementa            | ation                                             |  | 32 |  |

|   | 3.1   |                    | lThreads (hthreads)                               |  | 32 |  |

|   |       | 3.1.1              | Heterogeneous Compilation Flow                    |  |    |  |

|   |       | 3.1.2              | Limitations of hthreads                           |  |    |  |

|   | 3.2   |                    | orphism - Dynamic and adaptable behavior          |  |    |  |

|   | 3.3   | -                  | nining processor specialization - Thread affinity |  |    |  |

|    |            | 3.3.1   | Platform Analysis                                 | 48 |  |  |

|----|------------|---------|---------------------------------------------------|----|--|--|

|    |            | 3.3.2   | Instruction Flagging                              |    |  |  |

|    |            | 3.3.3   | Polymorphic Function Call Graph                   |    |  |  |

|    | 3.4        | Runtin  | ne System                                         |    |  |  |

|    |            | 3.4.1   | Two-tiered Scheduler                              |    |  |  |

|    |            | 3.4.2   | Mapping threads to processors                     | 53 |  |  |

| 4  | Evaluation |         |                                                   |    |  |  |

|    | 4.1        | Creatin | ng a heterogeneous system - Evaluation Setup      | 57 |  |  |

|    | 4.2        |         | ing homogeneous task loads                        |    |  |  |

|    | 4.3        |         | ne metrics for effective heterogeneous scheduling | 62 |  |  |

|    |            | 4.3.1   | Instruction Distribution                          | 63 |  |  |

|    |            | 4.3.2   | Resource-Awareness                                |    |  |  |

|    |            | 4.3.3   | Forward Progress Threshold                        | 71 |  |  |

|    | 4.4        | Putting | g it all together                                 | 74 |  |  |

|    |            | 4.4.1   | Executing real-world tasks                        |    |  |  |

|    |            | 4.4.2   | Task mapping/resource efficiency performance      |    |  |  |

| 5  | Con        | clusion |                                                   | 86 |  |  |

|    | 5.1        | Future  | Work                                              | 88 |  |  |

|    |            | 5.1.1   | Opcode Flagging and Instruction Distribution      | 88 |  |  |

|    |            | 5.1.2   | Slave Processor Queues and Work Stealing          | 89 |  |  |

|    |            | 5.1.3   | Adoption of another programming model             |    |  |  |

| Re | eferen     | ces     |                                                   | 91 |  |  |

# **List of Figures**

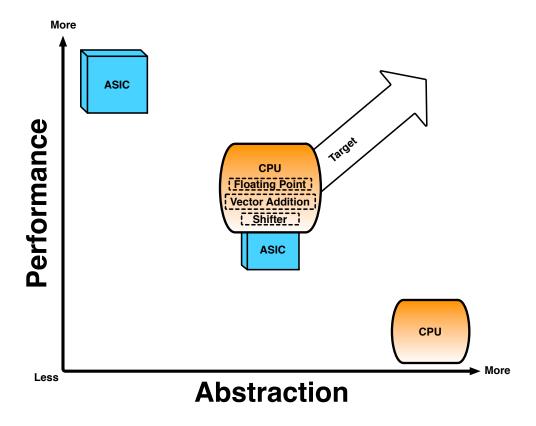

| 1.1  | CPU vs ASIC design considerations                                                 | 2  |

|------|-----------------------------------------------------------------------------------|----|

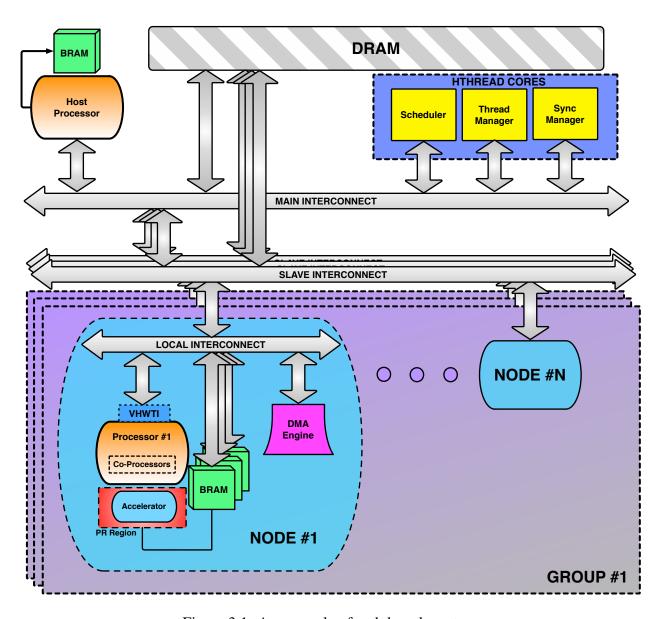

| 3.1  | An example of an hthreads system                                                  | 34 |

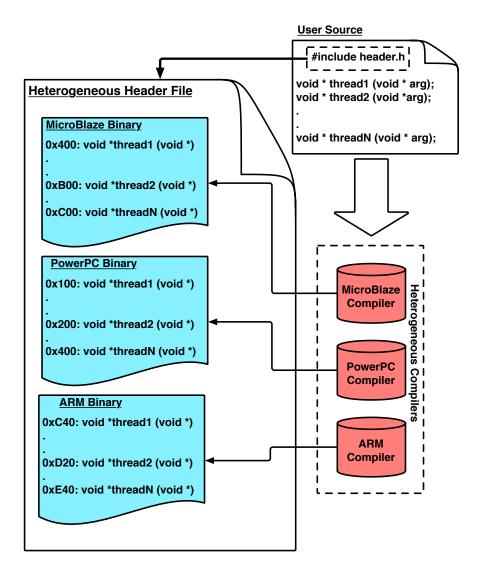

| 3.2  | A flow chart describing the embedding process for heterogeneous binaries          | 36 |

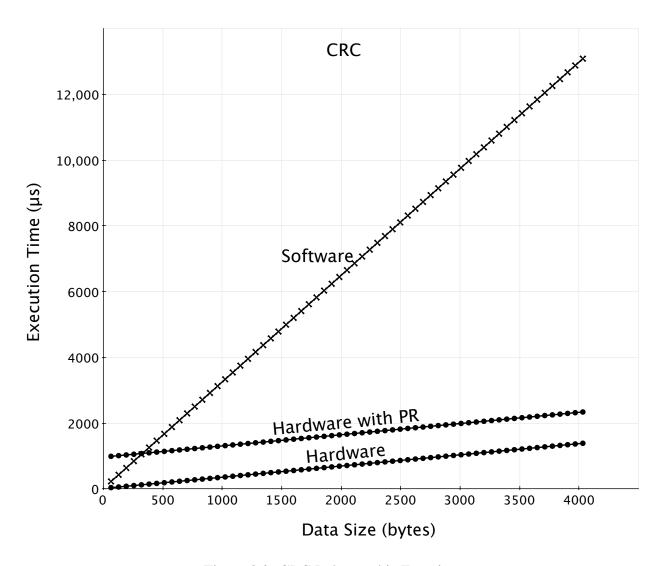

| 3.3  | CRC Polymorphic Function                                                          | 38 |

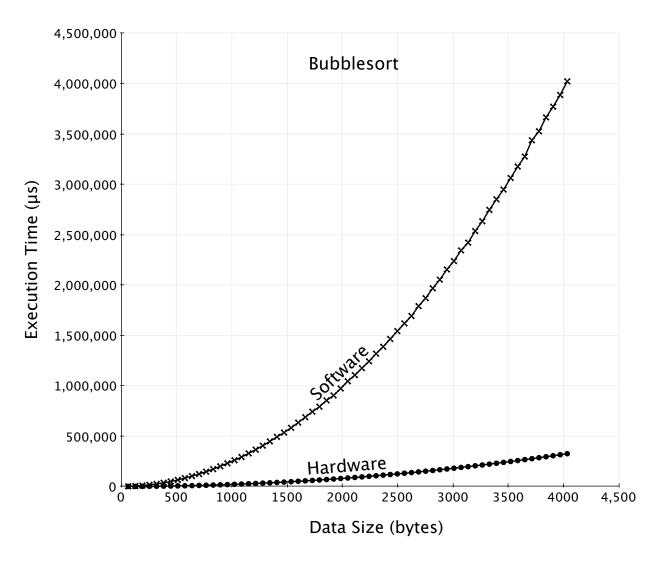

| 3.4  | Bubblesort Polymorphic Function. Hardware with PR overhead matches Hardware       |    |

|      | plot                                                                              | 39 |

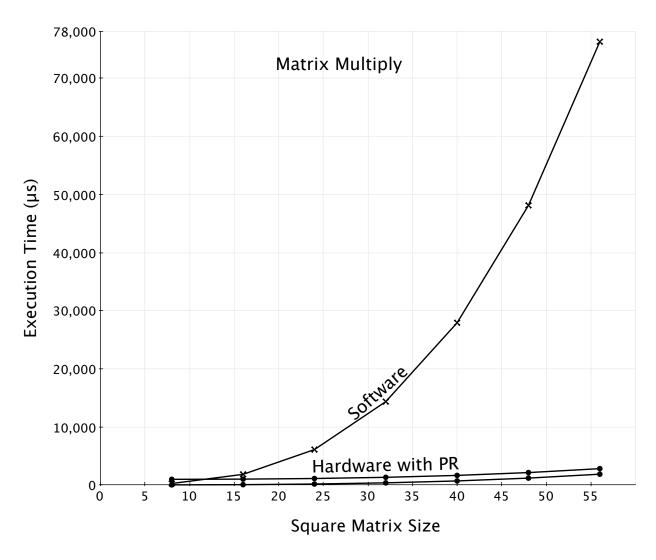

| 3.5  | Matrix Multiply Polymorphic Function                                              | 40 |

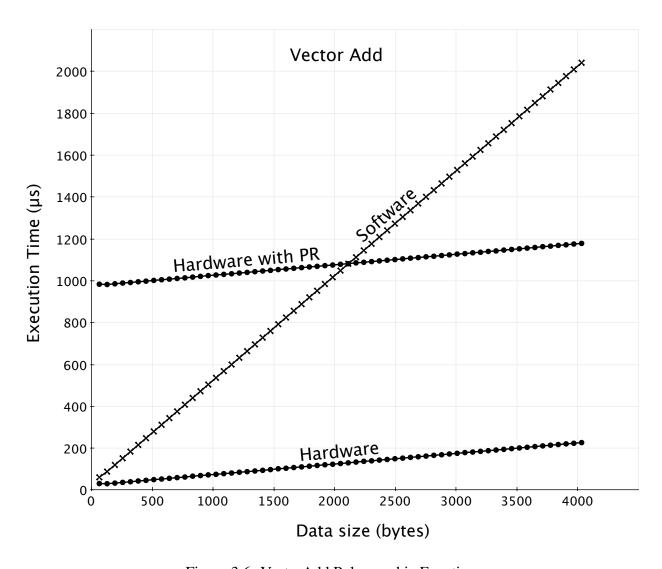

| 3.6  | VectorAdd Polymorphic Function                                                    | 41 |

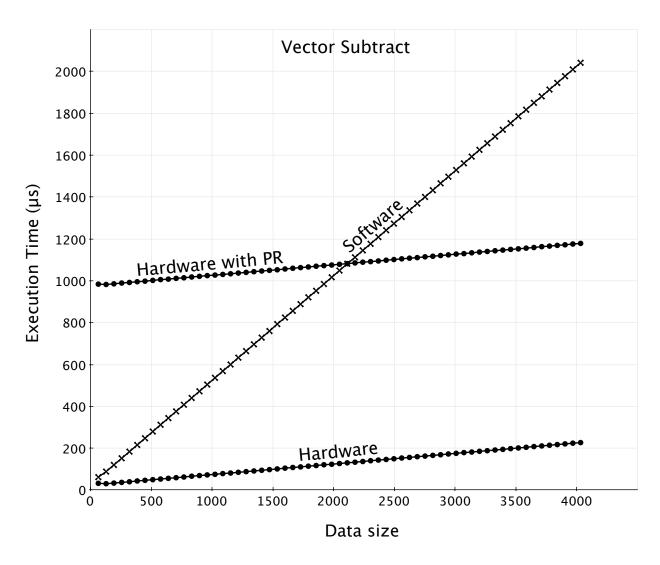

| 3.7  | VectorSubtract Polymorphic Function                                               | 42 |

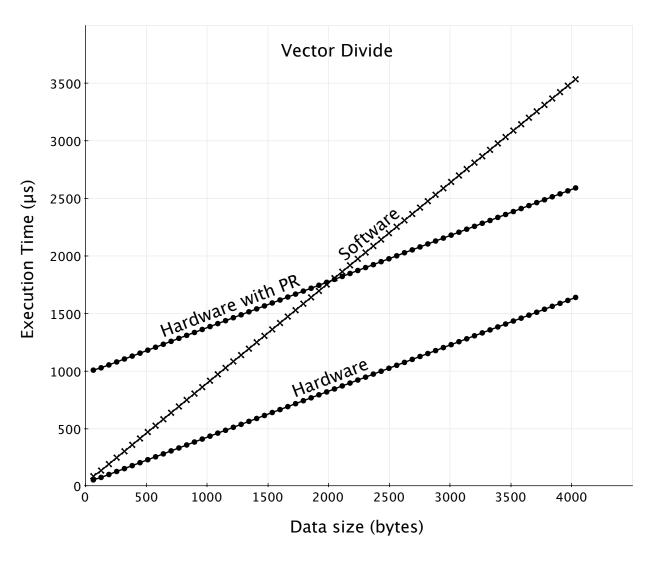

| 3.8  | VectorDivide Polymorphic Function                                                 | 43 |

| 3.9  | VectorMultiply Polymorphic Function                                               | 44 |

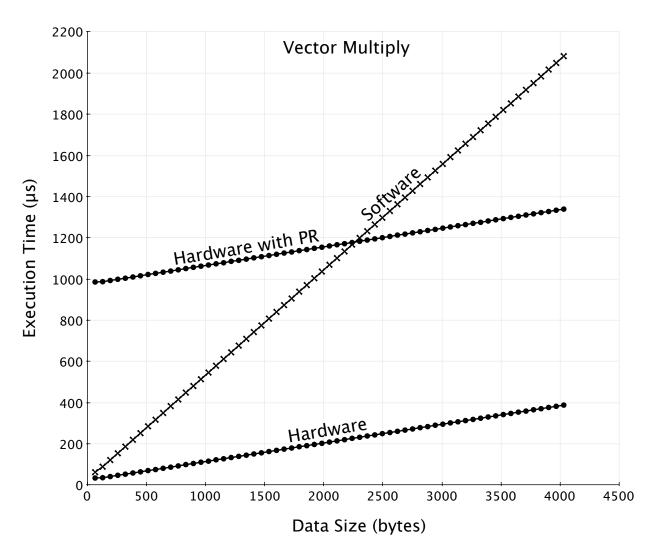

| 3.10 | Flow chart describing polymorphic function invocation                             | 46 |

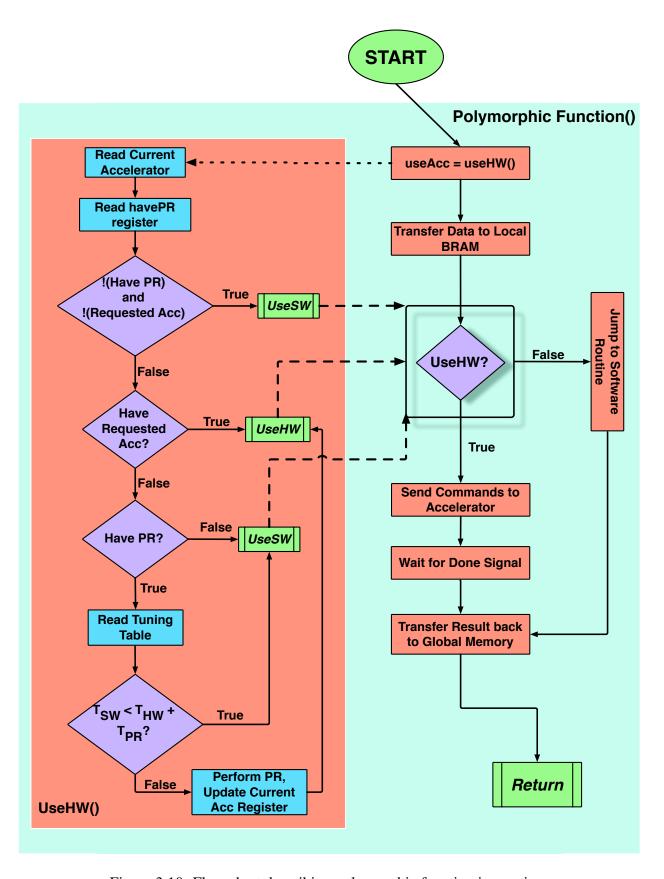

| 3.11 | Three-dimensional tuning table storing polymorphic function performance data      | 47 |

| 3.12 | Compiler flags for the MicroBlaze corresponding to configured parameters          | 49 |

| 3.13 | Thread profile structure that describes what co-processors a thread can use for a |    |

|      | given platform or a set of slave processors                                       | 50 |

| 3.14 | Instruction flagging information for the MicroBlaze's co-processors               | 51 |

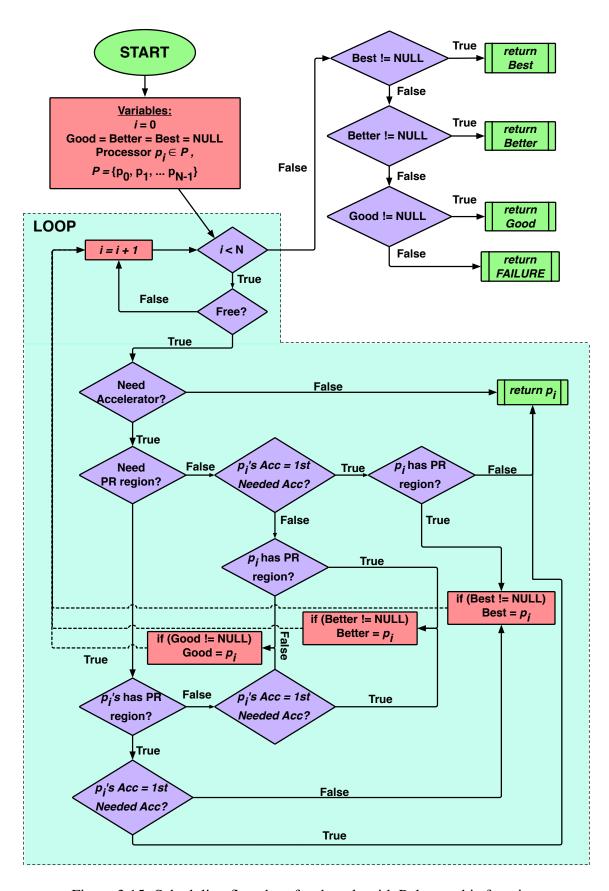

| 3.15 | Scheduling flowchart for threads with Polymorphic functions                       | 55 |

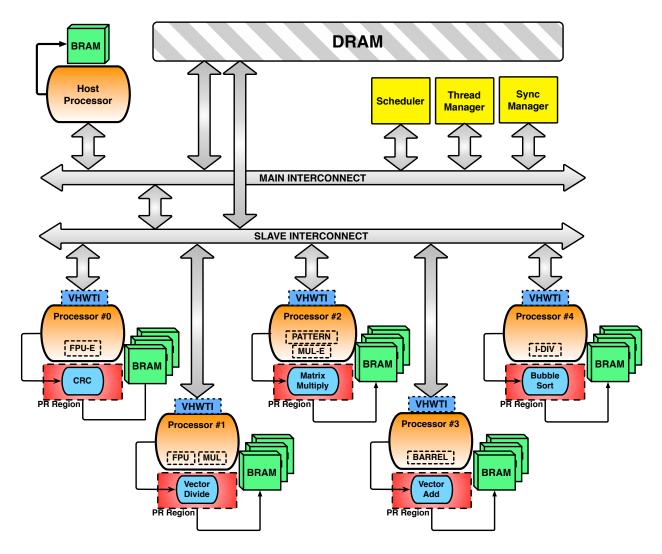

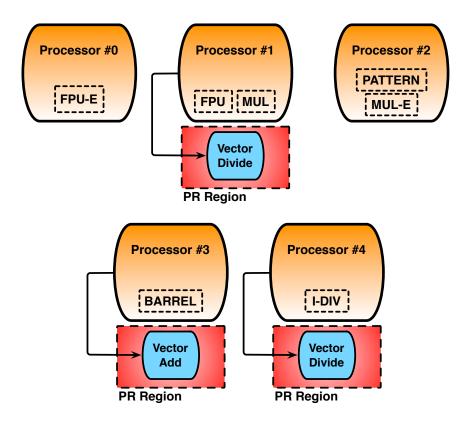

| 4.1  | Example system containing 5 heterogeneous slave processors                        | 58 |

| 4.2  | Instruction example: the floating point instructions may be dominant depending    |    |

|      | the number of times the for-loop executes                                         | 64 |

| 4.3  | Pseudocode for the synthetic benchmark                                            | 66 |

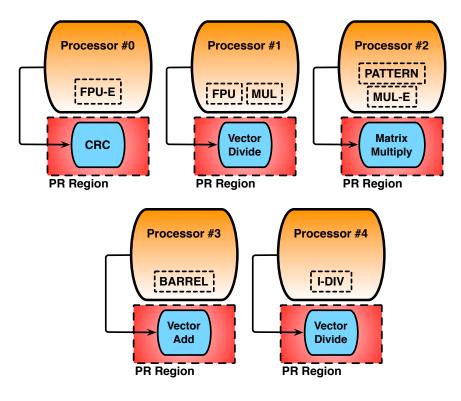

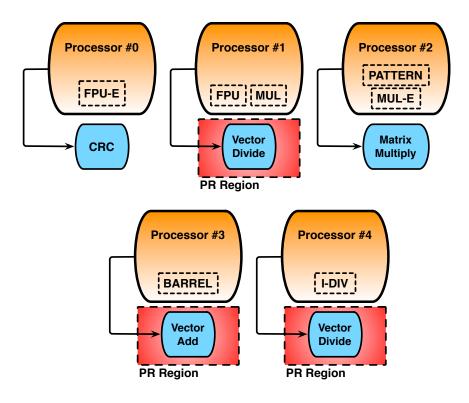

| 4.4  | Platform A                                                                         | 67 |

|------|------------------------------------------------------------------------------------|----|

| 4.5  | Platform B                                                                         | 68 |

| 4.6  | Platform C                                                                         | 68 |

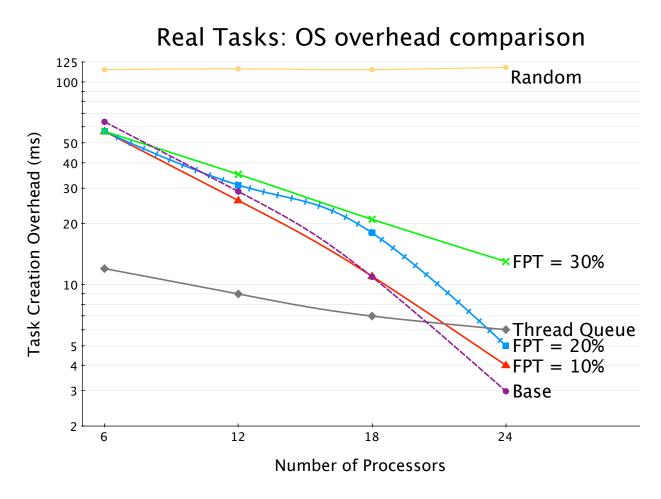

| 4.7  | Task Creation overhead for all variants of schedulers                              | 75 |

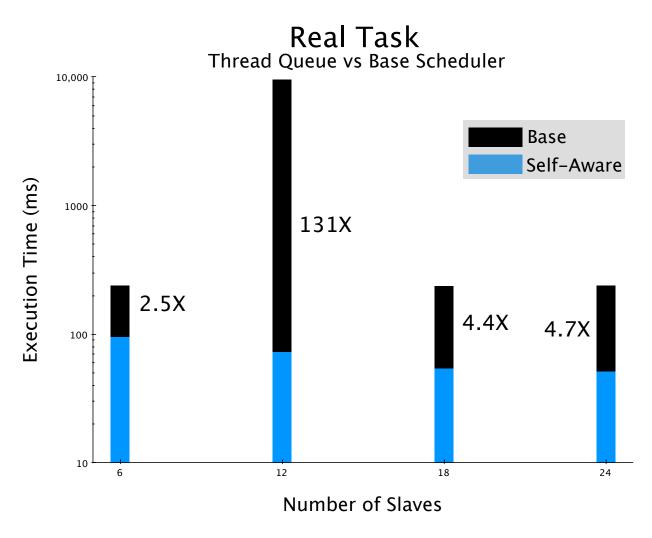

| 4.8  | Results of the Self-aware Scheduler with Thread Queuing vs Base Scheduler. Speedup |    |

|      | is also shown                                                                      | 78 |

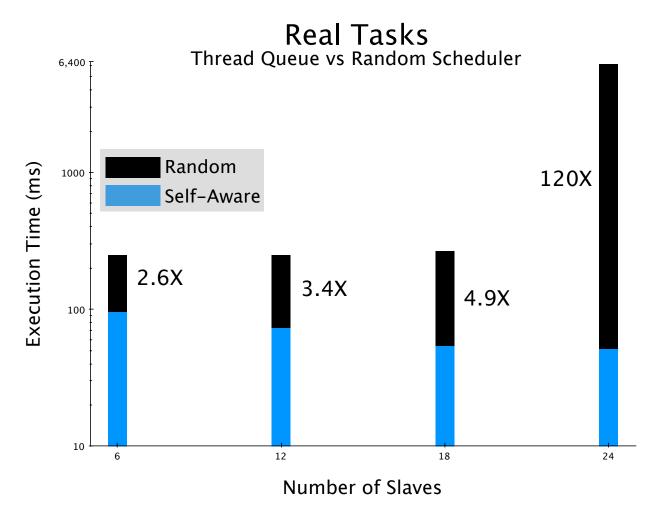

| 4.9  | Results of the Self-aware Scheduler with Thread Queuing vs Base Scheduler with     |    |

|      | Random Selection. Speedup is also shown.                                           | 79 |

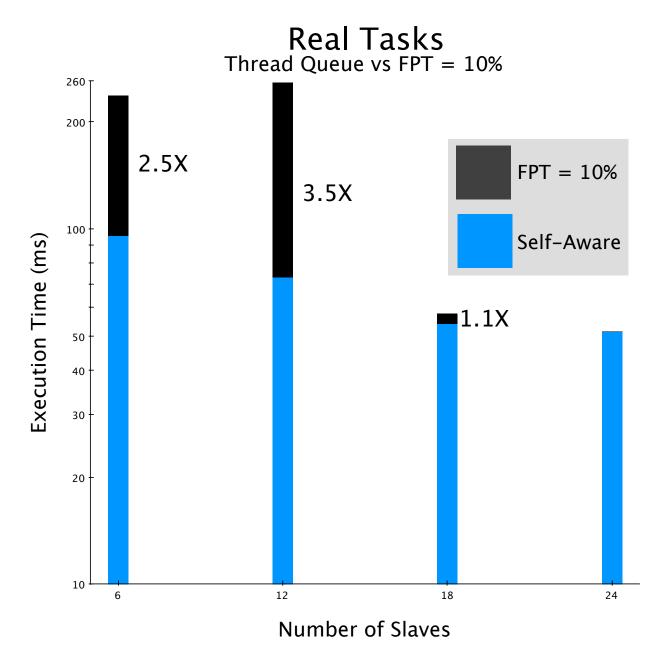

| 4.10 | Results of the Self-aware Scheduler with Thread Queuing vs with FPT = 10%.         |    |

|      | Speedup is also shown                                                              | 80 |

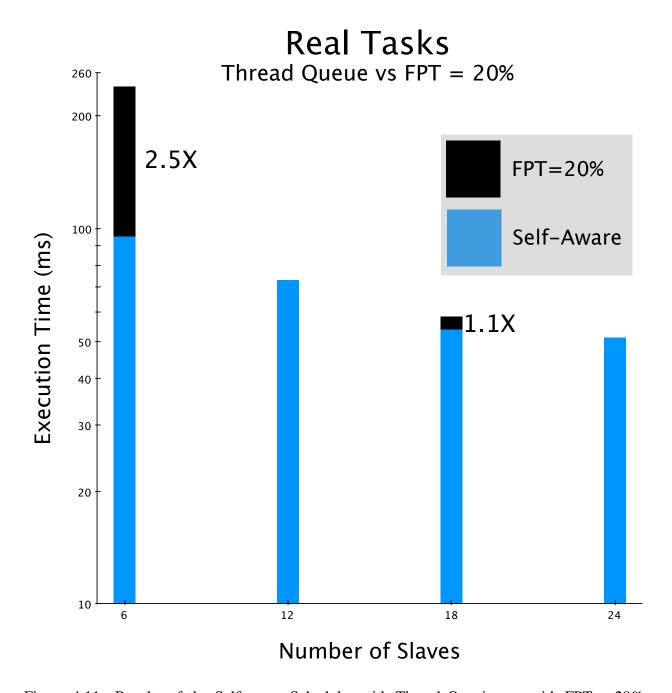

| 4.11 | Results of the Self-aware Scheduler with Thread Queuing vs with FPT = 20%.         |    |

|      | Speedup is also shown                                                              | 81 |

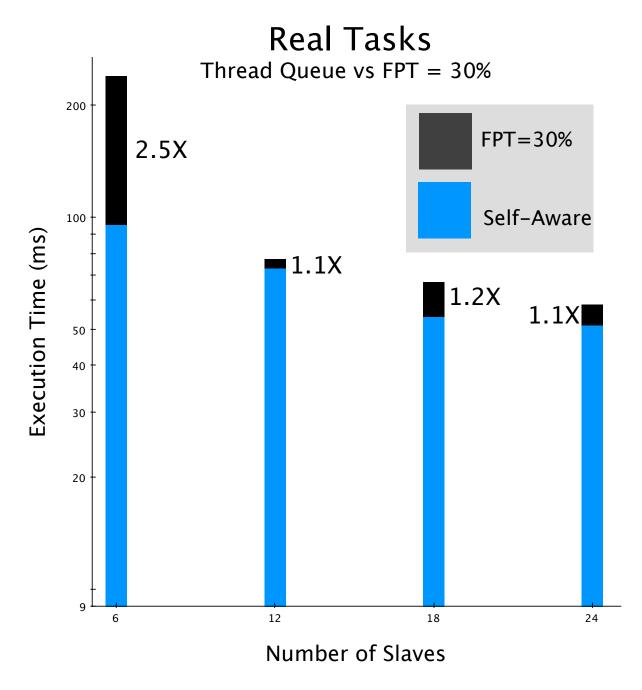

| 4.12 | Results of the Self-aware Scheduler with Thread Queuing vs with FPT = 30%.         |    |

|      | Speedup is also shown                                                              | 82 |

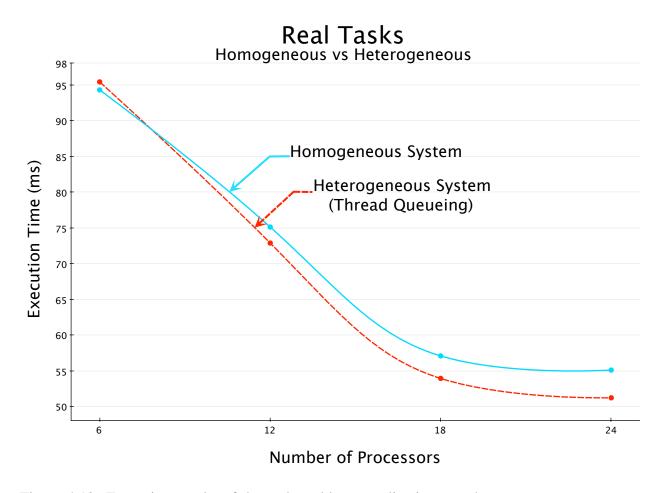

| 4.13 | Execution results of the real-world test application on a homogeneous system vs a  |    |

|      | heterogeneous system with the self-aware runtime utilizing thread queuing          | 84 |

# **List of Tables**

| 1.1 | Descriptions of the tasks used in Table 1.2                                          | ۷  |

|-----|--------------------------------------------------------------------------------------|----|

| 1.2 | Micro-benchmarks executing on heterogeneous processors                               | 5  |

| 4.1 | Performance of homogeneous tasks scheduled on all processors vs heterogeneous        |    |

|     | load of these tasks scheduled onto a heterogeneous system                            | 60 |

| 4.2 | Details on the shift benchmark executed on a heterogeneous system                    | 61 |

| 4.3 | Details on the idivu benchmark executed on a heterogeneous system                    | 62 |

| 4.4 | Results of executing a thread that includes an uneven distribution of shifting oper- |    |

|     | ations (18) and floating point operations (2400)                                     | 65 |

| 4.5 | Results of executing 128 detached threads that call various polymorphic functions,   |    |

|     | randomly. Data sizes for each call was also randomly chosen                          | 69 |

| 4.6 | PR percentage when executing in Hardware/Percentage of software executions out       |    |

|     | of the 154 polymorphic functions called across the 128 threads                       | 70 |

| 4.7 | Results of scheduling 128 detached threads, whereby threads are released only        |    |

|     | when 20% or more of the processors are available                                     | 72 |

| 4.8 | PR percentage when executing in Hardware/Percentage of software executions out       |    |

|     | of the 154 polymorphic functions called across the 128 threads                       | 73 |

| 4.9 | Table providing the name, MicroBlaze co-processor support, and descriptions of       |    |

|     | each real-world task used in this thesis. Fastest/Slowest Time is the time recorded  |    |

|     | for a MicroBlaze in the 24 processor system used in Section 4.4.1                    | 76 |

#### **Terms and Definitions**

- **ABI** Application Binary Interface. Refers to the calling convention and data layout of a particular processor-compiler pair.

- **API** Application Programmer Interface. The defined interface of a piece of software, often times a library or operating system.

- **CISC** Complex Instruction Set Computer.

- **CPU** Central Processing Unit. A programmable hardware component, often referred to as processor or core.

- **DMA** Direct Memory Access. Often referring to hardware devices that can perform memory-tomemory operations without processor assistance.

- **DPR** Dynamic Partial Reconfiguration. The process of which a portion of the FPGA is reconfigured without disrupting the rest of the chip while active.

- **DSP** Digital Signal Processor. A processor specialized for signal processing, often featuring vector and multiply-accumulate operations.

- **FIFO** First-In, First-Out. A hardware component or data structure that exhibits First-In, First-Out behavior (e.g. a queue).

- **FPGA** Field Programmable Gate Array. A hardware chip whose functionality can be changed post-fabrication.

- **GPU** Graphics Processing Unit. A hardware component specialized for graphics processing.

- **HAL** Hardware Abstraction Layer. A layer of software used to hide hardware-specific implementation details.

**HDL** Hardware Description Language (e.g. VHDL or Verilog).

**HLL** High-Level Language.

**HW** Abbreviation for Hardware.

**ISA** Instruction Set Architecture. Also known as the instruction set of a particular processor.

**IPC** Inter-Process Communication, when referring to software; or Inter-Processor Communication, when referring to hardware systems. Also used to abbreviate the average number of instructions that can be processed in a clock cycle.

I/O Input/Output.

**Kernel** The core component(s) of an operating system.

**LIFO** Last-In, First-Out. A hardware component or data structure that exhibits Last-In, First-Out Behavior (e.g. a stack).

MIMD Multiple-Instruction, Multiple-Data. A category of parallel programming/computational model in Flynn's Taxonomy that is represented by systems capable of executing different instruction streams that are able to operate on different streams of data simultaneously. Multiprocessor (multi-core) systems fit into the MIMD category.

**MISD** Multiple-Instruction, Single-Data. A category of parallel programming/computational model in Flynn's Taxonomy that is represented by a machine that executes multiple instructions on a single piece of data. It can be argued that pipelines and systolic arrays fit into this category.

**MMIO** Memory-Mapped I/O. The process of performing I/O through memory-mapped interactions such as reads and writes (loads and stores).

MPSoC Multiprocessor System-on-Chip.

**OS** Operating System.

**RPC** Remote-Procedure Call.

**SIMD** Single-Instruction, Multiple-Data. A category of a parallel programming/computational model in Flynn's Taxonomy that is represented by a vector processor that executes a single instruction on multiple data at once.

**SISD** Single-Instruction, Single-Data. A category of a parallel programming/computational model in Flynn's Taxonomy that is represented by a typical scalar processor.

**SW** Abbreviation for Software.

**RISC** Reduced Instruction Set Computer.

## Chapter 1

#### Introduction

General computing systems have evolved over the past decade to support the increasing diversity of concurrent and parallel tasks. System designers continually face the challenge of increasing performance while decreasing the energy footprint of these systems. One component that maintains its presence in many of these systems is the general purpose processor (GPP), otherwise known as the central processing unit (CPU). CPUs have long provided a flexible architecture for targeting applications that span across multiple domains. With the support of mature compilers and increasing levels of abstraction provided by high-level languages [42, 3, 35, 45, 36, 43], CPUs can provide high user productivity and application portability. Due to the generality of the architecture, however, performance (and energy consumption) cannot best an application-specific integrated circuit (ASIC). The use of ASICs has generally led to loss of portability and a significant decrease in productivity. One of the design choices that CPU architects have made to increase performance is outfitting parallel functional units throughout a CPU's pipeline, coining the term *superscalar* processors. These additional resources, coupled with advanced branch prediction techniques enables CPUs to exploit instruction-level parallelism (ILP).

Many of today's applications such as those in the linear algebra and image processing domains, benefit from an architecture that supports the single-instruction, multiple-data (SIMD) model. CPU support for data-level parallelism (DLP) has been achieved through the inclusion of co-processors or (application-specific) accelerators within the processor [63]. The advantage of this *tight-coupling* implementation is that the use of this specialized hardware registers as another instruction that is part of the CPU's instruction set architecture (ISA). Considering compiler support for such instructions, this level of transparency upholds application portability and user

Figure 1.1: CPU vs ASIC design considerations

productivity, while providing a new avenue for program acceleration traditionally achieved through ASICs alone.

The reality is, many of these optimizations may or may not make it into a CPU depending on the constraints given to the CPU architect or the system integrator. Designers are always forced to strike a balance between generalized and application-specific, area and performance, and time-to-market and item costs. While the CPU does provide support for targeting most applications, one must consider which particular features a CPU may provide over others that would best benefit the targeted applications. Alternatively, with the advent of the many-core era, the opportunity arises for integrating multiple heterogeneous processors in the system. Therefore, the sacrifice of choosing a single configuration of a CPU for a multiprocessor system becomes moot as one can simply incorporate multiple configurations, capable of being optimized for different sets of tasks. The question poised here is does heterogeneity bring performance

advantages of ASICS all the while maintaining CPU generality, and why or why not?

#### 1.1 Why Heterogeneity?

More than a decade ago, a shift towards multiprocessor systems occurred in the general purpose computing community to combat the *power wall*: with increased processor clock speeds for faster performance came increased power (and heat) output [13, 50, 11]. These symmetric multiprocessor (SMP) systems were composed of identical processors (with identical bus and memory hierarchies) executing identical instruction streams independently, resulting in higher computational throughput over uniprocessor systems. New programming models for SMP systems emerged, enabling software developers to leverage transparent instruction-level parallelism (ILP) found in processors with *explicit* thread-/task-level parallelism (TLP) [35, 14]. Although technology scaling allowed vendors to increase the numbers of processors, application performance did not necessarily scale at the same rate. Amdahl's law [6] provides a means to calculate how much performance can scale for an application. Small fractions of the application that can be parallelized may benefit or not due to other overhead costs (communication and memory I/O). Introducing multiple, heterogeneous processing elements optimized for different sets of tasks within an application would enable performance to scale beyond SMP systems [32].

Heterogeneous multiprocessor systems, herein referred to as heterogeneous systems, have demonstrated their performance and energy benefits over their homogeneous counterparts [59, 30]. By including multiple heterogeneous processing elements, one can begin to place tasks onto specific components that provide greater performance and/or energy benefits. For example, the system may choose to conserve energy by mapping a longer running, memory-bounded task onto a low-performance and low-powered processor over a higher performance, high powered core. Examples of commercially available heterogeneous architectures today include ARM's big.LITTLE<sup>TM</sup> multi-core architecture, Intel's QuickIA platform, and IBM's Cell platform [1, 15, 33]. However, due to the heterogeneity of these example platforms, a high-priority,

CPU-bound tasks have the opportunity to be scheduled onto a processor with a high affinity.

Contrasting this with a homogeneous platform, the design may consume more power, degrade in performance, or both due to minimal flexibility of where best to schedule tasks.

| Micro-Benchmark Task Descriptions |                                                                    |  |  |  |

|-----------------------------------|--------------------------------------------------------------------|--|--|--|

| Name                              | Description                                                        |  |  |  |

| mul32                             | 32-bit integer multiplication                                      |  |  |  |

| mul64                             | 64-bit integer multiplication                                      |  |  |  |

| idivu                             | 32-bit Unsigned integer division                                   |  |  |  |

| idiv                              | 32-bit Signed integer division                                     |  |  |  |

| fpu                               | 32-bit Floating point instructions. Includes square root function. |  |  |  |

Table 1.1: Descriptions of the tasks used in Table 1.2.

System heterogeneity, otherwise referred to as system asymmetry, can arise from multiple sources and does not necessarily translate into a system composed of multiple processing elements, each provided by a different vendor. Processors can introduce asymmetry in simple features such as clock frequency, or can encompass more micro-architectural differences such as the number of general purpose registers (GPR), inclusion of different co-processors, and in/out-of-order instruction execution capabilities [37]. Table 1.2 provides a simple example of the performance effects of processor heterogeneity. The description of each task is outlined in Table 1.1. This example provides the execution time of several micro-benchmarks running on a 6 processor system: 1 host processor that schedules work onto 5 slave processors. Each micro-benchmark focuses on one type of task. The idea here is to isolate one task at a time to provide better insight into the decisions a runtime system or operating system (OS) may need to make when presented with a diverse set of tasks in its ready-to-run-queue (R2RQ). While all of the slave processors in this system are derived from the same base design, each one is configured to include a different co-processor optimized for one of these tasks. As a result, the instruction set is slightly modified amongst them. As the table highlights, this can translate into a significant performance delta amongst these processors for a particular benchmark. This table also suggests the energy benefits that can be gained by scheduling with this constraint. If all processors expel the same amount of power, scheduling a task that minimizes rather than prolongs the execution of

| Micro-Benchmark Performance on a Heterogeneous system |                                                            |                |                |                |              |  |

|-------------------------------------------------------|------------------------------------------------------------|----------------|----------------|----------------|--------------|--|

|                                                       | Proc. 1                                                    | Proc. 2        | Proc. 3        | Proc. 4        | Proc. 5      |  |

| mul64                                                 | 303.14 (1x)                                                | 130.07 (2.3x)  | 23.11 (13.1x)  | 213.35 (1.4x)  | 303.02 (1x)  |  |

| mul32                                                 | 138.84 (1x)                                                | 15.24 (9.1x)   | 15.17 (9.2x)   | 138.61 (1x)    | 139.01 (1x)  |  |

| idivu                                                 | 45.97 (1x)                                                 | 46.10 (1x)     | 45.88 (1x)     | 45.94 (1x)     | 7.43 (6.2x)  |  |

| idiv                                                  | 44.69 (1x)                                                 | 44.34 (1x)     | 45.39 (1x)     | 44.68 (1x)     | 6.89 (6.6x)  |  |

| fpu                                                   | 104.56 (18.3x)                                             | 115.56 (16.7x) | 1058.22 (1.8x) | 718.44 (2.7x)  | 1931.18 (1x) |  |

| shift                                                 | 7099.59 (1x)                                               | 7098.70 (1x)   | 7098.85 (1x)   | 554.41 (12.8x) | 7099.37 (1x) |  |

|                                                       | Execution times (µs) and speedup relative to slowest time. |                |                |                |              |  |

Table 1.2: Micro-benchmarks executing on heterogeneous processors.

this task would net less energy consumed by the system.

The previous example demonstrated the potential performance gains from a heterogeneous multiprocessor system but is often not representative of a system today. Often, this multiprocessor system is also augmented with hardware accelerators external to the multiple processors. Hardware accelerators excel at DLP, offering a higher performance-to-power metric over general purpose processors [31, 23]. This leaves more *branchy* or speculative code and coarse-grained tasks (i.e. TLP) to processors. However, designers may work with a limited amount of area and accounting for any and all types of ASIC components within their design is not realistic. Hence, the appeal of CPUs. Alternatively, an enticing heterogeneous platform for providing exploration of both general purpose and application specific components is a Field Programmable Gate Array (FPGA).

FPGAs have the potential to bridge the gap between the benefits of general purpose processors and ASIC-like components. The increasing densities of the reconfigurable fabric allow users to implement complete chip heterogeneous multiprocessor (CHMP) systems [16]. The malleability of the FPGA allows CHMP systems to be built that are tailored to the exact types of parallelism that may be available in each application. Execution of unmodified software applications can benefit from familiar architectures equipped with general purpose processors integrated as either reconfigurable *soft*, or *hard* intellectual property (IP) cores. However, FPGA users wishing to extract additional performance from the application can do so by including

application-specific components onto the FPGA. Without having to commit to silicon as is done with an ASIC design cycle, this allows a more cost-effective solution. Leveraging this flexibility beyond processor heterogeneity, however, has been limited to FPGA device and tool experts as it imposes a high learning curve for the general software community. This requirement is continually being relaxed by new developments in high-level synthesis, re-useable IP, and programming models and abstractions [17, 41, 40]. Nevertheless, there still remains several challenges pertaining to FPGA-based CHMP systems and the heterogeneity it exposes.

## 1.2 Issues of Heterogeneity

Exploiting the use of heterogeneous components in a system faces several challenges. Today's commercial operating systems (OS) generally offer little to no support for system heterogeneity, and it is usually up to the software programmer to exploit this flexibility. As heterogeneous systems become more of a commodity item, it is important to address these challenges if one is to see a continued benefit in their use [4]. The following sections provides several challenges, specifically pertaining to CHMP systems on FPGAs.

#### 1.2.1 Application portability and complexity

Programming for heterogeneous systems has traditionally come at the cost of both application complexity and portability. To fully exploit the performance a heterogeneous system can provide without support of the runtime and/or the OS, programmers are required to know and leverage detailed knowledge of the underlying hardware. For example, where and when to schedule a task based on multiple variables such as performance characteristics that can vary from one FPGA-based CHMP configuration to another. Without any heterogeneous hardware abstractions, accounting for such intricacies increases application complexity. Furthermore, including platform-specific optimizations within the source also affects application portability and requires it to be modified when moving between one system configuration to another. It is infeasible to

account for all possible system configurations and doing so increases application complexity.

As noted previously, users of FPGA-based CHMP systems are required to know the hardware in order to design and use application-specific components within their systems. Consequently, the adoption rate of this heterogeneous platform by the general software community has been slow as a result of the imposed high learning curve. As will be discussed in Section 2.1, there is an abundance of research addressing the need for easier programmability. However, the use of user-provided hardware should coincide with application portability and complexity. Additionally, runtime decisions such as dynamically mapping tasks to the *appropriate* resource (i.e. accelerator or CPU) presents another challenge.

## 1.2.2 Dynamic Mapping

Determining how the application should be mapped onto heterogeneous systems before runtime is referred to as static mapping. Statically mapping the application is not sufficient for both homogeneous and heterogeneous systems alike [47]. Luk et. al note that not knowing the workload size renders performance estimation offline inaccurate [39]. Generating and optimizing a mapping scheme offline without knowing the data size can result in poor mapping. For example, allocating a small data-set onto hardware optimized for larger data sets can degrade performance (and increase power). Additionally, the heterogeneity of the system naturally exhibits asynchronous and indeterministic behavior. This can prove difficult to model the diverse components and their interactions in the system without making several (static) assumptions. This challenge is compounded further when considering FPGA CHMP systems. In addition to enabling FPGA users to realize their system designs on the chip itself through hardware synthesis, FPGAs also supports systems to change their hardware during runtime through a process known as dynamic partial reconfiguration (DPR) [64].

DPR offers an opportunity to shape the platform to the application's needs as it executes, gaining additional performance and/or energy savings wherever applicable. The process of

dynamically using additional hardware can unlock further speedup in comparison to static heterogeneous designs [32]. Furthermore, this can be advantageous on more resource-constrained CHMP systems by swapping in-and-out hardware. This offers greater flexibility for designers when trading hardware resources/area for performance.

To accommodate FPGA CHMP systems utilizing DPR, dynamic mapping is needed to reflect scheduling decisions based on runtime parameters such as workload sizes and current system configuration. It is also needed for the different phases of an application. Not doing do so can lead to non-optimal performance, and even worse, system failure as components assumed to be present may no longer exist. Consequently, this makes scheduling (or in general, programming) for such systems much more difficult as there are more scheduling decisions to explore. Navigating through this multidimensional search space can lead to high runtime overheads, thus increasing the application execution times further [51].

While knowing the intricacies of a relatively small heterogeneous system may suffice for statically mapping an application, targeting larger heterogeneous systems becomes less attainable to do so by hand. What is needed is a dynamic solution where, ultimately, the mapping decision is done (or further aided) by the runtime system. This enables better mapping solutions that appropriately reflect the state of the system and pending tasks. Additionally, offering a dynamic solution can scale the performance of an application further over time. In the case of FPGA CHMP systems, as the necessary hardware diminishes or increases online through the use of DPR, the runtime can accommodate the decrease/increase in computational power and map the application appropriately. Similarly, when better performing processing elements are introduced in the system, dynamically mapping the application against the current system configuration can immediately leverage this resource.

#### 1.2.3 Interoperability

Interoperability challenges within heterogeneous systems arises from the diversity of the components. For example, processors that differ in ISAs implement equivalent operations differently in hardware. As a result, this varies execution and memory access times amongst them. Another example is the application binary interface (ABI), which dictates the intricacies of a processor at the machine code level such as data storage and retrieval. The difference of ABI here can result in data misinterpretation. The introduction of custom hardware accelerators within FPGA CHMP system exacerbates this issue further, and gives a stronger need for some degree of standardization within a heterogeneous system.

Standardization in the form of hardware/software abstractions allows different components to interact within the system. Without such abstractions, this can lead to code complexity and non-portability. Standardization of OS services such as task management and synchronization should be provided for a machine that focusses on parallel execution. In addition to this, system configuration changes as a result of exploiting DPR should not introduce any interoperability issues and disrupt the flexibility of FPGA CHMP systems. Therefore, a need for an abstraction layer that seamlessly connect heterogeneous components at the HW/SW boundary is necessary and facilitates the flexibility offered by heterogeneous components.

#### 1.3 Thesis Statement

Programming support for heterogeneous multiprocessor systems remains a challenge today despite the increasing ubiquity of these systems over the years. One of the attractions towards heterogeneous systems lies within their diverse hardware, gaining opportunities for hardware task specialization to further maximize performance/energy savings [19, 29]. Consequently, this has encouraged programmers to include more platform specific information within the source code to take advantage of these performance/energy savings. Without higher levels of abstraction and/or

middleware support, this eliminates the idea of application portability, increases application complexity, and thus decreases programmer productivity. This thesis proposes to investigate if these trends can be reversed for FPGA-based heterogeneous multiprocessor systems by considering the following questions:

- Can platform specific details be moved from the source code and be encapsulated under platform neutral policies of a portable programming model to reinstate portability?

- Can the complexity of the software design process be reduced by enabling automatic profiling during runtime?

- Can dynamic mapping occur at reasonable overhead costs with high accuracy of fitting task placement? How best to determine task specialization for processors? Can some of this information be determined offline?

- Can resource efficiency be increased despite increasing levels of system complexity, by introducing additional self-awareness within the operating system?

**Thesis:** For FPGA-based heterogeneous multiprocessor systems, a self-aware runtime system can replace the need for a user to engage in hand profiling and explicit thread scheduling of an application on different configurations of heterogeneous resources. Through the integration of a self-aware runtime system in one's design, a heterogeneous multiprocessor system can better utilize its resources and match the performance of a homogeneous system where resource constraints are non-existent.

#### **1.3.1** Thesis Contributions and Organization

To support the thesis statement, this work provides the following set of contributions:

• Integrated identification of processor (and hardware accelerator) specialization within the scheduler that results in little additional runtime overhead in comparison to a naive

approach.

- Modified the hthreads compilation flow to parse platform configuration, including but not limited to MicroBlaze processor configuration and attached hardware accelerators.

- Integration of an accelerator library that enables users to utilize attached accelerators through software function invocations.

The remainder is organized as follows. Chapter 2 surveys the current state of the art approaches on multiple issues of heterogeneous computing, and concludes with FPGA related work. Next, Chapter 3 provides a detailed discussion of this thesis approach to addressing some of the issues raised in Chapter 1. A discussion of this thesis' evaluation against the proposed approach is presented in Chapter 4. Finally, the thesis concludes by reflecting back on the questions proposed and offers some potential future work that can follow this thesis.

## Chapter 2

# Background

Heterogeneous MPSoC systems are a commodity in today's society, and can be found in high performance computing data-centers to embedded devices within automobiles. Their heterogeneity, offering both flexibility and specialization, provides opportunities for additional levels of performance (and/or energy savings). However, achieving this continues to be met with the difficulty in programming such systems. Many have approached this problem with various solutions such as unified programming languages (and tools) and self-aware runtime systems. Others have incorporated both of these examples into programming frameworks. Still, very few have approached the reconfigurable domain. The following sections offer details on state of the art approaches in each of these categories.

# 2.1 Programming Languages and tools

To begin, many of the programming languages and tools (libraries and compilers) presented here attempt to provide one or more of the following:

- Device/platform abstractions for easier programming, and subsequently increasing user productivity.

- Platform portability between systems with both the presence or absence of *preferred* hardware.

- Easier accessibility of potential performance gains of the heterogeneous *component* while balancing programming effort.

Amongst these characteristics, the important goal many of the following languages and tools tend to focus on is enabling easier programmability. Therefore, many forgo addressing efficient utilization of resources. The absence of runtime information make programming languages and their use offline, not a complete solution for the programmability of heterogeneous systems. Many of these languages still require the programmer to explicitly identify where computation should execute and/or greedily schedule *all* work on a particular device (e.g. GPU vs. CPU). Nevertheless, the research presented here should be regarded as supplemental work as it provides a transparent front-end interface to a heterogeneous system.

#### 2.1.1 C++ AMP:

With the increasing use of general purpose graphics processing units (GPGPUs) on desktops, it has been made possible to accelerate non-graphics related applications on a cost-effective hardware solution. Microsoft proposed the C++ Accelerated Massive Parallelism (C++ AMP) project, enabling users to exploit DLP on these types of data-parallel hardware. The targeted hardware has generally included GPUs. However, modern CPUs containing support for SIMD (vector) operations allows the C++ AMP runtime to fall back to such hardware whenever GPUs fail to provide the computation [42].

# 2.1.2 Bolt:

Bolt is a C++ Standard Template Library (STL) that aims for accelerating user applications on accelerated hardware [3]. Bolt includes optimized implementations of common algorithmic patterns such as reduce and transform, and currently has a few back-ends for generating code to languages such as C++ AMP, OpenCL and Intel Thread Building Blocks. Having been brought to market by a GPU supplier, Advanced Micro Devices (AMD), Bolt is optimized specifically for AMD GPUs. However, like C++ AMP, the library includes fall-back mechanisms to CPUs. Bolt can dynamically query the platform, favoring the GPU device due to the assumption that it will

provide a higher level of data-parallel performance. Additionally, the memory hierarchy is not imposed on the user unlike OpenCL. As a result, programmers are presented with a linear address space found on familiar homogeneous architectures.

#### 2.1.3 Intel Thread Building Blocks:

The Intel Thread Building Blocks (Intel TBB) is a C++ STL designed for supporting parallelism across multiprocessor systems [35]. Unlike the previous discussed thus far, Intel TBB does not target other types of data-parallel hardware such as GPUs. Users write their application in terms of tasks and the library maps these tasks onto threads (CPUs assumed to be homogeneous) for more finer-grained parallelism. The Intel TBB runtime also provides load balancing of tasks and encourages users to reduce the granularity of tasks in order to provide the task-based scheduler greater opportunity for load-balancing. Currently, Intel TBB integrates load-balancing through task-queuing and work-stealing. Work stealing allows one to mask out any potential latencies attributed from a long running task, offering better load-balancing [12].

#### **2.1.4 OpenMP:**

OpenMP is an API for C/C++ and Fortran programmers enabling them to write parallel, shared-memory code for multiprocessor systems [18, 44]. Unlike task-based models such as Intel's TBB, OpenMP is a directive based parallel programming model: programmer's annotate parallel sections of the source code and leave implementation specific details up to the compiler (i.e. how to execute the annotated code in parallel). OpenMP is being adapted to extend support to heterogeneous multiprocessor systems such as the IBM Cell [45], and general purpose graphics processing units (GPGPUs) [65, 49]. However, it was becoming important to provide a standard set of directives for these accelerators. As a result, new emerging projects designed to naturally accommodate accelerators within the system such as GPUs include OpenACC [2] and OpenHMPP [22].

One of the dynamic properties of OpenMP (and its derivatives) can be found in its support for dynamic threading. When dynamic threading is disabled, the OpenMP greedily creates the maximum amount of threads when parallel code regions are encountered. When dynamic threading is enabled however, the runtime can create a variable number of threads. Currently, the OpenMP standard does not automatically adjust this variable number based on the runtime environment and is up to the programmer to define this number. Therefore, dynamic as defined here simply means user-configurable as opposed to self-adaptable.

#### 2.1.5 Cilk/Cilk Plus:

Cilk is another directive-based programming model aimed at providing a reasonable ratio between user productivity and performance. Cilk (C) or Cilk Plus (C++) was designed to quickly and easily parallelize code for both general multi-core processors and processors with SIMD extensions/vector support. It achieves this through its simple code annotations all the while maintaining the serial nature of existing code bases programmers are familiar with. As with directive-based models, parallel regions must be explicitly annotated for use during compilation (and runtime). However, the user is relieved from deciding where such tasks will run in parallel. Intel's Cilk Plus shares similar scheduling policies with Intel's TBB: both take a greedy approach by assigning as many worker threads as possible throughout the system, and both support randomized work-stealing across all thread's double-ended queues (deques) to provide reasonable system load-balancing. Like Intel's TBB, Cilk Plus also does not support processor affinity and processors are assumed to be homogeneous.

#### 2.2 Programming Frameworks

Programming frameworks can be defined as a collection of software (libraries) that provides an environment in which one can program a targeted platform. Programming frameworks differ from programming languages in that they guide the user in using its software to craft the application;

programming languages can too, use existing software but the decision is at the programmer's discretion.

Since programming in these frameworks entails making heavy use of their Application Programming Interfaces (APIs), much of the implementation-specific details are abstracted. These types of frameworks can provide their own virtual memory hierarchies and communication protocols atop the existing hardware platform. Furthermore, programming frameworks enables compiler and programming language developers to target such frameworks. This provides an opportunity for programmers to utilize legacy languages to target platforms that wouldn't otherwise be supported on its own.

# **2.2.1 OpenCL:**

OpenCL is a portable/cross-platform parallel programming framework designed to aid programmers in directing computation across a range of heterogeneous computational devices [36, 53]. These devices are but not limited to CPUs, GPUs, digital signal processors (DSPs) and FPGAs. OpenCL can be used to exploit both TLP as well as DLP.

The execution model of OpenCL is similar to a task-based model however, OpenCL defines tasks as kernels. Instances of kernels assigned to devices are referred to as *work-items*, which are ultimately grouped into a *work-group*. Since OpenCL devices can contain many processing elements (PEs) such as a GPU or a multi-core CPU, workgroups are assigned to these devices where work-items are then computed individually on the processing elements (PEs) of that device.

Alongside its execution model, OpenCL adopts a memory model that consists of four types of memories: private, local, constant, and global. Private memory is reserved for each individual PE on the OpenCL device. For example, the private cache for each core in a multi-core CPU can be considered as private memory. Local memory is temporal memory that is shared amongst PEs within the device, but not globally accessible by other OpenCL devices. Constant and global memory are similar such that they are accessible by all OpenCL devices but differ in that constant

memory is a read-only memory.

OpenCL exposes both the execution model and memory model to the programmer. Through the use of OpenCL's application programming interfaces (APIs), the memory hierarchy in addition to the heterogeneity of the device is abstracted. This allows portable code to be generated, however it is still possible for OpenCL programs to be *tuned* to specific platforms. This is realized through explicit management of where computation should occur by the programmer. Although one can query each device to obtain optimal working data sizes, OpenCL does not support automatic inference of where best to assign such tasks and the associated data. Additionally, one must explicitly perform memory management. When queuing workloads across different OpenCL devices, one must take care to transfer data between the system's global memory and the device's local memories.

#### 2.2.2 Heterogeneous System Architecture:

The Heterogeneous System Architecture (HSA) [4] is a specification created to unify heterogeneous computing components and provide support for familiar programming models such as C++, C++ AMP, OpenCL, and OpenMP. HSA was created to address many of the existing challenges within heterogeneous systems, namely:

- Power consumption the opportunity of leveraging the heterogeneity to reduce power is becoming more important as devices become smaller.

- Scalable performance the accessibility of devices offering higher levels of computational throughput necessitates the performance to scale in order to warrant such device integrations.

- Programmer productivity avoid soliciting a high learning curve by providing a familiar programming model to maintain and/or increase programmer productivity (and program portability).

Program portability - the need to maintain program portability across heterogeneous systems to avoid rewriting code is important. Not doing so can negatively affect the programmer's productivity.

HSA was founded by the HSA Foundation, comprising of companies such as ARM, Qualcomm, AMD, and many others. Among them, AMD has demonstrated HSAs on their Accelerated processing units (APUs) consisting of both CPU and GPU, alternatively labelled as *latency compute unit* (LCU) and *throughput compute unit* (TCU) respectively. LCUs are a generalization of a CPU whereas TCUs can refer to GPGPUs and FPGAs. Traditionally, programming such devices required two disparate programming models. To remedy this, HSA foundation proposes a common intermediate representation referred to as the HSAIL, enabling high-level programming languages and compilers to target. The HSA also abstracts the distributed memory hierarchy that can arise from multiple heterogeneous devices. By adhering to the HSA specification, companies can enable programmers to leverage their devices in a very transparent and portable fashion. This is in contrast to more popular programming frameworks such as OpenCL, or CUDA by Nvidia [43], where the memory hierarchy is exposed and explicit memory management is required.

#### **2.2.3 PLASMA:**

The authors in [46] recognize the myriad of specialized accelerators and the differing programming models each brings to high-performance computing systems. As mentioned previously, this introduces distributive memory and heterogeneity, and requires the programmer to identify scenarios that warrants their use. Load-balancing and computation scheduling also presents a challenge in these systems where tasks can optionally execute on more general-purpose hardware (e.g. CPU). To address such problems, the authors propose a programming framework, referred to as PLASMA. The framework consists of an Intermediate Representation (IR) allowing existing legacy programming languages and tools to target the PLASMA platform, a compiler

supporting multiple device specific back-ends, and a runtime to manage computation throughout the system. The authors integrate static partitioning within their work; hand-partitioning computation across both a (multi-core) CPU and GPU. This partitioning does not take into account data-sizes and other runtime data that may affect scheduling. The authors mention that the runtime system can be replaced to handle said dynamic partitioning and scheduling.

#### 2.2.4 Dandelion:

Dandelion is a programming framework for distributed heterogeneous systems [48]. Users targeting the Dandelion system write code in the .NET LINQ framework. Dandelion then maps tasks from the user's source onto cluster machines, onto which those machines map work onto their heterogeneous resources: multi-core CPUs and GPUs. The inclusion of heterogeneous hardware, namely GPUs, in addition to distributed computing introduces varying programming models. To insulate the programmer from varying implementation-specific details, Dandelion includes three execution engines: a distributed cluster engine, a multi-core CPU engine, and a GPU engine. Each of these engines receives a data-flow graph dictating the order of computation and synchronization. Computation mapping begins at the cluster level to an available machine; followed by the machine level where computation is mapped to either the multi-core CPU or the GPU. Currently, the mapping to a CPU or GPU is determined offline. Furthermore, the Dandelion does not address resource availability and assumes each machine in the cluster is homogeneous with respect to one another.

#### 2.2.5 OpenCPI:

OpenCPI is a software framework whose programming model is component-based [34]. This programming model abstracts a computing resource or a collection of computing resources (e.g. millions of gates on an FPGA) as a component. The programming model, coupled with a well-defined interface between components enables application portability and component

interoperability. As a result, OpenCPI focuses on bringing component-based programming onto real-time systems where it is natural for components to be swapped in and out (e.g. aerospace and military grade applications). OpenCPI provides a middleware solution for targeting such heterogeneous systems that are composed of CPUs, FPGAs, DSPs, and other emerging technologies.

## 2.3 Runtime Systems

According to [10], runtime systems do what programming languages cannot. That is to say, runtime systems have the advantage of utilizing the available runtime variables and resolved data sizes during runtime. Programming languages cannot extract information and optimize the scheduling of work on information that is not yet available.

Runtime systems provides several core services for the program and can be viewed as an extension of the programming language itself. Core services can include but are not limited to operating system calls, exception handling, stack management, scheduling, and profiling. Due to this, the position of runtime systems provides an appropriate opportunity to insert additional self-aware services such as processor affinity discovery, and resource-aware scheduling. The related works that follow, exhibit this autonomous behavior but are able to provide a level of transparency a programming language alone cannot do. Note, runtime system and scheduler are used interchangeably throughout the remaining of this thesis. The scheduler exists alongside many other core services that the runtime can provide.

#### 2.3.1 Elastic Computing:

The elastic computing system (ECS) is a combination of a programming framework and profiling tools that currently targets desktop systems composed of CPUs, GPUs, and FPGAs. ECS aims at providing transparent, portable and adaptable computing [57, 58]. To achieve this, ECS utilizes a

function library that stores a collection of commonly used functions referred to as elastic functions. Elastic functions differ from traditional functions in that they include implementation decisions within themselves based on runtime data such as input data and (available) computing resources. This enables them to provide a level of transparency to the user without requiring them to specify implementation details within their code, hence rendering their application non-portable.

Unlike other works that specify a single implementation for a given function [39, 10], ECS designed the elastic function library to include multiple implementations for each function. This presents an opportunity for ECS to explore alternative implementations of a given function and provide the fastest implementation based on runtime parameters. For example, choosing between *insertion sort* and *quick sort* when the size of the data is small, or if an FPGA with bitonic sort is provided. Furthermore, ECS enables the user to provide suggestions when using elastic functions that could benefit the runtime on choosing the most appropriate implementation. For example, if the data is mostly sorted, it may be best to choose *insertion sort* as compared to randomly sorted data would profit the most using *quick sort*.

ECS identifies the appropriate implementation (and parallelization strategies) offline through a processor know as *implementation assessment*. Implementation assessment is performed at installation time of ECS, and stores empirical results that take any architecture effects such as memory bottlenecks, cache configurations, and interconnect architectures. To begin, ECS exhaustively samples for all combinations of computing resources, every implementation for every elastic function to build an implementation performance graph (IPG). IPGs are two-dimensional piecewise linear functions that given a work metric, an estimate of execution time is provided. Work metrics are an abstract representation of the amount of work/computation that will be incurred for the input parameter(s). For elastic functions that have a single input parameter, a mapping is made on assigning this parameter as the the work metric. For elastic functions composed of multiple parameters, the work metric should identify the subset

of parameters that affect the function's execution time. In both cases, the work metric is assumed to be statically defined by the one designing the specific *implementation* of an elastic function.

To avoid expensive comparisons during runtime when deciding which implementation to choose when the application invokes an elastic function, ECS additionally employs optimization planning. Optimization planning is performed at ECS installation time, after implementation assessment. It involves combining all IPGs for a particular elastic function, and creating a new graph that reflects the fastest implementation for varying regions of the work metric. This function performance graph (FPG) enables the runtime to lookup a single source of performance information, circumventing a possibly large overhead for navigating elastic functions that include numerous implementations. Additionally, ECS also employs work parallelization planning (WPP) that can use FPGs to determine how to effectively partition the elastic function across multiple computing resources. This enables ECS to intelligently distribute work amongst computing resources rather than greedily assigning work to all, possibly negatively affecting performance. This information is also collapsed into a single graph, referred to as the work parallelization graph (WPG) for fast lookups during runtime. However, WPP does not take into account resource contention and other affects that arises when multiple instances are executing, and it is assumed the performance remains the same as it would when one implementation is executing on a single resource.

While ECS presents many unique solutions on adaptable computing, ECS targeted platform does not revolve around reconfigurable computing. ECS does demonstrate the use of FPGAs, however, there is no documented support for partial reconfiguration. Additionally, ECS does not queue work to devices as ECS does not attempt to minimize the overall/absolute execution time of the application. Rather, ECS aims at providing the fastest execution time for a given task, relative to the current state of the system.

#### 2.3.2 Harmony:

Harmony is a collection of runtime services that provide dynamic inference of concurrency, application portability, application scalability, and efficient utilization of heterogeneous resources through dynamic partitioning [20]. Harmony provides a task-based programming model that directs users in creating *sequentially specified imperative programs*. That is, applications are specified as a sequence of control structures and compute kernels. This follows very similarly to StarPU discussed in Section 2.4.3, whose applications are also described as a task control-flow data graph. Meta-data is also supplied from the user (and can be supplied through compilers), which provides runtime data to infer concurrency from a sequentially written program without resorting to pragmas such as those found in OpenMP and OpenACC. Some of this meta-data includes read and write memory locations used to determine concurrency or anticipate data dependencies between compute kernels, a pointer to the next kernel which provides a more explicitly controlled dependency, a user provided function that enables the runtime to determine kernel complexity/estimate performance based on input-data, binary implementations for compute kernel for at least one architecture (similar to StarPU's codelet, or SPREAD's switchable threads), and more.

These dependency graphs are generated during runtime and in order to balance performance with the overhead of scheduling and the generation of these graphs, Harmony limits the size of the scheduling window or how many kernels it manages at any given time before adding more to the graph. Harmony also collapses multiple kernels into one on these dependency graphs to reduce the overhead of managing multiple kernels on the graph. This is done by using a kernel's estimated execution time. If it is found that the execution time is less than some threshold, the compute kernels are either combined with a previous kernel on the dependency graph or the next one dictated by program order. As a result of combining multiple compute kernels, it enables the system to schedule more compute kernels with less overhead.

To estimate performance for a given compute kernel, Harmony uses a combination of

logging historical execution latencies for that kernel on various hardware, and computing offline regressional models over such logged data and meta-data. Users can indicate through meta-data, which inputs do affect the complexity of the compute kernels. Harmony can then aggregate this data with latencies already recorded (historical execution times on different hardware) to form a multivariate regressional model. They also indicate that they can improve results further if the user additionally adds "user-supplied estimates" of kernel complexity. However, most of this discussion on performance monitoring and optimization in [21] does not provide sufficient detail as to how the authors used these regressional models and how much overhead it generates. Although they mention such techniques are possible for their runtime system, they ultimately do not demonstrate the use of input data and latencies to shape a performance curve with a multivariate regressional model.

# 2.3.3 Qilin:

The authors in [39] recognize the importance of heterogeneity and its advantages on today's multiprocessor systems. They also mention that in order to take advantage of this heterogeneity, efficient utilization is necessary. Their solution includes automatically mapping computation to a CPU and GPU configuration where most appropriately. This is done transparently to the user, giving way to provide portable and scalable code across different system configurations.

To begin, Qilin leverages two threading-based APIs: Intel TBB for scheduling parallel workloads onto CPUs and NVIDIA CUDA for (NVIDIA) GPUs. As a result, Qilin does not support heterogeneous processors. Qilin's programming model requires the programmer to explicitly write parallelizable code through Qilin's APIs. The rationale behind this is it alleviates the complexity of extracting parallelism from serial code, and instead can focus on performance tuning [39]. Qilin programs compute on two types of data: QArray and QArrayLists. QArrays are multidimensional arrays and QArrayLists are list of QArray objects. Qilin programs can be written with two sets of APIs: Stream-API and Threading-API. The Stream-API approach

includes utilizing common data-parallel functions (and overloaded operators) that exist within the Qilin library. A few examples include sqrt(), BLAS(), shift(), and sum(). Threading-API enables the user to provide their own function to execute on QArrays and QArrayLists. This is done by writing both Intel TBB code as well as NVIDIA CUDA code, providing a wrapper function that includes both source code, and then calling the wrapper function at runtime to bootstrap into either or both of them. Additionally, the user can annotate data as partitionable. This enables the runtime to automatically partition and merge the data across both the CPU and GPU.

Qilin contains an online compilation flow when targeting CPUs and GPUs. Qilin API calls are translated into TBB or CUDA source code, from which are then passed to the appropriate compiler during runtime. The motivation for online compilation is that it allows the final binary to reflect the current runtime environment and/or data sizes that are unknown offline. This also leverages the optimizations of the respective compilers when the input data is known. However, the authors do not provide further insight on runtime overhead for online compilation and how it affects performance.

Performance modelling on Qilin is similar to that of StarPU 2.4.3, a linear performance model is built from empirical runtime data collected overtime. For the current system configuration, Qilin additionally stores such data offline for later use. If there exists tasks within a program of which no stored data exist, Qilin first trains on the data. This is performed by first dividing the data in half, where half of the data is assigned to the CPU(s) and the other half for the GPU. Qilin further divides the data into m subparts on each of the two hardware, whose execution on those subparts are recorded and used to approximate performance for it. Additionally, the fraction of the amount of work assigned to the CPU,  $\beta$ , is also found by computing the intersection of both the CPU's and GPU's performance equation line. This is utilized in partitioning a single task across both types of hardware for better load balancing. If  $\beta \leq 0$ , the entire argument size is offloaded to the GPU. If  $\beta \geq 0$ , the CPU is given the entire argument size. The authors recognize that the computational throughput of the CPU and GPU working

cooperatively is assumed to be the same in cases where one works alone in the system (i.e. one is idle and the other is busy). The authors attempt to account for this but provide insufficient details on the chosen method.

# 2.4 Reconfigurable Systems

The purpose of this section is to provide the state of the art that addresses heterogeneity on reconfigurable systems. Much of what has been discussed earlier will apply here as well. Besides targeting a new platform, capabilities such as DPR enables these systems to dynamically change its hardware to that of which an application requires. This brings a challenge previous works mentioning support for FPGAs have not explored. While this flexibility can provide the hardware on-demand, having the capability does not dictate that one should always exploit it. The following works provides exploration on this front and highlights more of the ingrained challenges as a result of a reconfigurable platform.

# 2.4.1 AMAP:

With the increased densities of FPGAs, application designers have much more flexibility on where portions of their application can execute: either in hardware or software or both. The authors in [52] agree that deciding how to partition the application at compile time misses opportunities for runtime optimizations. This static partitioning can not maximize optimization based on unknown function parameter values. Furthermore, changes to the system's environment (e.g. power or resource availability) can further affect partitioning decisions. To address this, [52] introduces an adaptive mapping algorithm (AMAP) that dynamically partitions the application during runtime based on previous execution times. The authors argue that by deferring this decision as late as possible (ALAP), better partitioning results can be achieved over compile time techniques.

### **2.4.2 SPREAD:**

SPREAD is a partially reconfigurable and adaptable system, and programming model that targets streaming applications such as multimedia and cryptographic applications [56]. SPREAD's programming model is thread-based and the authors include support for hardware threads through a hardware thread interface (HTI). The HTI enables both hardware and software threads to coexist during runtime. Additionally, SPREAD supports reconfigurable point-to-point communication channels to facilitate the pipeline parallelism needed for streaming-based applications. Another optimization that is included is caching runtime partial reconfigurations in order to amortize runtime overhead and increase the reuse of dynamically allocated resources.

In addition to dynamic resource allocation for hardware threads and reconfigurable point-to-point streaming channels, SPREAD integrates runtime adaptability through the seamless switching between hardware and software threads. Like ReconOS [38], every hardware thread that is created has a software delegate thread referred to as a stub thread that can be used for hardware monitoring and data stream redirection. SPREAD additionally defines a switchable thread, which contains both hardware and software implementations for a given thread function. This enables hardware/software threads to fall-back to software/hardware based on the application's needs during runtime such as higher priority resource allocation. However, these software implementation threads are limited only to a single processor, of which the OS resides on.

#### 2.4.3 StarPU:

When hardware accelerators are introduced into the system, a common approach towards utilizing it is to offload *all* work tuned for that device. Many programming models support this approach as discussed in Section 2.1. The authors in [10], believe that scheduling tasks across the entire system rather than simply offloading (and queuing) them all to a predetermined accelerator

provides greater benefit in terms of performance as well as mitigating *dark silicon* [24]: a term used to describe the increasing inefficiency of a system due to underutilization of components. Their solution is a runtime system called StarPU, which targets both numerical kernel libraries and parallel programming languages. Additionally, StarPU presents a task-level programming model, where the user writes the implementation of tasks and describe any dependencies between them. To enable execution of these tasks on any device, StarPU uses *codelets* which are containers for including multiple device-specific binary implementations for the given task. StarPU also does not require explicit marshalling of data similar to OpenCL. StarPU relieves this explicit memory management as the runtime ultimately has control of determining where best to schedule the task. Other transparent optimizations include data prefetching, and employing a write-back policy (delaying writes back to memory, thus localizing the data).

The authors of StarPU make further argument that a single scheduling policy does not suffice for all applications and believe that the runtime should be flexible to allow multiple scheduling policies to be utilized. To accommodate multiple scheduling strategies between the runtime system and the heterogeneous resources, the authors make use of queues. When the application submits tasks to be scheduled, tasks may be enqueued/dequeued from a single FIFO (e.g. greedy policy) or multiple dedicated FIFOs (e.g. work-stealing policy). Much of the analysis uses the heterogeneous earliest finishing time (HEFT) policy. The HEFT scheduling policy tries to minimize the completion time for the system by summing both pending tasks and the new task's estimated execution times for all hardware resources. This can naturally lead to the scheduling of certain tasks onto heterogeneous resources that demonstrate an affinity for such tasks (provided the data granularity is ideal for that resource). In order to demonstrate this, the authors estimate task completion time dynamically online through performance (and data) modelling [9].

Modelling the performance of tasks by hand can be tedious as it requires detailed knowledge of both architecture and algorithm. This is further exacerbated for a system with much heterogeneity. Pre-calibrating performance models through benchmarking suites also does not

present a viable solution as it does not represent a realistic workload, does not take into account the dynamic behavior of the system, or both. The authors decided on a history-based approach, where actual performance data is captured and referenced during runtime for the benefit of scheduling future scheduled tasks. The authors do assume some regularity hypothesis in many algorithms utilized *fixed sizes of data*, *or limited sets of data*. Execution information for a given kernel and hardware are stored and referenced in their respective online tables. The parameters to a given kernel pass through a hash function that ultimately generates an index into the tables. The authors claim this history-based approach is a simpler than multivariate performance models that distinguish table entries for data sizes such as a  $1024 \times 50$  matrix vs. a  $50 \times 1024$  matrix.

#### 2.4.4 CaaS: