# $\frac{\textbf{ISTANBUL TECHNICAL UNIVERSITY} \bigstar \textbf{GRADUATE SCHOOL OF SCIENCE}}{\textbf{ENGINEERING AND TECHNOLOGY}}$

# 8-BIT 1 GS/S ADC ARCHITECTURE AND 4-BIT FLASH ADC FOR +10 GS/S TIME INTERLEAVED ADC IN 65nm CMOS TECHNOLOGY

#### M.Sc. THESIS

## Alper AKDİKMEN

**Department of Electronics and Communications Engineering**

**Electronics Engineering Program**

# $\frac{\text{ISTANBUL TECHNICAL UNIVERSITY} \star \text{GRADUATE SCHOOL OF SCIENCE}}{\text{ENGINEERING AND TECHNOLOGY}}$

# 8-BIT 1 GS/S ADC ARCHITECTURE AND 4-BIT FLASH ADC FOR +10 GS/S TIME INTERLEAVED ADC IN 65nm CMOS TECHNOLOGY

M.Sc. THESIS

Alper AKDİKMEN (504121385)

Department of Electronics and Communication Engineering

Electronics Engineering Program

Thesis Advisor: Prof. Dr. Müştak Erhan YALÇIN

**OCTOBER 2015**

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ</u> ★ FEN BİLİMLERİ ENSTİTÜSÜ

## +10 GS/S ZAMAN ARALIKLI ADC İÇİN 65nm CMOS TEKNOLOJİSİNDE 8-BIT 1 GS/S ADC YAPISI VE 4-BIT FLASH ADC

### YÜKSEK LİSANS TEZİ

Alper AKDİKMEN (504121385)

Elektronik ve Haberleşme Mühendisliği Anabilim Dalı Elektronik Mühendisliği Programı

Tez Danışmanı: Prof. Dr. Müştak Erhan YALÇIN

Alper AKDİKMEN, a M.Sc. student of ITU Graduate School of Science Engineering and Technology 504121385, successfully defended the thesis entitled "8-BIT 1 GS/S ADC ARCHITECTURE AND 4-BIT FLASH ADC FOR +10 GS/S TIME INTERLEAVED ADC IN 65nm CMOS TECHNOLOGY", which he prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor: | <b>Prof. Dr. Müştak Erhan YALÇIN</b> Istanbul Technical University |      |

|-----------------|--------------------------------------------------------------------|------|

| Jury Members:   | Assist. Prof. Dr. Tufan Coşkun KAR Istanbul Technical University   | ALAR |

|                 | <b>Prof. Dr. Günhan DÜNDAR</b> Bogazici University                 |      |

Date of Submission: 8 October 2015 Date of Defense: 16 October 2015

To my family and friends,

### **FOREWORD**

This thesis work was done on my Erasmus+ Program Exchange Student period in Integrated Microsystems Laboratory (IMS) of University of Pavia under the supervision of Prof. Dr. Franco MALOBERTI as a collaborated project with his PhD candidate Dante Gabriel MURATORE. I would like to thank my advisor Prof. Franco MALOBERTI for his invaluable support and inspiration. I'm thankful to Dante MURATORE for being such a nice colleague. I would like to thank the members of the Integrated Microsystems Laboratory in Pavia, especially to Edoardo BONIZZONI, for their invaluable support in a year's period.

I'm grateful to Prof. Müştak Erhan YALÇIN for accepting to be my supervisor in ITU. I am also grateful to the members of ITU VLSI Labs for their support especially for the first half of my master studies. Last but not least, I'm grateful to Prof. Türker KÜYEL for his great contribution to my involvement in this area.

I dedicate this work, like all my achievements in this life, to my parents İzzet AKDİKMEN and Kadriye AKDİKMEN.

October 2015

Alper AKDİKMEN (Electronics Engineer)

# **TABLE OF CONTENTS**

|                                                                   | <b>Page</b> |

|-------------------------------------------------------------------|-------------|

| FOREWORD                                                          | ix          |

| TABLE OF CONTENTS                                                 |             |

| ABBREVIATIONS                                                     |             |

| LIST OF TABLES                                                    |             |

| LIST OF FIGURES                                                   |             |

| SUMMARY                                                           |             |

| ÖZET                                                              |             |

| 1. INTRODUCTION                                                   |             |

| 1.1 Thesis Motivation                                             |             |

| 1.2 Thesis Organization                                           |             |

| 2. TIME INTERLEAVED ADC ARCHITECTURES                             | 5           |

| 2.1 Introduction                                                  |             |

| 2.2 Time Interleaving Advantages and Disadvantages                | 5           |

| 2.3 Time Interleaving Errors.                                     |             |

| 2.3.1 Offset mismatch                                             | 7           |

| 2.3.2 Gain mismatch                                               |             |

| 2.3.3 Timing mismatch.                                            |             |

| 2.4 Existing Solutions to Time Interleaving Errors                |             |

| 2.5 Proposed Technique to Diminish the Effects of Timing Mismatch |             |

| 2.6 Behavioral Simulation Results                                 |             |

| 2.7 Implementation Considerations                                 | 13          |

| 3. SINGLE CHANNEL HIGH SPEED ADCS                                 | 17          |

| 3.1 Architectures                                                 | 17          |

| 3.2 Proposed Architecture                                         | 18          |

| 3.2.1 Search algorithm                                            | 18          |

| 3.2.2 ADC structure                                               | 22          |

| 3.2.3 Multiple threshold generating preamp                        | 24          |

| 4. COMPARATORS FOR HIGH SPEED ADCS                                | 27          |

| 4.1 Comparator Architectures                                      | 27          |

| 4.1.1 Dynamic latches                                             | 28          |

| 4.2 Preamplifiers                                                 | 31          |

| 4.3 Dynamic Latch with Embedded Preamp                            | 33          |

| 4.3.1 Speed                                                       | 33          |

| 4.3.2 Offset                                                      |             |

| 4.3.3 Kickback noise                                              | 35          |

| 4.3.4 Power consumption                                           |             |

| 4.4 Simulation Results                                            | 37          |

| 4.4.1 Speed                                                       |             |

| 4.4.2 Offset                                                      | 40          |

| 4.4.3 Kickback noise                                              |             |

| 4.4.4 Power consumption                                           |             |

| 5. DESIGN, LAYOUT AND CHARACTERIZATION OF CIRCUIT                 | BLOCKS      |

| FOR THE SINGLE CHANNEL ADC                                        | 49          |

| 5.1 Design of the Bootstrapped Sampling Switch                    | 49          |

| 5.2 Design of the Flash ADC                                       |             |

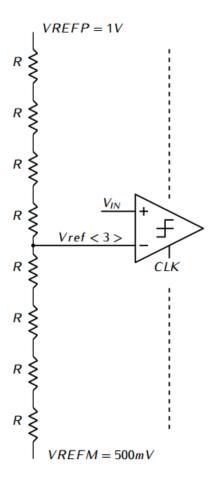

| 5.2.1 Resistor ladder                                             | 53          |

| 5.2.2 Comparators                              | 53 |

|------------------------------------------------|----|

| 5.2.3 Reference voltage sampling               | 57 |

| 5.3 Layouts Of The Designed Blocks             | 61 |

| 5.3.1 Bootstrapped switch                      | 61 |

| 5.3.2 Comparator                               |    |

| 5.3.3 Flash ADC                                | 63 |

| 5.4 Post-Layout Simulations                    | 67 |

| 5.4.1 Comparator                               | 67 |

| 5.4.2 Flash ADC                                | 67 |

| 5.4.3 Bootstrapped switch                      | 70 |

| 5.5 Overall Simulations                        | 70 |

| 5.6 Floorplan and Layout of Single Channel ADC | 73 |

| 6. CONCLUSIONS AND RECOMMENDATIONS             | 75 |

| REFERENCES                                     | 77 |

| APPENDICES                                     | 81 |

| CURRICULUM VITAE                               | 91 |

### **ABBREVIATIONS**

**ADC** : Analog to Digital Converter : Digital to Analog Converter **DAC DNL** : Differential Non-Linearity **ENOB** : Effective Number of Bits : Giga Bit per Second Gbps : Giga Sample per Second GS/s : Integral Non-Linearity INL : Least Significant Bit **LSB** : Most Significant Bit **MSB**

**SAR** : Successive Approximation Register

**SDR** : Software Defined Radio

**SFDR** : Spurious Free Dynamic Range

**SNR** : Signal to Noise Ratio

# LIST OF TABLES

|                                                                   | <b>Page</b> |

|-------------------------------------------------------------------|-------------|

| Table 4.1: RMS power consumption of the comparator architectures. | 47          |

| Table 5.1: Layout sizes of blocks.                                | 61          |

# LIST OF FIGURES

|                                                                                                                                                      | <b>Page</b> |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| Figure 1.1: Generic software radio receiver front-end [1].                                                                                           | 1           |

| Figure 1.2: ADC-based serial I/O receiver [2].                                                                                                       |             |

| Figure 2.1: Time interleaved ADC operation principle.                                                                                                |             |

| Figure 2.2: SNR versus input frequency graph of errors in a TI-ADC from [5]                                                                          |             |

| Figure 2.3: Ideal sine wave, sine wave with offset mismatch and error signal                                                                         |             |

| Figure 2.4: DFT of sine wave with offset mismatch in TI-ADC.                                                                                         |             |

| Figure 2.5: Ideal sine wave, sine wave with gain mismatch and error signal                                                                           |             |

|                                                                                                                                                      |             |

| Figure 2.6: DFT of sine wave with gain mismatch in TI-ADC.                                                                                           |             |

| Figure 2.7: Ideal sine wave, sine wave with timing mismatch and error signal                                                                         |             |

| Figure 2.8: DFT of sine wave with timing mismatch in TI-ADC.                                                                                         |             |

| Figure 2.9: Comparison of Regular TI-ADC (a) and TI-ADC with randomization                                                                           |             |

| (b)                                                                                                                                                  |             |

| <b>Figure 2.10:</b> Possible implementation of proposed technique.                                                                                   |             |

| Figure 2.11: Comparison of randomization sequence lengths: 16 (a) and 256 (b).                                                                       |             |

| Figure 2.12: Comparison of redundant channel number for 8-channel TI-ADC: 2                                                                          | ! (a)       |

| and 4 (b)                                                                                                                                            | 15          |

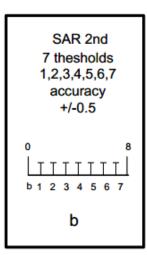

| Figure 3.1: Threshold placement in the proposed architecture.                                                                                        | 20          |

| Figure 3.2: Proposed ADC architecture.                                                                                                               |             |

| Figure 3.3: Timing arrangement of the proposed ADC architecture                                                                                      |             |

| <b>Figure 3.4:</b> Example of proposed searching path: (a) correct, (b) with decision                                                                |             |

| errors.                                                                                                                                              | 23          |

| Figure 3.5: Multiple threshold generating preamplifier.                                                                                              |             |

| Figure 3.6: Input DC sweep of multiple threshold generating preamplifier                                                                             |             |

| Figure 3.7: Improved multiple threshold generating amplifier                                                                                         |             |

|                                                                                                                                                      |             |

| Figure 4.1: Conventional dynamic sense amplifier latch.                                                                                              |             |

| Figure 4.2: Double-tail configuration dynamic latch.                                                                                                 |             |

| <b>Figure 4.3:</b> Modified dynamic sense amplifier latch.                                                                                           |             |

| Figure 4.4: Basic preamplifier schematic.                                                                                                            |             |

| Figure 4.5: Preamplifier with diode-connected load.                                                                                                  |             |

| <b>Figure 4.6:</b> Preamplifier with regenerative loop.                                                                                              |             |

| <b>Figure 4.7:</b> Proposed latch with embedded preamp.                                                                                              | 34          |

| Figure 4.8: Kickback noise mechanism in conventional sense amplifier latch                                                                           | 36          |

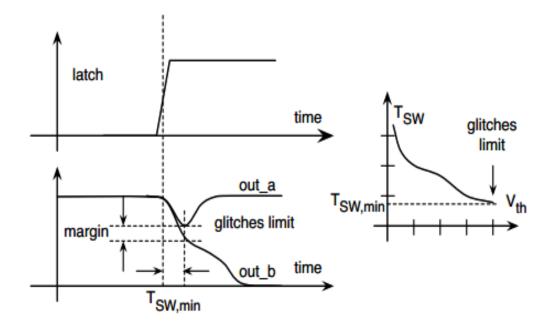

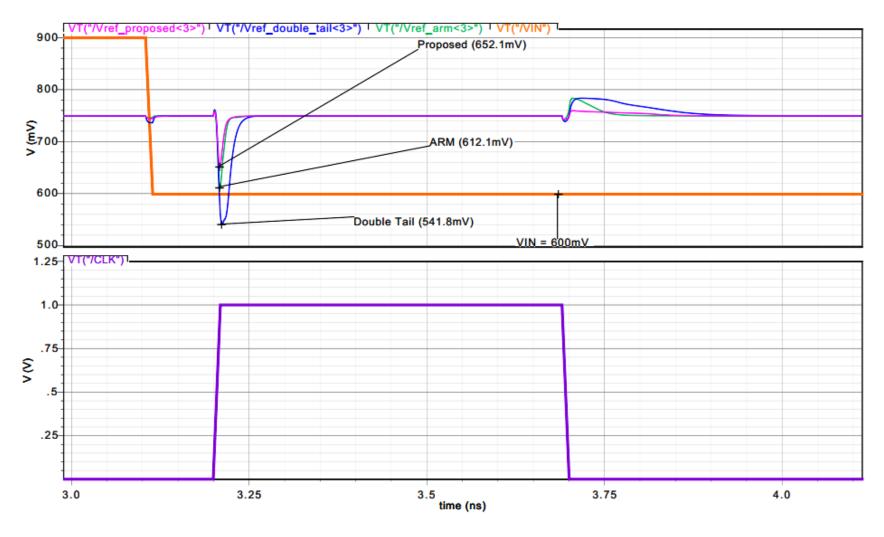

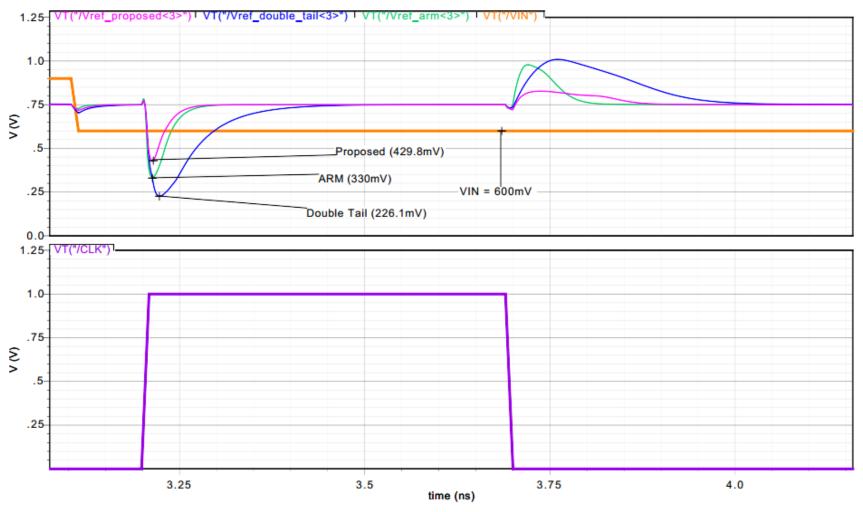

| Figure 4.9: Waveforms at the output of the latch for switching time definition                                                                       | 38          |

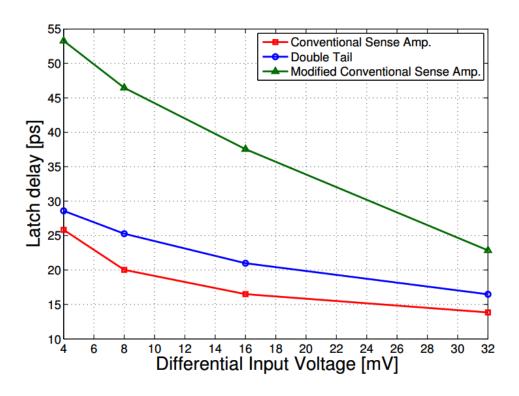

| <b>Figure 4.10:</b> Latch regeneration time comparison of conventional comparator                                                                    |             |

| architectures                                                                                                                                        | 39          |

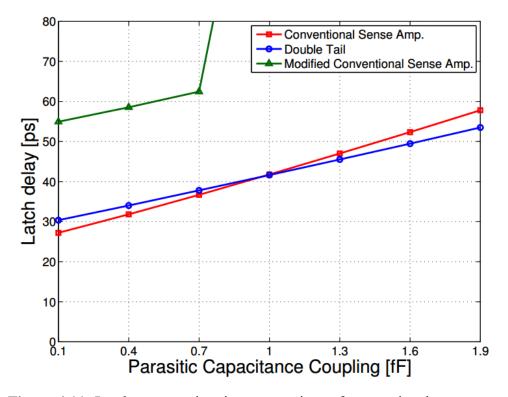

| <b>Figure 4.11:</b> Latch regeneration time comparison of conventional comparator                                                                    |             |

| architectures in case of capacitive coupling between outputs                                                                                         | 39          |

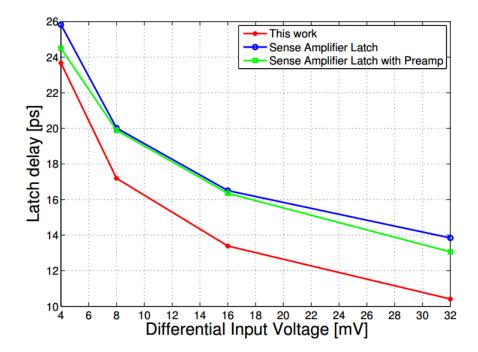

| <b>Figure 4.12:</b> Latch time comparison of proposed latch, SA latch and SA latch                                                                   |             |

| preceded by preamp.                                                                                                                                  | 40          |

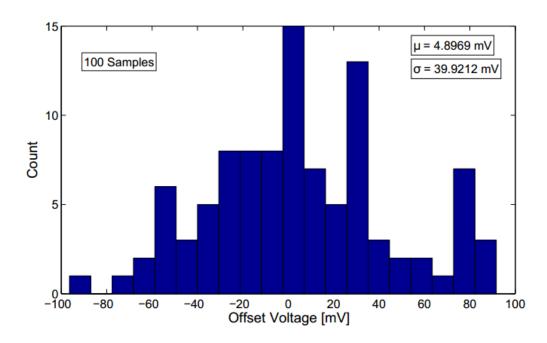

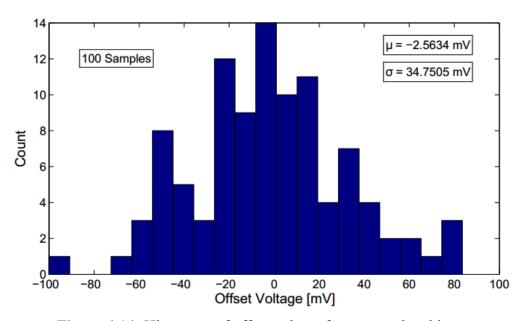

| <b>Figure 4.13:</b> Histogram of offset voltage for conventional sense amplifier                                                                     | • 0         |

| architecture.                                                                                                                                        | <b>41</b>   |

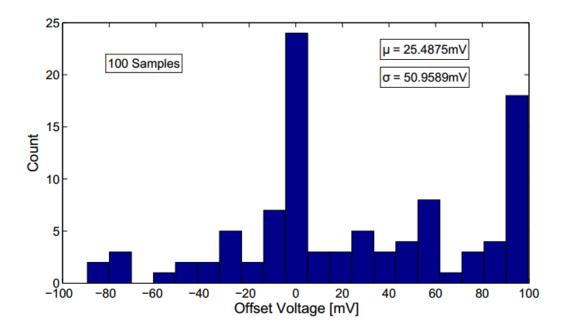

| Figure 4.14: Histogram of offset voltage for proposed architecture.                                                                                  |             |

|                                                                                                                                                      |             |

| Figure 4.15: Histogram of offset voltage for double tail architecture.                                                                               |             |

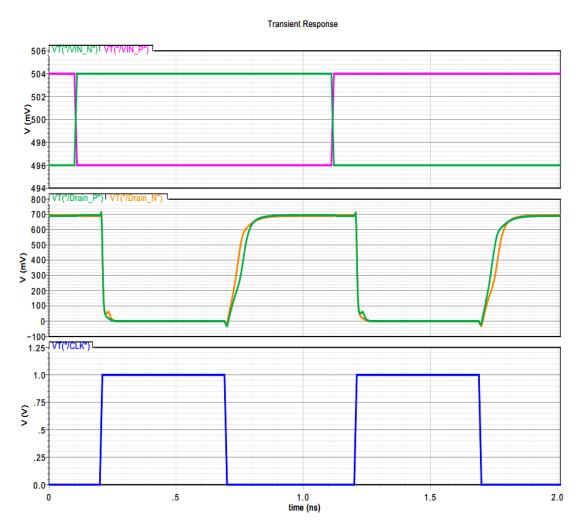

| Figure 4.16: Transients of input differential pair drain nodes for proposed latch.                                                                   |             |

| <b>Figure 4.17:</b> Test bench used in kickback noise simulations. <b>Figure 4.18:</b> Kickback noise for reference ladder unit resistance of 100 O. |             |

| <b>FIGURE 4.16:</b> Nickback hoise for reference ladder limit resistance of 100 O                                                                    | 47          |

| <b>Figure 4.19:</b> Kickback noise for reference ladder unit resistance of 1 k $\Omega$ .         | . 46 |

|---------------------------------------------------------------------------------------------------|------|

| Figure 5.1: Bootstrapping principle.                                                              |      |

| Figure 5.2: Conventional bootstrapped switch circuit [26].                                        | 51   |

| Figure 5.3: Bootstrapped switch structure from [27].                                              | 52   |

| Figure 5.4: NMOS input comparator used in flash ADC.                                              | 54   |

| Figure 5.5: PMOS input comparator used in flash ADC                                               | 55   |

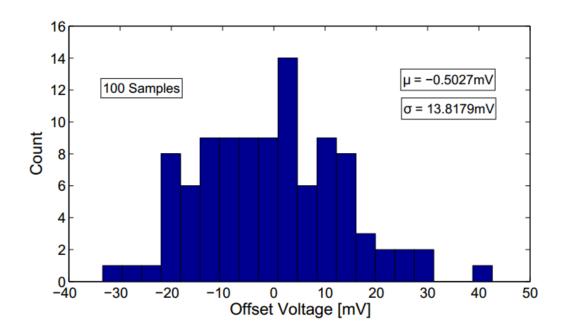

| Figure 5.6: Histogram of offset voltage for NMOS input comparator                                 | 55   |

| Figure 5.7: Histogram of offset voltage for PMOS input comparator.                                | 56   |

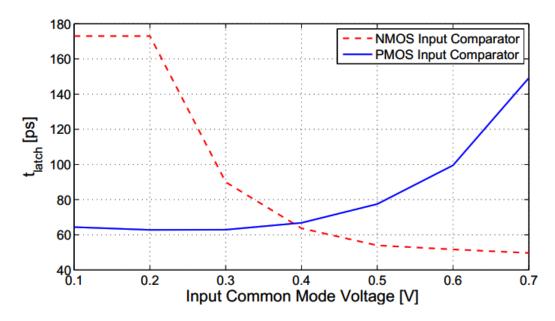

| Figure 5.8: Latch regeneration time versus input common mode voltage for NMC                      | S    |

| and PMOS input comparators with parasitics extracted                                              | 57   |

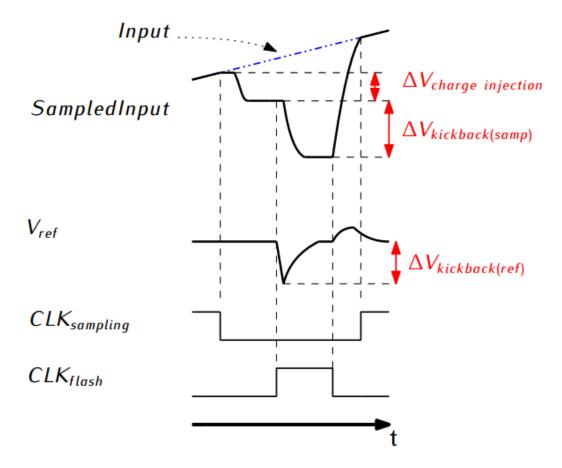

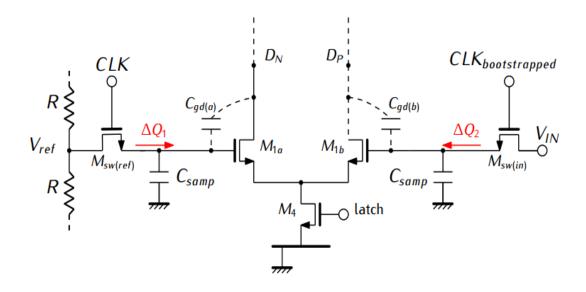

| Figure 5.9: Sampled input voltage and reference voltage waveforms in regular ca                   | se.  |

|                                                                                                   | 58   |

| Figure 5.10: Reference sampling approach.                                                         |      |

| Figure 5.11: Transient response of input sampling and reference sampling                          |      |

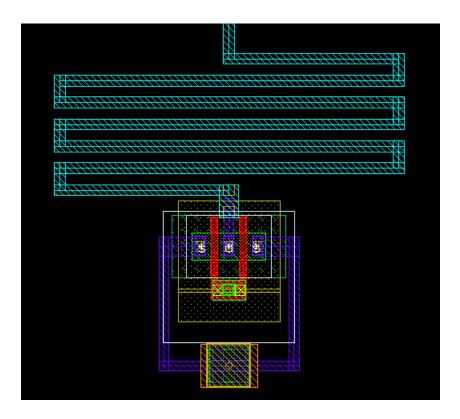

| Figure 5.12: Layout of bootstrap voltage generator.                                               |      |

| Figure 5.13: Layout arrangements in comparator layouts.                                           |      |

| Figure 5.14: Layout of NMOS input comparator.                                                     |      |

| Figure 5.15: Layout of PMOS input comparator.                                                     |      |

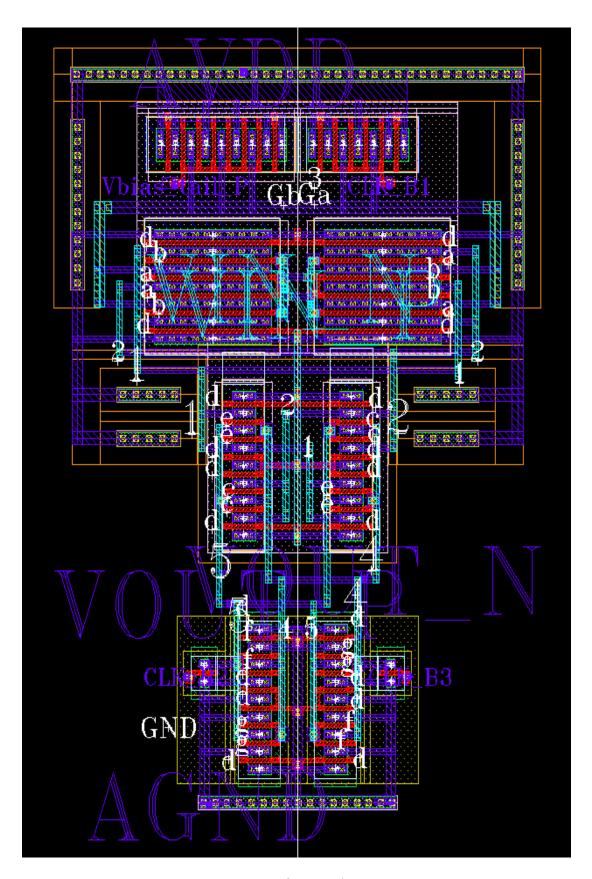

| <b>Figure 5.16:</b> Top-level layout of flash ADC.                                                | . 66 |

| <b>Figure 5.17:</b> Detail of flash ADC layout which shows serpent trace to equalize              |      |

| delays.                                                                                           | 67   |

| Figure 5.18: NMOS input comparator latch regeneration time comparison of                          |      |

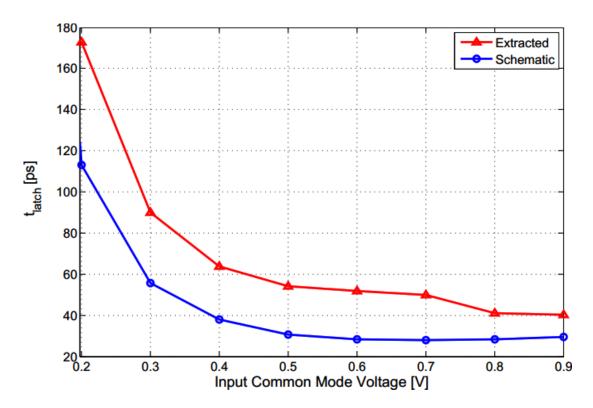

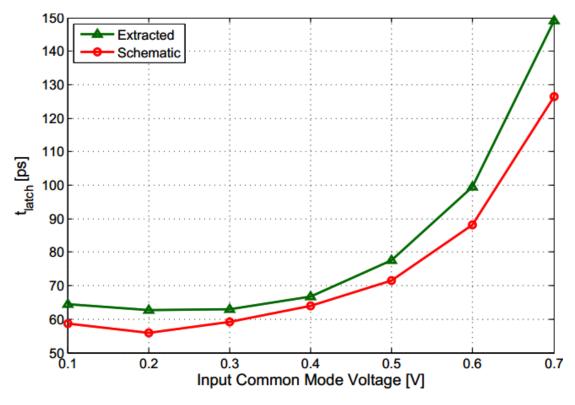

| schematic and post-layout ( $\Delta V_{in} = 4 \text{ mV}$ )                                      | . 68 |

| <b>Figure 5.19:</b> PMOS input comparator latch regeneration time comparison of                   |      |

| schematic and post-layout ( $\Delta V_{in} = 4 \text{ mV}$ )                                      |      |

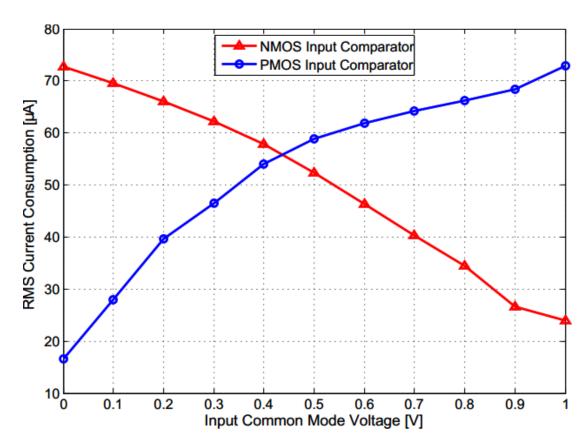

| Figure 5.20: RMS current consumption of comparators versus input common-mo                        |      |

| voltage                                                                                           |      |

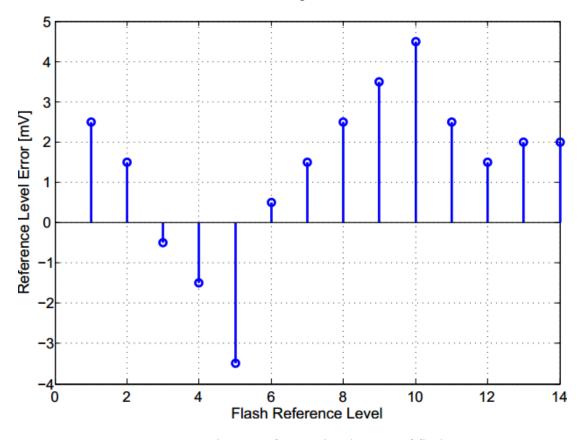

| <b>Figure 5.21:</b> Post-layout reference level errors of flash ADC.                              | . 69 |

| <b>Figure 5.22:</b> Post-layout waveforms of bootstrap voltage and input ( $f_{in} = 468.8$       |      |

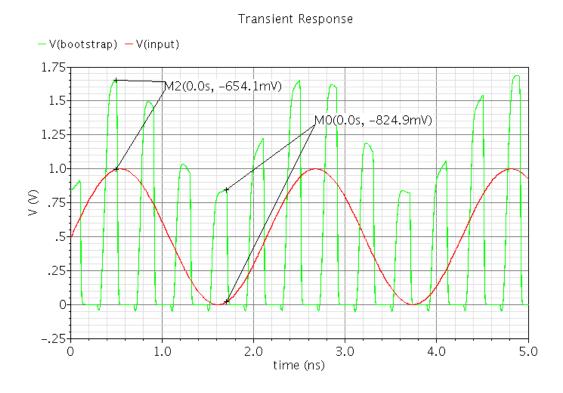

| MHz)                                                                                              |      |

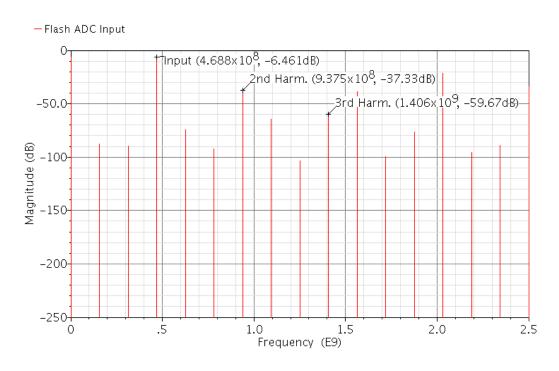

| Figure 5.23: Post-layout DFT of flash ADC input ( $f_{in} = 468.8$ MHz, single-ended)             |      |

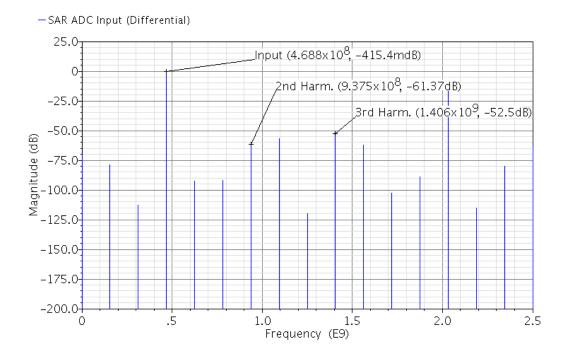

| <b>Figure 5.24:</b> Post-layout DFT of SAR ADC input (f <sub>in</sub> = 468.8 MHz, differential). |      |

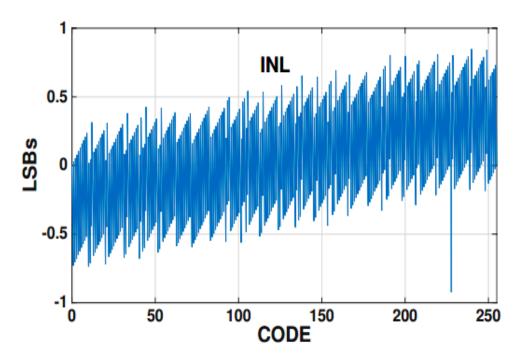

| Figure 5.25: INL graph of the overall single channel ADC.                                         |      |

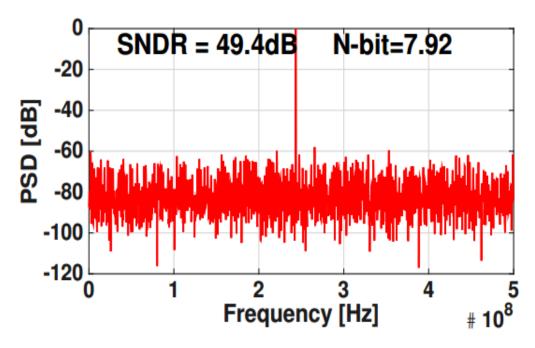

| <b>Figure 5.26:</b> Output DFT of the overall single channel ADC ( $f_{in}$ = 243 MHz, $f_{s}$ =  |      |

| GHz).                                                                                             |      |

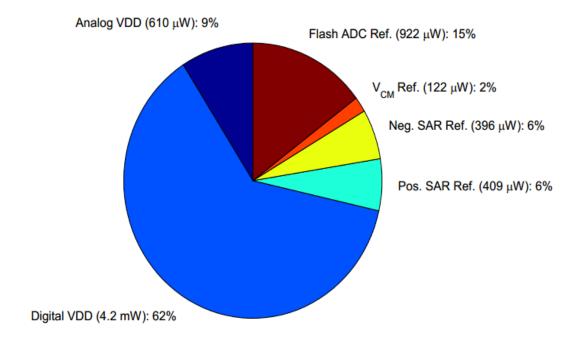

| Figure 5.27: Power consumption distribution of single channel ADC.                                |      |

| Figure 5.28: Floorplan of the ADC core                                                            |      |

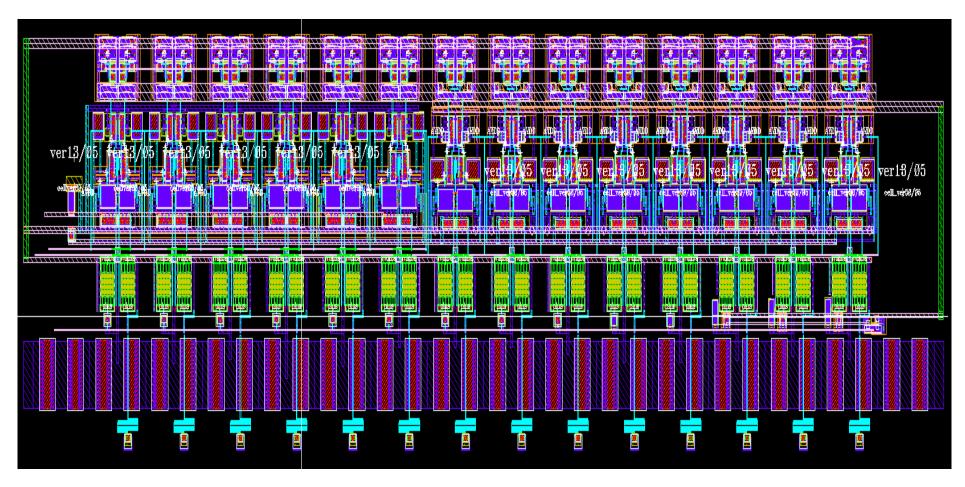

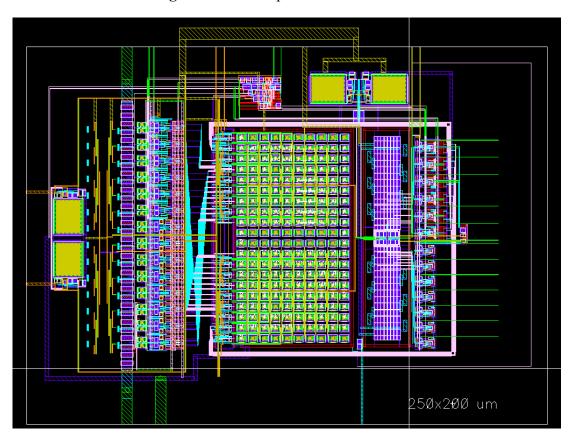

| <b>Figure 5.29:</b> Top-level layout of ADC core.                                                 | 74   |

# 8-BIT 1 GS/S ADC ARCHITECTURE AND 4-BIT FLASH ADC FOR 10+ GS/S TIME INTERLEAVED ADC IN 65nm CMOS TECHNOLOGY

#### **SUMMARY**

Data rate of communication systems constantly increasing. Rapid scaling of digital semiconductor technologies has moved the signal processing of these systems to digital domain. Therefore high-speed ADCs are required to form the bridge to take the analog signals in digital domain.

Data rates exceeding 10 Gbps makes the use of single channel ADCs unfeasible on this purpose. A power efficient solution is time-interleaving. Time-interleaving relaxes the speed requirements on single channel ADCs and lets designers to focus on power efficiency of the ADC.

Channel mismatches in time-interleaved ADCs causes performance degradation. Errors arise mainly due to offset, gain and timing mismatch of channels. Among them, timing error is the most problematic since estimation of timing errors becomes more cumbersome in high-frequencies.

Estimation and correction of timing errors in time-interleaved ADCs are hot topics of research. Calibration of errors can be on background or on foreground. Background calibration is more desirable since it allows system to adapt to changing conditions while not hindering the operation of the ADC.

Time interleaving errors generate spurs on the spectrum. Spurs are problematic for the wireless communication systems, since they may block the input signal. In order to extinguish the spurs a channel randomization technique is proposed. Technique is based on randomly taking one of the ADC channels to make the errors of the channels noise-like term. It is advantageous since it works on background. Technique maintains a spur-free spectrum however does not improve the SNR of the system.

Estimation of channel mismatch errors and clock distribution in a time-interleaved ADC becomes tedious as the number of channels increase. In order to keep the channel number low, channels should be fast while being power efficient. To satisfy this task, an 8-bit 1 GS/s multi-bit per cycle ADC is proposed. ADC employs a

novel search algorithm based on redundancy. No calibration scheme required thanks to the algorithm therefore the power efficiency of the system can be increased. In order to realize the multi-bit per cycle structure, a multiple-threshold generation preamp is proposed.

Comparators are the most important part of an ADC. Comparator specifications such as speed, accuracy and power consumption directly affect the relative specifications of the whole ADC. A novel latch with embedded preamp is proposed. Novel structure has latch regeneration time, offset, power consumption and kickback noise improvements over the conventional structures.

8-bit 1 GS/s multi-bit per cycle SAR ADC employs a flash ADC to perform the coarse conversion benefit from its speed. Although flash ADCs are fast, offset and kickback noise of comparators can penalize their accuracy. Proposed latch with embedded preamp improves the offset performance. To solve the kickback issue, reference voltages of the flash ADC are sampled. This technique is based on equalizing the kickback for both input and reference voltages therefore eliminating the effect.

Sampling network of the ADC is critically important since any error made in the sampling phase directly passes to the ADC. Bootstrapped switches are used to improve the linearity of the switches. By using bootstrap switches, charge injection can be made signal independent. If it is combined with the reference sampling technique used in flash ADC, effects of charge injection can be diminished significantly.

ADC blocks are designed and laid out in ST Microlectronics 65 nm process. Post-layout simulations have proven the efectiveness of the proposed techniques and blocks. Tape-out was done in July 2015. Measurements is expected to take place in November 2015.

## 10+ GS/S ZAMAN ARALIKLI ADC İÇİN 65nm CMOS TEKNOLOJİSİNDE 8-BIT 1 GS/S ADC YAPISI VE 4-BIT FLASH ADC

#### ÖZET

Haberleşme sistemlerinin veri aktarım sıklıkları ve bant genişlikleri sürekli olarak artmaktadır. Sayısal yarıiletken teknolojilerindeki gelişmeler, haberleşme sistemlerindeki işaret işleme kısımlarını sayısal domenine almıştır. Sayısal işaret işlemenin avantajları, ideal olmayan durumlara yüksek tolerans, gerçekleme kolaylığı, bir fonksiyonu gerçeklemek için gereken alanın dolayısıyla maliyetin düşük olması ve yeni teknolojilere taşınabilme olarak sayılabilir. Bu avantajlardan faydalanmak için analog işaretleri sayısal domene almada köprü görevi görecek yüksek hızlı analog-sayısal dönüştürücülere(ADC) ihtiyaç vardır.

Kablolu ve kablosuz haberleşme teknolojilerinde 10 GHz'yi de aşan bant genişlikleri tek kanallı ADCleri bu iş için elverişsiz kılmaktadır. Zaman aralıklı ADCler gerek ulaşabilecekleri dönüştürme hızı gerek güç verimliliği açısından iyi bir aday olarak karşımıza çıkar. Zaman aralıklama, tek kanallı eş ADClerin sıra ile kullanılması esasına dayanmaktadır. Sıradaki örneği alan ADC, sıra tekrar kendisine gelene kadar bu örneği dönüştürür. Dolayısıyla toplam dönüştürme hızı, tek bir dönüştürücünün hızı ile kanal sayısının çarpımı kadar olmaktadır. Bu şekilde yüksek dönüştürme hızları elde edilebilir. Ayrıca bu şekilde tek kanal ADCler daha fazla hız elde etmek için güç bakımından verimsiz oldukları noktalara itilmez ve daha verimli yapılar ortaya çıkar.

Zaman aralıklı ADClerdeki kanal uyumsuzlukları performansı düşürmektedir. Bu hatalar temel olarak dengesizlik, kazanç ve zamanlama uyumsuzluklarından ileri gelmektedir. Zamanlama hataları kestirilmeleri ve düzeltilmeleri noktasında diğerlerinden daha zorludur ve bu durum yüksek frekanslarda daha da zorlaşmaktadır.

Zaman aralıklı ADClerdeki zamanlama hatalarının kestirilmeleri ve düzeltilmeleri güncel bir araştırma konusu teşkil etmektedir. Hataların kalibrasyonu ön planda veya arka planda yapılabilir. Arka planda yapılan kalibrasyon sistemin işlerliği ile ilgili

herhangi bir sıkıntı yaratmaması ve değişen çevre şartlarına uyum sağlayabilme esnekliği açısından daha avantajlıdır.

Zaman aralıklama hataları frekans spektrumunda çıkıntılar(spur) oluşturmaktadır. Bu çıkıntılar, güçlü olmaları durumunda alıcı kısmındaki devreleri sıkıştırma noktasına iterek modülasyonlu işaretlerin sezilmesini zorlaştırabilir veya giriş işaretini tamamen engelleyebilirler. Dolayısıyla kanal uyumsuzluk hataları özellikle kablosuz haberleşme sistemleri için sorun teşkil etmektedir. Bu sorunlardan kurtulmak için kanalları rastgele kullanmaya dayanan bir teknik önerilmiştir. Bu teknik ile kanallardan kaynaklanan hatalar çıkışa rastgele bir sırayla etki yaptıklarından gürültü gibi bir karaktere geçerler. Dolayısıyla frekans spektrumundaki çıkıntılar söndürülmüş olur. Tekniğin bir diğer avantajı arka planda çalışmasıdır. Ancak dikkat edilmelidir ki bu teknik bir hata düzeltme tekniği değildir, dolayısıyla sistemin işaretgürültü oranını iyileştirmemektedir.

Kanal uyumsuzluk hatalarının kestirilmesi gibi, saat işaretlerinin dağıtılması da artan kanal sayısı ile zorlaşmaktadır. Ayrıca yüksek kanal sayısına sahip olan zaman aralıklı ADClerde saat işareti dağıtımının tükettiği güç yüksek seviyelere ulaşabilir. Belli bir dönüştürme hızı için kanal sayısını düşük tutmak ise kanal ADClerinin dönüştürme hızlarını arttırmak ile mümkündür. ADClerin hızları yüksek tutulurken aynı zamanda güç verimliliği de yüksek tutulmalıdır. Bu hedefler doğrultusunda 8-bit 1 GS/s bir çevrimde birden fazla bit dönüştüren bir SAR ADC yapısı önerilmiştir. Bir çevrimde birden fazla bit dönüştüren SAR ADCler, tek kanalda yüksek hızlara çıkmak konusunda sıkça kullanılan bir yöntem olarak karşımıza çıkmaktadır. Bunun yanında ilk üç en anlamlı bit bir flash ADC ile dönüştürüldüğünden önemli hız kazanımları elde edilir. Flash ADC çıkışında bir kod çözücü yapısı kullanılmaması da zaman kazanımında etkilidir.

Önerilen ADC yapısında özgün bir dönüştürme algoritması kullanılmaktadır. Algoritma temel olarak, dönüştürme fazlarına fazladan seviyeler eklemek ve fazların aralıklarını kesiştirmek sureti ile devre bloklarının hata toleranslarını arttırmasına dayanmaktadır. Bu nedenle herhangi bir kalibrasyon sistemine ihtiyaç duyulmaz dolayısıyla güç tüketimi azaltılabilir. Bu yapının gerçeklenebilmesi için çoklu seviye üreten bir ön kuvvetlendirici önerilmiştir. Önerilen ön kuvvetlendirici yapısı nedeniyle, algoritmadaki farklı fazlar için tek bir ön kuvvetlendirici kullanılabilmektedir. Bu sayede farklı ön kuvvetlendiricilerden kaynaklanacak dengesizlik uyumsuzluklarının da önüne geçilmiş olur.

Yüksek hızlı veri dönüştürücülerin gerçeklenmesindeki en etkili devre bloğu, kendisi de 1 bitlik bir ADC olarak sayılabilecek karşılaştırıcı devreleridir. Karşılaştırıcı devresinin hızı, doğruluğu ve güç tüketimi bir ADCnin ilgili performans parametrelerini doğrudan etkilemektedir. Yüksek karşılaştırıma hızlı özgün bir gömülü ön kuvvetlendiricili karşılaştırıcı devre önerilmiştir. Yapı geleneksel dinamik sezme kuvvetlendiricisi devresi temel alınarak tasarlanmıştır. Ek olarak giriş farksal kuvvetlendirici bölümüne bir statik akım kaynağı bağlanmıştır. Bu şekilde dinamik karşılaştırıcı yapısına ön kuvvetlendirici gömülmüş olur. Yapı geleneksel yapılara nazaran, hız, dengesizlik, güç tüketimi ve geri tepme gürültüsü açısından iyileştirmeler içermektedir.

8-bit 1 GS/s bir çevrimde birden fazla bit dönüştüren SAR ADC yapısı, ilk 3 biti olabildiğince hızlı dönüştürmek için bir flash ADC yapısı kullanmaktadır. Flash ADC yapılarının önemli hız avantajlarına rağmen, karşılaştırıcı devrelerin dengesizlik ve geri tepme gürültüsü performansı düşürmektedir. Önerilen gömülü ön kuvvetlendiricili karşılaştırıcı devresi dengesizlik performansını ve geri tepme gürültüsünü iyileştirmektedir. Ancak geri tepme gürültüsünden kaynaklanan hataları tam olarak çözmek adına, referans gerilimleri de giriş işaretleri gibi örneklenebilir. Bu teknik ile karşılaştırıcı geri tepme gürültüsünün giriş ve referans gerilimi üzerindeki etkisi eşitlenmekte ve geri tepme gürültüsünün etkisi bertaraf edilmektedir.

ADC girişleri örneklenerek geldiğinden ve örnekleme devrelerindeki bir hata doğrudan ADCye iletileceğinden bu devrelerin performansı çok önemlidir. Çapraz bağlamalı anahtar tekniği kullanılarak anahtarların doğrusallığı iyileştirilmiştir. Aynı zamanda çapraz bağlama tekniği anahtar yük enjeksiyonu hatasını giriş işaretinden bağımsız hale getirmektedir. Bu durum, yukarıda bahsedilen referans örnekleme tekniği ile birleştirildiğinde flash ADC için önemli bir doğruluk iyileştirmesi sağlamaktadır.

ADC blokları ST Microelectronics 65 nm CMOS teknolojisinde tasarlanmış ve serimleri yapılmıştır. Serim sonrası benzetim sonuçları tasarımların ve kullanılan tekniklerin doğruluğunu göstermektedir. Tasarlanan ADC Haziran 2015'de üretime yollanmıştır. Kasım 2015'de ölçümlere başlanması planlanmaktadır.

#### 1. INTRODUCTION

Communication systems are one of the main driving force behind the electronics industry. Advent of the semiconductor process technologies has paved the way for higher data rates in those systems. Therefore, not only wireless communication systems but also wireline communication systems should satisfy the speed demands while being accurate enough and power efficient.

Digital process technologies scale faster than analog, which shifted the bulk of the signal processing to the digital domain. Communication systems benefit from that approach too. In order to process high data rate signals on digital domain, high-speed ADCs are crucial.

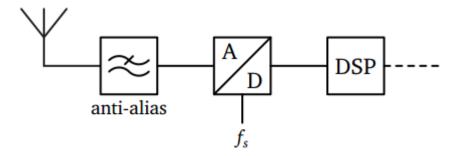

**Figure 1.1:** Generic software radio receiver front-end [1].

High-speed ADCs are present on software radio front-ends. Generic software radio structure is shown in Figure 1.1. The principle of software radio is to sample the RF input as close as possible to the antenna. In ideal case, the input is sampled right after the anti-aliasing filter following the antenna so that the operations such as demodulation, down-conversion can be done in digital domain. However as stated in [1], this approach is not currently realizable. Nevertheless, since it will allow easily realizable and portable multi-standard receiver and transceiver architectures, software radio concept is appealing and relies on high-speed, high-performance ADC architectures.

High-speed ADCs take part in wireline communication front-ends too. Wireline communication channels suffer from non-idealities such as channel loss, reflections and cross-talk. In order to overcome these effects complex equalization techniques are required which can be effectively realized with ADC-based receivers which is shown in Figure 1.2. As stated in [2], "the advantages of such ADC-based receiver include: better programmability and extensibility to different channel characteristics; better equalization robustness to process and coefficient variations; possibility of using more powerful signal processing techniques such as sequence detection to achieve lower BER; and potential of adopting complex modulation schemes beyond binary PAM".

Figure 1.2: ADC-based serial I/O receiver [2].

With the data rates exceeding 10 Gbps, single channel ADCs are not able to provide a power efficient solution for these demands, which calls for time-interleaved ADCs which achieve tens of GS/s sampling rates with power efficiency in low-medium resolution.

### 1.1 Thesis Motivation

Interferers should be problematic for communication systems, especially for wireless. This makes spurs in the frequency spectra important. Time-interleaving errors cause spurs in the spectra. Therefore time-interleaved ADCs benefit from a technique, which decreases the magnitude of spurs. Hence in this thesis, studies of such a technique have been done.

Time interleaving is a power efficient solution for high-speed conversion demands of communication systems. However, calibration techniques used in single-channel

ADCs may diminish the efficiency gained by time interleaving. Therefore time-interleaved ADCs benefit from, single-channel ADCs based on search algorithms, which do not require calibration. In addition, channel number of a time-interleaved ADC should be kept low in order to maintain a power-efficient and non-complex clock distribution and to keep estimation and calibration of channel mismatch errors affordable. This calls for fast single-channel ADCs. Hence, in this thesis an 8-bit 1 GS/s single channel ADC architecture is studied and designed to be used in a +10GS/s time-interleaved ADC.

#### 1.2 Thesis Organization

The organization of the thesis is as follows:

Chapter 2 explains the fundamentals of time interleaved ADCs and errors stem from channel mismatches. A technique to diminish the channel mismatch effects on SFDR is proposed.

Chapter 3 includes an overview of single-channel ADCs in state-of-the-art time-interleaved ADCs. Then a 8-bit multi-bit per cycle 1 GS/s single-channel ADC is proposed which combines a novel searching algorithm based on redundancy and novel multiple-threshold generation preamplifier.

Chapter 4 includes an overview of comparators used in state-of-the-art ADCs and main comparator specifications. Then a novel comparator architecture is proposed which embeds the preamplifier in latch. Comparison of novel architecture with conventional structures is presented and its advantages are explained.

Chapter 5 explains the design of comparators, flash ADC and bootstrapped switch to be used in the single-channel ADC. Layouts of the blocks are shown and results of post-layout simulations are presented in order to show the accuracy of design. Top-level layout as well as overall post-layout simulations of single-channel ADC is presented too.

Chapter 6 concludes the thesis and possible future work based on the thesis.

#### 2. TIME INTERLEAVED ADC ARCHITECTURES

#### 2.1 Introduction

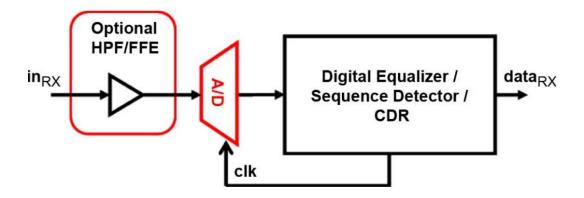

Time interleaved ADC (TI-ADC) [3] is power efficient response to the demand for high-speed ADCs where technology limits the efficiency of a single channel ADC. Basic principle of operation and timing diagram are shown in Figure 2.1 for an n-bit, N channel time interleaved ADC. Whole ADC consists of N n-bit single channel ADCs (slices) which operate concurrently. Input is sampled with a frequency of  $f_S = (1/Ts)$  which is also the aggregate frequency of overall ADC. Sampled inputs are fed into one of the ADCs in a row. Therefore, each ADC has an operating frequency of  $f_S / N$ . When one of the slices finishes the conversion, its output is picked by a multiplexer and is given to output.

Following sections explain the advantages and disadvantages of time-interleaved architectures and interleaving errors due to the mismatches between channels. Then some of the existing solutions to these errors are summarized. In the end, a technique to diminish the effects of timing mismatch error is presented and design considerations over this architecture are discussed.

#### 2.2 Time Interleaving Advantages and Disadvantages

Time interleaving offers several advantages over their single channel counterparts in terms of maximum speed, power consumption and metastability. Ideally, the overall speed can be increased just by increasing the channel number. As stated in [4], "Interleaving improves the FOM because, as the conversion speed of a single channel approaches the limits of the technology, the power-speed tradeoff becomes nonlinear, demanding a disproportionately higher power for a desired increase in speed". Interleaved ADC channels operate in slower frequencies in which they could be designed more power efficient. Since power consumption in dynamic circuits is proportional to operating frequency, clocking network benefit from slower operation

as well. Finally, metastability errors are reduced due to longer clock period of each channel so that comparators have more time to make a decision.

Time interleaving has disadvantages as well such as area penalty; complex clock distribution and channel mismatch errors. These errors are main factors, which limits the number of channels in a TI-ADC. More detailed explanation of channel mismatch errors are given in following sections.

Figure 2.1: Time interleaved ADC operation principle.

### 2.3 Time Interleaving Errors

Offset, gain and timing mismatches of channels in a time-interleaved ADC are main factors, which limit the overall resolution of the ADC. Following sections explain main characteristics of those errors.

In order to observe the error patterns of mismatch errors in TI-ADCs and their effects on frequency domain, a behavioral TI-ADC model is created and shown in Appendix A. Model creates a sine wave whose points are picked concurrently, such as in TI-ADC, from non-ideal sine waves created with relative errors. For all the cases,  $f_s = 10$  GHz and  $f_{in} = 127$  MHz.

#### 2.3.1 Offset mismatch

Considering different DC offsets of the ADC channels in a TI-ADC, during the concurrent operation, those offsets produce static errors with a frequency of  $(f_s / N)$ . As DC offsets are independent from input frequency and amplitude, this errors as well frequency and amplitude independent. As stated in [5], offset errors produce spurs at:

$$f_{noise} = k (f_s / N), \qquad k = 1,2,3,...$$

(2.1)

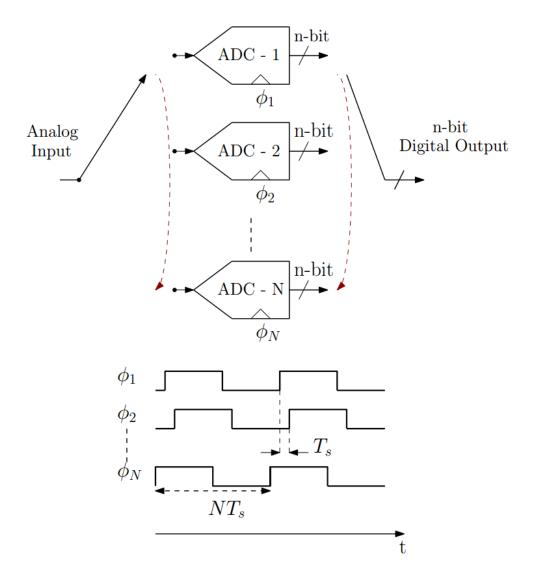

SNR versus input frequency graph of a TI-ADC with only offset error is shown in Figure 2.2. This graph again shows that input frequency does not affect the SNR in presence of offset mismatch.

**Figure 2.2:** SNR versus input frequency graph of errors in a TI-ADC from [5].

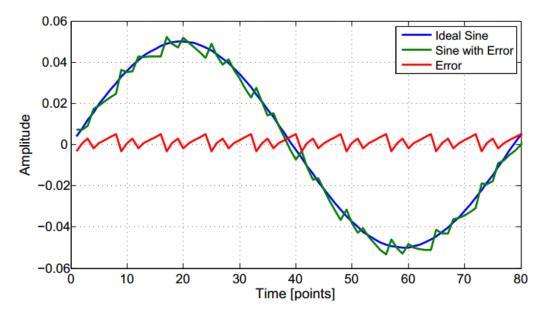

For N=8, effects of offset mismatch in time-domain and frequency-domain is observed via TI-ADC model in MATLAB. Peak amplitude of sine wave is picked as

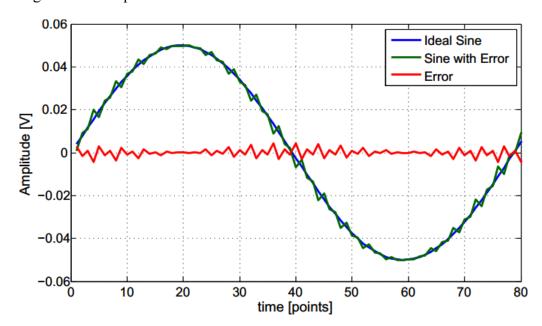

0.06 V and random offset errors with standard deviation of 4 mV were assigned to channels. Results in time-domain are shown in Figure 2.3. Note that, error has a constant envelope, which shows that the offset mismatch is amplitude independent. Frequency-domain results are shown in Figure 2.4. As anticipated, spurs due to offset mismatch appeared on  $(f_s/8) = 0.125 f_s$ ,  $2(f_s/8) = 0.25 f_s$  and so on.

Figure 2.3: Ideal sine wave, sine wave with offset mismatch and error signal.

Figure 2.4: DFT of sine wave with offset mismatch in TI-ADC.

#### 2.3.2 Gain mismatch

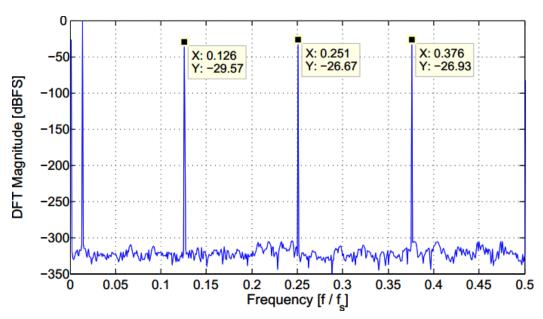

In order to observe effects of offset mismatch, non-ideal gain values were created with a standard deviation of 5%.

Figure 2.5: Ideal sine wave, sine wave with gain mismatch and error signal.

As shown in Figure 2.2, gain mismatch error does not depend on input frequency just like offset mismatch. However, as shown in Figure 2.5, error is low on zero-crossings meanwhile it increases close to the peaks of sine wave. Therefore, it can be said that gain mismatch error changes with input amplitude.

Figure 2.6: DFT of sine wave with gain mismatch in TI-ADC.

As stated in [5], spurs due to gain mismatch appear at:

$$f_{noise} = k (f_s / N), \qquad k = 1,2,3,...$$

(2.2)

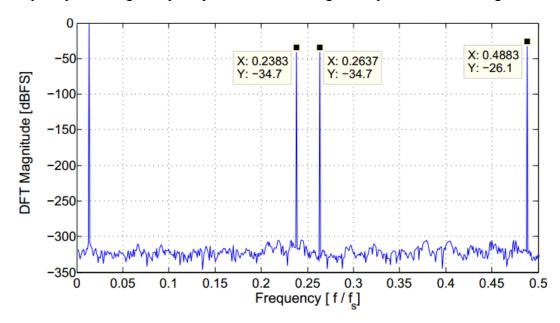

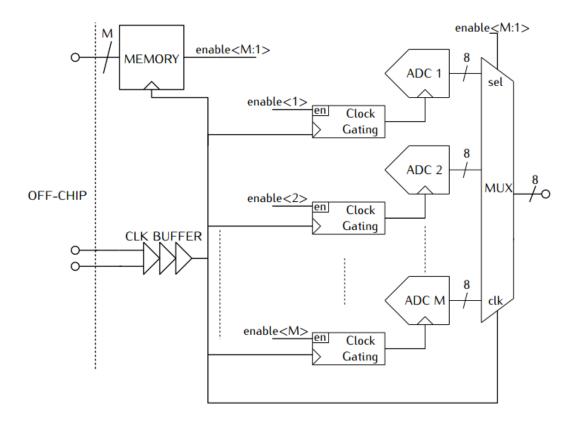

Effects of gain mismatch on frequency domain observed for N = 4. Frequency-domain results are shown in Figure 2.6. As expected for Equation 2.2, spurs appeared approximately at 0.0127 + 0.25 = 0.2627, (-0.0127) + 0.25 = 0.2373 and so on.

### 2.3.3 Timing mismatch

Proper clocking is one of the most challenging parts in of TI-ADC design. Timing errors in a TI-ADC can be random or systematic. Random timing error is jitter, which is unavoidable in practical cases. However, system can be made tolerant to jitter by the design. Systematic part of timing errors stems from the clock skew mismatch of channels. Those errors are much harder to estimate and correct compared to offset mismatch and gain mismatch. It is shown in Figure 2.2, degradation due to timing mismatch increases with input frequency, which makes timing errors more problematic.

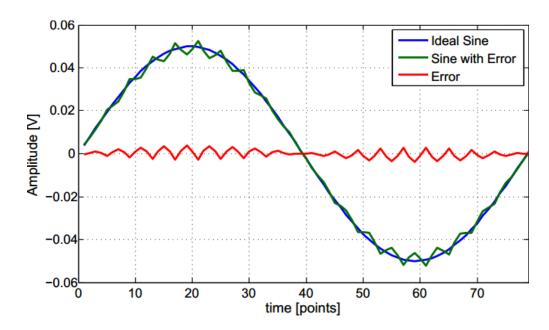

Figure 2.7: Ideal sine wave, sine wave with timing mismatch and error signal.

As stated in [5], spurs due to timing mismatch appear at:

$$f_{noise} = \pm f_{in} + \frac{k}{N} f_s, \qquad k = 1, 2, 3, ...$$

(2.3)

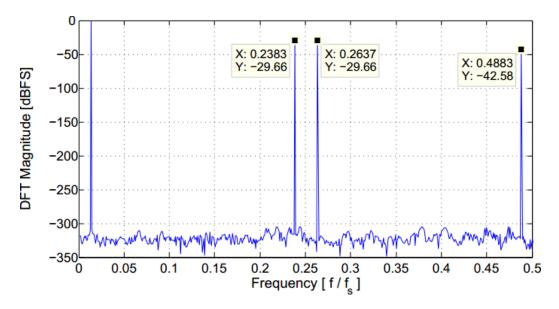

In order to observe the effects of timing mismatch on time and frequency domain, for N = 4, random timing skews were created with standard deviation of 100 ps and were assigned to channels. Figure 2.7 shows the time domain errors. Note that error increases on zero-crossings. Zero crossings are where the slope of the sine wave is at

its highest. This explains the performance degradation with increasing input frequency since high frequency sine waves has higher slope on zero-crossings.

Figure 2.8: DFT of sine wave with timing mismatch in TI-ADC.

Effects of timing mismatch on frequency domain are shown in Figure 2.8. As expected from Equation 2.3, spurs appeared approximately at (0.0127 + 0.25 = 0.2627), (-0.0127 + 0.25 = 0.2373) and so on.

# 2.4 Existing Solutions to Time Interleaving Errors

Recent literature shows an increasing effort on solutions to timing mismatch errors in a TI-ADC since it is problematic to both estimate and correct. Two types of estimation and correction are present, namely background and foreground. During foreground estimation and correction, ADC is offline. A time is allocated to calibration, which can be problematic for some applications. On the contrary, for background estimation and calibration, the work is done on the fly. This type is more suitable for adapting the frequently changing conditions.

Correction approach is mostly similar considering a digitally controlled delay line is employed for most of the cases. However, estimation techniques are still a popular research topic. This section gives few examples from recent literature to solve the timing mismatch errors for TI-ADCs with conversion speed of 10 GS/s and more.

One approach is employing a master track-and-hold circuit [6]. In this approach, timing errors are prevented since there is only one clock signal needed for the master

track-and-hold, which eliminates any clock skew. The samples are distributed to the channels after they are sampled. Although it is a simple and effective solution, designing a track-and-hold circuit with a wide bandwidth is highly challenging. In [7], an on-chip sinusoidal test signal is generated on-chip and fed to each ADC channel. Subsequently, digital outputs are processed off-chip to decide on the correction values. A disadvantage of this approach is that it is foreground. In [8], errors are statistically estimated. In [9], timing skews are estimated by employing feed forward equalizers. In [10] an embedded time-to-digital converter is used to estimate the mismatch. All of the last three techniques are background calibration techniques.

## 2.5 Proposed Technique to Diminish the Effects of Timing Mismatch

Increasing conversion rates make dynamic specifications of ADCs much more prominent. Among them, Spurious Free Dynamic Range (SFDR), is defined in [11] as "the ratio of the root-mean-square signal amplitude to the root-mean-square value of the highest spurious spectral component in the first Nyquist zone".

SFDR is especially important for communication systems. Higher data rates makes the communication bands crowded and this make filtering of interferer signals cumbersome. If the SFDR is low for the ADC in the receiver side, spurs due to the strong interferer on the antenna may block the input signal itself.

In Section 2.3, it has shown that the time interleaving errors cause spurs in frequency spectrum, whose amplitudes can be significantly high. Although high data rate communication systems benefit from the significant speed advantage of TI-ADCs, spurs due to interleaving errors may be problematic for those systems.

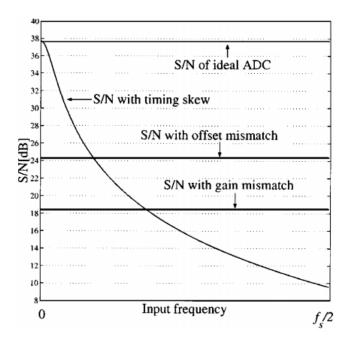

Instead of estimation and correction approaches in Section 2.4, an approach just to diminish the effect of spurs may be taken. In order to achieve this, an approach called dynamic element matching, like proposed in [12] for DACs, can be adopted. As stated in [11], "The goal of the approach is to equal the elements on average instead of performing a static correction of the values". Principle of operation is as follows: Each ADC channel is selected randomly to convert the next sample. In this way, periodic nature of mismatch errors explained in Section 2.3 is no longer valid. Therefore, spurs are extinguished and the power of mismatch errors is spread across

frequency like in the case of quantization noise. This technique is a background method, which makes it appealing. An important point is that, since there is no error correction, signal-to-noise ratio (SNR) of the system does not increase with the technique.

#### 2.6 Behavioral Simulation Results

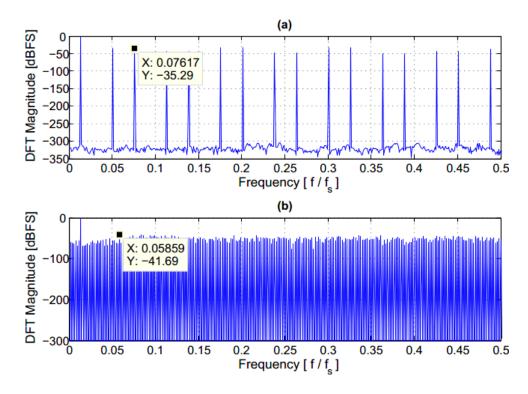

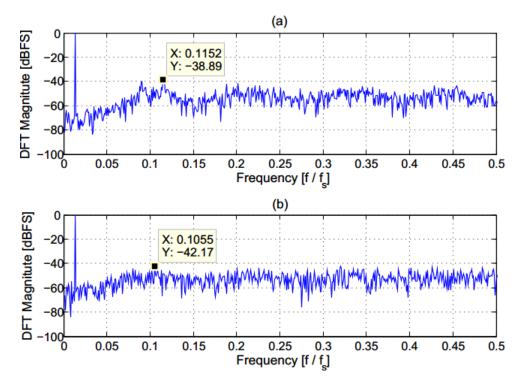

Behavioral model is used for showing the effectiveness of the technique. Again, random timing skews were created with standard deviation of 100 ps and assigned to 8-channel regular TI-ADC and 12-channel TI-ADC with 8 main and 4 redundant channels. Comparison of two cases was given in Figure 2.9. Note that an SFDR improvement of 8 dB.

**Figure 2.9:** Comparison of Regular TI-ADC (a) and TI-ADC with randomization (b).

# 2.7 Implementation Considerations

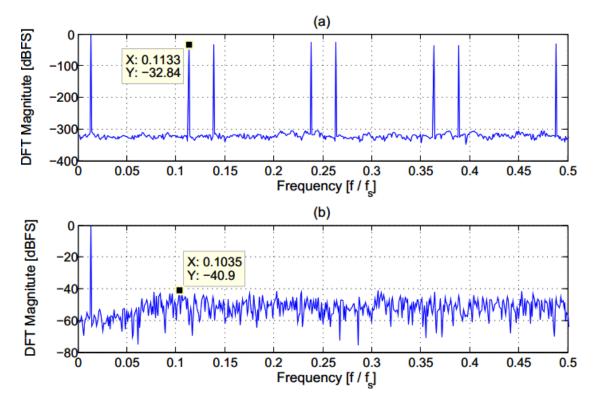

Possible implementation of the technique is depicted in Figure 2.10. Here M = N + R where N denotes the total main channel number and R denotes the number of redundant channels.

Figure 2.10: Possible implementation of proposed technique.

Main point where the implementation diverges from the theory is the impossibility of generating true random sequences. Pseudo-random sequences with finite length can be generated with circuits. Therefore, the sequence should be kept as long as possible.

Second issue arises due to the operation principle of TI-ADCs. A channel picked for conversion is not going to be ready to be picked for the next (N/fs) seconds. Therefore, the sequence should be generated keeping this point in mind, which makes the regular pseudo-random number generating circuits not available for this purpose.

Considering aforementioned issues, generating the sequence off-chip and writing it on an on-chip memory is a good solution for implementing the technique. Memory size should be chosen for the minimum sequence length, which improves the SFDR significantly.

In order to show the effect of the sequence length, random sequences with the lengths of 16 and 256 are generated and used on the behavioral model on MATLAB. Results are shown in Figure 2.11. Note that increasing the sequence length to 256 from 16 improves the SFDR performance by 6.4 dB.

Figure 2.11: Comparison of randomization sequence lengths: 16 (a) and 256 (b).

**Figure 2.12:** Comparison of redundant channel number for 8-channel TI-ADC: 2 (a) and 4 (b).

Number of redundant channels is another important design consideration. Using more redundant channels makes randomization more effective since it reduces the probability of periodicity. In order to prove the point, randomization with infinite-length sequence is applied to TI-ADC models with 2 and 4 redundant channels.

Results are shown in Figure 2.12. Note that by using 4 redundant channels, 4 dB of SFDR improvement is achieved. However, there is an area and complexity and SFDR tradeoff for the number of redundant channels in this case. Therefore, the number of redundant channels must be considered carefully.

#### 3. SINGLE CHANNEL HIGH SPEED ADCS

Time-interleaved architectures provide an efficient solution to the speed - power consumption trade-off [4]. Ideally, the speed can be increased just by increasing the channel count. However as stated in the Chapter 2, offset, gain and timing mismatches between the interleaved ADC channels degrades the performance. Increasing the interleaving factor not only exacerbates the estimation and correction of the interleaving errors but also pushes the power consumption of the whole ADC far from the optimum. In addition, feasibility of the proposed technique mentioned in Section 2.5 depends on low interleaving factor since it relies on the redundant ADC channels. Therefore, it is more desirable to increase the speed of a single channel as much as possible in order to keep the interleaving factor low.

Following sections investigate the high-speed single channel ADCs used in state-of-the-art time interleaved ADCs and then proposes a novel single channel architecture suitable for 10 GS/s time interleaved ADC.

#### 3.1 Architectures

In order to achieve more than 10 GS/s with an interleaving factor which lets power efficient design, single channel ADCs should reach the speeds greater than 1 GS/s.

Flash ADC is a good candidate since it lends itself for whole conversion in a single clock cycle. An n-bit flash ADC requires  $[(2^n) - 1]$  comparators. Combined with reference generation and auxiliary circuits, this makes flash ADCs impractical for medium and high resolutions in terms of power consumption and area. In recent literature there are several +10 GS/s time-interleaved ADCs employing a flash ADC for single channel. For instance in [10], a 20 GS/s 6 bit time-interleaved ADC is presented. ADC employs 8-way interleaved 2.5 GS/s flash ADCs. In [8], a 12 GS/s 5-bit 8-channel time-interleaved architecture, which employs 1.5 GS /s flash ADCs, is presented. These examples prove the feasibility of flash ADCs for a single channel in low-resolution time-interleaved architectures.

SAR ADC is one of the commonly used ADC architecture in time-interleaved architectures with medium and high-resolution applications. As stated in [11], "the method aims to reduce the circuit complexity and power consumption using a low conversion rate by allowing one clock period per bit".

However, SAR ADCs resolve 1 bit at a time, which limits their speed. There are several approaches to circumvent this drawback. One of them is asynchronous successive approximation ADC [13]. As the name suggests, this type of SAR ADC does not employ a synchronous internal clock to proceed the approximations, periodic clock signal is only used for input sampling. Successive approximation algorithm suggests that, only one of the approximations falls into 0.5 LSB band of the input in which comparator is close to metastability. Therefore, except this metastable cycle, approximations will be faster. This makes the use of a synchronous clock whose period is adjusted for the worst case, unnecessary. In asynchronous SAR ADC, a ready signal is generated after resolving each bit to continue with the next one, which makes the whole conversion faster than the synchronous counterpart does. In [14], 90 GS/s 8 bit 64-way interleaved SAR ADC is presented. This ADC employs a 1.2 GS/s 8-bit asynchronous SAR ADC as a single channel.

One other approach to increase the speed of a single channel SAR is realized by resolving multi-bit per cycle. This approach is based on combining speed advantage of flash architecture and the energy efficiency of SAR architecture [15]. In [15], input is sampled on three identical SAR ADCs. Then in other phases, appropriate switches of these SAR are switched to generate reference voltages of 2-bit flash ADC. 3 comparators which are connected to those capacitive networks resolve 2-bits in each cycle.

# 3.2 Proposed Architecture

# 3.2.1 Search algorithm

As stated in previous section, SAR ADCs, which resolve multi-bit per cycle, can achieve considerably higher speeds compared to conventional SAR ADC architecture. A novel architecture, which combines multi-bit per cycle and redundancy to achieve 8-bit and 1GS/s, is presented.

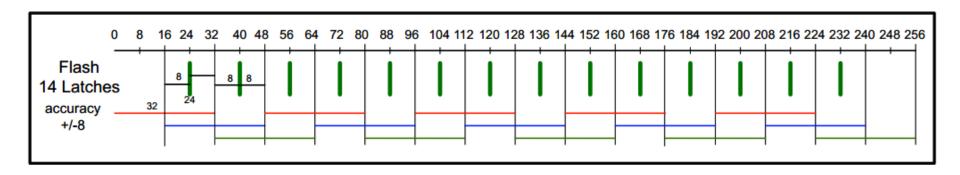

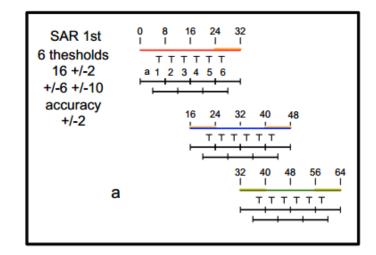

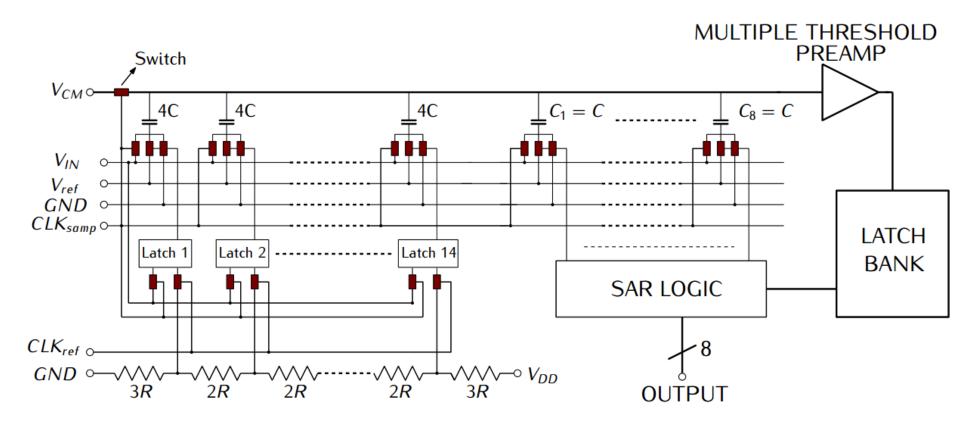

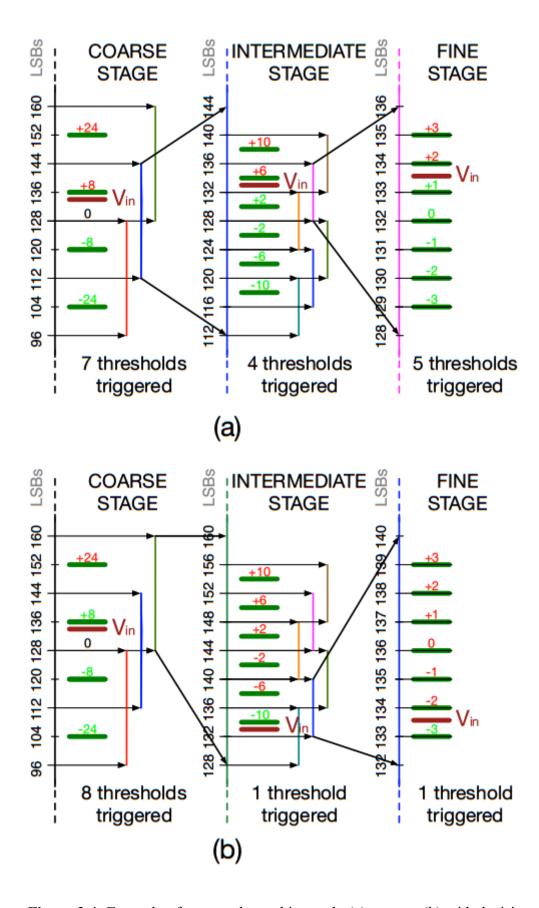

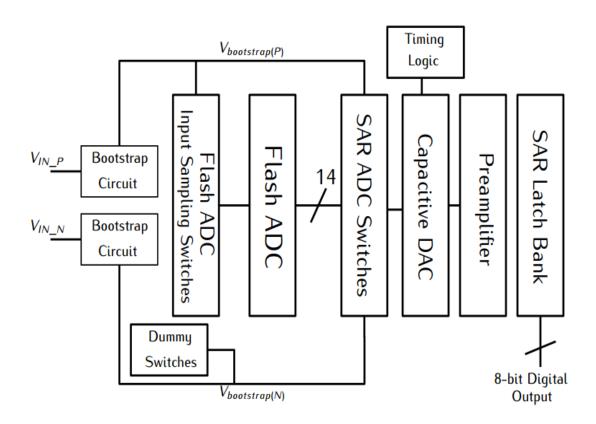

Proposed technique uses a novel searching algorithm with redundancy that allows for relaxed accuracy in the first stages of conversion. The conversion is carried out by three successive approximations. A flash ADC is employed for the coarse conversion, whereas a multi-bit SAR ADC does the fine conversion.

Figure 3.1 depicts threshold placements of the proposed architecture. 14 level flash ADC is employed for the coarse conversion. In a standard 4 bit flash ADC, thresholds would be placed every 16 LSBs. Meanwhile in the proposed architecture, thanks to the redundancy used in the next stage, thresholds are placed at  $V_{TH} = (8 + k \times 16)$  LSBs. It can be seen from the Figure 3.1 that the next SAR stage intervals overlap. This makes the 1 bit of coarse conversion redundant. This allows thresholds to be created with a reduced accuracy of  $\pm$  8 LSBs.

After the coarse conversion output of the capacitive DAC is given in Equation 3.1, where  $k_{flash}$  stands for the number of thresholds that is triggered during the coarse conversion.

$$V_{DAC.1} = (k_{flash} + 1) \times 16 LSB - V_{IN}$$

(3.1)

Coarse conversion by the flash ADC is succeeded by an intermediate stage (SAR-1) which has intervals of [-16; +16] LSBs. Note that the intervals of this stage is larger than the flash stage. This relaxes the accuracy requirements of flash ADC.

SAR-1 stage is a multi-bit per cycle SAR ADC with redundant levels, which has thresholds at  $V_{TH} = (2 + k \times 4) LSBs$  where  $k = -\frac{N_{th}}{2} : + \frac{N_{th}}{2} - 1$  being  $N_{th} = 6$ . In this stage, redundant levels relax the threshold accuracy requirements by  $\pm 2 LSB$ . Figure 3.1 demonstrates the placement of thresholds in this stage. Again, overlap of the intervals is leveraged to relax accuracy requirements. In this stage, 3rd, 4th and 5th MSBs are resolved and the output of the capacitive DAC becomes as given in Equation 3.2. Here  $k_{SAR1}$  stands for the number of thresholds that is triggered during the first fine conversion.

$$V_{DAC,1} = (k_{flash} \times 16 LSB) + (k_{SAR1} + 1) \times 4 LSB - V_{IN}$$

(3.2)

**Figure 3.1:** Threshold placement in the proposed architecture.

**Figure 3.2:** Proposed ADC architecture.

The second SAR stage (SAR-2) performs a standard 3-bit conversion in a cycle. This stage resolves 3 LSBs which requires maximum accuracy. As it will be explained later, these accuracy requirements perfectly match the way thresholds are implemented in the proposed architecture. In fact, it is easier in our solution to generate more accurate thresholds when the absolute interval to explore is reduced in term of LSBs as it is the case of the last stage, [-3; +3] LSBs.

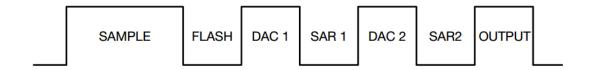

Timing arrangement of the proposed architecture is given in Figure 3.3. 4 GHz master clock is used in the architecture. Sample window is 250 ps long and other phases are 125 ps long each.

Figure 3.3: Timing arrangement of the proposed ADC architecture.

The effectiveness of the proposed searching path is explained with an example. In Figure 3.4(a), a decision process without an error is depicted. In Figure 3.4(b) decision errors have been made both of the first two stages. Note that, thanks to the redundancy, in both of the cases final decisions are same and correct. Figure 3.4 is important, too, for showing the strict accuracy requirements of the last stage.

#### 3.2.2 ADC structure

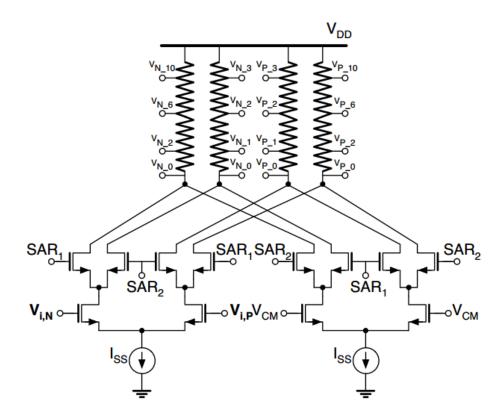

Search algorithm mentioned in Section 3.2.1 is realized by the architecture shown in Figure 3.2. For the sake of compactness only the positive input half is shown. This half of the ADC includes the flash ADC to resolve the first 3 MSB whereas negative part does not employ a flash ADC. This is due to save area and power since it is not essential to use a differential to determine on the first 3 bits. As discussed in following sections, errors due to single-ended flash ADC doesn't affect the overall performance of ADC significantly as necessary measures have been taken to mitigate the effects.

Flash ADC is not succeeded by a decoder structure. Instead, a thermometric capacitive DAC is used. This is advantageous since this DAC also forms the MSB part of the SAR capacitive DAC.

**Figure 3.4:** Example of proposed searching path: (a) correct, (b) with decision errors.

Conversion of the remaining 5 LSBs are carried out by the combination of a thermometric capacitive DAC and a multiple threshold generating preamplifier succeeded by a latch bank. Capacitive DAC of SAR-1 and SAR-2 stages are made thermometric for the same reason as in flash, in order to avoid a decoder. C-2C structure would be another option; however, simulations have shown that for the same linearity, C-2C structure requires more area than thermometric structure.

## 3.2.3 Multiple threshold generating preamp

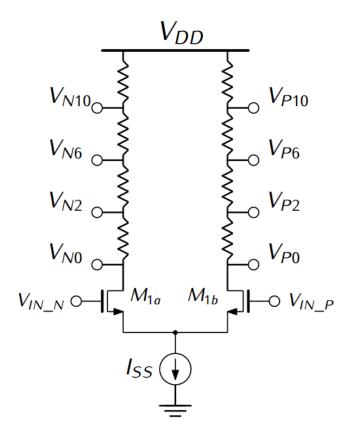

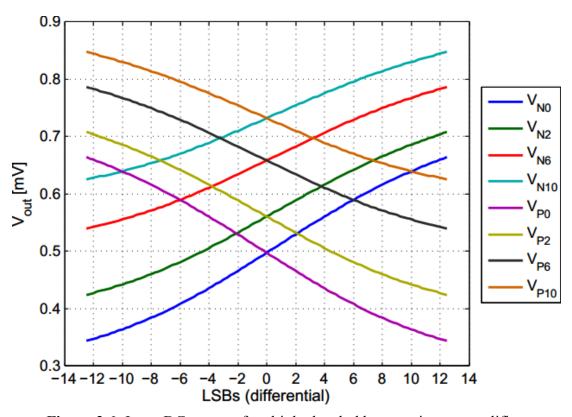

In this solution, a single preamplifier realizes multi-bit per cycle structure, which is able to generate multiple thresholds and a latch bank. Thresholds are inherently generated in the preamplifier by selecting the combination of outputs from a resistive string. Applying a voltage shift to one of the outputs moves the crossing point of the characteristic either to a positive or negative value of the differential input. The shift is simply obtained by collecting the output at a higher point of the resistive string. This output is then sent to the latch together with the reference output of the other branch; and if the resistive string has been accurately designed, the imbalance required to the differential input to make the latch trigger is equivalent to the threshold required.

The multiple threshold generating preamp is presented in Figure 3.5 and generated thresholds are shown through a input DC sweep in Figure 3.6. Considering in coarse conversion stage one of the SAR-1 intervals is chosen where  $p_{mid}$  denotes the midpoint of the interval. As shown in Figure 3.1, thresholds of the SAR-1 intervals are placed on  $(p_{mid} \pm 2)$ ,  $(p_{mid} \pm 6)$  and  $(p_{mid} \pm 10)$  LSBs. Suppose that a threshold of  $(p_{mid} + 2)$  LSB is required. In this case, inputs of one of the latches on the succeeding latch bank must be connected to the preamp outputs  $V_{N0}$  and  $V_{P2}$ . Same principle applies for the rest of thresholds.

Interval width of SAR-1 is  $\pm 16$  LSB whereas for SAR-2 it is  $\pm 4$  LSB. In addition, thresholds of the SAR-2 must be generated with maximum accuracy. This imposes a lower dynamic range for the SAR-2 preamp, which necessitates two different preamps. However, for two different preamps, offset mismatch can be problematic. Therefore, an improvement has been made on multiple threshold generating preamp, which is shown in Figure 3.7.

Figure 3.5: Multiple threshold generating preamplifier.

Figure 3.6: Input DC sweep of multiple threshold generating preamplifier.

Here, depending on the switch configuration, one of the resistor string couples is connected to the differential pair whereas the idle string couple is connected to dummy branch. In the case where there is not a dummy branch, nodes of idle resistor string get pulled to  $V_{DD}$ . This occupies some time for nodes to settle when the idle string is activated. Hence, dummy branch is employed to eliminate the recovery time of the idle resistor string. This approach is analogous to the approach utilized in current-steering DAC topologies.

Another significant benefit of using a preamp is that the offset of succeeding latches is divided by the gain achieved by the preamplifier when referred to the input.

**Figure 3.7:** Improved multiple threshold generating amplifier.

#### 4. COMPARATORS FOR HIGH SPEED ADCS

Ultra-high-speed data converters are used more and more in modern applications. Ultra wide band is an effective communication method that requires some processing at the receiver side. For this, it is necessary to use data converters with low resolution (3-5 bit) but conversion rate in the 3-5 GS/s range or more. Another application is the wireless USB that transmits data at a rate of 500 Mb/s or more. Ethernet and SERDES interfaces are two other examples of application that need ultra-high-speed data converters. They require ADC with medium resolution and conversion speed that can be as high as 10GS/s. It is expected that in the near future the requests of data conversion will become many ten of GS/s with resolutions in the 8-10 bit range. The data converter architectures for ultra-high speed applications depend on many factors such as technology, supply voltage and consumed power. However, all the solutions rely on the availability of ultra-fast comparator.

This section first analyzes various architectures of very fast comparators and studies features and limits. Then, it discusses techniques for further increase the conversion rate.

### 4.1 Comparator Architectures

Ultra-high-speed comparators use two possible general architectures, the cascade of a preamplifier and a latch or a simple latch. In the first case the gain of the preamplifier, normally low, reduces the kickback caused by the fast output transition and diminishes the probability of metastability. However, the complexity and the number of nodes in the schematic increase and this, possibly, limit the speed.

For low resolution, ADC the comparator can avoid the preamplifier and it is just made by a latch. Latches can be divided into dynamic and static. The former ones foresee a reset phase so they start the comparison with the output nodes at the same voltage level; while the latter ones are unbalanced during the preamplifier phase thus

increasing drastically the speed. Although being faster, they constantly consume power.

In order to assess the performance implication on the use of preamplifiers, we first analyze dynamic latch structures.

### 4.1.1 Dynamic latches

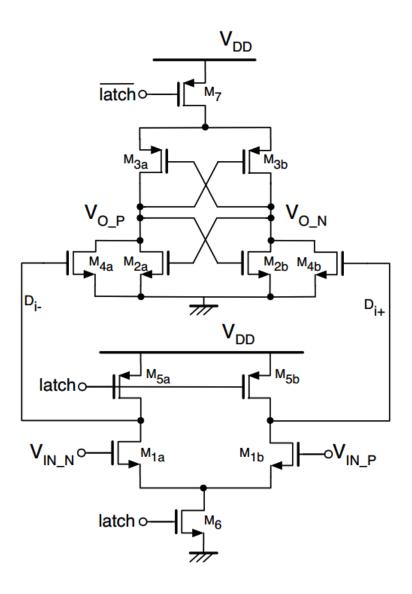

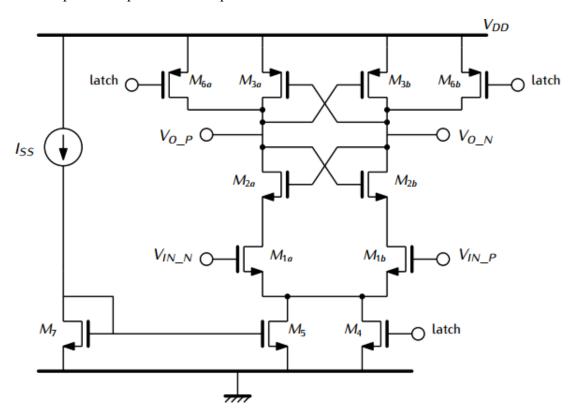

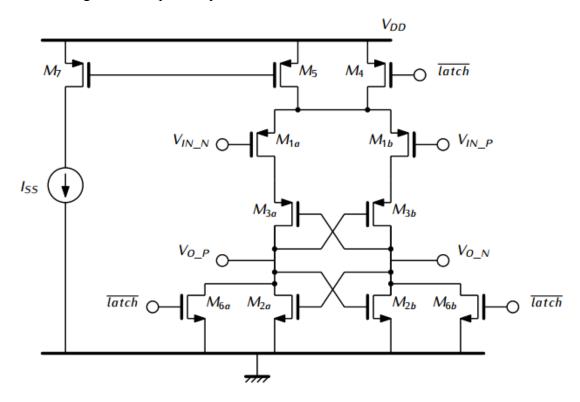

High-speed latches are typically based on two architectures: the dynamic sense amplifier [16] and the double tail latch scheme in [17]. There is another more complicated fast solution, the modified sense amplifier [18]. All these architecture are widely used in ADCs presented in [14], [6] and [19] achieving +10 GS/s conversion rate.

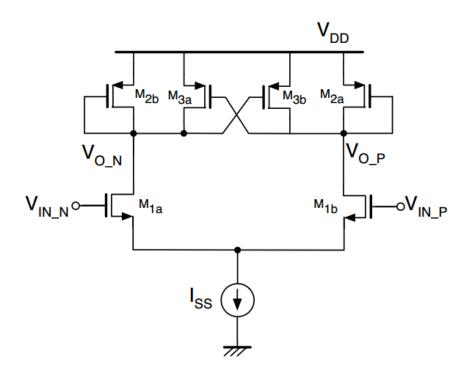

Figure 4.1: Conventional dynamic sense amplifier latch.

Figure 4.1 shows the dynamic sense amplifier latch. The solution is low power because it sinks current from the supply only when regeneration occurs. During the reset phase, output nodes are reset to  $V_{DD}$ . The drains of the input pair are either reset

to  $V_{DD}$  or shorted together. The former solution is preferred because there is no capacitive coupling between those nodes. Even if they are separated from the outputs by a transistor, the possible reset switches  $M_7$ ,  $M_{5a}$  or  $M_{5b}$  degrade speed. The circuit is fast because the input current flows through the sources of the lower regenerative loop without needing to use connections to the output nodes. The rail-to-rail excursion of the drains of the differential pair causes kickback noise. Another possible limit is the used stack of four transistors. This constrains the common mode range of the input signal.

Figure 4.2: Double-tail configuration dynamic latch.

The double-tail dynamic latch configuration in Figure 4.2, reduces the number of transistors in the stack. It uses a double regenerative loop with current injection at the output. The signal current results from the double tail of current made by the pairs

$M_{1a}$  and  $M_{1b}$  followed by  $M_{4a}$  and  $M_{4b}$ . It results in a separation between the input and the output nodes, which reduces the kickback noise. The more effective action of the double tail is contrasted by the extra load established by the drains of  $M_{4a}$  and  $M_{4b}$ . The balance of the two factors determines an increase or a slowing down of speed.

Figure 4.3: Modified dynamic sense amplifier latch.

Figure 4.3 shows a modified sense amplifier latch. It uses an auxiliary p-type latch to activate the p-type latch of the main section. This obtains a rail-to-rail output and increases the equivalent gain of the latch but as we will see shortly, the augmented complexity penalizes the conversion speed.

### 4.2 Preamplifiers

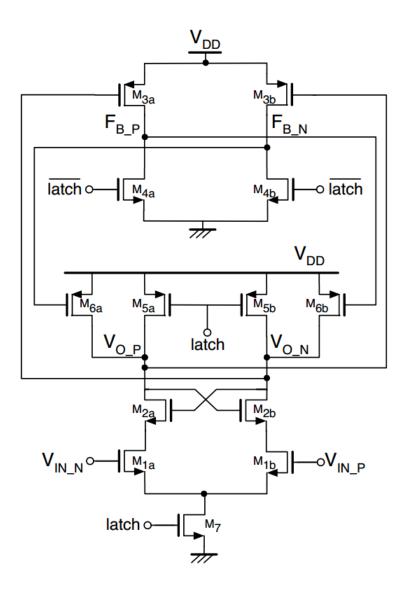

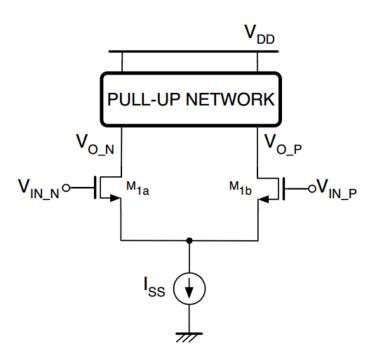

The speed improvement for larger input signal suggests using a preamplifier in front of the latch. This also reduces glitches caused by the kickback toward the input terminal and attenuates the input referred offset of the latch. The speed of the preamplifier, however, can limit the benefit of pre-amplification. The ADC architectures can distant a given time-slot for the preamp operation and within this time the outputs of the preamp must reach the stationary levels. Unfortunately, this is difficult for sampling rates of ten of GS/s and the actual gain is the one provided by the transient response at the end of the preamp period. For the above reason the preamplifiers in ultra-fast comparators are single stage with very large bandwidth and, consequently, relatively low gain.

Figure 4.4: Basic preamplifier schematic.

Figure 4.4 shows the generic configuration with n-channel input differential pair. The use of a resistive pull-up network gives a very fast response; other schematics use a diode-connected load, possibly with a current source in parallel, Figure 4.5. Another solution is the one of Figure 4.6 with diode-connected loads and cross-coupled transistors that increases the output resistance [20]. For all the solutions the  $f_T$  is given by  $g_{m,in}/C_L$ , where  $C_L$  accounts for the parasitic capacitance at the output of the preamplifier and the input capacitance of the latch. Modern technologies reduce

the load capacitance to few tens of femto Farads; with a  $g_{m,in}$  of 0.4 mA/V an  $f_T$  of tens GHz is achieved.

Figure 4.5: Preamplifier with diode-connected load.

Figure 4.6: Preamplifier with regenerative loop.

All the above solutions work suitably for comparator speeds of few GS/s. The available time allows pre-amplification lasting hundreds of ps. For ultra-high speed (10 GS/s or more) the pre-amplification time is much shorter and the achieved dynamic gain is given in Equation 4.1.

$$A_0 = \frac{g_{m,in} \times T}{C_I} \tag{4.1}$$

Suppose to have  $C_L = 20 \, fF$  and a preamp time of 25 ps, in order to achieve a gain  $A_0 = 4$  it is necessary to use a differential input pair with  $g_m = 3.2 \, mA/V$  a large value that requires a non-negligible static power.

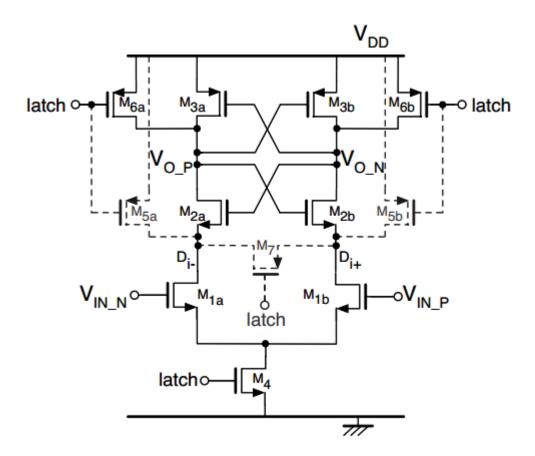

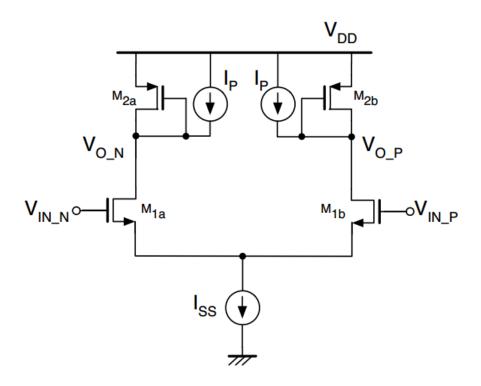

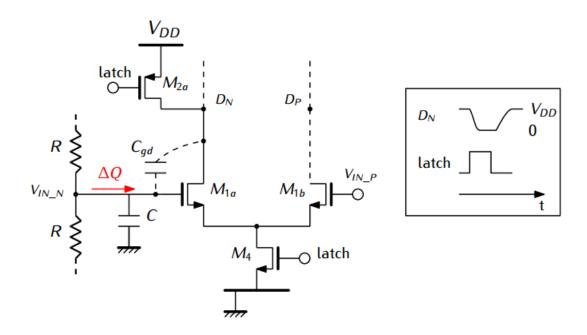

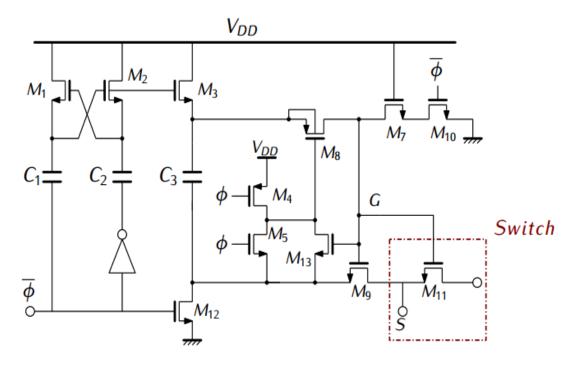

## 4.3 Dynamic Latch with Embedded Preamp

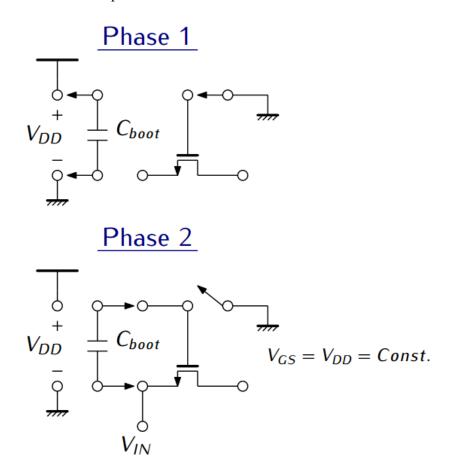

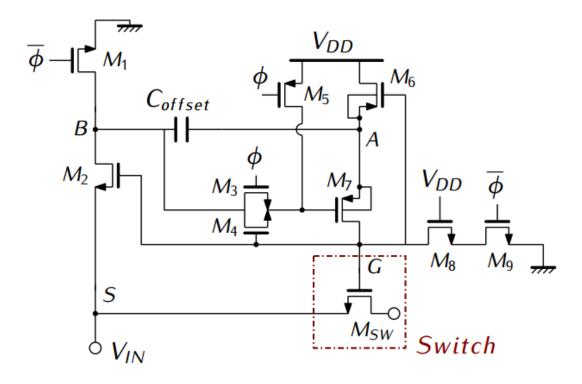

The use of a preamplifier for ultra-high speed comparator is problematic due to reasons stated in previous sections. In order to secure the expected benefit it is necessary to use a preamp with a good dynamic gain. The parasitic capacitances of the preamplifier are normally dominated by the input transistors of the latch whose aspect ratio must be chosen large. A comparison of the input stage of a preamp and the input of the sense amplifier latch show that the circuits are equal. The difference is in the role of the transistor connected to the common sources. In one case, it is a current source in the other is a switch. This suggests merging the two functions to obtain the circuit of Figure 4.7. The dynamic latch integrates the pre-amplification function into the latch itself. Following sections explain the advantages of this architecture over the conventional sense amplifier.

#### **4.3.1 Speed**

The latch with embedded preamp, works in the same way as the conventional sense amplifier latch in the latch phase. In the reset phase, the current  $I_{SS}$  flows into the pair  $M_{1a}$ ,  $M_{1b}$  while transistors  $M_{2a}$ ,  $M_{2b}$  are diode connected by the reset. The result is a static amplification of the input signal equal to the square root of the aspect ratios of input transistors and diode connected load. The parasitic capacitance is significantly reduced because it is only due to the one at nodes  $D_{i+}$  and  $D_{i-}$ . This increases the speed of the comparator with respect to an equivalent latch preceded by a preamp.

In conventional sense amplifier, reset time depends on the output load and the sizes of the reset switches. In latch with embedded preamp, employed tail current source pulls down the output nodes in reset phase which opposes the action of reset switches. This effect gets stronger with the higher input common-mode voltage (for PMOS input comparators, lower common-mode voltage) since the current of tail current source increases due to the channel length modulation. Therefore, if a large input common-mode is required, it is necessary to employ bigger reset transistors, which loads the output and penalizes the regeneration time, as well as maximum clock frequency.

**Figure 4.7:** Proposed latch with embedded preamp.

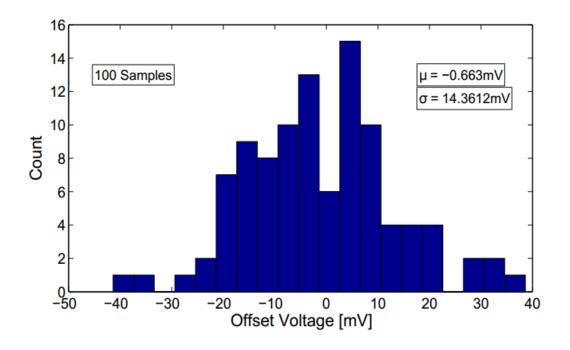

#### **4.3.2** Offset

Offset is one of the most critical design criteria of the comparators since it directly affects the yield and accuracy of the design. Two kinds of offset are present in the comparator structures; static offset and dynamic offset.

Static offset has both random and systematic nature. Random component is mainly due to the mismatch of transistors. As stated in [21], mismatch is inversely

proportional to the area of the transistors. Therefore, by using large transistors, static offset of the comparators can be reduced. However, this approach increases node capacitances and has two main disadvantages in return which are reduction in speed and increase in power consumption.

According to the analysis performed in [22] for conventional sense amplifier, "there is a significant influence of  $V_{INDC}$  on the yield" and "the yield increases inversely to  $V_{INDC}$ ", where  $V_{INDC}$  represents the input common mode voltage. This can be explained on the structure shown in Figure 4.1 as follows: Lower  $V_{INDC}$  is equal to the lower drain current  $I_o$  of the switch transistor  $M_4$ . Initial voltage difference of outputs  $V_{OP}$  and  $V_{ON}$  is defined for the instant when one of  $M_{3a}$  or  $M_{3b}$  turns on.  $V_O$  is formulated in [22] as:

$$V_O = V_{thp} \sqrt{\frac{8\beta}{I_O}} \Delta V_{IN} \tag{4.2}$$

Therefore the initial voltage difference  $V_O$  increases with lower  $V_{INDC}$ . Higher  $V_O$  makes cross-coupled inverters less likely to make an error in the presence of mismatches. In this way, yield increases hence offset decreases.

Dynamic offset in a latch mainly stems from load capacitor mismatch. According to the analysis in [23], dynamic offset is given by the Equation 4.3.  $V_{OCO}$  denotes the initial common-mode of the outputs whereas  $V_S$  denotes the switching voltage of the inverters present in the regenerative loop of the comparator. According to the equation, dynamic offset can be reduced either by minimizing ( $V_{OCO} - V_S$ ) or minimizing  $\Delta C_L$ . Since in the state-of-the-art comparators  $V_{OCO}$  is being either VDD or GND,  $\Delta C_L$  mainly a systematic error and can be minimized by careful layout.

$$V_{OS,dynamic} = \frac{1}{2} \frac{\Delta C_L}{C_L} (V_{OCO} - V_S)$$

(4.3)

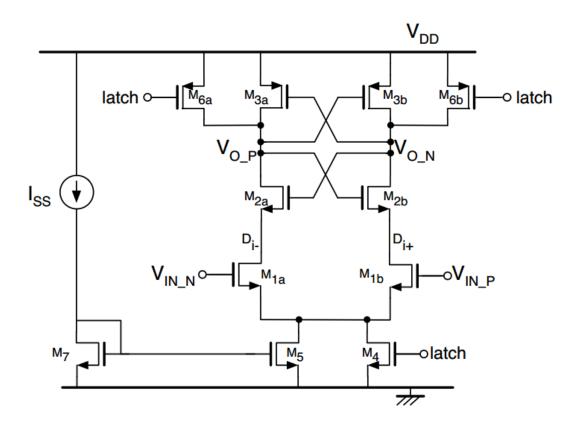

#### 4.3.3 Kickback noise

Comparators are non-linear circuit elements and they give rail-to-rail outputs VDD or GND depending on the polarity of differential input signal. These rail-to-rail voltage swings on the nodes of a comparator get coupled through the parasitic

capacitances to the input nodes of the comparators. Charge variations on the input nodes of comparator, combined with non-zero output impedance of preceding stage, causes disturbances on those nodes. This effect is called kickback noise. Kickback noise can be problematic for flash ADCs, since it may disturb the reference voltages on resistor string.

**Figure 4.8:** Kickback noise mechanism in conventional sense amplifier latch.

Power consumption is a major concern in modern electronic systems, therefore majority of state-of-the-art ADCs use dynamic latched comparators that are superior to the static and Class-AB latched comparators in terms of power consumption. However, as stated in [24], dynamic latched comparators generate more kickback noise, compared to static and class-AB counterparts. Kickback noise generation is qualitatively explained for the conventional dynamic sense amplifier \cite{arm} with a resistor ladder connected to one of the inputs. Figure 4.8 depicts the mechanism. When "latch" signal is low, latch is in reset mode where nodes  $D_P$  and  $D_N$  are pulled to  $V_{DD}$  from 0 V. In this phase as well kickback occurs but if there is enough time for references to go back their normal value, is not problematic. When "latch" goes high,  $M_4$  turns on and pulls  $D_P$  and  $D_N$  to ground. This rail-to-rail voltage swings are coupled to relative input nodes via  $C_{gd}$  of input transistors. This charge variation creates a current, which passes through the resistors on the ladder and disturbs the input.

Another source of charge variation is the changing operation regime of input transistors. Charge variation can be reduced by using smaller transistors. However, this approach contradicts the one used for decreasing the static offset and therefore creates a trade-off between kickback noise and offset.

### 4.3.4 Power consumption

Power consumption is a major concern in ADC design. Considering that each ADC has at least one comparator, power efficiency of the comparator becomes important, especially for architectures such as flash ADC, which has several comparators.

Latches can be divided in three main categories in terms of their current consumption characteristic. In static latches, there is constant current consumption, which makes them power inefficient. In class-AB latches, there is static power consumption for input pair however; in latch part, current consumption is present only in regeneration phase. For dynamic latches, there is no static power consumption and power is only consumed in regeneration phase, which makes these structures the most power efficient among three.

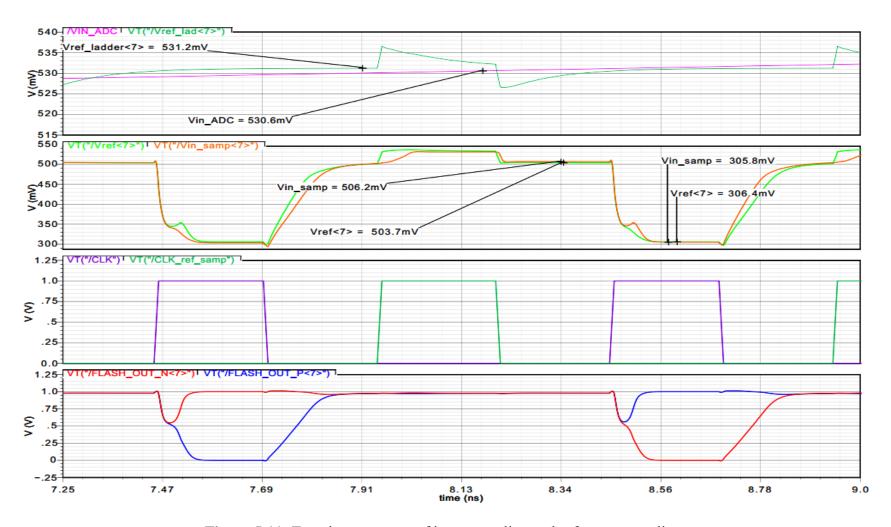

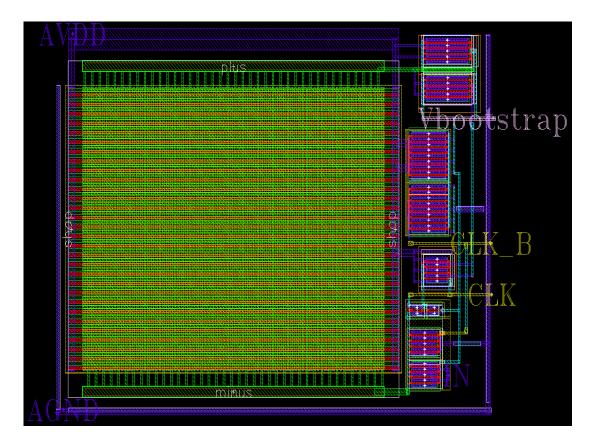

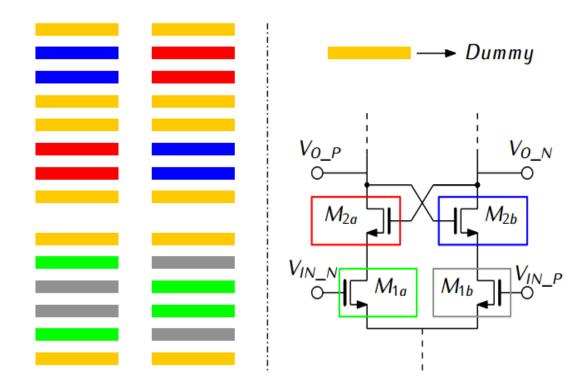

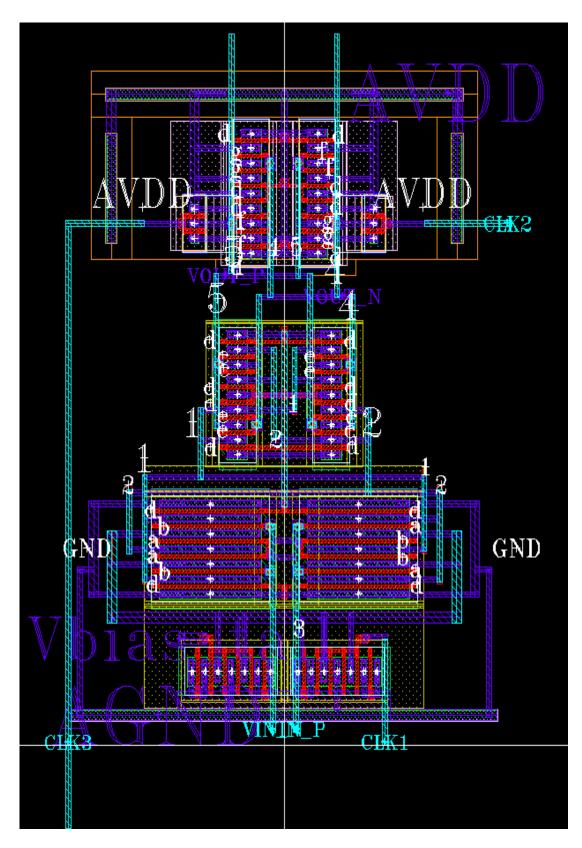

#### 4.4 Simulation Results