# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

# TUNABLE WINDOW COMPARATOR APPLICATIONS IN CURRENT-MODE CIRCUITS

**M.Sc. THESIS**

Melek KURNAZ

**Department of Electronics and Communications Engineering**

**Electronics Engineering Master Programme**

MAY 2014

# ISTANBUL TECHNICAL UNIVERSITY ★ GRADUATE SCHOOL OF SCIENCE ENGINEERING AND TECHNOLOGY

# TUNABLE WINDOW COMPARATOR APPLICATIONS IN CURRENT-MODE CIRCUITS

**M.Sc. THESIS**

Melek KURNAZ (504081214)

**Department of Electronics and Communications Engineering**

**Electronics Engineering Master Programme**

Thesis Advisor: Prof. Dr. Serdar OZOGUZ

MAY 2014

# <u>İSTANBUL TEKNİK ÜNİVERSİTESİ ★ FEN BİLİMLERİ ENSTİTÜSÜ</u>

# AKIM MODLU DEVRELERDE AYARLANABİLİR PENCERE KARŞILAŞTIRICI UYGULAMALARI

YÜKSEK LİSANS TEZİ

Melek KURNAZ (504081214)

Elektronik ve Haberleşme Mühendisliği Anabilim Dalı

Elektronik Mühendisliği Yüksek Lisans Programı

Tez Danışmanı: Prof. Dr. Serdar ÖZOĞUZ

**MAYIS 2014**

Melek Kurnaz, a M.Sc. student of ITU Institute of / Graduate School of Science Engineering and Technology student ID 504081214, successfully defended the thesis/dissertation entitled "TUNABLE WINDOW COMPARATOR APPLICATIONS IN CURRENT-MODE CIRCUITS", which she prepared after fulfilling the requirements specified in the associated legislations, before the jury whose signatures are below.

| Thesis Advisor : | Prof. Dr. Serdar OZOGUZ       |  |

|------------------|-------------------------------|--|

|                  | Istanbul Technical University |  |

|                  |                               |  |

|                  |                               |  |

|                  |                               |  |

| Jury Members : | Yrd.Doç.Dr. Metin YAZGI       |  |

|----------------|-------------------------------|--|

|                | Istanbul Technical University |  |

.....

**Prof. Dr. Cem GOKNAR** Dogus University

Date of Submission : 05 May 2014 Date of Defense : 30 May 2014

vi

To my spouse and daughter,

viii

## FOREWORD

I would like to explain my sincere pleasure to my leading supervisor Serdar ÖZOĞUZ. Also, I appreciate that Cem GÖKNAR and Shahram MINAEI without their advice and unique support. Furthermore, I am grateful to all of my teachers in Doğuş University Electronics and Communications Engineering Department especially Merih YILDIZ.

Besides, I want to thank my whole family for their understanding and lovely support.

Finally, I have a heartful thank to my husband Deniz SERIFOGLU for his patience and support. Also, I dedicate to my cute daughter Ece SERIFOGLU whom has an important place in my life for six months.

May 2014

Melek KURNAZ (Electronics and Communications Engineering)

х

# **TABLE OF CONTENTS**

## Page

| FOREWORD                                            |      |

|-----------------------------------------------------|------|

| TABLE OF CONTENTS                                   | xi   |

| ABBREVIATIONS                                       | xiii |

| LIST OF TABLES                                      | XV   |

| LIST OF FIGURES                                     | xvii |

| SUMMARY                                             | .xix |

| ÖZET                                                |      |

| 1. INTRODUCTION                                     | .1   |

| 1.1 Literature Survey                               |      |

| 1.1.1 Delay models / Time delay                     | 2    |

| 1.1.2 Ring oscillator                               | .4   |

| 1.2 Scope of Thesis                                 |      |

| 2. DYNAMIC MODELLING OF CURRENT MIRROR              |      |

| 2.1 Current-Mode Circuits                           |      |

| 2.1.1 Improvement of integration technologies       |      |

| 2.1.2 Stimulation for current-mode circuit design   |      |

| 2.1.3 Evolution of current-mode building blocks     |      |

| 2.1.4 Current-mode circuits advantages              |      |

| 2.2 Capacitances of the MOS Transistor              |      |

| 2.2.1 Thin oxide capacitance                        |      |

| 2.2.2 pn junction capacitances                      |      |

| 2.2.3 Overlap capacitance                           |      |

| 2.3 Time Delay                                      |      |

| 2.4 Introducing Core Circuit                        |      |

| 3. TIME DELAY CALCULATION                           |      |

| 3.1 Equivalent Circuit Model                        |      |

| 3.2 Junction Capacitances Calculations              |      |

| 3.2.1 Junction capacitances calculations for Node 1 |      |

| 3.3 Time Delay Calculation for the Core Circuit     |      |

| 3.3.1 Delay calculations for Node 1                 |      |

| 3.3.1.1 Time delay calculations without $r_o$       |      |

| 3.3.1.2 Time delay calculations with $r_o$          |      |

| 3.3.2 Delay calculations for Node 3                 |      |

| 3.3.3 Delay calculations for Node 5                 |      |

| 3.4 SPICE Simulation Results                        |      |

| 3.4.1 Simulation of subcircuit at Node 1            |      |

| 3.4.2 Simulation of subcircuit at Node 3            |      |

| 3.4.3 Simulation of subcircuit at Node 5            |      |

| 3.4.4 Simulation of the entire core cell            |      |

| 3.5 Comparison with Bench Test Results              | 38   |

| 4. RING OSCILLATORS CONSTRUCTED WITH CORE CIRCUIT          | 39 |

|------------------------------------------------------------|----|

| 4.1 Topologies of the Ring Oscillators                     | 41 |

| 4.1.1 Differential topology                                | 41 |

| 4.1.2 Single ended topology                                |    |

| 4.2 Proposed Ring Oscillator Constructed with Core Circuit |    |

| 4.3 SPICE Simulation Results                               | 45 |

| 4.4 Comparison with Bench Test Results                     | 46 |

| 5. CONCLUSIONS AND RECOMMENDATIONS                         |    |

| REFERENCES                                                 | 51 |

| APPENDICES                                                 | 55 |

| CURRICULUM VITAE                                           |    |

# ABBREVIATIONS

| AMS<br>BiCMOS | : Analog and Mixed Signal<br>: Bipolar Complementary Metal Oxide Semiconductor |

|---------------|--------------------------------------------------------------------------------|

| CC            | : Core Circuit                                                                 |

| CCII          | : Second Generation Current Conveyor                                           |

| CCO           | : Current Controlled Oscillator                                                |

| CMOS          | : Complementary Metal Oxide Semiconductor                                      |

| CVSL          | : Cascode Voltage Switch Logic (CVSL)                                          |

| FDE           | : Functional Differential Equations                                            |

| HDL           | : Hardware Description Language                                                |

| KCL           | : Kirchhoff's Current Law                                                      |

| MOS           | : Metal Oxide Semiconductor                                                    |

| MOSFET        | : Metal Oxide Semiconductor Field Effect Transistor                            |

| MVCM          | : Multiple Valued Current-Mode                                                 |

| NMOS          | : N-Channel Mosfet                                                             |

| PMOS          | : P-Channel Mosfet                                                             |

| PLL           | : Phase Locked Loop                                                            |

| PWM           | : Pulse Width Modulator                                                        |

| SC            | : Switched Capacitor                                                           |

| SCMS          | : Series Connected MOSFET Structure                                            |

| SI            | : Switched Current                                                             |

| SPICE         | : Simulation Program for Integrated Circuits Emphasis                          |

| STA           | : Static Timing Analysis                                                       |

| S-VCCS        | : Subtraction Based Voltage Controlled Current Source                          |

| VCO           | : Voltage Controlled Oscillator                                                |

| VLSI          | : Very Large Scale Integration                                                 |

|               |                                                                                |

xiv

# LIST OF TABLES

## Page

| Table 2.1: Dimensions of the CMOS Transistors in Core Circuit | 21 |

|---------------------------------------------------------------|----|

| Table 3.1: PSpice Model Parameters                            | 27 |

| Table 4.1: Change of Two Block Ring Oscillator frequency with |    |

| respect to control current                                    | 46 |

| Table 4.3: Measurement Results for Two Block Ring Oscillator  | 48 |

xvi

## LIST OF FIGURES

## Page

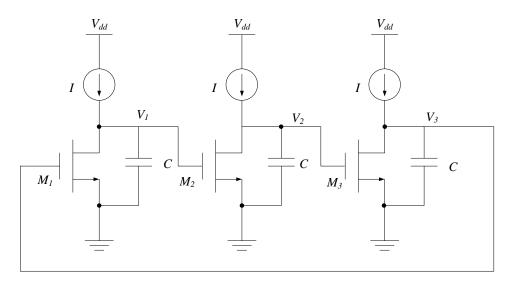

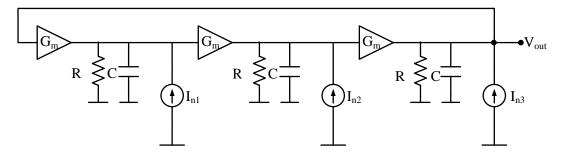

| Figure 1.1: A CMOS 3-stage inverting ring oscillator using current load [41]     | 5   |

|----------------------------------------------------------------------------------|-----|

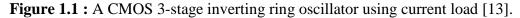

| Figure 1.2: Differential four-stage dual-delay-path ring oscillator [43]         | 6   |

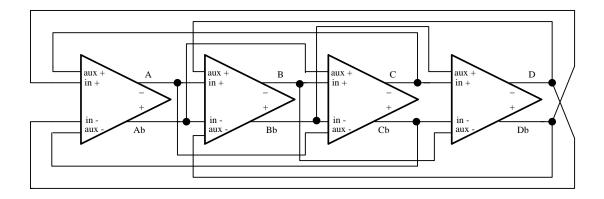

| Figure 2.1: Process technologies and there impact on Current-Mode Building       |     |

| Blocks and Systems [45]                                                          | 9   |

| Figure 2.2: Current-Mode Analog Building Blocks [45]                             | 10  |

| Figure 2.3: Capacitances of the MOS transistor [13]                              |     |

| Figure 2.4: MOS capacitance values with respect to region of operation [4]       | 15  |

| Figure 2.5 : Calculation of the MOS junction capacitance                         | 17  |

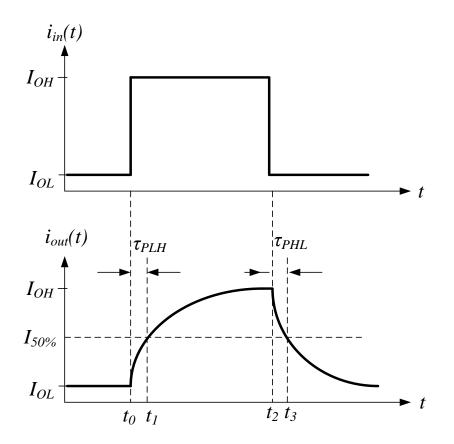

| Figure 2.6 : I-O current waveforms                                               |     |

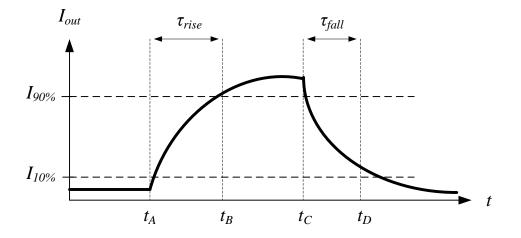

| Figure 2.7 : Output current rise and fall times                                  | 19  |

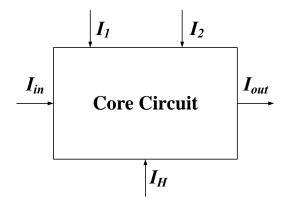

| Figure 2.8 : Core circuit block diagram                                          | 20  |

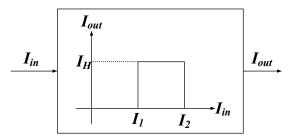

| Figure 2.9 : Transfer characteristic of the core circuit                         | 20  |

| Figure 2.10 : CMOS implementation of the core circuit [5]                        | 21  |

| Figure 3.1 : (a) PMOS circuit model. (b) Large-signal Equivalent circuit model   |     |

| without <i>r</i> <sub>o</sub>                                                    | 23  |

| Figure 3.2 : Large-signal equivalent circuit model with r <sub>o</sub> [27]      | 24  |

| Figure 3.3 : CMOS implementation of the core circuit [5]                         | 25  |

| Figure 3.4 : Input section of the core cell with parasitic capacitances [55]     | 25  |

| Figure 3.5 : MOS Model with parasitic capacitances for Node 3                    | .31 |

| Figure 3.6 : MOS Model with parasitic capacitances for Node 5 [54]               |     |

| Figure 3.7 : Step response for the input stage of the core circuit of Figure 3.3 | .35 |

| Figure 3.8 : Time delay versus input current graph                               | .35 |

| Figure 3.9 : Simulation Result for Node 3                                        |     |

| Figure 3.10 : Simulation Result for Node 5                                       |     |

| Figure 3.11 : Step response for the core circuit of Figure 3.3                   |     |

| Figure 3.12 : Bench Test Results for Core Circuit.                               |     |

| <b>Figure 4.1 :</b> Ring Oscillator with $N = 5$ [53]                            |     |

| Figure 4.2 : (a) A Single inverting amplifier (b) Small Signal Model [30]        |     |

| Figure 4.3 : Three stage differential ring oscillator [27]                       |     |

| Figure 4.4 : The small signal single-ended equivalent for the ring of 4.3        |     |

| Figure 4.5 : Proposed Two Block Ring Oscillator                                  |     |

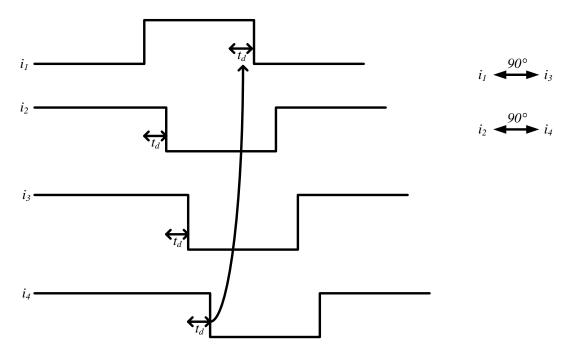

| Figure 4.6 : Time Delay of Two Block Ring Oscillator                             |     |

| Figure 4.7 : Proposed Four Block Ring Oscillator                                 |     |

| Figure 4.8 : Time Delay of Four Block Ring Oscillator                            |     |

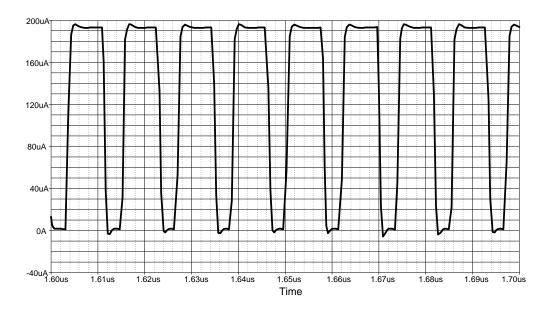

| Figure 4.9 : Simulation Result of Two Block Ring Oscillator                      |     |

| Figure 4.10 : Bench Tested Ring Oscillator                                       |     |

| Figure 4.11 : Bench Test Results for Two Block Ring Oscillator                   | .47 |

## TUNABLE WINDOW COMPARATOR APPLICATIONS IN CURRENT-MODE CIRCUITS

#### SUMMARY

In this thesis time delay calculations for current-mode circuits are investigated and equivalent circuit models for delay estimation are improved. This is one of the most important problems for us as Electronic Engineers. Many researches are already made for voltage-mode circuits, but our study is one of the few applications for current-mode circuits.

During this study, we used the CMOS Core Circuit in DU-TCC1209 which is designed and realized under Project 106E139 supported by the Scientific & Technological Research Council of Turkey (TUBITAK) in 2009 [5]. Primarily, a detailed literature survey was performed. Afterwards, missing in the literature identified and this work has continued on that topic. The first aim was to calculate time delay on current-mode circuits, then crosscheck the obtained results with simulation and bench tests. There are two phases in the calculation of the time delay: first, an equivalent circuit model has to be developed then analyzing the obtained equivalent circuit model, time delay formulae have to be extracted in terms of circuit elements' parameters. Some complicate calculation is performed with Wolfram Mathematica programme. Then simulations and bench tests have to be performed to confirm the theoretical analysis. To further verify the delay formulation in current-mode circuits, the CMOS Core Circuit in DU-TCC1209 [5] has been simulated, bench-tested and time delay results given for three different nodes.

After that with connecting two or four core circuits in a loop and a ring-oscillator circuit is proposed. The time delay of this ring-oscillator circuit is calculated. In the second step, the simulation results using SPICE Simulation Program are given and compared with theoretical ones. Finally, the ring-oscillator circuit is tested experimentally in the laboratory. That, calculated, simulated and measured delays agree quite well can be concluded. This application, which is obtained perfect results, throw light on the further suggestions such as phase detectors, modulators, clippers and comparators.

The publications and the presentations on the thesis are given end of the thesis.

## AKIM MODLU DEVRELERDE AYARLANABİLİR PENCERE KARŞILAŞTIRICI UYGULAMALARI

# ÖZET

Hazırlanmış olan bu tezde akım-modlu devrelerde zaman gecikmesi problemi ele alınmıştır. Üzerinde durmuş olduğumuz bu konu, biz Elektronik Mühendisleri için çok önemlidir. Öncelikli olarak detaylı bir literatür çalışması yapılmıştır. Bu sayede yapılan çalışmalardaki eksikler belirlenerek, çalışmalarımıza yön verilmiştir. Zaman gecikmesi hesapları ilk olarak 1964 yılında Burns tarafından gerilim-modlu devrelerde yapılmıştır. Devamında yapılan çalışmalarda ise gerilim-modlu devrelerle ilgili pek çok çalışma yapılmıştır. Ancak modern entegrasyon teknolojisinin yüksek hız, düşük güç tüketimi ve düşük güç kaynağı gibi ihtiyaçları artttığından akım modlu devrelerle ilgili çalışmalar önem kazanmıştır. Literatür araştırmasının gösterdiği gibi akım-modlu devrelerin, gerilim-modlu devrelerle kıyaslandığında hız, bantgenişliği, duyarlılık gibi pek çok avantajı vardır. Tüm bu ihtiyaçları ışığında akım-modlu devrelerde zaman gecikmesi hesaplanması büyük önem kazanmaktadr. Belirtmek gerekirse, bu çalışma akım-modlu devrelerle yapılan çok az uygulamalardan biridir. Yapılan birkaç çalışmadan kısaca bahsedilmiş ve bizim çalışmamız yanındaki eksikleri de belirtilmiştir.

Birincil amacımız akım-modlu devrelerde zaman gecikmesini hesaplamak ve sonrasında elde edilen değerlerin benzetim ve test devresi ile sağlamasını yapmaktır. İkincil amacımız ise elde edilen formülleri kullanılarak ring osilatör uygulaması geliştirmektir.

Bu tezdeki temel amaç, akım-modlu bir devrede zaman gecikmesini hesaplayan basit bir formül elde etmektir. Zaman gecikmesi hesabı iki aşamadan oluşmaktadır. Birinci aşama, eşdeğer devre modeli tasarlamak ve sonrasında elde edilen eşdeğer devre modelinin analizini yapmaktır. Bunun için iki tane PMOS içeren basit akım aynasıyla oluşmuş bir devre seçildi ve geçikme tahmini yapabilmek için eşdeğer devre modeli geliştirilmiştir. Kirchhoff akım yasası ile elde edilen denklemden yola çıkarak akım değerinin %50'ye çıktığı andaki zaman elde edilmeye çalışılmıştır. Cünkü zaman gecikme problemlerinde giriş-çıkış akımlarının yarıya yükseldiği ya da düştüğü andaki fark zaman gecikmesini vermektedir. Ortalama gecikmeyi hesaplamak için ise düştüğü ve yükseldiği kenardaki gecikmelerin ortalaması alınarak bulunabilir. Bu bilgiler ısığında basit akım avnasından olusan iki PMOS transistörlü devrenin zaman gecikmesi için çok basit bir denklem elde edilmiştir. Öncelikli olarak çıkış direnci eklenmeden yapılan bu hesaplar aynı şekilde çıkış direnci eklenerek de tekrarlanmıştır. Elde edilen formül çıkış direnci eklenmemiş hali kadar basit değildir. Ancak iki formülün de doğruluğunu görmek için, çıkış direnci sonsuz alınarak denklem çözülmüştür. Bu formüller benzer yapıdaki pek çok akımmodlu devreye uyum sağlamaktadır. Formüllerden görülebileceği gibi gecikmeyi yaratan en büyük etken parazitik kapasitelerdir. Bu kapasitelerin değerini düşürmek, gecikmeyi büyük ölçüde düşürecektir. Tezin diğer bir amacı ise, önerilen formülleri bir uygulamada kullanmaktır. 2009 yılında TÜBİTAK projesi olarak tasarlanan ve gerçeklenen DU-TCC1209 CMOS çekirdek devresi kullanılarak hesaplamaların doğruluğu gösterilmiştir. Kullanılan bu devre iki eşik devreşi ve bir fark devreşinden oluşmaktadır. Akım aynaları kullanılarak da kontrol akımları eşik devrelere aktarılmıştır. Giriş akımı  $I_{in}$ ,  $I_1$  ve  $I_2$  akımlarının arasında bir değerde ise çıkış akımı  $I_{out}$  ise  $I_H$  kontrol akımı kadardır. Diğer durumlarda ise çıkış akımı sıfırı göstermektedir. Kontrol akımları sayesinde ayarlanabilme özelliğine sahip bu devre pek çok uygulama için kullanılabilir.

Kullanılan çekirdek devrede, birinci düğüm için önerilen denklem kullanılarak zaman gecikme hesapları yapılmıştır. Formülden de görülebileceği gibi eşdeğer kapasitenin hesaplanması gerekmektedir. Bir MOS devredeki parazitik kapasiteler, transistorun çalışma aralığına göre değişiklik göstermektedir. Devredeki transistorların doymada çalıştığı düşünülerek hesaplamalar yapılmıştır. Transistor doymada çalıştığında ise  $C_{gs}$  ve  $C_{db}$  kapasiteleri ile overlap kapasiteleri hesaba katılmıştır. Kapasitelerin hesaplanmasında kullanılan değerler SPICE modelinden alınmıştır. Birinci düğüm için eş değer kapasite hesaplanarak çıkış direnci yokken ve varken zaman gecikmesi hesaplanmıştır. Elde edilen değerlerden görülebileceği gibi çıkış direnci eklendiğinde gecikmede %10'luk bir artış olmuştur. Zaman gecikmesi ile ilgili hesaplamalar yapılırken karmaşık denklemleri çözmek için Wolfram Mathematica programı kullanılmıştır. Yine de elde edilen formülleri daha iyi açıklamak için Ek-C'de matematiksel ifadeler detaylı olarak verilmiştir.

Çekirdek devrenin tamamının zaman gecikmesini hesaplayabilmek için girişten çıkışa olan katların hesaplarının ayrı ayrı yapılabilmesi gerekmektedir. Node 3 olarak kullandığımız ikinci farklı tipteki devre yapısı için benzer gecikme formülü elde edilmiştir. Yine parazitik kapasitelere bağlı basit bir denklem bulunmuştur. Üçüncü farklı tipteki devremiz ise Node 5 olarak belirtilen düğümdür. Her üç düğüm için bulunan formüllerden de anlaşılacağı gibi parazitik kapasite değerlerini düşürmek zaman gecikmesinin düşmesindeki en büyük etkendir. Tüm hesaplamaların yapılmasıyla çekirdek devrenin toplam gecikmesi hesaplanabilir. Devrenin girişinden çıkışına bakıldığında birinci ve ikinci düğüm için  $t_1$ , üçüncü düğüm için  $t_2$ , dördüncü düğüm için transistor boyutları üçüncü düğümdekinin dörtte biri olduğu için  $0.25t_2$ ve beşinci düğüm için  $t_3$ , toplam gecikme ise bu beş düğümün art arda bağlı olduğu için toplanmasıyla bulunur.

Teorik analizi doğrulamak için SPICE benzetim programı kullanılmıştır. 0.35µm TSMC CMOS teknoloji parametreleri ile simülasyonlar gerçekleştirilmiştir. Her üç düğüm için ayrı ayrı hesaplar yapıldığı gibi simülasyonlar da yapılmıştır. Ayrıca birinci düğüm için yapılan bir analiz giriş akımı arttıkça, zaman gecikmesinin azaldığını da göstermektedir. Çekirdek devrenin tamamı için de simülasyon yapıldığında, hesaplamalarla elde edilen değerlerin büyük ölçüde birbirini doğruladığı gözlenmiştir. Teorik hesapların yanında simülasyon sonuçları ile de sağlaması yapılan bu çalışmada son aşama ise laboratuvarda deneysel olarak test edilmesidir. Öncelikli olarak iki PMOS'dan oluşan devre CD4007 kullanılarak test edilmiştir. Burada elde edilen değer teorik ve simüle edilen değerlerle büyük oranda benzerlik sağlamış olsa da ölçüm ucu kapasitelerinden ve parazitik etkilerden kaynaklı olarak iki katı bir fark görülmüştür. Laboratuvar ortamını iyileştirebilmek aradaki farkı azaltacaktır.

Tek bir çekirdek hücrenin tüm analizi yapıldıktan sonra, bu yapı ring osilatör uygulamasını önermek için kullanılmıştır. Ard arda iki tane çekirdek devrenin bağlanmasıyla basit bir ring osilatör oluşturulmuştur. Öncelikli olarak teorik analizi yapılan devrenin daha sonra simülasyon sonuçları ile karşılaştırılması yapılmıştır. Osilasyon frekansı teorik olarak hesaplandığı gibi yapılan benzetimlerle üç ayrı değerlerle test edilmiştir. Kontrol akım değerlerinin artmasıyla osilasyon frekansının da arttığı görülmüştür. Üçüncü aşamamız ise DU-TCC1209 CMOS çekirdek devresi kullanarak laboratuvar ortamında testini sağlamaktır. Ancak bu şekilde ard arda bağlanmasıyla zaman gecikmesi arttığından osilasyon frekansı da düşmektedir. Benzer şekilde dört çekirdek devrenin peş peşe bağlanmasıyla dört bloklu ring osilatör devre yapısı önerilmiştir. İhtiyaç duyulan osilasyon frekansına göre iki ya da dört bloklu ring osilatör devresi kullanılabilir.

Yapılan çalışmayı genel olarak değerlendirmek gerekirse, elde edilen basit formüller akım-modlu pek çok devreye uyarlanabilir ve böylece hesaplamalar sayesinde gecikme minimum düzeye ingirgenebilir. Önerilen ring osilatör yapısı da çeşitli ihtiyaçlara göre kullanılabilir.

Hesaplanan, simüle edilen ve ölçülen gecikmeler birbirine çok yakın değerler vermiştir. Ölçüm sonuçlarının elde edilen değerlerin iki katı kadar farklı çıkması laboratuvar imkanlarının yetersizliği ve parazitik etkilerden kaynaklanmaktadır.

Elde edilen iyi sonuçlar sonraki çalışmalarımıza da ışık tutacaktır. Bu konu ile ilgili yapılabilecek sonraki çalışmalardan bazıları şöyle sıralanabilir: faz dedektörleri, modülatörler, karşılaştırıcılar ve kırpıcı devrelerdir.

Bu tezden türetilen bildiri ve yayınlar son bölümde verilmiştir.

#### **1. INTRODUCTION**

Nowadays, modern integration technologies are in a serious development stage, because of the requirements of higher speed, lower power consumption and lower power supply values. Due to the reduction in the dimensions of integration devices, maximum voltage ratings are reduced as well. The reduction in supply voltage values does not limit the design of digital circuits; but the design of high performance analog integrated circuits with low supply voltages becomes more complicated.

In this case, there is a small amount of integrated devices in digital integration technologies for circuit design. In the worst convenient scenario, there are only transistors suitable are in order to designing analog circuit. Infrequently, there might be capacitances and resistors. However, in this case there are disadvantages such as small values and parasitic components. Therefore, if it is desired quickest integration technologies suitable, it typically prevent to active components in the propose of integrated analog circuits [1].

Current-mode circuit design can be considered as a solution to design highperformance analog circuits with lower supply voltages. A literature survey shows that current-mode circuits have many advantages in comparison with voltage-mode circuits in terms of speed, bandwidth, accuracy, etc. In current-mode circuits, high voltage gain amplifiers, passive components with high sensitivity, summers are not required and that is why these circuits can be designed completely with transistors. This advantage provides the compatibility of current-mode circuits with digital processes as well [2,3].

Generally, in the literature, dynamic characteristics of CMOS inverter circuits are investigated; delay calculations of inverters were presented primarily by Burns in 1964 [4].

If it is needed to compare similar applications, the study provides the following advantages:

- has a simple mathematical expression.

- gives more physical comprehension about the current-mode circuits implement the existing core circuit in the ring oscillator application.

The motivation of these study as follows:

Secondary effect is a practical challenge. The expectation of these study dynamic performances of the system is developed. It is needed more realistic models. In the internal dynamics of many processes include second effect event. For examples of related studies biology, mechanics, physics. In addition, delays are presented by actuators, detectors and field networks in feedback loops. Thus, they are contained in communication area and information technologies such as service quality in MPEG video transmission or high-speed communication networks, computing times in robotics, etc. After all, delay times are used to reduce high order models.

#### **1.1 Literature Survey**

### 1.1.1 Delay models / Time delay

In literature, dynamic characteristics of the CMOS inverter circuit is investigated generally. CMOS inverter delay calculations was presented as primarily by Burns in 1964 [5].

One of the first studies on the time delay calculations is about series connected MOSFET structures (SCMS's) [6]. The usage of the new possible short channel MOS model provides analysis of CMOS gate delay. Including short channel effects, for CMOS inverters and SCMS's closed form time delay formulas are acquired. As is clear from here, the time delay of NAND/NOR compare with the time delay of inverter getting smaller in the area of submicrometer. The reason is that every MOSFET's  $V_{DS}$  and  $V_{GS}$  in the SCMS are lower than MOSFET inverter. In minimized MOSFET, the lower voltages respectively decrease and relieve the hard carrier speed saturation. This event support more extended use of NAND/NOR complex gates and Cascode Voltage Switch Logic (CVSL) which refers to a CMOS type logic family in the submicrometer circuit design [6].

In another study, for a different applications, CMOS inverter delay calculations and formulas are determined. In this embodiment, simple but practical  $\alpha$ -power law

MOS model is suggested. This model is enclosed to containing the carrier velocity saturation effect caused by prominent in short channel MOSFET's. The model which operates in saturation region, is continuation of Shockley's square-law MOS model. By using this model for calculating delay, closed form statements are provided. If applications of this model is indicated as follows, closed form analytical statements are provided for calculating delay, short circuit power and logic threshold voltage of CMOS inverters. All applications were supported on the Shockley model, also all studies is essential to aware of the behaviour in submicrometer area. At the same time source and drain resistance is taken into consideration as delay statement. Source and drain resistance affect is play a significant role in assessment of delay retrogression a kind of parasitic diffusion resistance of MOSFET's and hot carrier retrogression affect [5].

In another application, timing jitter is investigated in CMOS ring oscillators. In CMOS ring oscillators, the consequences of thermal noise in transistors on timing jitter compiled of source coupled differential delay cells is inquired. Correlation between delay component design variable and implicit in thermal noise jitter of the generated waveform are studied. In this structure delay control is used with phase detection for designing ring oscillator. Time delay of this ring oscillator is formulated by first order timing jitter decomposition. This is found out by the number of stages in the ring and the delay for each stage. In this structure delay-mode circuit structure is used for calculating delay calculation [7].

Some studies have been conducted on current-mode circuits. In 2004, delay line with continous time offset compensation is discussed. For Laguerre adaptive filter structure, second order fully differential offset compensated current-mode delay line is recommended. Current state enable to use minimum length of the transistors which enlarge the bandwidth without considerable increasing the power consumption [8].

High speed timing recognition outline by using delay tables is recommended for a wide ranging Multiple Valued Current-Mode (MVCM). This application is proposed because of the necessity of high performance arithmetic VLSI, in a lot of application areas, such as multimedia processing and intelligent signal processing. The proposed recognition consists of two main stages. The first stage is logic verification using Verilog AMS which is a Hardware Description Language (HDL) conceived for

analog and mixed signal systems. The second stage is delay estimation based on parasitic capacitance occupier static timing analysis (STA) tool which is standard timing verification methodology [9].

In another implementation is about Pulse Width Modulator (PWM). This study consist of the stability of current-mode controlling with time delay model of PWM. As with many studies in recent years, also in this study, the structure of the currentmode circuit proved to be many advantages compared to the structure of the voltagemode circuit. Firstly time delay model of PWM in voltage-mode control is represented, and then time delay model of PWM in current-mode control is designed with additional current loop inside the external voltage loop. But in here, duty ratio is no more argument however is controlled by the inductor current. Recommended model exposes some supremacy as a simpler mathematical expression, gives more physical insight into the sample and of current loop and obtain preferable prediction of the critical condition of the current loop stability without of slope compensation [1].

In another study, CMOS wireless temperature sensor is designed with integrated radiating element. For this wireless temperature there are two ring oscillators. It is known that a ring oscillator is a sensitive circuit because temperature variances reason adjustments of oscillation frequency. The relation between frequency and temperature is the delay of each stage. This technique was applied that solving the problem of unwanted dependence on the bias voltage of the ring oscillation frequency [10].

In [11] the analytic step response of an NMOS current mirror has been examined. The settling time of the current mirror has been derived analytically. However, the output resistances of the transistors were not taken into account.

#### 1.1.2 Ring oscillator

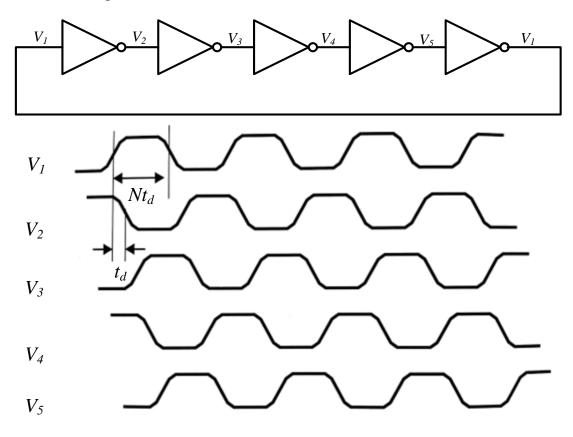

A ring oscillator is a structure consisted of an odd number of NOT gates. Their output oscillates between two voltage levels [12].

In literature ring oscillators are extensively used in phase locked loops (PLL). This is utilized for frequency synthesizers for their small die size, clock synchronization in microprocessors, clock and data recovery and a lot of implementation of polyphase sampling [7]. Another applications of ring oscillators are as follows; voltage controlled oscillator in most phase locked loops is built from a ring oscillator, many wafers include a ring oscillator as part of the scribe line test structures which is used during wafer testing to measure the effects of manufacturing process variety.

In one of the studies, 3-stage inverting ring oscillator is proposed to acquire a formula for its frequency. Designed circuit structure is shown in Figure 1.1. As can be seen from the figure, inverting stage uses an NMOS device driving a current source I with an output capacitor C. Therefore there is no  $V_{dd}$  supply current spike generally contained in a static inverter and consumption of power depends on I. As a result of work done, for large NMOS or small current, the frequency alters linearly with the load current [13].

A Dual Delay Path Ring Oscillator is presented by Chen and Lee. The designed structure which is shown in Figure 1.2 has two operation modes which mentioned as the differential and common modes. The oscillation frequencies and output waveform characteristics help that distinguish each other the two operation modes. The main distinction among the operation modes is the output waveform characteristics. The tunning ranges are from 1.01 to 1.055 GHz for common-mode, 1.77 to 1.92 GHz for differential operations for differential four-stage dual delay path ring oscillator [14].

Figure 1.2 : Differential four-stage dual delay path ring oscillator [14].

One of the recent studies, VCO as is presented as a process variation compansated voltage controlled ring oscillator (VCO) with subtraction based voltage controlled current source (S-VCCS). In this study to compansate voltage controlled ring oscillators variation for process variations a simple methodolgy is proposed. The compensation is acquired by supplying the VCO with stable current which comes from S-VCCS. For implementing a current reference amplifier S-VCCS can be colligated to voltage to current converter. Also it can be used in differential ring VCOs, continous time filters and automatic gain control circuits to compensate corner variations [15].

#### 1.2 Scope of Thesis

The aim of this thesis is to give a general calculation of time delay in current-mode circuits then to verify it by simulations and bench tests. There are two phases in the calculation of the time delay: first, an equivalent circuit model has to be developed then analyzing the obtained equivalent circuit model, time delay formulae have to be extracted in terms of circuit elements' parameters. A ring oscillator is proposed as two block and four block application. Its calculation is also extracted. Then simulations and bench tests have to be performed to confirm the theoretical analysis. To further verify the delay formulation in current-mode circuits, the CMOS Core Circuit in DU-TCC1209 [1] has been simulated, bench-tested and time delay results given for three different nodes.

The sequel of the thesis is organized as follows: in chapter 2, dynamic modelling of current mirror is clarified. Improvement of integration technologies, current-mode

building blocks and the advantages of current-mode circuits are explained. In chapter 3, design of equivalent circuit model is explained. There is a simple current-mode current-mirror circuit and its large-signal equivalent circuit model are given. The time delay formulation of the equivalent circuit model is extracted. In addition the effects of the parasitic capacitances on the delay calculations are considered. Time delay is calculated for three distinctive node and the total time delay is computed. SPICE simulations for three node and bench test results are presented. The time delay calculation is also computed in ring oscillator as two block and four block in chapter 4. As well, simulation results and bench test results provided theoretical consequence. Finally, some concluding remarks and further sugestion are given in chapter 5.

## 2. DYNAMIC MODELLING OF CURRENT MIRROR

### **2.1 Current-Mode Circuits**

In recent studies, current-mode circuits present a better performance than voltagemode structures in analog circuit design [8].

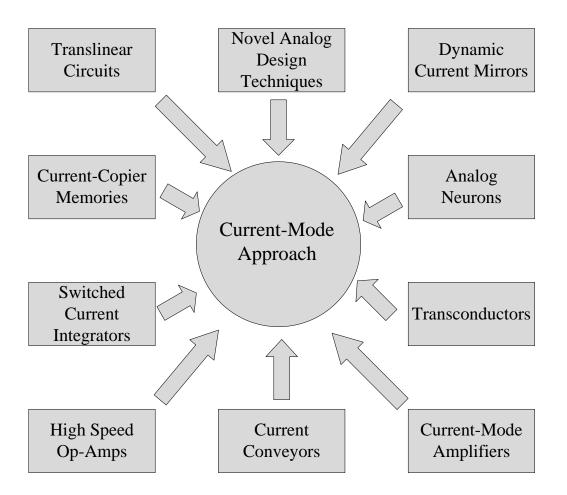

In Figure 2.1 process technologies are shown. These technologies effect on currentmode building blocks and systems. Besides, current-mode analog building blocks are shown in Figure 2.2.

Figure 2.1: Process technologies and there impact on Current-Mode Building Blocks and Systems [2].

Figure 2.2 : Current-Mode Analog Building Blocks [2].

## **2.1.1 Improvement of integration technologies**

Nowadays, the requirements of digital CMOS circuit design provide the improvement of modern integration technologies. While the size of the integrated devices reduction, the voltage ratings rapidly decrease. But the reduction of supply voltage do not constrain the design of digital circuits.

There are little integrated devices suitable for circuit design, in digital integration technologies. The worst case there will be analogue circuit design with only transistors. There may be resistors or capacitances, however their values may be small or there will be parasitic components. If desired that to optimize fastest integration technologies, there will be active components in analog circuits design.

The operational amplifier has attended as the basic constructing blocks in the analog circuit design while the innovation of integrated circuits. After that, the

execution necessities for analog circuits have been altered and new integrated analog circuit applications have came forth. At high closed-loop gain system acquires due to the stable gain-bandwidth product voltage-mode operational amplifier circuits have bounded bandwidth. Moreover, the fixed slew-rate of the operational amplifier involves the large-signal, high-frequency operation. That's why it is needed low voltage analog circuit techniques [16].

#### 2.1.2 Stimulation for current-mode circuit design

There is a method for finding disjunctive; circuit implementation is to use current signals instead of voltage signals for signal processing. MOS transistors are more appropriate for manipulating currents rather than voltages just because common-source, common-gate and common-drain amplifier configurations have current at the output signal. In MOS current mirrors, base currents limit the accuracy so according to bipolar current mirrors, MOS current mirrors are more accurate and fewer sensitive to process configuration. Furthermore, MOS transistor circuits can be simplified by using current signals preferable to voltage signals. Therefore, integrated current-mode circuit actualizations nearer to the transistor level than the traditional voltage-mode actualizations and therefore simpler circuits and systems should result.

The parasitic capacitances are charged and discharged with voltage oscillation when signals are distributed as voltages. That limits the speed and increments the power consumption of voltage-mode circuits. Consequently, it is realizable to accomplish higher speed and lower dynamic power consumption with currentmode circuit processes. Current-mode connection circuits particularly display assuring performance.

The voltages in MOS transistor circuits are relative to the square root of the signal while the signal is carried for a current, whenever saturation region operation is acquired for the devices. Likewise, the voltages are proportional to the logarithm of the signal in bipolar transistor circuits. Hence, a decrease of supply voltage and a compressing of voltage signal swing are possible. This speciality is applied e.g. in log domain filters, switched current filters, and in non-linear current-mode circuits commonly. Unfortunately, because of the device mismatches this nonlinear procedure can yield an extravagant quantity of deformation for applications with high linearity demands. Therefore, to reduce the nonlinearity of the transistor transconductance, linearization methods are being applied. Thereby the voltage signal oscillation is not minimized.

Nevertheless, new results regular imply new problems. Sensitivity to mismatches is increment by the compressing of the voltage signal swing. Moreover, some current-mode techniques are very old such as the current feedback. They are used as developed voltage-mode signal processing building blocks instead of current-mode such as signal processing building blocks [16].

#### 2.1.3 Evolution of current-mode building blocks

The first building block conceived for current signal processing is published in 1968 as current conveyor [17]. The improvement form of the current conveyor, which called the second-generation current conveyor CCII, is emerged in 1970. None of them became popular because of the integrated operational amplifier [18]. In forties, voltage-mode operational amplifiers notion had already been presented. In addition to this, integrated current conveyors were crucial to realize. In 1970s, PNP devices without high performance are used in the integration technologies [17-20].

In 1980's, fast PNP devices were presented in bipolar integration technologies. At that time, researchers realize that voltage-mode operational amplifier is not best solution to all analog circuit design problems. New surveys show that by using current conveyors, current-mode signal processing is presented. Additionally the current feedback operational amplifier can be produced as a commercial product [18-20].

Different circuit topologies and operation basis are essential for realizing currentmode circuits. In 1988, the fundamental of a MOS current copier was offered [21]. In 1989, the switched current (SI) principle was offered. Then switched capacitor (SC) circuits that do not need linear capacitors were presented as an alternative to the SI circuits [19]. Moreover, with a differential input and single ended output or with a single ended input and differential output, diverse suggestion for CMOS current-mode operational amplifier have been published [21].

### 2.1.4 Current-mode circuits advantages

A literature survey shows that current-mode circuits have many advantages according to the voltage-mode circuits. The current-mode circuits obtaining a better performance is these circuits usually are less complex and use less loop gain.

With regard to Schmid, the actual difference between current-mode circuits and voltage-mode circuits are arived from the distinctive studies of researchers [22].

Therefore, researchers who work on current-mode can give precious point of view to voltage-mode researchers while they try to design the circuits with low power, low voltage, high speed circuits [22].

If we want to summarily indicate the advantages of current-mode circuits according to the voltage-mode circuits, listed as follows:

- Lower power consumption,

- Smaller chip area,

- Higher gain variation,

- Circuit simplicity,

- Cost of higher distortion,

- Less loop gain,

- Faster.

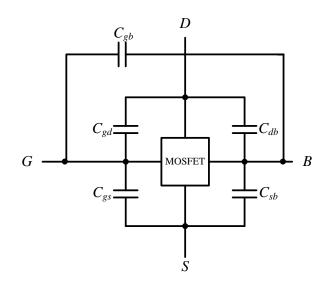

# 2.2 Capacitances of the MOS Transistor

Switching rates are being limited with the lengths of the time interval required for charging and discharging capacitances contained in the MOS transistor. It is known that many of the capacitances in VLSI circuits are very small for measuring accurately. For circuit analysis, these parasitic capacitances must be calculated from device proportions and dielectric constants. The MOS transistor's significant capacitances are between the terminals of the transistor as shown in Figure 2.3. According to physical properties, these parasitic capacitances can be grouped under

three headings as thin oxide capacitances, junction capacitances and overlap capacitances [35].

Figure 2.3 : Capacitances of the MOS transistor [9].

# 2.2.1 Thin oxide capacitance

In MOS transistors, the thin oxide capacitance is the most important capacitance. The thin oxide capacitances are consisted of  $C_{gs}$ ,  $C_{gd}$ , and  $C_{gb}$  are symbolized by  $C_g$ . The two plates of the capacitances are defined as the gate and the channel. Among these two plates the dielectric material is the oxide. The gate capacitances  $C_g$  is found as the following equality:

$$C_g = C_{ox} \times W \times L \tag{2.1}$$

where  $C_{ox}$  is the capacitance per unit area of the gate dielectric is defined as:

$$C_{ox} = \frac{\mathcal{E}_{ox}}{t_{OX}}$$

(2.2)

where  $t_{ox}$  is the gate oxide thickness and  $\varepsilon_{ox}$  is the permittivity of oxide can be found as:

$$\varepsilon_{ox} = 3.9 \times \varepsilon_o \tag{2.3}$$

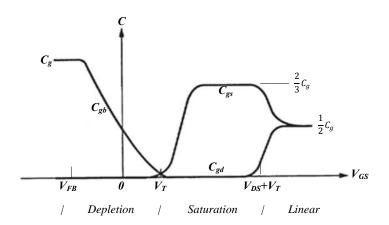

where  $\varepsilon_o$  is the dielectric constant and the value of this constant is  $8.85 \times 10^{-12} F/m$ . The gate capacitance is divided into three capacitances namely; the gate to source capacitance  $C_{gs}$ , the gate to drain capacitance  $C_{gd}$ , and gate to bulk capacitance  $C_{gb}$ . These parasitic capacitances are calculated numerically depending on whether the device is in cut off, in linear or saturation regions as indicated in Figure 2.4.

Figure 2.4 : MOS capacitance values with respect to region of operation [23].

when the device is in cut off the capacitances gate source and gate drain is equal to zero as shown in equality (2.4). The gate bulk capacitance is in (2.5).

$$C_{gs} = C_{gd} = 0 \tag{2.4}$$

$$C_{gb} = C_{ox} \times W \times L \tag{2.5}$$

when the device is in linear region the capacitances obtained as:

$$C_{gb} = 0 \tag{2.6}$$

$$C_{gs} \cong C_{gd} \cong \frac{1}{2} C_{ox} \times W \times L$$

(2.7)

when the device is in saturation mode the parasiticic capacitances gate drain and gate bulk gives a value of zero as shown following equality:

$$C_{gd} = C_{gb} = 0 \tag{2.8}$$

The formula of the gate to source capacitance  $C_{gs}$  is given by:

$$C_{gs} = 2/3 \ C_{ox} \times W \times L \tag{2.9}$$

where,  $C_{ox}$  is the capacitance per unit area of the gate dielectric, W and L are width and length of the transistor respectively.

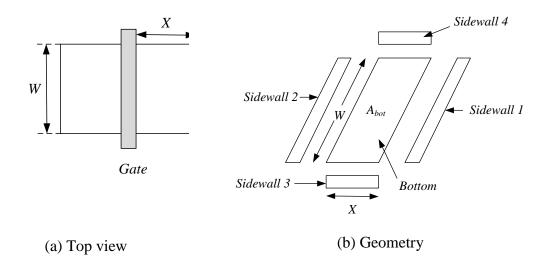

### 2.2.2 pn junction capacitances

The source and drain regions and substrate form pn junctions that give rise to two additional capacitances. The junction capacitances are composed of source bulk and drain bulk capacitances respectively as symbolized  $C_{sb}$ , and  $C_{db}$ . Each of two capacitances is owing to the depletion charge of the source or drain diffusion area in substrate. These junction capacitances are very complicate to calculate by the three dimensional shape of the diffusion regions that constitute source substrate and the drain substrate junctions.

There are two types of junction capacitances calculate for NMOS device, in such a way that the bottom capacitance and the sidewall capacitance. The detailed junction capacitance ( $C_{db}$ ) is found from the following equality:

$$C_{db} = \left(\frac{CJ}{\left(1 + \frac{VDB}{PB}\right)^{MJ}} \times AD\right) + \left(\frac{CJSW}{\left(1 + \frac{VDB}{PB}\right)^{MJSW}} \times PD\right)$$

(2.10)

where CJ is the zero-bias body-junction capacitance per unit area over the drainsource region and CJSW is the zero-bias body-junction capacitance per unit length along the sidewall (periphery) of the drain-source region. MJ is the grading coefficient for area component and MJSW is the grading coefficient for the sidewall component; PB is the body-junction built in potential, AD is the area while PD is the perimeter of the drain region of MOSFET [24].

The formula AD as given by expression (2.11) where  $x_j$  called the junction depth and PD as given following equalities:

$$AD = 2(W * xj) + 2(X * xj) \ (X \cong L/2)$$

(2.11)

$$PD = 2 * (W + X)$$

(2.12)

The top view of the MOS transitor in Figure 2.5 defines the channel width W of the transistor and the extent X away from the gate of the region.

Figure 2.5 : Calculation of the MOS junction capacitance.

#### 2.2.3 Overlap capacitance

The overlap capacitance is arising from lateral diffusion and fringing component. This voltage free capacitance is connected from gate to drain and from gate to source [22].

The capacitance due to lateral diffusion is computed as:

$$C_{ov} = W \times L_{ov} \times C_{ox} \tag{2.13}$$

where  $L_{ov}$  is overlap length and typically,  $L_{ov} = 0.05$  to 0.1*L*.  $C_{ox}$  is the capacitance per unit area as shown in Equation (2.2) and *W* is width of the transistor.

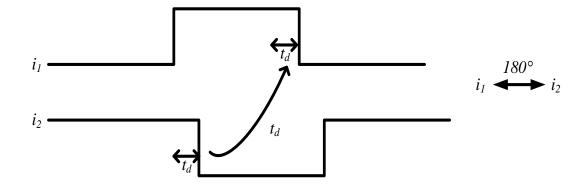

### 2.3 Time Delay

Time delay systems can be called a secondary effect or a dead-time system. In functional differential equations (FDEs) class, these systems can be included. Since 1963, there are lots of surveys and research papers [25].

The Input-Output (I-O) waveforms of the current-mirror circuit are shown in Figure 2.6. As can be seen from Figure 2.6, low to high time delay  $\tau_{PLH}$  of MOS transistors can be defined as time duration between the initial time  $t_0$  (the output current is at its minimum value) and the time  $t_1$  (the output current increases to half of its maximum value). Similarly, high to low transition propagation delay  $\tau_{PHL}$  is the time duration

required for the output to decrease to half of its maximum value from its maximum value. Thus, the propagation delay times  $\tau_{PHL}$  and  $\tau_{PLH}$  are found from Figure 2.6 as:

$$\tau_{PLH} = t_1 - t_0 \tag{2.14}$$

$$\tau_{_{PHL}} = t_3 - t_2 \tag{2.15}$$

$$\tau_P = \frac{\tau_{PLH} + \tau_{PHL}}{2} \tag{2.16}$$

Figure 2.6 : I-O current waveforms.

There is another specification for output current rise and fall times as shown in Figure 2.7.  $\tau_{fall}$  as called falling time can be clarified as the time necessary for the output current reduce from  $I_{90\%}$  level to  $I_{10\%}$  level. Similarly,  $\tau_{rise}$  as called rising time can be clarified as the time necessary for the output current reduce from  $I_{10\%}$  level to  $I_{90\%}$  level. Similarly,  $\tau_{rise}$  as called rising time can be clarified as the time necessary for the output current reduce from  $I_{10\%}$  level to  $I_{90\%}$  level.  $I_{10\%}$  and  $I_{90\%}$  current levels can be described as follows:

$$I_{10\%} = I_{OL} + 0.1(I_{OH} - I_{OL})$$

(2.17)

$$I_{90\%} = I_{OL} + 0.9(I_{OH} - I_{OL})$$

(2.18)

Figure 2.7 : Output current rise and fall times.

So that, the output  $\tau_{fall}$  and  $\tau_{rise}$  can be found from Figure 2.7 as the following equations:

$$\boldsymbol{\tau}_{fall} = t_B \boldsymbol{-} t_A \tag{2.19}$$

$$\tau_{rise} = t_D - t_C \tag{2.20}$$

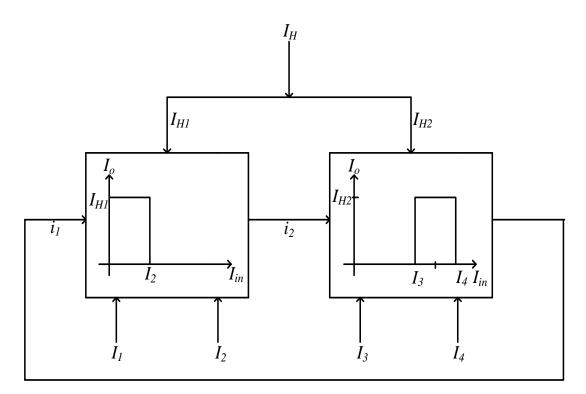

# 2.4 Introducing Core Circuit

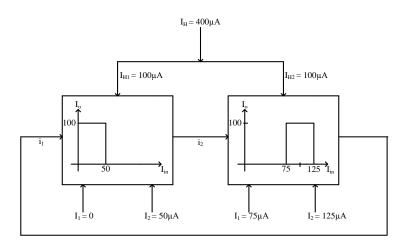

As an example for calculation of the time delay of the circuit, the CMOS Core Circuit which was developed as a classifier integrated circuit and manufactured as DU-TCC1209 in 2009 [13], has been used. The block diagram and the transfer characteristic of the core circuit are shown in Figure 2.8 and Figure 2.9, respectively.

The input-output transfer characteristics of the core circuit shown in Figure 2.9 can be expressed as:

$$I_{out} = \begin{cases} I_H & if \quad I_1 < I_{in} < I_2 \\ 0 & otherwise \end{cases}$$

(2.21)

Figure 2.8 : Core circuit block diagram.

Figure 2.9 : Transfer characteristic of the core circuit.

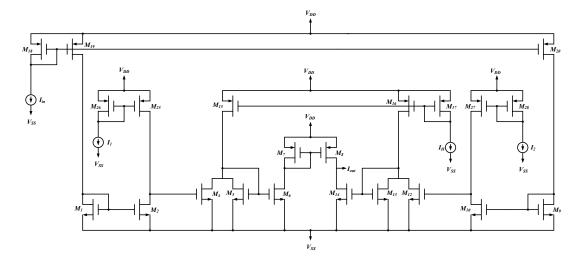

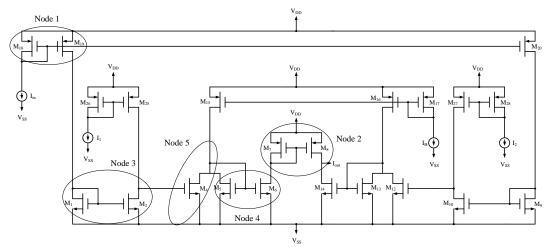

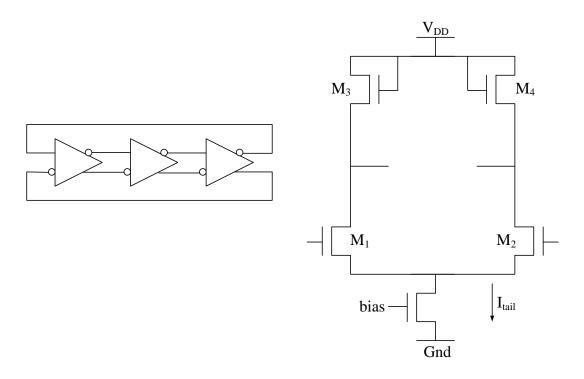

The CMOS implementation of the classifier core circuit is shown in Figure 2.10. The core circuit is constituted with two threshold circuits and one subtructor circuit.  $I_1$ ,  $I_2$  and  $I_H$  called as external control currents. With simple current mirror structures, input currents are performed to the core circuit. The change of the output waveform in a horizantal position is provided by the currents  $I_1$  and  $I_2$ ,  $I_H$  describes the amplitude of the output waveform. The transistors  $M_1$ ,  $M_2$ ,  $M_4$ ,  $M_5$  and  $M_9$ ,  $M_{10}$ ,  $M_{12}$ ,  $M_{13}$  create two threshold circuits shown in Figure 2.10. The transistors  $M_7$  and  $M_8$  are used to generate a subtractor circuit with simple current mirror structure. The transistors  $M_{15}$ ,  $M_{16}$  and  $M_{17}$  are used to apply the same  $I_H$  current for the threshold circuits. Similarly, the transistors  $M_{18}$ ,  $M_{19}$ , and  $M_{20}$  are used to apply the same  $I_{in}$  current to both of the threshold circuits.

Figure 2.10 : CMOS implementation of the core circuit [26].

The core circuit in Figure 2.10 has been simulated with  $0.35\mu m$  TSMC CMOS technology parameters using SPICE simulation software. The supply voltages  $V_{DD}$  and  $V_{SS}$  were selected  $\pm 1.65V$ . The transistors dimensions are given in Table 2.1.

| MOSFET                                                                                                          | W[µm] | L[µm] |

|-----------------------------------------------------------------------------------------------------------------|-------|-------|

| $M_1, M_2, M_9, M_{10}$                                                                                         | 42    | 1.05  |

| $\begin{array}{l} M_7,M_8,M_{15},M_{16},M_{17},M_{18},M_{19},\\ M_{20},M_{25},M_{26},M_{27},M_{28} \end{array}$ | 21    | 1.05  |

| $M_4, M_5, M_6, M_{12}, M_{13}, M_{14}, M_{21}, M_{22}$                                                         | 10.5  | 1.05  |

Table 2.1: Dimensions of the CMOS Transistors in Core Circuit.

# **3. TIME DELAY CALCULATION**

The main aim of this paper is to give a general calculation of time delay in currentmode circuits. There are two phases in the calculation of the time delay: First, an equivalent circuit model has to be developed then analyzing the obtained equivalent circuit model, time delay formulae have to be extracted in terms of circuit elements' parameters.

### **3.1 Equivalent Circuit Model**

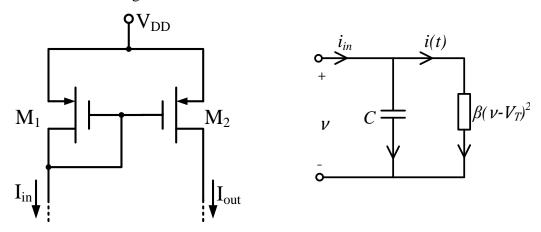

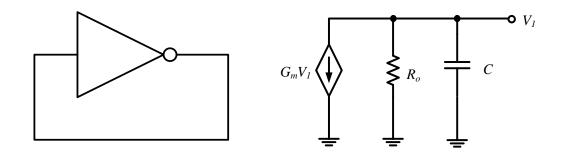

As a simple current-mode circuit, a PMOS basic current mirror is selected for time delay investigation. In Figure 3.1(a), a PMOS current-mirror, which is widely used in complex current-mode circuits is shown. Both of the transistors are assumed to operate in saturation region. The large-signal equivalent circuit model of the PMOS transistor  $M_1$  is shown in Figure 3.1(b); it consists of a capacitor in parallel with a non-linear resistor. The capacitor *C* in Figure 3.1(b) represents the total parasitic capacitances of MOS transistors (including the loading capacitors of  $M_2$ .) The non-linear resistor stems from the dependent current source of the MOS transistor model working in saturation region.  $r_0$  is the output resistance (not shown) which will be taken into account in Figure 3.2.

**Figure 3.1 :** (a) PMOS circuit model. (b) Large-signal Equivalent circuit model without  $r_o$ .

According to Kirchhoff's Current Law the following equation can be written for the circuit of Figure 3.1(b).

$$C\frac{dv(t)}{dt} = -\beta \left( v(t) - V_T \right)^2 + i_{in}(t)$$

(3.1)

where  $\beta = 1/2\mu_p C_{ox} W/L$  is the gain factor of MOS transistors, the parameters  $\mu_p$ ,  $C_{ox}$ , W, L have their usual meanings and  $V_T$  is the threshold voltage.

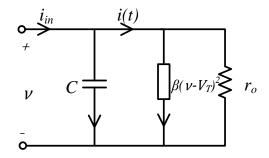

To see the effect of the output resistance of the transistors on time delay, similar analyses can be performed. The equivalent circuit model with transistor output resistance  $r_0$  is illustrated in Figure 3.2.

Figure 3.2 : Large-signal equivalent circuit model with *r*<sub>o</sub> [27].

Adding the output resistance and writing the KCL at the input node, the Eq. (3.1) is modified as:

$$C\frac{d\nu(t)}{dt} = -\beta(\nu(t) - V_T)^2 + I_{OH} - \frac{\nu(t)}{r_o}$$

(3.2)

## **3.2 Junction Capacitances Calculations**

As mentioned before, the total parasitic capacitance has the main effect on the value of the time delay. Therefore, a precise calculation of these capacitances is an important issue for current-mode circuits. As an example for calculation of the total parasitic capacitances at the input node of the circuit, the CMOS Core Circuit which was developed as a classifier integrated circuit and manufactured as DU-TCC1209 in 2009 [26], has been used. The CMOS implementation of the classifier core circuit is shown in Figure 3.3.

Figure 3.3 : CMOS implementation of the core circuit [26].

# 3.2.1 Junction capacitances calculations for Node 1

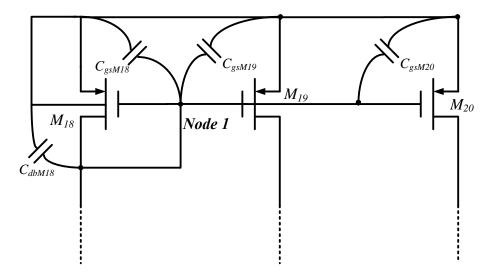

To calculate the total parasitic capacitances, the input section of the classifier core circuit with parasitic capacitances of each transistor is shown in Figure 3.4.

Figure 3.4 : Input section of the core cell with parasitic capacitances [27].

The parasitic capacitances  $C_{dbM18}$ ,  $C_{gsM18}$ ,  $C_{gsM19}$ ,  $C_{gsM20}$  affecting Node 1 are all connected in parallel to each other hence the equivalent overall input capacitance is calculated approximately as shown in Eq. (3.3).

$$C_{eq} = C_{db}M_{18} + C_{gs}M_{18} + C_{gs}M_{19} + C_{gs}M_{20} + 7C_{ov}$$

(3.3)

The formula of the gate to source capacitance  $C_{gs}$  is given by:

$$C_{gs} = \frac{2}{3} \times C_{ox} \times W \times L \tag{3.4}$$

where,  $C_{ox}$  is the capacitance per unit area of the gate dielectric, W and L are width and length of the transistor respectively. In addition,  $C_{ov}$  in expression (3.3) is the overlap capacitance of each transistor effecting Node 1. The drain-bulk junction capacitance ( $C_{db}$ ) is found from the following Eq. (3.5):

$$C_{db} = \left(\frac{CJ}{\left(1 + \frac{VDB}{PB}\right)^{MJ}} \times AD\right) + \left(\frac{CJSW}{\left(1 + \frac{VDB}{PB}\right)^{MJSW}} \times PD\right)$$

(3.5)

To find the numeric value of the the drain bulk capacitance of M<sub>18</sub> transistor ( $C_{dbM18}$ ) firstly the area of the drain region of MOSFET as called *AD* is calculated where  $xj = 3 \times 10^{-7}m$  called the junction depth as shown in Eq. (3.6) and *AD* is found  $12.915 \times 10^{-12}$ .

$$AD = 2(W \times xj) + 2(X * xj) (xj = 3 \times 10^{-7}m)$$

(3.6)

$$AD = (2 \times (21 \times 3 \times 10^{-7})) + 2 \times ((1.05/2) \times 3 \times 10^{-7})$$

= 12.915 \times 10^{-12} (3.7)

Secondly, *PD* is calculated as called the perimeter of the drain region of MOSFET from following equalities:

$$PD = 2 \times (W + X), \ X = X + Lov \to X = L/2$$

(3.8)

$$PD = 2 * (21 + (1.05/2)) = 43.05 * 10^{-6}$$

(3.9)

Current phase is finding the numeric value of drain bulk capacitance by using Eq. (3.4). The numerical values of parasitic capacitances of transistors shown in Figure 3.4 are given as follows for  $0.35\mu$ m CMOS technology as shown in Table 3.1. These values are taken from the PSpice Model. By using these values  $C_{dbM18}$  is calculated 14.115fF.

$$C_{dbM18} = \left(\frac{1.419508 \times 10^{-3}}{\left(1 + \frac{0.56}{0.8152753}\right)^{0.5}} \times (12.915 \times 10^{-12})\right) + \left(\frac{4.813504 \times 10^{-10}}{\left(1 + \frac{0.56}{0.8152753}\right)^{0.5}} \times (43.05 \times 10^{-12})\right)$$

$$= 14.115 \times 10^{-15} F$$

(3.10)

| Symbols of source code | Description                                                                 | Value                                                                 |

|------------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------|

| TOX                    | Gate oxide thickness                                                        | 7.9*10 <sup>-9</sup> (m)                                              |

| CJ                     | Source-drain (S/D) bottom junction capacitance per unit area at zero bias   | $\begin{array}{c} 1.419508 {}^{*}10^{{}^{-3}} \\ (F/m^2) \end{array}$ |

| CJSW                   | S/D field oxide side wall junction capacitance per unit length at zero bias | 4.813504*10 <sup>-10</sup><br>(F/m)                                   |

| PB                     | Bottom junction built in potential                                          | 0.8152753 (V)                                                         |

| MJ                     | S/D bottom junction capacitance grading coefficient                         | 0.5                                                                   |

| MJSW                   | S/D field oxide side wall junction capacitance grading coefficient          | 0.5                                                                   |

| XJ                     | Junction depth                                                              | $3*10^{-7}$ m                                                         |

| UO                     | Surface mobility                                                            | 212.2319801*10 <sup>-4</sup><br>(m <sup>2</sup> /V.s)                 |

| THETA                  | Mobility Modulation                                                         | 0.2020774 (1/s)                                                       |

| VTO                    | Zero-bias threshold voltage                                                 | -0.7140674 (V)                                                        |

#### **Table 3.1 :** PSpice Model Parameters.

To find the gate to source of the capacitance of transistor  $M_{18}$ ,  $M_{19}$  and  $M_{20}$  are found from Eq. (3.4). Three of the capacitances values are equal to each other because of the dimensions (*W* and *L*) of transistors are equal as following:

$$C_{gsM18} = C_{gsM19} = C_{gsM20} = \left(\frac{2}{3} \times 0.00436899 \times 21 \times 1.05 \times 10^{-12}\right)$$

= 64.2242 × 10<sup>-15</sup>F (3.11)

The overlap capacitance, which appears due to the fact that source and drain diffusions extend under the gate oxide, is computed as:

$$C_{ov} = W \times L_{ov} \times C_{ox} \tag{3.12}$$

where  $L_{ov}$  is overlap length and typically  $0.1 \times L$ . The value  $C_{ov}$  must be added to the  $C_{gs}$  and  $C_{gd}$  for each transistor. With a routine analysis and applying Miller effect it can be seen that a total number of  $7C_{ov}$  appears in expression (3.3). In the light of this information, overlap capacitance  $2*C_{gdovM19} + 2*C_{gdovM20} + C_{gsov18}$ +  $C_{gsov19} + C_{gsov20} = 7C_{ov}$  (The factor 2 comes from Miller effect) can be found as:

$$C_{ov} = 21 \times 10^{-6} \times 0.1 \times 1.05 \times 10^{-6} \times 0.00436899 = 9.63362 \times 10^{-15} F$$

(3.13)

To sum up  $C_{gsM18} = C_{gsM19} = C_{gsM20} = 64.22$  fF,  $C_{dbM18} = 14.11$  fF,  $C_{ov} = 9.6$  fF. So the equivalent capacitance is calculated in Eq. (3.14) and  $C_{eq} = 274.223$  fF.

$$C_{eq} = 1.4115 \times 10^{-14} + (3 \times 6.42242 \times 10^{-14}) + (7 \times 9.63362 \times 10^{-15}) = 274.22294 \times 10^{-15} F$$

(3.14)

## 3.3 Time Delay Calculation for the Core Circuit

## **3.3.1 Delay calculations for Node 1**

### 3.3.1.1 Time delay calculations without $r_o$

The Input-Output (I-O) waveforms of the current-mirror circuit are shown in Figure 2.6 and the average propagation delay is given in Eq. (2.16).

The next step is to calculate the time delay  $\tau_{PLH}$  from the equivalent circuit model, which is given in Figure 3.1(b). To do this, the value of the current i(t) at time  $t_1$  must be equated to half of the value of the input current ( $I_{OH}$ ). To find the time  $t_1$  Eq. (3.1) must be used; that is at  $t_1$  Eq. (3.15) must be satisfied [27].

$$i(t_1) = \frac{I_{OH}}{2} \Leftrightarrow C \ \frac{dv(t_1)}{dt} = \frac{I_{OH}}{2}$$

(3.15)

By substituting Eq. (3.15) into Eq. (3.1), the following set of equations can be reached.

$$C\frac{dv(t_{I})}{dt} = -\beta (v(t_{I})-V_{T})^{2} + I_{OH} = \frac{I_{OH}}{2}$$

(3.16)

$$\beta(v(t_1) - V_T)^2 = \frac{I_{OH}}{2}$$

(3.17)

$$v(t_1) - V_T = \frac{1}{\sqrt{\frac{I_{OH}}{2\beta}}}$$

(3.18)

$$v(t_I) = V_T \mp \sqrt{\frac{I_{OH}}{2\beta}}$$

(3.19)

Eq. (3.19) shows the input node voltage at time  $t_1$ . Taking  $t_0 = 0$  and solving Eq. (3.1) with initial value of  $v(0) = V_{T_1}$  one can find the following expression for the voltage v(t):

$$V(t) = V_T + \frac{\sqrt{I_{OH}} \tanh[\frac{\sqrt{I_{OH}}\sqrt{\beta}}{C}t]}{\sqrt{\beta}}$$

(3.20)

From Eq. (3.20), *t* can be found as:

$$\operatorname{arctanh}\left[\frac{\nu(t) - V_{T}}{\sqrt{I_{OH}/\beta}}\right]$$

$$t = \frac{\sqrt{I_{OH}\sqrt{\beta}}}{\sqrt{I_{OH}\sqrt{\beta}}}$$

(3.21)

Substituting  $v(t_1)$  from (3.19) into (3.21) for v(t), the time delay is obtained as:

$$t_I = 0.8814 \times \frac{C}{\sqrt{I_{OH} \times \beta}} = \tau_{PLH}$$

(3.22)

Thus, with Eq. (3.22) a very simple time delay formulation is achieved for the current mirror. In fact, the propagation delay  $\tau_{PLH} = t_1$  depends on the value of the total parasitic capacitances (*C*), the input current initial value  $I_{OH}$  and the parameter  $\beta$ . Thus, by minimizing the total value of the parasitic capacitances, the propagation delay can be reduced; another possibility would be to increase the ratio *W/L* increasing  $\beta$  at the denominator.

For calculating the time delay on Node 1,  $\beta$  must be calculated with using the following set of equations:

$$\mu = \frac{UO}{(1 + THETA(VGS - VTO))}$$

(3.23)

where *UO* is surface mobility, *THETA* is mobility modulation, *VTO* is zero-bias threshold voltage. Their numerical values are given in Table 3.1 and  $\mu$  is calculated as:

$$\mu = \frac{212.2319801^{*10^{-4}}}{(1+0.2020774 \cdot (0.56 \cdot (-0.7140674)))} = 0.0168778$$

(3.24)

$C_{ox}$  is the capacitance per unit area of the gate dielectric is defined as:

$$C_{ox} = \frac{\varepsilon_{ox}}{t_{ox}}$$

,  $\varepsilon_{ox} = 3.9 \times \varepsilon_o$ , where  $\varepsilon_o = 8.85 \times 10^{-12} F/m$  (3.25)

By using Eq. (3.25)  $C_{ox}$  is found as  $C_{ox} = 0.00436899$ .

$\beta$  is calculated using the values obtained in equation (3.24) and (3.25) as given by following expression and  $\beta = 737.389 \,(\mu \text{A/V}^2)$  is found:

$$\beta = \frac{1}{2} \mu Cox W/L \qquad (3.26)$$

To sum up,  $\beta = 737.389 \ (\mu \text{A/V}^2)$ ,  $I_{OH} = 50\mu\text{A}$  and  $V_T = 0.714$  V. Using these specified values in Eq. (3.22) the time delay is found to be  $\tau_{PLH} = 1.26$  ns as shown in Eq. (3.27).

$$t_1 = 0.8814 * \frac{2.7422294 \times 10^{-13}}{\sqrt{50 * 10^{-6} * 0.000737389}} = 1.26 \, ns \tag{3.27}$$

## 3.3.1.2 Time delay calculations with r<sub>o</sub>

The equivalent circuit model with transistor output resistance  $r_0$  is illustrated in Figure 3.2 [28].

Solving the Eq. (3.2) differential equation for the time value  $t_1$  at which  $i(t_1) = \frac{I_{OH}}{2}$ , results in:

$$t_{1} = \frac{(ArcTan[\frac{-v(t_{1})2r_{0}\beta - 1 + 2r_{0}V_{T}\beta}{\sqrt{-1 + 4r_{0}(-I_{OH}r_{0} + V_{T})\beta}}] - ArcTan[\frac{-1 + 2r_{0}V_{T}\beta - 2r_{0}\beta V_{T}}{\sqrt{-1 + 4r_{0}(-I_{OH}r_{0} + V_{T})\beta}}]) 2Cr_{0}}{\sqrt{-1 + 4r_{0}(-I_{OH}r_{0} + V_{T})\beta}}$$

(3.28)

where;

$$v(t_1) = \frac{-1 + 2r_o V_T \beta \mp \sqrt{1 + 2r_o (l_{OH} r_o - 2V_T)\beta}}{2r_o \beta}$$

(3.29)

Taking into account the output resistance of the MOS transistors ( $r_o = 100 \ k\Omega$ ) and using equalities (3.28) and (3.29) the time delay value is found to be  $\tau_{PLH}=1.4 \ ns$  which shows an increase of 10% in the time delay when  $r_o$  is considered.

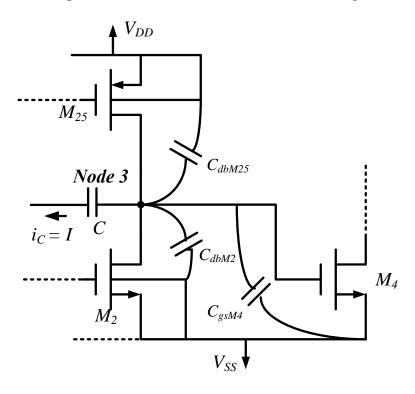

### 3.3.2 Delay calculations for Node 3

To calculate the time delay of the second type circuit in the core circuit on Node 3, the total parasitic capacitances of each transistor are shown in Figure 3.5 [28].

Figure 3.5 : MOS Model with parasitic capacitances for Node 3.

The parasitic capacitances  $C_{dbM25}$ ,  $C_{dbM2}$ ,  $C_{gsM4}$ , which influence Node 3 are all connected in parallel hence, the equivalent overall input capacitance is calculated approximately as given by expression (3.30).

$$C_{eq} = C_{dbM25} + C_{dbM2} + C_{gsM4}$$

(3.30)

The formula of the gate to source capacitance  $C_{gs}$  and the drain-bulk junction capacitance  $C_{db}$  is found from the expressions (2.9) and (2.10) respectively.

The numerical values of parasitic capacitances of the transistors shown in Figure 3.5 are given as follows for the CMOS technology  $(0.35\mu m)$ :

$C_{gsM4} = 32.11$  fF,  $C_{dbM2} = 27.88$  fF,  $C_{dbM25} = 14.11$  fF. So the equivalent capacitance is  $C_{eq} = 74.1$  fF. In addition,  $I_I = 20\mu$ A and  $V_{DD} = 1.65$  V,  $V_{SS} = -1.65$  V  $V_T = 0.545$  V. Using these specified values in equality (3.35) the time delay is found to be  $\tau_{PLH} = 5.1$  ns.

In order to derive the expression (3.31) for the time delay on Node 3 the value of the current I, which is called  $I_1$  in the core circuit, is the negative sum of the drain current of transistors  $M_{25}$ ,  $M_2$  and is constant:

$$I = i_C = -(i_{DM25} + i_{DM2})$$

(3.31)

The gate voltage of transistor  $M_4$  is shown in equality (3.32), where  $V_T = 0.545$  V.

$$V_{G4} = V_{SS} + V_T$$

(3.32)

To find the time delay  $t_2$  on Node 3, the following set of equalities can be written:

$$\frac{1}{2}(V_{DD} - V_{G4}) = \frac{1}{C} \int_0^{t_2} I \, dt$$

(3.33)

$$\frac{1}{2}(V_{DD} - V_{G4}) = \frac{I \times t_2}{C}$$

(3.34)

then using equality (3.34), the time delay  $\tau_{PLH}$  is obtained as:

$$t_2 = \frac{C(V_{DD} - (V_{SS} + V_T))}{2I}$$

(3.35)

Hence, with expression (3.35) a very simple time delay formulation is obtained for the second type sub-circuit in the Core Circuit. Actually, the propagation delay on Node 3  $\tau_{PLH} = t_2$  depends on the value of the total parasitic capacitances (*C*), the input current value *I*, supply voltages  $V_{DD}$ ,  $V_{SS}$  and gate voltage of M<sub>4</sub> ( $V_{G4}$ ). Consequently, minimizing the total value of the parasitic capacitances the propagation delay can be decreased, as was the case for Node 1.

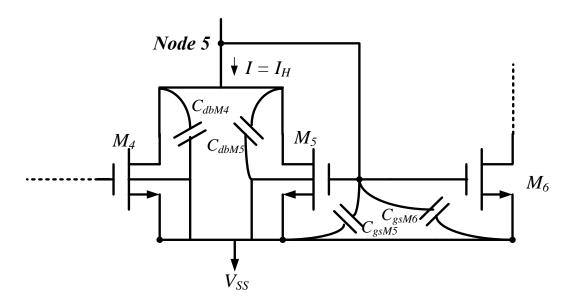

#### 3.3.3 Delay calculations for Node 5

In order to calculate the time delay for the third type circuit on Node 5 of the Core Circuit, total parasitic capacitances of each transistor are shown in Figure 3.6 [28].

Figure 3.6 : MOS Model with parasitic capacitances for Node 5 [28].

The parasitic capacitances  $C_{dbM4}$ ,  $C_{dbM5}$ ,  $C_{dbM15}$ ,  $C_{gsM5}$  and  $C_{gsM6}$  affecting Node 5 are also all connected in parallel and the equivalent overall input capacitance is calculated approximately as shown with equality (3.36).

$$C_{eq} = C_{dbM4} + C_{dbM5} + C_{gsM5} + C_{dbM15} + C_{gsM6}$$

(3.36)

The parasitic capacitances of the transistors shown in Figure 3.6 for the CMOS technology  $(0.35\mu m)$  are given as follows:

$C_{dbM4} = C_{dbM5} = 7.22$  fF,  $C_{dbM15} = 14.11$  fF,  $C_{gsM5} = C_{gsM6} = 32.11$  fF. Hence, the equivalent capacitance is  $C_{eq} = 92.77$  fF. In addition,  $I_H = 50\mu$ A and  $V_{DD} = 1.65$  V,  $V_{SS} = -1.65$  V  $V_T = 0.545$  V. Using these specified values in Eq. (3.41) the time delay is found to be  $\tau_{PLH} = 1.9$  ns.

In order to derive expression (3.41) the time delay on Node 5, the value of the current *I* being equal to  $I_H$  as can be seen from Figure 3.6:

$$I = (i_{DM4} + i_{DM5}) \tag{3.37}$$

is obtained. The drain voltage of transistor  $M_5$  is shown in equality (3.38) with  $V_T = 0.545$  V.

$$V_{D5} = V_{SS} + V_T \tag{3.38}$$

To find the time delay  $t_3$  on Node 5, the following set of equations can be written:

$$\frac{1}{2}(V_{D5} - V_{SS}) = \frac{1}{C} \int_0^{t_3} I \, dt$$

(3.39)

$$\frac{1}{2}(V_{D5} - V_{SS}) = \frac{I \times t_3}{C}$$

(3.40)

Using Eq. (3.40), the time delay  $\tau_{PLH} = t_3$  is obtained as:

$$t_3 = \frac{CV_{\rm T}}{2I} \tag{3.41}$$

Hence, with equality (3.41) a very simple time delay formulation is obtained for the third type circuit in the core circuit. Actually, the propagation delay on Node 5  $\tau_{PLH} = t_3$  depends on the value of the total parasitic capacitances (*C*), the input current initial value *I* and threshold voltage  $V_T$ . Consequently, as for Node 1 and Node 2, by minimizing the total value of the parasitic capacitances the propagation delay can be decreased.

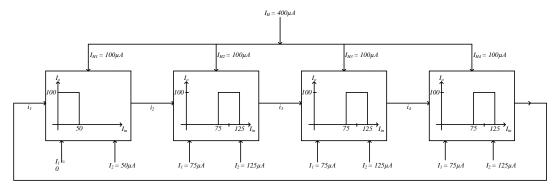

The total time delay of the core circuit can now be calculated analytically by adding delays of the stages from the input to the output considering that the subcircuit at nodes 1 and 2 are the same whereas the subcircuit at node 3 is four times wider than the one at node 4 that is, delays for Node 1:  $t_1$ , Node 3:  $t_2$ , Node 5:  $t_3$ , Node 2:  $t_1$ , Node 4: 0.25 $t_2$ , as given with expression (3.42):

$$t_{d(total)} = 2t_1 + 1.25t_2 + t_3 = 11.1$$

ns. (3.42)

#### **3.4 SPICE Simulation Results**

The core circuit in Figure 3.3 has been simulated with  $0.35\mu m$  TSMC CMOS technology parameters using SPICE simulation software. The supply voltages  $V_{DD}$  and  $V_{SS}$  were selected as  $\pm 1.65V$ . The transistors' dimensions are given in Table 2.1.

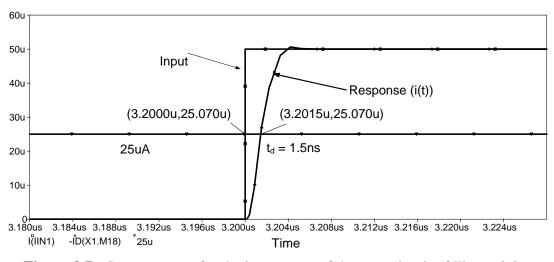

### 3.4.1 Simulation of subcircuit at Node 1

First, the input section (Node 1) of the core cell has been simulated. Resulting input waveform and output waveform obtained from the drain of transistor  $M_{19}$  of the CMOS core circuit are shown in Figure 3.7. The resulting time delay  $\tau_{PLH}$  is equal to 1.5ns for an input current of 50µA. From calculations using expressions (3.22) and

(3.28), time delay without  $r_o$  effect is 1.26 ns and with  $r_o$ , 1.4 ns, which are very close to the value obtained from the simulation; thus the simulation results verify well the proposed circuit model and the calculations.

Figure 3.7 : Step response for the input stage of the core circuit of Figure 3.3.

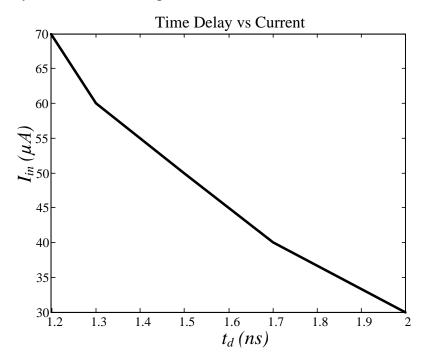

Time delay versus input current graph is shown in Figure 3.8. By taking the input current values as  $30\mu A$ ,  $40\mu A$ ,  $50\mu A$ ,  $60\mu A$ ,  $70\mu A$ , the time delays  $\tau_{PLH}$  are found as 2ns, 1.7ns, 1.5ns, 1.3ns and 1.2ns, respectively. As indicated, the lower the input current of the circuit the higher is the time delay; as expected one way of reducing the time delay is to increase the input current.

Figure 3.8 : Time delay versus input current graph.

#### 3.4.2 Simulation of subcircuit at Node 3

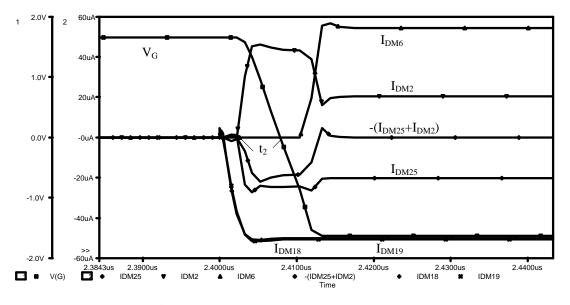

Next, simulated currents obtained from the drain of transistors  $M_2$ ,  $M_6$ ,  $M_{18}$ ,  $M_{19}$ ,  $M_{25}$ of the CMOS core circuit are shown in Figure 3.9. Based on this description, by taking  $I_H = 50\mu$ A,  $I_1 = 20\mu$ A and  $I_2 = 80\mu$ A, the simulation can be interpreted as follows: in the first region, when  $I_{in} < I_1$ , the gate voltage of transistor  $M_4$ ,  $V_{G4}$  is equal to the supply voltage  $V_{DD}$  ( $V_{G4} \cong V_{DD} = 1.65V$ ). The transistors' operation regions are:  $M_{25}$  in triode region,  $M_2$  is off,  $M_4$  is in triode region. In the second region, when  $I_{in}$  is increased  $M_2$  operates in triode and  $M_{25}$  is in the saturation region. In case of the third region, when the gate voltage  $M_4$  is equal to sum of  $V_{SS}$  and  $V_T$  the transistor  $M_4$  is off and  $M_{25}$  is on. Under these conditions drain current of  $M_6$  ( $I_{DM6}$ ) and output current ( $I_{out}$ ) are equal to  $I_H$ . With these values, simulated time delay becomes  $\tau_{PLH} = t_2 = 6$  ns.

Figure 3.9 : Simulation Result for Node 3.

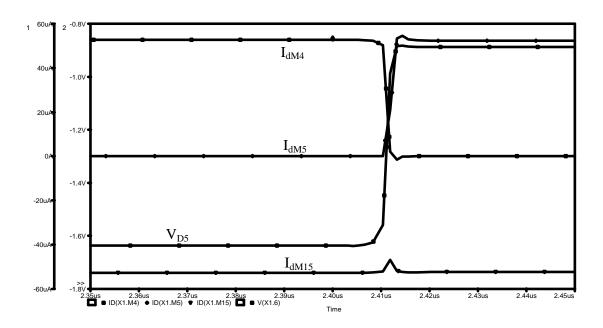

#### 3.4.3 Simulation of subcircuit at Node 5

The following simulation for Node 5 is shown in Figure 3.10. Simulated currents obtained from the drain of transistors  $M_{4}$ ,  $M_{5}$ ,  $M_{15}$  of the CMOS core circuit are shown. Based on this condition, by taking  $I_{H} = 50\mu$ A,  $I_{1} = 20\mu$ A and  $I_{2} = 80\mu$ A. With these values simulated time delay becomes  $\tau_{PLH} = t_{3} = 1.9$ ns and the total simulated delay is:

$t_{d(total)} = 2t_1 + 1.25t_2 + t_3 = 12.4$ ns. (3.43)

Figure 3.10 : Simulation Result for Node 5.

# 3.4.4 Simulation of the entire core cell

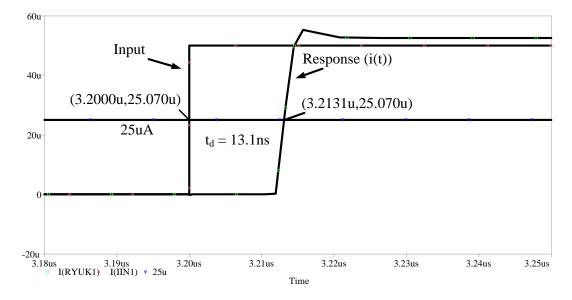

Simulated input waveform and output waveform of the entire core circuit given in Figure 3.3 is shown in Figure 3.11. By taking  $I_H = 50\mu A$ ,  $I_I = 20\mu A$ ,  $I_2 = 80\mu A$  and  $I_{in} = 50\mu A$  the resulting time delay  $\tau_{PLH}$  is equal to 13.1 ns.

Figure 3.11 : Step response for the core circuit of Figure 3.3.

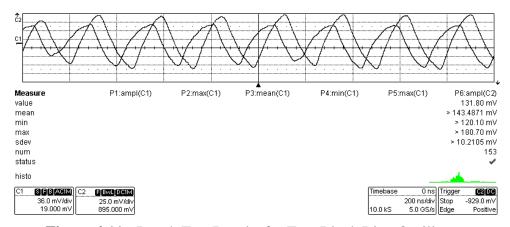

#### **3.5 Comparison with Bench Test Results**

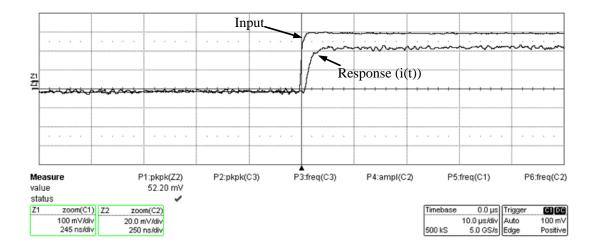

In addition, the circuit in Figure 3.3 has been bench tested using the CMOS Core Circuit in DU-TCC1209 IC. The outcome of the measurements is shown in Figure 3.12. The input waveform and the resulting output waveform for  $I_H = 50\mu$ A,  $I_I = 45\mu$ A,  $I_2 = 100\mu$ A and  $I_{in} = 60\mu$ A (for  $I_{in}$  a voltage of 300mV and a resistor of 5k $\Omega$ , for  $I_H$  50mV and 1k $\Omega$  were used) show a good agreement with the simulated results, the measured time delay  $\tau_{PLH}$  being approximately equal to 25 ns (this difference in measured delay can be explained with the existence of stray and probe capacitances).

In addition, the circuit in Figure 3.1(a), using CD 4007 CMOS array transistors with +5 V supply voltage was bench tested experimentally. The output current is taken from the drain of the transistor M<sub>2</sub>.

From calculations time delay was found as 11.1ns, from simulations of Node 1, Node 3 and Node 5 as 12.4ns, from the simulation of the entire core circuit as 13.1ns and as 25ns (for  $I_H = 50\mu$ A) from the bench test of the entire core cell. That, calculated, simulated and measured delays agree quite well can be concluded.

Figure 3.12 : Bench Test Results for Core Circuit.