## **PROCEEDINGS OF SPIE**

SPIEDigitalLibrary.org/conference-proceedings-of-spie

# Universal and inductorless DC/DC converter for multi-output power supplies in sensor and actuator networks

Sergio Saponara, Gabriele Ciarpi

Sergio Saponara, Gabriele Ciarpi, "Universal and inductorless DC/DC converter for multi-output power supplies in sensor and actuator networks," Proc. SPIE 10246, Smart Sensors, Actuators, and MEMS VIII, 1024612 (31 May 2017); doi: 10.1117/12.2265188

Event: SPIE Microtechnologies, 2017, Barcelona, Spain

### Universal and inductorless DC/DC converter for multi-output power supplies in sensor and actuator networks

Sergio Saponara, Gabriele Ciarpi

Dip. Ingegneria dell'Informazione, Università di Pisa, via G. Caruso 16, 56122, Pisa, I

#### ABSTRACT

This work proposes a universal and inductorless DC/DC converter that can be used for a wide input range, from few V to 60 V, to regulate output voltages from 5 V down to 1 V in Sensor and Actuator Network nodes. The proposed converter has been developed within the Athenis3D European project. It is composed by a cascade of multiple switching capacitor stages, with a proper skip-mode control to implement both step-down and step-up converting ratios, thus regulating all input sources to a voltage of about 6 V. These switching stages are further cascaded with linear regulators, which can provide stable output voltages down to 1 V. The multi-output regulator has been realized as a single-chip in a low-cost 0.35 µm CMOS technology. It is available as a naked die or in a ceramic package. The only needed external components are surface mount capacitors, which can be integrated on top of the naked chip die, creating a 3D structure, using trench capacitors embedded in a passive interposing layer. This way the size of the power management unit is further minimized. An advantage of the proposed converter is that it isn't optimized for a particular input voltage, therefore it can be used with no constant input power, like power harvesting systems (e.g. solar cells, wind and water turbines) and very disturbed power supplies.

Keywords: DC/DC Converter, Inductorless Converter, 48 V power systems, Integrated Passive Devices

#### 1. INTRODUCTION

A key building block for a node of a Sensor and Actuator Network (SAN) is the DC/DC converter. While for low-power sensing applications the power source is typically a few Volts (e.g. 3.6 V for a Li-Ion cell), in case of vehicles, satellites, telecom apparatus, industrial machines, robots, the DC power source can be tens of Volts. For example, the power supply in the automotive world is at least 12 V, and it is going towards 48 V for hybrid and electric vehicles [1]. Electric scooters, e-bikes and trucks use 24 V to 36 V batteries. The standard telecom power bus is 48 V, as well as that on-board a satellite. To address the low voltage supply requirements of sensors and control boards (from 5 V down to 1 V), a DC/DC converter able to regulate a large input voltage range is needed. However, in the market there are thousands of DC/DC converters, with different performances and costs, each addressing a specific application. Moreover, to achieve high-energy efficiency the DC/DC converters usually adopt inductors, which are cumbersome and difficult to integrate.

Two types of device are dominating the market of the DC/DC converters: the linear converters and the switching converters with inductors. Despite the popularity of switching converters, the linear regulators still account for a high percentage of power management systems. They have optimal integration features, because use few small components, only a pass element, a feedback network and some bypass capacitors. Thanks to their best output voltage in terms of ripple, noise and disturb rejection of all converter topologies linear regulators are widely used in high sensitivity systems. On the other side their operation modality, based on the modulation of the pass element resistance, leads to a lower efficiency than switching converters and limits their use to low power applications. For medium power systems, this low efficiency is paid with an area cost due to the non-integration of the pass element and to the use of its cumbersome heat-sink. For medium-high power the switching converters are used for their better efficiency (up to 75 %), and thanks to their ability to do step up (boost), step down (buck), and invert voltages conversion they cover all the applications. Their major area cost and assembly effort is due to their complexity and to the use of non-integrated elements as inductors, diodes and big filter capacitors. In addition, using switching techniques, they are affected by electromagnetic interference problems that are usually countered with expensive solutions. Some architectures combining the two converters are designed to obtain high efficiency and good output quality, but they continue to have low integrability features [2].

Smart Sensors, Actuators, and MEMS VIII, edited by Luis Fonseca, Mika Prunnila, Erwin Peiner, Proc. of SPIE Vol. 10246, 1024612 · © 2017 SPIE · CCC code: 0277-786X/17/\$18 · doi: 10.1117/12.2265188

#### 2. INDUCTORLESS CONVERTER

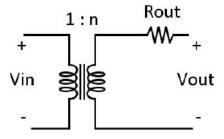

The switched capacitor converters (SC) can be inserted between the previous converter topologies because they are characterized by the use of only capacitors and switches, the latter being realized with mosfets. SC converters can be integrated in a single chip with the benefit of a smaller area and assembly cost. In addition, they have higher efficiency performance than linear converters. On the other hand, they can achieve the efficiency of inductor-based switching converters only for discrete voltage ratios. The voltage conversion ratios (VCRs) of these converters are mainly determined by the repetitive changing of the circuit structure, thanks to switches, which modify the capacitors connections. The SC converter can be modelled, at low frequency, as an ideal transformer to represent the VCRs while the losses are taken into account with an output resistor, see Fig. 1.

Fig. 1: Model of a generic Switched Capacitor converter

The output resistor is typically calculated considering the charge flow analysis, which analyses the converter in two welldefined operating regimes: the Slow Switching Limit (SSL) and the Fast Switching Limit (FSL). In SSL, the converter operates at a frequency much lower than the time constant of the converter, thereby allowing the full charge and discharge of the capacitors. The losses are then dominated by the charge transfer between capacitors, see eq. (1). Where  $f_{sw}$  is the switching frequency and  $C_i$  is the value of the i-th fly capacitor used in the converter.

$$R_{SSL} \propto \frac{1}{f_{sw}} \sum_{i \in cap} \frac{1}{C_i}$$

(1)

In FSL, the converter operates with a switching frequency much higher than the time constant of the converter, limiting the charge and discharge transient times of the capacitors, then the conduction losses due to the parasitic resistive elements ( $R_{ON}$ ) dominate, see eq. (2). Where *D* is the duty-cycle of the signals used to drive the switches and  $R_i$  is the i-th resistance value of the switches in the on-state.

$$R_{FSL} \propto \frac{1}{D} \sum_{i \in sw} R_i \tag{2}$$

Both approaches can be unified by considering both natures as complementary. In [3], it is demonstrated that the total output impedance is accurately approximated as eq. (3).

$$R_{out\_eq} \approx \sqrt{\left[(R_{SSL})^2 + (R_{FSL})^2\right]} \tag{3}$$

The main feature of a DC/DC converter is regulating the output voltage and, considering the model, there are two ways to get it: i) change the VCR with the network reconfiguration or ii) change the output resistor. The first technique keeps high the efficiency but requires a very large number of VCRs to obtain a good regulated output voltage. A large number of the VCRs is obtainable only with a very complex network. The number of capacitors and switches necessary to obtain the desired VCRs can be calculated with the Makowski's theorem [4]. To reduce the complexity of the network, keeping a regulated output, it is possible changing the value of the output resistance with a feedback network that typically modulates the frequency or the duty cycle of the switching signal, see eq. (1) and eq. (2). This technique allows achieving an output signal quality close to the linear converter but it is paid with lower efficiency performance.

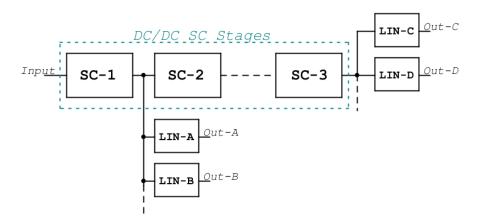

Each device in a complex system may require a different supply voltage level in order to optimize its performance so, typically, the power management unit has more than one output voltage. For this reason, we have developed a modular model of a generic converter, see Fig. 2, that can be expanded or reduced in relation to the application.

#### Proc. of SPIE Vol. 10246 1024612-2

Fig. 2: Generic Converter based on SC and Linear converter

The linear converters can only work as step-down converters and their efficiency depends on the difference between their input and output voltage. If the voltages are close together, they have an acceptable efficiency level. Therefore, the SC converters purpose is to reduce or increase the input voltage to put the linear converter in the best working condition. In addition, the use of linear converters to obtain different output voltages improves the quality of the output so that the control technique based on the output resistor modulation is not necessary. This way, a simplification of the control system is obtained. The switching converters with inductor have a high efficiency but only one output voltage. A greater number of outputs requires more than one inductor, e.g. a converter for each output voltage level. Alternatively, some linear converter in cascade can be used but this leads to the loss of benefits in terms of efficiency [5].

#### 3. MODEL OF A REALIZED CONVERTER

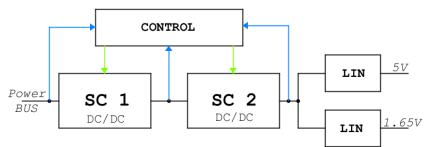

The proposed inductorless converter is realized following the previous model and is designed for a very wide input voltage range, as the voltage level in the automotive power bus (including overvoltage and cranking conditions). The global architecture, displayed in Fig. 3, is a three stages solution: two SC converter blocks and two linear converters in parallel.

Fig. 3: Converter architecture

The aims of the converter block can be resumed in:

- First Conversion Stage (called SC1) is a step up / step down converter and manages the wide input dynamic voltage (from 6 V to 60 V).

- Second Conversion Stage (called SC 2) reduces the output resistance of the SC sub-system in order to ensure the correct operation of the two linear converters.

- LIN (Linear regulator) complies the output nominal voltages and ripple requirements.

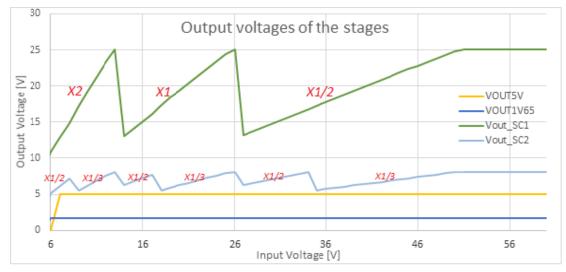

The SC1 implements three VCRs (X1/2, X1 and X2) while the SC2 can work with two VCRs (X1/2 and X1/3), which are mixed together to cover all the wide input range; six global VCRs can be obtained with this configuration. To ensure the correct functionality of the 5 V linear converter the VCRs thresholds are set to obtain an output voltage of the SC sub-system close to 5 V for all the input dynamic. The system is optimized to supply a variable number of hall sensors

(up to thirty 5 V sensors) and low-power thermal sensors (up to twenty 1.65 V sensors). The currents constraint for this application are 300 mA for 5 V and 20 mA for 1.65 V. A trade-off between the use of another SC stage to generate the 1.65 V and its occupied area leads to use a linear converter from 5 V to 1.65 V because its efficiency losses are negligible.

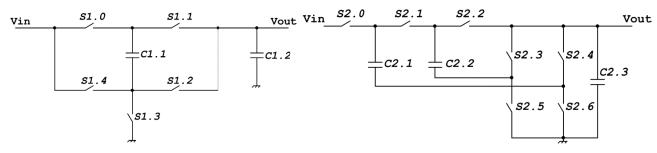

In accord with Makowski's theorem [4], the SC architecture displayed in Fig. 4 are used to obtain the desiderate VCRs. The left architecture (Fig. 4 Left), used to realize the SC1 in Fig. 3, uses one fly capacitor and a buffer capacitor while the right architecture (Fig. 4 Right), used to realize the SC2 in Fig. 3, uses two fly capacitors and a buffer capacitor. The model realized allows doing a wide design space exploration to understand the converter performance and to know the possibility to integrate the whole system in a single die.

Fig. 4: SC stages model. SC1 at left and SC2 at right.

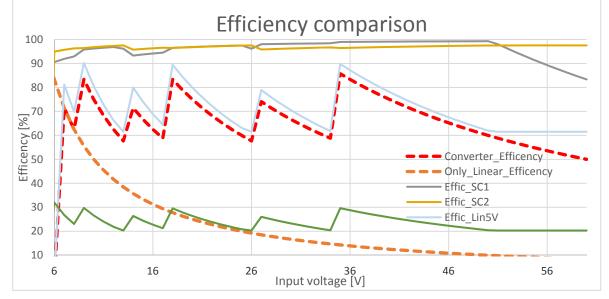

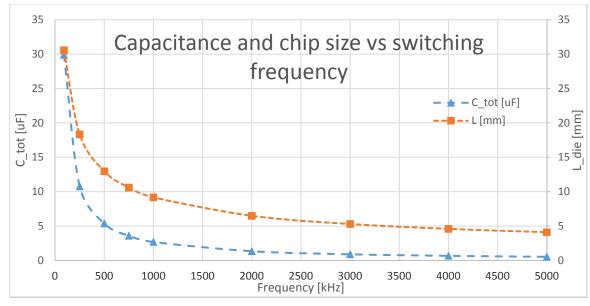

For this application a very low cost technology is used; the AMS 0.35  $\mu$ m HV-CMOS is chosen to manage voltage levels up to 60 V. The on-resistance of the switches and the R<sub>FSL</sub> depend on the technology chosen. Each switch is realized in relation to the voltage and to its role in the converter; it can be made with single P-mos/N-mos or with a complex configuration up to four mosfets. To reduce the switching resistance and so the R<sub>FSL</sub>, see eq. (2), the mosfets width are above 40000  $\mu$ m. Each mosfet is made of hundreds of parallel transistors to get an appropriate aspect-ratio for the layout phase. In addition, a very low switching frequency, only 90 kHz, is used to reduce the radiated electromagnetic interference (EMI) problems and so, to keep a good efficiency, fly capacitance values greater than 3  $\mu$ F are selected, see eq.(1). This limits the complete integration of this converter. Fig. 5 shows the output voltages of the single stages, highlighting the VCRs used in the SC1 and SC2. Up to 50 V input a skip algorithm is implemented to limit the SC1 output voltage at 25 V. Fig. 6 shows the efficiency of the whole converter (in red) and how the single stages influence it. A comparison with a single linear converter efficiency (in orange) can be done, highlighting the greater efficiency of the proposed solution. This realized solution, as mentioned above, uses fly capacitances greater than 3  $\mu$ F and buffer capacitances up to 10  $\mu$ F, for a total capacitance of 29.9  $\mu$ F that limits the integration expectations.

Fig. 5: Output voltage of each stage

In this context the integration of the passive components, especially capacitors, plays a key role, in the possibility to realize a completely integrate converter. The use of 3D technology allows to stack the passive device on the silicon die reducing the PCB area and the assembly cost of the whole system. Today the integration density of commercially available low voltage 3D capacitors is up to 250 nF/mm<sup>3</sup> [6] but these capacitors operate at only 6 V. The operating voltage of the capacitors depends on the dielectric thickness. A higher width and a higher voltage lead to lower capacitance. Therefore, for voltages above 60 V the integration density decreases at 32 nF/mm<sup>3</sup> [1].

Fig. 6: Efficiency of the whole converter (red line), of each stage and of a linear converter in the same conditions (orange line). The efficiency of the 1.65 V output affects slightly the whole converter efficiency because the load current of the 1.65 V output is much lower than the one of the 5 V output.

Fig. 7: Global capacitance in function of the switching frequency and the chip size required to a complete integration of the 3D capacitors.

Using the previous model it is possible to understand how we can reduce the total capacitance value to fully integrate the converter, keeping the same efficiency. Thanks to the eq. (1), lower capacitance value can be obtained with higher switching frequency. Using the capacitance density of 32nF/mm<sup>3</sup> it is possible to estimate the die size (see Fig. 7).

The size of the realized chip  $(36 \text{ mm}^2)$  is due to the large width of the mosfet used. According to Fig. 7, the side size of the 3D stacking capacitance necessary for the converter is about 5.3 mm (28.09 mm2) for a switching frequency of 3 MHz. The use of a 3D capacitor approach with direct contact between the chip and the capacitor layer (like flip chip techniques) reduces the use of bonding wire. This alleviates the parasitic resistance problems and the inductive effects that generate radiated EMI problems. The increase of the switching frequency reduces the ripple values on the signals inside the system and the conductive EMI due to request of input charge. The disturbs on the input power bus will shift from 90 kHz to 3 MHz allowing to reduce the size of the EMI filtering devices. An increase of the switching frequency leads to an increasing of the power to switch the big mosfets. However, the used HV-mosfet have a low gate capacitance (thick gate oxide) and so the efficiency losses due to this effect are negligible for this application (56  $\mu$ W vs 1.5 W).

#### 4. CONCLUSIONS

An universal and inductorless DC/DC converter has been proposed in the paper. It can be used for a wide input range, from few V to 60 V, to regulate output voltages from 5 V down to 1 V in Sensor and Actuator Network nodes. The proposed converter, developed within the Athenis3D European project, is composed by a cascade of multiple switching capacitor stages, with a proper skip-mode control to implement both step-down and step-up converting ratios, thus regulating all input sources to a voltage of about 6 V. These switching stages are further cascaded with linear regulators, which can provide stable output voltages down to 1 V. The multi-output regulator has been realized as a single-chip in a low-cost CMOS technology. The only needed passive components are surface mount capacitors, which can be integrated on top of the naked chip die, creating a 3D structure, using trench capacitors embedded in a passive interposing layer. This way the size of the power management unit is further minimized and a fully integrated DC/DC regulator solution is enabled. Another advantage of the proposed converter is that it isn't optimized for a particular input voltage, therefore can be used with no constant input power, like power harvesting systems (e.g. solar cells, wind and water turbines) and very disturbed power supplies.

#### 5. ACKNOWLEDGEMENT

The support of Valeo PES, Creteil (F) and AMS, Cascina (I), is gratefully acknowledged.

#### REFERENCES

- F. Huening, "ATHENIS 3D: Automotive Tested High-voltage and Embedded Non-volatile Integrated SoC platform with 3D technology", Power semiconductors for the automotive 48V board net, IEEE PCIM Europe 2016

- [2] V. Shirmohammadil, et al., "LDO-assisted vs. Linear-assisted DC/DCconverters: a comprehensive study and comparison", IEEE ICES 2016, DOI: 10.1109/ICECS.2016.7841143

- [3] M. D. Seeman, S. R. Sanders, "Analysis and Optimization of Switched-Capacitor DC-DC Converters", IEEE Transaction on Power Electronics, vol 23, n. 2, March 2008

- [4] M. S. Makowski, D. Maksimovic, "Performance limits of Switched Capacitors DC-DC Converters", Power Electronics Specialist Conference, 1995

- [5] M. Jafari, G. Hunter, J. G. Zhu, "A new topology of multi-input multi-output buck-boost DC-DC converter for microgrid applications", IEEE PECON 2012

- [6] C. Brunel, et al., "Silicon capacitors with extremely high stability and reliability ideal for high temperature applications", HiTEC2012, Baltimore.