Modeling and Simulation of Non-Classical MOSFETs for HP and LSTP Applications at 20 nm Gate Length

Devender Singh (213EE1275)

Department of Electrical Engineering, National Institute of Technology, Rourkela, Rourkela-769 008, Orissa, India. May, 2015. Copyright 2015 Devender Singh All Rights Reserved

# Modeling and Simulation of Non-Classical MOSFETs for HP and LSTP Applications at 20 nm Gate Length

A dissertation submitted in partial fulfillment of the requirements for the degree of

## Master of Technology in Electronic Systems and Communication

by

Devender Singh (Roll No: 213EE1275)

Under the Guidance of

Prof. Prasanna Kumar Sahu

Department of Electrical Engineering, National Institute of Technology, Rourkela, Rourkela-769 008, Orissa, India 2013-2015 Dedicated to

My Loving Parents,

Brothers and Sister.

#### Department of Electrical Engineering National Institute of Technology, Rourkela Rourkela-769 008, Orissa, India.

#### Certificate

This is to certify that the thesis entitled "Modeling and Simulation of Non-Classical MOSFETs for HP and LSTP Applications at 20 nm Gate Length" by Devender Singh, submitted to the National Institute of Technology, Rourkela for the award of Master of Technology in Electrical Engineering, is a record of bonafide research work carried out by him in the Department of Electrical Engineering, under my supervision. I believe that this thesis fulfills part of the requirements for the award of degree of Master of Technology. The results embodied in the thesis have not been submitted for the award of any other degree elsewhere.

Place: Rourkela

Date:

Prof. Prasanna Kumar Sahu Associate Professor Department of Electrical Engineering National Institute of Technology, Rourkela

Rourkela-769 008, Orissa, India.

#### Acknowledgment

First and foremost, I am truly indebted and wish to express my gratitude to my supervisor Associate Professor Dr. Prasanna Kumar Sahu for his inspiration, excellent guidance, continuing encouragement and unwavering confidence and support during every stage of this endeavour without which, it would not have been possible for me to complete this undertaking successfully.

I express my deep gratitude to the members of Masters Scrutiny Committee, Dr. Dipti Patra, Dr. Susmita Das, Dr. Supratim Gupta and K. R. Subhashini for their loving advise and support. I am also very much obliged to the Head of the Department of Electrical Engineering, NIT Rourkela for providing all possible facilities towards this work. Thanks to all other faculty members in the department.

I am also thankful to all the professors of the department for their support and encouragement.

I would also like to express my heartfelt gratitude to PhD research scholars Kumar Prasannajit Pradhan, Sushanta Kumar Mohapatra, Astik Biswas, Damodar Panigrahy, Sambhudutta Nanda and Debajit De who always inspired me and particularly helped me in the lab.

I would like to extend special gratitude to my friends in NIT Rourkela, without whom, this journey would not have been this enjoyable.

I would conclude with my deepest gratitude to my parents. My full dedication to the work would not have been possible without their blessings and moral support. This thesis is a dedication to them who did not forget to keep me in their hearts when I could not be beside them.

Devender Singh

#### Abstract

The endless miniaturization of Si-based Metal Oxide Semiconductor Field-Effect Transistors (MOSFETs) has the key for urging the electronic uprising. However, scaling of the channel length is the enormous challenge to preserve the performance in terms of speed, power, and electrostatic integrity at each technology nodes. From the commencement of CMOS scaling, the simple planar MOSFETs are not up to the performance because of the increased SCEs and leakage current. To slacken the SCEs and leakage currents, different types of structures i.e. Multi-Gate MOSFETs like double-gate (DG), triple-gate (TG), FinFETs have introduced in the literature. Fully Depleted (FD) Silicon-On-Insulator (SOI) devices have shown potentially significant scalability when compared to bulk MOSFETs. In spite of, the introduced structures in literature are not offering concurrent SCE repression and improved circuit implementation. And some involve tangled processing not suggested for smooth integration into the here and now CMOS technology.

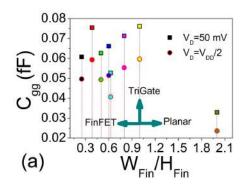

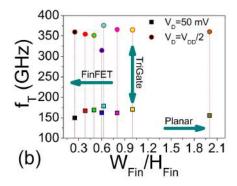

The scaling capability of nanoscale ultra-thin (UT) silicon directly on insulator (SDOI) single gate (SG) and DG MOSFETs is investigated to overcome SCEs and improve power consumption. Dependence of underlap length on drain current, Subthreshold Slope (SS), transition frequency, delay, Energy Delay Product (EDP), etc. is studied for DG MOSFET and FinFET, to find the optimum value of underlap length for low power consumption. DG MOSFET is an excellent candidate for high current drivability whereas FinFET provides better immunity to leakage currents and hence improved delay, EDP over DG MOSFET. Furthermore, FinFET provides a high value of transition frequency which indicates that it is faster than DG MOSFET. III-V channel materials are proposed for the discussed two structures to improve the On current at the same integration density as in Si-based channel FETs. The role of geometry parameters in sub 20 nm SOI Fin-FET is studied to find the optimum value of height and width of Fin for analog and RF circuit design. This work provides the influence of the height and width of Fin disparity on different performance matrices that comprises of static as well as dynamic figures of merit (FoMs). Based on the Aspect Ratio  $(W_{Fin}/H_{Fin})$ , the device can be divided into three parts, i.e., FinFET, Tri-gate, and Planar MOSFET.

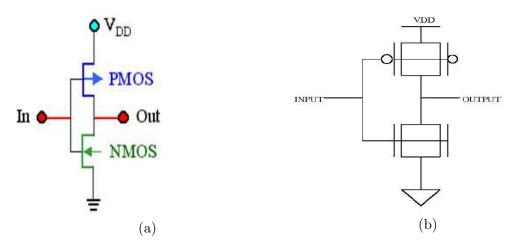

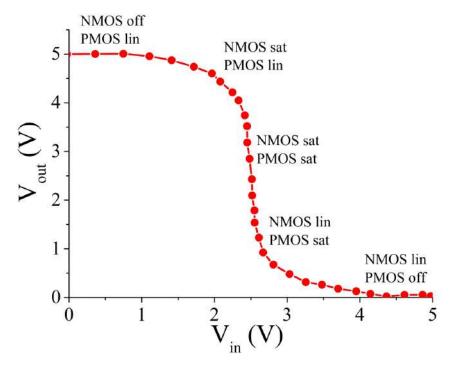

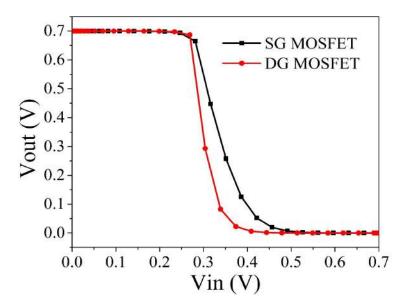

CMOS for SG and DG is made using the combination of NMOS and PMOS by engineering the work function in order to have same threshold voltage for N-channel and P-channel MOS. The inverter is without doubt the core of all digital applications. Once its operation and characteristics are understood with clarity, designing more complicated structures such as NAND gates, multipliers, adders, and microprocessors are significantly explained. The performance of CMOS is articulated. All the dimensions are according to the ITRS 2013 datasheet. The work provided here is requisited to give the purpose for forward experimental investigation.

**Keywords:** High Performance (HP), Low Standby Power (LSTP), MOSFET, Silicon Directly on Insulator (SDOI), FinFET, CMOS, Aspect Ratio (AR), Figure of Merits (FoMs).

#### List of Acronyms

| Acronym   | Description                                                   |

|-----------|---------------------------------------------------------------|

| ITRS      | International Technology Roadmap for Semiconductors           |

| CMOS      | Complementary Metal-Oxide Semiconductor                       |

| TCAD      | Technology Computer Added Design                              |

| IC        | Integrated Chip                                               |

| RF        | Radio Frequency                                               |

| SoC       | System on Chip                                                |

| TFTs      | Thin Film Transistors                                         |

| SOI       | Silicon on Insulator                                          |

| UTB       | Ultra Thin Body                                               |

| MugFETs   | Multiple Gate Mosfets                                         |

| FD-SOI    | Fully Depleted Silicon on Insulator                           |

| DG MOSFET | Double Gate Metal-Oxide Semiconductor Field Effect Transistor |

| SS        | Sub-threshold Slope                                           |

| DIBL      | Drain Induced Barrier Lowering                                |

| EOT       | Equivalent Oxide Thickness                                    |

| SCEs      | Short Channel Effects                                         |

| HCEs      | Hot Carrier Effects                                           |

| CLM       | Channel Length Modulation                                     |

| DM        | Dual Material                                                 |

| PDP       | Power Delay Product                                           |

| EDP       | Energy Delay Product                                          |

| LP        | Low Power                                                     |

| HP        | High Performance                                              |

| LSTP      | Low Standby Power                                             |

| SiGe      | Silicon Germanium                                             |

| FoMs      | Figures of Merit                                              |

| TGF       | Transconductance Generation Factor                            |

| TCP       | Temperature Compensation Point                                |

| 2-D       | Two Dimension                                                 |

| 3-D       | Three Dimension                                               |

| AR        | Aspect Ratio                                                  |

#### List of Symbols

| Symbol           | Description                    |  |

|------------------|--------------------------------|--|

| Symbol           | Description                    |  |

| $V_{th} or V_T$  | Threshold Voltage              |  |

| $V_{GS}orV_{gs}$ | Gate to Source Voltage         |  |

| $V_{DS}orV_{ds}$ | Drain to Source Voltage        |  |

| $I_{ds}orI_D$    | Drain Current                  |  |

| $t_{ox}orT_{ox}$ | Gate-Oxide Thickness           |  |

| $t_b$            | Buried Oxide Thickness         |  |

| $L_gor L$        | Channel Length                 |  |

| W                | Channel Width                  |  |

| $N_A$            | Acceptor Doping Concentration  |  |

| $N_D$            | Donor Doping Concentration     |  |

| $t_{Si}orT_{Si}$ | Silicon Body Thickness         |  |

| $\epsilon_{Si}$  | Permittivity of Silicon        |  |

| $\epsilon_{ox}$  | Permittivity of Oxide          |  |

| $N_{Sub}$        | Substrate Doping               |  |

| $I_{on}$         | On-State Drive Current         |  |

| $I_{off}$        | Off-State Leakage Current      |  |

| $g_m$            | Transconductance               |  |

| $g_d$            | Output Conductance             |  |

| $E_v$            |                                |  |

| $A_V$            | Intrinsic Gain                 |  |

| $C_{gs}$         | Gate to Source Capacitance     |  |

| $C_{gd}$         | Gate to Drain Capacitance      |  |

| $f_T$            | Cut-off Frequency              |  |

| $C_T$            | Total Internal Capacitance     |  |

| $\phi_M$         | Metal Work Function            |  |

| $\phi_{Si}$      | Silicon Work Function          |  |

| $V_{bi}$         | Built-in Potential             |  |

| X                | Germanium Mole Fraction        |  |

| $t_{s-Si}$       | Strained Silicon Thickness     |  |

| $E_C$            | Electron Affinity              |  |

| $E_G$            | Energy Band Gap                |  |

| $\eta$           | Body Factor                    |  |

| $SiO_2$          | Silicon Dioxide                |  |

| $Si_3N_4$        | Silicon Nitride                |  |

| $T_K$            | Thickness of High-k Dielectric |  |

| $\varphi_S$      | Surface Potential              |  |

| $v_{Sat}$        | Saturation Velocity            |  |

| USat             | paruration velocity            |  |

continued on the next page

${\bf List\ of\ Symbols}\ ({\it continued})$

| Symbol   | Description                     |  |

|----------|---------------------------------|--|

| $V_{FB}$ | Flat Band Voltage               |  |

| $\eta_i$ | Intrinsic Carrier Concentration |  |

### List of Used Constants with their Values

| Constants                                        | Values                   |

|--------------------------------------------------|--------------------------|

| Electronic Charge (q)                            | $1.6*10^{-19} Coulomb$   |

| Electron Mass (m)                                | $9.1*10^{-31} Kg$        |

| Permeability of Vacuum $(\mu_0)$                 | $4\pi*10^{-7}H/m$        |

| Permittivity of Vacuum $(\varepsilon_0)$         | $8.85*10^{-12}F/m$       |

| Boltzmann Constant $(k_B)$                       | $1.38*10^{-23}J/K$       |

| Permittivity of Silicon $(\varepsilon_{Si})$     | 11.68                    |

| Permittivity of $SiO_2(\varepsilon_{SiO_2})$     | 3.9                      |

| Permittivity of $Si_3N_4(\varepsilon_{Si_3N_4})$ | 7.5                      |

| Room Temperature (T)                             | 300 K                    |

| Thermal Voltage $(V_T)$                          | $26~\mathrm{mV}$         |

| Intrinsic Carrier Concentration $(\eta_i)$       | $1.45 * 10^{10} cm^{-3}$ |

### Contents

| $\mathbf{C}_{0}$ | ertific       | cate                                                    | i   |

|------------------|---------------|---------------------------------------------------------|-----|

| A                | cknov         | wledgment                                               | ii  |

| $\mathbf{A}$     | bstra         | ct                                                      | iii |

| $\mathbf{Li}$    | st of         | Acronyms                                                | iv  |

| ${f Li}$         | st of         | Figures                                                 | x   |

| Li               | st of         | Tables                                                  | xiv |

| 1                | Intr          | roduction                                               | 1   |

| _                | 1.1           | Background                                              | 2   |

|                  | 1.2           | Future Technology Node Requirements                     |     |

|                  |               | 1.2.1 High performance (HP)                             |     |

|                  |               | 1.2.2 Low operating power (LOP)                         |     |

|                  |               | 1.2.3 Low stand-by power dissipation (LSTPD)            |     |

|                  | 1.3           | Technology Scaling                                      | 5   |

|                  |               | 1.3.1 Why MOSFET Scaling?                               |     |

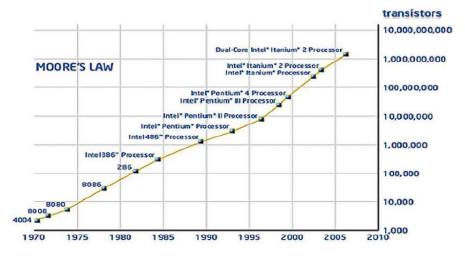

|                  |               | 1.3.2 Moore's Law                                       |     |

|                  |               | 1.3.3 Challenges to Miniaturization of MOSFETs          | 7   |

|                  | 1.4           | Motivation                                              | 8   |

|                  | 1.5           | Research Problem Statement                              | 9   |

|                  | 1.6           | Thesis Organisation                                     | 10  |

| 2                |               | ra Thin Si Directly on Insulator (SDOI) MOSFETs: SG and |     |

|                  | $\mathbf{DG}$ |                                                         | 12  |

|                  | 2.1           | Introduction                                            |     |

|                  | 2.2           | Device Structure and Its Parameters                     | 13  |

|                  | 2.3           | Simulation                                              |     |

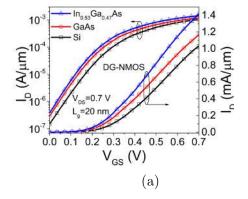

|                  | 2.4           | III-V Channel Materials                                 |     |

|                  | 2.5           | Results and Discussion                                  |     |

|                  | 2.0           | 2.5.1 Effects of high mobility channel materials        |     |

|                  | 2.6           | Summary                                                 | 21  |

| 3                | _             | imization of Underlap Length for DG MOSFET and FinFET   |     |

|                  | 3.1           | Introduction                                            | 23  |

|                  | 3.2           | Device Structure                                        | 23  |

|                  | 3.3           | Simulation                                              | 24  |

|                  | 3.4           | III-V Channel Materials In FinFET                       |     |

|                  | 3.5           | Results And Discussion                                  |     |

|                  | 3.6           | Summary                                                 | 30  |

| 4                         | Role | e of Fin Height, Width and Aspect Ratio In SOI FinFET | 32 |

|---------------------------|------|-------------------------------------------------------|----|

|                           | 4.1  | Introduction                                          | 33 |

|                           | 4.2  | Device Structure                                      | 33 |

|                           | 4.3  | Simulation                                            | 35 |

|                           | 4.4  | Results and Discussion                                | 36 |

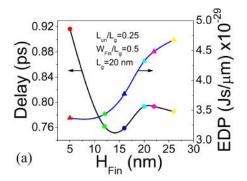

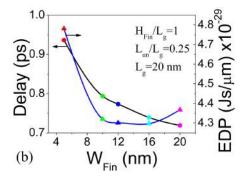

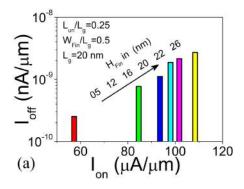

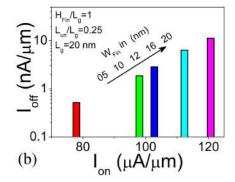

|                           |      | 4.4.1 Effect of $H_{Fin}$                             | 36 |

|                           |      | 4.4.2 Effect of $W_{Fin}$                             | 41 |

|                           | 4.5  | Summary                                               | 47 |

| 5                         | Ana  | alysis of CMOS Design                                 | 48 |

|                           | 5.1  | Introduction                                          | 49 |

|                           | 5.2  | Device Structure                                      | 49 |

|                           | 5.3  | Simulation                                            | 51 |

|                           | 5.4  | Results and Discussion                                | 52 |

|                           | 5.5  | Summary                                               | 53 |

| 6                         | Con  | nclusions And Future Work                             | 54 |

|                           | 6.1  | Conclusions                                           | 55 |

|                           | 6.2  | Future Scope                                          | 55 |

|                           | 6.3  | Publications                                          | 56 |

|                           |      | 6.3.1 Journal                                         | 56 |

|                           |      | 6.3.2 Conferences                                     | 56 |

| $\mathbf{B}^{\mathbf{i}}$ | blio | rraphy                                                | 58 |

### List of Figures

| 1.1  | Moore's Law                                                                                                                                                                                                                                  | 6   |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.2  | Scaling trend of power supply voltage $(V_{dd})$ , threshold voltage $(V_{th})$ , and gate-oxide thickness $(T_{ox})$ as a function of CMOS channel length                                                                                   | 8   |

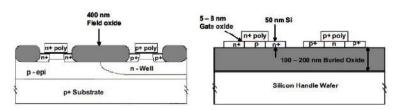

| 1.3  | Cross-sectional view of the bulk Si (left) and SOI (right) CMOS $$ . $$                                                                                                                                                                      | 9   |

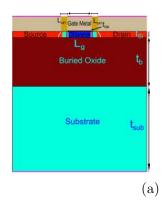

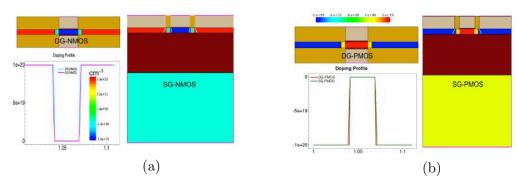

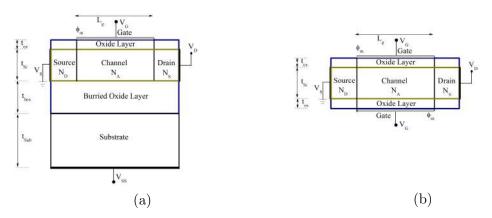

| 2.1  | Illustrative Architecture of UT-SDOI (a) SG and (b) DG, SDOI                                                                                                                                                                                 |     |

| กก   | MOSFETs                                                                                                                                                                                                                                      | 14  |

| 2.2  | Doping profile of the UT-SDOI MOSFET structures (a) Single and Double Gate NMOS (b) Single and Double Gate PMOS                                                                                                                              | 14  |

| 2.3  | 2-dimensional cross sectional view of the (a) UTB SG (b) UTB DG, MOSFETs                                                                                                                                                                     | 15  |

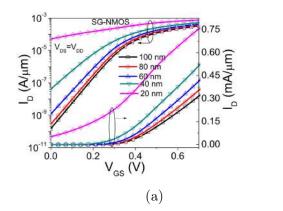

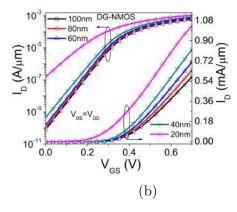

| 2.4  | Drain current $(I_D)$ of the devices as a part of $V_{GS}$ at $V_{DS} = V_{DD}$ (a)                                                                                                                                                          |     |

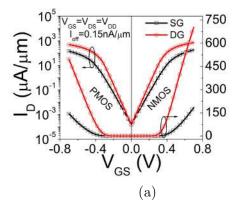

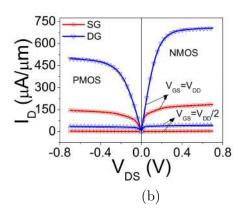

| 2.5  | SG, with variation of $L_g$ (b) DG with variation of $L_g$ The characteristics of both UT-SDOI SG and DG MOSFETs (n and patterns) for $V_g = 0.7 V_g$ and $V_g = 0.25 V_g$ beging some $V_g = 0.15 \text{ p.}^{\Lambda}$                     | 16  |

|      | p type) for $V_{GS}$ =0.7 V, and $V_{GS}$ =0.35 V having same $I_{off}$ =0.15 nA,<br>(a) The transfer curve between $I_D$ and $V_{GS}$ (b) The output curve                                                                                  | 1.0 |

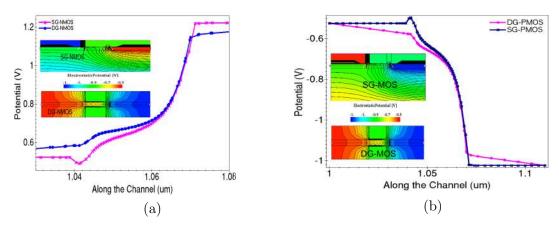

| 2.6  | between $I_D$ and $V_{DS}$                                                                                                                                                                                                                   | 16  |

| 2.0  | for UT-SDOI SG and DG MOSFET (a) NMOS devices (b) PMOS                                                                                                                                                                                       |     |

| 2.7  | devices                                                                                                                                                                                                                                      | 17  |

| 2.1  | (b) PMOS devices                                                                                                                                                                                                                             | 17  |

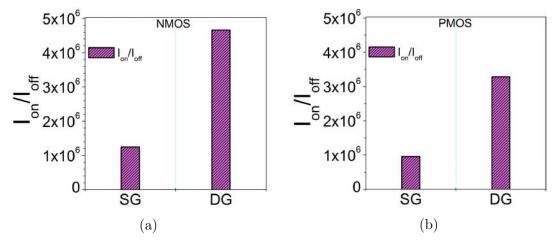

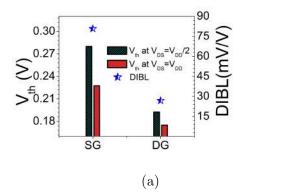

| 2.8  | Two important SCEs, $V_{th}$ variation and DIBL of UT-SDOI SG and DG MOSFET (a) NMOS devices (b) PMOS devices                                                                                                                                | 18  |

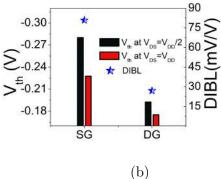

| 2.9  | The performance metrices for both SG and DG MOSFETs at $V_{DS}$ =0.05 V and $V_{DD}$ (a) DIBL and $I_{on}/I_{off}$ ratio for different $L_g$ (b) $I_{on}/I_{off}$ ratio of DG with variation of $N_A$ (c) SS for different $L_g$ (d) SS with |     |

| 2.10 | variation of $N_A$                                                                                                                                                                                                                           | 18  |

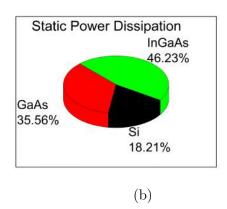

|      | ation for saturation region (b) Static power dissipation pie chart                                                                                                                                                                           | 20  |

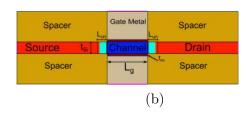

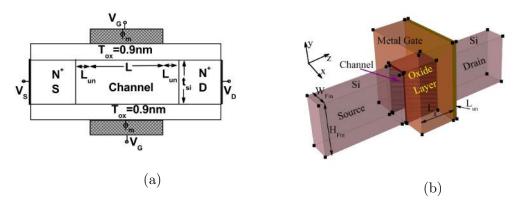

| 3.1  | Cross sectional view of (a) DG; (b) FinFET                                                                                                                                                                                                   | 24  |

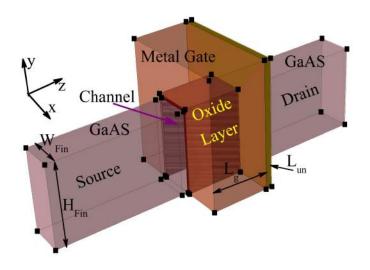

| 3.2  | Cross sectional view of GaAs FinFET                                                                                                                                                                                                          | 24  |

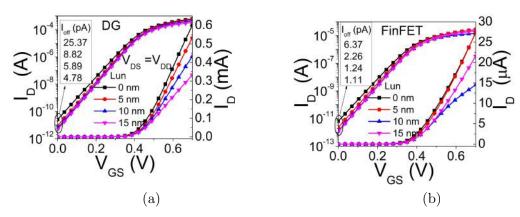

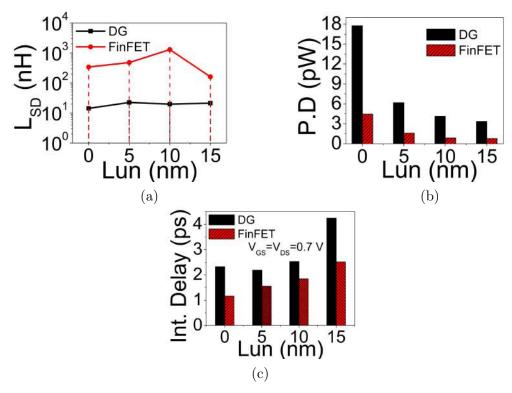

| 3.3  | $I_D$ as a part of $V_{GS}$ for $V_{DS}=V_{DD}$ with variation of $L_{un}$ (a) DG; (b) FinFET                                                                                                                                                | 25  |

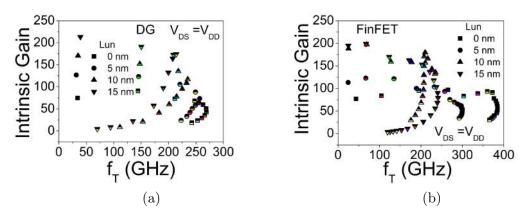

| 3.4  | Dependency of Intrinsic Gain $(A_V)$ on cutoff frequency $(f_T)$ for                                                                                                                                                                         | ~~  |

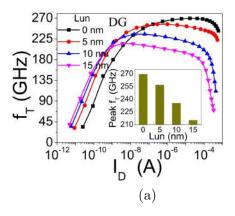

| 2 5  | $V_{DS}=V_{DD}$ with variation of $L_{un}$ (a) DG; (b) FinFET Dependency of cut-off frequency $(f_T)$ on drain current for $V_{DS}=V_{DD}$                                                                                                   | 25  |

| 3.5  | with variation of $L_{uv}$ (a) DG; (b) FinFET                                                                                                                                                                                                | 26  |

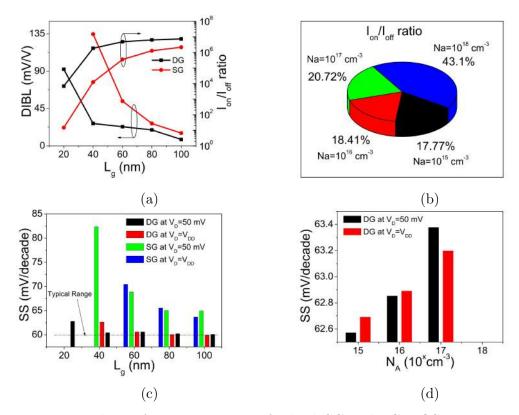

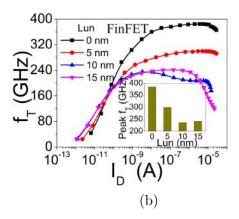

| 3.6          | Dependency of various performance parameters on under lap length $(L_{un})$ of DG MOSFET and FinFET at $V_{DS}=V_{DD}$ (a) Energy Delay Product (EDP); (b) on-off ratio $(I_{on}/I_{off})$ ; (c) subthreshold swing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 3.7          | (SS); (d) Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 27<br>28        |

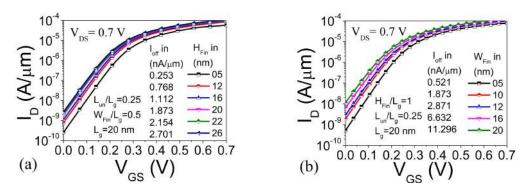

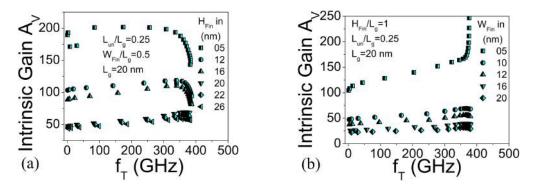

| 3.8          | $I_D$ - $V_{GS}$ with variation of (a) $H_{Fin}$ ; (b) $W_{Fin}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 28              |

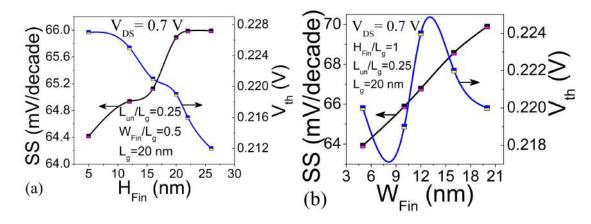

| 3.9          | Dependency of SS and $V_{th}$ on (a) $H_{Fin}$ (b) $W_{Fin}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 29              |

| 3.10<br>3.11 | Dependency of $A_V$ on $f_T$ with variation of (a) $H_{Fin}$ (b) $W_{Fin}$ Dependency of cut-off frequency $(f_T)$ on drain current for $V_{DS}=V_{DD}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29              |

|              | with variation of $L_{un}$ (a) DG; (b) FinFET                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 30              |

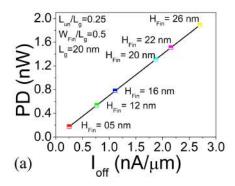

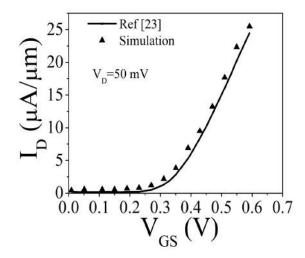

| 3.12         | Trade-off between $I_{off}$ on $I_{on}$ for different (a) $H_{Fin}$ (b) $W_{Fin}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 30              |

|              | Dependency of Delay on $I_{off}$ with variation of (a) $H_{Fin}$ (b) $W_{Fin}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 30              |

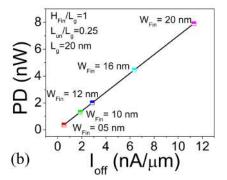

| 4.1          | Perspective view of SOI FinFET (a) 3-D view (b) 2-D view in x-y (c) 2-D view in x-z. The metal and spacer regions are made transparent in (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 34              |

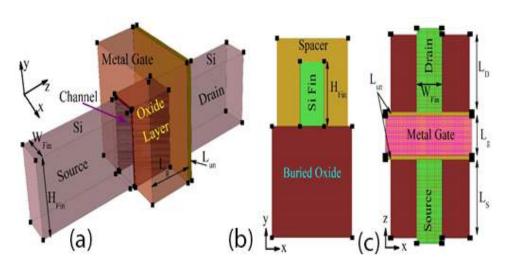

| 4.2          | transparent in (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | $\frac{34}{35}$ |

| 4.3          | Simulation procedure in Sentaurus TCAD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36              |

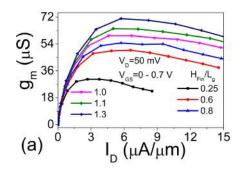

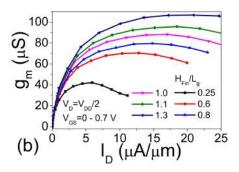

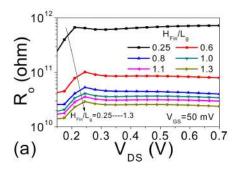

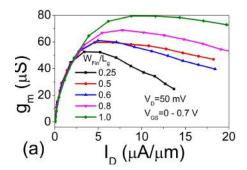

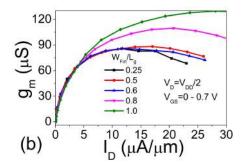

| 4.4          | Transconductance $(g_m)$ as a part of drain current $(I_D)$ of the device (a) for $V_{DS}$ =0.05 V (b) for $V_{DS}$ =0.35 V. Main Device Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 30              |

|              | are $L_g$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm, $t_{sub}$ =70 nm, $L_{un}$ = 5 nm, T=300 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 37              |

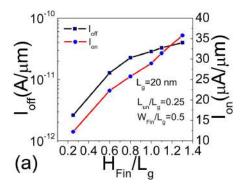

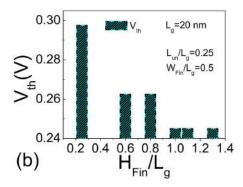

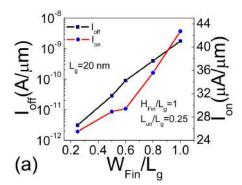

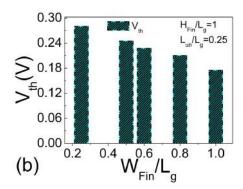

| 4.5          | (a) Drain on current $(I_{on})$ , Drain leakage current $(I_{off})$ and (b) $V_{th}$ of the device as a part of normalized Fin height $H_{Fin}$ with respect to physical gate length $L_q$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 37              |

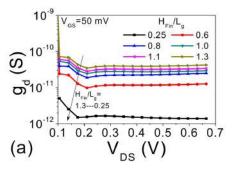

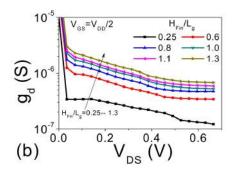

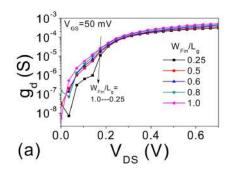

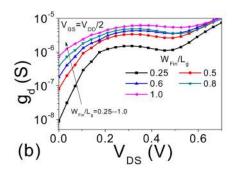

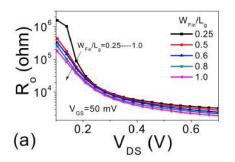

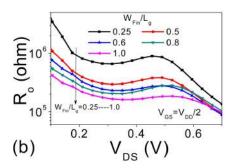

| 4.6          | Drain conductance $(g_d)$ of the device as a part of drain to source voltage $(V_{DS})$ (a) for $V_{GS}$ =0.05 V (b) for $V_{GS}$ =0.35 V. Main Device Parameters are $L_g$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 91              |

|              | $t_{sub}{=}70$ nm, $L_{un}{=}5$ nm, $V_{DS}$ varied from 0 V-to-0.7 V, T=300 K. $$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 38              |

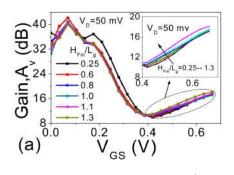

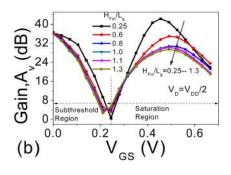

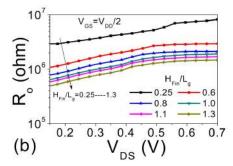

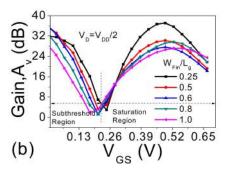

| 4.7          | Intrinsic gain $(A_V = g_m/g_d)$ as a part of gate to source voltage $(V_{GS})$<br>(a) for $V_{DS} = 0.05$ V (b) for $V_{DS} = 0.35$ V. Main Device Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 |

|              | are $L_g$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm, $t_{sub}$ =70 nm, $L_{un}$ =5 nm, $V_{GS}$ varied from 0 V-to-0.7 V, T=300 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 39              |

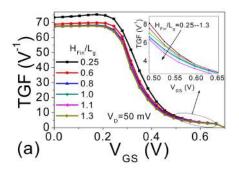

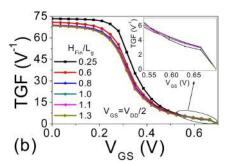

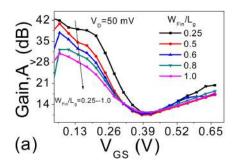

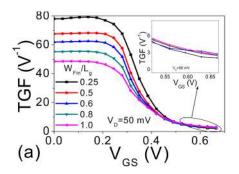

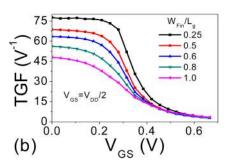

| 4.8          | Transconductance generation factor (TGF= $g_m/I_D$ ) as a part of gate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                 |

|              | to source voltage $(V_{GS})$ (a) for $V_{DS}$ =0.05 V (b) for $V_{DS}$ =0.35 V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |

|              | Main Device Parameters are $L_g$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm, $t_{sub}$ =70 nm, $L_{un}$ =5 nm, $V_{GS}$ varied from 0 V-to-0.7 V,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |

|              | T=300 K                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39              |

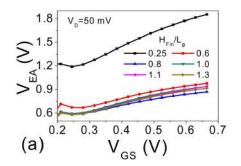

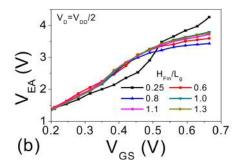

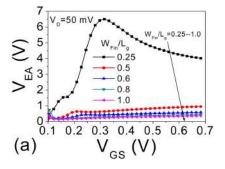

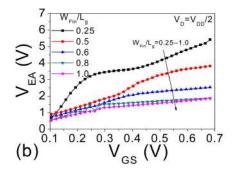

| 4.9          | Early Voltage $(V_{EA}=I_D/g_d)$ as a part of drain to source voltage $(V_{DS})$ (a) for $V_{GS}=0.05$ V (b) for $V_{GS}=0.35$ V. Main Device Pa-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |

|              | rameters are $L_g$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm, $t_{sub}$ =70 nm, $L_{un}$ = 5 nm, $V_{GS}$ varied from 0 V-to-0.7 V, T=300 K.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 40              |

|              | $v_{sub}$ - $v_{s$ | 40              |

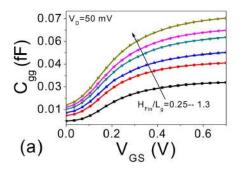

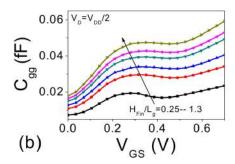

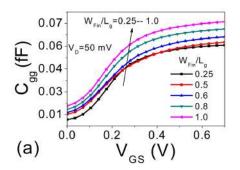

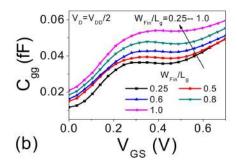

| 4.10 | Total gate capacitance $(C_{gg})$ as a part of gate to source voltage                                                                       |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | $(V_{GS})$ (a) for $V_{DS}$ =0.05 V (b) for $V_{DS}$ =0.35 V. Main Device Pa-                                                               |    |

|      | rameters are $L_g$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm,                                                            |    |

|      | $t_{sub}$ =70 nm, $L_{un}$ = 5 nm, $V_{GS}$ varied from 0 V-to-0.7 V, T=300 K                                                               | 40 |

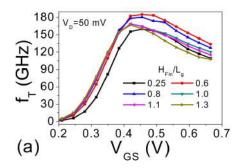

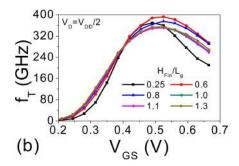

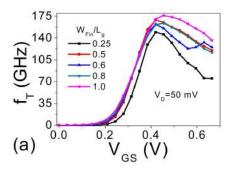

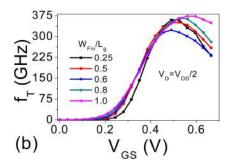

| 4.11 | Cut-off frequency $(f_T)$ as a part of gate to source voltage $(V_{GS})$ (a)                                                                |    |

|      | for $V_{DS}$ =0.05 V (b) for $V_{DS}$ =0.35 V. Main Device Parameters are                                                                   |    |

|      | $L_q$ =20 nm, $W_{Fin}$ =10 nm, $t_{ox}$ =0.9 nm, $t_{box}$ =40 nm, $t_{sub}$ =70 nm,                                                       |    |

|      | $L_{un} = 5$ nm, $V_{GS}$ varied from 0 V-to-0.7 V, T=300 K                                                                                 | 41 |