# Performance Enhancement of Shunt APFs Using Various Topologies, Control Schemes and Optimization Techniques

#### SUSHREE SANGITA PATNAIK

Department of Electrical Engineering

National Institute of Technology Rourkela, India

November, 2015

# Performance Enhancement of Shunt APFs Using Various Topologies, Control Schemes and Optimization Techniques

#### DISSERTATION

submitted in partial fulfilment of the requirements for the degree of

Doctor of Philosophy

in

**Electrical Engineering**

## By

### SUSHREE SANGITA PATNAIK

(Roll No.: 512EE105)

Under the supervision of Prof. Anup Kumar Panda

Department of Electrical Engineering

National Institute of Technology Rourkela, India

November, 2015

**CERTIFICATE**

This is to certify that the thesis titled "Performance Enhancement of Shunt APFs Using

Various Topologies, Control Schemes and Optimization Techniques", submitted by

Ms. Sushree Sangita Patnaik to the National Institute of Technology Rourkela, for the

award of the degree of *Doctor of Philosophy* in *Electrical Engineering*, is a bona fide

record of research work carried out by her under my supervision and guidance.

The matter embodied in the thesis is candidate's original work and has not been

submitted elsewhere for the award of any degree or diploma.

In my opinion, the thesis is fully adequate in scope and quality as a dissertation for the

degree of Doctor of Philosophy in Electrical Engineering.

| Date:               |              |

|---------------------|--------------|

| Place: NIT Rourkela |              |

|                     | (Supervisor) |

Prof. Anup Kumar Panda

Department of Electrical Engineering

National Institute of Technology

Rourkela, India

Email: akpanda@nitrkl.ac.in

# Acknowledgements

First and foremost, I take this opportunity to express my sincere gratitude to my supervisor, Prof. Anup Kumar Panda for his invaluable guidance, encouragement, innovative technical discussions, and for providing me with all the requisite facilities throughout the course of this work. This would not have been possible without his endless motivation and support.

I am highly grateful to the Doctoral Scrutiny Committee members, Prof. B. D. Subudhi, Prof. S. Karmakar, Prof. Gopalakrishna S. and Prof. P. M. Khilar for their valuable suggestions and contribution in my research work. They have been great sources of inspiration to me. I would like to thank Prof. P. C. Panda and Prof. K. B. Mohanty, whose lectures were very helpful in developing various concepts related to active power filter.

I express my thanks to all the faculty members, administrative and laboratory staff of the Department of Electrical Engineering at NIT Rourkela, especially Mr. Jagdish Kar and Mr. Rabindra Nayak for their cooperation and for providing me with all the official and laboratory facilities in various ways for the completion of this thesis.

My indebted respect goes to my teacher Prof. P. K. Panigrahi for sowing the seed of motivation to pursue research and higher studies. I thank him from the bottom of my heart.

I express my greatest admiration to my family for the love, blessings, sacrifices, encouragement and moral support they have showered on me throughout my career. I can't express my gratitude for my mother in words, whose unconditional love has been my greatest strength. I am grateful to my father for the constant inspiration that kept me focused and motivated. I thank my elder brother Santosh for being a guiding light and constant support throughout my life.

Last but not the least, I thank all my friends and lab mates, whose direct or indirect support has helped me in the completion of this project. I also thank my seniors, M. Suresh Sir and T. Ramesh Sir, who have been very helpful in providing all the technical and personal support.

Above all, my greatest acknowledgment goes to the divine power, the Almighty for bestowing upon me the strength, courage and innovative ideas to complete this project successfully.

# Contents

| Ackı | nowledgements                                                             | i     |

|------|---------------------------------------------------------------------------|-------|

| Cont | tents                                                                     | ii    |

| List | of Figures                                                                | vi    |

| List | of Tables                                                                 | xvi   |

| Acro | onyms                                                                     | xvii  |

| Nota | ntions                                                                    | xix   |

| Abst | ract                                                                      | xxiii |

|      |                                                                           |       |

| 1.   | Introduction                                                              | 1     |

|      | 1.1. Overview                                                             | 1     |

|      | 1.1.1. Causes behind production of harmonics                              | 2     |

|      | 1.1.2. Consequences of harmonics                                          | 3     |

|      | 1.2. Research Background                                                  | 5     |

|      | 1.2.1. Passive power filters                                              | 7     |

|      | 1.2.2. Active power filters                                               | 8     |

|      | 1.2.3. Control schemes for APF                                            | 12    |

|      | 1.2.4. Conventional PI controller for inverter DC-link voltage regulation | 14    |

|      | 1.2.5. Implementation of optimization techniques                          | 14    |

|      | 1.2.6. Shunt APF configurations                                           | 17    |

|      | 1.2.7. Multilevel inverter based APF                                      | 18    |

|      | 1.3. Analysis Tools                                                       | 19    |

|      | 1.4. Motivation                                                           | 23    |

|      | 1.5. Scope of the Thesis                                                  | 25    |

|      | 1.6. Thesis Organization                                                  | 26    |

| 2. | Shunt Active Power Filter and Its Control Schemes                                 | 29 |

|----|-----------------------------------------------------------------------------------|----|

|    | 2.1. Introduction                                                                 | 29 |

|    | 2.2. Shunt APF                                                                    | 31 |

|    | 2.3. Control Schemes for APF                                                      | 34 |

|    | 2.3.1. Instantaneous active and reactive power $(p-q)$ method                     | 36 |

|    | 2.3.2. Modified $p-q$ method                                                      | 39 |

|    | 2.3.3. Instantaneous active and reactive current component $\left(i_d-i_q\right)$ | 40 |

|    | method                                                                            |    |

|    | 2.4. Regulation of Inverter DC-link Voltage                                       | 43 |

|    | 2.5. Design of Conventional PI Controller                                         | 44 |

|    | 2.6. Results and Discussion                                                       | 45 |

|    | 2.6.1. Simulation results                                                         | 47 |

|    | 2.6.2. RT-Lab results                                                             | 60 |

|    | 2.7. Summary                                                                      | 66 |

|    |                                                                                   |    |

| 3. | Optimizing APF Performance Using PSO and BFO, and Development of an               | 67 |

|    | Enhanced BFO Technique                                                            |    |

|    | 3.1. Introduction                                                                 | 67 |

|    | 3.1.1. Problem formulation                                                        | 68 |

|    | 3.1.1.1. Regulation of inverter DC-link voltage                                   | 68 |

|    | 3.1.1.2. Need for optimization                                                    | 68 |

|    | 3.1.1.3. Objective function and optimization parameters                           | 69 |

|    | 3.2. Particle Swarm Optimization (PSO)                                            | 70 |

|    | 3.2.1. Mechanism of PSO                                                           | 70 |

|    | 3.2.2. Iterative algorithm for PSO                                                | 74 |

|    | 3.3. Bacterial Foraging Optimization (BFO)                                        | 77 |

|    | 3.3.1. Mechanism of BFO                                                           | 77 |

|    | 3.3.2. Iterative algorithm for BFO                                                | 81 |

|    | 3.4. Enhanced Bacterial Foraging Optimization (Enhanced BFO) | 83  |

|----|--------------------------------------------------------------|-----|

|    | 3.4.1. Mechanism of Enhanced BFO                             | 84  |

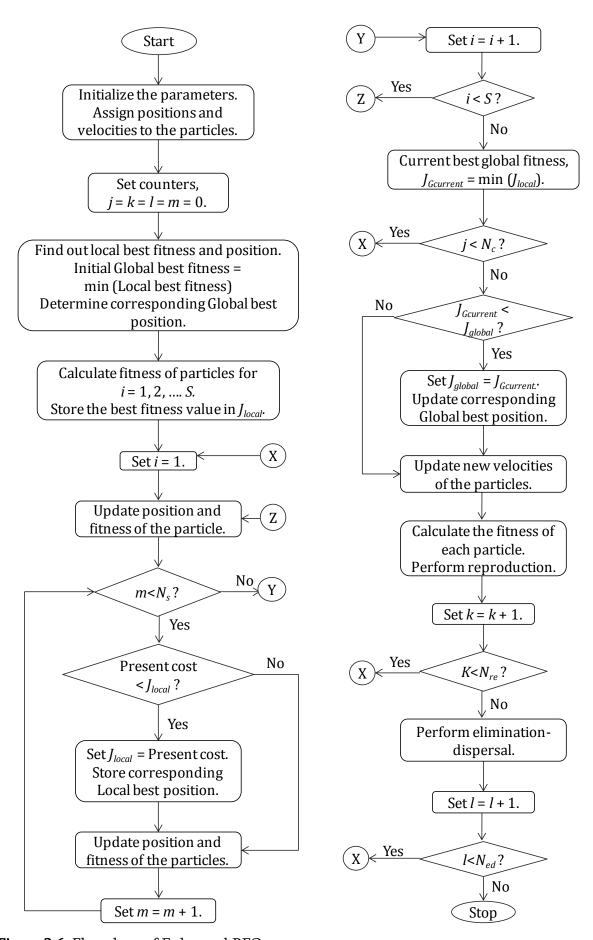

|    | 3.4.2. Iterative algorithm for Enhanced BFO                  | 86  |

|    | 3.5. Results and Discussion                                  | 89  |

|    | 3.5.1. Simulation results                                    | 92  |

|    | 3.5.2. RT-Lab results                                        | 102 |

|    | 3.6. Summary                                                 | 108 |

|    |                                                              |     |

| 4. | APF Topologies for Three-Phase Three-Wire Systems            | 109 |

|    | 4.1. Introduction                                            | 109 |

|    | 4.2. Multilevel Inverter (MLI)                               | 111 |

|    | 4.2.1. Types of MLI                                          | 112 |

|    | 4.2.1.1. Diode-clamped (Neutral-point clamped) inverter      | 112 |

|    | 4.2.1.2. Capacitor-clamped (Flying-capacitor) inverter       | 114 |

|    | 4.2.1.3. Cascaded inverter                                   | 117 |

|    | 4.2.2. PWM schemes for cascaded MLI                          | 119 |

|    | 4.2.2.1. Space vector modulation (SVM)                       | 120 |

|    | 4.2.2.2. Selective harmonic elimination (SHE)                | 121 |

|    | 4.2.2.3. Carrier-based PWM                                   | 122 |

|    | 4.3. System Description of Cascaded MLI Based APF            | 126 |

|    | 4.4. Results and Discussion                                  | 129 |

|    | 4.4.1. Simulation results                                    | 129 |

|    | 4.4.2. RT-Lab results                                        | 141 |

|    | 4.5. Summary                                                 | 147 |

| 5. | APF Topologies for Three-Phase Four-Wire Systems             | 148 |

|    | 5.1. Introduction                                            | 148 |

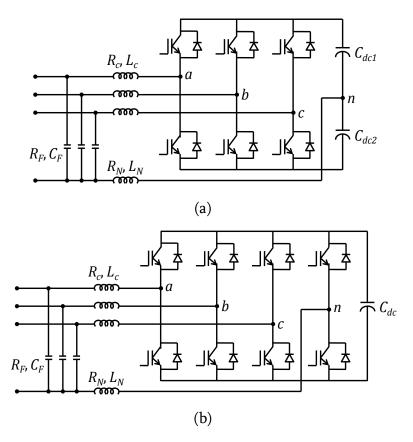

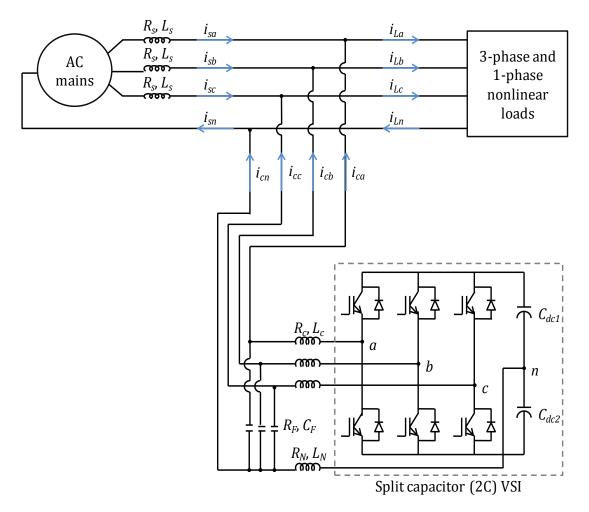

|    | 5.2. Split-Capacitor (2C) Topology                           | 150 |

|     | 5.3. Four-Leg (4L) Topology                                             | 154 |

|-----|-------------------------------------------------------------------------|-----|

|     | 5.4. Three H-Bridges (3HB) Topology                                     | 156 |

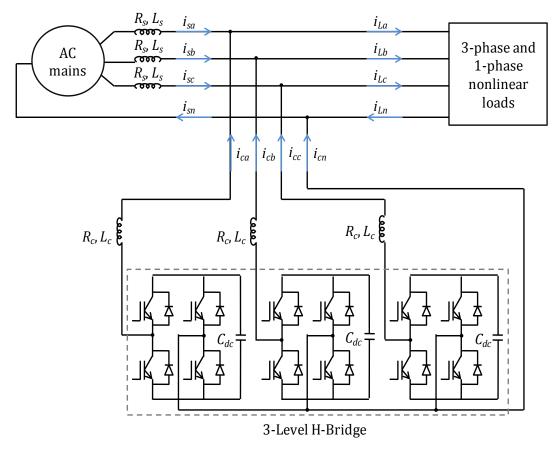

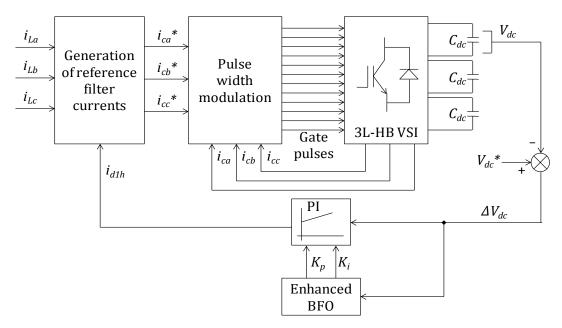

|     | 5.5. Three-Level H-Bridge (3L-HB) Topology                              | 158 |

|     | 5.6. Results and Discussion                                             | 161 |

|     | 5.6.1. Simulation results                                               | 161 |

|     | 5.6.2. RT-Lab results                                                   | 166 |

|     | 5.7. Summary                                                            | 173 |

|     |                                                                         |     |

| 6.  | Thesis Contributions, General Conclusions and Scope for Future Research | 174 |

|     | 6.1. Thesis Contributions                                               | 174 |

|     | 6.2. General Conclusions                                                | 175 |

|     | 6.3. Scope for Future Research                                          | 177 |

|     |                                                                         |     |

| Ref | erences                                                                 | 179 |

| The | esis Disseminations                                                     | 197 |

# List of Figures

| 1.1  | Harmonics                                                                          | 2  |

|------|------------------------------------------------------------------------------------|----|

| 1.2  | Types of three-phase passive harmonic filters, (a) Single-tuned, (b)               | 7  |

|      | Double-tuned, (c) High-pass, (d) C-type High-pass                                  |    |

| 1.3  | (a) APF employing VSI, (b) APF employing CSI                                       | 9  |

| 1.4  | Basic types of APF connections, (a) Shunt APF, (b) Series APF                      | 10 |

| 1.5  | Hybrid combinations of filters, (a) Shunt active filter and series active          | 11 |

|      | filter, (b) Series active filter and shunt passive filter, (c) Shunt active filter |    |

|      | and shunt passive filter, (d) Active filter in series with shunt passive filter    |    |

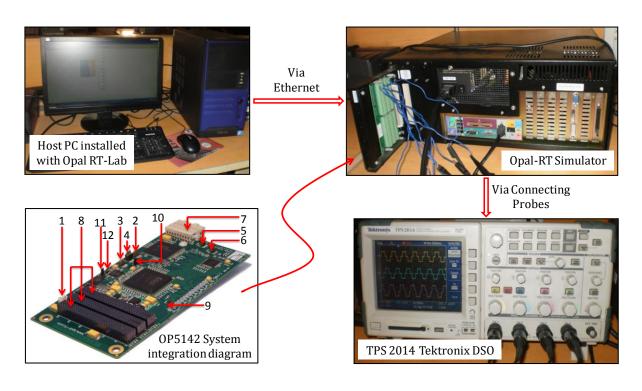

| 1.6  | RT-Lab set up and OP5142 system integration showing its components                 | 22 |

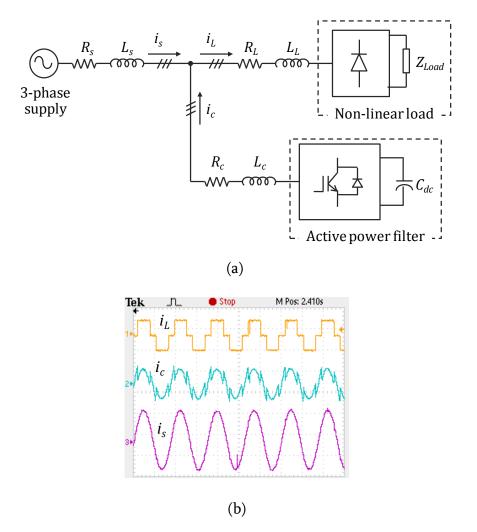

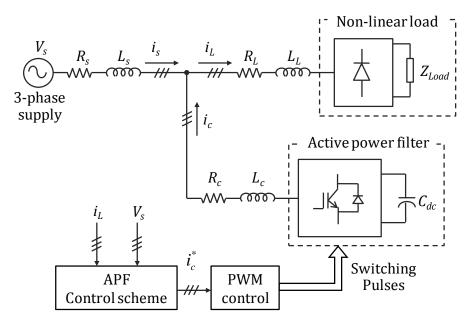

| 2.1  | Compensation principle of shunt APF, (a) Schematic diagram, (b)                    | 30 |

|      | Waveforms for load current $(i_L)$ , filter current $(i_c)$ and compensated        |    |

|      | source current $(i_s)$                                                             |    |

| 2.2  | General configuration of a shunt APF system                                        | 31 |

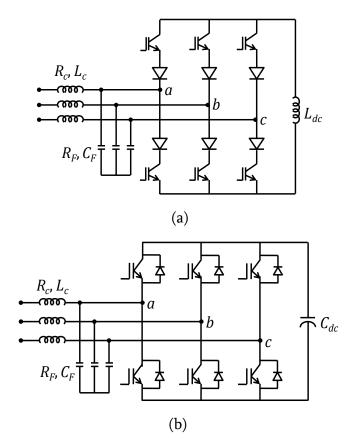

| 2.3  | Inverter configurations for APF, (a) CSI configuration, (b) VSI                    | 32 |

|      | configuration                                                                      |    |

| 2.4  | Conventional three-phase four-wire APF configurations, (a) Three-leg               | 33 |

|      | six-switch VSI, (b) Four-leg eight-switch VSI                                      |    |

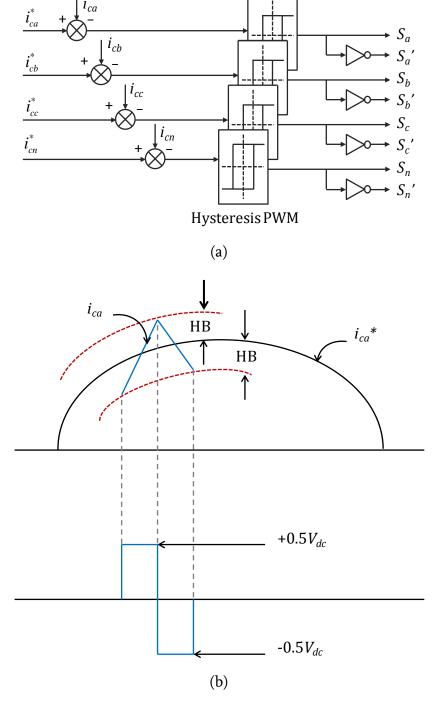

| 2.5  | Hysteresis PWM current controller, (a) Generation of switching signals,            | 35 |

|      | (b) Current and voltage waveforms                                                  |    |

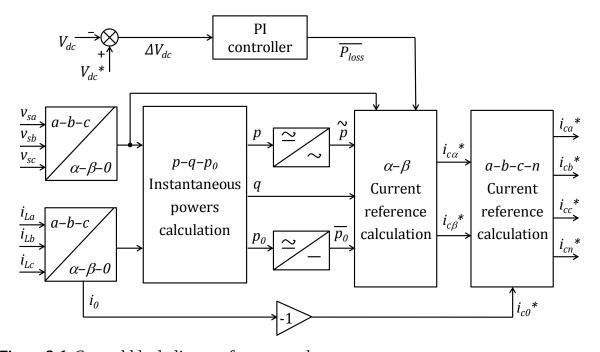

| 2.6  | Control block diagram for $p-q$ scheme                                             | 36 |

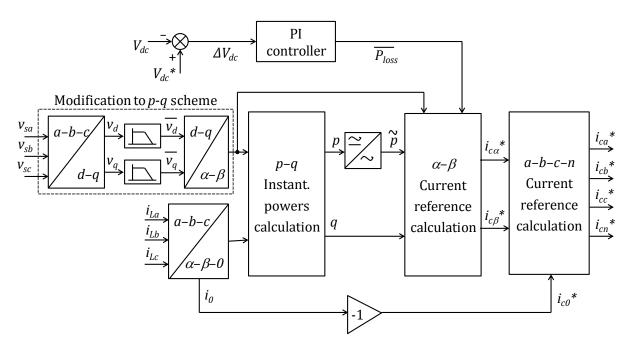

| 2.7  | Control block diagram for modified $p-q$ scheme                                    | 39 |

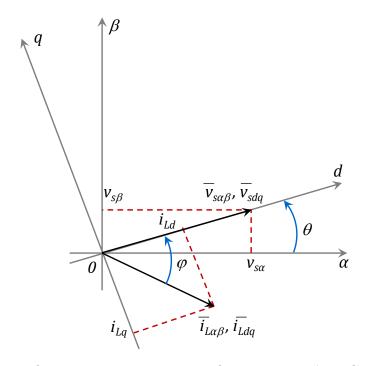

| 2.8  | Voltage and current space vectors in the stationary $(\alpha - \beta)$ and         | 41 |

|      | synchronous $(d-q)$ reference frames                                               |    |

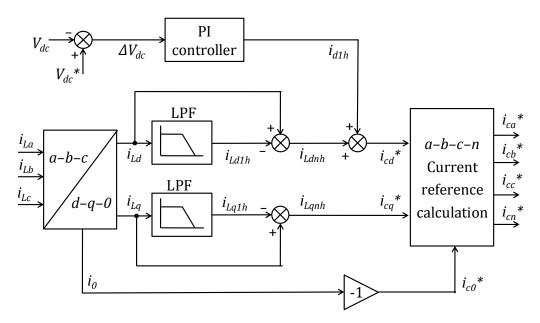

| 2.9  | Control block diagram for $i_d - i_q$ scheme                                       | 43 |

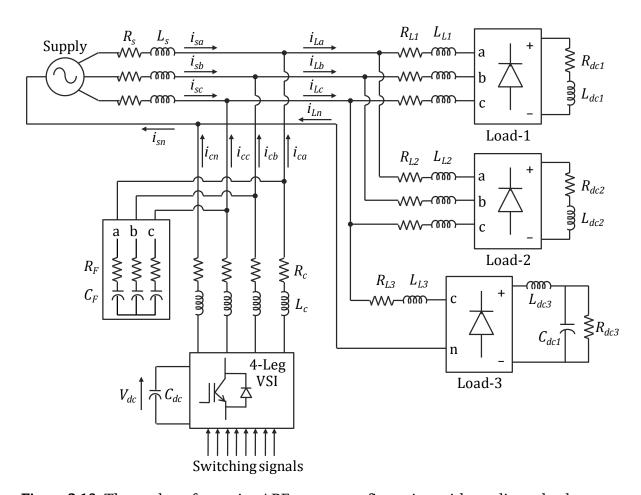

| 2.10 | Three-phase four-wire APF system configuration with nonlinear loads                | 45 |

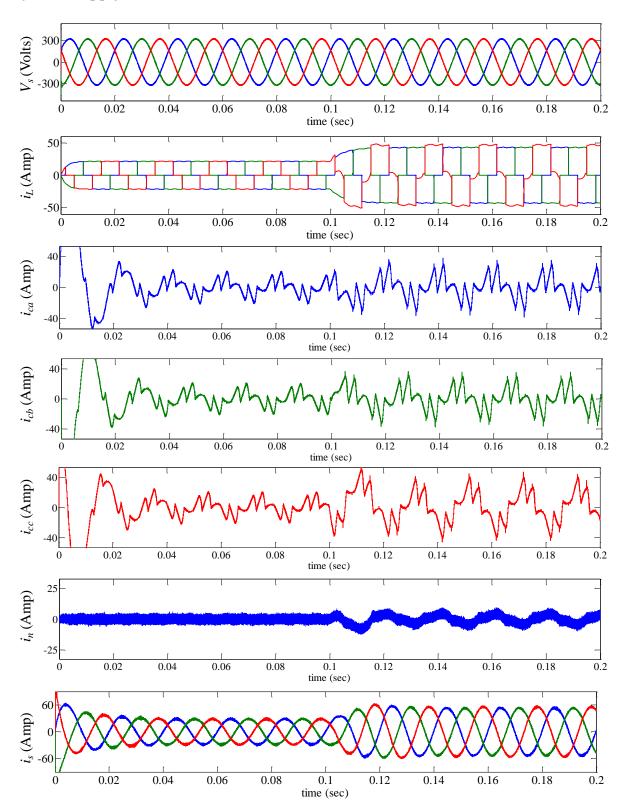

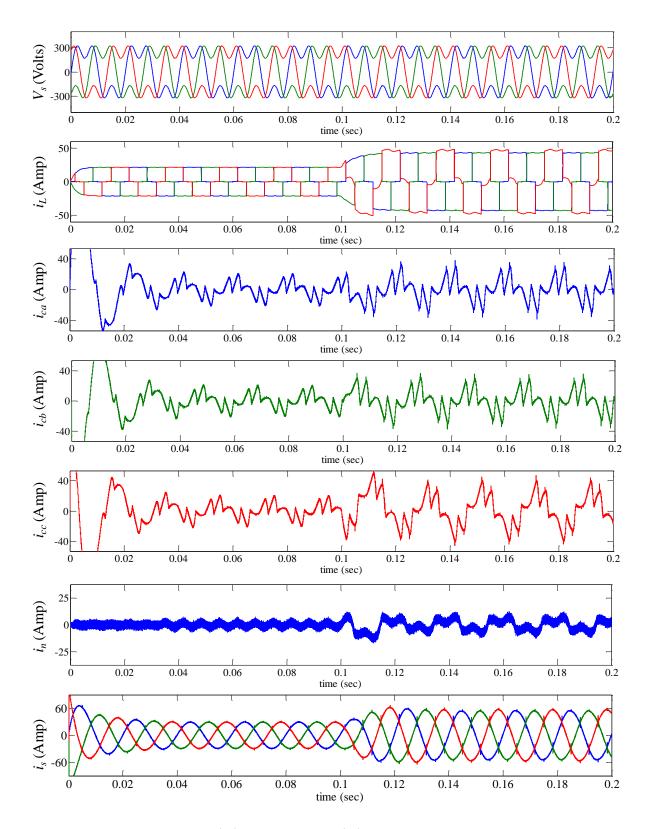

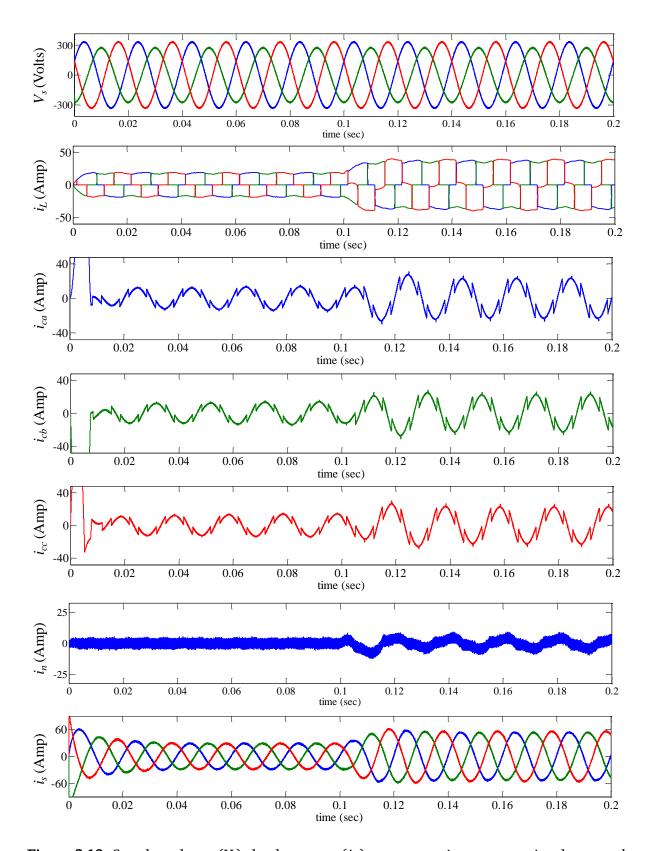

- 2.11 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing p-q control scheme under ideal supply condition

- 2.12 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing modified p-q control scheme under ideal supply condition

- 2.13 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, 50 b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing  $i_d i_q$  control scheme under ideal supply condition

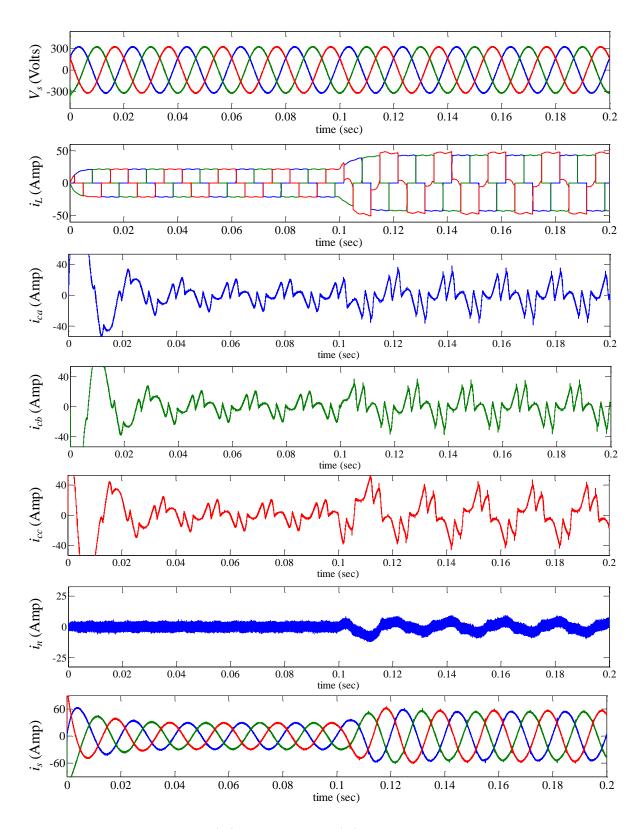

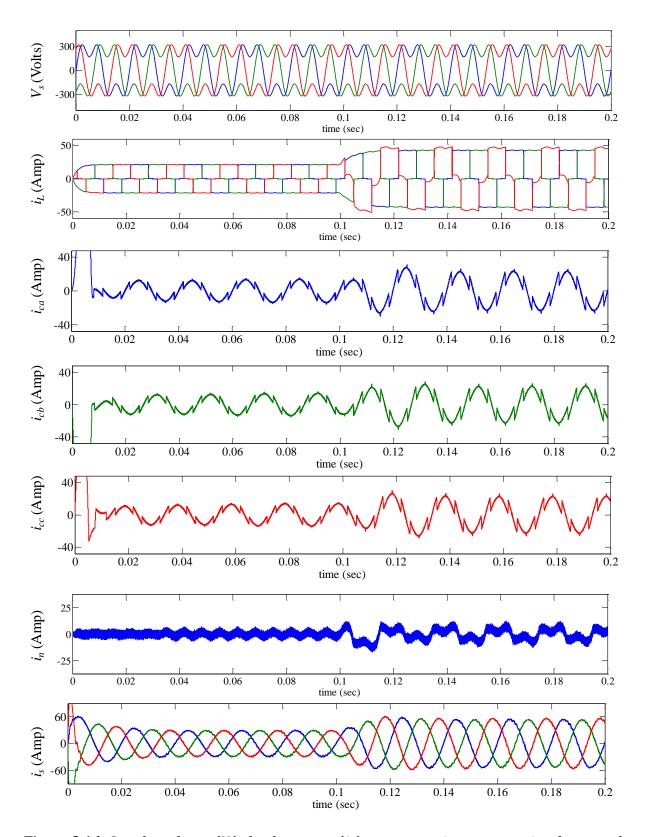

- 2.14 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, 51 b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing p-q control scheme under distorted supply condition

- 2.15 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, 52 b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing modified p-q control scheme under distorted supply condition

- 2.16 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, 53 b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing  $i_d i_q$  control scheme under distorted supply condition

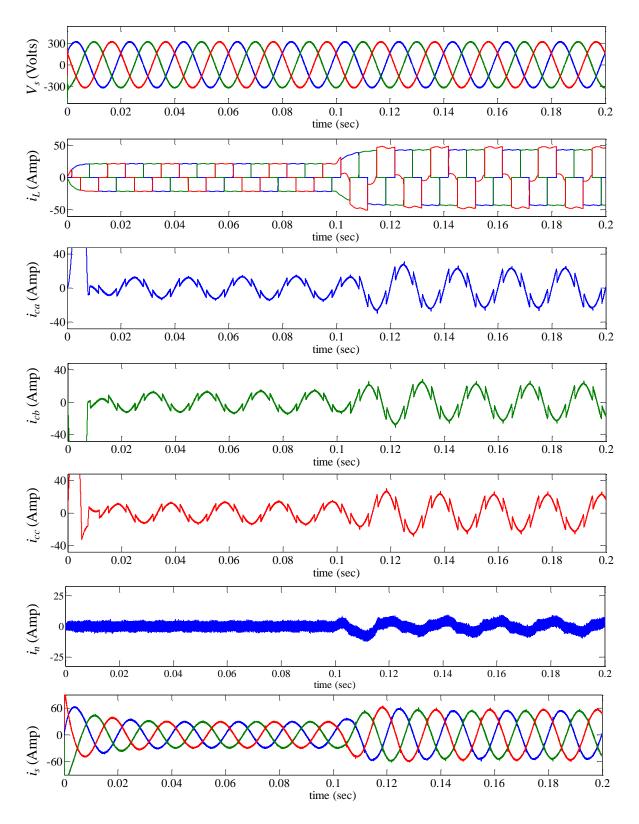

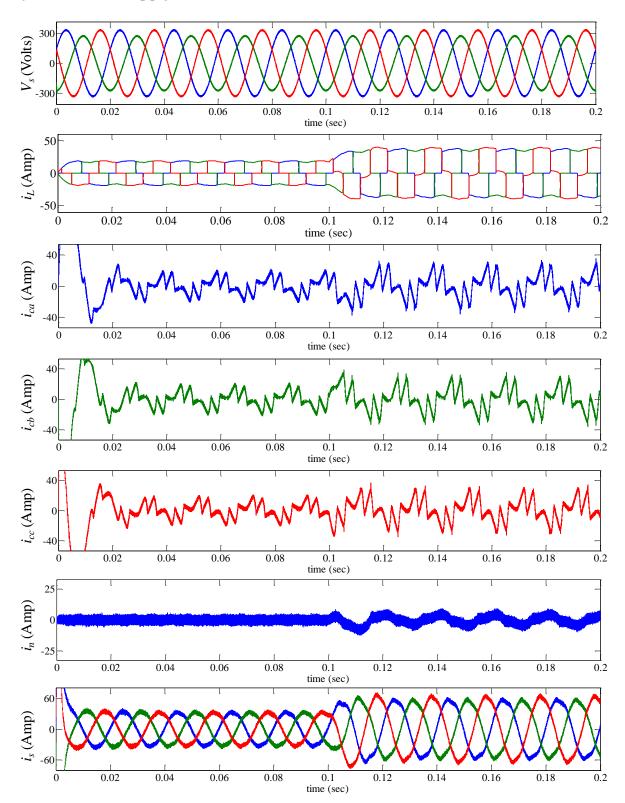

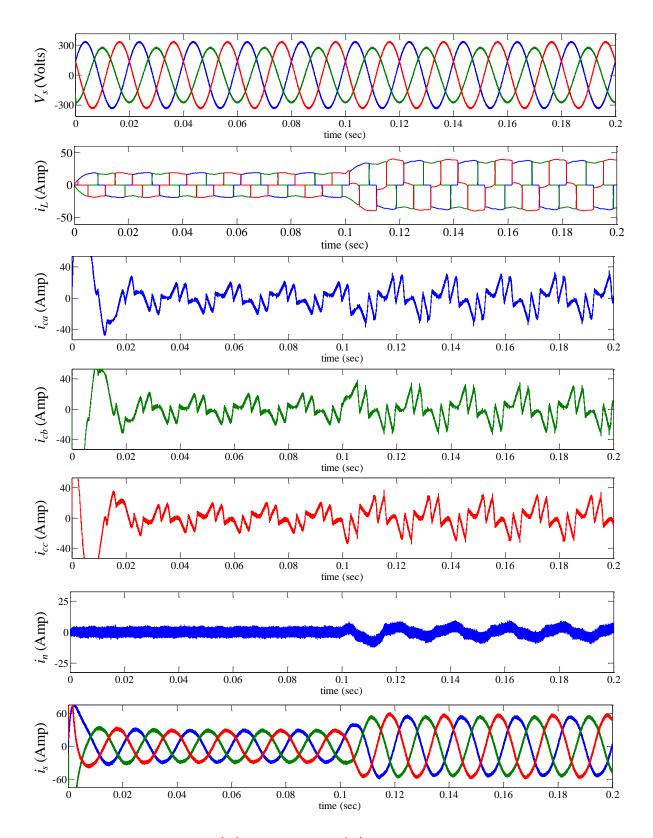

- 2.17 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing p-q control scheme under unbalanced supply condition

- 2.18 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, 55

- b and c ( $i_{ca}$ ,  $i_{cb}$ ,  $i_{cc}$ ), neutral current ( $i_n$ ) and source current ( $i_s$ ) waveforms for APF employing modified p-q control scheme under unbalanced supply condition

- 2.19 Supply voltage  $(V_s)$ , load current  $(i_L)$ , compensation currents in phases a, b and c  $(i_{ca}, i_{cb}, i_{cc})$ , neutral current  $(i_n)$  and source current  $(i_s)$  waveforms for APF employing  $i_d i_q$  control scheme under unbalanced supply condition

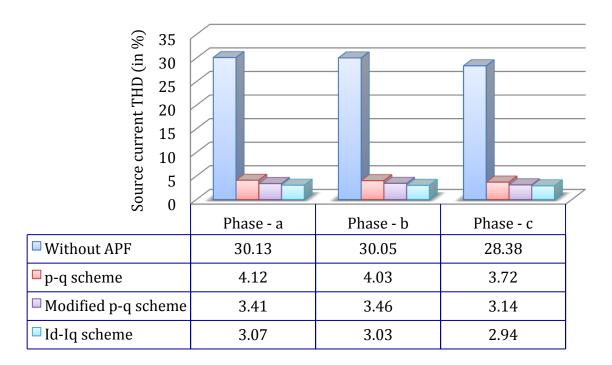

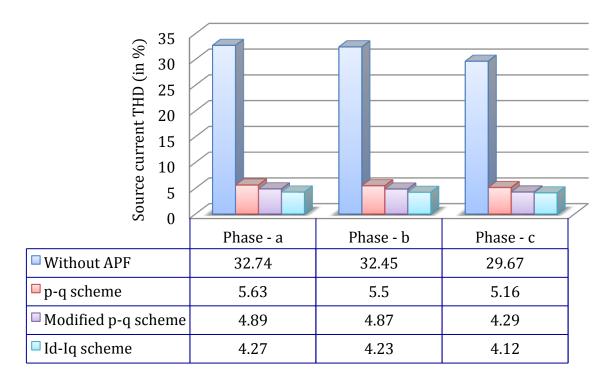

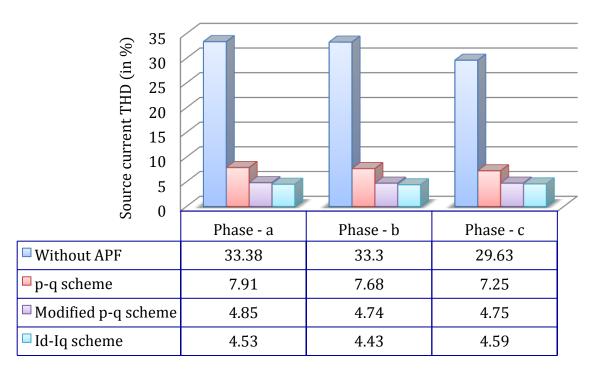

- 2.20 Chart diagram showing source current THDs (in %) before and after compensation with p-q, modified p-q and  $i_d-i_q$  control schemes for simulations under ideal supply condition

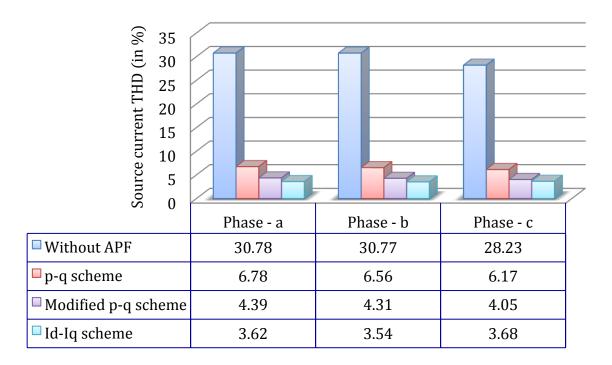

- 2.21 Chart diagram showing source current THDs (in %) before and after compensation with p-q, modified p-q and  $i_d-i_q$  control schemes for simulations under distorted supply condition

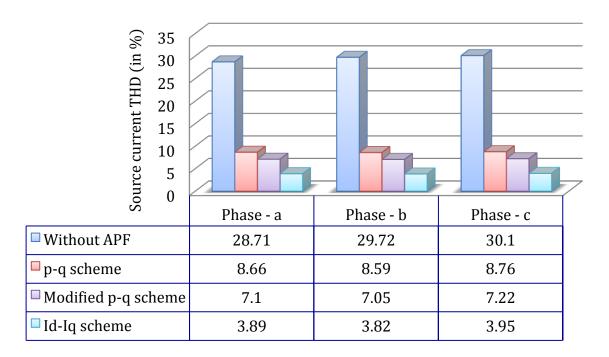

- 2.22 Chart diagram showing source current THDs (in %) before and after compensation with p-q, modified p-q and  $i_d-i_q$  control schemes for simulations under unbalanced supply condition

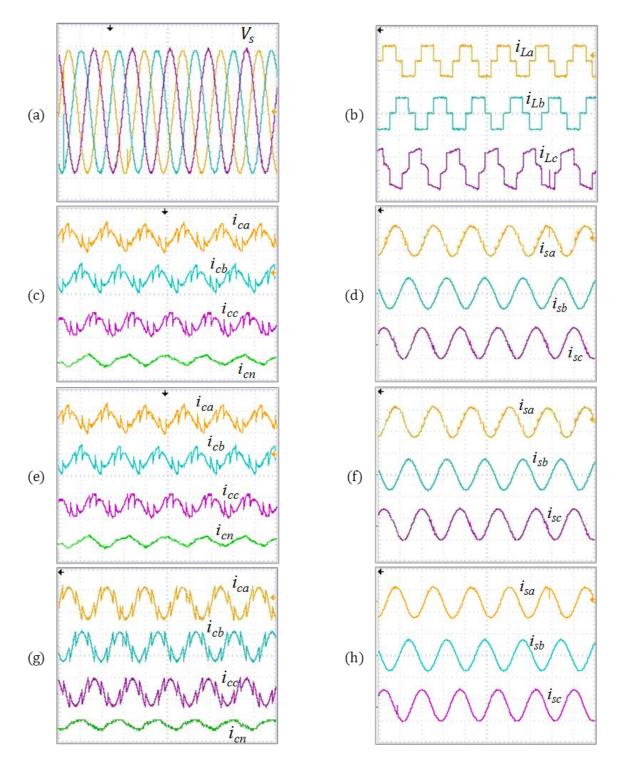

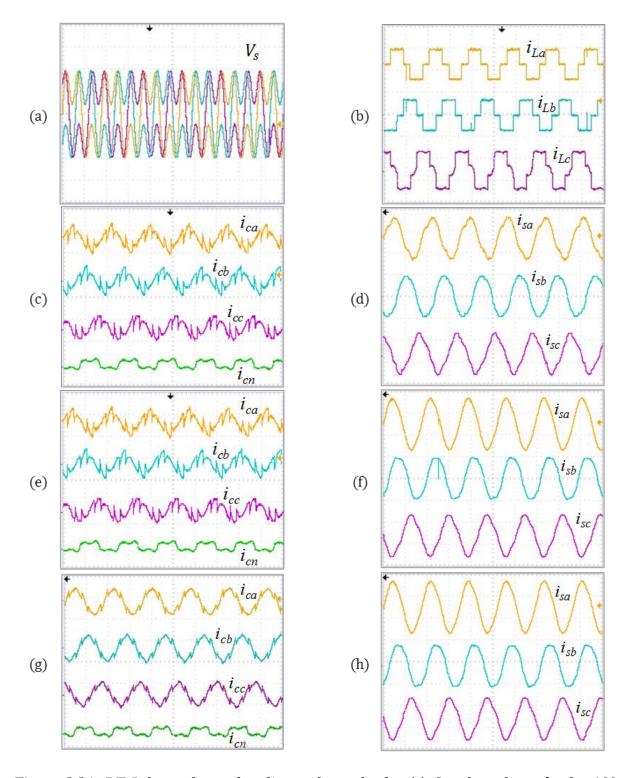

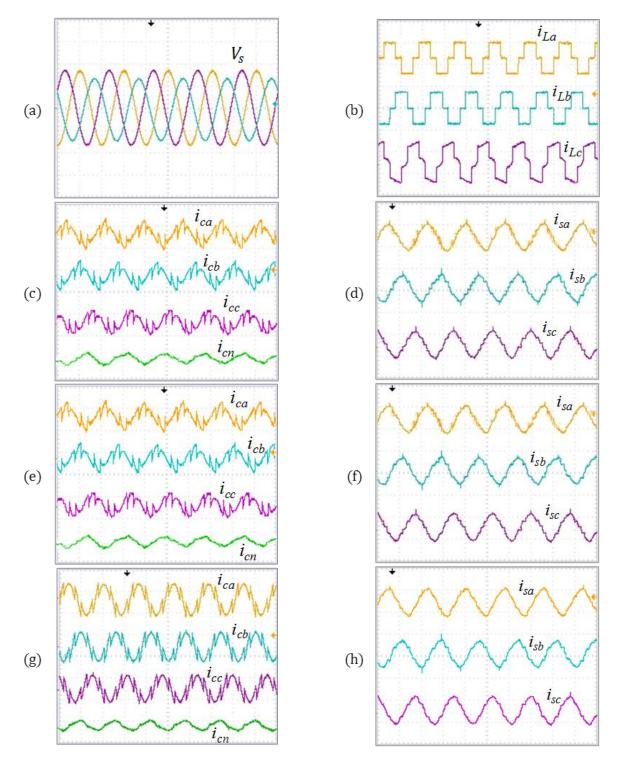

- 2.23 RT-Lab results under ideal supply for (a) Supply voltage, (b) Load current,

(c) Filter current for p q scheme, (d) Source current for p q scheme,

(e) Filter current for modified p q scheme, (f) Source current for modified p q scheme, (g) Filter current for i<sub>d</sub> i<sub>q</sub> scheme, (h) Source current for i<sub>d</sub> i<sub>q</sub> scheme

- 2.24 RT-Lab results under distorted supply for (a) Supply voltage, (b) Load current, (c) Filter current for p-q scheme, (d) Source current for p-q scheme, (e) Filter current for modified p-q scheme, (f) Source current for modified p-q scheme, (g) Filter current for  $i_d-i_q$  scheme, (h) Source current for  $i_d-i_q$  scheme

- 2.25 RT-Lab results under unbalanced supply for (a) Supply voltage, (b) Load current, (c) Filter current for p-q scheme, (d) Source current for p-q scheme, (e) Filter current for modified p-q scheme, (f) Source current

- for modified p-q scheme, (g) Filter current for  $i_d-i_q$  scheme, (h) Source current for  $i_d-i_q$  scheme

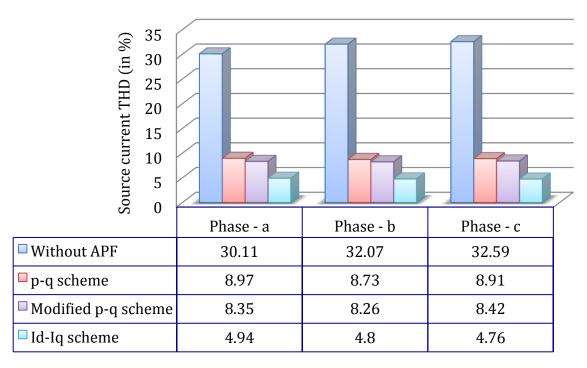

- 2.26 Chart diagram showing source current THDs (in %) obtained with RT- 64 Lab before and after compensation with p-q, modified p-q and  $i_d-i_q$  control schemes under ideal supply condition

- 2.27 Chart diagram showing source current THDs (in %) obtained with RT- 65 Lab before and after compensation with p-q, modified p-q and  $i_d-i_q$  control schemes under distorted supply condition

- 2.28 Chart diagram showing source current THDs (in %) obtained with RT- 65 Lab before and after compensation with p-q, modified p-q and  $i_d-i_q$  control schemes under unbalanced supply condition

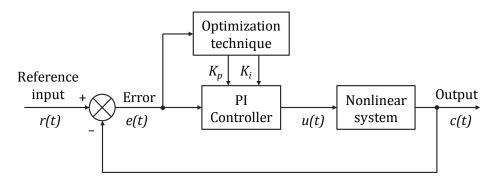

- 3.1 Block diagram for PI controller design with optimization technique

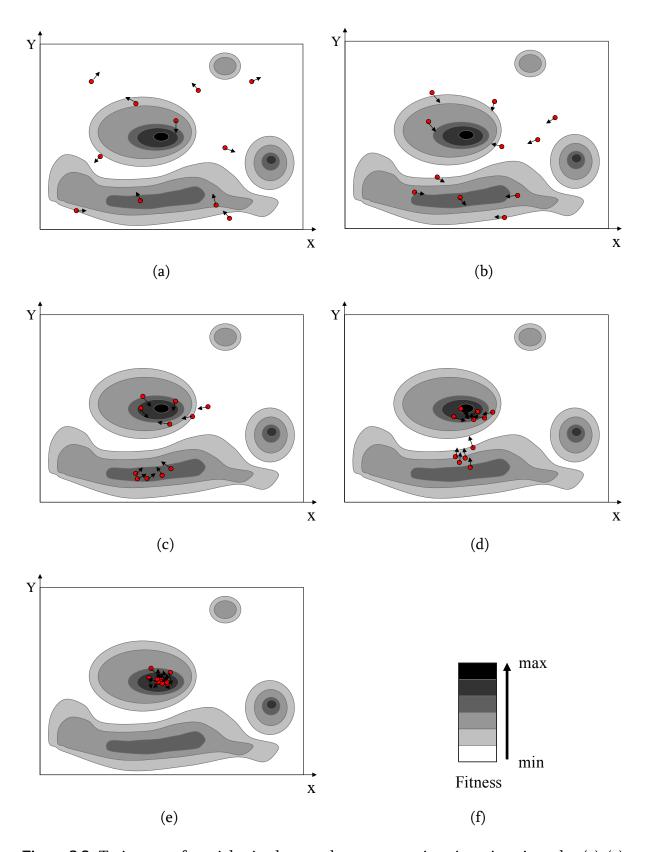

3.2 Trajectory of particles in the search space at various iterations in order

72

- (a)-(e) while moving towards the global minima, (f) Figure indicating the values of fitness function at various locations in the search space

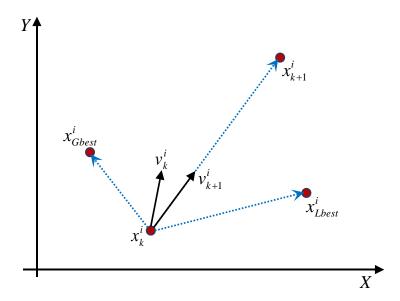

- 3.3 Position and velocity update of  $i^{\text{th}}$  particle in the swarm 73

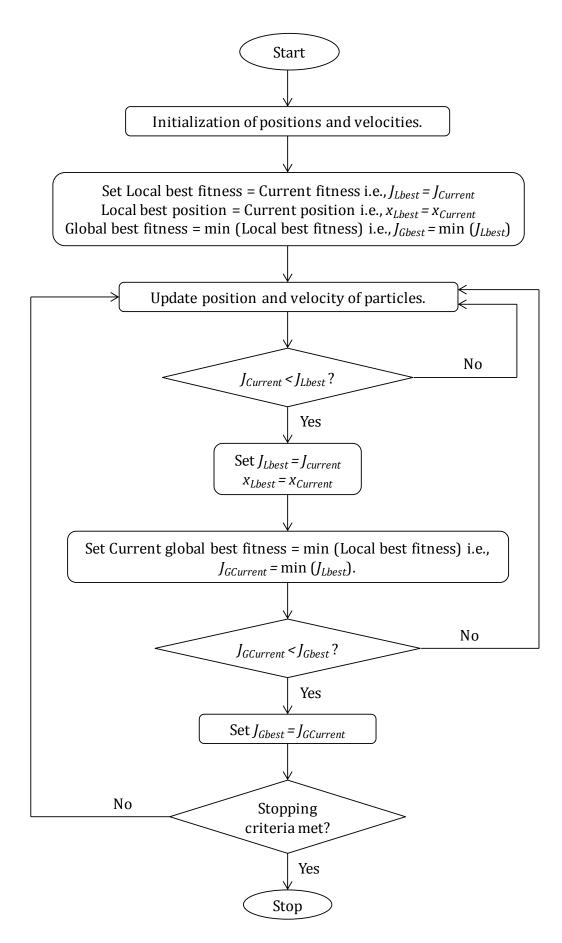

- 3.4 Flowchart of PSO 76

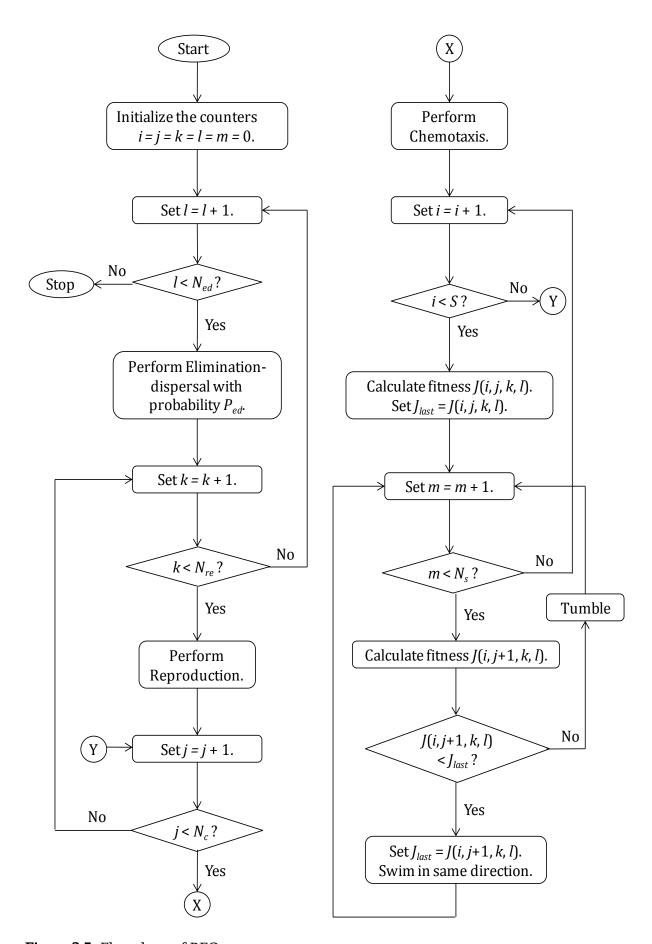

- 3.5 Flowchart of BFO 80

- 3.6 Flowchart of Enhanced BFO 85

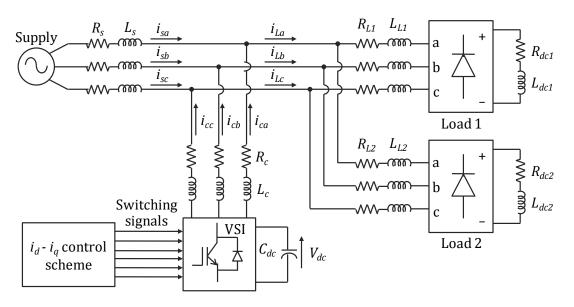

- 3.7 VSI-based shunt APF system configuration along with the nonlinear loads 89

- 3.8 Block diagram of closed loop control of inverter DC-link voltage for the

APF system employing optimization techniques

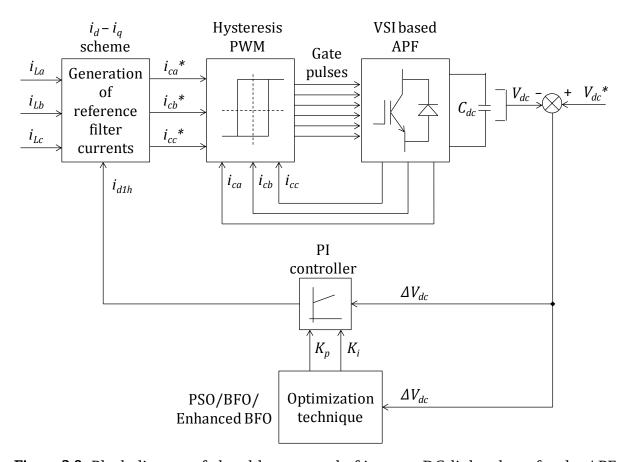

- 3.9 Convergence characteristics of PSO, BFO and Enhanced BFO algorithms 94 under (a) Ideal, (b) Distorted, (c) Unbalanced supplies

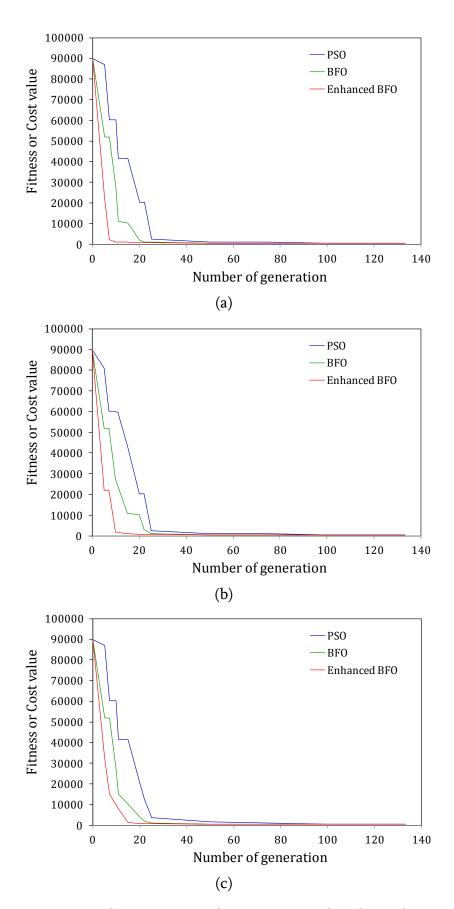

- 3.10 Relative convergence of  $V_{dc}$  for conventional, PSO, BFO and Enhanced 95 BFO-based APFs under (a) Ideal, (b) Distorted, (c) Unbalanced supplies

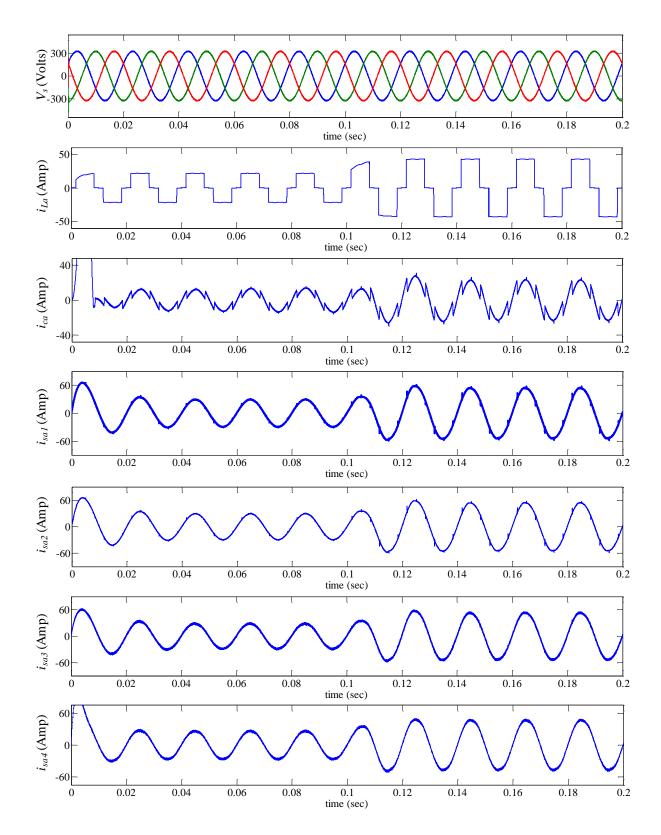

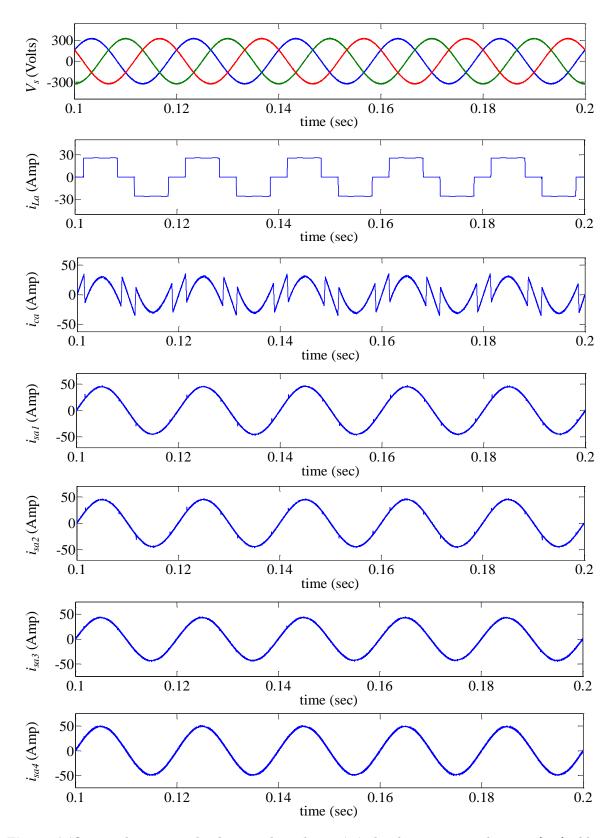

- 3.11 Simulation waveforms for supply voltage  $(V_s)$ , load current in phase-a 98  $(i_{La})$ , compensation current in phase-a  $(i_{ca})$ , and source currents in

| phase- $a$ for APF employing conventional PI $(i_{sa1})$ , PSO-based PI $(i_{sa2})$ |

|-------------------------------------------------------------------------------------|

| BFO-based PI $(i_{sa3})$ and Enhanced BFO-based PI $(i_{sa4})$ under ideal supply   |

99

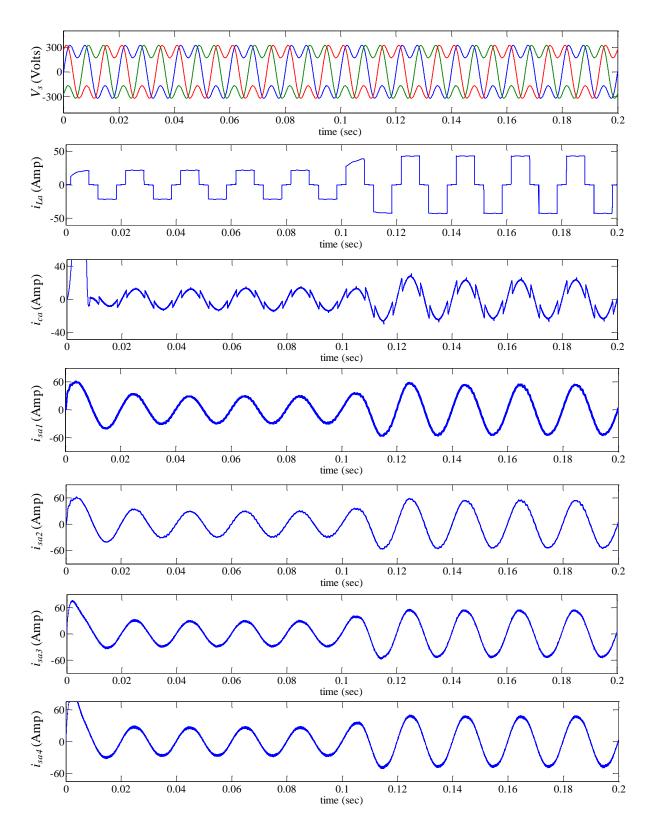

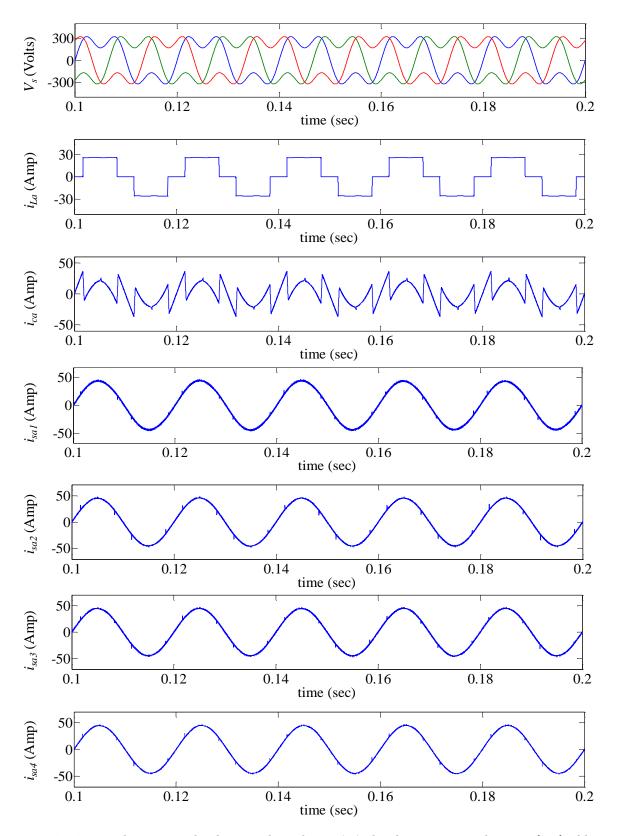

- 3.12 Simulation waveforms for supply voltage  $(V_s)$ , load current in phase-a  $(i_{La})$ , compensation current in phase-a  $(i_{ca})$ , and source currents in phase-a for APF employing conventional PI  $(i_{sa1})$ , PSO-based PI  $(i_{sa2})$ , BFO-based PI  $(i_{sa3})$  and Enhanced BFO-based PI  $(i_{sa4})$  under distorted supply

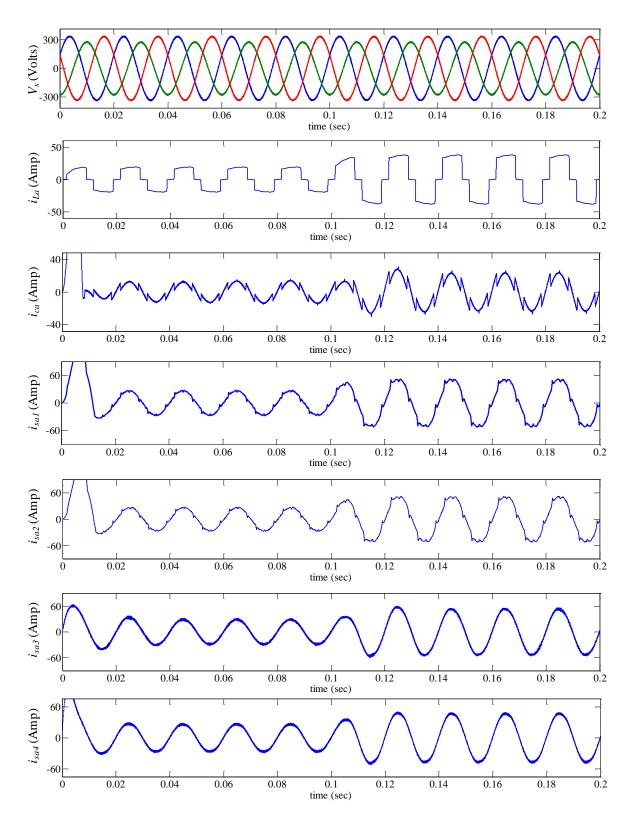

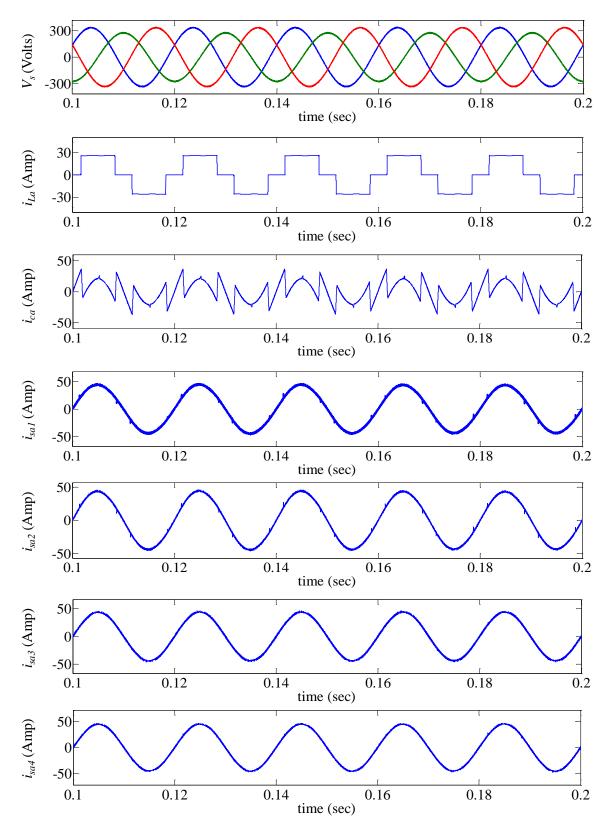

- 3.13 Simulation waveforms for supply voltage ( $V_s$ ), load current in phase-a 100 ( $i_{La}$ ), compensation current in phase-a ( $i_{ca}$ ), and source currents in phase-a for APF employing conventional PI ( $i_{sa1}$ ), PSO-based PI ( $i_{sa2}$ ), BFO-based PI ( $i_{sa3}$ ) and Enhanced BFO-based PI ( $i_{sa4}$ ) under unbalanced supply

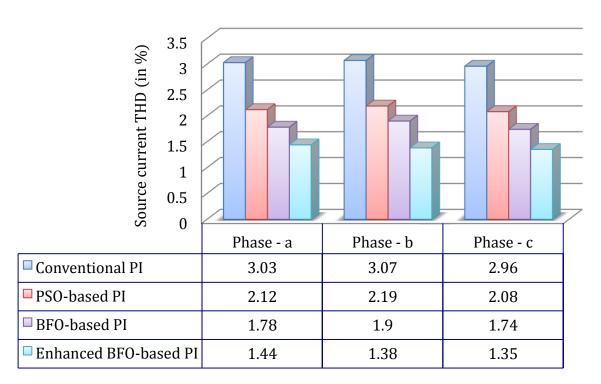

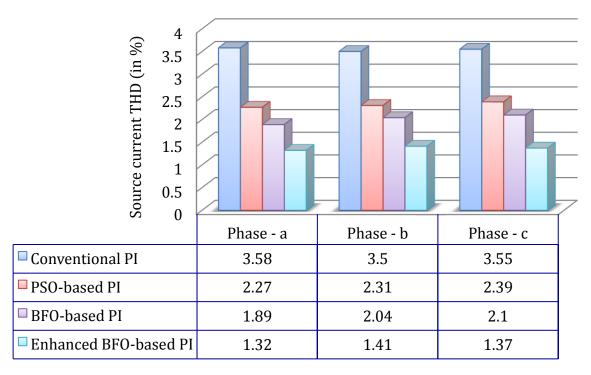

- 3.14 Chart diagram showing source current THDs (in %) obtained with 101 simulation of APF employing conventional, PSO-based, BFO-based and Enhanced BFO-based PI controllers under ideal supply condition

- 3.15 Chart diagram showing source current THDs (in %) obtained with 101 simulation of APF employing conventional, PSO-based, BFO-based and Enhanced BFO-based PI controllers under distorted supply condition

- 3.16 Chart diagram showing source current THDs (in %) obtained with 102 simulation of APF employing conventional, PSO-based, BFO-based and Enhanced BFO-based PI controllers under unbalanced supply condition

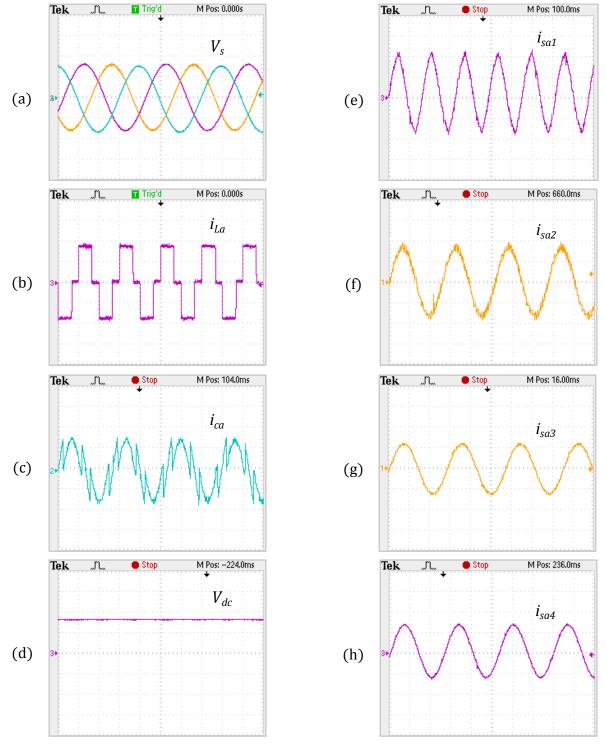

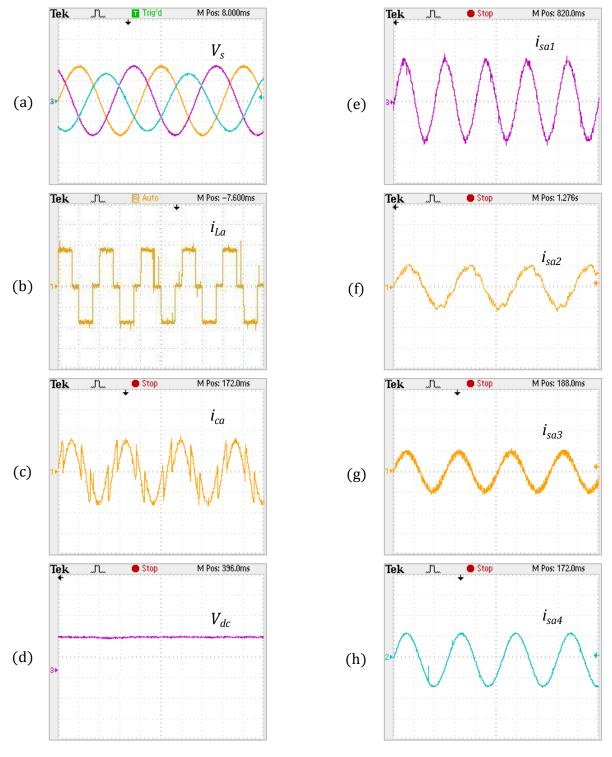

- 3.17 RT-Lab results for (a) Supply voltage  $(V_s)$ , (b) Load current in phase-a 103  $(i_{La})$ , (c) Compensation filter current in phase-a  $(i_{ca})$ , (d) DC-link voltage  $(V_{dc})$ , (e)-(h) Source current in phase-a for APF employing conventional PI  $(i_{sa1})$ , PSO-PI  $(i_{sa2})$ , BFO-PI  $(i_{sa3})$  and Enhanced BFO-PI  $(i_{sa4})$  under ideal supply

- 3.18 RT-Lab results for (a) Supply voltage  $(V_s)$ , (b) Load current in phase-a 104  $(i_{La})$ , (c) Compensation filter current in phase-a  $(i_{ca})$ , (d) DC-link voltage  $(V_{dc})$ , (e)-(h) Source current in phase-a for APF employing

|      | conventional PI $(i_{sa1})$ , PSO-PI $(i_{sa2})$ , BFO-PI $(i_{sa3})$ and Enhanced BFO- |     |

|------|-----------------------------------------------------------------------------------------|-----|

|      | PI $(i_{sa4})$ under distorted supply                                                   |     |

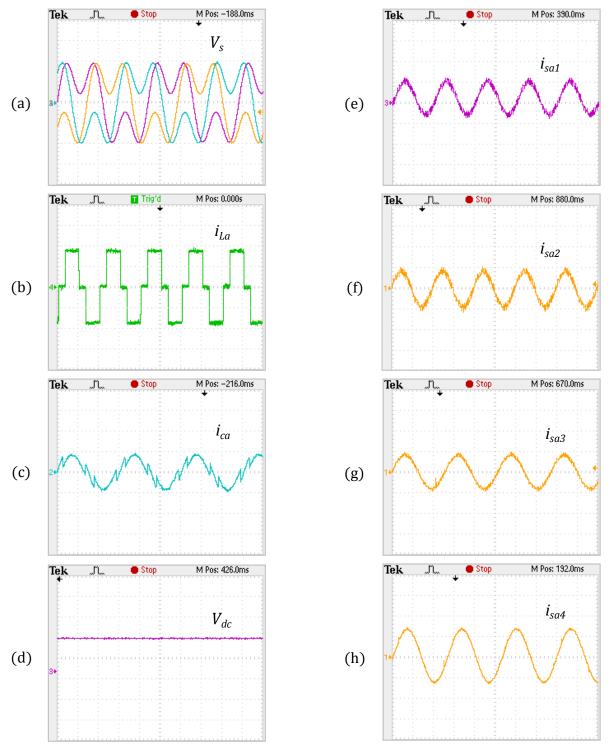

| 3.19 | RT-Lab results for (a) Supply voltage $(V_s)$ , (b) Load current in phase- $a$          | 105 |

|      | $(i_{La})$ , (c) Compensation filter current in phase- $a$ $(i_{ca})$ , (d) DC-link     |     |

|      | voltage ( $V_{dc}$ ), (e)-(h) Source current in phase- $a$ for APF employing            |     |

|      | conventional PI $(i_{sa1})$ , PSO-PI $(i_{sa2})$ , BFO-PI $(i_{sa3})$ and Enhanced BFO- |     |

|      | PI ( $i_{sa4}$ ) under unbalanced supply                                                |     |

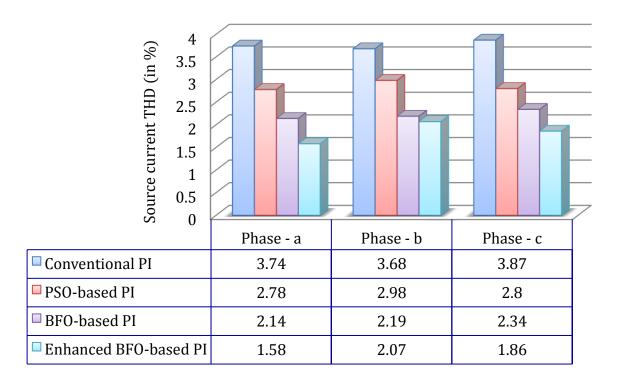

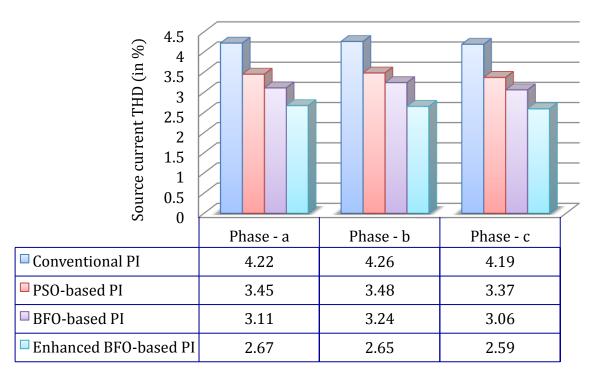

| 3.20 | Chart diagram showing source current THDs (in %) obtained in RT-Lab                     | 106 |

|      | with APF employing conventional, PSO-based, BFO-based and Enhanced                      |     |

|      | BFO-based PI controllers under ideal supply condition                                   |     |

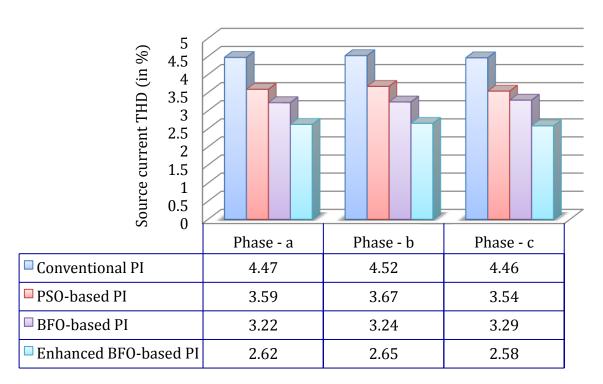

| 3.21 | Chart diagram showing source current THDs (in %) obtained in RT-Lab                     | 107 |

|      | with APF employing conventional, PSO-based, BFO-based and Enhanced                      |     |

|      | BFO-based PI controllers under distorted supply condition                               |     |

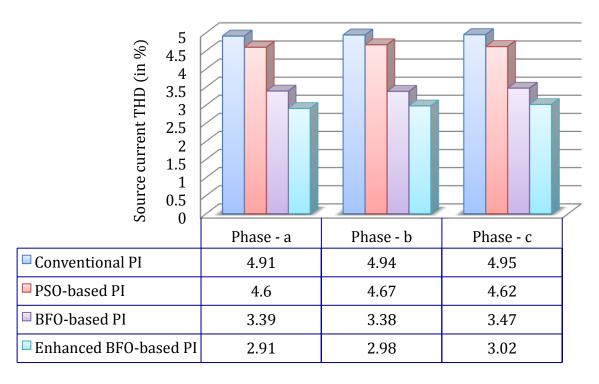

| 3.22 | Chart diagram showing source current THDs (in %) obtained in RT-Lab                     | 107 |

|      | with APF employing conventional, PSO-based, BFO-based and Enhanced                      |     |

|      | BFO-based PI controllers under unbalanced supply condition                              |     |

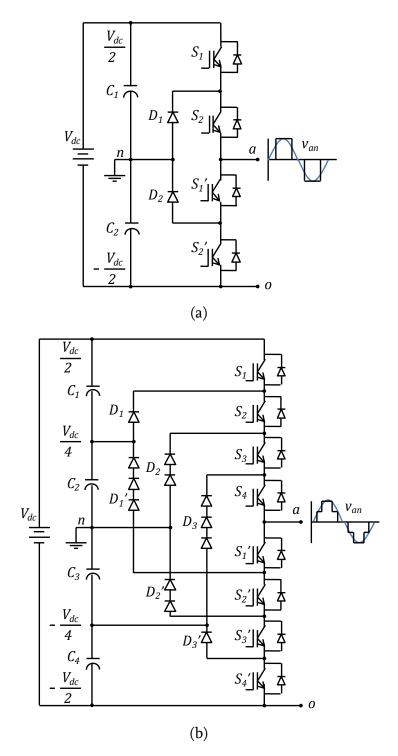

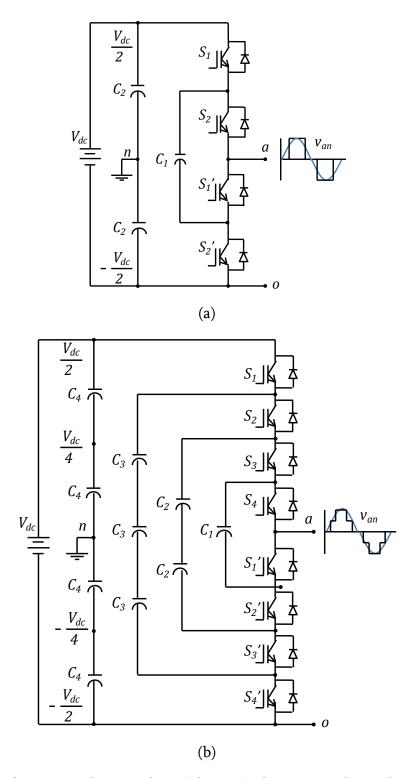

| 4.1  | Configurations for one phase (phase-a) of diode-clamped inverter of (a)                 | 113 |

|      | Level 3, (b) Level 5                                                                    |     |

| 4.2  | Configurations for one phase (phase-a) of capacitor-clamped MLI of (a)                  | 115 |

|      | Level 3, (b) Level 5                                                                    |     |

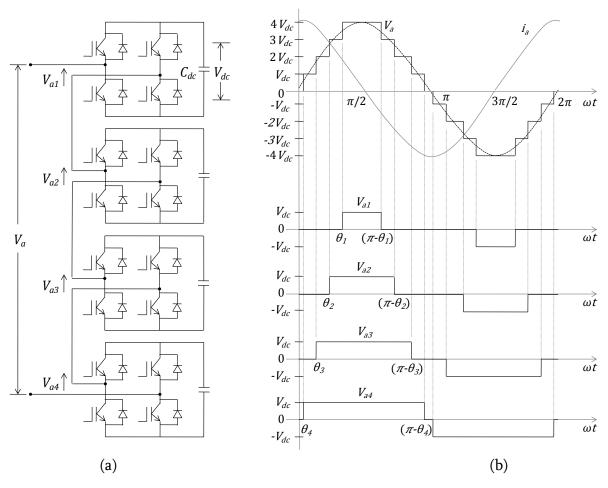

| 4.3  | (a) Circuit diagram, (b) Output phase voltage waveform for one phase                    | 117 |

|      | (phase-a) of a cascaded H-bridge 9-level inverter                                       |     |

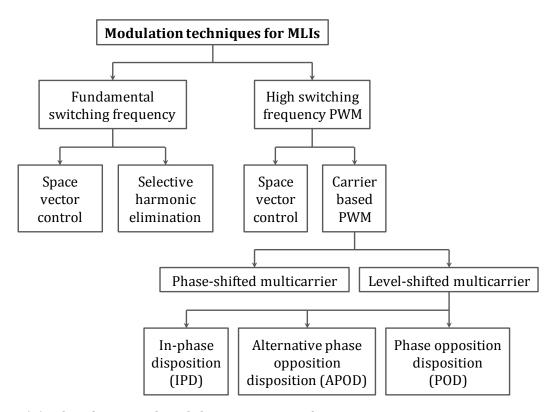

| 4.4  | Classification of modulation strategies for MLI                                         | 120 |

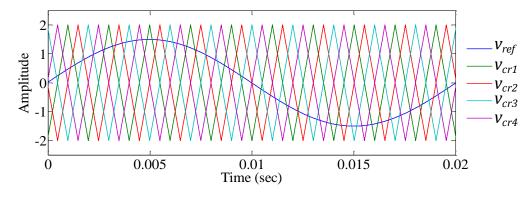

| 4.5  | Phase-shifted multicarrier PWM for a 5-level cascaded MLI                               | 122 |

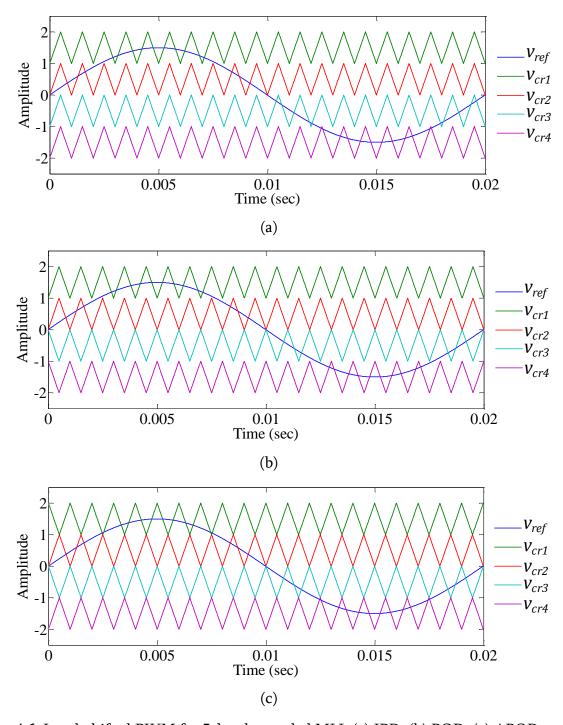

| 4.6  | Level-shifted PWM for 5-level cascaded MLI, (a) IPD, (b) POD, (c) APOD                  | 123 |

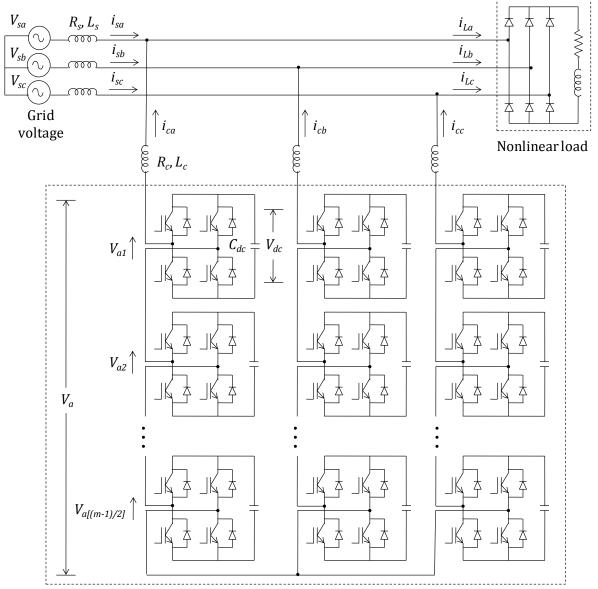

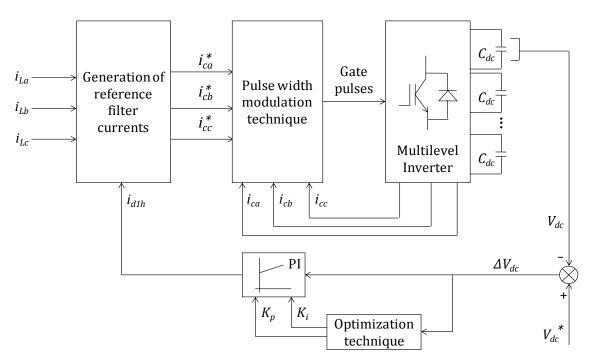

| 4.7  | System configuration of shunt APF employing cascaded MLI                                | 127 |

| 4.8  | Closed loop control block diagram of the cascaded MLI based APF system                  | 129 |

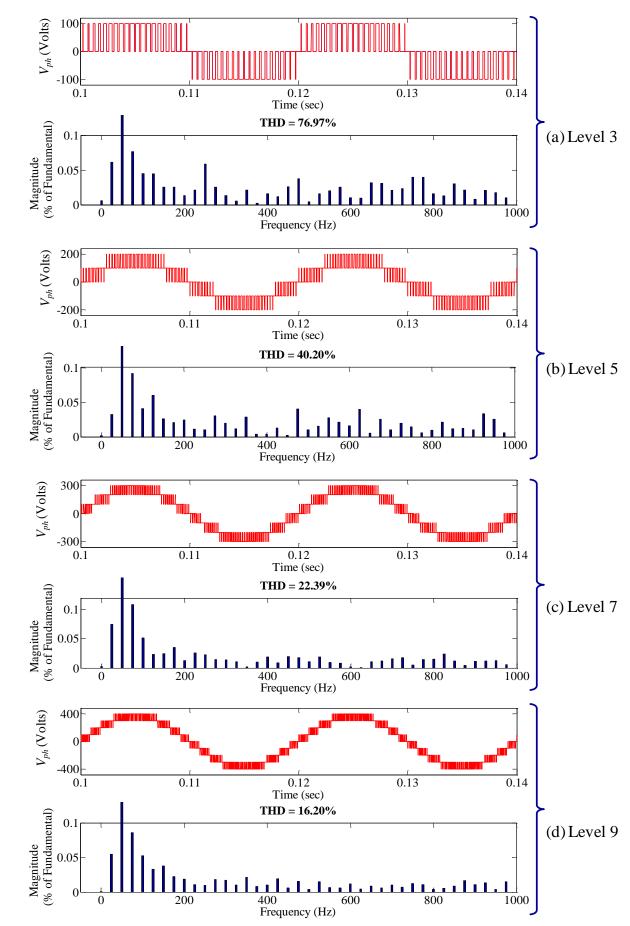

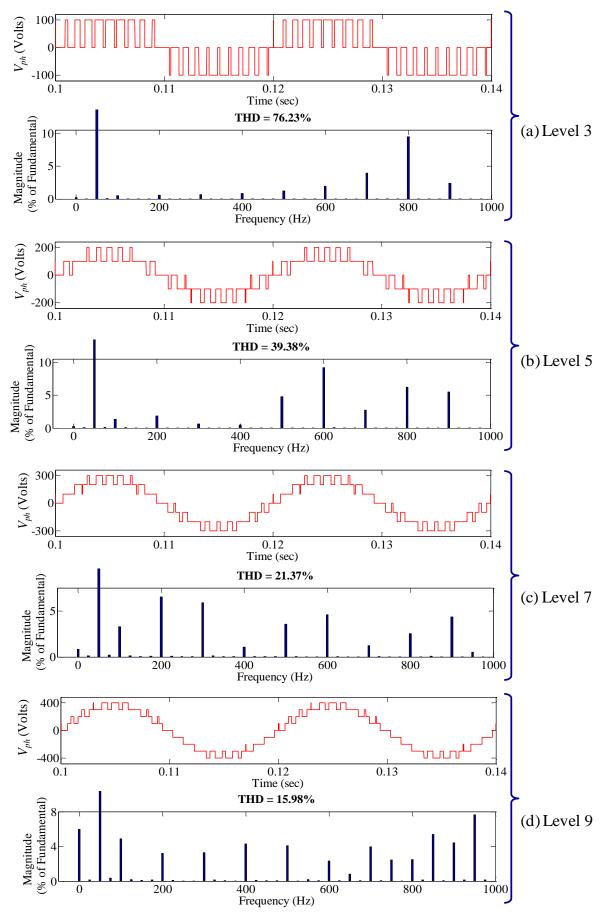

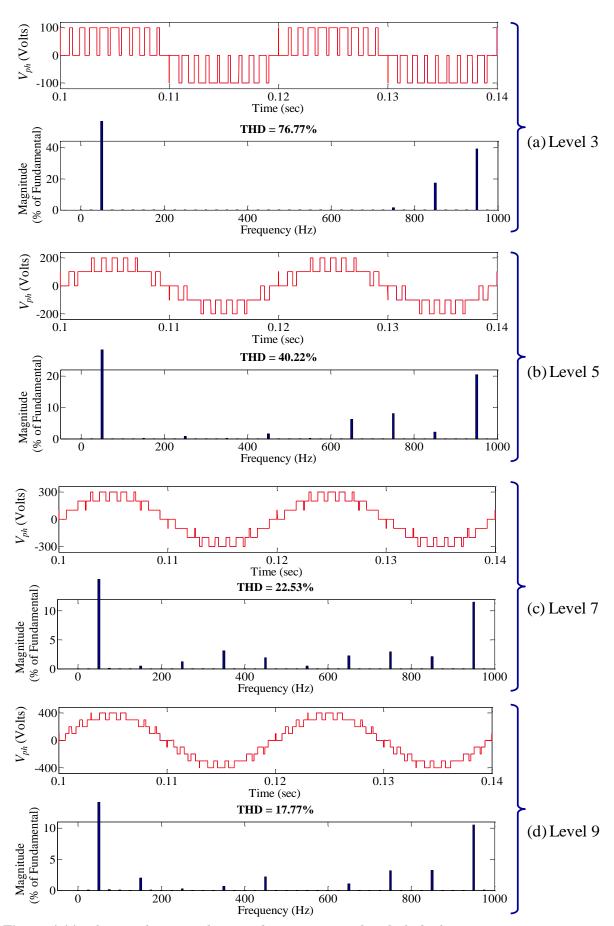

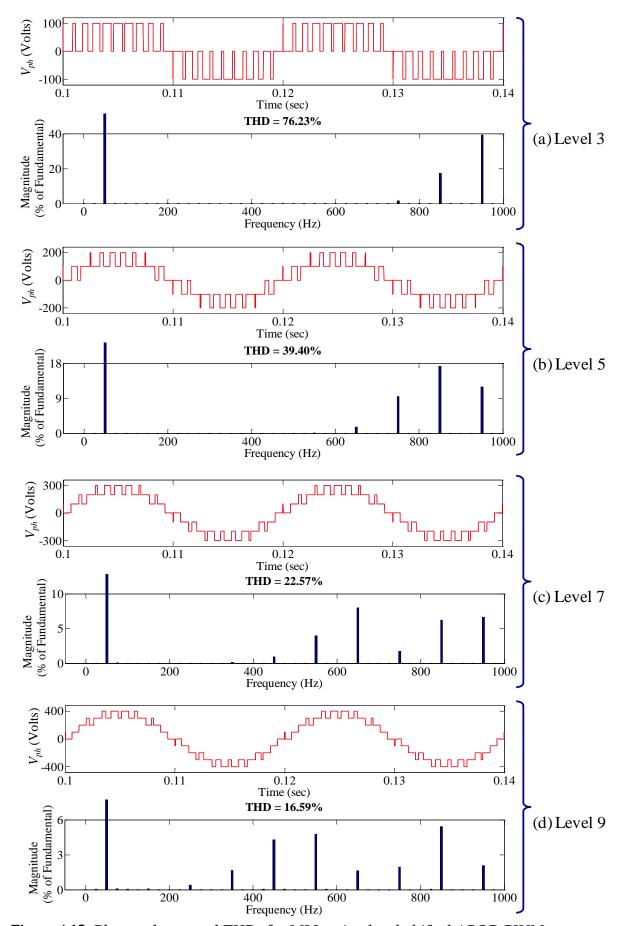

| 4.9  | Phase voltages and THDs for MLIs using phase-shifted PWM                                | 130 |

| 4.10 | Phase voltage and THD for MLIs using level-shifted IPD PWM                                | 131 |

|------|-------------------------------------------------------------------------------------------|-----|

| 4.11 | Phase voltage and THD for MLIs using level-shifted POD PWM                                | 132 |

| 4.12 | Phase voltage and THD for MLIs using level-shifted APOD PWM                               | 133 |

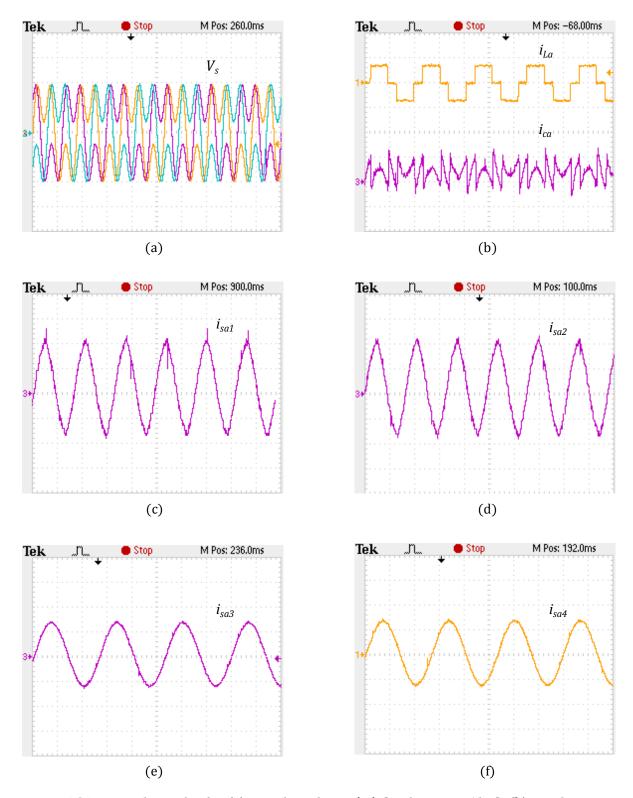

| 4.13 | Simulation results for supply voltage $(V_s)$ , load current in phase- $a$ $(i_{La})$ ,   | 136 |

|      | filter current in phase- $a$ ( $i_{ca}$ ), and compensated source currents in phase-      |     |

|      | a obtained with APF employing 3-level ( $i_{sa1}$ ), 5-level ( $i_{sa2}$ ), 7-level       |     |

|      | $(i_{sa3})$ and 9-level $(i_{sa4})$ MLIs under ideal supply condition                     |     |

| 4.14 | Simulation results for supply voltage $(V_s)$ , load current in phase- $a$ $(i_{La})$ ,   | 137 |

|      | filter current in phase- $a$ ( $i_{ca}$ ), and compensated source currents in phase-      |     |

|      | a obtained with APF employing 3-level ( $i_{sa1}$ ), 5-level ( $i_{sa2}$ ), 7-level       |     |

|      | $(i_{sa3})$ and 9-level $(i_{sa4})$ MLIs under distorted supply condition                 |     |

| 4.15 | Simulation results for supply voltage $(V_s)$ , load current in phase- $a$ $(i_{La})$ ,   | 138 |

|      | filter current in phase- $a$ ( $i_{ca}$ ), and compensated source currents in phase-      |     |

|      | a obtained with APF employing 3-level ( $i_{sa1}$ ), 5-level ( $i_{sa2}$ ), 7-level       |     |

|      | $(i_{sa3})$ and 9-level $(i_{sa4})$ MLIs under unbalanced supply condition                |     |

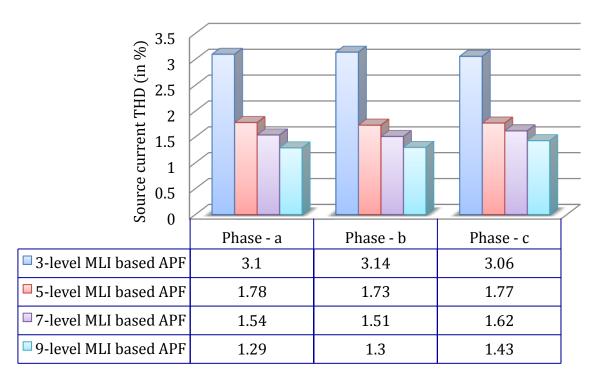

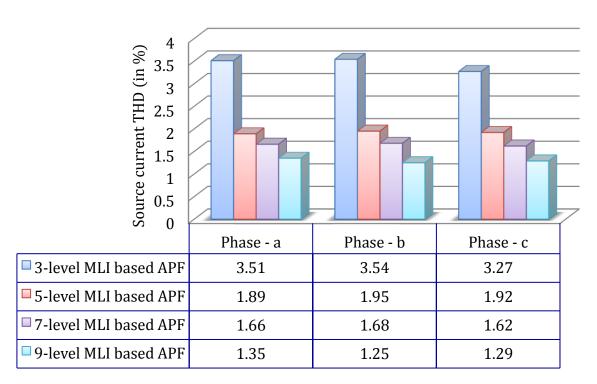

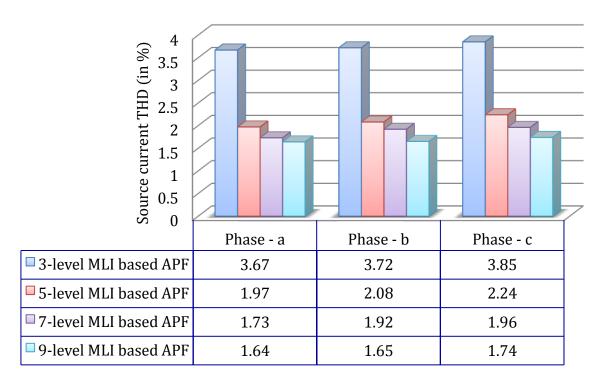

| 4.16 | Chart diagram showing source current THDs (in %) obtained with                            | 139 |

|      | simulation of APF employing 3-level, 5-level, 7-level and 9-level cascaded                |     |

|      | MLIs under ideal supply condition                                                         |     |

| 4.17 | Chart diagram showing source current THDs (in %) obtained with                            | 140 |

|      | simulation of APF employing 3-level, 5-level, 7-level and 9-level cascaded                |     |

|      | MLIs under distorted supply condition                                                     |     |

| 4.18 | Chart diagram showing source current THDs (in %) obtained with                            | 140 |

|      | simulation of APF employing 3-level, 5-level, 7-level and 9-level cascaded                |     |

|      | MLIs under unbalanced supply condition                                                    |     |

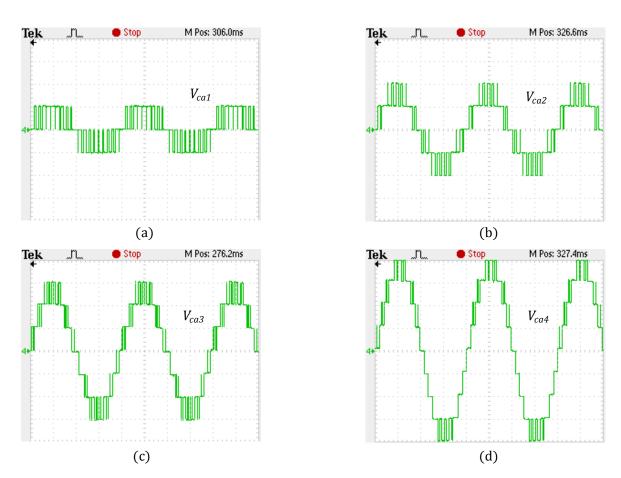

| 4.19 | RT-Lab results for output phase voltages for cascaded MLIs of (a) Level-3                 | 141 |

|      | $(V_{ca1})$ , (b) Level-5 $(V_{ca2})$ , (c) Level-7 $(V_{ca3})$ , (d) Level-9 $(V_{ca4})$ |     |

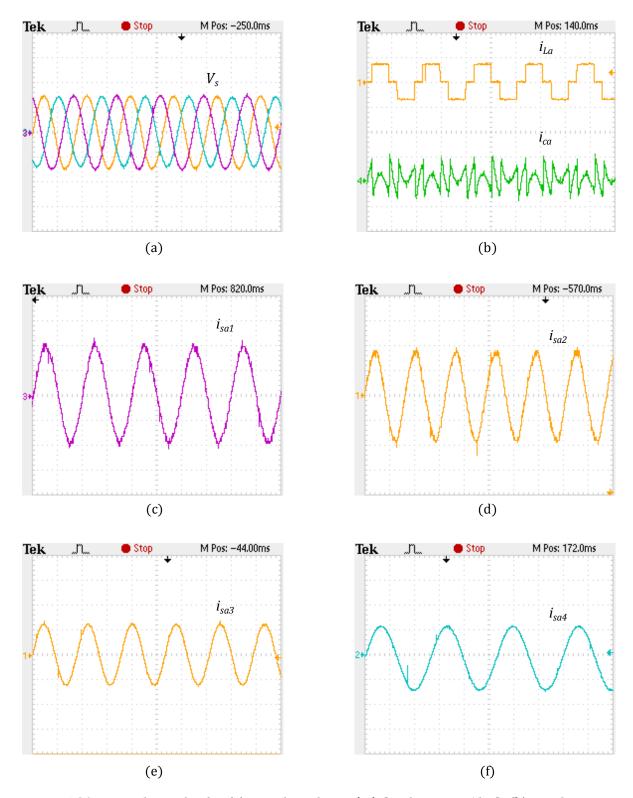

| 4.20 | RT-Lab results for (a) Supply voltage $(V_s)$ , (b) Load current $(i_{La})$ and filter    | 142 |

|      | current $(i_{ca})$ , $(c)$ – $(f)$ Source currents after compensation with APF            |     |

|      | employing MLIs of level-3 $(i_{sa1})$ , level-5 $(i_{sa2})$ , level-7 $(i_{sa3})$ and level-9 |     |

|------|-----------------------------------------------------------------------------------------------|-----|

|      | $(i_{sa4})$ under ideal supply                                                                |     |

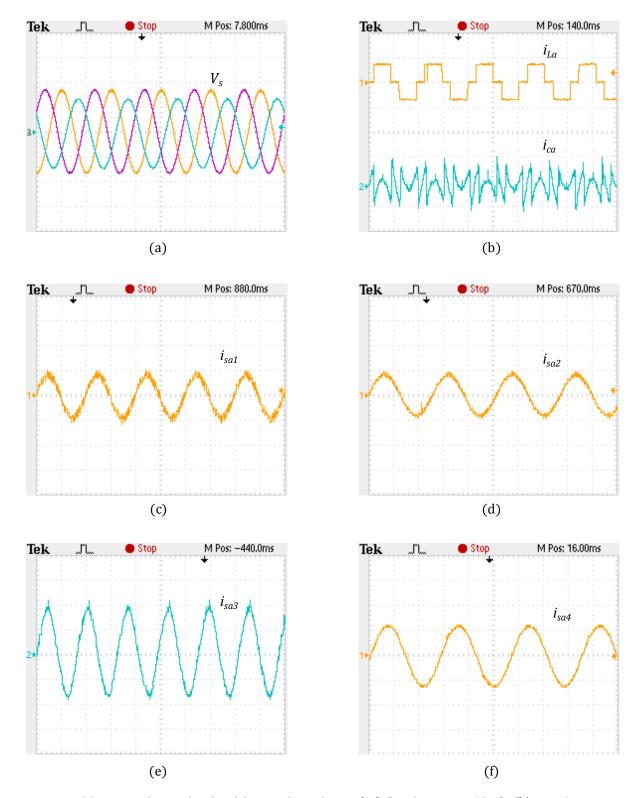

| 4.21 | RT-Lab results for (a) Supply voltage $(V_s)$ , (b) Load current $(i_{La})$ and filter        | 143 |

|      | current $(i_{ca})$ , $(c)$ – $(f)$ Source currents after compensation with APF                |     |

|      | employing MLIs of level-3 $(i_{sa1})$ , level-5 $(i_{sa2})$ , level-7 $(i_{sa3})$ and level-9 |     |

|      | $(i_{sa4})$ under distorted supply                                                            |     |

| 4.22 | RT-Lab results for (a) Supply voltage $(V_s)$ , (b) Load current $(i_{La})$ and filter        | 144 |

|      | current ( $i_{ca}$ ), (c)–(f) Source currents after compensation with APF                     |     |

|      | employing MLIs of level-3 $(i_{sa1})$ , level-5 $(i_{sa2})$ , level-7 $(i_{sa3})$ and level-9 |     |

|      | $(i_{sa4})$ under unbalanced supply                                                           |     |

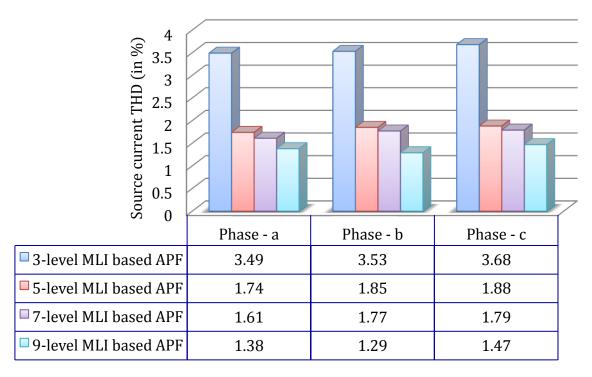

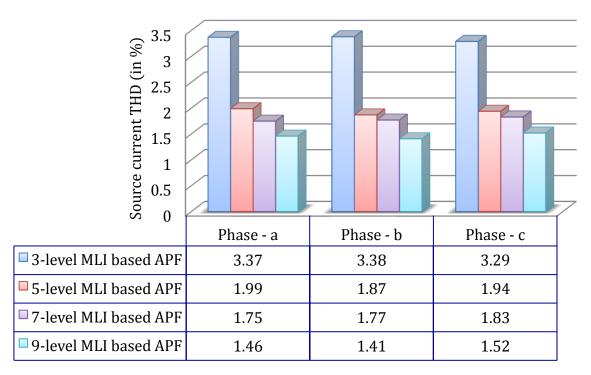

| 4.23 | Chart diagram showing source current THDs (in %) obtained in RT-Lab                           | 145 |

|      | after compensation with APFs employing 3-level, 5-level, 7-level and 9-                       |     |

|      | level MLIs under ideal supply condition                                                       |     |

| 4.24 | Chart diagram showing source current THDs (in %) obtained in RT-Lab                           | 146 |

|      | after compensation with APFs employing 3-level, 5-level, 7-level and 9-                       |     |

|      | level MLIs under distorted supply condition                                                   |     |

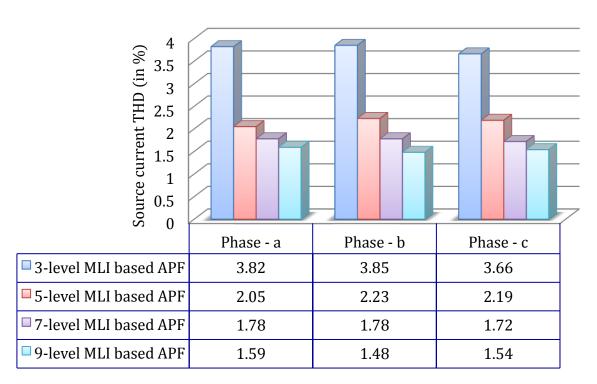

| 4.25 | Chart diagram showing source current THDs (in %) obtained in RT-Lab                           | 146 |

|      | after compensation with APFs employing 3-level, 5-level, 7-level and 9-                       |     |

|      | level MLIs under unbalanced supply condition                                                  |     |

| 5.1  | Triplen harmonic currents in three-phase power systems                                        | 149 |

| 5.2  | System configuration of split-capacitor (2C) VSI based shunt APF                              | 151 |

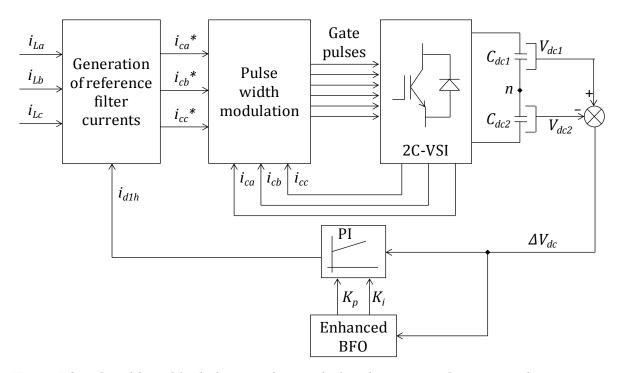

| 5.3  | Closed loop block diagram for DC-link voltage control in 2C topology                          | 153 |

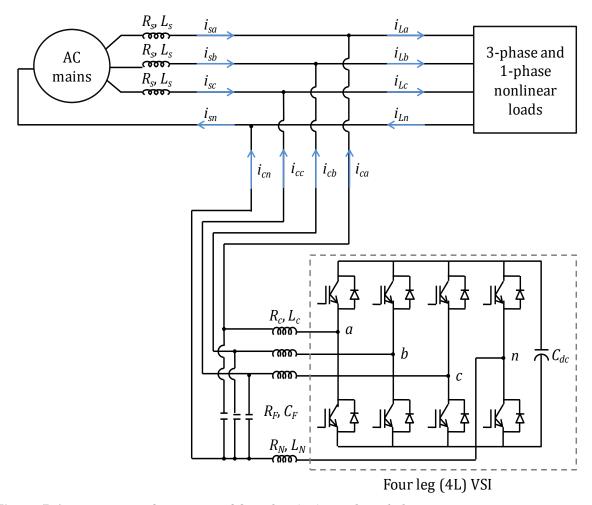

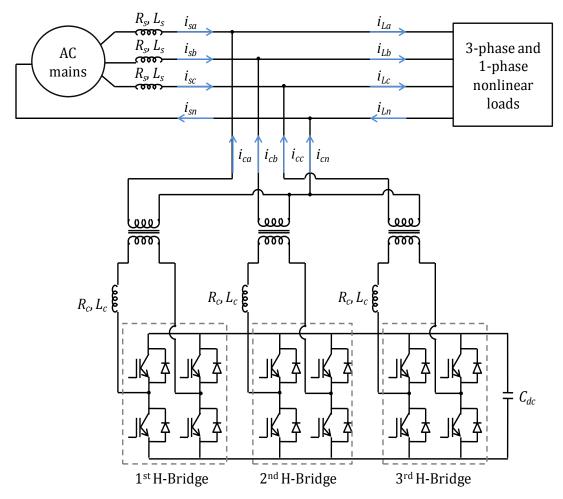

| 5.4  | System configuration of four-leg (4L) VSI based shunt APF                                     | 155 |

| 5.5  | Closed loop block diagram for DC-link voltage control in 4L topology                          | 155 |

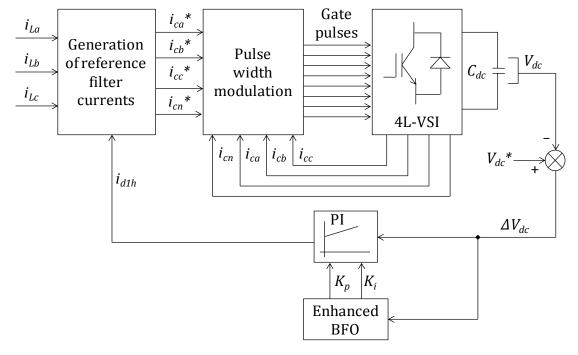

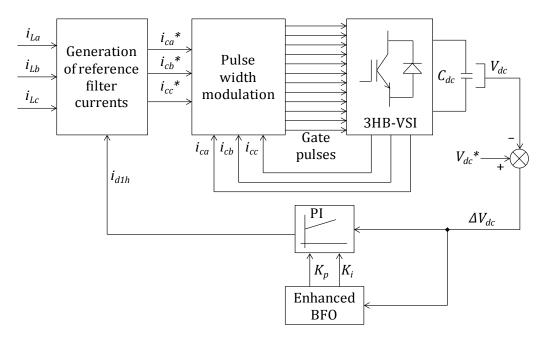

| 5.6  | System configuration of three H-bridges (3HB) VSI based shunt APF                             | 157 |

| 5.7  | Closed loop block diagram for DC-link voltage control in 3HB topology                         | 158 |

| 5.8  | System configuration of three-level H-bridges (3L-HB) VSI based shunt                         | 159 |

|      | APF                                                                                           |     |

|      |                                                                                               |     |

| 5.9  | Closed loop block diagram for DC-link voltage control in 5L-HB topology                | 100 |

|------|----------------------------------------------------------------------------------------|-----|

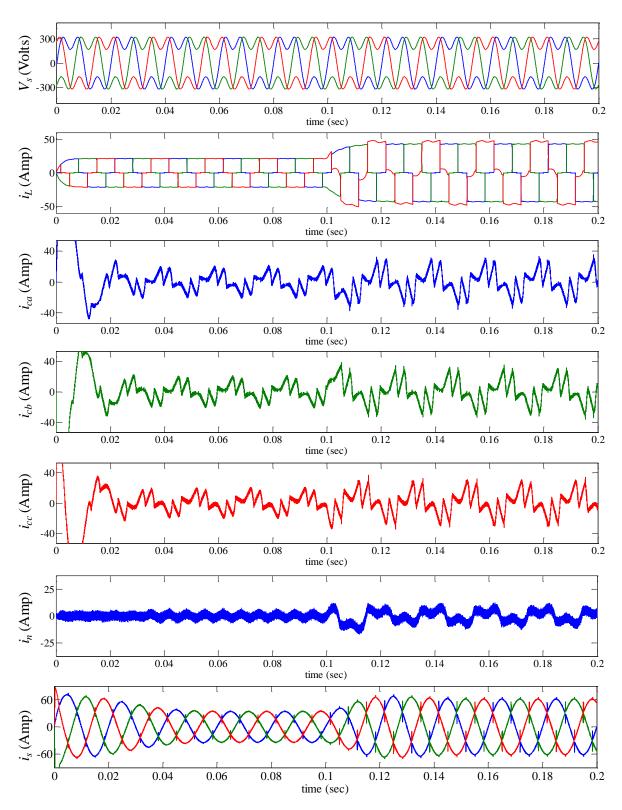

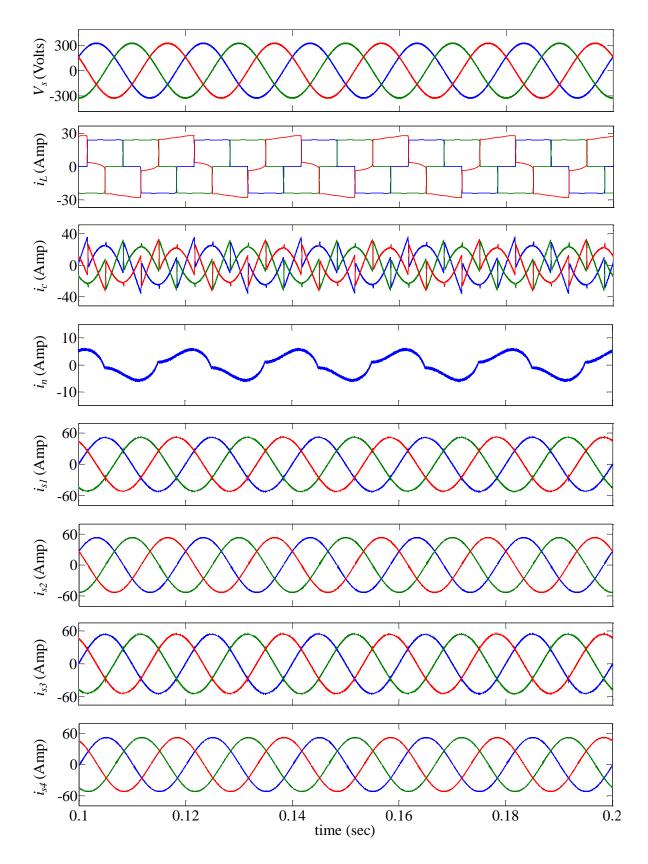

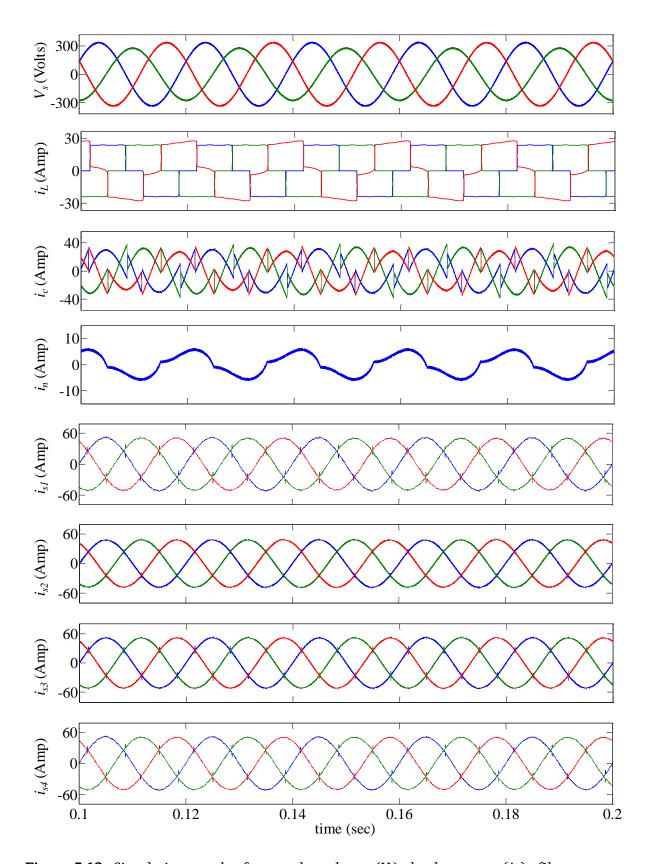

| 5.10 | Simulation results for supply voltage $(V_s)$ , load current $(i_L)$ , filter current  | 162 |

|      | $(i_c)$ , neutral current $(i_n)$ and source currents after compensation with          |     |

|      | APF employing 2C-VSI $(i_{s1})$ , 4L-VSI $(i_{s2})$ , 3HB-VSI $(i_{s3})$ and 3L-HB VSI |     |

|      | $(i_{s4})$ under ideal supply                                                          |     |

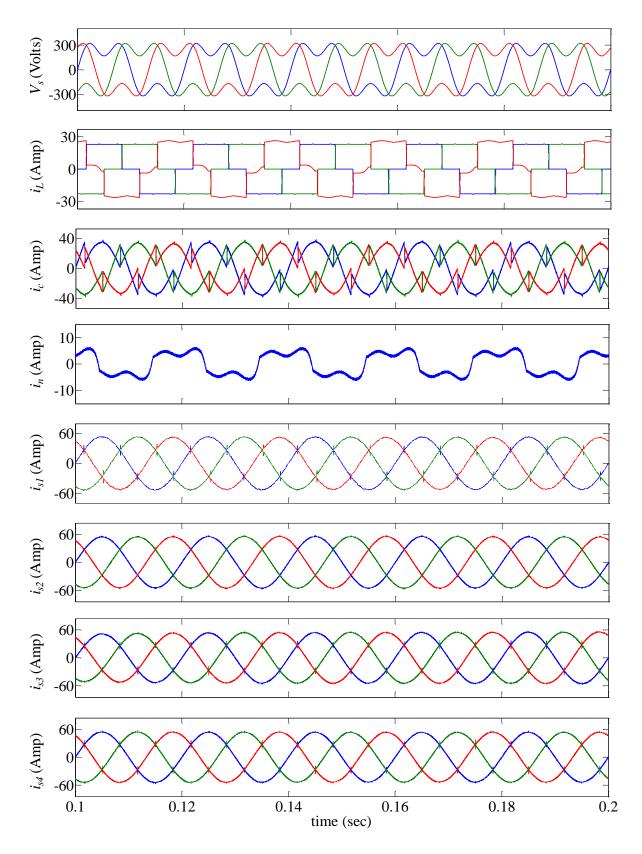

| 5.11 | Simulation results for supply voltage $(V_s)$ , load current $(i_L)$ , filter current  | 163 |

|      | $(i_c)$ , neutral current $(i_n)$ and source currents after compensation with          |     |

|      | APF employing 2C-VSI $(i_{s1})$ , 4L-VSI $(i_{s2})$ , 3HB-VSI $(i_{s3})$ and 3L-HB VSI |     |

|      | $(i_{s4})$ under distorted supply                                                      |     |

| 5.12 | Simulation results for supply voltage $(V_s)$ , load current $(i_L)$ , filter current  | 164 |

|      | $(i_c)$ , neutral current $(i_n)$ and source currents after compensation with          |     |

|      | APF employing 2C-VSI $(i_{s1})$ , 4L-VSI $(i_{s2})$ , 3HB-VSI $(i_{s3})$ and 3L-HB VSI |     |

|      | $(i_{s4})$ under unbalanced supply                                                     |     |

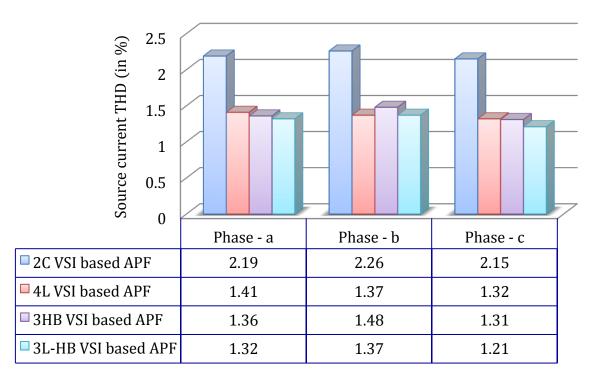

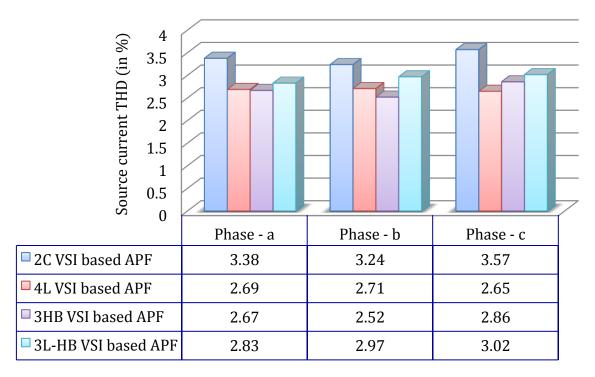

| 5.13 | Chart diagram showing source current THDs (in %) obtained with                         | 165 |

|      | simulation of APF employing 2C, 4L, 3HB and 3L-HB VSI topologies                       |     |

|      | under ideal supply condition                                                           |     |

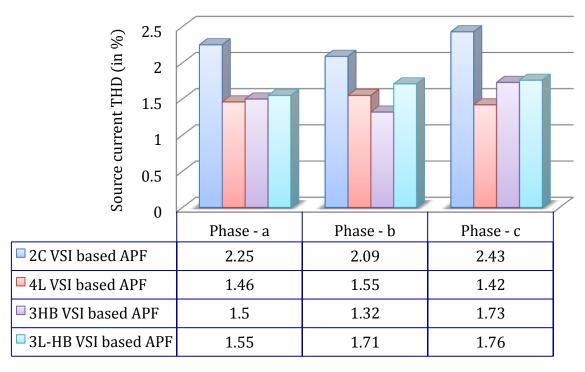

| 5.14 | Chart diagram showing source current THDs (in %) obtained with                         | 165 |

|      | simulation of APF employing 2C, 4L, 3HB and 3L-HB VSI topologies                       |     |

|      | under distorted supply condition                                                       |     |

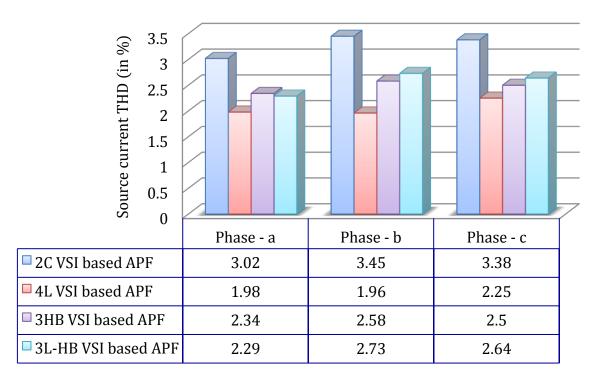

| 5.15 | Chart diagram showing source current THDs (in %) obtained with                         | 166 |

|      | simulation of APF employing 2C, 4L, 3HB and 3L-HB VSI topologies                       |     |

|      | under unbalanced supply condition                                                      |     |

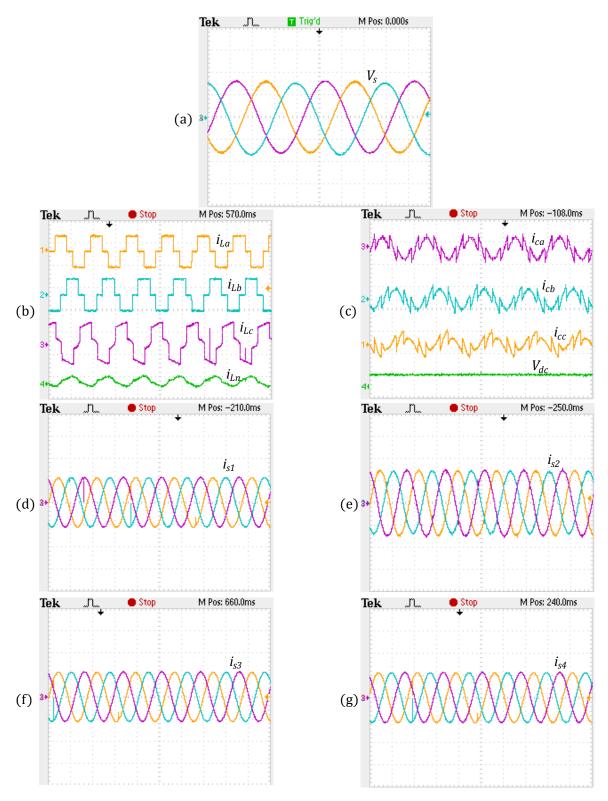

| 5.16 | RT-Lab results under ideal supply for (a) Supply voltage, (b) Load current             | 167 |

|      | in four wires, (c) Compensation current in three phases and DC-link                    |     |

|      | voltage, (d)-(g) Source currents after compensation with 2C APF ( $i_{s1}$ ), 4L       |     |

|      | APF $(i_{s2})$ , 3HB APF $(i_{s3})$ and 3L-HB APF $(i_{s4})$ respectively              |     |

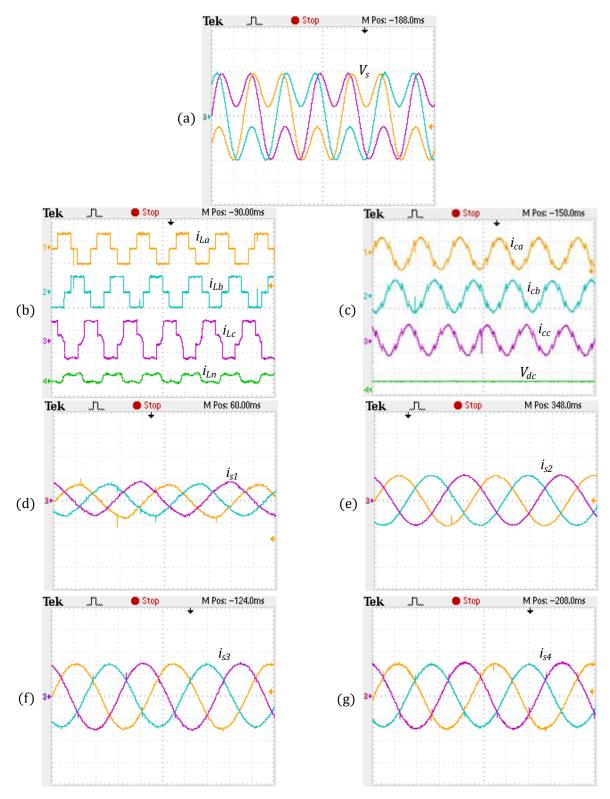

| 5.17 | RT-Lab results under distorted supply for (a) Supply voltage, (b) Load                 | 168 |

|      | current in four wires, (c) Compensation current in three phases and DC-                |     |

link voltage, (d)-(g) Source currents after compensation with 2C APF

- $(i_{s1})$ , 4L APF  $(i_{s2})$ , 3HB APF  $(i_{s3})$  and 3L-HB APF  $(i_{s4})$  respectively

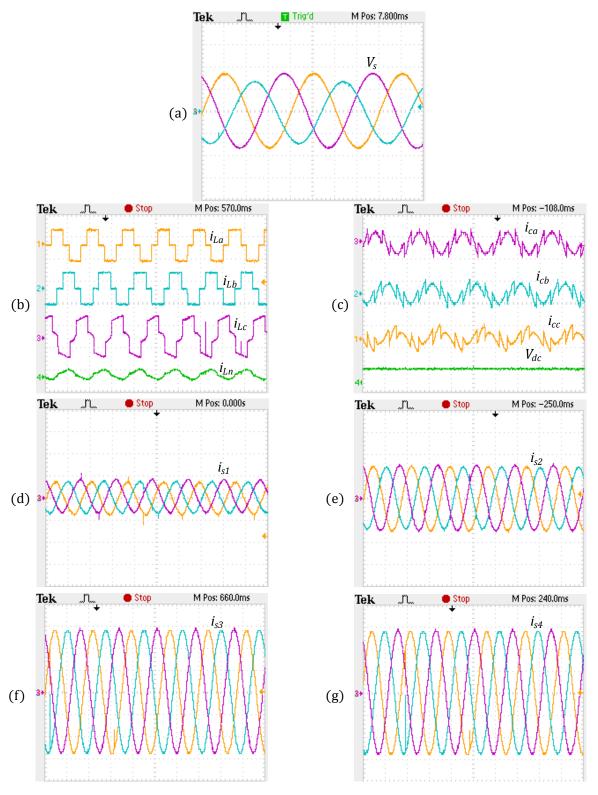

- 5.18 RT-Lab results under unbalanced supply for (a) Supply voltage, (b) Load current in four wires, (c) Compensation current in three phases and DC-link voltage, (d)-(g) Source currents after compensation with 2C APF  $(i_{s1})$ , 4L APF  $(i_{s2})$ , 3HB APF  $(i_{s3})$  and 3L-HB APF  $(i_{s4})$  respectively

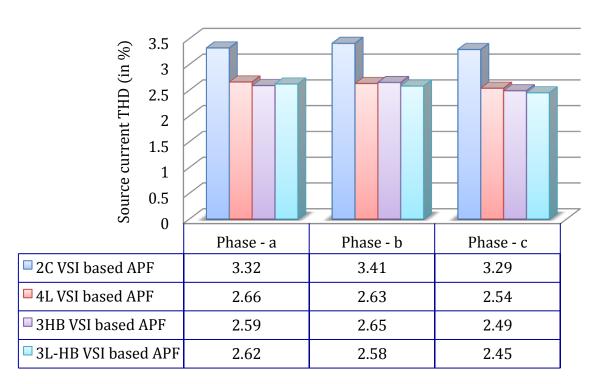

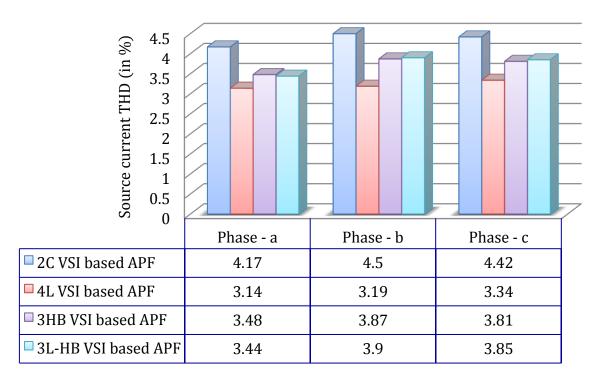

- 5.19 Chart diagram showing source current THDs (in %) obtained in RT-Lab

after compensation with APFs employing 2C, 4L, 3HB and 3L-HB VSI

topologies under ideal supply condition

- 5.20 Chart diagram showing source current THDs (in %) obtained in RT-Lab

after compensation with APFs employing 2C, 4L, 3HB and 3L-HB VSI

topologies under distorted supply condition

- 5.21 Chart diagram showing source current THDs (in %) obtained in RT-Lab 171 after compensation with APFs employing 2C, 4L, 3HB and 3L-HB VSI topologies under unbalanced supply condition

# List of Tables

| 1.1 | IEEE 519-2014 Standard for harmonic current limits for general                                    | 6   |

|-----|---------------------------------------------------------------------------------------------------|-----|

|     | distribution systems (120–69,000 V)                                                               |     |

| 2.1 | Values of system parameters used in simulation                                                    | 46  |

| 2.2 | Overshoots and settling times for different values of gains $K_p$ and $K_i$ with                  | 47  |

|     | p-q scheme                                                                                        |     |

| 2.3 | Overshoots and settling times for different values of gains $K_p$ and $K_i$ with                  | 47  |

|     | modified $p-q$ scheme                                                                             |     |

| 2.4 | Overshoots and settling times for different values of gains $K_p$ and $K_i$ with                  | 47  |

|     | $i_d - i_q$ scheme                                                                                |     |

| 3.1 | Values of system parameters used in simulation                                                    | 90  |

| 3.2 | Values of parameters used in Optimization techniques                                              | 90  |

| 3.3 | Comparison of maximum overshoots undershoots and settling times of the                            | 96  |

|     | four controllers from $V_{dc}$ transient response under ideal supply                              |     |

| 3.4 | Comparison of maximum overshoots undershoots and settling times of the                            | 96  |

|     | four controllers from $V_{dc}$ transient response under distorted supply                          |     |

| 3.5 | Comparison of maximum overshoots undershoots and settling times of the                            | 96  |

|     | four controllers from $V_{dc}$ transient response under unbalanced supply                         |     |

| 4.1 | Comparison of component requirements for MLI topologies                                           | 118 |

| 4.2 | THDs of output phase voltages for cascaded MLIs employing phase-shifted,                          | 134 |

|     | IPD, POD and APOD PWM techniques                                                                  |     |

| 5.1 | Conditions for charging and discharging of capacitors $\mathcal{C}_{dc1}$ and $\mathcal{C}_{dc2}$ | 152 |

| 5.2 | Comparison between 2C, 4L, 3HB and 3L-HB VSI topologies of shunt APF                              | 172 |

## Acronyms

ABC Artificial bee colony

AC Alternating current

ACO Ant colony optimization

ADALINE Adaptive linear neuron

ANN Artificial neural network

APF Active power filter

APOD Alternative phase opposite disposition

BFO Bacterial foraging optimization

CSI Current-source inverter

CSNL Current source nonlinear load

DC Direct current

DSO Digital storage oscilloscope

DVR Dynamic voltage restorer

EMI Electro-magnetic interference

FFT Fast Fourier transform

GA Genetic algorithm

GTO Gate turn-off thyristor

IEC International Electrotechnical Commission

IEEE Institute of Electrical and Electronics Engineers

IGBT Insulated-gate bipolar transistor

IPD In-phase disposition

ISE Integral square error

LPF Low-pass filter

MLI Multilevel inverter

PCC Point of common coupling

PHC Perfect harmonic cancellation

POD Phase opposite disposition

PI Proportional-integral

PLL Phase-locked loop

PSO Particle swarm optimization

PWM Pulse-width modulation

RDFT Recursive discrete Fourier transform

RMS Root mean square

RT-Lab Real-time Laboratory

SHE Selective harmonic elimination

SVM Space vector modulation

TDD Total demand distortion

THD Total harmonic distortion

UPQC Unified power quality conditioner

VSI Voltage-source inverter

VSNL Voltage source nonlinear load

2C Split capacitor VSI

3HB Three H-bridges VSI

3L-HB Three-level H-bridge VSI

4L Four leg VSI

## **Notations**

#### Notations for parameters used in APF

f Operating frequency of supply

*R* Resistance

L Inductance

*C* Capacitance

$R_s$ ,  $L_s$  Source resistance and inductance

$R_c$ ,  $L_c$  Filter resistance and inductance

$R_F$ ,  $C_F$  RC high-pass filter on AC-side of APF

$R_L, L_L$  Load resistance and inductance

$i_s$  Source current

$i_L$  Load current

$i_c$  Compensation filter current

$i_1, i_n$  Fundamental and  $n^{\text{th}}$  order harmonic components of current

$V_1, V_n$  Fundamental and  $n^{\text{th}}$  order harmonic components of voltage

$K_p$ ,  $K_i$  Proportional and Integral gains of PI controller

$C_{dc}$  DC-link capacitance

$e_{dc}$  Actual average energy stored on DC bus

$e_{dc}^*$  Nominal energy stored on DC bus

$\Delta e_{dc}$  Energy loss of DC bus

$V_{dc}$  Actual DC-link voltage

$V_{dc}^*$  Reference DC-link voltage

$V_{dca}$  Average value of actual DC-link voltage

$\Delta V_{dc}$  Deviation in DC-link voltage from its reference value

$V_c$ ,  $I_c$  AC-side voltage and current of VSI

$I_{c0}$ ,  $V_{dc0}$  Steady-state operating points of  $I_c$  and  $V_{dc}$

$I_{c,rated}$  Rated filter current

$V_{dc,\max\_rip(p-p)}$  Peak-to-peak ripple in DC-link voltage

J Objective/cost/fitness function

HB Hysteresis bandwidth

$\omega$  Rotational speed of synchronously rotating d-q axes

$v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  Supply voltage in three phases

$v_{\alpha}, v_{\beta}, v_{0}$  Supply voltage in  $\alpha - \beta - 0$  coordinates

$v_d$ ,  $v_q$  Supply voltage in d-q coordinates

$\overline{v_d}, \overline{v_q}$  Fundamental components of voltages  $v_d$  and  $v_q$

$i_{La}$ ,  $i_{Lb}$ ,  $i_{Lc}$  Load currents in three phases

$i_n$  Neutral current in three-phase four-wire systems

$i_{\alpha}$ ,  $i_{\beta}$ ,  $i_{0}$  Load current in  $\alpha - \beta - 0$  coordinates

$i_{Ld}$ ,  $i_{Lq}$ ,  $i_0$  Load current in d-q-0 coordinates

$i_{ca}, i_{cb}, i_{cc}, i_{cn}$  Actual compensation filter currents in four wires

$i_{ca}^*, i_{cb}^*, i_{cc}^*, i_{cn}^*$  Reference compensation filter currents in four wires

$i_{c\alpha}^*, i_{c\beta}^*, i_{c0}^*$  Reference compensation filter currents in  $\alpha - \beta - 0$  coordinates

$i_{cd}^*, i_{cq}^*, i_{c0}^*$  Reference compensation filter currents in d-q-0 coordinates

$p, q, p_0$  Instantaneous active, reactive and zero-sequence powers

$\overline{p_0}, \widetilde{p_0}$  Average/mean/DC and oscillating/AC components of power  $p_0$

$\bar{p}, \tilde{p}$  Average/mean/DC and oscillating/AC components of power p

$\overline{q}$ ,  $\widetilde{q}$  Average/mean/DC and oscillating/AC components of power q

$\overline{P_{loss}}$  Average value of loss occurring inside VSI

$i_d$ ,  $i_q$  Instantaneous d-axis and q-axis current components

$i_{d1h}$  Active current required to maintain a constant DC-link voltage

$i_{Ld1h}$ ,  $i_{Lq1h}$  Fundamental frequency components of  $i_{Ld}$  and  $i_{Lq}$

$i_{Ldnh}$ ,  $i_{Lqnh}$  Oscillating components of  $i_{Ld}$  and  $i_{Lq}$

m Level of MLI

$\theta_1, \theta_2, \dots \theta_s$  Switching angles for cascaded MLI with s number of DC sources

$v_{ref}$  Reference signal for multicarrier PWM

$v_{cr1}, v_{cr2}, v_{cr3}, v_{cr4}$  Triangular carrier signals for multicarrier PWM

$f_c$ ,  $f_m$  Frequencies of carrier and modulating signals

$A_c$ ,  $A_m$  Amplitude of carrier and modulating signals

$m_f, m_a$  Frequency and amplitude modulation indices

$f_{dev}$  Device switching frequency

$f_{inv}$  Inverter switching frequency

#### Notations for parameters used in optimization techniques

*x* Position of a particle in the search space

*v* Velocity of the particle

i, j, k, l, m Pointers for particle index, chemotaxis, reproduction, elimination

dispersal event and swimming

$x_{Lbest}^{i}$  Position corresponding to best fitness attained by  $i^{th}$  particle

$x_{Gbest}^{i}$  Position corresponding to global best fitness

$r_1, r_2$  Random numbers in the interval [-1,1]

$c_1, c_2$  Cognitive and social acceleration constants

*w* Inertia constant

$W_{max}$ ,  $W_{min}$  Maximum and minimum values of W

*G*, *g* Maximum and current values of number of generation

$\theta^i(j,k,l)$   $i^{ ext{th}}$  bacterium at  $j^{ ext{th}}$  chemotactic,  $k^{ ext{th}}$  reproductive and  $l^{ ext{th}}$

elimination-dispersal step

C(i) Step size

$\Delta(i)$  Vector in arbitrary direction whose elements lie in [-1,1]

$J_{cc}$  Cost function accounting for cell-to-cell communication

$d_{att}$ ,  $w_{att}$  Quantity and diffusion rate of attractant signal

$h_{rep}$ ,  $w_{rep}$  Quantity and diffusion rate of repellent effect magnitude

P Number of parameters to be optimized

S Population size

$N_s$  Swimming length

$N_c$  Number of chemotactic steps

$N_{re}$  Number of reproduction steps

$N_{ed}$  Number of elimination-dispersal steps

$P_{ed}$  Probability at which elimination-dispersal occurs

$J_{health}^{i}$  Fitness of  $i^{ ext{th}}$  bacterium

## **Abstract**

Following the advent of solid-state power electronics technology, extensive usage of nonlinear loads has lead to severe disturbances like harmonics, unbalanced currents, excessive neutral current and reactive power burden in three-phase power systems. Harmonics lower down the efficiency and power factor, increase losses, and result in electromagnetic interference with neighbouring communication lines and other harmful consequences. Over the years, active power filter (APF) has been proven to be a brilliant solution among researchers and application engineers dealing with power quality issues.

Selection of proper reference compensation current extraction scheme plays the most crucial role in APF performance. This thesis describes three time-domain schemes viz. Instantaneous active and reactive power (p-q), modified p-q, and Instantaneous active and reactive current component  $(i_d-i_q)$  schemes. The objective is to bring down the source current THD below 5%, to satisfy the IEEE-519 Standard recommendations on harmonic limits. Comparative evaluation shows that,  $i_d-i_q$  is the best APF control scheme irrespective of supply and load conditions. Results are validated with simulations, followed by real-time analysis in RT-Lab.

In view of the fact that APFs are generally comprised of voltage source inverter (VSI) based on PWM, undesirable power loss takes place inside it due to the inductors and switching devices. This is effectively minimized with inverter DC-link voltage regulation using PI controller. The controller gains are determined using optimization technique, as the conventional linearized tuning of PI controller yield inadequate results for a range of operating conditions due to the complex, nonlinear and time-varying nature of power system networks. Developed by hybridization of Particle swarm optimization (PSO) and Bacterial foraging optimization (BFO), an Enhanced BFO technique is proposed here so as to overcome the drawbacks of both PSO and BFO, and accelerate the convergence of optimization problem. Extensive simulation studies and RT-Lab real-time investigations are performed for comparative assessment of proposed implementation of PSO, BFO and

Enhanced BFO on APF. This validates that, the APF employing Enhanced BFO offers superior harmonic compensation compared to other alternatives, by lowering down the source current THD to drastically small values.

Another indispensable aspect of APF is its topology, which plays an essential role in meeting harmonic current requirement of nonlinear loads. APFs are generally developed with current-source or voltage-source inverters. The latter is more convenient as it is lighter, cheaper, and expandable to multilevel and multistep versions for improved performance at high power ratings with lower switching frequencies. There can be different topologies of VSI depending on the type of supply system. With each topology, constraints related to DC-link voltage regulation change. For effective compensation, irrespective of the number and rating of DC-link capacitors used in any particular topology, voltages across them must be maintained constant with optimal regulation of DC-link voltage. Various topologies for three-phase three-wire systems (conventional two-level and multilevel VSIs) and four-wire systems (split-capacitor (2C), four-leg (4L), three H-bridges (3HB) and three-level H-bridge (3L-HB) VSIs) are analyzed and compared based on component requirements, effectiveness in harmonic compensation, cost and area of application.

**Keywords:** Current harmonics compensation; shunt active power filter; voltage source inverter topologies; multilevel inverter; optimization technique; RT-Lab

# Chapter 1

### Introduction

#### 1.1. Overview

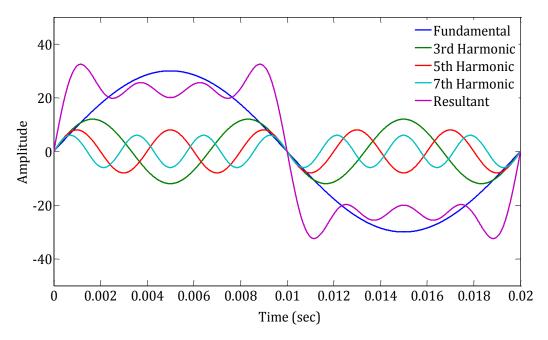

Harmonics can be defined as "a sinusoidal component of a periodic wave or quantity having a frequency that is an integral multiple of the fundamental supply frequency" [1]. Therefore, harmonics can be thought of as voltages and/or currents present in an electrical system at some multiple of the fundamental frequency, which when added together result in a distorted waveform. For example, Figure 1.1 illustrates how the resultant distorted waveform is produced when the 3<sup>rd</sup>, 5<sup>th</sup> and 7<sup>th</sup> order harmonic components are added to the fundamental component of the signal.

Total harmonic distortion (THD) is the measure of effective value of harmonic content in a distorted current or voltage signal. It is defined as the ratio of the RMS of harmonic content to the RMS value of fundamental quantity.

Mathematically, THD in a current signal can be given by (1.1).

$$THD_{i} = \frac{\sqrt{\sum_{n=2}^{\infty} i_{n}^{2}}}{i_{1}}$$

(1.1)

Where,  $i_1$  and  $i_n$  are the RMS values of fundamental and n<sup>th</sup> order harmonic components of current respectively.

Similarly, equation (1.2) gives away the THD in a voltage signal.

$$THD_V = \frac{\sqrt{\sum_{n=2}^{\infty} V_n^2}}{V_1} \tag{1.2}$$

Where,  $V_1$  and  $V_n$  indicate the RMS values of fundamental and  $n^{\text{th}}$  order harmonic components of voltage respectively.

Figure 1.1: Harmonics

#### 1.1.1. Causes behind production of harmonics

Harmonic production is resulted due to the usage of large number of nonlinear loads. Nonlinear loads are the loads which do not draw a sinusoidal current even when they are supplied with a sinusoidal voltage. There are two types of harmonics sources, current source nonlinear loads (CSNLs) producing current harmonics and voltage source nonlinear loads (VSNLs) producing voltage harmonics [2], [3].

However, the work presented in this thesis is confined to mitigation of current harmonics. With the advent of low-cost solid-state electronics, modern forms of power conversions such as static rectifiers and drives have mostly substituted the older methods of conversion. As a consequence, the solid-state converter unit and/or its loads now-adays represent a substantial portion of the total power system requirements. Current harmonics result from the switching operations of power electronic devices. The loads which are primarily responsible for production of harmonic currents can be as follows:

- *a) Commercial loads:* Single-phase power supplies, fluorescent lighting, adjustable speed drives for HVAC, elevators etc.

- *b) Industrial loads:* Three-phase power converters (DC and AC drives), arcing devices, saturable devices etc.

- c) Domestic loads: Computer systems and other electronic loads

#### 1.1.2. Consequences of harmonics

Current harmonics is one of the major culprits behind the rigorous deterioration of power quality as it leads to various harmful consequences [4], [5] such as:

- a) Overheating of transformers, motors etc.

- b) Overheated neutral conductors

- c) Poor efficiency and power factor

- d) Increased losses in power system

- e) Electro-magnetic interference with nearby communication lines

- f) False tripping of protective relays

- g) Failure or misoperation of microprocessors

- h) Vibration in rotating machines

- i) Voltage quality degradation

- j) Malfunctioning of medical facilities etc.

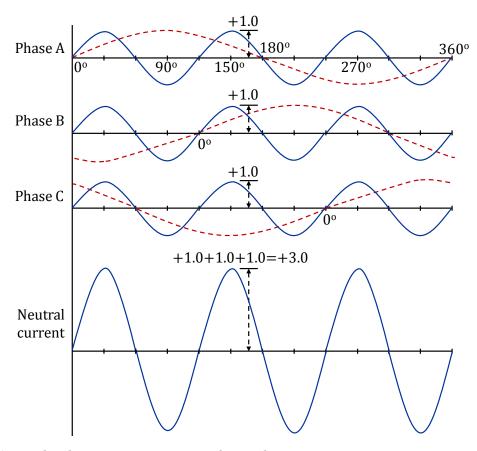

In the past few years, the proliferation of nonlinear loads in power system has been growing at an unprecedented pace, following the pervasive use of solid-state control of AC power. Typical nonlinear loads such as arc furnaces, fluorescent lights, power electronic converters, microprocessors, motor drives, electronic loads, saturated transformers, switching mode power supplies, various domestic appliances, etc. draw significant amount of harmonic current from the utility bringing down the efficiency and power factor, and increasing the risk of electromagnetic interference with neighbouring communication lines. The triplen order harmonic currents (3<sup>rd</sup>, 6<sup>th</sup>, 9<sup>th</sup>, etc.) add on to the

neutral conductor being in-phase with each other, which may result in overloaded power feeders, overloaded transformers, voltage distortion and common mode noise [6].

This thesis discusses the basics of passive power filter. This is followed by a description on the role of shunt active power filter (APF) in compensation of the undesirable consequences caused due to nonlinear loads, the priority being mitigation of current harmonics in power system. Three different APF control schemes namely, Instantaneous active and reactive power (p-q), modified p-q, and Instantaneous active and reactive current component  $(i_d-i_q)$  schemes for the extraction of reference compensation currents are analysed rigorously and compared to determine the best one among them. Here the APF is considered to be comprised of a Pulse-width modulation (PWM) based voltage source inverter (VSI); therefore it involves huge power loss inside the inverter itself. To overcome this, a DC-link voltage regulator is used to make the DC-link voltage constant with the help of a PI controller. However, the conventional method of PI controller tuning does not yield satisfactory results for wide range of operating conditions. So, goal of the dissertation is to find out optimized values of PI controller gains with the help of stochastic optimization techniques like Particle swarm optimization (PSO) and Bacterial foraging optimization (BFO). This leads to the lowering down of overall THD of source current. An Enhancement to the BFO algorithm is also proposed here, developed by the hybridization of PSO and BFO algorithms. It is validated to give superior performance even under highly distorted and unbalanced supplies, and sudden load change conditions. Various shunt APF configurations for three-phase threewire distribution systems are modelled. It also showcases the use of multilevel inverters (MLIs) for active power line conditioning. Furthermore, various three-phase four-wire APF topologies are discussed, the focus being split-capacitor (2C), four-leg (4L), three Hbridges (3HB), and three-level H-bridge (3L-HB) topologies. Performances of all the above mentioned APF topologies are evaluated in terms of current harmonic compensation. The evaluations are carried out by performing simulation studies and realtime performance analysis in RT-Lab. Finally, the general conclusions, major contributions and scope for future research are discussed.

Section 1.2 gives an overall idea about the efforts done so far in order to sort out these power quality issues as literature survey. The tools used for carrying out the analyses presented in this thesis are discussed in Section 1.3. Section 1.4 summarizes the motivation behind the thesis, followed by the objectives in Section 1.5. The next section illustrates the organization of the thesis in various chapters.

#### 1.2. Research Background

In order to solve the problem of harmonic pollution effectively, many harmonic limitation standards such as IEEE 519-2014, IEC 1000-3-2 and IEC 1000-3-4 have been established [7]–[10]. However, IEEE Recommended Practice and Requirements for Harmonic Control in Electric Power Systems (IEEE 519-2014 Standard) [7], [8] provides an excellent basis for limiting harmonics.

IEEE 519-2014 Standard for harmonic current limits for general distribution systems (120-69,000 V) is presented in Table 1.1. A lot of research has been done to find out a tool that would be able to compensate the disturbances caused due to nonlinear loads so that the IEEE-519 Standards can be met even under sudden load changes, irrespective of the supply voltage condition. The supply voltage can be either ideal or non-ideal (distorted and unbalanced supply conditions). Distorted supply is resulted due to static frequency converters, cycloconverters, arcing devices, switching power supplies and other power electronic devices, where a steady state deviation of supply voltage from an ideal sine wave of fundamental operating frequency is observed. Presence of unequal single-phase loads, blown fuses in one of the phases of a three-phase capacitor bank or single phasing conditions result in unbalanced supply condition as the voltage becomes asymmetrically balanced between the three phases of supply.

The detrimental consequences of current harmonics, excessive neutral current and unbalanced source current in the power systems can be avoided by the use of a device known as Active power filter. But, prior to the development of semiconductor technology, Passive power filters were being extensively used for this purpose.

**Table 1.1:** IEEE 519-2014 Standard for harmonic current limits for general distribution systems (120–69,000 V)

| Maximum              |                                           |                 |                 |                 |        |      |

|----------------------|-------------------------------------------|-----------------|-----------------|-----------------|--------|------|

| Harmonic Current     | Individual Harmonic Order (Odd Harmonics) |                 |                 |                 |        |      |

| Distortion in        |                                           |                 |                 |                 |        |      |

| Percent of $I_L$     |                                           |                 |                 |                 |        |      |

| $\frac{I_{sc}}{I_L}$ | <11                                       | $11 \le n < 17$ | $17 \le n < 23$ | $23 \le n < 35$ | 35 ≤ n | TDD  |

| < 20*                | 4.0                                       | 2.0             | 1.5             | 0.6             | 0.3    | 5.0  |

| 20–50                | 7.0                                       | 3.5             | 2.5             | 1.0             | 0.5    | 8.0  |

| 50–100               | 10.0                                      | 4.5             | 4.0             | 1.5             | 0.7    | 12.0 |

| 100–1000             | 12.0                                      | 5.5             | 5.0             | 2.0             | 1.0    | 15.0 |

| >1000                | 15.0                                      | 7.0             | 6.0             | 2.5             | 1.4    | 20.0 |

Even harmonics are limited to 25% of the odd harmonic limits above.

Current distortions that result in a DC offset, e.g. half-wave converters, are not allowed.

\*All power generation equipments are limited to these values of current distortion, regardless of actual  $\left(\frac{l_{sc}}{l_{I}}\right)$ .

Where,

$I_L$  = Maximum demand load current (fundamental frequency component) at the point of common coupling (PCC)

$I_{sc}$  = Maximum short-circuit current at PCC

TDD = Total demand distortion; harmonic current distortion in % of maximum demand load current (15 or 30 min demand)

#### 1.2.1. Passive power filters

Passive filters have been most commonly used to limit the flow of harmonic currents in distribution systems. It comprises of basic linear elements such as resistors, capacitors, inductors and transformers. It provides a low-impedance path to ground for the harmonic frequencies. These are usually custom designed for the application; however they may be tuned to a frequency between two prevalent harmonics so as to help attenuate both. The resistance, inductance, and capacitance values are determined from the filter type and from the following parameters [11]–[14]:

- a) Reactive power at nominal voltage

- b) Tuning frequencies

- c) Quality factor, which is a measure of the sharpness of tuning frequency

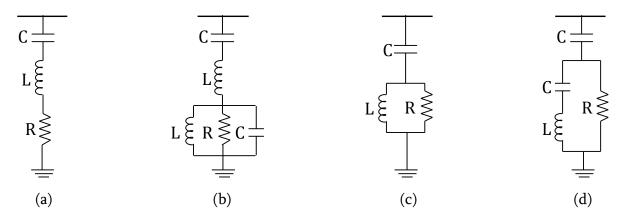

**Figure 1.2:** Types of three-phase passive harmonic filters, (a) Single-tuned, (b) Double-tuned, (c) High-pass, (d) C-type High-pass

Four types of filters that can be modelled with the three-phase harmonic filter block are shown in Figure 1.2. In order to achieve an acceptable distortion, several banks of filters of different types are usually connected in parallel. The most commonly used filter types are:

*a)* Band-pass filters. These are used to filter lowest order harmonics such as 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, 13<sup>th</sup>, etc. Band-pass filters can be tuned at a single frequency (single-tuned filter) or at two frequencies (double-tuned filter).

*b) High-pass filters*: These are used to filter higher order harmonics and cover a wide range of frequencies. A special type of high-pass filter called C-type high-pass filter is used to provide reactive power and avoid parallel resonances. It also allows filtering low order harmonics (such as 3<sup>rd</sup>), keeping zero losses at fundamental frequency.

Conventionally, passive filter is used to solve the issues of harmonic pollution in industrial power system due to its low cost. However, it suffers from following drawbacks [15]–[17]:

- a) Sensitive to the variation of power system impedance

- b) Sensitive to frequency variation of the utility

- c) Risk of series/parallel resonance with power system impedance

- d) Poor flexibility due to selective harmonic compensation

- e) Ineffective when the harmonic content varies randomly

Among those listed above, the series/parallel resonance is the most serious disadvantage. It may result in over-current/over-voltage on the inductor and capacitor causing damage to the passive power filter. Since the system impedance has a significant effect on the performance of passive power filter, it is very hard to obtain an excellent filter performance in practical applications. Moreover, the harmonic currents produced by neighbouring nonlinear loads may flow into the passive power filter and result in overloading of the filter.

#### 1.2.2. Active power filters

After the advent of semiconductor switching devices in 1970s, harmonic suppression facilities based on power electronic technique were developed [18]. These active harmonic suppression facilities known as Active power filters (APFs) can suppress different order harmonic components of nonlinear loads simultaneously [16], [19]–[30]. APF confines the load current harmonics at the load terminals, hindering its penetration into the power system. The advantage of active filtering is that it automatically adapts to

changes in the network and load fluctuations [31]. Few most important advantages of APF are:

- a) Intelligent filter

- b) Can be used globally or locally

- c) Extremely efficient even when the harmonic content varies randomly

- d) More than one devices can be installed on the same supply

This device uses Insulated gate bipolar transistors (IGBTs) or Gate turn-off thyristors (GTOs), and Pulse-width modulation (PWM) control techniques [32]. The PWM converter comprising of IGBTs/GTOs can have many configurations, but standard inverter topology is mostly preferred [26], [31], [33], [34].

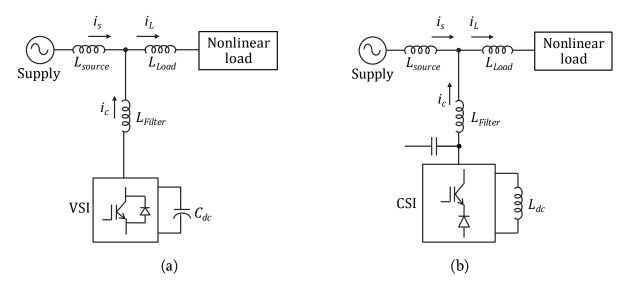

Figure 1.3: (a) APF employing VSI, (b) APF employing CSI

The PWM inverter is either a Voltage source inverter (VSI) or a Current source inverter (CSI) as depicted in Figure 1.3. Here,  $L_{source}$ ,  $L_{Load}$  and  $L_{Filter}$  represent source, load and filter impedances respectively. Likewise, source current, load current and compensation filter current are denoted as  $i_s$ ,  $i_L$  and  $i_c$ . The energy storage element on DC side of inverter is capacitor ( $C_{dc}$ ) in case of VSI and inductor ( $L_{dc}$ ) in case of CSI. This is indicative of a drawback in the latter, as the inductor is less efficient in energy storage compared to capacitor. Further, on-state losses are more in CSI than VSI. These losses are

now-a-days reduced using a diode in series with IGBT for reverse voltage blocking, as shown in Figure 1.3 (b). VSI is the most preferred alternative in industrial applications as well as APFs; as it is less costly, lighter and more efficient compared to CSI. The capacity of power converter employed as APF must be larger than the product of harmonic components and fundamental component of load current and the utility voltage [35].

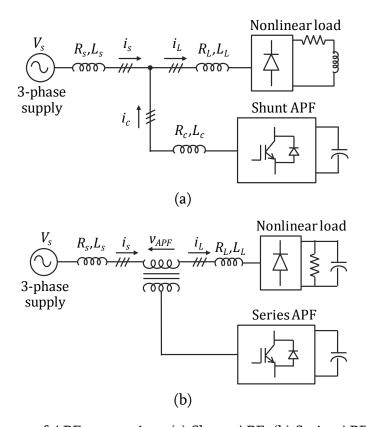

According to the power circuit configurations and connections, APFs can be divided into shunt APFs, series APFs and other filter combinations [2], [29], [36]. The shunt APF is connected in parallel to the load and generates compensation current which opposes the load harmonic current from being injected into the power feeder. The shunt APF is devised to inject current harmonics of equal magnitude but in phase opposition with the load current harmonics at the point of common coupling (PCC) between source and load as shown in Figure 1.4 (a), thereby cancelling out each other. Similarly, series APF compensates for harmonic voltages generated by nonlinear loads such as a diode rectifier with smoothing DC capacitor [37]. Figure 1.4 (b) shows a voltage harmonic producing load and the connection of series APF for the required voltage harmonic compensation.

Figure 1.4: Basic types of APF connections (a) Shunt APF, (b) Series APF

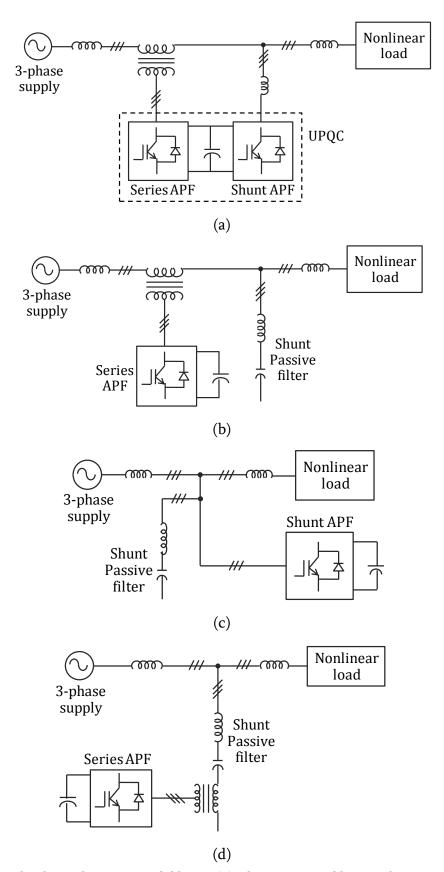

**Figure 1.5:** Hybrid combinations of filters, (a) Shunt active filter and series active filter, (b) Series active filter and shunt passive filter, (c) Shunt active filter and shunt passive filter, (d) Active filter in series with shunt passive filter

In some applications, the combination of several types of filters can achieve greater benefits [27]–[30]. The hybrid filter consists of a single or multiple numbers of APFs, combined with passive power filters. The major hybrid combinations include shunt active filter and series active filter, series active filter and shunt passive filter, shunt active filter and shunt passive filter, and active filter in series with shunt passive power filter as shown in Figure 1.5 [2], [36].

APFs can also be classified based on the type of compensation such as reactive power compensation, harmonic compensation, balancing of three-phase systems and multiple compensations [29]. However, the conventional shunt APF belongs to multiple compensations type and can compensate for harmonic current, reactive power and unbalanced loading simultaneously [19]–[26].

#### 1.2.3. Control schemes for APF

The control schemes for APF constitute a crucial part in the harmonic compensation, as any inaccuracy leads to inexact compensation. Various schemes such as Instantaneous active and reactive power (p-q), Instantaneous active and reactive current component  $(i_d-i_q)$ , Perfect harmonic cancellation (PHC), Generalized integral, Adaptive filter, Delay-less filtering based on Artificial Neural Network (ANN), Adaptive Linear Neuron (ADALINE), Wavelet Transform, Fast Fourier Transform (FFT) and Recursive Discrete Fourier Transform (RDFT) have been proposed since the development of APFs [38]–[43]. Time-domain methods are preferred here because of (a) fast response to changes in power system, (b) easy implementation with less memory requirements, and (c) less computational burden unlike frequency-domain methods, where the number of calculations increases with an increase in the highest order of harmonics to be eliminated, resulting in longer response time. The ANN and ADALINE methods are also associated with few shortcomings. Number of ADALINE required to tune is equal to the number of harmonics considered in load current, thus slowing down the convergence. Generation of the input vector  $X = [\cos \omega t, \sin \omega t... \cos n\omega t... \sin n\omega t]^T$  is difficult and involves a

tedious process. Moreover, the error being minimized by gradient-based method has likelihood of converging to local minima [43].

Following are the three APF control schemes those are discussed elaborately in Chapter 2 of this thesis. In addition, a comparison of their effectiveness to harmonic compensation is also studied from the simulation and RT-Lab results.

#### 1) Instantaneous active and reactive power (p - q) scheme

Out of all the APF control schemes, the p-q method introduced by Akagi *et al.* has gained well recognition as a viable solution to the problems created by nonlinear loads [44], [45]. It is most widely used as it offers a very precise reference compensation current template and allows obtaining a clear difference between instantaneous active and reactive powers. However, it is criticized as a disappointment under non-ideal supply conditions [46]–[48], because the multiplication of instantaneous load currents and voltages while calculating the instantaneous active and reactive powers leads to amplification of harmonic content, when the supply itself is distorted and/or unbalanced.

#### 2) Modified instantaneous active and reactive power (Modified p-q) scheme

To overcome the above drawback, Kale and Ozdemir proposed an enhancement to the conventional p-q scheme in the year 2005 [46]. This modified scheme uses voltage harmonic filtering in order to make the source voltage sinusoidal; before utilizing the same for calculation of instantaneous active and reactive powers. Though both p-q and modified p-q schemes have almost same effectiveness to harmonic compensation under ideal supply voltage condition, modified p-q scheme has been validated to possess superior harmonic compensation capability under distorted supply voltage conditions [46], [47]. However, its performance under unbalanced supply still needs improvement.

# 3) Instantaneous active and reactive current component $(i_d-i_q)$ scheme

It has been reported in literature that, the  $i_d - i_q$  scheme is more efficient than the p-q

scheme [48]. With the implementation of this scheme, harmonics can be mitigated under all kinds of supply voltages (ideal, distorted and unbalanced supplies).

# 1.2.4. Conventional PI controller for inverter DC-link voltage regulation

During steady state of operation, real power supplied by the source is equal to the real power demand of the loads plus a small power to compensate the losses occurring inside APF due to the presence of inductors and switching devices. Thus, the DC-link voltage can be maintained at a particular reference value. However, during load variation there is a real power difference between the two, which can be compensated by the charging/discharging of DC-link capacitor. If the DC-link capacitor voltage is recovered to attain the reference voltage, real power supplied by the source again becomes equal to that consumed by the load. APF uses a PI controller for minimizing the undesirable losses occurring inside the APF itself, by maintaining a constant DC-link voltage [49].

In the present work, parameters of conventional PI controller are designed using a linear model. The linear model of PWM converter along with DC-link voltage regulator is derived by applying small-signal perturbation technique [49], [50].

## 1.2.5. Implementation of optimization techniques

Though the APF is efficient enough for load compensation, optimal performance by the APF is always desirable. APFs with conventional PI controller yield inadequate results under a range of operating conditions [50], [51], and are also criticized for being case dependent because, when they are applied to same model with different parameters, the result varies. Moreover, the modelling of power system networks using conventional mathematical based linearized approaches is very difficult as it represents an extremely complex system that is highly nonlinear, non-stationary and involves a large number of inequality constraints. Hence load compensation capability of APF under non-ideal

supply and sudden load change conditions can be enhanced by optimizing the gains of PI controller using various optimization techniques [52]–[55].

A few solutions to the harmonic mitigation problem are found in References [56], [57], where harmonics are minimized through an objective function by optimization. In recent years, many advances have been made to solve optimization problems by the use of numerous non-traditional methods like Simulated annealing, Tabu search, Genetic algorithm (GA), Ant colony optimization (ACO), Artificial Bee colony (ABC) optimization, PSO, BFO etc. in various fields of application and research [50], [52]–[85]. Some artificial intelligence based techniques such as Fuzzy logic, Neural network and GA are exploited in Reference [71] to design a control scheme for APFs dealing with harmonics and reactive power compensation.

#### 1) Particle swarm optimization (PSO)

The biologically inspired optimization technique called as PSO was introduced by Kennedy and Eberhart in the year 1995 [67]. It imitates the swarm behavior exhibited by bird flocks or fish schools, for optimization of nonlinear functions. A swarm consists of number of particles that fly through the feasible solution space to explore optimal solutions. Each particle in the population updates its position based on its own best exploration and best swarm overall experience that is the swarm intelligence.

PSO is being extensively used due to its simple concept, easy implementation, inexpensive computation and well-balanced mechanism to promote both local and global explorations [52], [53], [68]–[70]. Na He *et al.* demonstrated PSO to be effective and suitable for multi-objective optimal design of filters [72]. Multi-objective planning of distribution systems using PSO is also reported in literature [86]–[88]. Despite having so many advantages, it suffers from the severe drawback of premature convergence [73], [74]. Hence, though it performs well in early iterations, slows down or even becomes stagnant as the number of iterations increases. While solving problems with multiple optima, it may easily get trapped in a local optimum instead of global optimum at the end of iterations.

#### 2) Bacterial foraging optimization (BFO)

The concept of BFO was introduced by Passino in 2002, where the social foraging behavior of *Escherichia coli* bacteria has been used to solve multi-optimal non-gradient optimization problems [75]. It is based on the evolutionary process of natural selection that tends to eliminate animals with poor foraging strategies and supports survival of the fittest. Four principal mechanisms such as chemotaxis, swarming, reproduction and elimination-dispersal are observed in bacterial population. The BFO algorithm mimics these mechanisms to map out the global optimum position in a search space. An interesting characteristic feature of BFO is that, it has its own local search mechanism through the computational chemotactic step, and reproduction with elimination-dispersal helps in global search.