# ANALYSIS OF VARIOUS DCVSL STRUCTURES AND IMPLEMENTATION OF FULL ADDER WITH THEM

A THESIS SUBMITTED IN THE PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF TECHNOLOGY

IN

## VLSI DESIGN AND EMBEDDED SYSTEM

BY

**SUBHRAJIT ROY**

213EC2210

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA

ODISHA, INDIA - 769008

2015

# ANALYSIS OF VARIOUS DCVSL STRUCTURES AND IMPLEMENTATION OF FULL ADDER WITH THEM

A THESIS SUBMITTED IN THE PARTIAL FULFILMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF TECHNOLOGY

IN

### VLSI DESIGN AND EMBEDDED SYSTEM

BY

SUBHRAJIT ROY

### 213EC2210

Under the Guidance of

### **PROF. MUNSHI NURUL ISLAM**

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA

ODISHA, INDIA - 769008

2013-2015

DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

Rourkela, Odisha – 769008

India

# CERTIFICATE

This is to certify that the Thesis Report entitled

## ANALYSIS OF VARIOUS DCVSL STRUCTURES AND IMPLEMENTATION OF FULL ADDER WITH THEM

submitted by

# Mr. Subhrajit Roy

bearing Roll No. 213EC2210

in partial fulfilment of the requirements for the award of

MASTER OF TECHNOLOGY

in

VLSI DESIGN AND EMBEDDED SYSTEM

during session 2013-2015 at National Institute of Technology, Rourkela is an authentic work carried out by him under my supervision and guidance. To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other university/institute for the award of any degree or

ROURKELA

**Prof. Munshi Nurul Islam.** Department of ECE, National Institute of Technology Rourkela.

Date - 31.05.2015

### DEPARTMENT OF ELECTRONICS AND COMMUNICATION ENGINEERING

### NATIONAL INSTITUTE OF TECHNOLOGY

### Rourkela, Odisha – 769008

### India

# DECLARATION

### I certify that -

- The work contained in this thesis is original and has been done by myself under the general supervision of my supervisor.

- > The work has not been submitted to any other Institute for any degree or diploma.

- > I have followed the guidelines provided by the Institute in writing the thesis.

- Whenever I have used materials (data, theoretical analysis, and text) from other sources, I have given due credit to them by citing them in the text of the thesis and giving their details in the references.

- Whenever I have quoted written materials from other sources, I have put them under quotation marks and given due credit to the sources by citing them and giving the required details in the references.

# SUBHR&JIT ROY subhrajit.royy@gmail.com

### **ACKNOWLEDGEMENT**

First and foremost, I would like to express my sincerest appreciation to my Project Guide, **Prof. Munshi Nurul Islam**, for his guidance and tremendous support throughout the course of this project. His knowledge and expertise have been really helpful in this research work. The regular discussions with him and his ideas for approaching each problem statement in a different manner have been extremely useful. Without his utmost help, this dissertation would not have been possible.

Next, I would like to thank **Prof. K. K. Mahapatra**, **Prof. P. K. Tiwari**, **Prof. D. P. Acharya**, and **Prof. A. K. Swain** for their thoughtful teaching and suggestions during my course of M.Tech and making available all necessary facilities and infrastructure for studies.

Next, I would like to express my thanks to all the Ph. D. and Research scholars who have readily provided a helping hand in my time of need and acknowledged my numerous requests without any pique regarding any technical support.

I would also like to thank all the other faculty members and non-teaching staff of the Department of ECE for helping me directly or indirectly in completion of this project.

Away from home in a distant land, the people who constantly support and encourage a person are his friends. I am utmost grateful to my friends, here at NIT Rourkela. Apart from the regular education from my professors, I have learnt many things from my friends. I would like to express my thanks to all of them for making these two years a fantabulous journey.

Finally, I owe my heartiest gratitude to the most important people in my life, i.e. my parents and my elder brother for their unconditional support, love, inspiration and sacrifices. They have always been a source of inspiration throughout my life. The discussions with them, especially my brother, have assisted me through many a time of ordeal. I would like to thank them from the bottom of my heart.

### SUBHRAJIT ROY

Dedicated To

# My Parents, My Brother

and

# All My Dear Friends

# **ABSTRACT**

The Differential Cascode Voltage Switch Logic (DCVSL) is a CMOS circuit technique which has potential advantages over conventional NAND/NOR logic in terms of power dissipation, circuit delay, layout density and logic flexibility. In this paper, a detailed comparison of all the DCVSL structures are provided including the implementation of Full Adder circuit with the help of those DCVSL structures, which includes Static DCVSL, Dynamic DCVSL and Modified DCVSL. The performance analysis is done in Cadence Virtuoso 90nm CMOS Technology.

The working of these DCVSL structures is based on the concept of 'Multiplexer'. A multiplexer also known as 'mux', which is a device where from a number of input signals, selection is done. It is basically a combinational logic circuit. The multiplexer is a unidirectional device, which is used in applications where a data must be switched from multiple sources to a destination.

The analysis of all these DCVSL structures is followed by the implementation of Full Adder. Adders are the building blocks in computer systems. Digital Computer Systems widely uses Arithmetic operations. Addition is a necessary arithmetic operation, which is also the root for arithmetic operation such as multiplication. Similarly, adding another XOR gate, the basic adder cell can be modified to function as subtractor, which can be used for division. Therefore, 1-bit Full Adder cell is the ultimate and simple block of an arithmetic unit of a system. So, the basic 1-bit Full Adder cell must be improved, so that the performance of the digital circuits. In VLSI, there is always a trade-off between speed and power dissipation. One parameter is improved, the other gets degraded. Hence, the parameter power delay product is introduced.

So, to achieve speeds, high drivability hybrid-DCVSL design methodologies are used to build adder cell in this work. The DCVSL gates produces both complementary and true outputs using single gate architecture. And, the multipliers in the design are based on the pass transistor logic (PTL), because these occupies less chip area per component and also are simple to construct.

The parameters compared are power dissipation, propagation delay time, power delay product, transistor number and power dissipation (average). The Static DCVSL structure produces best result in terms of power dissipation, delay and power delay product. Whereas, in case of the Adder circuit, the power consumption is best for the Dynamic DCVSL Adder, along with the delay and the power delay product for the output Sum; but for the output Cout, the best option is Static DCVSL Adder, as the delay and the power delay product is least in this case.

# **CONTENTS**

| (1) | Introduction $-$ {1-5}                                        |                                     |         |  |  |  |

|-----|---------------------------------------------------------------|-------------------------------------|---------|--|--|--|

|     | (1.1)                                                         | Topic Overview                      | (2-3)   |  |  |  |

|     | (1.2)                                                         | Literature Review                   | (4)     |  |  |  |

|     | (1.3)                                                         | Thesis Overview                     | (5)     |  |  |  |

| (2) | Details on Differential Cascode Voltage Switch Logic – {6-13} |                                     |         |  |  |  |

|     | (2.1)                                                         | Introduction                        | (7-9)   |  |  |  |

|     | (2.2)                                                         | Basic DCVSL Circuit                 | (9-12)  |  |  |  |

|     | (2.3)                                                         | Different Types of DCVSL Structures | (12-13) |  |  |  |

|     |                                                               | Static DCVSL                        | (12-13) |  |  |  |

|     |                                                               | Dynamic DCVSL                       | (13)    |  |  |  |

|     |                                                               | Modified DCVSL                      | (13)    |  |  |  |

| (3) | Circuit Techniques for DCVSL – {14-28}                        |                                     |         |  |  |  |

|     | (3.1)                                                         | Introduction                        | (15)    |  |  |  |

|     | (3.2)                                                         | Different Techniques                | (15-28) |  |  |  |

|     |                                                               | Design by Intuition                 | (15-19) |  |  |  |

|     |                                                               | ► K-Map Procedure                   | (19-24) |  |  |  |

|     |                                                               | Tabular Method                      | (24-28) |  |  |  |

| (4) | Testing                                                       | g Schemes on DCVSL Structures       | {29-31} |  |  |  |

| (5) | Performance Analysis of DCVSL Structures – {32-56}            |                                     |         |  |  |  |

|     | (5.1)                                                         | Static DCVSL                        | (34-40) |  |  |  |

|     | (5.2)                                                         | Dynamic DCVSL                       |         |  |  |  |

|     | (5.3)                                                         | Modified DCVSL                      |         |  |  |  |

| (6) | Performance Analysis of DCVSL Adder Circuits – {57-78}        |                                     |         |  |  |  |

|     | (6.1)                                                         | Static DCVSL Adder                  | (59-63) |  |  |  |

|     | (6.2)                                                         | Dynamic DCVSL Adder                 | (64-68) |  |  |  |

|     | (6.3)                                                         | Modified DCVSL Adder                |         |  |  |  |

|     | (6.4)                                                         | Layouts                             |         |  |  |  |

| (7) | Conclu                                                        | usion                               |         |  |  |  |

| (8) | Biblio                                                        | graphy                              | {81-83} |  |  |  |

# LIST OF FIGURES

| <u>Figure 1</u> – The structure of a DCVS circuit                                                        | (4)  |

|----------------------------------------------------------------------------------------------------------|------|

| <u>Figure 2</u> – DCVSL Structure.                                                                       | (7)  |

| <u>Figure 3</u> – Basic DCVSL circuit                                                                    | (9)  |

| Figure 4 – CVSL implementation of Q                                                                      | (10) |

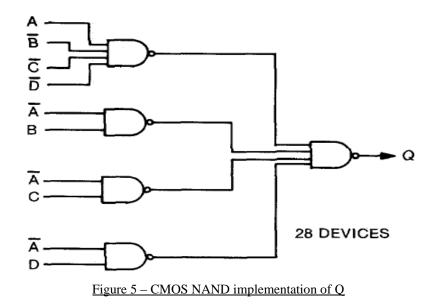

| <u>Figure 5</u> – CMOS NAND implementation of Q                                                          | (10) |

| Figure 6 – Clocked CVSL                                                                                  | (11) |

| Figure 7 – Clocked CVSL 4-way XOR                                                                        | (12) |

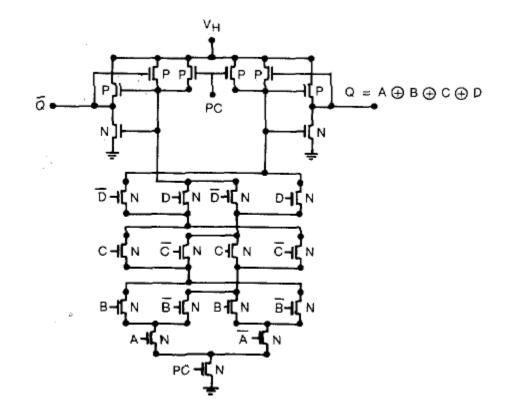

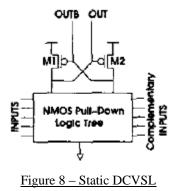

| Figure 8 – Static DCVSL                                                                                  | (12) |

| Figure 9 – Dynamic DCVSL                                                                                 | (13) |

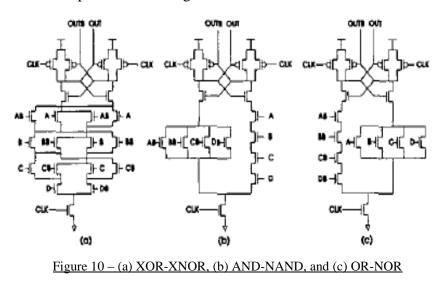

| <u>Figure 10(a), 10(b), 10(c)</u> – XOR-XNOR, AND-NAND, OR-NOR                                           | (13) |

| Figure 11 – Structure of DCVSL                                                                           | (15) |

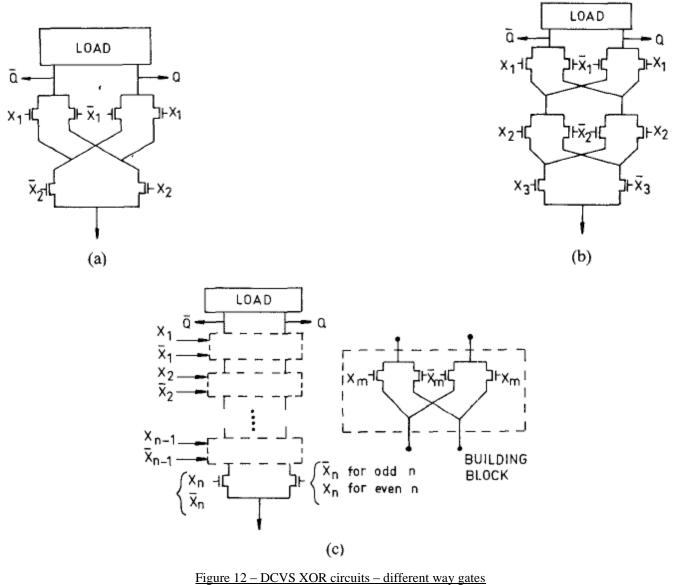

| Figure 12 – DCVS XOR circuits – different way gates                                                      | (16) |

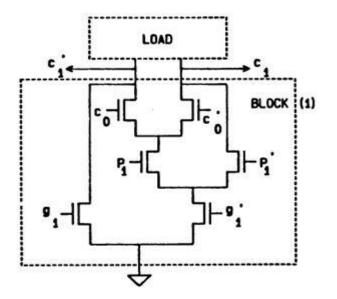

| <u>Figure 13(a)</u> – Function $cla_1 = s_1 + t_1 cla_0$ for DCVS circuit                                | (17) |

| <u>Figure 13(b)</u> – Recursive DCVS structure for function $cla_n = s_n + t_n cla_{n-1}$                | (17) |

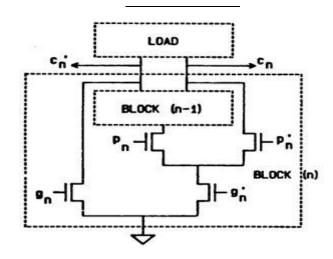

| <u>Figure 14(a)</u> – The DCVS tree with symbolic representation for the function $P = x_1x_2x_n$        | (18) |

| <u>Figure 14(b)</u> – For the function $f_1$                                                             | (18) |

| <u>Figure 14(c)</u> – For the function $f_2$                                                             | (19) |

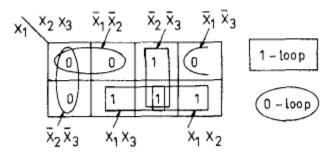

| <u>Figure 15(a)</u> – K-map of a Full Adder showing the carry-out function                               | (19) |

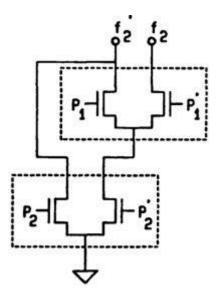

| <u>Figure 15(b)</u> – DCVS implementation on Full Adder representing carry-out                           | (20) |

| Figure 16(a) – K-map with different encirclements than the Figure of 15(a)                               | (20) |

| Figure 16(b) – DCVS tree with implementation on 10-loops                                                 | (21) |

| <u>Figure 16(c)</u> – Complete DCVS tree                                                                 | (21) |

| Figure 17(a) – K-map with function Q                                                                     | (22) |

| <u>Figure 17(b)</u> – DCVS circuit representing 01- loop                                                 | (22) |

| <u>Figure 17(c)</u> – Complete DCVS tree                                                                 | (23) |

| Figure 18(a) – Another example of K-map arrangement                                                      | (23) |

| <u>Figure 18(b)</u> – Circuit resulting from the previous figure. Compare it with that of Figure $17(c)$ | (23) |

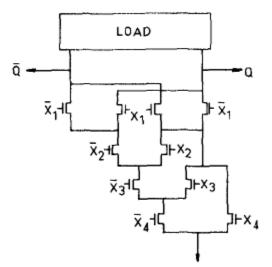

| <u>Figure 19</u> – The basic DCVS tree structure developed from Table 1                                  | (25) |

| <u>Figure 20</u> – The shared DCVS tree circuit with the 10-list                                         | (27) |

| <u>Figure 21</u> – 3-bit Magnitude Comparator having complete DCVS tree                                  | (28) |

| <u>Figure 22</u> – 3-input NAND gate with illegal inputs                                                 | (30) |

| <u>Figure 23</u> – Illegal state detector for the DCVS trees                                             | (31) |

| Figure 24(a) and 24(b) – Conventional and Proposed Static DCVSL                                          | (34) |

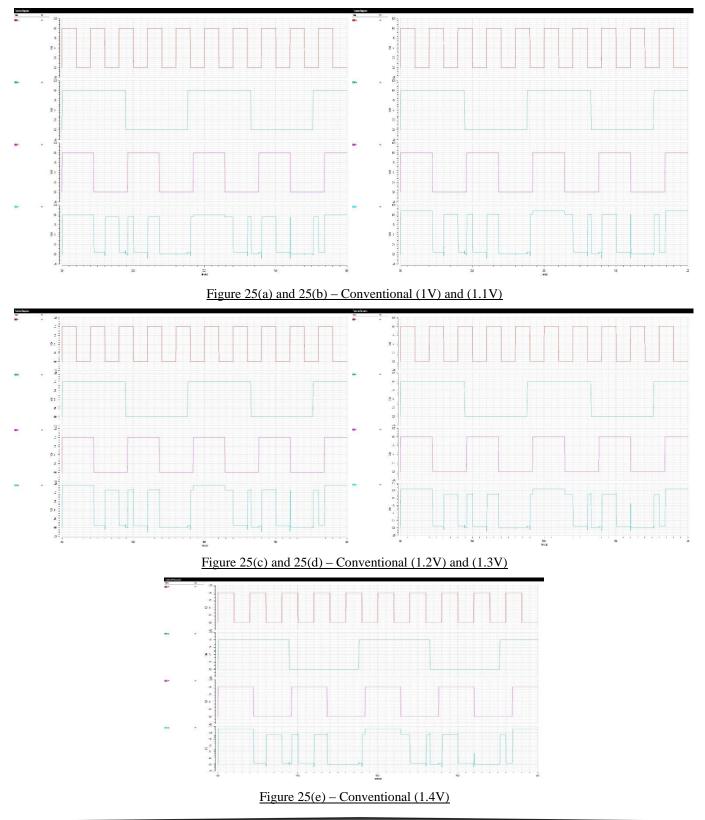

| Figure 25(a, b, c, d, e) – Conventional.                                            | (35)    |

|-------------------------------------------------------------------------------------|---------|

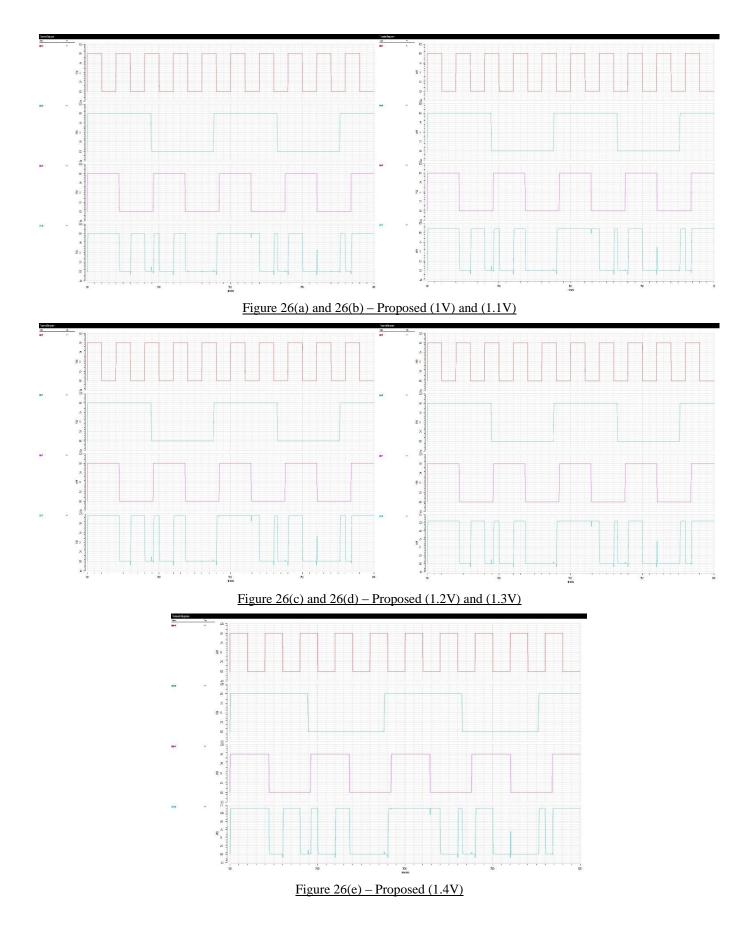

| Figure 26(a, b, c, d, e) – Proposed.                                                | (36)    |

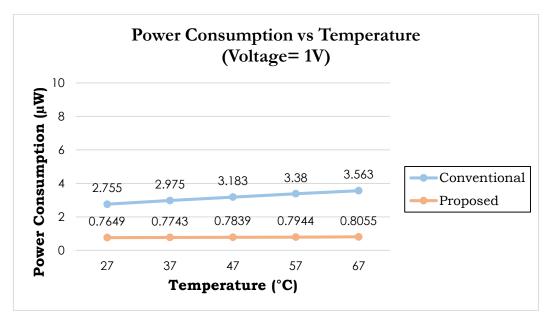

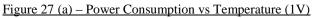

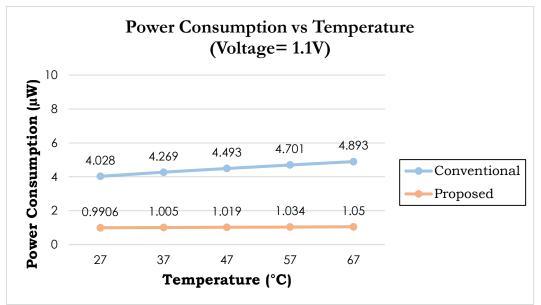

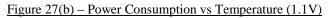

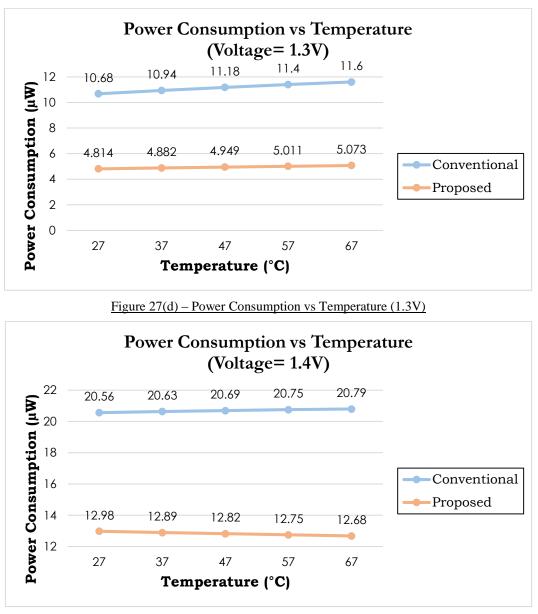

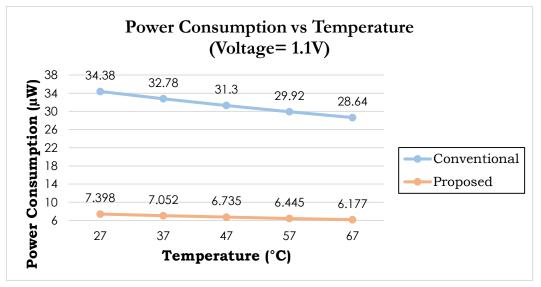

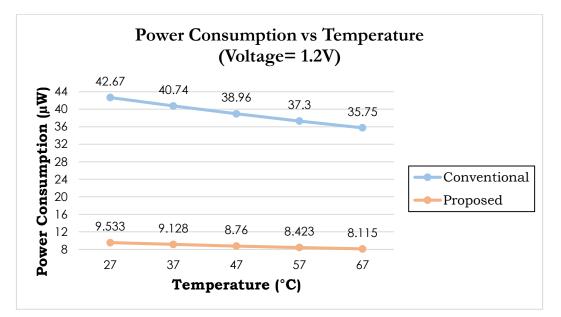

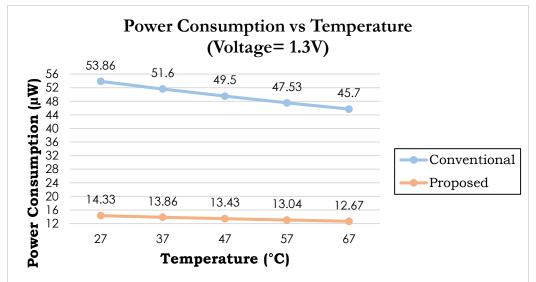

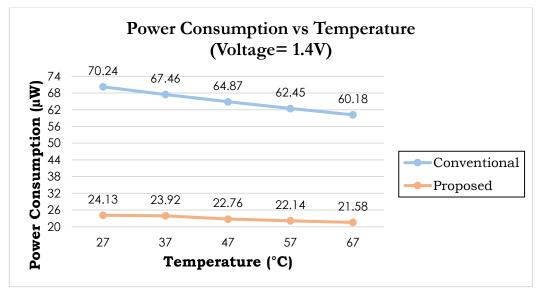

| Figure 27(a, b, c, d, e) – Power Consumption vs Temperature                         | (37-38) |

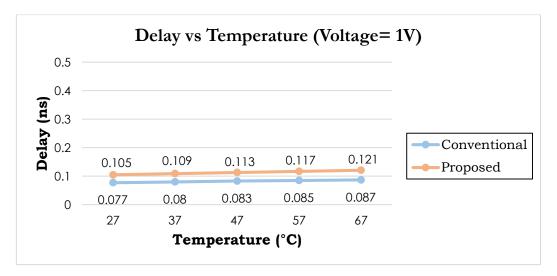

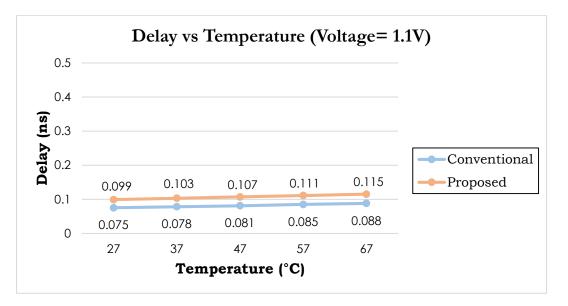

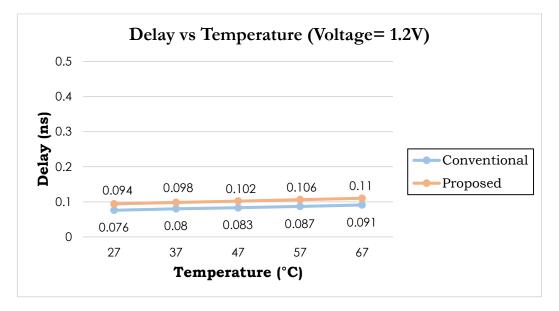

| Figure 28(a, b, c, d, e) – Delay vs Temperature.                                    | (38-40) |

| <u>Figure 29</u> – Power Delay Product (Temperature= 27°C)                          | (40)    |

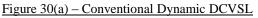

| Figure 30(a) and 30(b) – Conventional and Proposed Static DCVSL                     | (40-41) |

| Figure 31(a, b, c, d, e) – Conventional.                                            | (42)    |

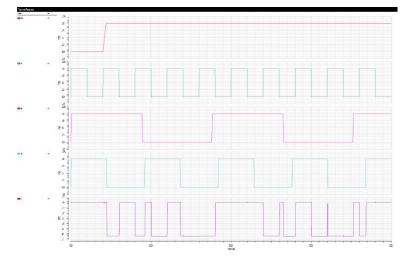

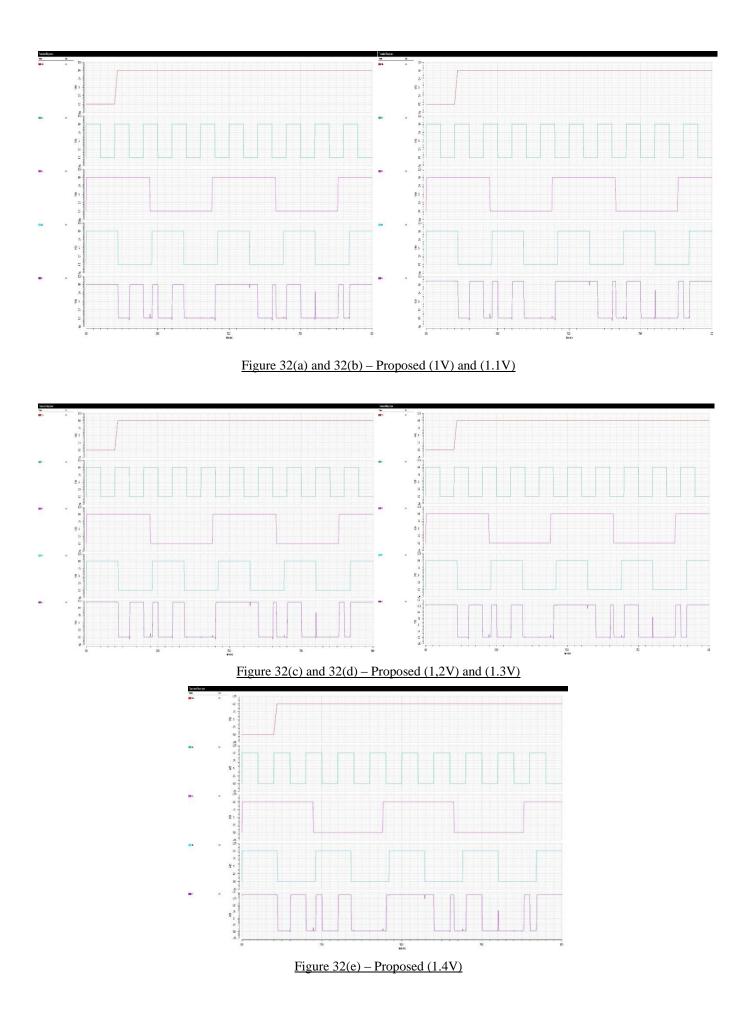

| <u>Figure 32(a, b, c, d, e)</u> – Proposed                                          | (43)    |

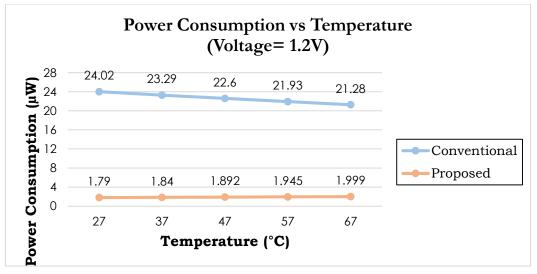

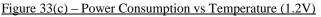

| Figure 33(a, b, c, d, e) – Power Consumption vs Temperature                         | (44-45) |

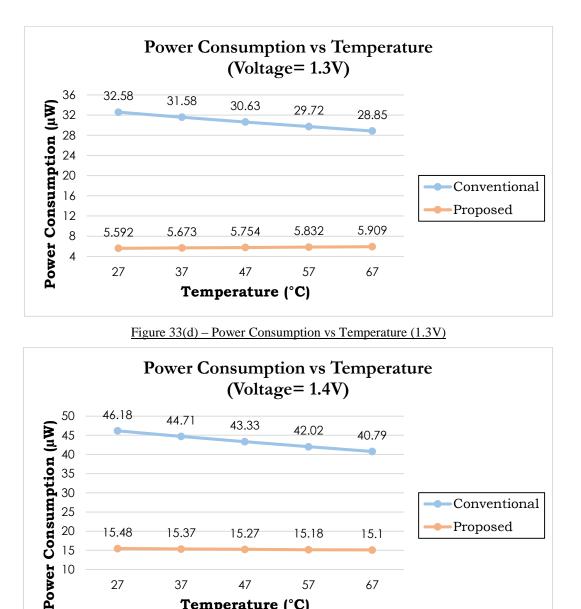

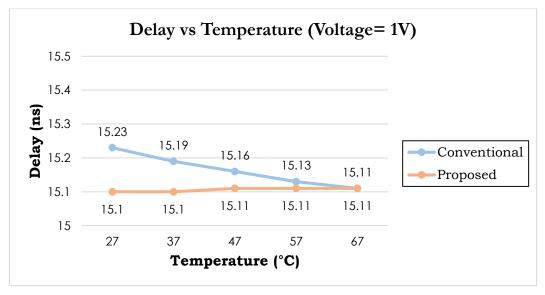

| Figure 34(a, b, c, d, e) – Delay vs Temperature.                                    | (45-47) |

| <u>Figure 35</u> – Power Delay Product vs Voltage (Temperature= 27°C)               | (47)    |

| Figure 36(a) and 36(b) – Conventional and Proposed Modified DCVSL                   | (47-48) |

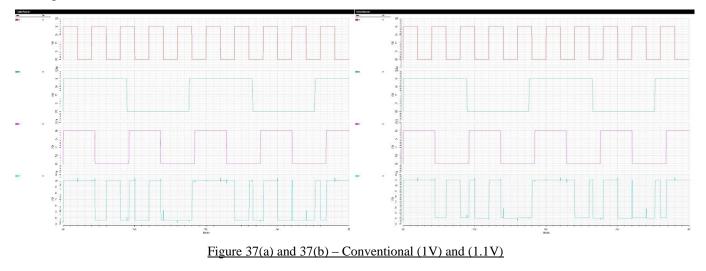

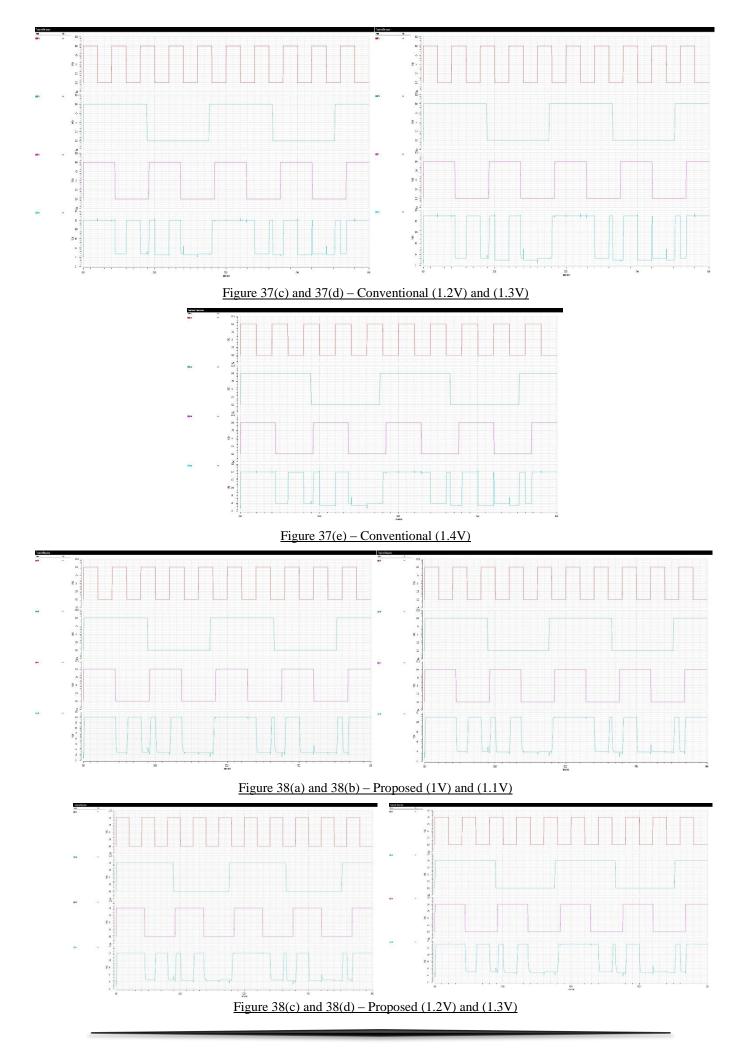

| Figure 37(a, b, c, d, e) – Conventional                                             | (48-49) |

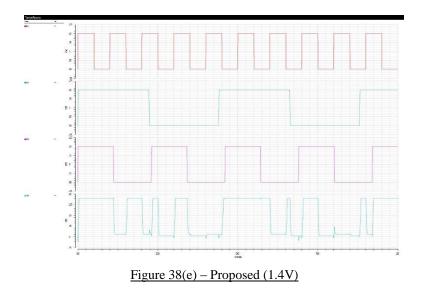

| <u>Figure 38(a, b, c, d, e)</u> – Proposed                                          | (49-50) |

| Figure 39(a, b, c, d, e) – Power Consumption vs Temperature                         | (50-51) |

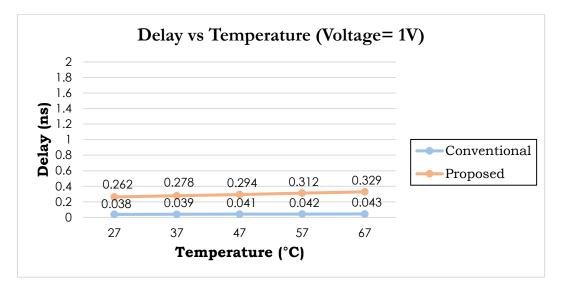

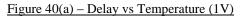

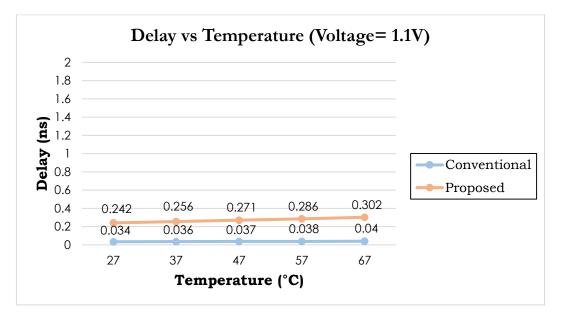

| <u>Figure 40(a, b, c, d, e)</u> – Delay vs Temperature                              | (52-53) |

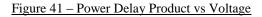

| <u>Figure 41</u> – Power Delay Product vs Voltage (Temperature= 27°C)               | (53)    |

| <u>Figure 42</u> – Stacking Effect in 2-input NAND gate                             | (58)    |

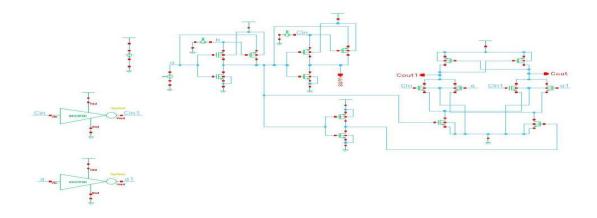

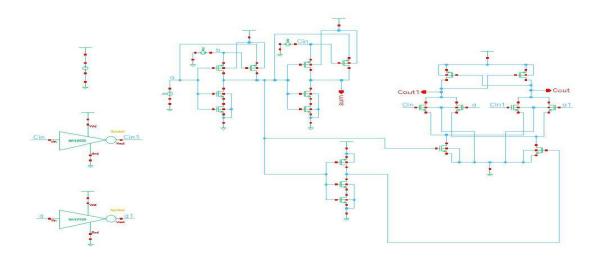

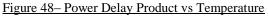

| Figure 43(a) and 43(b) – Conventional and Proposed Static DCVSL Adder               | (59-60) |

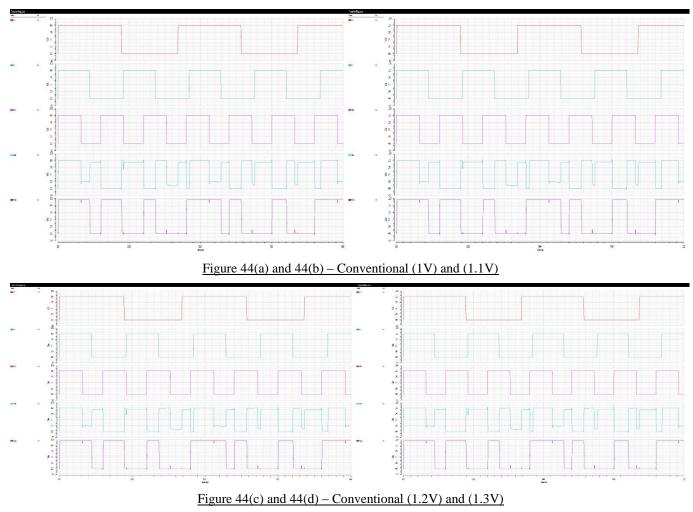

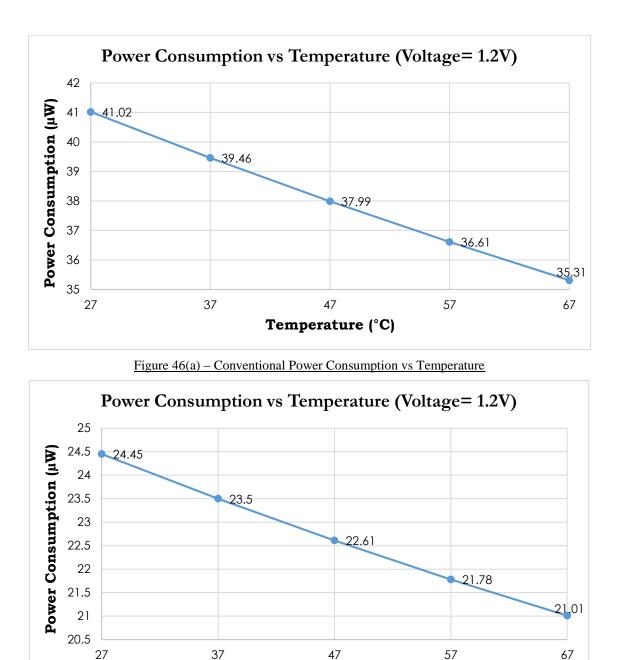

| <u>Figure 44(a, b, c, d, e)</u> – Conventional                                      | (60-61) |

| Figure 45(a, b, c, d, e) – Proposed                                                 | (61)    |

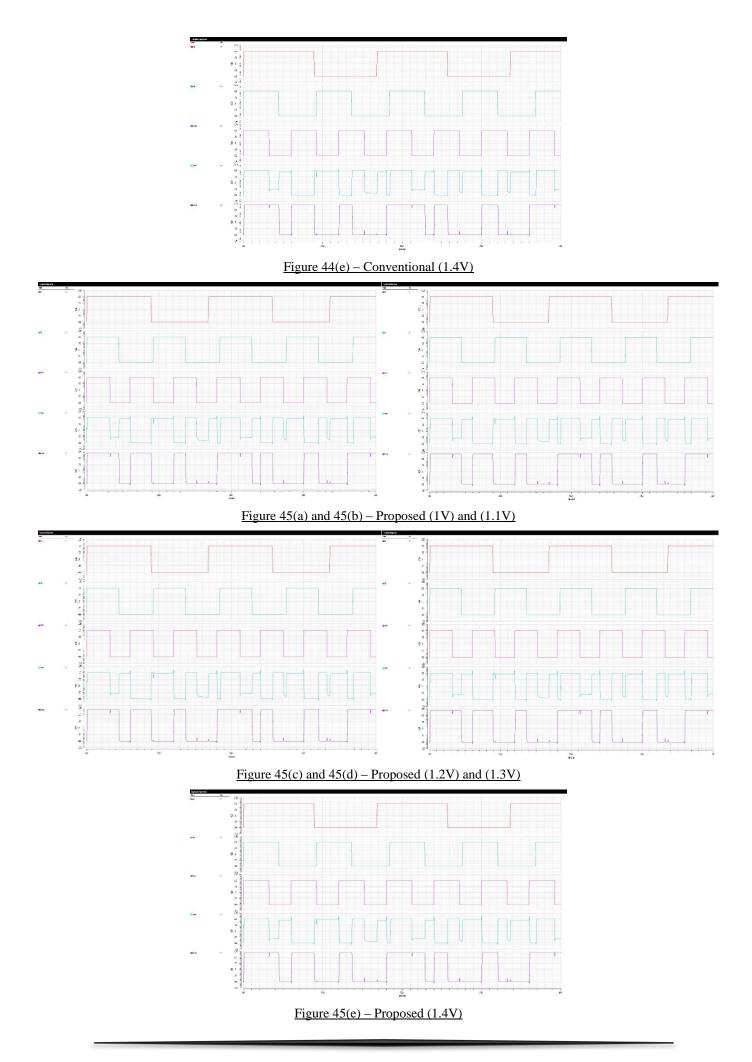

| Figure 46(a) and 46(b) – Conventional and Proposed Power Consumption vs Temperature | (62)    |

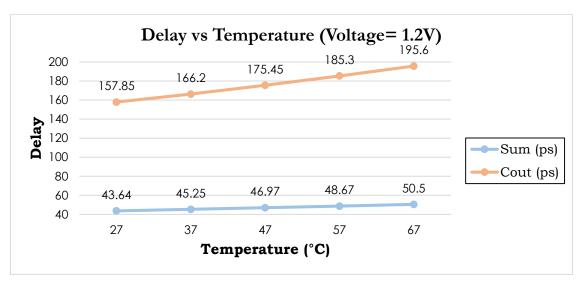

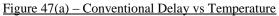

| Figure 47(a) and 47(b) – Conventional and Proposed Delay vs Temperature             | (63)    |

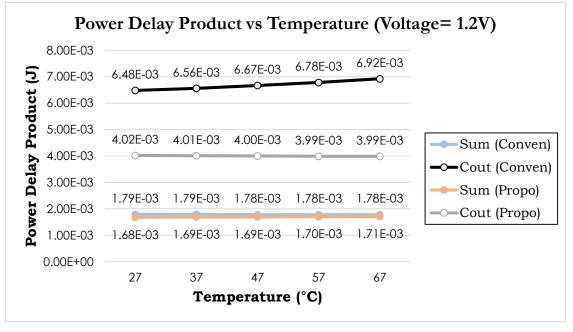

| <u>Figure 48</u> – Power Delay Product vs Voltage (Temperature= 27°C)               | (63)    |

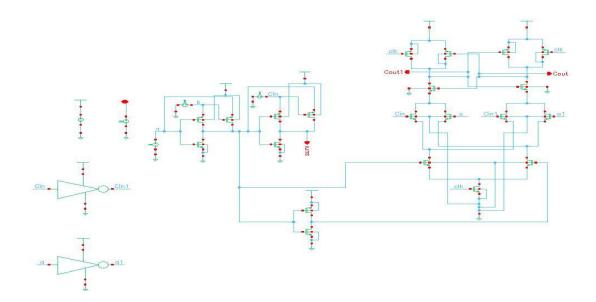

| Figure 49(a) and 49(b) – Conventional and Proposed Dynamic DCVSL Adder              | (64)    |

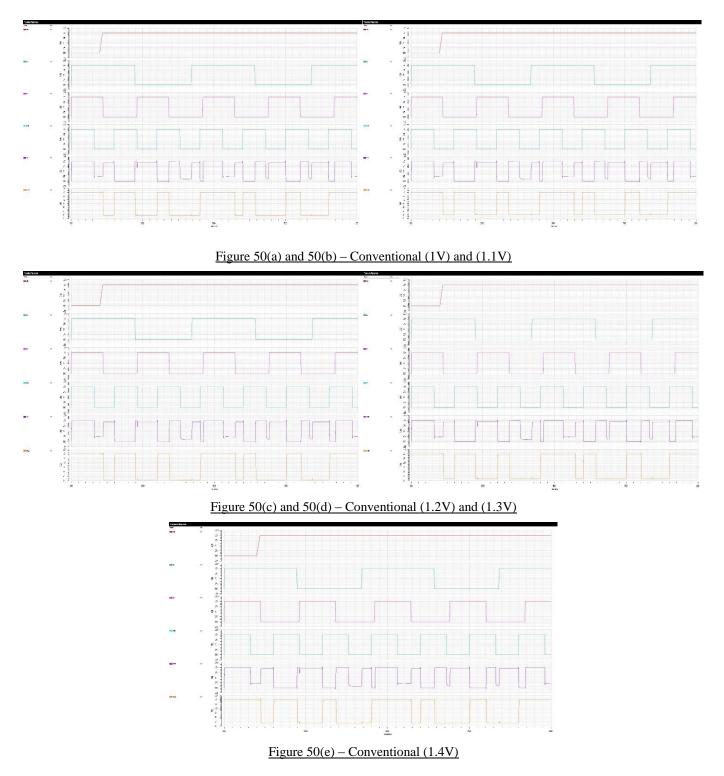

| <u>Figure 50(a, b, c, d, e)</u> – Conventional                                      | (65)    |

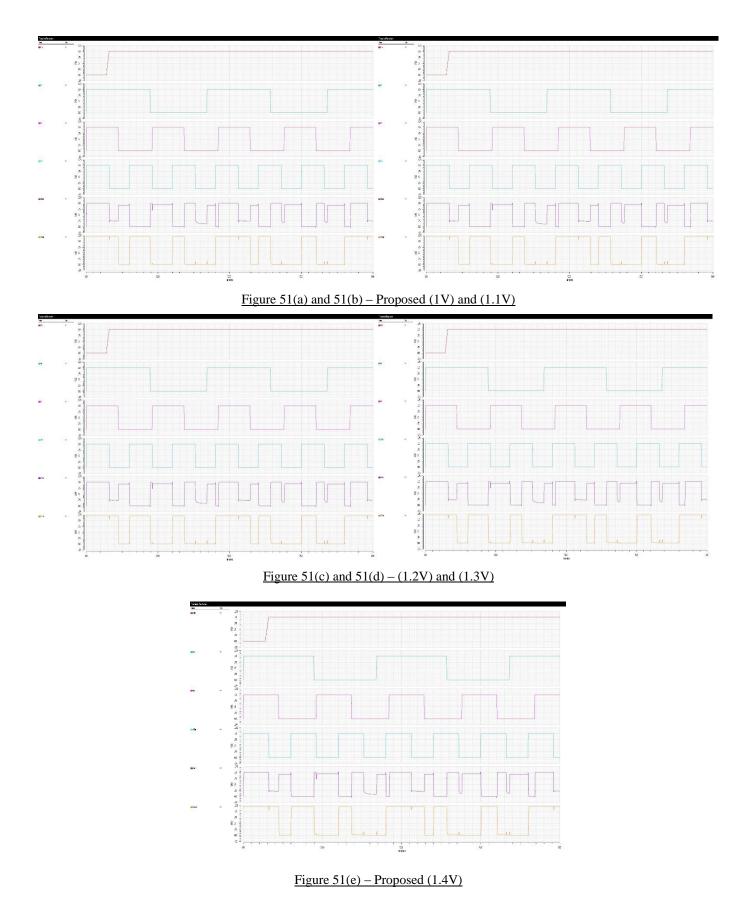

| <u>Figure 51(a, b, c, d, e)</u> – Proposed                                          | (66)    |

| Figure 52(a) and 52(b) – Conventional and Proposed Power Consumption vs Temperature | (67)    |

| Figure 53(a) and 53(b) – Conventional and Proposed Delay vs Temperature             | (67-68) |

| <u>Figure 54</u> – Power Delay Product vs Voltage (Temperature= 27°C)               | (68)    |

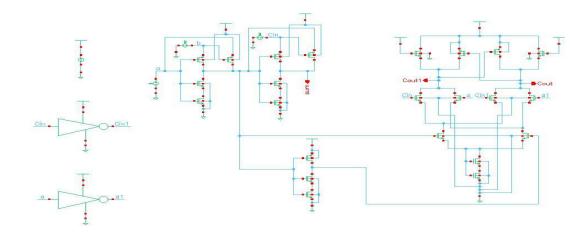

| Figure 55(a) and 55(b) – Conventional and Proposed Modified DCVSL Adder             | (68-69) |

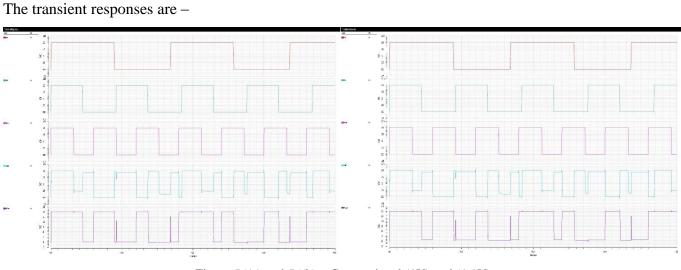

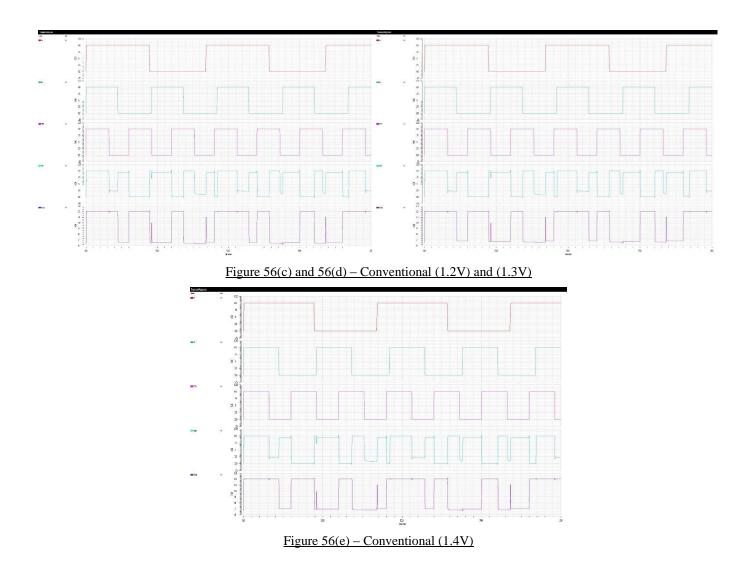

| <u>Figure 56(a, b, c, d, e)</u> – Conventional                                      | (69-70) |

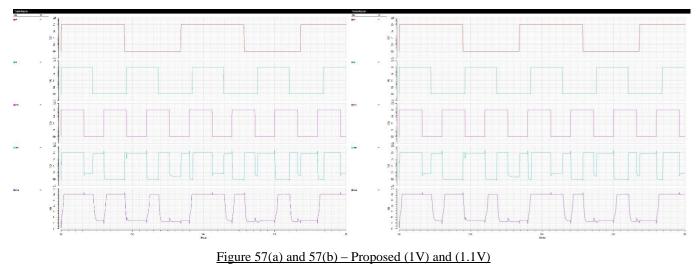

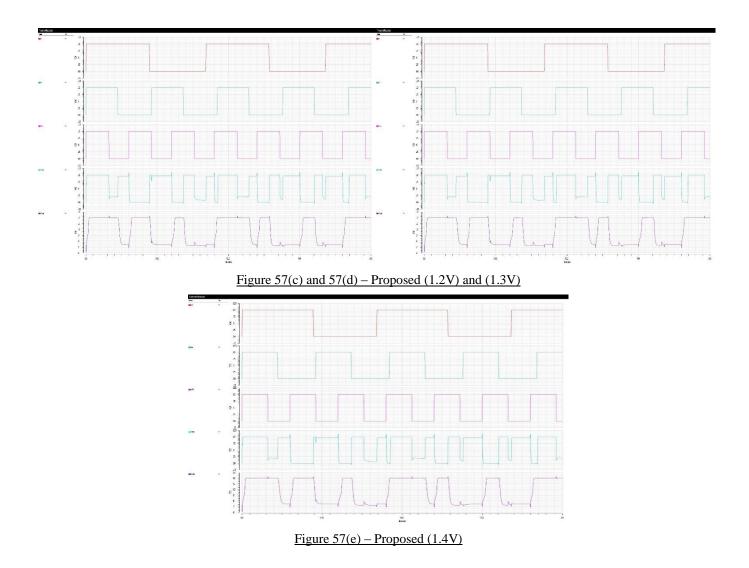

| <u>Figure 57(a, b, c, d, e)</u> – Proposed                                          | (70-71) |

| Figure 58(a) and 58(b) – Conventional and Proposed Power Consumption vs Temperature | (71-72) |

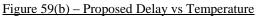

| Figure 59(a) and 59(b) – Conventional and Proposed Delay vs Temperature             | (72)    |

| <u>Figure 60</u> – Power Delay Product vs Temperature (Temperature= 27°C)           | (73)    |

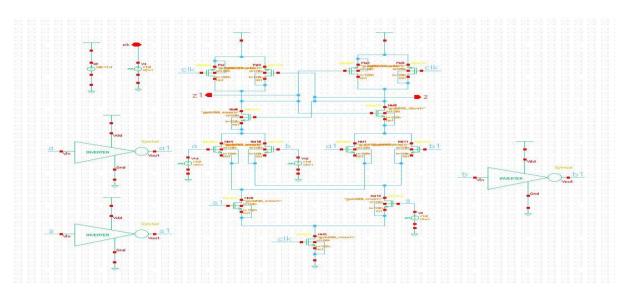

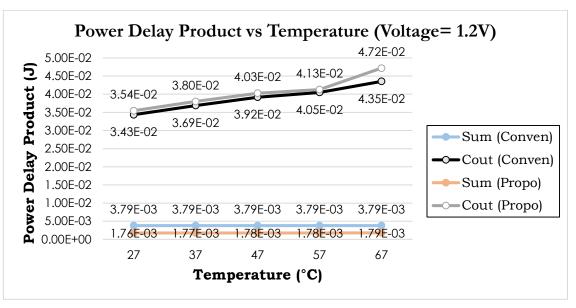

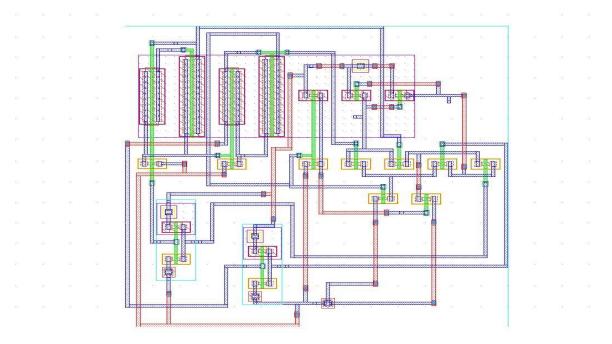

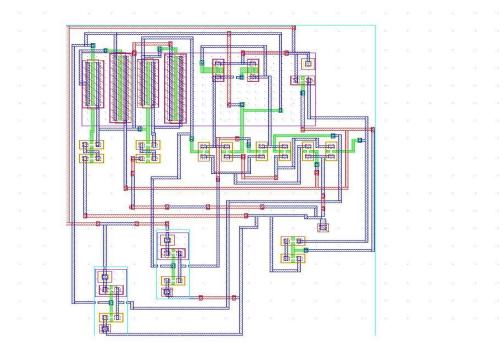

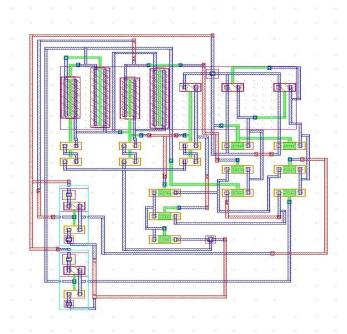

| Figure 61 – Conventional Static DCVSL Adder   | (76) |

|-----------------------------------------------|------|

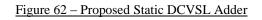

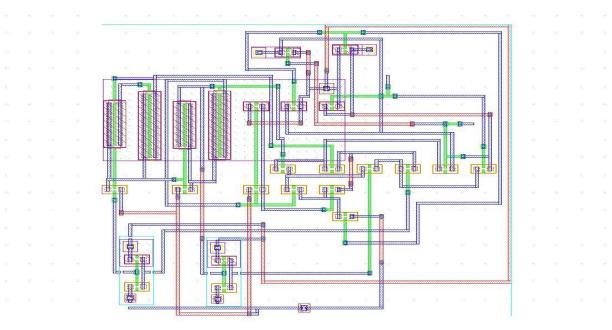

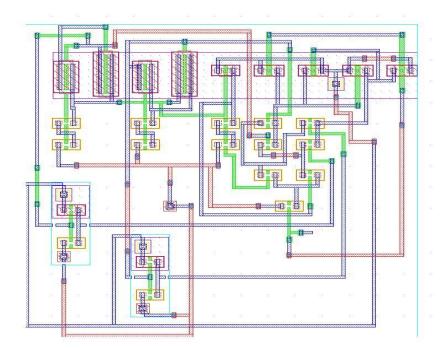

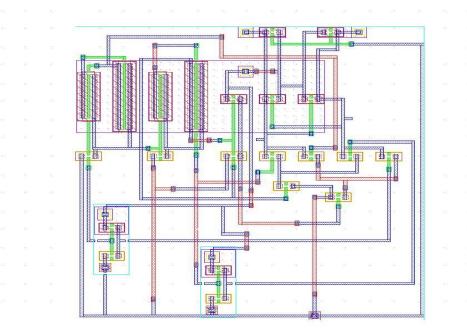

| Figure 62 – Proposed Static DCVSL Adder       | (76) |

| Figure 63 – Conventional Dynamic DCVSL Adder  | (77) |

| Figure 64 – Proposed Dynamic DCVSL Adder      | (77) |

| Figure 65 – Conventional Modified DCVSL Adder | (78) |

| Figure 66 – Proposed Modified DCVSL Adder     | (78) |

# LIST OF TABLES

| <u>Table 1</u> – The list format for Tabular Method                                      | (24)          |

|------------------------------------------------------------------------------------------|---------------|

| Table 2 – Format of 10-list                                                              | (25)          |

| <u>Table 3</u> – The 10-list of a 3-bit Magnitude Comparator                             | (26)          |

| <u>Table 4</u> – Prime implicant table of the 10-list                                    | (27)          |

| <u>Table 5</u> – The 1-list and its minimal sum for the Magnitude Comparator             | (27)          |

| <u>Table 6</u> – The 0-list and its minimal sum for the Magnitude Comparator             | (28)          |

| <u>Table 7</u> – Truth Table of 2:1 Multiplexer                                          | (33)          |

| <u>Table 8</u> – Comparison between the three DCVSL structures (Power Consumption vs Ten | perature)(54) |

| <u>Table 9</u> – Comparison between the three DCVSL structures (Delay vs Temperature)    | (55)          |

| <u>Table 10</u> – Power Delay Product vs Voltage (Temperature= $27^{\circ}$ C)           | (56)          |

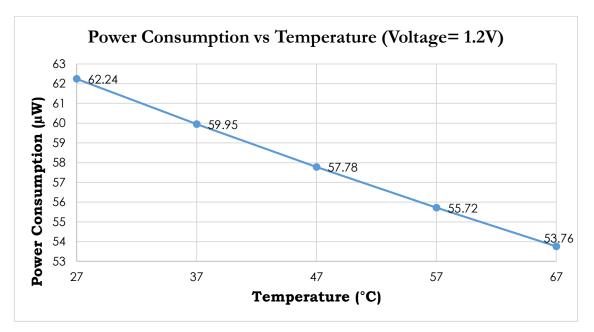

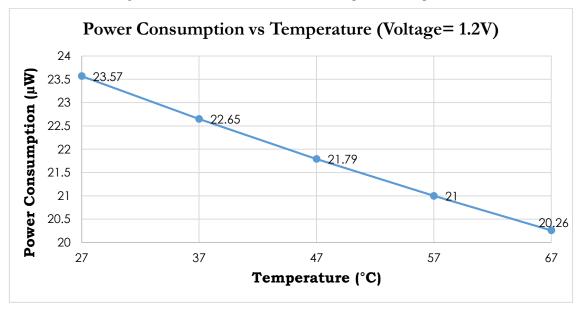

| <u>Table 11</u> – Power Consumption vs Temperature (1.2V)                                | (73)          |

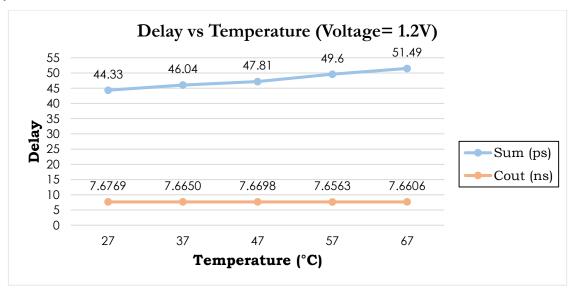

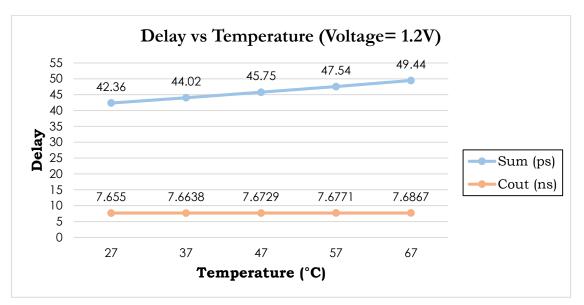

| <u>Table 12</u> – Delay vs Temperature for Sum (Voltage= 1.2V)                           | (74)          |

| <u>Table 13</u> – Delay vs Temperature for Cout (Voltage= 1.2V)                          | (74)          |

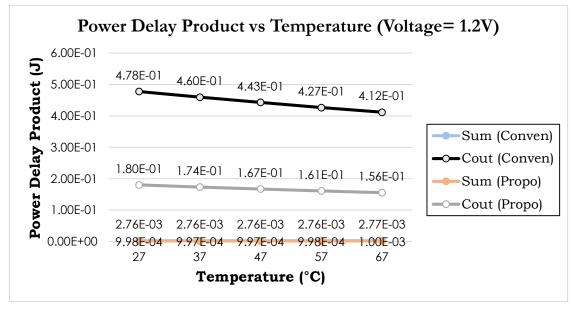

| <u>Table 14</u> – Power Delay Product vs Temperature for Sum (Voltage= 1.2V)             | (75)          |

| <u>Table 15</u> – Power Delay Product vs Temperature for Cout (Voltage= 1.2V)            | (75)          |

| <u>Table 16</u> – Comparison of Area and No. of Transistors for the Adder Circuits       | (78)          |

Chapter 1

# **INTRODUCTION**

### (1.1) <u>Topic Overview</u>

A comparison between Differential Cascode Voltage Switch Logic (DCVSL) and traditional NAND/NOR Logic resulted in the former having several advantages over the latter one in terms of logic flexibility [1], device count, layout area, power dissipation and circuit delay. Less number of transistors are required, including both p and n- type than the NAND/NOR Logic [1]. It also provides advantages such as stuck-at and dynamic faults because of its self-testing property [2]. A leverage circuit provides a perfect example where a single CVS gate is obtained from numerous stages of delay [3]. The CVS circuit has increased stack height but it also has certain advantages such as smaller chip area, lesser power dissipation and shorter circuit delay which is achieved due to the decrease in quantity of stages. The advantage of logic flexibility is achieved in situations; where in Domino CMOS Logic, complex functions are implemented. As Standard Domino Logic cannot implement functions having inverting logic gates, hence Clocked DCVS Logic is used which overcomes this restriction by providing complementary outputs [1]. The various advantages of DCVS Logic over the standard CMOS NAND/NOR Logic can be outlined as-

- Circuits having great complication and fan-in gates can be implemented as it may be done with lesser transistor count. For definite circuits having large complex gates, the clocked DCVS Logic families have very low propagation delay since it can integrate a single complex gate from both sequential and combinatorial portions. Hence, for high-speed VLSI this logic style is appropriate.

- In DCVS Logic, the faster response comes through the reduction of parasitic capacitances at the output as it is not having a complementary pull-up network. Therefore, it has the speed advantage over domino circuit and also eliminates the static power consumption.

- The output voltage swings from rail to rail and it doesn't provide the direct current path between V<sub>DD</sub> and ground in steady states.

- In DCVS Logic, the completion of gate evaluation is easy to detect since true and complementary outputs are formed. For this reason, DCVS Logic is the suitable choice for implementing self-timed circuits.

- Due to its true and complementary outputs, the performance is further improved by elimination of inverting stage [4].

- While the standard domino logic cannot implement inverting logic gates, but the DCVSL logic style can implement both inverting and non-inverting logic style [1].

The DCVSL circuit also saves area by sharing the common transistors in the logic network for both of the outputs when a complex logic gate is designed.

These above advantages indicates the DCVS Logic as a new dimension in CMOS Logic design. However, along with these advantages there are certain disadvantages such as the high power along with extra area and complexity due to dual logic networks having complementary signals are the definite hindrances towards their acceptance as a design logic. The power consumption in DCVS gate comprises of the outputs switching and the switching at internal nodes of the gate. With gate complexity, the number of internal nodes switched in NMOS evaluation tree increases. The switching in internal nodes is the dominant factor of total gate power.

The **Algebraic Technique** is used for the design of DCVS trees, which is the ultimate existing procedure and is also based on the identification of sub-expressions which is common to two or numerous Boolean functions [5]. It also has decomposition and factorization technique which is quite mathematical, hence this method is not suitable for IC designers as it doesn't provide the insight into circuit behaviour. Along with the algebraic technique, there are two other techniques which are more practical and also much simpler for constructing DCVS trees.

- The Karnaugh Map (K-Map) Method Here, the pictorial nature is used. This hand-processing method is quite efficient in realizing circuits with low device count and is implemented with functions having five or six variables. More than the specified variables, the complexity of K-maps increases.

- The Quine-McCluskey Method It is uniform and hence procedural for complexities upto n number of variables and it is tabular in nature [6].

The worthwhile features of the DCVS Logic makes it a very promising CMOS circuit technique. To investigate this possibility, we have done analysis on various types of DCVS Logic namely,

- > Static DCVSL.

- > Dynamic DCVSL.

- > Modified DCVSL.

Along with it, we have also implemented these various DCVS Logic on Full Adder circuit since the full adder is common, yet reasonably complex building block in digital circuits and design. The work is done on CADENCE VIRTUOSO 90nm technology to assess the performance parameters of power dissipation, delay, area, speed and power delay product. The area is represented from the layout drawn in cadence. Speed is reflected through the worst-case propagation time.

#### (1.2) <u>Literature Review</u>

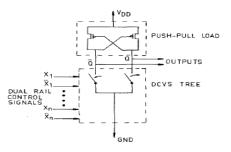

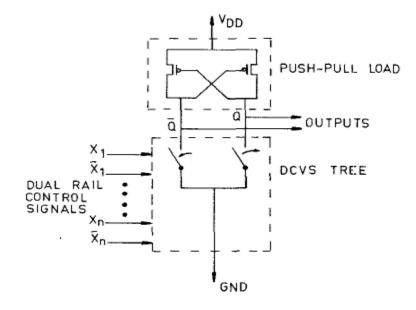

When the differential pairs of MOSFET devices are cascoded into strong combinational logical tree networks, then we can achieve a design leverage in CVSL which is within a single circuit delay and is capable of implementing complex Boolean logic. When there is a Boolean function which might have input variables upto (2<sup>N</sup>-1) is being processed with N-high cascoding of differential pairs of NMOS devices. CVSL offers a performance advantage of up to 4X compared to standard CMOS NAND/NOR logic families, while maintaining the expected low power characteristics of CMOS circuitry. The primitive NAND/NOR Logic and the CVSL, both are potentially dense and are well-suited with previous design automation tools. Using cascoded high-performance NMOS devices, logic trees which are compatible in nature are designed and the unstacked P mosfet devices are used as pull-up devices in load and buffer circuitry. Therefore the P mosfet devices can be optimized and hence critical spacing between P and N devices are relaxed, releasing the device complexity burden for CVSL designs. CMOS is widely used in making logic circuits, but then also the DCVSL has its own features such as no static power, higher speed [7] as it produces complementary outputs due to dual rail logic and is very efficient in designing full adder circuits [8]. Heller et.al presented DCVSL [1] & then Chu et.al compared the conventional and DCVS Logic Full Adder circuit [9], [10]. Full Adder is considered as a vital building block for circuits like adders and multipliers, therefore reducing the delay would improve the circuits in terms of speed [7]. In Very Large Scale Integrated Circuits, by abandoning the signal slope effect, similar value of capacitance for rising and falling transistors is obtained with uniform gate capacitance and diffusion capacitance rate/unit width and assuming uniform P to N size ratio for various logic gates; the delay modelling for conventional circuits is done. Along with it, Shockley's a-power law is used to calculate the MOS transistor current where the  $\alpha$  is a value amid 1 and 2 and is termed the velocity saturation index [7]. There is an additional precise model for MOS transistors proposed in [11] by Shams with same level of complexity. The propagation delay of conventional and some unconventional logic styles like DCVSL, CPL and PTL can be modelled and designed accurately and exhaustively using the stated current relation supposing nonsimilar capacitance values for rising and falling transistors [11], [12] and also the signal slope effect. This helps us in optimizing CMOS circuits which is of mixed styles of logic. Figure 1 shows the structure of a DCVS circuit which consisting of a load which is push-pull in formation and also consist of a couple of interconnected binary decision trees.

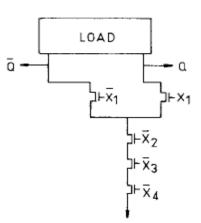

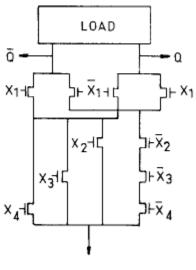

Figure 1 – The structure of a DCVS circuit

### (1.3) <u>Thesis Overview</u>

<u>Chapter 1</u> introduces the topic, discusses about the importance of DCVSL structures, its evolution, past significance, advantages and disadvantages. It also gives an idea of its discovery as mentioned in the Literature Review portion of it.

<u>Chapter 2</u> starts with the details of the Differential Cascode Voltage Switch Logic (DCVSL), it shows the basic structure of DCVS circuit. Apart from that, three different types of DCVSL structures are defined, namely Static DCVSL, Dynamic DCVSL and Modified DCVSL.

<u>Chapter 3</u> gives the idea about the circuit techniques by which one can measure the various parameters of DCVSL structures. Here, three types of circuit techniques are explained – Algebraic Method, K-map Method and Tabular Method; out of which only algebraic method is used in recent forms.

<u>Chapter 4</u> gives the idea about the testing schemes of the DCVSL circuits.

<u>Chapter 5</u> gives the detail study of each of these DCVSL structures, with parameters such as power consumption, temperature, delay, PDP and transistor number. These analysis determines the best DCVSL structures among the three.

<u>Chapter 6</u> uses the three DCVSL structures to implement the adder circuits with each of them. A performance analysis is done with the same parameters used in the previous chapter and helps determine the best DCVSL structure for the adder circuit, as per the power delay product.

<u>Chapter 7</u> – This chapter concludes with the overall work done in this thesis, generalising the best DCVSL structure, whether it may be the structure itself or the implementation of adder circuit with it. This chapter ends the thesis work.

Chapter 2

# **DETAILS** on **DIFFERENTIAL CASCODE VOLTAGE SWITCH LOGIC**

### (2.1) <u>Introduction</u>

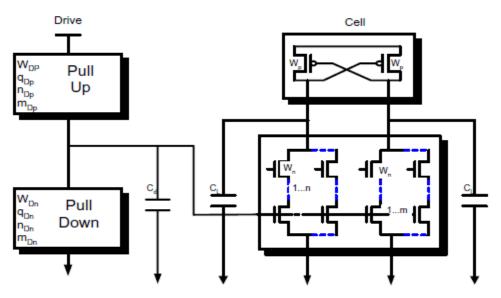

With the advancement in CMOS technology, there is a new interest in designing simple functional units for digital systems. ICs are widely used in consumer electronics, telecommunications and high performance computing. This is to continue with power-efficient VLSI and system designs. CMOS circuits are normally used by digital integrated circuits as building blocks. Power Consumption is a chief worry in VLSI with increasing chip density and operating frequency along with corresponding decreasing feature size. The main setback of portable systems is excessive power dissipation which not only reduces chip life due to overheating but also degrades performance [13], [14]. Portable systems with low power consumption has directed to advanced developments in Low Power VLSI design in current years. The driving forces that are essential for portable devices are low power consumption and high throughput due to their increased complexity, small chip area, large density of components and high frequencies. A DCVS Logic is based on 2:1 Multiplexer which is used as an important element in many various circuit designs such as implementation of memory circuits and FPGA. It is valuable in situations where price is a factor and for modularity. A 2:1 Multiplexer is considered to be the basic building block of the "switch logic". "Switch Logic" basically proposes that logic circuits are implemented not as logic gate but as combination of switches. Multiplexers are used to create a single line from two or more digital signals, by engaging them there at changed times. This is basically known as Time-Division Multiplexing. Multiplexers are used as programmable logic devices, such as in digital video, computer networks and in telecommunications. It is also used in building digital semiconductors such as in graphics controller and in CPUs. The Multiplexers are based on Pass Transistor Logic (PTL) where the transistors are used as voltage controlled switches to implement the logic. The logic is bidirectional and there is no static power dissipation in PTL gates. However, the PTL suffers degradation of its logic at the output by an amount of Threshold Voltage (V<sub>th</sub>). Figure 2 shows the schematic of DCVSL structure which is quite general, along with corresponding drive & also having load and then the output and its complementary output of the gate on both sides.

Figure 2 – DCVSL structure

So, we can see, according to evenness, the loads obtained from the result are equivalent to Lumped Capacitances including both fan-out & interrelated capacitances. The rising delay and falling delay amid the drive's input and the cell's output are shown by [11].

$$De' = (1 + Sf_n)De'_D + (1 + Sf_p)De'_C + De'_C.....(1)$$

$$De' = (1 + Sf_n)De'_D + De'_C.....(2)$$

where  $De_D - driver$  step delay,  $De_C - cell$  step delay, '\' and '/' - rising and falling transistors. Sf<sub>N</sub> and Sf<sub>P</sub> are the N & P's slope factors & its calculation is done by Sakurais Relation [15], where V<sub>TH</sub> is Threshold Voltage of transistor, De<sub>T</sub> is ramp delay;  $\tau$  is the rise/fall time of input and  $\alpha$  is the velocity saturation index.

$$Sf = 2 \left( \frac{1}{2} - \frac{1 - \frac{V_{TH}}{V_{DD}}}{1 + \alpha} \right) \dots \dots (3)$$

$$\alpha = \frac{\left( 1 - \frac{V_{TH}}{V_{in}} \right)}{\left( \frac{1}{2} - \frac{1 - De_T}{\tau} \right)} \dots \dots (4)$$

In DCVSL gates, output which is falling produces the rising output, therefore rising delay always represents the worst case delay. Calculation of rising delay of circuit can be obtained using the above scenario and is shown in the equation [11]:

$$De = \left(1 + Sf_{T_n}\right)De_{D} + \left(1 + Sf_{T_p}\right)De_{C} + De_{C} \dots \dots (5)$$

$$Sf_{T_n} = \frac{Sf_n DM_n(v_n Y_n)}{DM_n(v_n Y_n) - DM_p v_p} \dots (6)$$

$$De_{D} = \frac{v_p}{DM_{D_p}}Y_{D_p}\left(mg_n DM_n + C_D\right)\dots (7)$$

$$De_{C} = \frac{v_p v_n Y_n}{DM_n v_n - 0.5DM_p v_n Y_n} \times \left[\left(gc_p + dc_p\right)DM_p + qd_n DM_n + C_L\right]\dots (8)$$

$$De_{C} = \frac{v_p}{DM_p}\left[\left(gc_p + dc_p\right)DM_p + qd_c DM_n + C_L\right]\dots (9)$$

where  $gc_p$  and  $dc_p$  are represented as gate and diffusion capacitance/unit length in the rising output stage. Solving  $\frac{\partial D'}{\partial W_p} = \frac{\partial D'}{\partial W_n} = 0$  gives us the following set of equations for the optimal DM<sub>p</sub> and DM<sub>n</sub> for the delay minimization [11], [12]:

$$DM_{n}^{'} = \sqrt{A \frac{(1 + Sf_{p}^{'})[C_{L}^{`} + DM_{p}(dc_{p}^{`} + gc_{p}^{`}) + 0.5ADM_{p}d_{n}^{`}]}{(1 + Sf_{n}^{'})Y_{D_{p}}^{'}mg_{n}^{'}/DM_{D_{p}} + qd_{n}^{`}/DM_{p}}} + \frac{1}{2}ADM_{p}.....(10)}$$

$$\frac{1}{\Gamma} = \frac{DM_{n}^{'}}{DM_{p}^{'}} = \sqrt{(1 + Sf_{p}^{'})\left[\frac{1}{2}A^{2}\frac{C_{L}^{`} + qDM_{n}d_{n}^{`}}{C_{L}^{'} + qDM_{n}d_{n}^{'}} + A\frac{W_{n}(dc_{p}^{`} + gc_{p}^{`})}{C_{L}^{'} + qDM_{n}d_{n}^{'}}}\right]} + \frac{1}{2}A.....(11)$$

where  $\Gamma$  is used for minimizing the rising delay as it is the finest width ratio of P to N of MOS structure, S is slope factor, Y is the delay degradation factor, C<sub>L</sub> is the total output capacitance/unit length, g is the gate capacitance/unit length and d is the diffusion capacitance/unit length.  $A = \frac{n}{\sqrt{\mu_n/\mu_p}}$ . With n increasing,

the pull-down network becomes weaker and the theory of delay optimization for the Conventional Logic Style is not applicable to the DCVSL gates directly [7], [11].

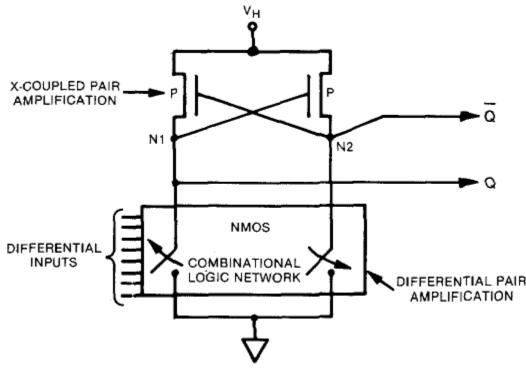

### (2.2) <u>Basic DCVSL Circuit</u>

The DCVSL circuit is illustrated in Figure 3.

Figure 3 - Basic DCVSL circuit

Either the node N1 or the node N2 is pulled down by the NMOS combinational logic tree network which depends on the differential inputs. The PMOS latch is set to the static outputs Q, Qbar of full differential  $V_H$  and ground logic levels by regenerative actions. After the latch sets, the logic trees are being cut-off from direct current. The input gate capacitance loading is a factor of 3X smaller than CMOS circuits which requires a complementary N-channel and P-channel devices to be driven since the NMOS tree devices is driven by the inputs only. Using the existing logic minimization algorithms [5], logic tree networks are

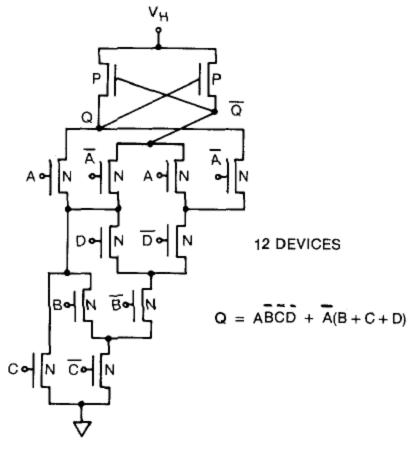

designed spontaneously. Example of DCVSL circuit, having 12 devices is shown in Figure 4. The differential version has six less large P-channel devices & also the input capacitance is small in number.

Figure 4 – CVSL implementation of Q

The functional power of the differential logic trees reduces the device redundancy. Using the similar Boolean function in simple CMOS NAND gates, requires 5 NAND gates and 28 devices, without having additional inverters for the complementary outputs, shown in Figure 5.

The number of circuit delays is reduced in CVSL compared to primitive logic, which enhances the performance leverage of the circuit. The Boolean function Q can also be designed in a cascaded fully CMOS circuit with 16 devices.

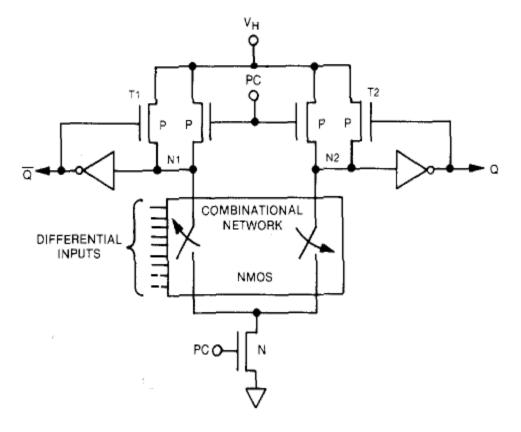

There is a limitation to the circuit's performance in Figure 3 which is considered as the set time for the P mosfet latch. Therefore a high-performance Clocked CVSL circuit is proposed, which is shown in Figure 6.

Figure 6 – Clocked CVSL

When the clock pulse is low, the outputs Q & Qbar are precharged low and as soon as the PC goes high, the data are generated in a domino mode [16]. The internal nodes N1 and N2 are set statically high preceding the switching inside the logic tree by the feedback devices T1 and T2. The feedback devices improves the noise margin with only a little bit of detriment in performance and it also reduces the charge sharing noise within the tree. Either the node N1 or the node N2 is drawn downward during switching & either of the device T1 or the device T2 is shut off. And after switching, there was no direct flow of current. The Clocked DCVSL circuit is inherently a clear benefit over the other partial domino type logic families due to the logic invert function. All the logic functions could be executed including the XOR. A 4-way clocked XOR is in Figure 7.

Figure 7 – Clocked CVSL 4-way XOR

### (2.3) <u>Different Types of DCVSL structures</u>

In this paper, we have explained three types of DCVSL structures -

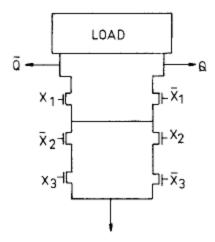

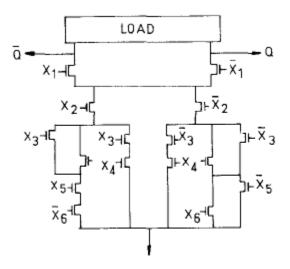

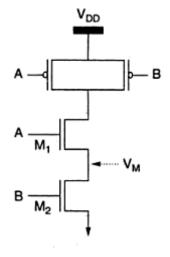

Static DCVSL – It is actually a static version of Differential Cascode Voltage Switch Logic (DCVSL) and is shown in Figure 8.

According to the figure shown above, the nodes OUT and OUTB are either pulled high or low according to the switching of the inputs. The static version of DCVSL transits slowly and it consumes high current since during the switching period, the PMOS pull-ups fight the NMOS pull-down trees. It is the differential style of logic in which the true and complementary inputs to the gate provides the complementary outputs. This structure consumes no static power (like standard CMOS) and it utilizes latch to calculate output rapidly [14], [17], [18]. In this logic style, large PFETS are eliminated from each logic function. It allows complex gates, doesn't need inverter in its logic path and consumes low power. A logic function and

complement of it is inevitably realized [18], [19]. The complementary output is generated by the pull-down network which is implemented by the NMOS logic tree. Therefore, it can be divided into two basic parts – a differential latching circuit and a cascaded complementary logic array [1], [20], [21], [22], [23].

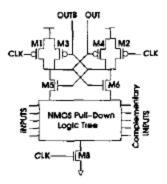

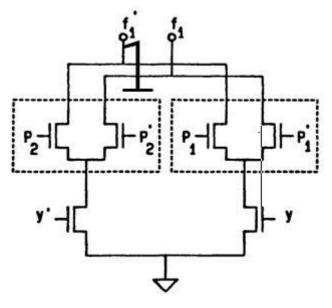

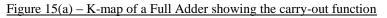

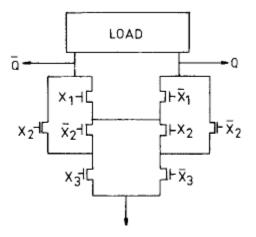

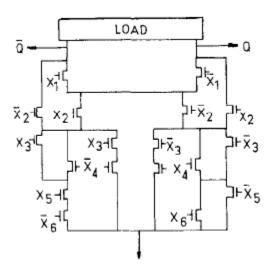

Dynamic DCVSL – Many clocked versions of DCVSL gate was also introduced to increase the performance and reduce the power consumption. Figure 9 shows that

Figure 9 – Dynamic DCVSL

The PMOS pull-up transistors are connected by two complementary NMOS switch structures. By setting the clock low, OUT and OUTB are pre-charged first. The NMOS logic tree determines the true and its complementary output, once the clock goes high and either side is pulled down depending upon the input signals. The gate switches when the positive feedback is applied to the PMOS pull-ups (M3 and M4). With the additional accelerating circuitry (M5 and M6), the performance of the dynamic DCVSL gate is improved. Here are few examples shown in Figure 10.

Modified DCVSL – The modified DCVSL is nothing but the static DCVSL but with extra added NMOS transistors in the pull up part. Chapter 3

# **CIRCUIT TECHNIQUES** for **DCVSL**

### (3.1) <u>Introduction</u>

The algebraic technique is the only prevailing method for the design of DCVS trees which is constructed on the basis of sub-expressions mutual to various Boolean functions which is two or more in number [5]. In this approach, the decomposition and factorization technique is involved which is quite mathematical. Therefore this method doesn't provide the details of circuit behaviour which is important for IC designers. There are other two techniques which is simple and also very practical than the algebraic one, when construction of DCVS trees is to be done. The first procedure is the Karnaugh Map which depicts the pictorial nature. It is a hand-processing method and is a well-organised approach for realizing circuits with low device-count, with functions having five to six variables. Moreover, if the variables increases more than five, then the complexity of K-map suddenly increases. Here comes the second procedure which replaces the first one, due to the advantage of having even routined complexity for variables in terms of n numbers. So the method is Quine-McCluskey method which is also a modified version and also tabular in nature [6]. There is no existence of a unique, one-to-one correspondence between a DCVS tree structure and a Boolean expression [24]. Therefore for realizing specific logic operation, several tree structures can be constructed using the above design procedures. Several of the input variables might be acceptable to rearrange for a given structure.

Therefore for construction of Boolean function of any numbers, one certainly need the help of truth tables which must be accurate too. DCVS structures can be implemented with the two design procedures mentioned here.

### (3.2) <u>Different Techniques</u>

Design by Intuition – DCVS circuits consisting of a couple of interrelated binary decision trees and a push-pull load. It is shown in Figure 11.

Figure 11 - Structure of DCVSL

The DCVS tree is designed as such -

- ✓ Node T and Node T' (considered T in case of Q) is disconnected and associated to ground respectively via some sole conducting path over the trees, when the input vector  $a = (a_1, a_2, ..., a_n)$  {instead of x, a is considered} is the vector which in true in nature of the switching function Q(a).

- ✓ The reverse is obtained when  $a = (a_1, a_2, ..., a_n)$  is the vector which is false in nature of Q(a).

An example is shown in Figure 12.

<u>I Igule 12 Devis Non chedits different way gates</u>

Through analysing all the likely blends of the input paths, the functionality of this circuit can be easily verified. Then also we can verify the circuit by observing the set of unique paths from nodes T and T' to the ground. For Node T, the expression  $T'(a) = a_1a_2 + a_1a_2$  and for Node T', the expression  $T(a) = a_1a_2 + a_1a_2$

For Boolean functions with a recursive nature, the DCVS tree can sometimes be created effortlessly by perception. Example such as, a 3-way XOR tree (Figure 12(b)) can be implemented by replacing the  $a_2, a_2$  couple in (Figure 12(a)) with alternative 2-way XOR tree. The n-way XOR tree is shown in Figure 12(c), which is having a stacking height equal to n.

Boolean functions with recursive nature can also be shown in carry-look ahead circuit [25]. Given the recursive expression –

$$cla_n = s_n + t_n cla_{n-1}$$

(for n = 1, 2, 3,....),

a circuit with cla<sub>n</sub> and  $cla'_n$  (considered instead of c<sub>n</sub> and  $c'_n$ ) as outputs, with input vector equal to  $(s_n, s'_n, ..., s_1, s'_1, t_n, t'_n, ..., t_1, t'_1, cla_0, cla'_0)$  {considered instead of  $(g_n, g'_n, ..., g_1, g'_1, p_n, p'_n, ..., p_1, p'_1, c_0, c'_0)$  }. First of all, the function  $cla_1 = s_1 + t_1 cla_0$  is realized as the circuit in Figure 13(a), and is the basic circuit for recursion. The general structure for cla<sub>n</sub> with stacking height equal to 2n+1 is shown in Figure 13(b).

<u>Figure 13(a) – Function</u>  $cla_1 = s_1 + t_1 cla_0$  for DCVS circuit

<u>Figure 13(b) – Recursive DCVS structure for function</u>  $cla_n = s_n + t_n cla_{n-1}$

It is easy to construct the DCVS tree network, for Boolean expressions consisting of only a few product terms. Considering a simple function S (considering P as S) =  $a_1a_2...a_n$ ; the corresponding structure and its symbolic representation are shown in Figure 14(a).

Figure 14(a) – The DCVS tree with symbolic representation for the function  $S = a_1 a_2 \dots a_n$

Using the above figure as basic building block, we can construct numerous complex functions.

$$i_1 = R_1 y + R_2 y$$

$$i_2 = R_1 + R$$

where the variable R's (considered instead of P) are two different product terms, and the variable y's are literals. The structures are shown in Figure 14(b) and Figure 14(c).

Figure 14(b) – For the function  $i_1$

Figure 14(c) – For the function  $i_2$

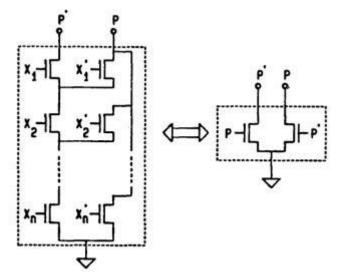

► <u>**K-map Procedure**</u> – The DCVS tree's input variable is represented by  $q_i$ , for i = 1, 2, ..., n, where there is a variable  $q_i$  and also the complement  $q'_i$ . Also the set P is represented by a cube, where  $q_i \in P$  represents  $q_i \notin P$ .

In a K-map which is having n number of variables, there are  $2^n$  boxes and each which is having exactly n literals represents a cube. Boxes containing 0's are called 0-boxes (similarly, 1-boxes). A 0-loop encircling two adjacent 0-boxes containing a cube which is having literals but one less in number than each of the cubes signifying the original 0-box (same for 1-loop). If we consider two rectangular 0-loops, which is adjacent to K-map and is consisting  $2^i$  0-boxes. The 0-loops expresses cubes, say  $Cx_k andCx'_k$ , and we get a new rectangular 0-loop consisting  $2^{i+1}$  0-boxes with combination of two 0-loops and the new 0-loop which is expressing cube C (which is same for 1-loops).

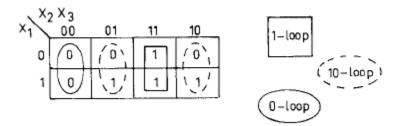

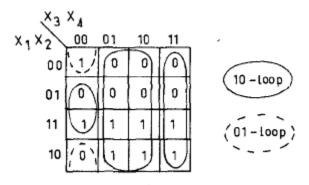

Here is an example introducing the K-map algorithm, which exhibits certain ideas, given the Boolean function S (considered instead of Q) =  $x_1x_2+x_2x_3+x_3x_1$  (representing the FA's carry function), constructing the Differential Cascode Voltage Switch Logic. Figure 15(a) shows the K-map.

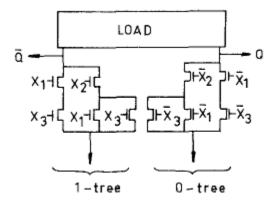

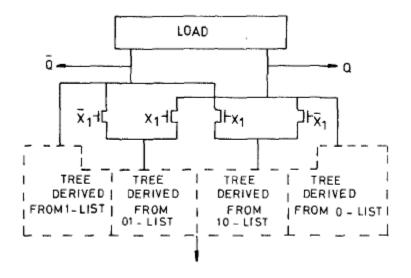

Figure 15(b) - DCVS implementation on Full Adder representing carry-out

The 0-loops and 1-loops are surrounded appropriately to represent the marginal cover for both the loops. The Figure 15(b) represents the subsequent DCVS tree pair. The tree which is committed to Node T (T instead of Q) is called the 0-tree and is derived from 0-cells. Similarly, for the node T' representing 1-cells and is derived from 1-cells. But both the trees are disjointed because both the cells are grouped separately. To realize the function S, this DCVS circuit requires 10 N-devices. Apart from constructing the two disjointed 0 and 1 trees, it does a lot more. Maximum commonality is allowed between the trees for its discovery. A 'shared' structure can be developed which leads to the minimization of device count.

Taken into consideration, if a 0-box (1-box) which is representing cube  $x_1R$  and 1-box (0-box) representing  $x_1R$  exist concurrently, then the cell representing the cube R can be demarcated as a 10-box (01-box). These 01 or 10-boxes are treated as separate boxes of dissimilar forms. When two or more contiguous 01-cells (10-cells) are being encircled, then a 01-loop (10-loop) is formed.

Let's revisit the previous example, with these new concepts added. See the Figure 16(a), where three types of encirclements are there, as 0-loop, 1-loop and 10-loop.

Figure 16(a) - K-map with different encirclements than the Figure of 15(a)

The 'shared' tree with 10-loops is first constructed in Figure 15(b).

Figure 16(b) – DCVS tree with implementation on 10-loops

The complete DCVS tree with branches 0-loop and 1-loop are added and shown in Figure 16(c).

Figure 16(c) – Complete DCVS tree

Here only 8 N-devices are essential, and it is two devices less than disorganised tree which is shown in Figure 15(b). But the quantity of the levels which are stacked is amplified by 3.

The K-map procedure has 4 steps:

• Identify the 4 different types of cells, 0-boxes, 1-boxes, 01-boxes & 10-boxes.

• The marginal cover for all the 01-boxes are found out. Then the tree is constructed equivalent to marginal envelope. With magnitude i in ascending order, the variables  $x_i$  are arranged from top to bottom in each of the tree branches. The construction of tree branches is done according to the size of the loops, starting with small size loop. The control inputs which are of top pair are  $y'_1$  related with Node T' and  $y_1$

which is associated with Node T. Gate inputs  $y_1$  and  $y'_1$  having the sources of the transistors are always connected together.

• A minimal cover is found out from the prime implicates of all the 10-cells such that the tree which is constructed may share some of the branches with the one in the second step.  $y_1$  which is related with Node T' and  $y'_1$  which is related with Node T are the top pair of control inputs according to the second step.

• Then, a minimal cover is found out for the remaining 0-cells and 1-cells. The sharing of tree branches is always looked out for, while constructing the tree. The Node T (Node T') are connected to base of 0-tree (1-tree).

If  $y_i$ 's are rearranged (e.g. the variables  $y_1$  and  $y_2$  are inter-changed), the above technique might generate altered tree structures. Also to share tree branches and to choose minimal cover, there may be several ways to choose.

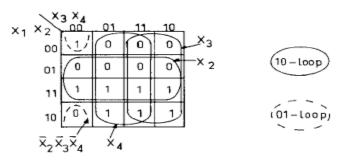

A 4-variable K-map is in Figure 17(a) and the first two steps are applied to generate the tree structure in Figure 17(b).

<u>Figure 17(a) – K-map with function Q =  $y_1y_2y_3y_4 + y_1(y_2 + y_3 + y_4)$  showing 01 and 10-encirclements</u>

Figure 17(b) – DCVS circuit representing 01-loop

The complete DCVS tree is generated by applying step (3) and is shown in Figure 17(c).

Figure 17(c) – Complete DCVS tree

There is no remaining 0-cells and 1-cells, therefore step (4) has been skipped.

Here is another example, where a changed method of encompassing K-map is in Figure 18(a), which points to an altered structure shown in Figure 18(b).

In some tree branches, the levels which are stacked gets incremented since the 10-cells are not covered marginally in this demonstration. This adverse article, in combination with huge parasitic capacitances which is also linked with several shared source and drain connections, indicates 18(b) has inferior electrical performance than that of Figure 17(c).

If a DCVS is having levels which are stacked and is more than 6, then the presentation might be degraded, the reason might be that the parasitic source & drain capacitances keeps on charging & also along with it discharges too, having transistors with long chains. Therefore it is much better to divide DCVS circuits having 5 or less variables when the logic is complicated, for circuits where speed is required. In this case, the design procedure is very useful.

**Tabular Method** – Quine-McCluskey Method is used in this tabular method where the prime implicants and the minimal covering set are found out [6]. A list is provided where it is consisting of two fields, viz. the input vector  $(y_1, ..., y_n)$  {y taken instead of x} on the right and left is having decimal portrayal which is shown in Table 1.

| Decimal representation<br>of input vector | Input vector                                                   |              |

|-------------------------------------------|----------------------------------------------------------------|--------------|

| - input vector                            | $\mathbf{x}_1 \mathbf{x}_2 \cdots \mathbf{x}_n$                |              |

| e.g.<br>1<br>4                            | 0 0 1<br>1 0 0                                                 | } Record i   |

| 3<br>6                                    | $\begin{smallmatrix} 0 & 1 & 1 \\ 1 & 1 & 0 \end{smallmatrix}$ | } Record j>i |

|                                           |                                                                |              |

Table 1 – The list format for Tabular Method

The input vectors are arranged in a rising order of their index (number of 1's in binary representation) and are grouped into records. We start with a 0-list (list containing 0's) and a 1-list (list containing 1's) of the functions. Two other lists are also generated from the above two lists' namely, 10-list and 01-list. This procedure is same as the generation of 01-boxes and 10-boxes from the 0-boxes and 1-boxes, in the K-map method. The choice of marginal envelope from the 1-list, 0-list, 01-list and 10-list by the modified Quine-McCluskey method yields a DCVS structure which is in Figure 19.

Figure 19 – The basic DCVS tree structure developed from Table 1

The Tabular method consists of five procedures -

• The 1-list is drawn with vectors which are true  $(y_1, ..., y_n)$  of f(Q). Then the list is split into accounts containing growing i from topmost to lowermost. Thereafter, the 0-list is drawn containing vectors which are false of f(Q) and also increasing i from top to bottom.

• For i which is from 1 to n;

In the 1-list, rows which are beginning with  $y_1 = 1$  within account i is matched with rows which is within record i-1 of the 0-list. Considering the degraded vector ( $y_2$ , ...,  $y_n$ ) of two rows are same, then the 1-list and the 0-list are checked correspondingly & a new row is added to 10-list. The arrangement of 10-list is a bit altered, which is in Table 2. The variable  $x_1$  is not required anymore.

| Decimal representation<br>of reduced input vector | Reduced input vector                         |   |        |     |

|---------------------------------------------------|----------------------------------------------|---|--------|-----|

| of reduced input vector                           | x <sub>2</sub> x <sub>3</sub> x <sub>n</sub> |   |        |     |

| e.g.                                              |                                              |   |        |     |

| 1                                                 | 0 1                                          |   | Record | 1   |

| 2                                                 | 1 0                                          | ſ |        |     |

| 3                                                 | 1 1                                          | } | Record | j>i |

| ·                                                 | •                                            |   |        |     |

| · ·                                               |                                              |   |        |     |

|                                                   |                                              |   |        |     |

| · .                                               | •                                            |   |        |     |

#### Table 2 – Format of 10-list

#### • For i = 0 to n-1;

For the 1-list, the rows which is starting with  $y_1 = 0$  within account i is matched with the rows of the 0-list which is starting with i+1. Here also, considering the degraded vector  $(y_2, ..., y_n)$  of the two rows are same,

then the two rows in the 0-list and 1-list are checked correspondingly & a new row is added to 01-list. Both the formats of 01-list and 10-list are same.

• The Quine-McCluskey Method is applied to the rows in the 01-list and 10-list for finding the prime implicants. The marginal cover set is selected for each of the two lists by row and column supremacy measures, and while constructing the corresponding trees the maximum amount of sharing of tree branches is looked out for. Thus, a 'shared' is built.

• For selecting a minimal cover set, a conventional procedure is applied for abandoned rows in the 0list and 1-list. Then the trees are constructed according to these two marginal sums, by addition of more branches to the tree which is 'shared'. By this way, a DCVS structure is constructed which is shown in Figure 19.

3-Bit Magnitude Comparator designed is considered by Tabular Method. The circuit equates between binary numbers,  $A=A_3A_2A_1$  &  $B=B_3B_2B_1$ , and which also gives an output Q=1, whenever A>B. The variables (y<sub>1</sub>, y<sub>2</sub>, y<sub>3</sub>, y<sub>4</sub>, y<sub>5</sub>, y<sub>6</sub>) are equal to (A<sub>3</sub>, B<sub>3</sub>, A<sub>2</sub>, B<sub>2</sub>, A<sub>1</sub>, B<sub>1</sub>). A dissimilar duty will lead to altered structure.

From the initial step, we tabulate the 0-list (36 rows) and 1-list (28 rows). Then when the second stage is completed, a 10-list is drawn as shown in Table 3.

| Decimal representation<br>of reduced input vector | Red                   | uced                       | Inp                   | ut v                       | ector                 |

|---------------------------------------------------|-----------------------|----------------------------|-----------------------|----------------------------|-----------------------|

| of reduced input vector                           | <b>x</b> <sub>2</sub> | x <sub>3</sub>             | x4                    | x <sub>5</sub>             | × <sub>6</sub>        |

| 0                                                 | 0                     | 0                          | 0                     | 0                          | 0                     |

| 4<br>1                                            | 0<br>0                | 0<br>0                     | 1<br>0                | 0<br>0                     | 0<br>1                |

| 5<br>6<br>12<br>3<br>24<br>18                     | 0<br>0<br>0<br>1<br>1 | 0<br>0<br>1<br>0<br>1<br>0 | 1<br>1<br>0<br>0<br>0 | 0<br>1<br>0<br>1<br>0<br>1 | 1<br>0<br>1<br>0<br>0 |

| 7<br>13<br>25<br>26                               | 0<br>0<br>1<br>1      | 0<br>1<br>1<br>1           | 1<br>1<br>0<br>0      | 1<br>0<br>0<br>1           | 1<br>1<br>1<br>0      |

| 15<br>27<br>30                                    | 0<br>1<br>1           | 1<br>1<br>1                | 1<br>0<br>1           | 1<br>1<br>1                | 1<br>1<br>0           |

Table 3 – The 10-list of a 3-bit Magnitude Comparator

The third step doesn't generate any 01-list. From the fourth step, a prime implicant table is obtained from the 10-list which is shown in Table 4 and these prime implicants actually form a marginal envelope.

| Decimal<br>prime representation<br>implicants         | 0 | 1 | 3 | 4           | 5                          | 6 | 7           | 12 | 13 | 15 | 18 | 24 | 25 | 26     | 27 | 30 |

|-------------------------------------------------------|---|---|---|-------------|----------------------------|---|-------------|----|----|----|----|----|----|--------|----|----|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$  |   |   |   |             |                            |   |             |    |    |    | x  |    |    | x<br>x |    | x  |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | x | x | x | x<br>x<br>x | x<br>x<br>x<br>x<br>x<br>x | x | x<br>x<br>x | x  | x  | x  |    | x  | x  | x      | x  |    |

Table 4 – Prime implicant table of the 10-list

The 'shared' tree is shown in Figure 20.

Figure 20 – The tree circuit with the 10-list

From the fifth step, the abandoned rows of the 0-list and 1-list results in Table 5 and Table 6.

| Decimal representation |            | Inpu | it Ve | ctor           |    |                |

|------------------------|------------|------|-------|----------------|----|----------------|

| of input vector        | <b>x</b> 1 | x2   | x3    | x <sub>4</sub> | ×5 | × <sub>6</sub> |

| 1                      | 0          | 0    | 0     | 0              | 1  | 0              |

| - 8                    | 0          | 0    | 1     | 0              | 0  | 0              |

| 9                      | 0          | 0    | 1     | 0              | 0  | 1              |

| 10                     | 0          | 0    | 1     | 0              | 1  | 0              |

| 40                     | 1 1        | 0    | 1     | 0              | 0  | 0              |

| 34                     | 1          | 0    | 0     | 0              | 1  | 0              |

| 11                     | 0          | 0    | 1     | 0              | 1  | 1              |

| 14                     | 0          | 0    | 1     | 1              | 1  | 0              |

| 41                     | 1          | 0    | 1     | 0              | 0  | 1              |

| 42                     | 1          | 0    | 1     | 0              | 1  | 0              |

| 43                     | 1          | 0    | 1     | 0              | 1  | 1              |

| 46                     | 1          | 0    | 1     | 1              | 1  | 0              |

Table 5 – The 1-list and its minimal sum for the Magnitude Comparator

| Decimal representation<br>of input vector |     |                | Inp                   | Input vector   |    |                |                |  |  |

|-------------------------------------------|-----|----------------|-----------------------|----------------|----|----------------|----------------|--|--|

| or input vector                           |     | x <sub>1</sub> | <b>x</b> <sub>2</sub> | x <sub>3</sub> | x4 | x <sub>5</sub> | х <sub>б</sub> |  |  |

| 16                                        |     | 0              | 1                     | 0              | 0  | 0              | 0              |  |  |

| 20                                        | -   | 0              | 1                     | 0              | 1  | 0              | 0              |  |  |

| 17                                        |     | 0              | 1                     | 0              | 0  | 0              | 1              |  |  |

| 48                                        | 1   | 1              | 1                     | 0              | 0  | 0              | 0              |  |  |

| 21                                        |     | 0              | 1                     | 0              | 1  | 0              | 1              |  |  |

| 22                                        | 1   | 0              | 1                     | 0              | 1  | 1.             | 0              |  |  |

| 28                                        | Į   | 0              | 1                     | . 1            | 1  | 0              | 0              |  |  |

| 19                                        |     | 0              | 1                     | 0              | 0  | 1              | 1              |  |  |

| 52                                        |     | 1              | 1                     | <u>o</u>       | 1  | 0              | 0              |  |  |

| 49                                        |     | 1              | 1.                    | 0              | 0  | 0              | 1              |  |  |

| 29                                        | 1   | 0              | 1                     | 1              | 1  | 0              | -1             |  |  |

| 23                                        |     | 0              | 1                     | 0              | 1  | 1              | 1              |  |  |

| 53                                        |     | 1              | 1                     | 0              | 1  | 0              | 1              |  |  |

| 54                                        | 1   | 1              | 1                     | 0              | 1  | 1              | 0              |  |  |

| 60                                        | · · | 1              | 1                     | 1              | 1  | 0              | 0              |  |  |

| 51                                        |     | 1              | 1                     | 0              | 0  | 1              | 1              |  |  |

| 31                                        |     | 0              | 1                     | 1              | 1  | 1              | 1              |  |  |

| 61                                        |     | 1              | 1                     | 1 .            | 1  | Ő.             | 1              |  |  |

| 55                                        |     | 1              | 1                     | 0              | 1  | 1              | 1              |  |  |

| 63                                        | 11  | 1              | 1                     | 1              | 1  | 1              | 1              |  |  |

Table 6 - The 0-list and its minimal sum for the Magnitude Comparator

The equivalent marginal sums done by the Quine-McCluskey Method are specified and the complete DCVS is shown in Figure 21.

Figure 21 – 3-bit Magnitude Comparator.

Chapter 4

# **TESTING SCHEMES** on **DCVSL STRUCTURES**

There is a concept in the most structured design practices that with some additional circuitry, all the memory elements in an IC can be threaded together into a shift register. A control switch is able to switch the memory elements to shift register mode from their normal modes of operation and that is when the current state of IC is frozen and shifted out for examination. Level-Sensitive Scan Design (LSSD) is IBM's discipline for structured design for testability. Here, the term 'Scan' refers to the ability for any network to shift into or out of any state and the term 'Level-Sensitive' indicates to the logic depth, circuit excitation and handling of clocked circuitry. The key element in the design is the 'shift register latch' (SRL), which is being implemented in DCVS Logic [26].

The self-testing property of DCVS trees is described through a different scheme [2]. Due to the presence of complementary outputs for every tree, the DCVS circuit has unique property of online testability. This provides us with stuck-at and dynamic fault coverage (e.g., due to alpha particles or power glitches).

Differential paths from two nodes (Q and Qbar) are produced by a DCVS tree, which is represented by an ordered pair (Q,Q<sup>2</sup>) to ground. According to fault-free operation, only one of the two paths to ground is active, which produces a legal (code space) output (1,0) or (0,1). For a faulty operation, the output changes state from one legal state to an illegal (non-code space) state such as (0,0) or (1,1) [2]. Thus, the presence of fault in the tree is clearly indicated by the detection of an illegal state at the output of any tree. This is called the self-testing property of DCVS trees.

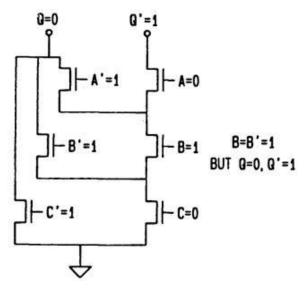

A DCVS tree also has another property called the fault-secure property, which describes that any single illegal input to a functioning tree causes the tree to produce either an illegal output or correct output [2]. In spite of the DCVS tree having one of its inputs in an illegal state, it can produce correct legal output provided if its output is independent of other illegal input. An example of 3-input NAND gate is shown in Figure 22.

Figure 22 – 3-input NAND gate with illegal inputs

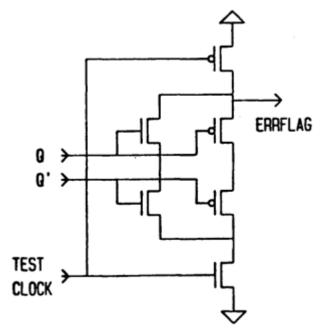

To increase the error observability, we can place the illegal state detector at the outputs of internal DCVS trees rather than placing them only at the latches of logical block boundaries. Thus the illegal state detector can be a XOR circuit shown in Figure 23. Whenever (Q,Q') is equal to (0,0) or (1,1), the 'error flag' is pulled down.

Figure 23 – Illegal state detector for DCVS trees

Chapter 5

# Performance Analysis of DCVSL Structures

A comparison of all the three DCVSL structures are shown in this following section, with parameters such as Temperature, Voltage, Power Consumption, Delay and Power Delay Product. All the analysis shows that the proposed structures shows better result in terms of power consumption than the conventional ones. But the delay is comparatively a bit more for the proposed structure than the conventional one. So, for scheming a 'faster' digital gate, one generally requires a better power plus for designing a gate to lower power consumption, the digital device is slowed down. Therefore, both way there is a hindrance and so propagation delay and power dissipation generally form a design trade off, i.e. you improve one and the other is degraded. To quantify how effective, or efficient a digital design is in terms of delay and power, a product of both propagation delay and power dissipation is used. Hence, the term PDP. The DCVSL structures are based on the 2:1 Multiplexer. Here is the Truth Table of 2:1 Multiplexer shown in Table 7.

| S | A | В | Z |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Table 7 – Truth Table of 2:1 Multiplexer

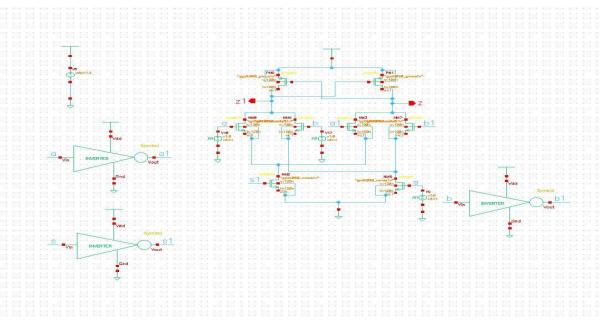

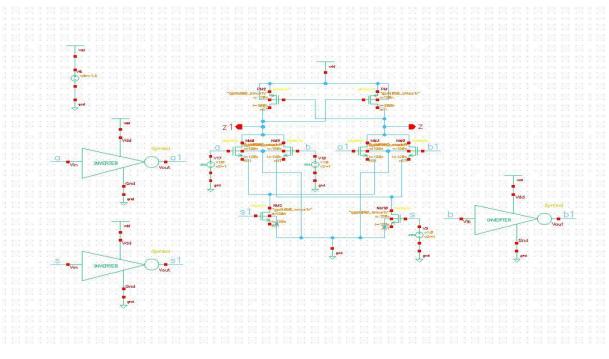

In all the DCVSL Structures, there are three inputs, namely (a, b, s). 'a' and 'b' are the two inputs of a multiplexer, and 's' is the select line. 'z' and 'z1' are the outputs, where 'z1' is the complementary output of z. Similarly, 'a1', 'b1' and 's1' are the complementary inputs which is provided by the inverter. Vpulse from Cadence Virtuoso is used to supply voltage to the three inputs, where V1 is 0V and V2 is 1V. The supply voltage is varied from 1V to 1.4V for all the DCVSL structures on the basis of which analysis is done, starting from Static DCVSL, then Dynamic DCVSL and ending with Modified DCVSL.

For the input 'a', the 'Period' is kept at 44ns and the 'Pulse Width' is kept at 22ns. For the input 'b', the 'Period' is kept at 23ns and the 'Pulse Width' is kept at 11ns. For the input 's', the 'Period' is kept at 10ns and the 'Pulse Width' is kept at 5ns.

#### (5.1) <u>Static DCVSL</u> –

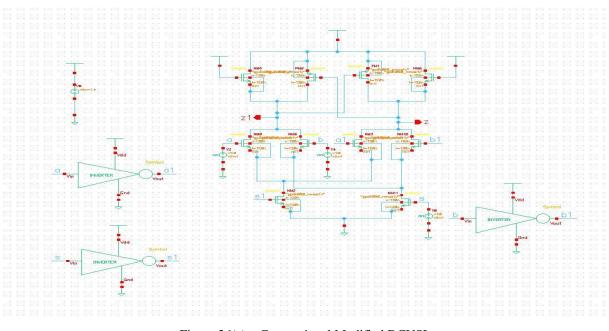

Figure 24(a) – Conventional Static DCVSL

There are 2 PMOS and 6 NMOS in the main DCVSL Structure. Considering the three inverters, the PMOS count goes up to 5 PMOS and 9 NMOS. Here, the W/L ratio of each transistor is kept at 120nm/120nm, i.e. 1:1. Whereas, the transistors within the inverter is kept at – for PMOS, it is 240nm/120nm, i.e. 2:1 and for NMOS, it is 120nm/120nm, i.e. 1:1. Moreover, in conventional structure, for the DCVSL portion; out of the 6 NMOS, the above 4 NMOS's body are connected to the source of the NMOS but the source of the NMOS is not connected to the ground and is internally connected to other NMOS's source. The rest 2 NMOS's body are connected to the source, which is ultimately connected to the ground. For PMOS, the body and the source are connected to V<sub>DD</sub>.

Figure 24(b) – Proposed Static DCVSL

In the proposed design, the PMOS's (W/L) ratio is kept at 120nm/300nm, i.e. 2.5:1 and NMOS's (W/L) ratio is kept at 120nm/120nm, i.e. 1:1. Here, the above 4 NMOS's body are connected to the ground and the rest 2 NMOS's body are connected to the source, which is ultimately connected to the ground. For PMOS, the body's and source's connection is done to the  $V_{DD}$ .

The transient responses for both the conventional and proposed circuits are shown below, with varying Voltages from 1V to 1.4V.

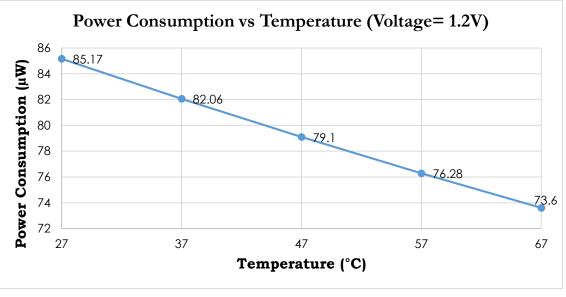

Between the conventional and proposed Static DCVSL circuits, a comparison is done between the power consumption and temperature, varying the Voltage from 1V to 1.4V. The comparison shows better results for the proposed DCVSL circuit, in terms of power consumption.

Figure 27(e) – Power Consumption vs Temperature (1.4V)

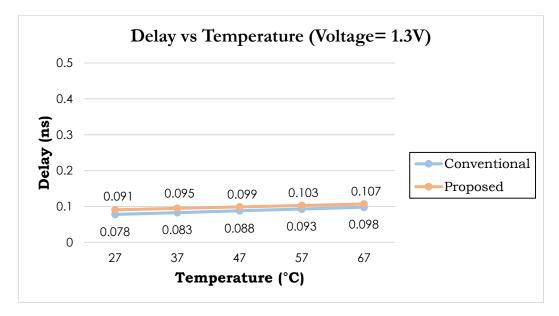

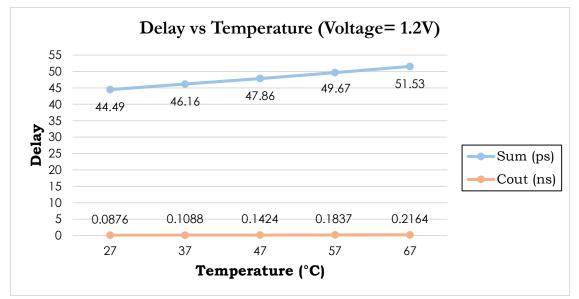

Now, we compare between the delay and temperature.

Figure 28(a) – Delay vs Temperature (1V)

Figure 28(b) – Delay vs Temperature (1.1V)

Figure 28(c) – Delay vs Temperature (1.2V)

Figure 28 (d) – Delay vs Temperature (1.3V)

Figure 28(e) – Delay vs Temperature (1.4V)

Here, the delay is a bit more for the proposed DCVSL circuit.

Figure 29 - Power Delay Product vs Voltage

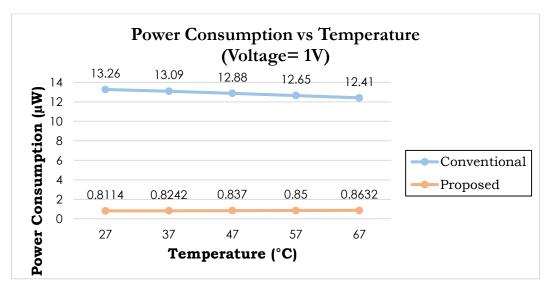

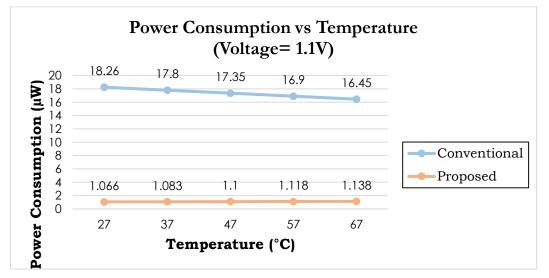

## > (5.2) <u>Dynamic DCVSL</u> –

There are 4 PMOS and 9 NMOS in the DCVSL structure. Apart from that, there are 3 inverters, which constitutes 1 PMOS and 1 NMOS each, which accounts to 3 PMOS and 3 NMOS in total. The PMOS is having (W/L) = 240nm/120nm, i.e. 2:1 in ratio, whereas the NMOS is having (W/L) = 120nm/120nm, i.e. 1:1 in ratio. In Dynamic DCVSL, a clock is also used which is the input of the gate to 2 PMOS and 1 NMOS. The clock is having a delay of 10ns. Here, out of the 4 PMOS, 2 extreme PMOS having clock as the input to the gate is also having the bodies of both of them connected to the V<sub>DD</sub>. The other two PMOS having their bodies connected to the drain of it and also internally connected to the gate of the intermediate NMOS and to the gate of the other two PMOS. Two intermediate NMOS are used here, which is having their body connected to the source of it, but the source is not connected to the ground but to the drains' of the other NMOS, two for each. Except the NMOS having clock as the input, the rest of the NMOS are having their body connected to the source which are not connected to the ground.

Figure 30(b) – Proposed Dynamic DCVSL

Here, the body of all the PMOS of the DCVSL structure are connected to the source which is ultimately connected to the  $V_{DD}$ . Same way, the body of all the NMOS of the DCVSL structure are connected to the source which in turn is connected to the ground. The (W/L) ratio of all the PMOS are 120nm/180nm, i.e. 1/1.5 whereas the (W/L) ratio for all the NMOS are 120nm/100nm, i.e. 1.2/1.

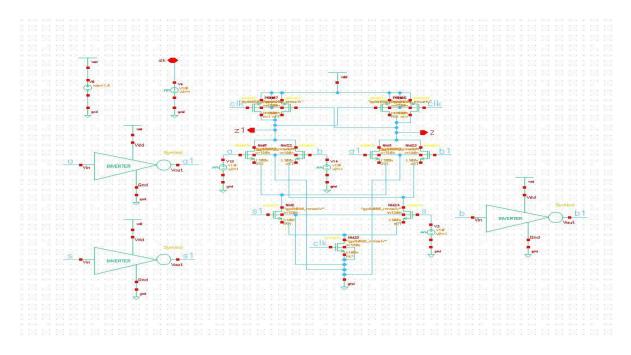

The transient responses for both the conventional and proposed circuits are shown below, with varying Voltages from 1V to 1.4V.

Figure 30(c) and 30(d) – Conventional (1.2V) and (1.3V)

Figure 30(e) – Conventional (1.4V)

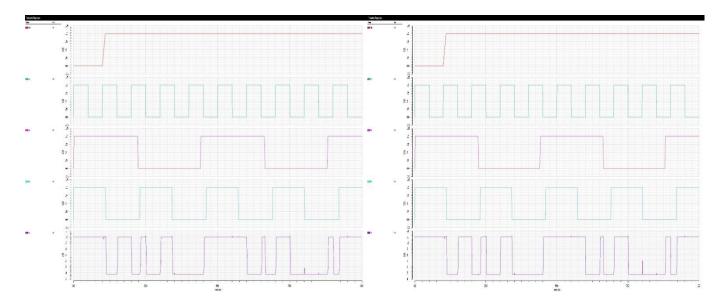

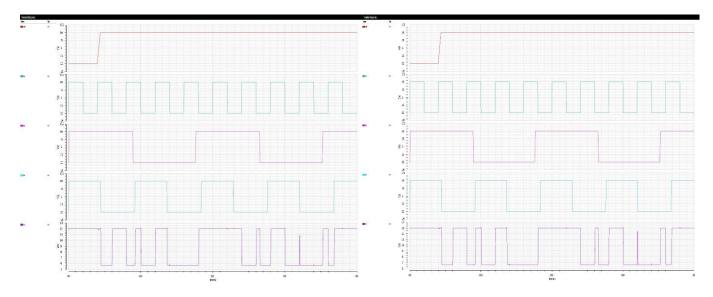

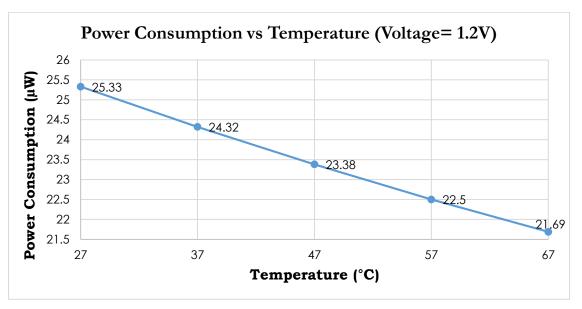

Between the conventional and proposed Dynamic DCVSL circuits, a comparison is done between the power consumption and temperature, varying the Voltage from 1V to 1.4V. The comparison shows better results for the proposed DCVSL circuit, in terms of power consumption.

Figure 33(a) – Power Consumption vs Temperature (1V)

Figure 33(b) – Power Consumption vs Temperature (1.1V)

Figure 33(e) – Power Consumption vs Temperature (1.4V)

15.18

57

15.1

67

Conventional

Proposed

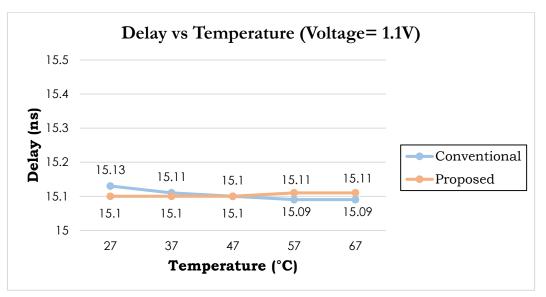

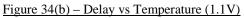

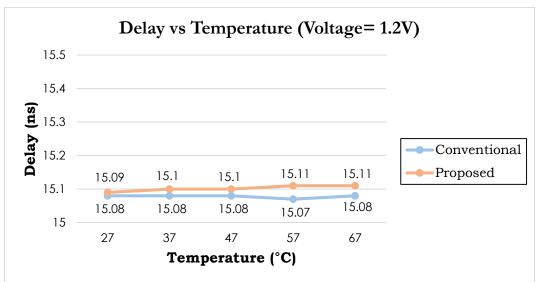

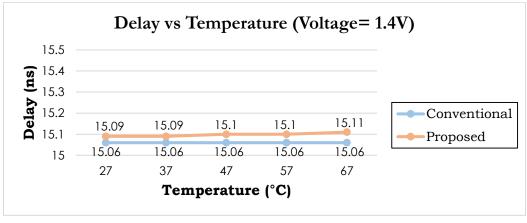

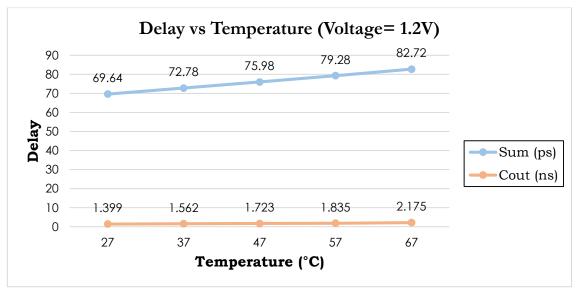

Now, we compare between the delay and temperature.

15.48

27

15.37

37

15.27

47

Temperature (°C)

30

25

20

15 10

Figure 34(a) – Delay vs Temperature (1V)

Figure 34(c) – Delay vs Temperature (1.2V)

Figure 34(d) – Delay vs Temperature (1.3V)

Figure 34(e) – Delay vs Temperature (1.4V)

Here, the delay is a bit more for the proposed DCVSL circuit, in most of the cases.

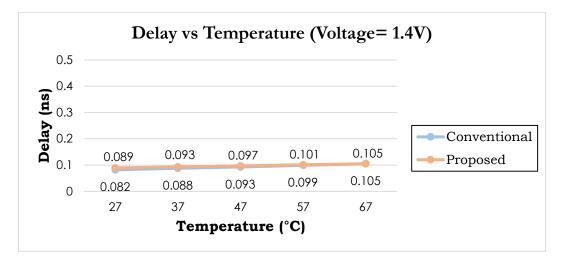

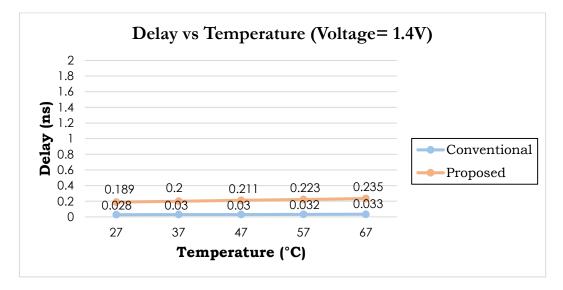

Figure 35 – Power Delay Product vs Voltage

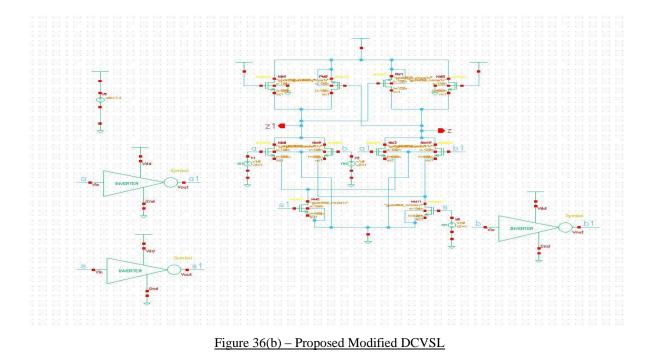

### > (5.3) <u>Modified DCVSL</u> –

Here, there are 2 PMOS and 8 NMOS. 2 NMOS are equivalent to 2 PMOS. These 2 NMOS are having  $V_{DD}$  at the gates and the body connected to the source of it, which in turn is connected to the drain of its parallel PMOS. The gates of these 2 PMOS are connected to the outputs. The rest NMOS are same way connected to the source of it, without its connection being done with the ground. All the transistors within the DCVSL structure are having their (W/L) ratio as 1:1, since it is 120nm/120nm.

In the proposed circuit, the 2 NMOS equivalent to 2 PMOS are having their body grounded. And rest of the other 6 NMOS are having their body grounded too. Here, the (W/L) ratio is kept at 1:1.5, i.e. 120nm/180nm for the PMOS and for NMOS, it is 1:1, i.e. 120nm/120nm.

The transient responses for both the conventional and proposed circuits are shown below, with varying Voltages from 1V to 1.4V.

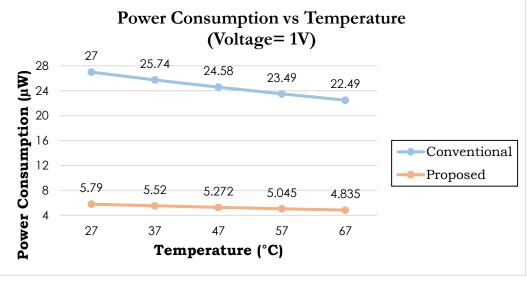

Between the conventional and proposed Modified DCVSL circuits, a comparison is done between the power consumption and temperature, varying the Voltage from 1V to 1.4V. The comparison shows better results for the proposed DCVSL circuit, in terms of power consumption.

Figure 39(a) – Power Consumption vs Temperature (1V)

Figure 39(b) – Power Consumption vs Temperature (1.1V)

Figure 39(c) – Power Consumption vs Temperature (1.2V)

Figure 39(d) – Power Consumption vs Temperature (1.3V)

Figure 39(e) – Power Consumption vs Temperature (1.4V)

Now, we compare between the delay and temperature.

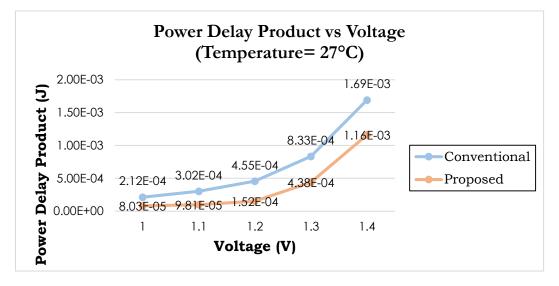

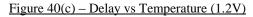

Figure 40(b) – Delay vs Temperature (1.1V)

Figure 40(d) – Delay vs Temperature (1.3V)

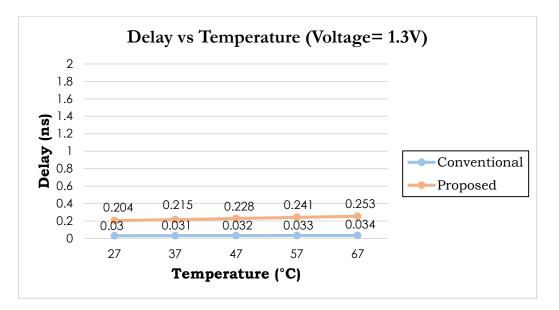

Figure 40(e) – Delay vs Temperature (1.4V)

The delay is a bit more for the proposed circuit.