# Design and Development of Advanced Control strategies for Power Quality Enhancement at Distribution Level

Rajesh Kumar Patjoshi

Department of Electronics and Communication Engineering

National Institute of Technology

Rourkela-769008

2015

# Design and Development of Advanced Control strategies for Power Quality Enhancement at Distribution Level

A Thesis submitted in partial fulfillment of the requirements for the degree

of

## **Doctor of Philosophy**

in

## **Electronics and Communication Engineering**

By

Rajesh Kumar Patjoshi

Roll: 510EC907

**Under the Supervision of**

Prof. Kamalakanta Mahapatra

National Institute of Technology Rourkela-769008 (ODISHA) 2015

## **CERTIFICATE**

This is to certify that the thesis entitled "Design and Development of Advanced Control Strategies for Power Quality Enhancement at Distribution Level", submitted to the National Institute of Technology, Rourkela by Mr Rajesh Kumar Patjoshi, bearing Roll No. 510EC907 for the award of the degree of Doctor of Philosophy in Department of Electronics and Communication Engineering, is a bonafide record of research work carried out by him under my supervision.

The candidate has fulfilled all the prescribed requirements.

The thesis is based on candidate's own work, has not submitted elsewhere for the award of degree/diploma.

In my opinion, the thesis is in standard fulfilling all the requirements for the award of the degree of **Doctor of Philosophy** in Electronics and Communication Engineering.

## Prof. Kamalakanta Mahapatra

**Supervisor**

Department of Electronics and Communication Engineering

National Institute of Technology, Rourkela, 769008

Odisha (INDIA)

Dedicated to

My Nation

**ACKNOWLEDGEMENTS**

I would like to express my deepest gratitude towards my supervisor, Professor Kamalakanta

Mahapatra for his generous support and supervision, and for the valuable knowledge that he

shared with me. I learned valuable lessons from his personality and his visions.

I am also grateful to my Doctoral Scrutiny Committee Members, Dr. (Prof.) Sukadev Meher,

Dr. (Prof.) Sanjay Kumar Jena, and Dr. (Prof.) Dipti Patra.

I am thankful to Prof. Ayaskanta Swain, Mr. Prafulla K. Patra, Mr. Jaganath Mohanty, Mr

Sauvagya R. Sahoo, Mr. George Tom Varghese, Mr. K.V Ratnam, Mr. Sudheendra Kumar,

Mr. V. Ramakrishna, Mr. Govind Rao, Mr. Vijay K. Sharma, Mr Srinivasa V S Sarma, Mr.

Gokulananada Sahoo, Dr. P. Karuppanan, Dr. Kanhu C. Bhuyan and Dr. Preethy Sudha

Meher who have given the support in carrying out the work. Special thanks to my lovable

friends and everybody who have helped me to complete the thesis work successfully.

Last but not the least, I would like to express my deep appreciation to my beloved family

members Rakhee (My wife), Munmun/Ritwika (My daughter), father, mother in-

law and father in-law for all their encouragement, understanding, support, patience, and true

love throughout my ups and downs.

Lastly, I thank and praise God for always being on my side.

Rajesh Kumar Patjoshi

### **ABSTRACT**

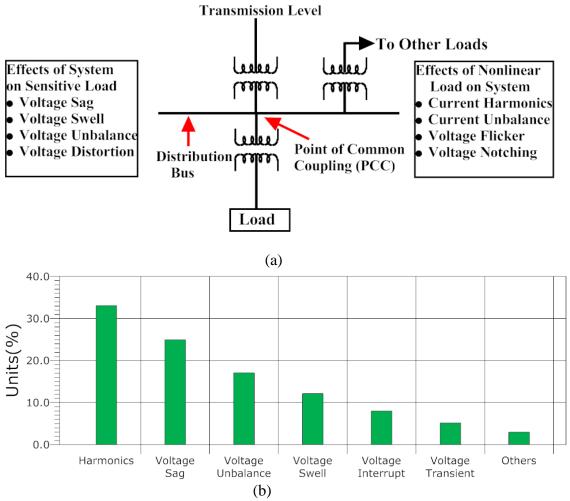

In recent times, power quality (PQ) issues such as current and voltage harmonics, voltage sag/swell, voltage unbalances have become the important causes for malfunctioning and degradation of the quality of power. Poor power quality severely affects on electrical equipment and finally results in significant economic losses. Hence, installation of the custom power devices to improve the power quality issues becomes an important consideration. Therefore, this thesis considers the enhancement of power quality for power distribution systems by utilizing unified power quality conditioner (UPQC). An UPQC can adequately handle several power quality problems such as load current harmonics, supply voltage distortions, voltage sags/swells and voltage unbalance. Therefore, the main focus behind this thesis is to develop advanced control strategies that improve the compensation capability of the UPQC so that power quality issues of distribution network are efficiently improved.

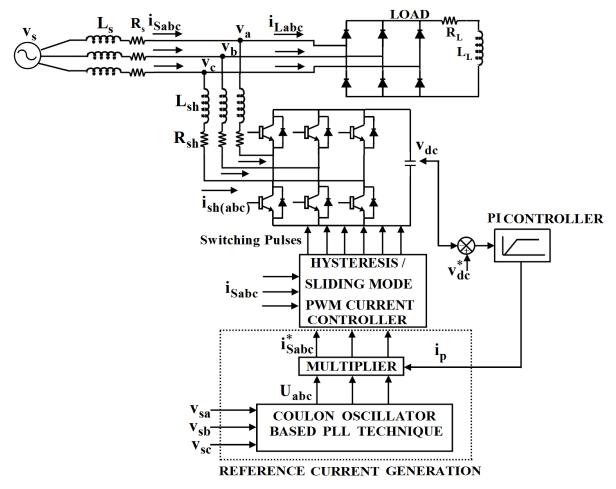

Firstly, the current harmonics are considered and are compensated by using the shunt active power filter (SAPF). Therefore, two control strategies such as Hysteresis current control (HCC) and Sliding Mode Control (SMC) based control algorithms are implemented to compensate current harmonics in the power distribution network. Furthermore, both the current control techniques utilize the Coulon oscillator based PLL (CO-PLL) for extraction of positive sequence signal from the supply voltage and generate the three-phase reference currents by employing PI-controller based DC-link voltage regulation. The performances of both current control techniques for SAPF are evaluated under different source voltage conditions such as balanced, unbalanced and non-sinusoidal.

The SAPF effectively compensates currents harmonic, however, it is unable to compensate voltage related problems. To overcome this drawback, this thesis considers the UPQC, which comprises with shunt APF and series APF, can be utilized to compensate both current and voltage related problems. The research on UPQC is carried out progressively by considering different advanced control strategies. Each progress in the research enhances the compensation capabilities of the previous UPQC control system. The simulation and real-time Opal-RT studies are carried out to verify the operating performance of each design concept of UPQC.

At first, operating principle and design of UPQC is presented and then a novel control algorithm is introduced with the aid of nonlinear DC-link voltage controller such as nonlinear variable gain fuzzy (NVGF) controller and nonlinear sliding mode controller (NLSMC) with modified synchronous reference frame (SRF) control strategy for improvement of both current and voltage compensation performance of the UPQC. However, existence of large settling time in dc voltage leads to poor dynamic performance of NVGF control technique and hence current harmonics, voltage distortions and voltage disturbance such as voltage sag/swell as well as voltage unbalance compensation capability of this technique is not quite effective in comparison to the NLSMC technique. Moreover, NLSMC is very sensitive to model mismatch and noise. It is quite sluggish in rejecting long drifting grid disturbances. Hence, a suitable control strategy has to be developed in UPQC, which has improved DC-link voltage regulation as well as tracking performance through load and grid perturbations.

To overcome this drawback a resistive optimization technique (ROT) incorporated with enhanced phase-locked loop (EPLL) based NVGF hysteresis control strategy and an optimum active power (OAP) technique combined with enhanced phase-locked loop (EPLL) based fuzzy sliding mode (FSM) pulse-width modulation (PWM) control strategy for UPQC have been discussed. ROT-NVGF and OAP-FSMC based UPQC control strategies are adaptive as well as robust and able to mitigate the PQ problems satisfactorily during all dynamic conditions of power system perturbation. However, performances of these controllers are not effective when there is a variation occurring either in the nonlinear load parameter or supply voltage parameter. Thus, UPQC may not be able to compensate PQ problems satisfactorily.

Considering aforesaid problems, this thesis proposes a command generator tracker (CGT) based direct adaptive control (DAC) applied to a three-phase three-wire UPQC to improve the current and voltage harmonics, sag/swell and voltage unbalance in the power system distribution network. CGT is a model reference control law for a linear time-invariant system with known coefficients and is formulated for the generation of reference signal for both shunt and series inverter. The main advantage of the proposed control algorithm is that no online extraction is needed to perceive the UPQC parameters. Moreover,

the adaptive control law is designed to track a linear reference model to reduce the tracking error between model reference output and measured signal to be controlled. Additionally, this proposed algorithm adaptively regulates the DC-link capacitor voltage without utilizing additional controller circuit. As a result, the proposed algorithm provides more robustness, flexibility and adaptability in all operating conditions of the power system network.

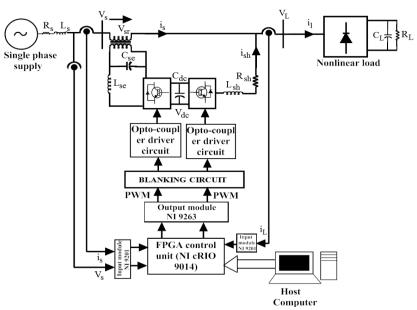

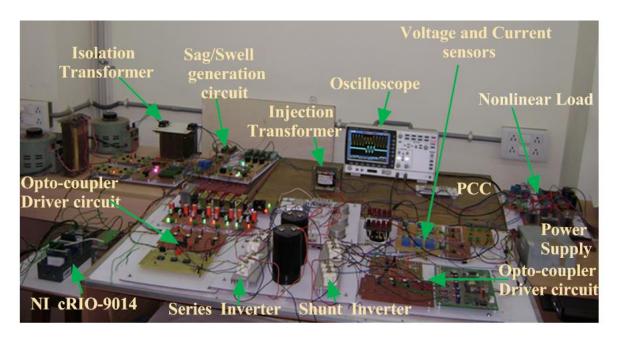

At last, model reference robust adaptive control (MRRAC) technique is proposed for single phase UPQC system. This control strategy is designed with the purpose of achieving high stability, high disturbance rejection and high level of harmonics cancellation. From simulation results, it is not only found to be robust against PI-controller, but also satisfactory THD results have been achieved in UPQC system. This has motivated to develop a prototype experimental set up in the Laboratory using FPGA (Field Programmable Gate Array) based NI (National Instruments) cRIO-9014. From both the simulation and experimentation, it is observed that the proposed MRRAC approach to design a UPQC system is found to be more effective as compared to the conventional PI-controller.

## **Contents**

| Contents                                                            |       |

|---------------------------------------------------------------------|-------|

| List of Abbreviations                                               | х     |

| List of Figures                                                     | xiii  |

| List of Tables                                                      | xxii  |

| List of Symbols                                                     | xxiii |

| 1 Introduction                                                      | 1     |

| 1.1 Background                                                      | 1     |

| 1.2 Power Quality issues                                            | 2     |

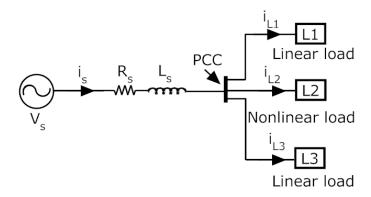

| 1.2.1 Current and voltage harmonics distortion                      | 2     |

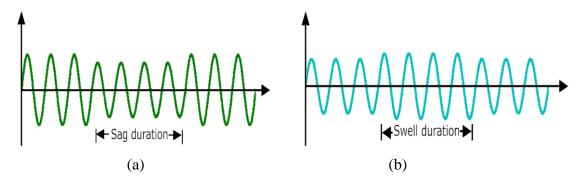

| 1.2.2 Voltage Sags                                                  | 5     |

| 1.2.3 Supply voltage swell                                          | 6     |

| 1.2.4 Voltage unbalance                                             | 6     |

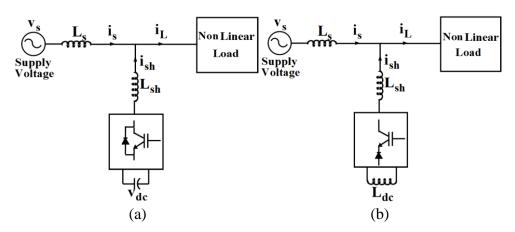

| 1.3 Solution to the Power Quality issue                             | 7     |

| 1.3.1 Shunt compensator                                             | 7     |

| 1.3.2 Series compensator                                            | 9     |

| 1.3.3 Unified power quality conditioner (UPQC)                      | 9     |

| 1.4 Literature Review                                               | 13    |

| 1.4.1 Related Work on Shunt Active Power Filter                     | 13    |

| 1.4.2 Literature Review of Unified Power Quality Conditioner (UPQC) | 15    |

| 1.5 Motivation of the Thesis                                        | 19    |

| 1.6 Objective of the Thesis                                         | 20    |

| 1.7 Thesis Organization                                             | 21    |

| 2 Shunt Active Power Filter (SAPF) Design and Control                                                                                                    | 24 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 Introduction                                                                                                                                         | 24 |

| 2.2 Design of the shunt APF system                                                                                                                       | 25 |

| 2.3 Active Power filter control strategies                                                                                                               | 30 |

| 2.4 Development of HCC/SMC based SAPF                                                                                                                    | 32 |

| 2.4.1 Reference Current Generation Technique                                                                                                             | 33 |

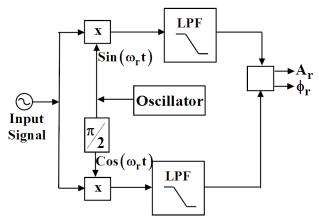

| 2.4.2 Positive Sequence Signal extraction method using CO-PLL                                                                                            | 34 |

| 2.4.3 Hysteresis Current controller                                                                                                                      | 37 |

| 2.4.4 Sliding Mode current control                                                                                                                       | 38 |

| 2.5 Simulation Results and Analysis                                                                                                                      | 40 |

| 2.6 Real-Time experimental Results                                                                                                                       | 45 |

| 2.7 Chapter Summary                                                                                                                                      | 50 |

| 3 Novel Nonlinear DC-link voltage controller with Modified SRF based<br>Control philosophy for Unified Power Quality power quality conditioner<br>(UPQC) | 51 |

| 3.1 Introduction                                                                                                                                         | 51 |

| 3.2 Structural design and operating principle of UPQC                                                                                                    | 51 |

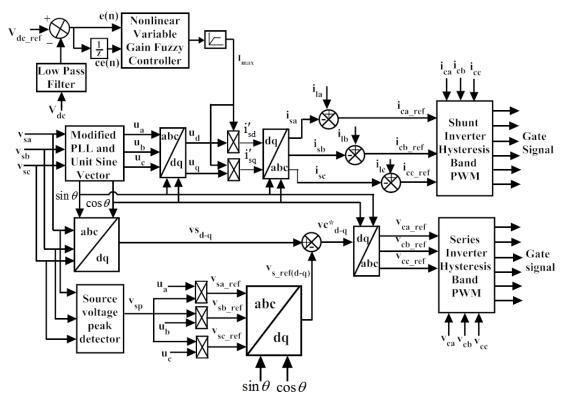

| 3.3 Nonlinear variable gain fuzzy and modified PLL based SRF control strategy                                                                            | 54 |

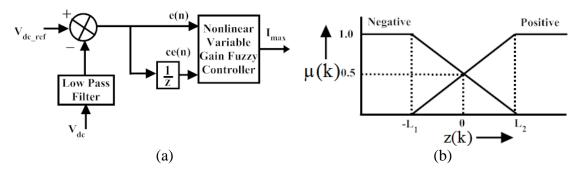

| 3.3.1 Design of NVGF for DC-link voltage regulation                                                                                                      | 54 |

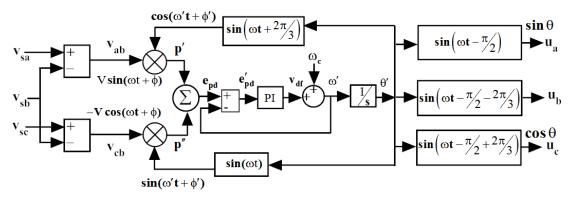

| 3.3.2 Modified PLL technique                                                                                                                             | 58 |

| 3.3.3 Proposed SRF based Reference signal generation technique                                                                                           | 60 |

| 3.4 Design of nonlinear sliding mode control and novel switching dynamic control strategy                                                                | 62 |

| 3.4.1 Nonlinear sliding mode control scheme for DC-link voltage control                                                                                  | 63 |

| 3.4.2 Proposed SRF based control strategy                                                                                                                | 68 |

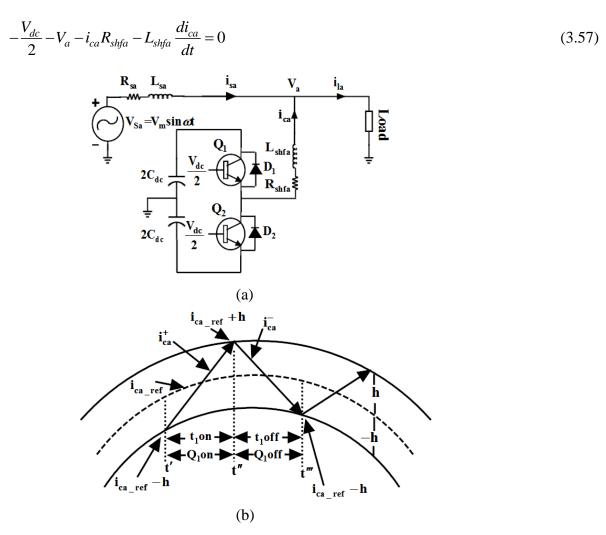

| 3.4.3 Analysis of switching dynamics in shunt APF                                                   | 69  |

|-----------------------------------------------------------------------------------------------------|-----|

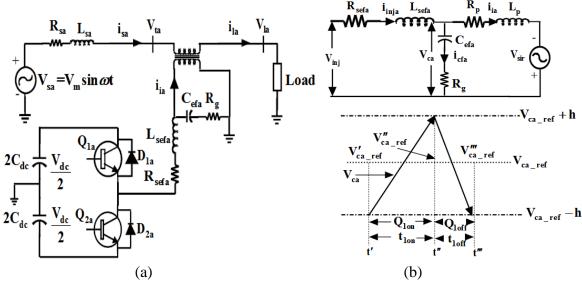

| 3.4.4 Analysis of switching dynamics in series APF                                                  | 72  |

| 3.5 Performance analysis                                                                            | 75  |

| 3.5.1 Simulation and real-time HIL based OPAL-RT result of NVGF based modified SRF theory           | 75  |

| 3.5.2 Simulation and real-time HIL based OPAL-RT result of NLSMC based modified SRF theory          | 84  |

| 3.6 Chapter Summary                                                                                 | 95  |

| 4 Optimization Based Reference Extraction Methods with Novel PWM Techniques for UPQC                | 97  |

| 4.1 Introduction                                                                                    | 97  |

| 4.2 Resistive optimization with nonlinear variable gain fuzzy (RO-NVGF) based hysteresis controller | 98  |

| 4.3 Proposed Resistive Optimization Technique                                                       | 99  |

| 4.3.1 Enhanced PLL (EPLL)                                                                           | 100 |

| 4.3.2 Resistive optimization technique for calculation of reference signal                          | 100 |

| 4.3.3 Design of Nonlinear Variable Gain Fuzzy controller for hysteresis band calculation            | 103 |

| 4.4 Power optimization with fuzzy sliding mode controller (PO-FSMC) based PWM control technique     | 107 |

| 4.5 Reference signal extraction technique                                                           | 108 |

| 4.5.1 Optimized Active Power (OAP) Technique                                                        | 109 |

| 4.5.2 Fuzzy sliding mode for shunt APF                                                              | 111 |

| 4.5.3 Fuzzy sliding mode for series APF                                                             | 114 |

| 4.6 Performance analysis                                                                            | 117 |

| 4.6.1 Simulation and real-time HIL based OPAL-RT result of ROT with NVGF hysteresis controller      | 117 |

| 4. 6.2 Simulation and real-time HIL based OPAL-RT result of OAP with FSMC-PWM controller            | 128 |

| 4.7 Chapter Summary                                                                                 | 138 |

| 5 High Performance UPQC using Command Generator Tracker (CGT) Based Direct Adaptive Control Strategy | 140 |

|------------------------------------------------------------------------------------------------------|-----|

| 5.1 Introduction                                                                                     | 140 |

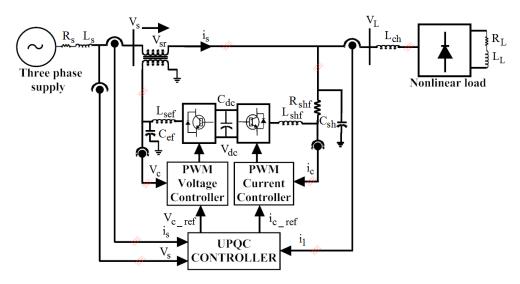

| 5.2 Structure of UPQC                                                                                | 141 |

| 5.3 Plant model for UPQC                                                                             | 142 |

| 5.4 Control design                                                                                   | 145 |

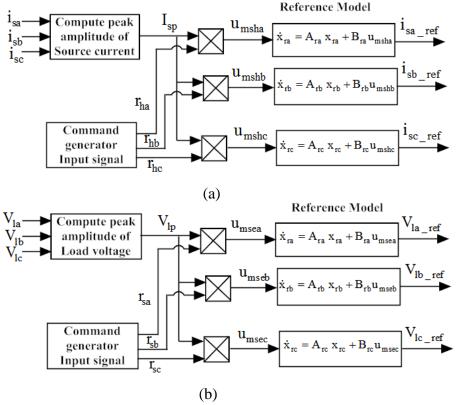

| 5.4.1 Construction of the CGT based reference generation                                             | 145 |

| 5.4.2 Direct adaptive control algorithm                                                              | 147 |

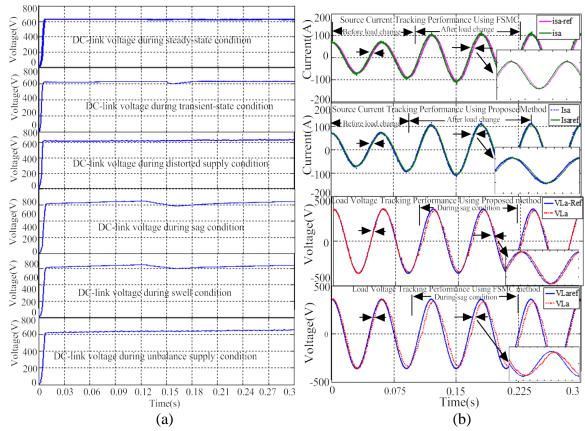

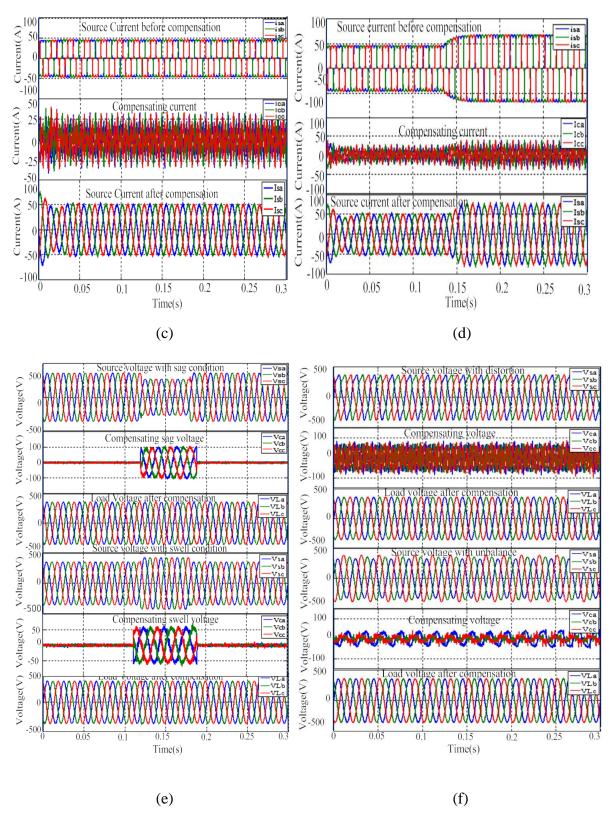

| 5.5 Simulation Results and Discussions                                                               | 149 |

| 5.6 Experimental validation using the real time HIL system                                           | 155 |

| 5.7 Chapter Summary                                                                                  | 160 |

| 6 Model Reference Robust Adaptive Control (MRRAC) based Experimental Prototype set-up for UPQC       | 161 |

| 6.1 Introduction                                                                                     | 161 |

| 6.2 Description of an experimental prototype Set-up for UPQC                                         | 162 |

| 6.2.1 Non-Linear Load                                                                                | 165 |

| 6.2.2 Voltage Source Inverter with DC-link capacitor                                                 | 165 |

| 6.2.3 Interfacing Inductors                                                                          | 166 |

| 6.2.4 LC filter for series APF                                                                       | 167 |

| 6.2.5 Series coupling transformer                                                                    | 167 |

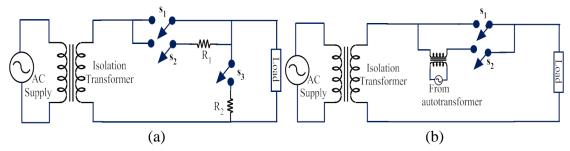

| 6.2.6 Design of sag/swell generation circuit                                                         | 168 |

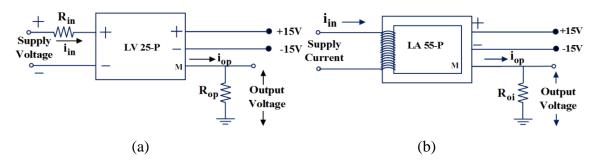

| 6.2.7 Voltage & Current Sensors                                                                      | 169 |

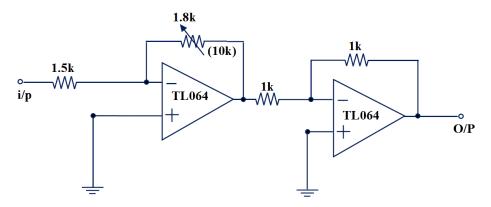

| 6.2.8 Signal Conditioning Circuit                                                                    | 171 |

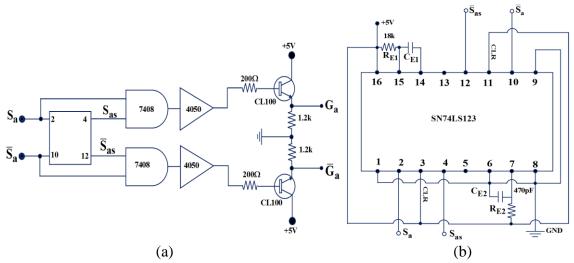

| 6.2.9 Blanking Circuit                                                                               | 171 |

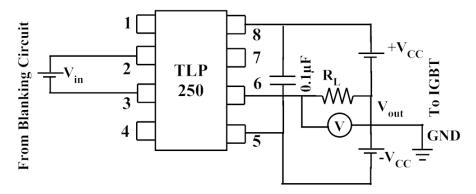

| 6.2.10 Opto-Isolation Circuit                                                                        | 172 |

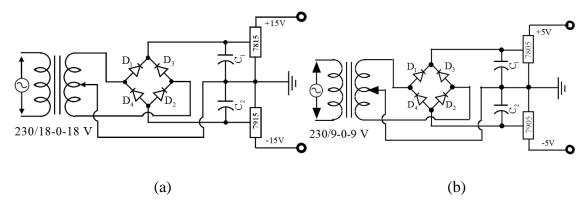

| 6.2.11 Power supply                            | 173 |

|------------------------------------------------|-----|

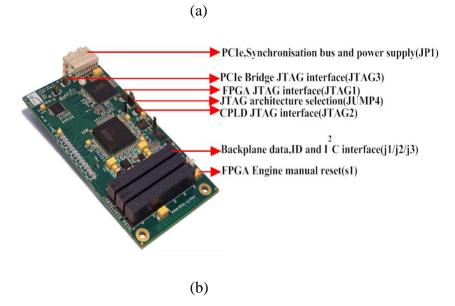

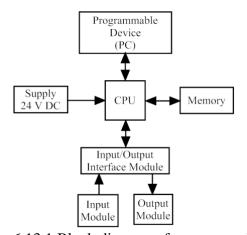

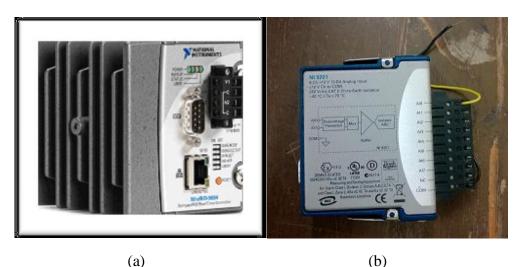

| 6.3 Field-Programmable Gate Array (FPGA)       | 174 |

| 6.4 CompactRIO-9014                            | 174 |

| 6.4.1 Reconfigurable Chassis                   | 175 |

| 6.4.2 Power supply                             | 175 |

| 6.4.3 Real Time Embedded Processor             | 176 |

| 6.4.5 Input/output Modules                     | 176 |

| 6.5 Model Reference Robust Adaptive controller | 176 |

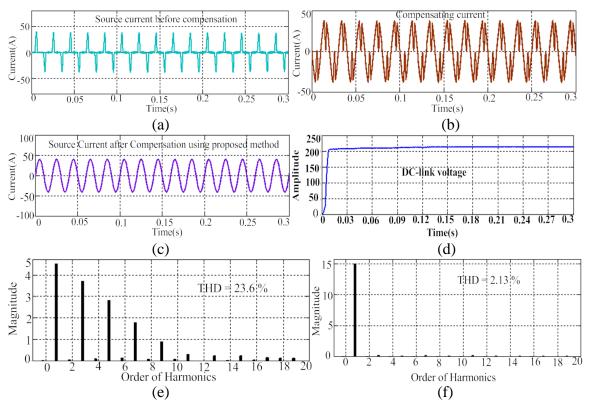

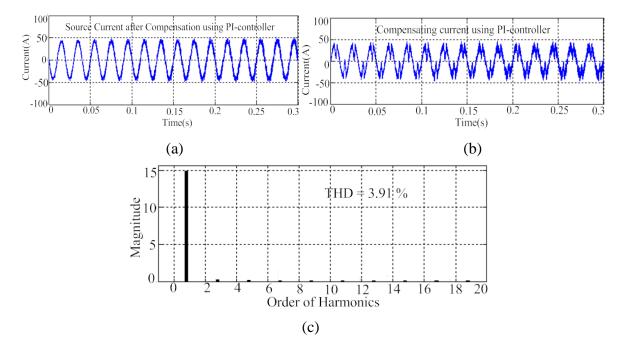

| 6.5.1 Simulation Results and Discussions       | 180 |

| 6.5.2 Experimental Results and Discussions     | 185 |

| 6.6 Chapter Summary                            | 188 |

| 7 Conclusion and Suggestions For Future Work   | 190 |

| 7.1 Overall Conclusion                         | 191 |

| 7.2 Contributions of the Thesis                | 192 |

| 7.3 Suggestions for Future Work                | 193 |

| References                                     | 195 |

| Thesis Dissemination                           | 204 |

| Appendix-1                                     | 206 |

| Appendix-2                                     | 207 |

| Appendix-3                                     | 208 |

| Appendix-4                                     | 209 |

| Appendix-5                                     | 210 |

## **List of Abbreviations**

| ASD     | Adjustable Speed Drives                                   |

|---------|-----------------------------------------------------------|

| AC      | Alternative Current                                       |

| ACVC    | STATCOM AC Voltage Controller                             |

| ARTEMIS | Advanced Real-Time Electro-Mechanical Transient Simulator |

| ASVC    | Advanced Static Var Compensator                           |

| ATC     | Available Transfer Capability                             |

| AVR     | Automatic Voltage Regulator                               |

| BFO     | Bacterial Foraging Optimization                           |

| CGT     | Command Generator Tracker                                 |

| COTS    | Commercial Off The Shelf                                  |

| CPSO    | Conventional Particle Swarm Optimization                  |

| CPD     | Custom Power Devices                                      |

| CSI     | Current Source Inverter                                   |

| DAC     | Direct Adaptive Control                                   |

| DC      | Direct Current                                            |

| DCVC    | STATCOM DC voltage controller                             |

| DVR     | Dynamic Voltage Restorers                                 |

| DSP     | Digital Signal Processor                                  |

| EMT     | Electromagnetic Transientcs                               |

| EPLL    | Enhanced Phase-Locked Loop                                |

| FACTS   | Flexible AC Transmission Systems                          |

| FLC     | Fuzzy Logic Controller                                    |

| FPGA    | Field-Programmable Gate Array                             |

| GA      | Genetic Algorithms                                        |

| GTO     | Gate-Turn-Off Thyristor                                   |

| HDL     | Hardware description language                             |

| HIL     | Hardware-In-the-Loop                                      |

| HVDC    | High-Voltage Direct Current                               |

| IEEE        | Institute of Electrical and Electronics Engineers   |

|-------------|-----------------------------------------------------|

| IGBT        | Insulated Gate Bipolar Transistor                   |

| I/O         | Input/output                                        |

| ITAE        | Integral of Time-Multiplied Absolute Value of Error |

| IWO         | Invasive Weed Optimization                          |

| JTAG        | Joint Test Action Group                             |

| MATLAB      | Matrix Laboratory                                   |

| MRRAC       | Model Reference Robust Adaptive Control             |

| MPC         | Model Predictive Control                            |

| MSO         | Mixed Signal Oscilloscope                           |

| MPLL        | Modified Phase-Locked Loop                          |

| NLSMC       | Non-Linear Sliding Mode Control                     |

| NVGFC       | Nonlinear Variable Gain Fuzzy Controller            |

| OAP         | Optimum Active Power                                |

| ORC         | Output Regulation-Based Controlle                   |

| PQ          | Power Quality                                       |

| PC          | Personnel Computer                                  |

| PCI-Express | Peripheral Component Interconnect - Express         |

| PF          | Power Factor                                        |

| PID         | Proportional Integral Derivative                    |

| POD         | Power Oscillations Damping                          |

| PSB         | Power System Block set                              |

| PSCAD       | Power Systems Computer Aided Design                 |

| PSO         | Particle Swarm Optimization                         |

| PCC         | Point of Common Coupling                            |

| PSS/E       | Power System Simulator for Engineering              |

| RTOS        | Real-Time Operating Systems                         |

| RTW         | Real-Time Workshop                                  |

| ROT         | Resistive Optimization Technique                    |

| SLG         | Single-line-to-ground                               |

| SAPF    | Shunt Active Power Filters                        |

|---------|---------------------------------------------------|

| SMPS    | Switch-Mode Power Supply                          |

| STATCOM | Static Synchronous Compensator                    |

| SVC     | Static Var Compensator                            |

| SVM     | Space Vector-Modulation                           |

| THD     | Total harmonic distortion                         |

| TCP/IP  | Transmission Control Protocol / Internet Protocol |

| TCPST   | Thyristor controlled phase shifting transformer   |

| TCR     | Thyristor Controlled Reactor                      |

| TCSC    | Thyristor Controlled Series Capacitor             |

| TNAs    | Transient Network Analysers                       |

| TSC     | Thyristor Switched Capacitor                      |

| TVAC    | Time-Varying Acceleration Coefficients            |

| UPFC    | Unified Power Flow Controller                     |

| UPQC    | Unified Power quality Conditioner                 |

| VAR     | Volt Ampere Reactive                              |

| VSI     | Voltage Source Inverter                           |

| VUF     | Voltage Unbalance Factor                          |

# **List of Figures**

| Figure No.  | Title                                                                                                                                                                                                                                                                                     | Page<br>Number |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|             | CHAPTER - 1                                                                                                                                                                                                                                                                               |                |

| Figure 1.1  | General power quality issues in an electrical system, (a) Schematic diagram, (b) Graphical representation.                                                                                                                                                                                | 3              |

| Figure 1.2  | Schematic diagram of power system with linear and nonlinear load                                                                                                                                                                                                                          | 4              |

| Figure 1.3  | Supply voltage sag and swell, (a) Voltage sag, (b) Voltage swell                                                                                                                                                                                                                          | 6              |

| Figure 1.4  | The shunt-connected power quality compensator, (a) Voltage Source Inverter, (b) Current Source Inverter.                                                                                                                                                                                  | 8              |

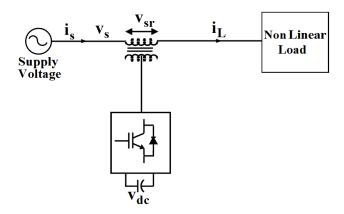

| Figure 1.5  | The series-connected power quality compensator                                                                                                                                                                                                                                            | 9              |

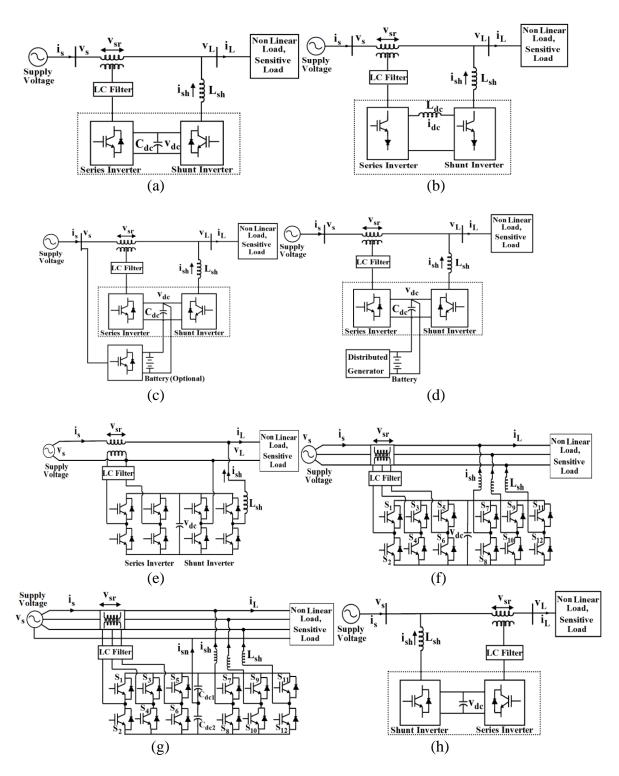

| Figure 1.6  | UPQC system topologies, (a) General block diagram representation of UPQC, (b) CSI-based UPQC topology, (c) UPQC-MC system topology, (d) UPQC-DG system topology, (e) 1P2W UPQC system topology, (f) 3P3W UPQC system topology, (g) 3P4W UPQC system topology, (h) UPQC-L system topology. | 10             |

|             | CHAPTER - 2                                                                                                                                                                                                                                                                               |                |

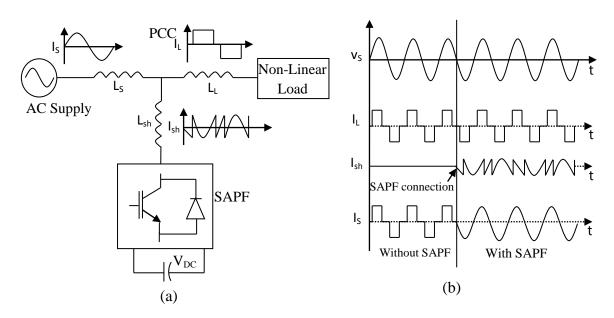

| Figure 2.1  | (a) Block diagram of shunt APF system, (b) Waveforms characteristic of SAPF                                                                                                                                                                                                               | 24             |

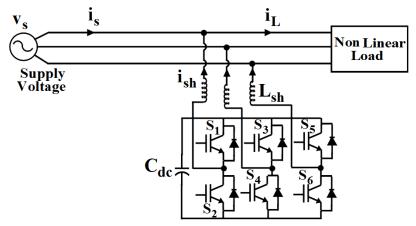

| Figure 2.2  | Three-phase three-wire shunt active power filter                                                                                                                                                                                                                                          | 26             |

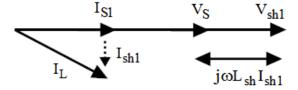

| Figure 2.3  | Vector diagram of SAPF                                                                                                                                                                                                                                                                    | 27             |

| Figure 2.4  | HCC/SMC based SAPF                                                                                                                                                                                                                                                                        | 32             |

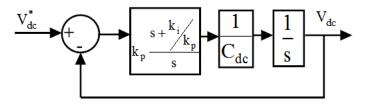

| Figure 2.5  | Outer control loop for dc-link voltage control                                                                                                                                                                                                                                            | 33             |

| Figure 2.6  | Block Diagram of Coulon Oscillator                                                                                                                                                                                                                                                        | 34             |

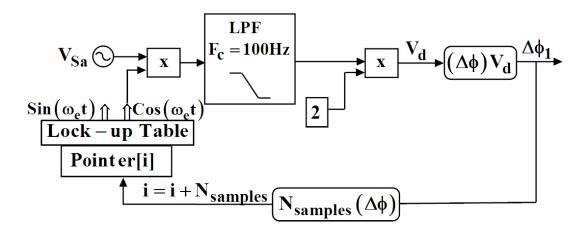

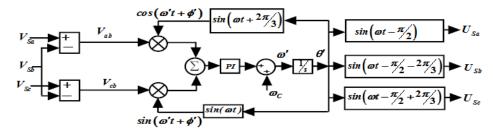

| Figure 2.7  | Block diagram of the CO-PLL structure                                                                                                                                                                                                                                                     | 36             |

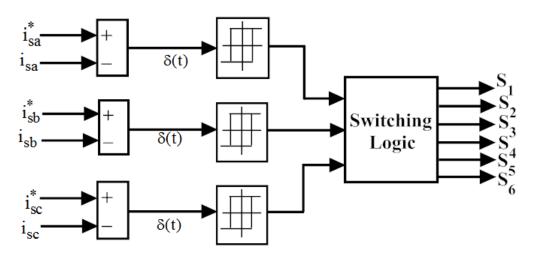

| Figure 2.8  | Schematic block diagram of hysteresis current controller                                                                                                                                                                                                                                  | 37             |

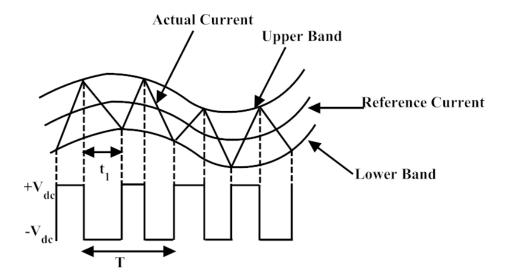

| Figure 2.9  | Switching pattern of hysteresis current controller                                                                                                                                                                                                                                        | 38             |

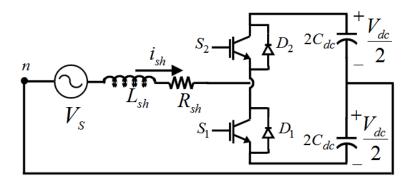

| Figure 2.10 | Equivalent Circuit for one leg of the shunt converter                                                                                                                                                                                                                                     | 39             |

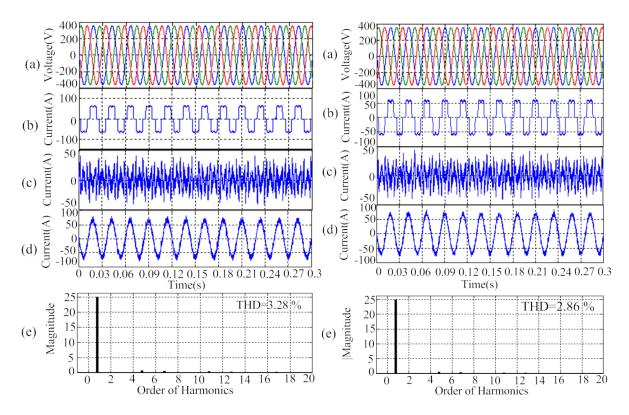

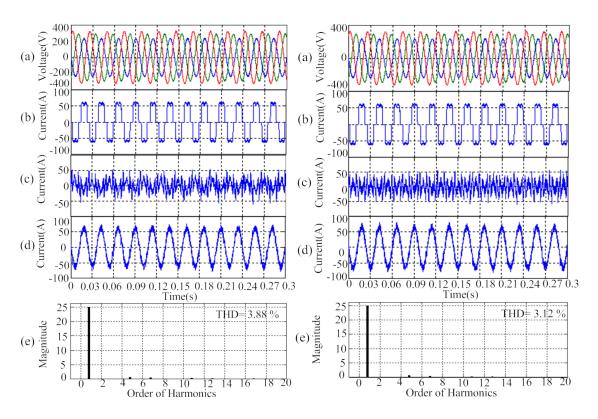

| Figure 2.11 | Simulation Waveform of the HCC with balanced supply condition (a) Source voltage, (b) Load current, (c) Compensation current (d) Source current, (e) FFT of source current after compensation                                                                                             | 41             |

| Figure 2.12 | Simulation Waveform of the SMC with balanced supply condition, (a) Source voltage, (b) Load current, (c) Compensation current, (d) Source current, (e) FFT of source current after compensation                                                                                           | 41             |

| Figure 2.13 | Simulation Waveform of the HCC with unbalanced supply condition, (a) Source voltage, (b) Load current, (c) Compensation current, (d) Source current, (e) FFT of source current after compensation                                                                                         | 42             |

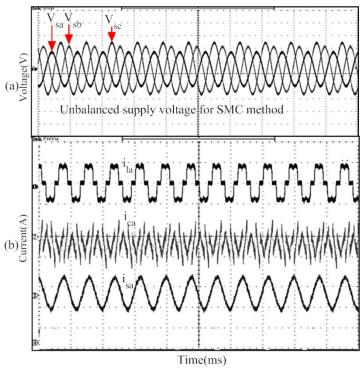

| Figure 2.14 | Simulation Waveform of the SMC with unbalanced supply condition, (a) Source voltage, (b) Load current, (c) Compensation current, (d) Source current, (e) FFT of source current after compensation                                  | 42 |

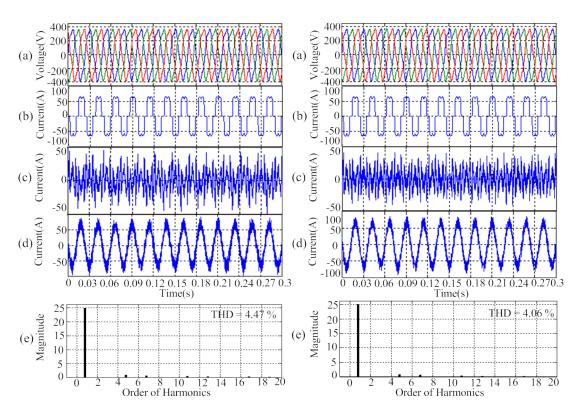

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.15 | Simulation Waveform of the HCC with distorted supply condition, (a) Source voltage, (b) Load current, (c) Compensation current, (d) Source current, (e) FFT of source current after compensation                                   | 43 |

| Figure 2.16 | Simulation Waveform of the SMC with distorted supply condition, (a) Source voltage, (b) Load current, (c) Compensation current, (d) Source current, (e) FFT of source current after compensation                                   | 43 |

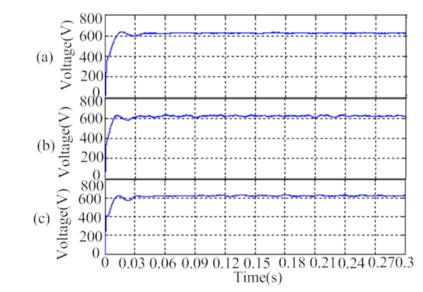

| Figure 2.17 | DC-link voltage waveforms, (a) During balanced supply voltage condition, (b) During unbalanced supply voltage condition, (c) During distorted supply voltage condition                                                             | 44 |

| Figure 2.18 | Real-time OPAL-RT experimental setup, (a) Real time HIL system, (b) OP5142 connectors and layout                                                                                                                                   | 46 |

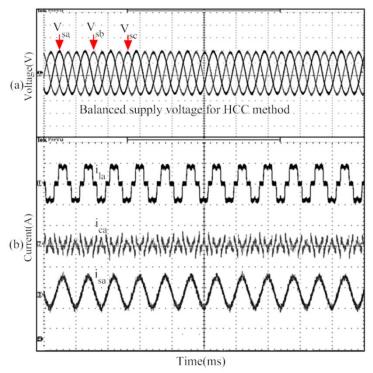

| Figure 2.19 | RT-lab experimental waveform under Balanced supply voltage with HCC method, (a) Source voltage (scale: 200 V/div), (b) Load current (scale: 75A/div), Compensation current (scale: 125 A/div), Source current (scale: 84 A/div).   | 47 |

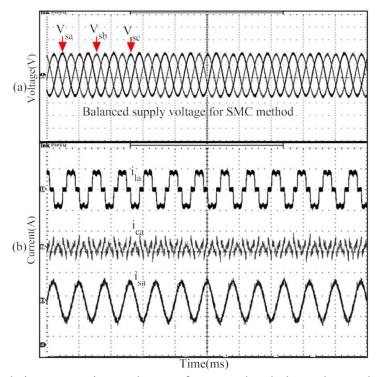

| Figure 2.20 | RT-lab experimental waveform under balanced supply voltage with SMC method, (a) Source voltage (scale: 200 V/div), (b) Load current (scale: 75 A/div), Compensation current (scale: 125 A/div), Source current (scale: 84 A/div).  | 47 |

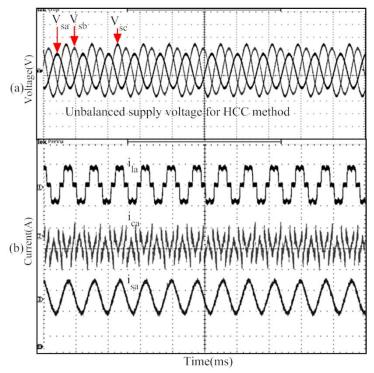

| Figure 2.21 | RT-lab experimental waveform under unbalanced supply voltage with HCC method, (a) Source voltage (scale: 200 V/div), (b) Load current (scale: 75 A/div), Compensation current (scale: 70 A/div), Source current (scale: 84 A/div). | 48 |

| Figure 2.22 | RT-lab experimental waveform under unbalanced supply voltage with SMC method, (a) Source voltage (scale: 200 V/div), (b) Load current (scale: 75 A/div), Compensation current (scale: 70 A/div), Source current (scale: 84 A/div). | 48 |

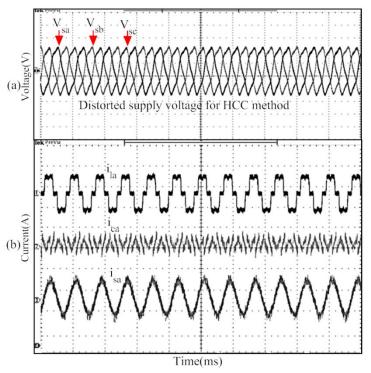

| Figure 2.23 | RT-lab experimental waveform under distorted supply voltage with HCC method, (a) Source voltage (scale: 200 V/div), (b) Load current (scale: 75 A/div), Compensation current (scale: 125 A/div), Source current (scale: 84 A/div). | 49 |

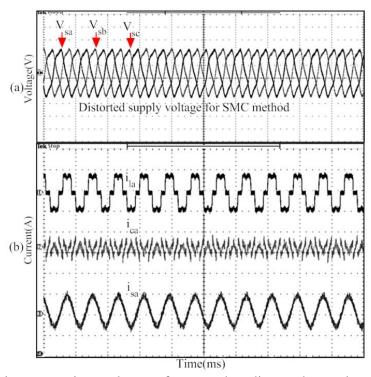

| Figure 2.24 | RT-lab experimental waveform under distorted supply voltage with SMC method, (a) Source voltage (scale: 200 V/div), (b) Load current (scale: 75 A/div), Compensation current (scale: 125 A/div), Source current (scale: 84 A/div). | 49 |

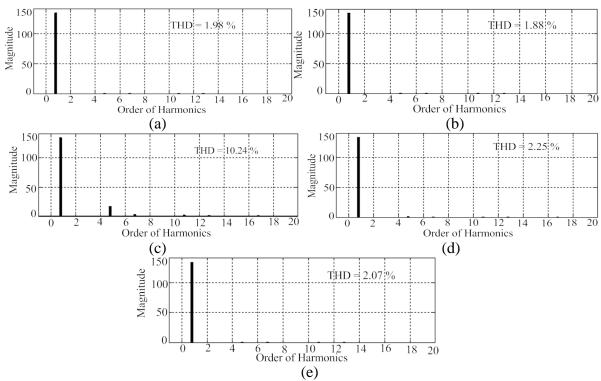

| Figure 2.25 | THD of Source Current for HCC and SMC strategies Using MATLAB-SIMULINK and Real-time digital simulator  CHAPTER - 3                                                                                                                | 50 |

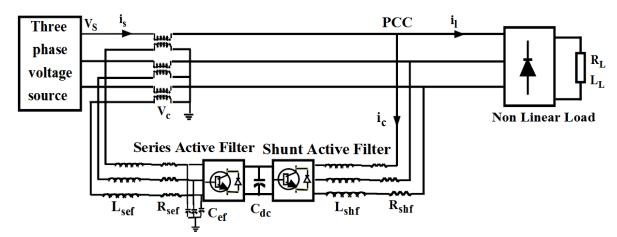

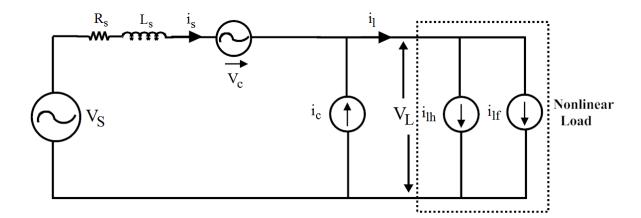

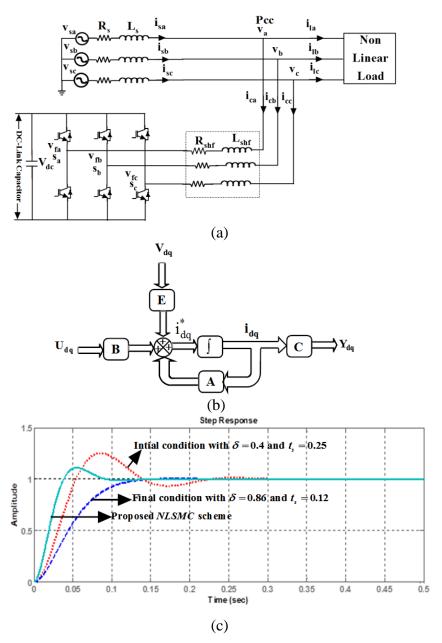

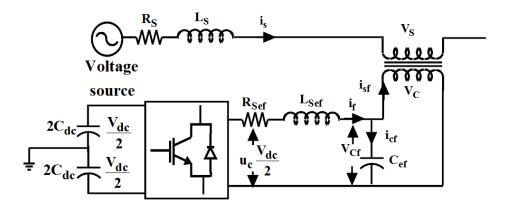

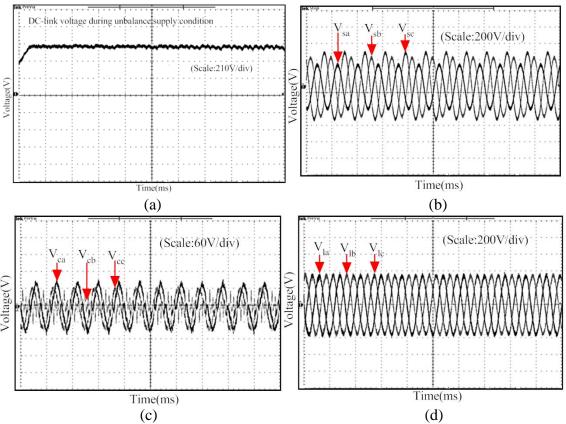

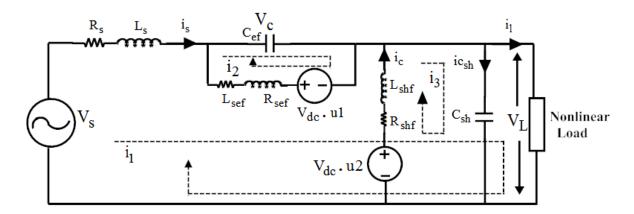

| Figure 3.1  | Structural design of UPQC                                                                                                                                                                                                          | 52 |

| Figure 3.2  | Equivalent single-phase circuit of UPQC                                                                                                                                                                                            | 53 |

| Figure 3.3  | Schematic diagram of the fuzzy control, (a) Control Structure, (b) Membership function                                                                                                                                             | 55 |

| Figure 3.4  | Modified PLL structure                                                                                                                                                                                                             | 58 |

| Figure 3.5  | Proposed SRF based control structure of UPQC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 62 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.6  | System configuration and response of UPQC, (a) Schematic diagram of shunt voltage source inverter, (b) System representation of part of the plant model of shunt APF, (c) Step response of the proposed method with initial and final condition of damping ratio and settling time                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 64 |

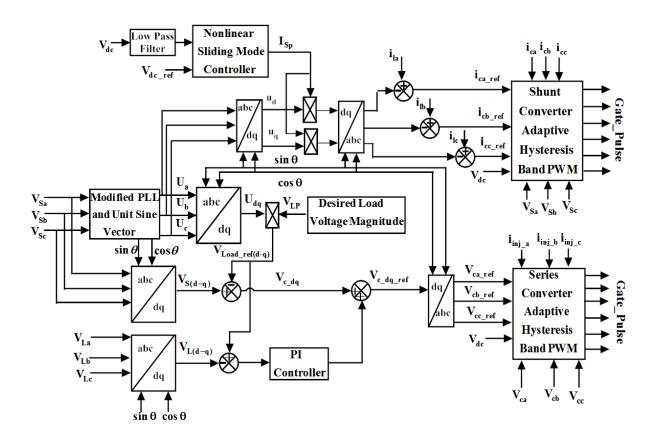

| Figure 3.7  | Proposed SRF based control strategy for UPQC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69 |

| Figure 3.8  | Switching dynamics analysis for the shunt APF, (a) Schematic circuit of equivalent single phase shunt APF, (b) Schematic diagram of switching dynamics for shunt APF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 71 |

| Figure 3.9  | Switching dynamics analysis for the series APF, (a) Schematic circuit of equivalent single phase series APF, (b) Equivalent circuit of series APF by exterior circuit and switching action of band control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 73 |

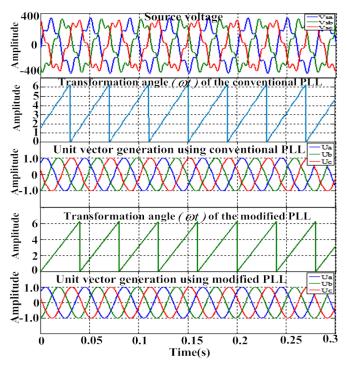

| Figure 3.10 | Performance of conventional and modified PLL during voltage distortion condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 76 |

| Figure 3.11 | Real-time experimental results of PLL algorithm under distorted supply condition, (a) Transformation angle ( $\omega t$ ) of conventional PLL (scale: 2 V/div), (b) Transformation angle ( $\omega t$ ) of modified PLL (scale: 2 V/div), (c) Unit vector signal from conventional PLL (scale: 1 V/div), (d) Unit vector signal from modified PLL (scale: 1 V/div).                                                                                                                                                                                                                                                                                                                                                                        | 77 |

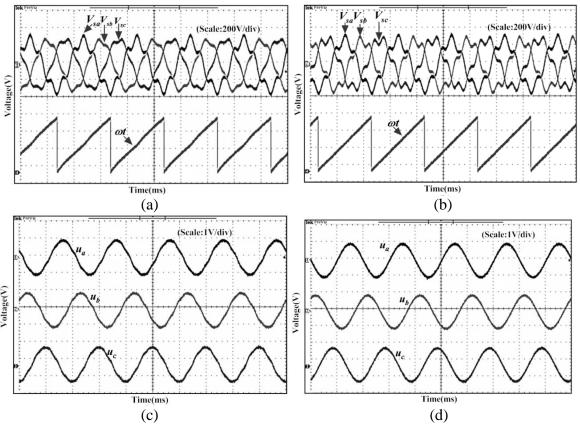

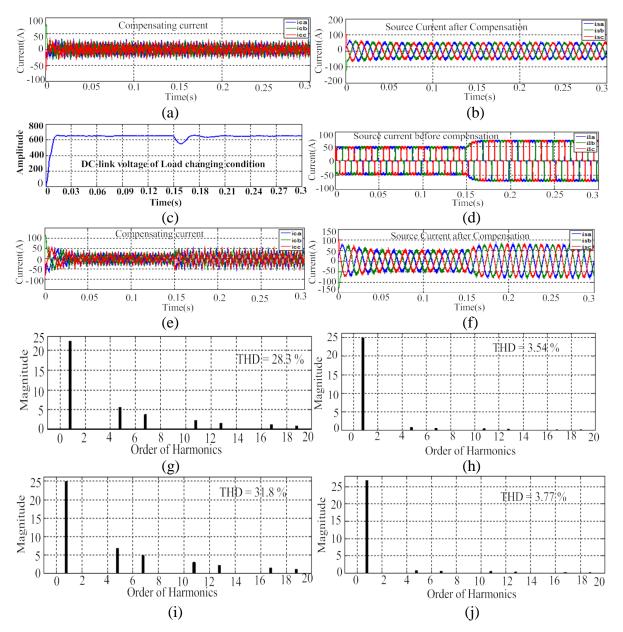

| Figure 3.12 | Simulation results, (a) Compensation current during steady-state condition, (b) Source current after compensation during steady-state condition, (c) dc-link voltage under transient condition, (d) Source current before compensation during transient-state condition, (e) Compensation current during transient-state condition, (f) Source current after compensation during transient-state condition, (g) Source current spectrum before compensation during steady-state condition, (h) Source current spectrum after compensation during steady-state condition (i) Source current spectrum before compensation during transient-state condition, (j) Source current spectrum after compensation during transient-state condition. | 78 |

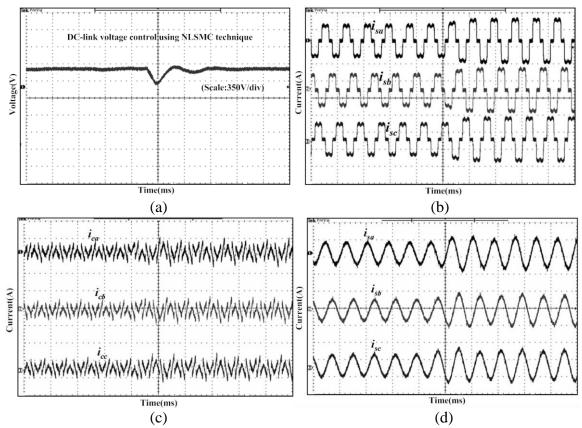

| Figure 3.13 | Real-time experimental results, (a) dc-link voltage under transient condition, (b) Source current before compensation (scale: 52 A/div), (c) Compensation current (scale: 40 A/div), (d) Source current after compensation (scale: 55 A/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79 |

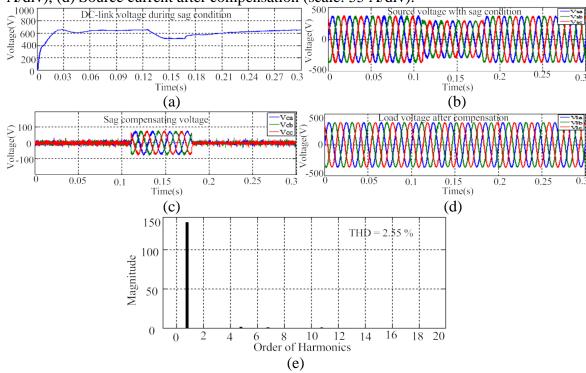

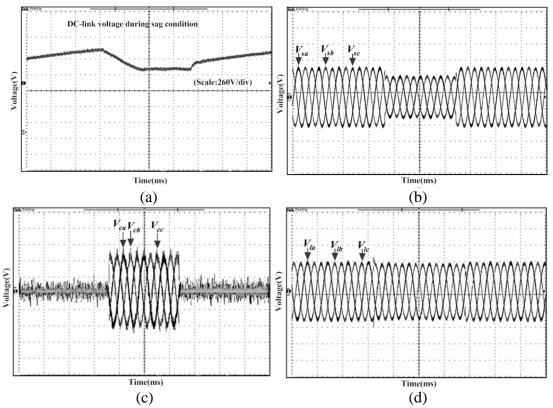

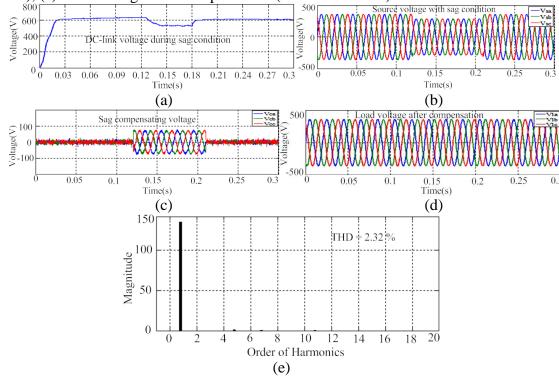

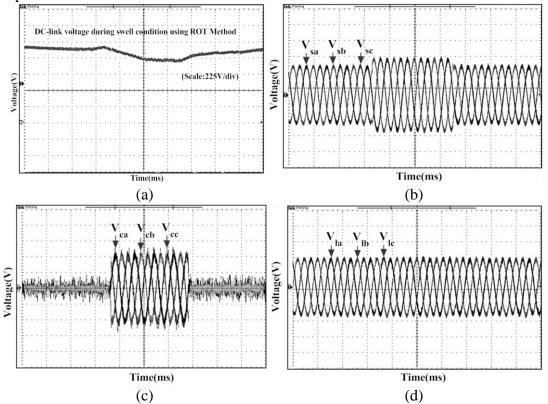

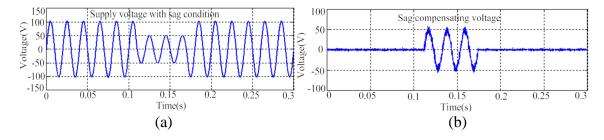

| Figure 3.14 | Simulation results during sag condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage, (e) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 79 |

| Figure 3.15 | Real-time experimental results during sag condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 65 V/div), (d) Load voltage after compensation (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 80 |

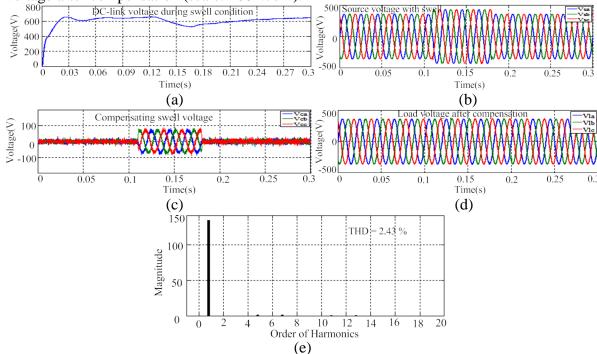

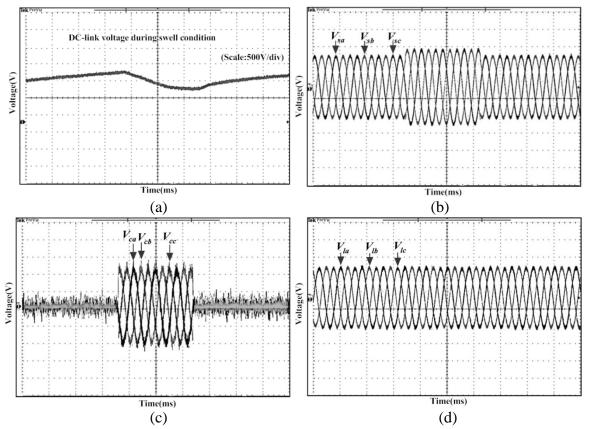

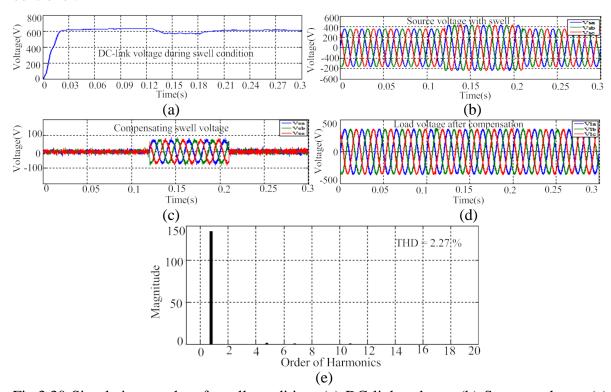

| Figure 3.16 | Simulation results of swell condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 80 |

| Figure 3.17 | Real-time experimental results during swell condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 73 V/div), (d) Load voltage (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 81 |

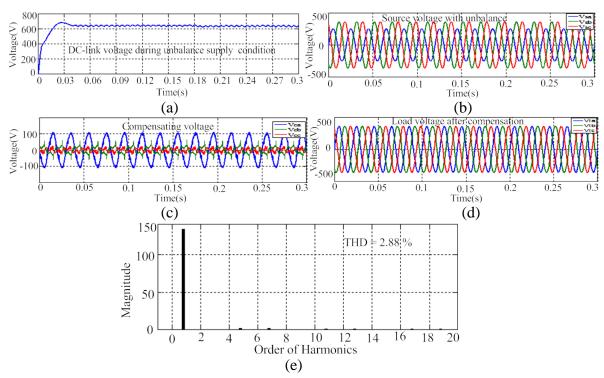

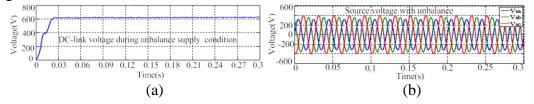

| Figure 3.18 | Simulation results during unbalanced supply condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 82 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

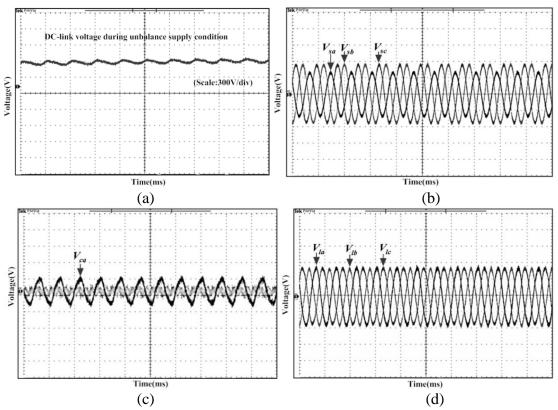

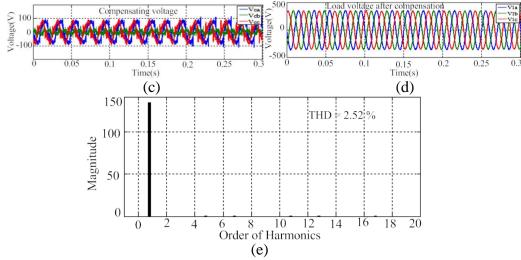

| Figure 3.19 | Real-time experimental results during unbalanced supply condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 80 V/div), (d) Load voltage after compensation (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 83 |

| Figure 3.20 | Simulation results during distorted supply condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Distorted supply voltage spectrum, (f) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 83 |

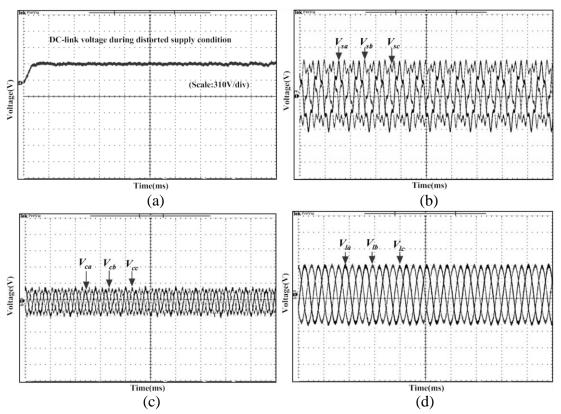

| Figure 3.21 | Real-time experimental results under distorted supply voltage condition, (a) Source voltage (scale: 200V/div), (b) Compensation voltage (scale: 25V/div), (c) Load voltage after compensation (scale: 200V/div) and DC-link voltage (scale: 330V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 84 |

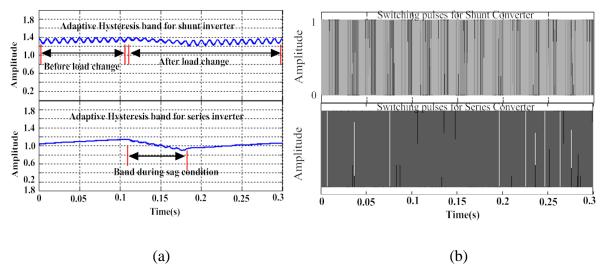

| Figure 3.22 | Hysteresis band and switching patterns for shunt and series inverter, (a) Hysteresis band for shunt and series inverter, (b) Switching patterns for shunt and series inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 85 |

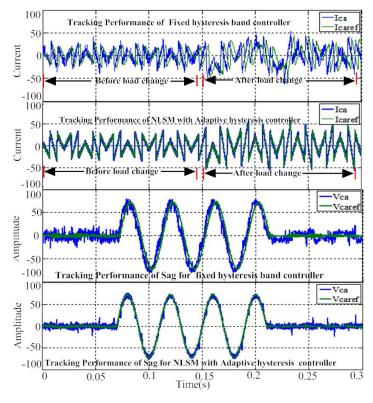

| Figure 3.23 | Tracking Performance of fixed hysteresis controller and NLSM with adaptive hysteresis controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 85 |

| Figure 3.24 | Simulation results, (a) Compensation current during steady-state condition, (b) Source current after compensation during steady-state condition, (c) dc-link voltage under transient condition, (d) Source current before compensation during transient-state condition, (e) Compensation current during transient-state condition, (f) Source current after compensation during transient-state condition, (g) Source current spectrum before compensation during steady-state condition, (h) Source current spectrum after compensation during steady-state condition (i) Source current spectrum before compensation during transient-state condition, (j) Source current spectrum after compensation during transient-state condition | 86 |

| Figure 3.25 | Real-time experimental results, (a) DC-link voltage under transient condition, (b) Source current before compensation (scale: 52 A/div), (c) Compensation current (scale: 40 A/div), (d) Source current after compensation (scale: 55 A/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 87 |

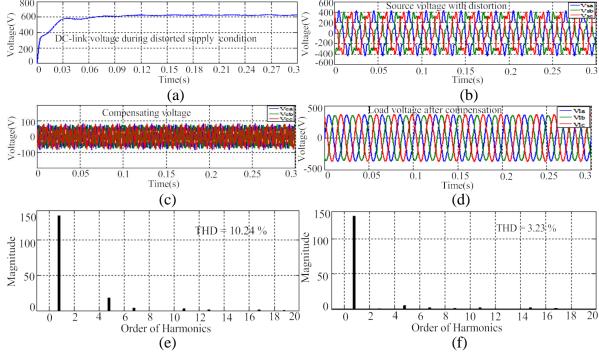

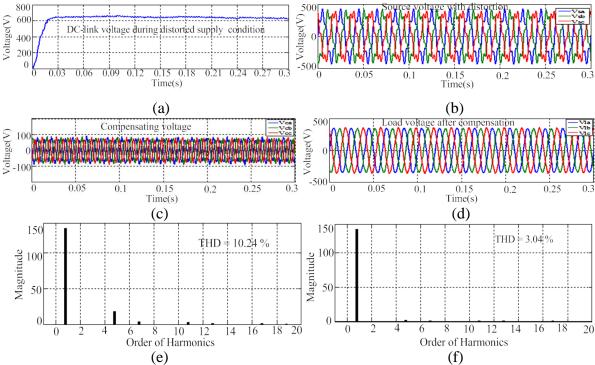

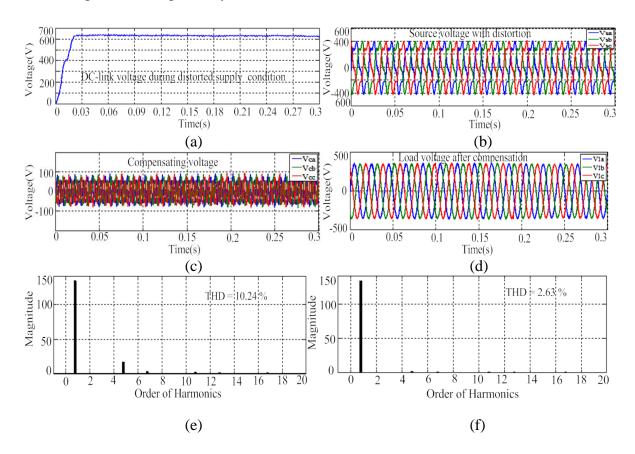

| Figure 3.26 | Simulation results during distorted supply condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Distorted supply voltage spectrum, (f) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 89 |

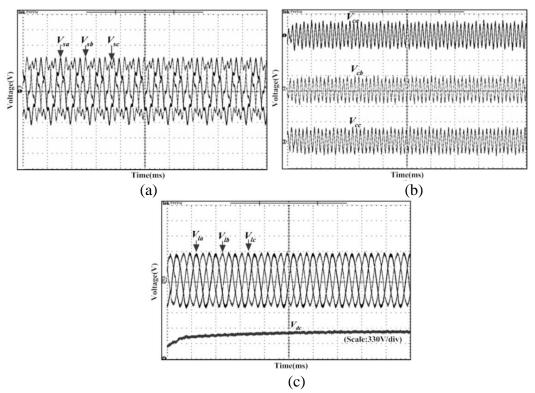

| Figure 3.27 | Real-time experimental results under distorted supply voltage condition, (a) DC-link voltage, (a) Source voltage (scale: 200 V/div), (b) Compensation voltage (scale: 25 V/div), (c) Load voltage after compensation (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 90 |

| Figure 3.28 | Simulation results during sag condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage, (e) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 90 |

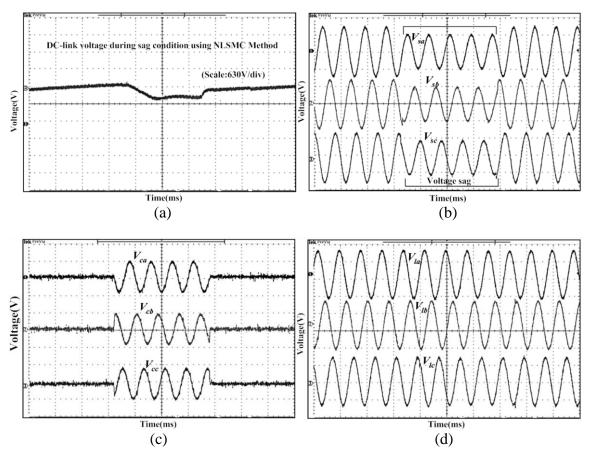

| Figure 3.29 | Real-time experimental results during sag condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 65 V/div), (d) Load voltage (scale: 200 V/div).                                                                                                                                            | 91  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

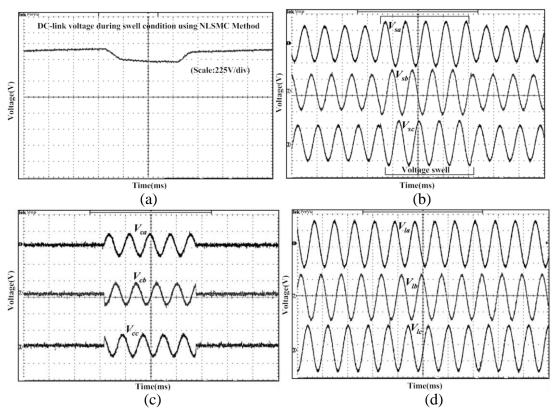

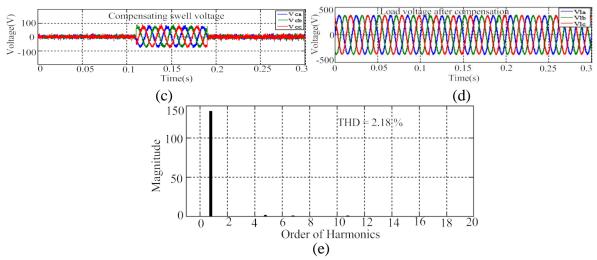

| Figure 3.30 | Simulation results of swell condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation.                                                                                                                                                 | 92  |

| Figure 3.31 | Real-time experimental results during swell condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 73 V/div), (d) Load voltage (scale: 200 V/div).                                                                                                                                          | 93  |

| Figure 3.32 | Simulation results during unbalanced supply condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation                                                                                                                                  | 93  |

| Figure 3.33 | Real-time experimental results during unbalanced supply condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 80 V/div), (d) Load voltage after compensation (scale: 200 V/div).                                                                                                           | 94  |

|             | CHAPTER - 4                                                                                                                                                                                                                                                                                                                                  |     |

| Figure 4.1  | Enhanced PLL structure                                                                                                                                                                                                                                                                                                                       | 100 |

| Figure 4.2  | Proposed control structure of UPQC                                                                                                                                                                                                                                                                                                           | 101 |

| Figure 4.3  | Schematic diagram of NVGF hysteresis band, (a) Shunt APF control scheme,<br>Series APF control scheme                                                                                                                                                                                                                                        | 103 |

| Figure 4.4  | Membership function                                                                                                                                                                                                                                                                                                                          | 104 |

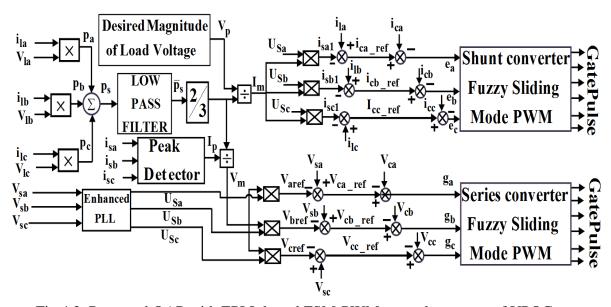

| Figure 4.5  | Proposed control structure of UPQC                                                                                                                                                                                                                                                                                                           | 110 |

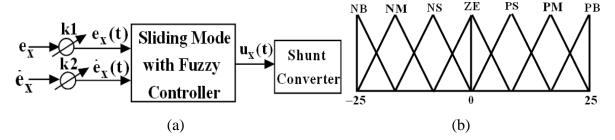

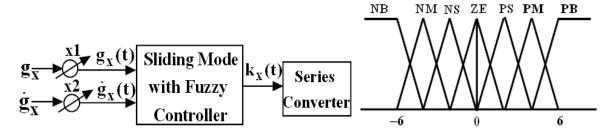

| Figure 4.6  | FSMC for shunt converter, (a) Block diagram representation, (b) Membership functions for the input variable $e_x(t)$ and $\dot{e}_x(t)$                                                                                                                                                                                                      | 113 |

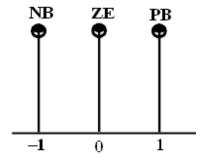

| Figure 4.7  | Membership functions for the output variable                                                                                                                                                                                                                                                                                                 | 113 |

| Figure 4.8  | Equivalent circuit for a single phase of the series converter                                                                                                                                                                                                                                                                                | 115 |

| Figure 4.9  | FSMC for series converter, (a) Block diagram representation, (b) Membership functions for the input variable $\dot{g}(t)$ and $\ddot{g}(t)$                                                                                                                                                                                                  | 117 |

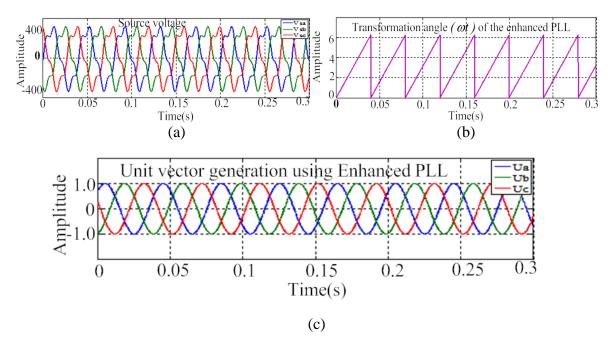

| Figure 4.10 | Simulation results of EPLL algorithm under distorted supply condition, (a) Distorted supply voltage, (b) Transformation angle ( $\omega t$ ) of EPLL, (c) Unit vector signal from EPLL.                                                                                                                                                      | 118 |

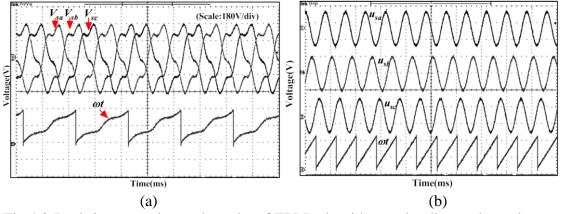

| Figure 4.11 | Real-time experimental results of EPLL algorithm under distorted supply condition (a) Distorted supply voltage and transformation angle $(\omega t)$ of conventional PLL (scale: 2 V/div), (b) Unit vector signal generation using EPLL technique (scale: 1 V/div) and transformation angle $(\omega t)$ of EPLL technique (scale: 2 V/div). | 119 |

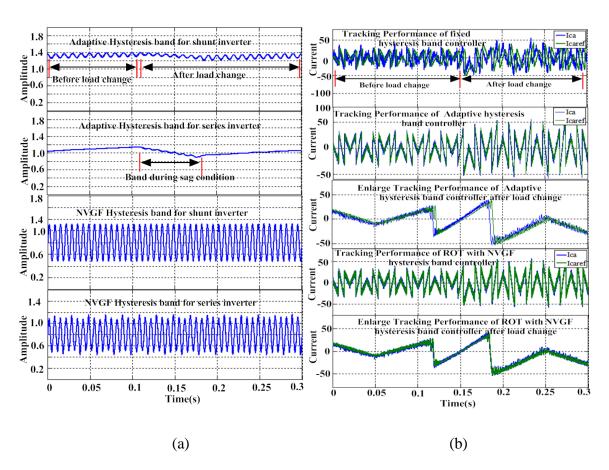

| Figure 4.12 | Hysteresis band and tracking performance of reference signal, (a) Adaptive hysteresis band and NVGF Hysteresis band controller for shunt and series APF, (b) Performance comparison for tracking of compensating reference signal using NLSMC with AHB and ROT with NVGF hysteresis band controller                                          | 120 |

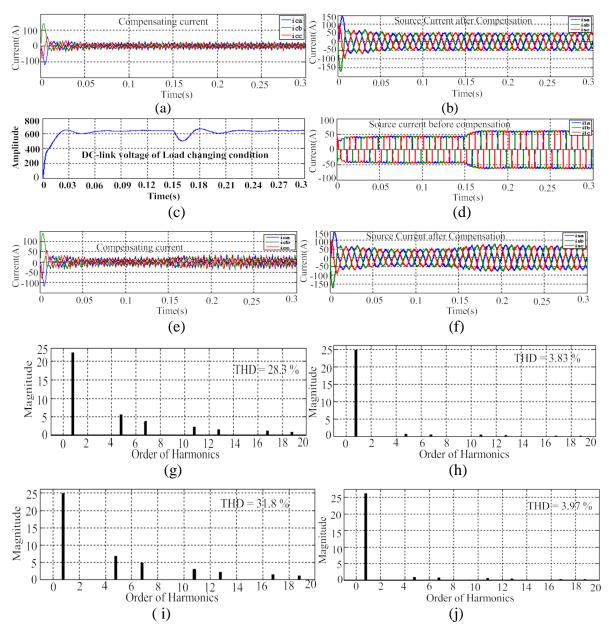

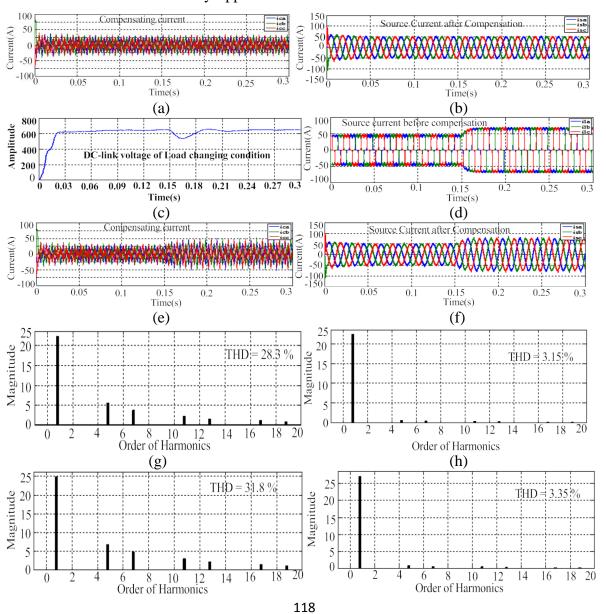

| Figure 4.13 | Simulation results, (a) Compensation current during steady-state condition, (b) Source current after compensation during steady-state condition, (c) DC-link voltage under transient condition, (d) Source current before compensation during transient-state condition, (e) Compensation current during transient-state condition, (f) Source current after compensation during transient-state condition, (g) Source current spectrum before compensation during steady-state condition, (h) Source current spectrum after compensation during steady-state condition (i) Source current spectrum before compensation during transient-state condition, (j) Source current spectrum after compensation during transient-state condition. | 121 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

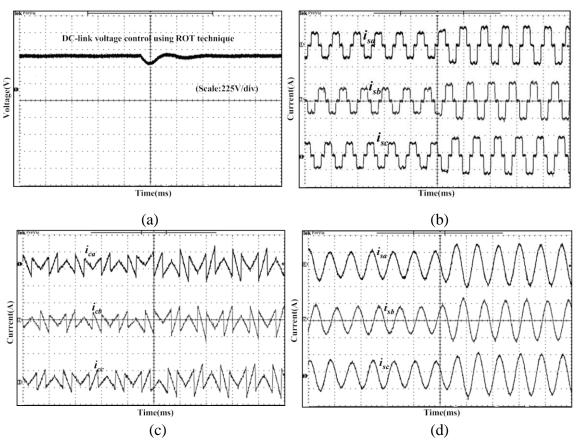

| Figure 4.14 | Real-time experimental results, (a) DC-link voltage under transient condition, (b) Source current before compensation (scale: 62 A/div), (c) Compensation current (scale: 40 A/div), (d) Source current after compensation (scale: 65 A/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 122 |

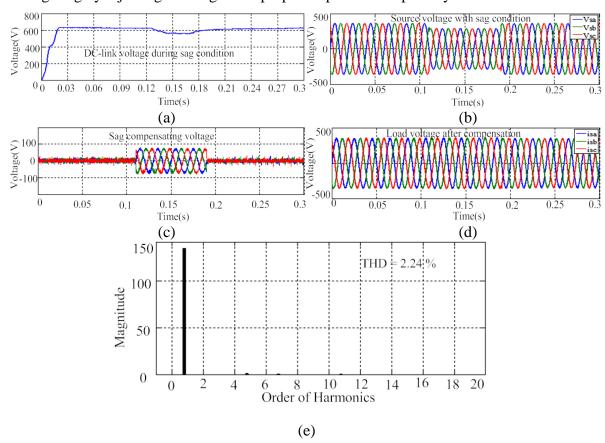

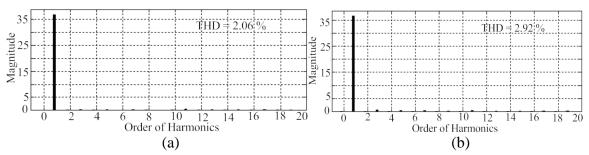

| Figure 4.15 | Simulation results during sag condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 123 |

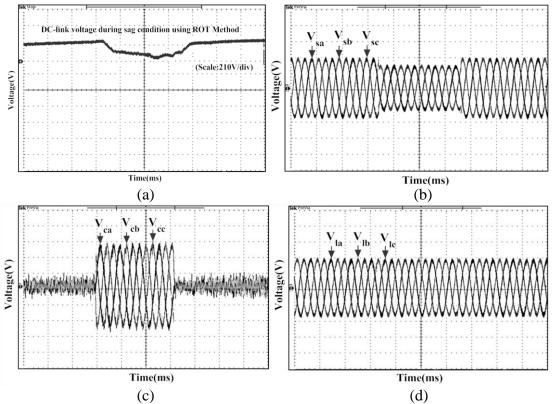

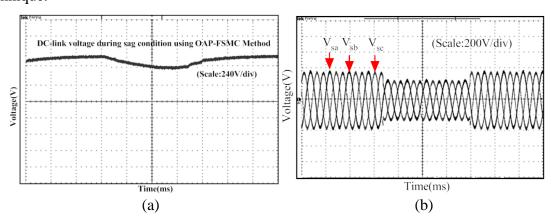

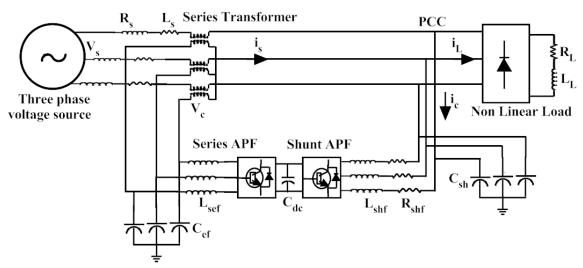

| Figure 4.16 | Real-time experimental results during sag condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 65 V/div), (d) Load voltage after compensation (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 124 |

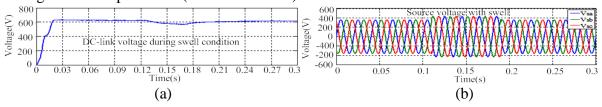

| Figure 4.17 | Simulation results of swell condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 124 |

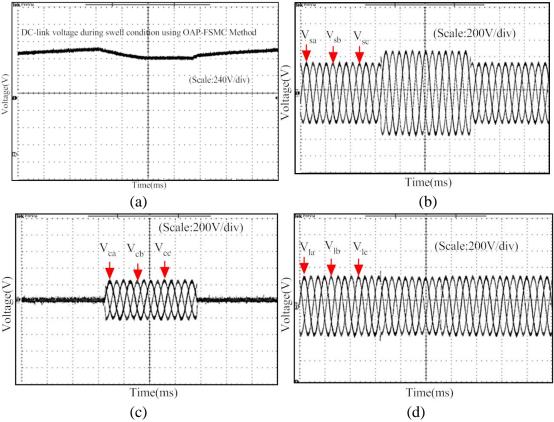

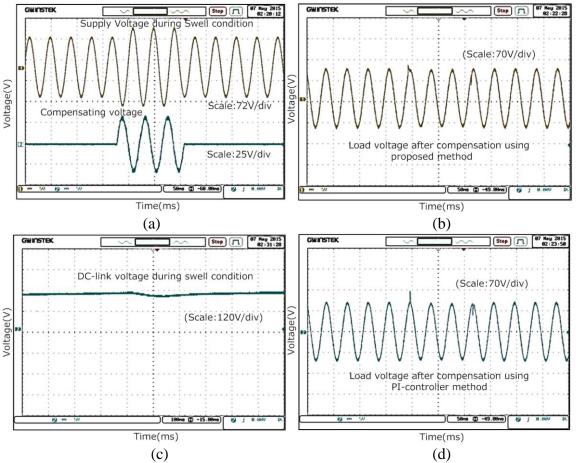

| Figure 4.18 | Real-time experimental results during swell condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 73 V/div), (d) Load voltage (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 125 |

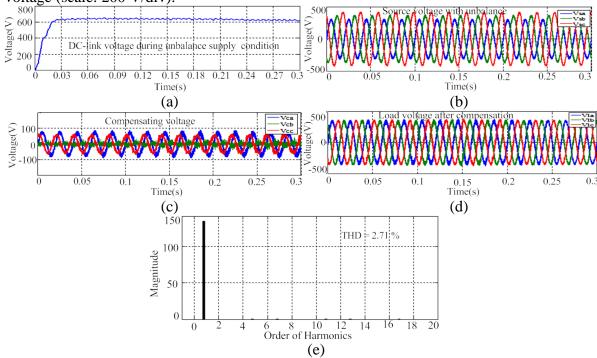

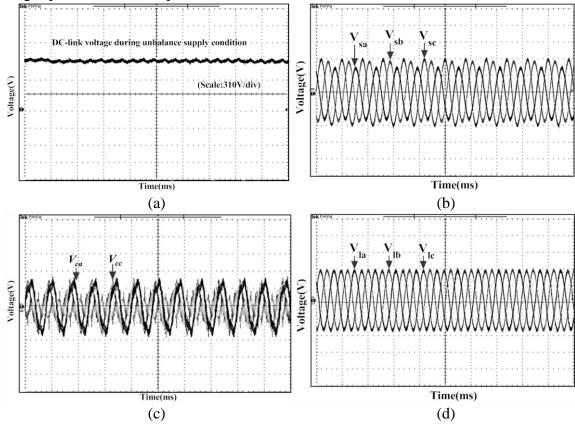

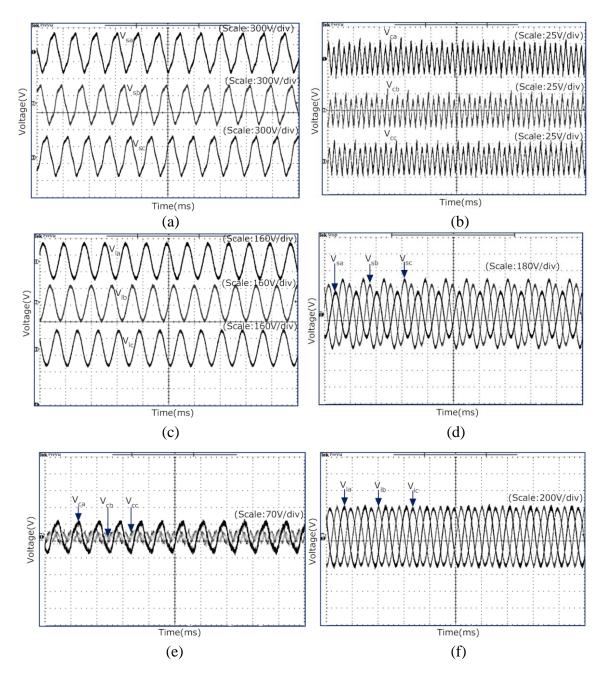

| Figure 4.19 | Simulation results during unbalanced supply condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 125 |

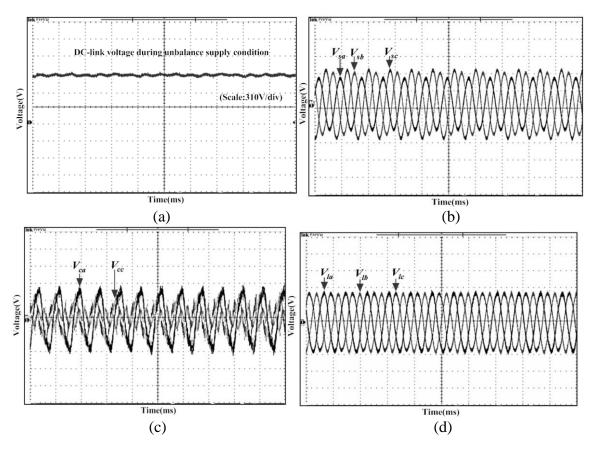

| Figure 4.20 | Real-time experimental results during unbalanced supply condition, (a) DC-link voltage, (b) Source voltage (scale: 200V/div), (c) Compensation voltage (scale: 80 V/div), (d) Load voltage after compensation (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 126 |

| Figure 4.21 | Simulation results during distorted supply condition, (a) DC-link voltage, (b) Source voltage, (c) Compensation voltage, (d) Load voltage after compensation, (e) Distorted supply voltage spectrum, (f) Load voltage spectrum after compensation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 127 |

| Figure 4.22 | Real-time experimental results under distorted supply voltage condition, (a) DC-link voltage, (b) Source voltage (scale: 200 V/div), (c) Compensation voltage (scale: 25 V/div), (d) Load voltage after compensation (scale: 200 V/div).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 128 |

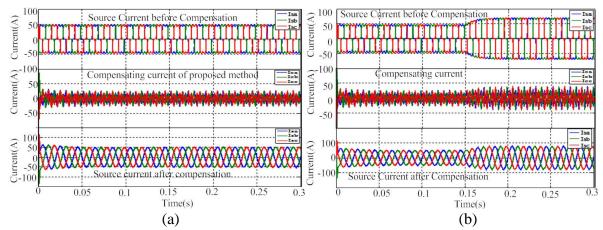

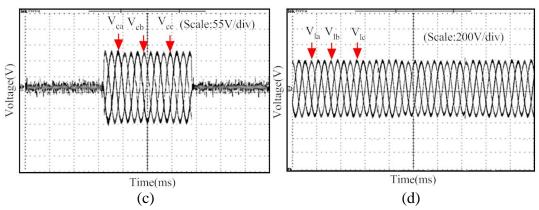

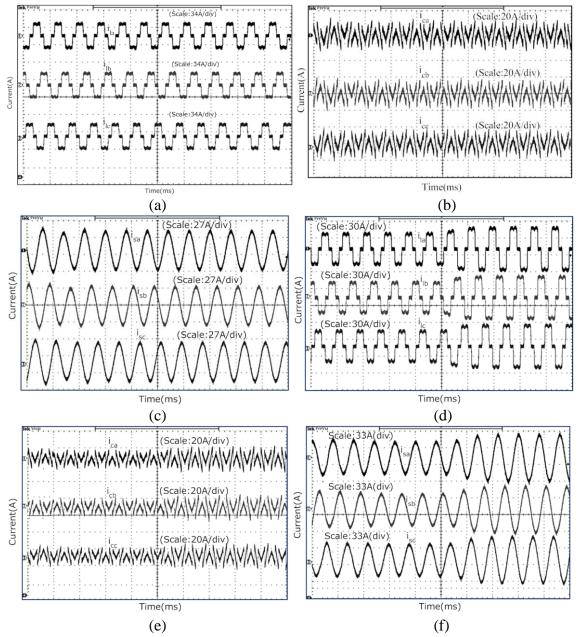

| Figure 4.23 | Simulation result of shunt APF, (a) Shunt APF compensation waveforms during steady state condition, (b) Shunt APF compensation waveforms during transient-state condition.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 129 |

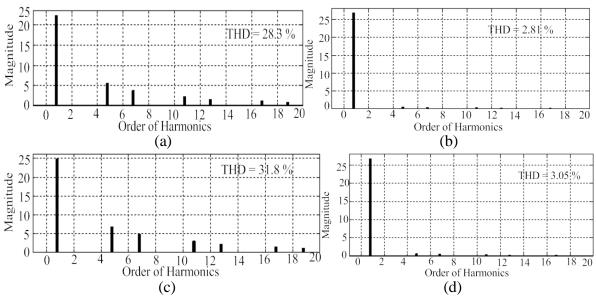

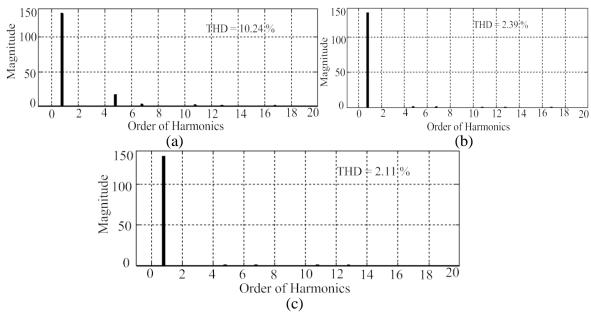

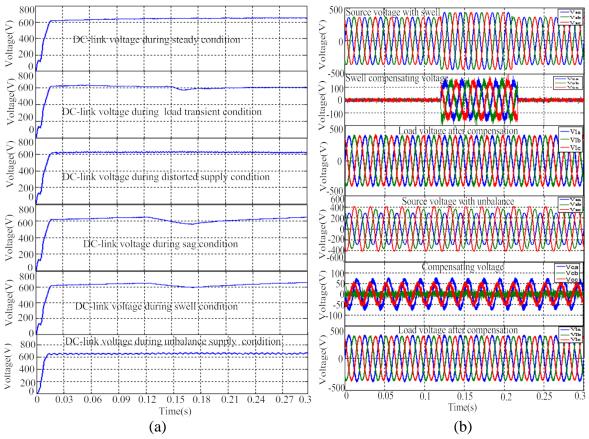

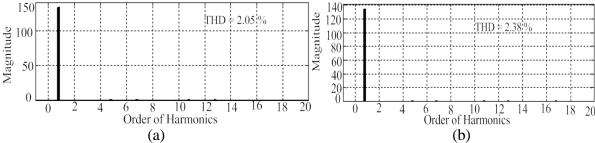

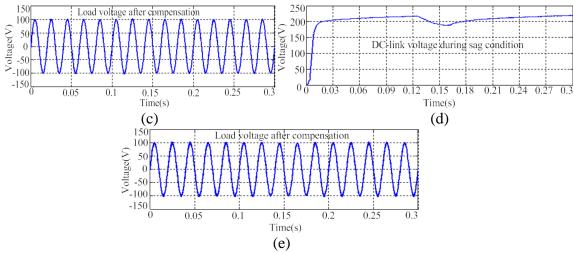

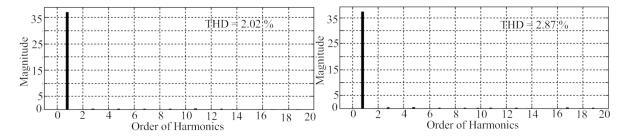

| Figure 4.24 | Current harmonics spectrum before and after compensation, (a) Source current spectrum before compensation during steady-state condition, (b) Source current spectrum after compensation during steady-state condition (c) Source current spectrum before compensation during transient-state condition, (d) Source current spectrum after compensation during transient-state condition                                                                                                                                                                                                                                                                                                                                                    | 129 |

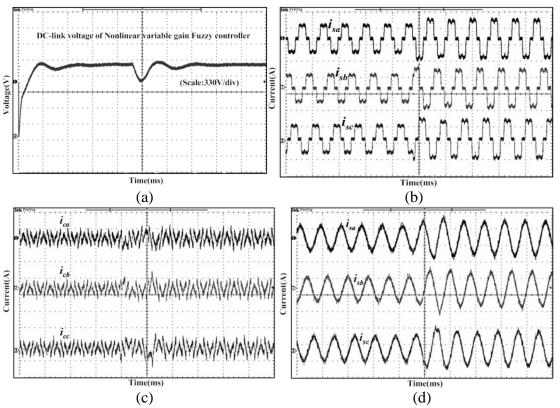

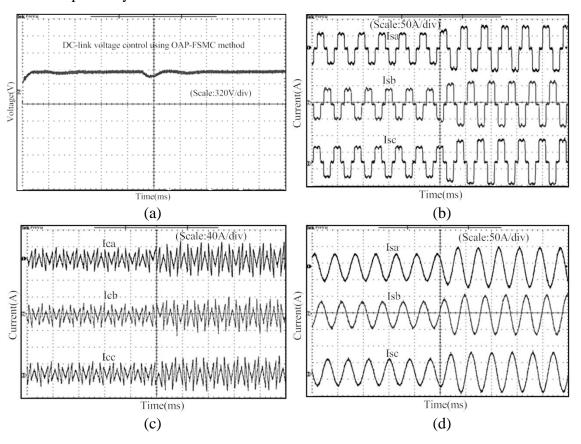

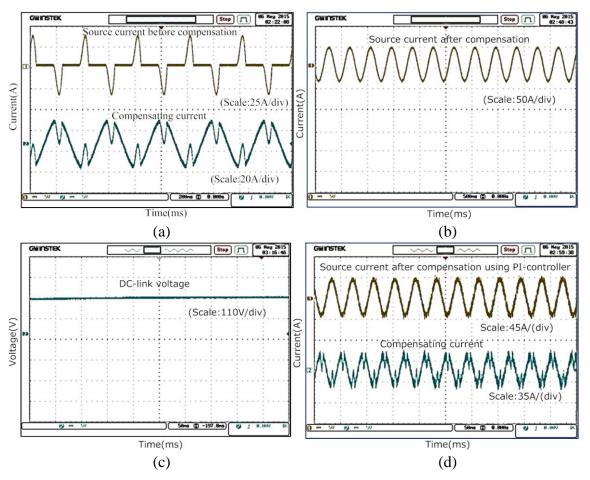

| Figure 4.25 | Experimental results of shunt APF of UPQC during transient condition, (a) DC-link voltage during transient-state, (b) Source current before compensation under transient-state, (c) Compensation current under transient -state (d) Source current after compensation under transient -state                                                                                                                                                                                                                                                                                                           | 130 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

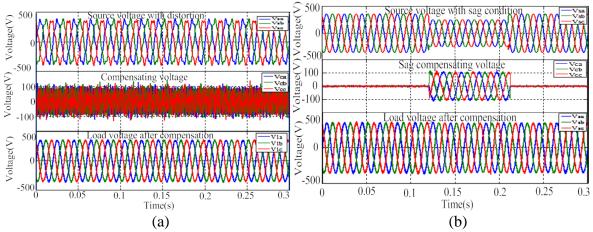

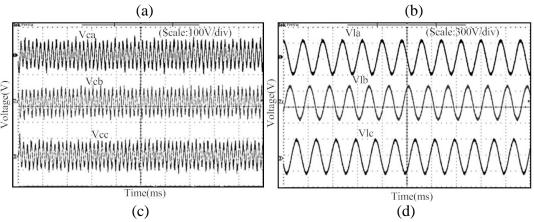

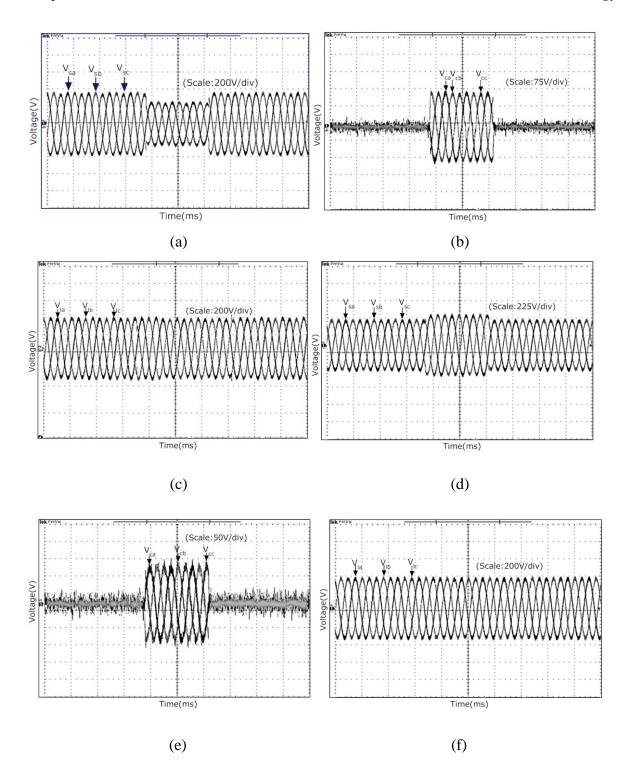

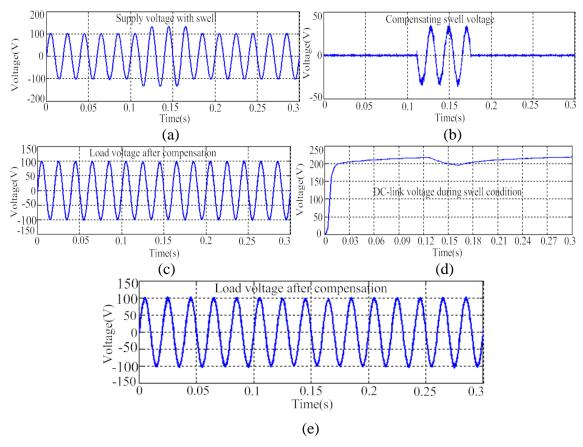

| Figure 4.26 | Simulation result of distorted and supply voltage sag condition, (a) Series APF compensation waveform during voltage distortion condition, (b) Supply voltage sag compensation waveform.                                                                                                                                                                                                                                                                                                                                                                                                               | 131 |

| Figure 4.27 | Voltage distortion and sag compensation spectrum, (a) Distorted supply voltage spectrum, (b) Load voltage spectrum after compensation, (c) Load voltage spectrum after compensation during sag condition                                                                                                                                                                                                                                                                                                                                                                                               | 131 |

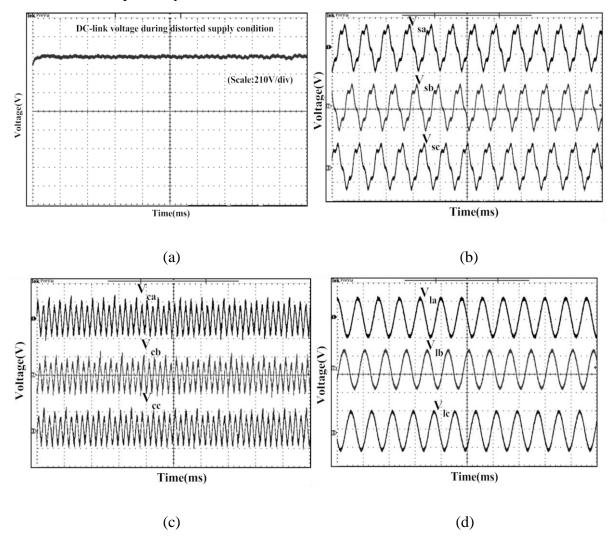

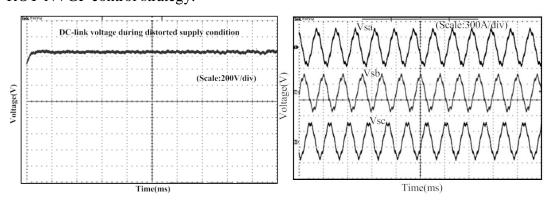

| Figure 4.28 | Experimental results of series APF of UPQC, (a) DC-link voltage during distorted supply condition, (b) Source voltage under distortion condition, (c) Distortion compensation voltage, (d) Load voltage after distortion compensation                                                                                                                                                                                                                                                                                                                                                                  | 132 |

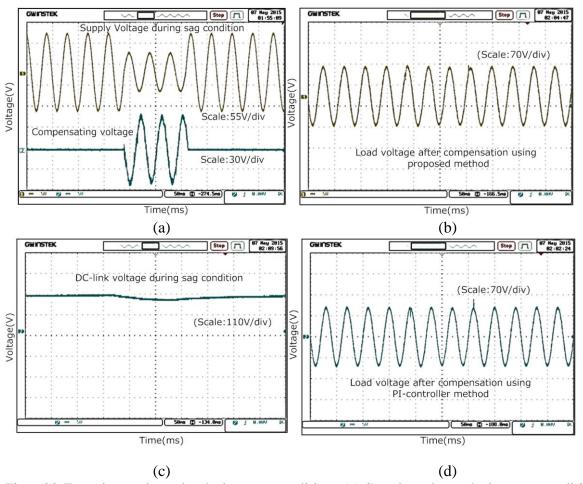

| Figure 4.29 | Experimental results of series APF of UPQC during sag condition, (a) DC-link voltage during sag condition, (b) Sag Voltage, (c) Sag compensation voltage, (d) Load voltage after compensation during sag condition                                                                                                                                                                                                                                                                                                                                                                                     | 133 |