# DESIGN AND IMPLEMENTATION OF NOVEL HIGH PERFORMANCE DOMINO LOGIC

A thesis submitted in partial fulfillment of the requirements for the award of the degree of

**Doctor of Philosophy**

in

**VLSI Design and Embedded Systems**

by

SRINIVASA V S SARMA D

**Roll No: 510EC102**

Under the Guidance of

## Prof. KAMALAKANTA MAHAPATRA

**Electronics and Communication Engineering Department**

**National Institute of Technology**

Rourkela-769008

**Odisha**

2015

# DESIGN AND IMPLEMENTATION OF NOVEL HIGH PERFORMANCE DOMINO LOGIC

A thesis submitted in partial fulfillment of the requirements for the award of the degree of

**Doctor of Philosophy**

in

**VLSI Design and Embedded Systems**

by

SRINIVASA V S SARMA D

**Roll No: 510EC102**

Under the Guidance of

## Prof. KAMALAKANTA MAHAPATRA

**Electronics and Communication Engineering Department**

**National Institute of Technology**

Rourkela-769008

**Odisha**

2015

**CERTIFICATE**

This is to certify that the thesis report entitled "DESIGN AND

IMPLEMENTATION OF NOVEL HIGH PERFORMANCE DOMINO

LOGIC" submitted by Srinivasa V S Sarma D, Roll No: 510EC102, in

partial fulfillment of the requirements for the award of the degree of Doctor of

Philosophy with specialization in "VLSI Design and Embedded Systems"

in Electronics and Communication Engineering at the National Institute

of Technology, Rourkela is an authentic work under my supervision and

guidance.

To the best of my knowledge, the matter embodied in the thesis has not been

submitted to any other University / Institute for the award of any Degree or

Diploma.

Place: NIT ROURKELA

Date:

Prof. K. K. Mahapatra

**Electronics & Communication Engineering Department,**

National Institute of Technology,

Rourkela - 769008.

**Dedicated to**

My parents

**ACKNOWLEDGEMENTS**

This project is by far the most significant accomplishment in my life and it would be

impossible without people (especially my family) who supported me and believed in me.

I express my deep sense of gratitude to Dr. K. K. Mahapatra, Professor in the

Department of Electronics and Communication Engineering, NIT Rourkela for giving me

the opportunity to work under him and lending every support at every stage of this research

work. I am indebted to his esteemed guidance, constant encouragement and fruitful

suggestions from the beginning to the end of this thesis. His trust and support inspired me

in the most important moments of making right decisions and I am really blessed to be

student of him without whom this work would not have been possible.

I am thankful to all my teachers Prof. S.K. Patra, Prof. S. Meher, Prof.

**D.P.Acharva**, **Prof.A.K.Swain** and all other faculty members for providing a solid

background for my studies and research thereafter.

My sincere and heart full thanks to **Dr. S. K. Sarangi, Director** of **NIT-Rourkela**,

for providing the working platform and required research equipment in the department

laboratory at NIT.

Also, I would like to thank all my classmates and friends (Bhaskar, Govind, Vijay,

Preethi, Ramakrishna, Rajesh Patjoshi, Gokulanand and others) of VLSI lab who always

encouraged me in the successful completion of my thesis work. I am indebted to the

service provided by Ayas sir, sudi, Tom, Sauvagya, Venkat Ratnam and Jagannath who

helped me in crucial stage of submission of my thesis.

Finally, I thank GOD-Almighty for being with me forever end ever.

SRINIVASA V S SARMA D

**Roll No: 510EC102**

i

## **ABSTRACT**

This dissertation presents design and implementation of novel high performance domino logic techniques with increased noise robustness and reduced leakages. The speed and overhead area became the primary parameters of choice for fabrication industry that led to invention of clocked logic styles named as Dynamic logic and Domino logic families. Most importantly, power consumption, noise immunity, speed of operation, area and cost are the predominant parameters for designing any kind of digital logic circuit technique with effective trade-off amongst these parameters depending on the situation and application of design.

Because of its high speed and low overhead area domino logic became process of choice for designing of high speed application circuits. The concerning issues are large power consumption and high sensitivity towards noise. Hence, there is a need for designing new domino methodology to meet the requirements by overcoming above mentioned drawbacks which led to ample opportunities for diversified research in this field. Therefore, the outcome of research must be able to handle the primary design parameters efficiently. Besides this, the designed circuit must exhibit high degree of robustness towards noise.

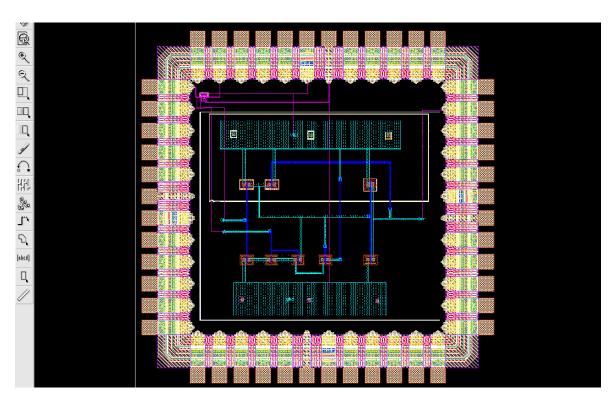

In this thesis, few domino logic circuit techniques are proposed to deal with noise and sub-threshold leakages. Effect of signal integrity issues on domino logic techniques is studied. Furthermore, having been subjected to process corner analysis and noise analysis, the overall performance of proposed domino techniques is found to be enhanced despite a few limitations that are mentioned in this work. Besides this, lector based domino and dynamic node stabilized techniques are also proposed and are investigated thoroughly. Simulations show that proposed circuits are showing superior performance. In addition to this, domino based Schmitt triggers with various hysteresis phenomena are designed and simulated. Pre-layout and post-layout simulation results are compared for proposed Schmitt trigger. Simulations reveal that proposed Schmitt trigger techniques are more noise tolerant than CMOS counterparts. Moreover, a test chip for domino based Schmitt trigger is done in UMC 180 nm technology for fabrication.

## **Contents**

| ACKNOV  | WLEDGEMENTS                                                  |          |

|---------|--------------------------------------------------------------|----------|

| ABSTRA  | CT                                                           | i        |

| LIST OF | FIGURES                                                      | V        |

| LIST OF | TABLES                                                       | x        |

| ABBREV  | TATIONS                                                      | xi       |

| СНАРТЕ  | R 1                                                          | 1        |

| INTROD  | UCTION                                                       | 1        |

| 1.1 I   | Introduction                                                 | 1        |

| 1.2 I   | History                                                      | 2        |

| 1.3     | Motivation                                                   | 3        |

| 1.4     | Objectives of the research work                              | 3        |

| 1.5     | Thesis structure and over all contribution                   | 3        |

| 1.6     | Conclusion                                                   | 5        |

| СНАРТЕ  | R 2                                                          | <i>6</i> |

| OVERVI  | EW OF LOGIC STYLES AND RELATED WORK                          | 6        |

| 2.1     | CMOS AND NMOS                                                | <i>6</i> |

| 2.2 I   | Different static logic styles                                | 12       |

| 2.2.1   | Pseudo N-MOS                                                 | 12       |

| 2.2.2   | Differential Cascode Voltage Swing Logic (DCVSL)             | 13       |

| 2.2.3   | Pass Transistor Logic                                        | 14       |

| 2.2.4   | Differential / Complementary Pass Transistor Logic           | 15       |

| 2.3 I   | Dynamic CMOS logic design                                    | 17       |

| 2.4 I   | Domino logic circuits                                        | 19       |

| 2.4.1   | Impact on power consumption                                  | 23       |

| 2.4.2   | Technique to compensate charge lost, through PMOS keeper     | 26       |

| 2.5     | Conclusion                                                   | 31       |

| СНАРТЕ  | R 3                                                          | 32       |

| NOVEL I | DOMINO LOGIC TOPOLOGIES                                      | 32       |

| 3.1 I   | Introduction                                                 | 32       |

| 3.2 I   | Different high-performance noise tolerant circuit techniques | 34       |

| 3.2.1   | Wide fan-in Domino OR gate-Footless and Footed schemes       | 34       |

| 3.2   | 2.2      | Wide fan-in Domino OR gate Diode footed scheme                        | 37  |

|-------|----------|-----------------------------------------------------------------------|-----|

| 3.2   | 2.3      | Wide fan-in Domino OR gate-Replicated evaluation scheme               | 40  |

| 3.2   | 2.4      | Wide fan-in Domino OR gate-Dynamic node footed scheme                 | 41  |

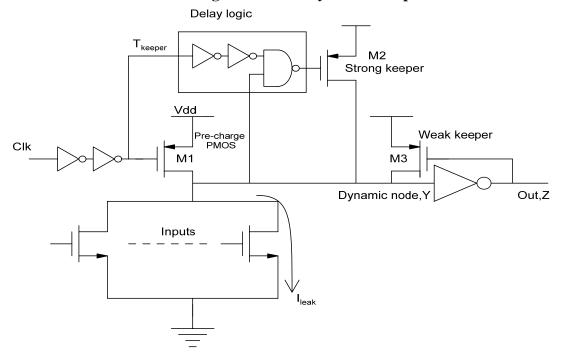

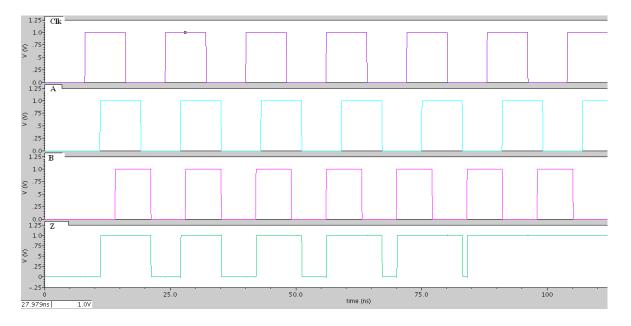

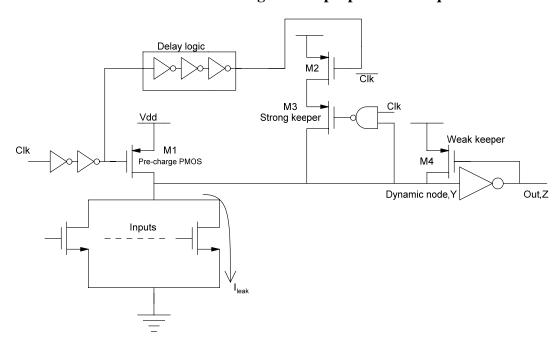

| 3.2   | 2.5      | Wide fan-in Domino OR gate-Clock delayed single keeper scheme         | 44  |

| 3.2   | 2.6      | Wide fan-in Domino OR gate-Clock delayed dual keeper scheme           | 45  |

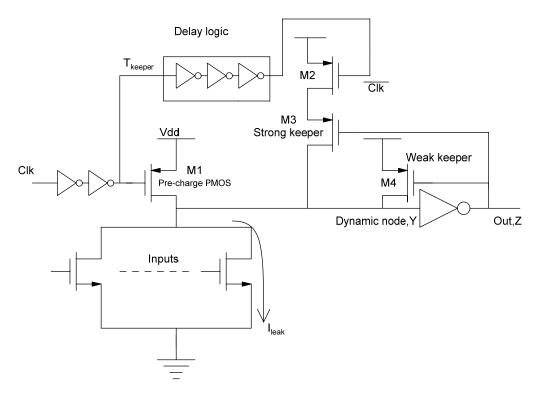

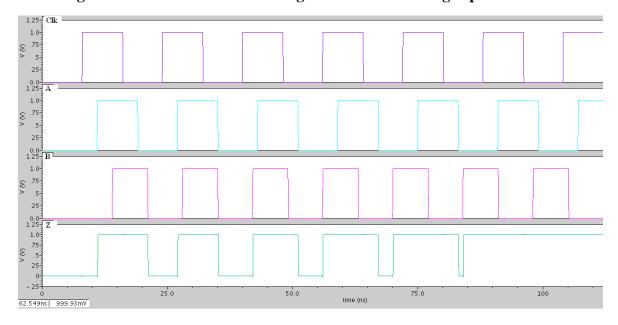

| 3.2   | 2.7      | Wide fan-in Domino OR gate-Skew tolerant high speed scheme            | 47  |

|       | 2.8 heme | Wide fan-in Domino OR gate-Source following evaluation gate (SFEG) 49 |     |

| 3.3   | UNC      | G & ANTE                                                              | 50  |

| 3.4   | Proc     | ess Corner analysis                                                   | 53  |

| 3.5   | Nove     | el high-performance noise tolerant domino logic circuit techniques    | 55  |

| 3.:   | 5.1      | Wide fan-in domino OR gate with proposed technique-1                  | 55  |

| 3.:   | 5.2      | Wide fan-in domino OR gate with proposed technique-2                  | 60  |

| 3.:   | 5.3      | Wide fan-in domino OR gate with proposed technique-3                  | 65  |

| 3.6   | Simu     | ulation results and discussion                                        | 71  |

| 3.7   | Conc     | clusion                                                               | 80  |

| CHAP' | TER 4    |                                                                       | 82  |

| SIGNA | AL INT   | EGRITY ISSUES & MODIFIED CIRCUIT TECHNIQUES                           | 82  |

| 4.1   | Intro    | duction                                                               | 82  |

| 4.2   | Sign     | al integrity issues in clocked logic circuits                         | 84  |

| 4.3   | Rela     | ted work on lector power reduction technique                          | 97  |

| 4.4   | Prop     | osed Domino lector technique and dynamic node stabilizing technique   | 101 |

| 4.5   | Simu     | ulation results and discussion                                        | 114 |

| 4.6   | Conc     | clusion                                                               | 122 |

| CHAP' | TER 5    |                                                                       | 125 |

| DESIC | GN OF    | VARIOUS DOMINO BASED SCHMITT TRIGGER CIRCUITS                         | 125 |

| 5.1   | Intro    | duction                                                               | 125 |

| 5.2   | Conv     | ventional Schmitt triggers                                            | 126 |

| 5.2   | 2.1      | Op-amp based Schmitt trigger                                          | 126 |

| 5.2   | 2.2      | CMOS Schmitt trigger                                                  | 131 |

| 5.3   | Prop     | osed domino Schmitt trigger                                           | 142 |

| 5.3   | 3.1      | Proposed domino Schmitt trigger-1                                     | 142 |

| 5.3     | 2 Proposed     | l domino Schmitt trigger-2                | 147 |

|---------|----------------|-------------------------------------------|-----|

| 5.4     | Results and di | iscussion                                 | 152 |

| 5.5     | Conclusion     |                                           | 155 |

| CHAPT   | ER 6           |                                           | 156 |

| CHIP T  | APE-OUT        |                                           | 156 |

| 6.1     | Introduction   |                                           | 156 |

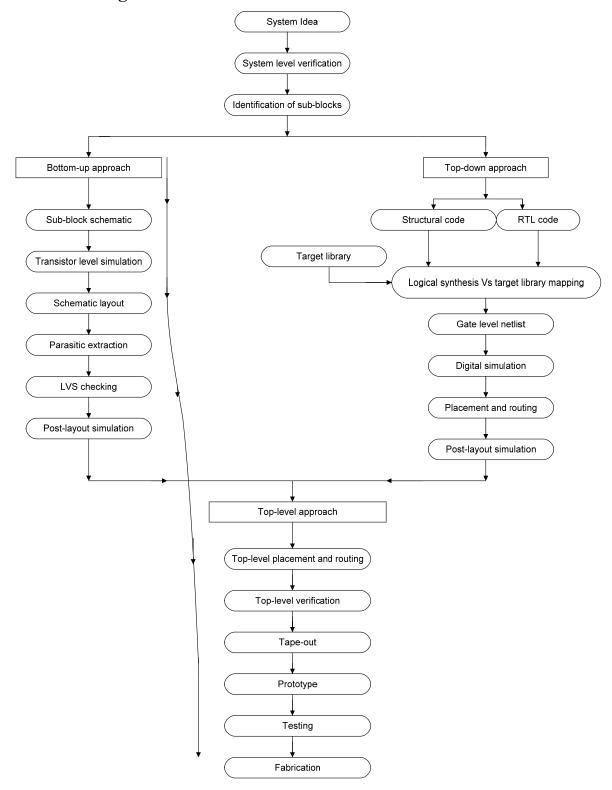

| 6.2     | VLSI design f  | flow                                      | 157 |

| 6.2     | 1 Bottom-u     | up (Back-end design) approach             | 158 |

| 6.2     | 2 Top-dow      | rn (Front-end design) approach            | 160 |

| 6.2     | 3 Top-leve     | l approach                                | 160 |

| 6.3     | Test chip of p | proposed domino Schmitt trigger circuit-1 | 161 |

| 6.4     | Results and di | iscussion                                 | 169 |

| 6.5     | Conclusion     |                                           | 170 |

| CHAPT   | ER 7           |                                           | 171 |

| CONCI   | USIONS & FU    | UTURE WORK                                | 171 |

| 7.1     | Conclusions    |                                           | 171 |

| 7.2     | Future work    |                                           | 173 |

| Bibliog | aphy           |                                           | 174 |

## LIST OF FIGURES

| Fig. 1.1 Moore's law                                                                | 2  |

|-------------------------------------------------------------------------------------|----|

| Fig. 2.1 Static CMOS logic Inverter                                                 | 6  |

| Fig. 2.2 Static CMOS 2-input NAND gate                                              | 7  |

| Fig. 2.3 Static CMOS 2-input NAND gate simulation                                   | 8  |

| Fig. 2.4 NMOS 2-input NAND gate                                                     | 11 |

| Fig. 2.5 NMOS 2-input NAND gate simulation                                          | 11 |

| Fig. 2.6 Pseudo N-MOS Logic                                                         | 12 |

| Fig. 2. 7 Differential Cascode Voltage Swing Logic                                  | 13 |

| Fig. 2.8 Pass Transistor Logic implementation of 2-input AND gate                   | 14 |

| Fig. 2.9 Differential/Complementary Pass Transistor Logic implementation of 2-input |    |

| AND gate                                                                            | 15 |

| Fig. 2.10 Transmission Gate                                                         | 16 |

| Fig. 2.11 2:1 Multiplexer using Transmission Gate                                   | 16 |

| Fig. 2.12 Dynamic CMOS logic                                                        | 17 |

| Fig. 2.13 Block diagram of Domino logic                                             | 19 |

| Fig. 2.14 Domino CMOS logic                                                         | 20 |

| Fig. 2.15 Domino CMOS 2-input AND gate                                              | 20 |

| Fig. 2.16 Domino CMOS 2-input AND gate simulation                                   | 21 |

| Fig. 2.17 Domino CMOS 2-input AND gate                                              | 24 |

| Fig. 2.18 Domino CMOS 2-input AND gate simulation                                   | 25 |

| Fig. 2.19 Clock signal in Domino logic Circuit                                      | 26 |

| Fig. 2.20 Domino CMOS logic circuit with weak PMOS Keeper                           | 27 |

| Fig. 2.21 Domino CMOS 2 Input AND gate with weak PMOS Keeper                        | 29 |

| Fig. 2.22 A Domino CMOS 2 Input AND gate with weak PMOS Keeper simulation           | 29 |

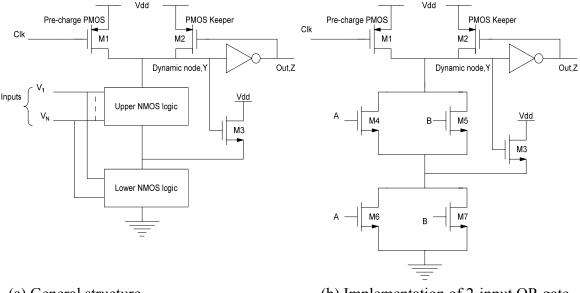

| Fig. 3.1 Wide fan-in domino OR gate-footless                                        | 34 |

| Fig. 3.2 Wide fan-in domino OR gate-footed                                          | 34 |

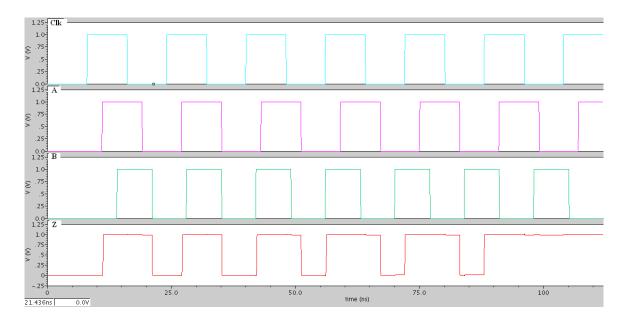

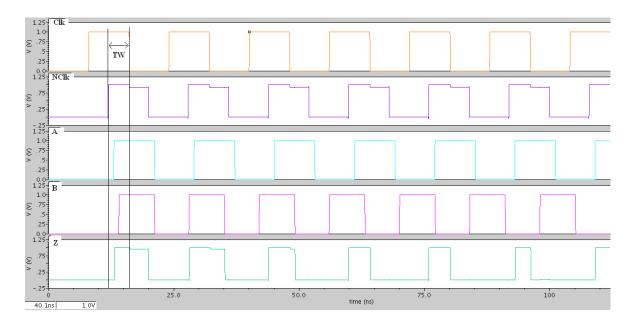

| Fig. 3.3 Domino 2-input OR gate-footless simulation                                 | 36 |

| Fig. 3.4 Domino 2-input OR gate-footed simulation                                   | 37 |

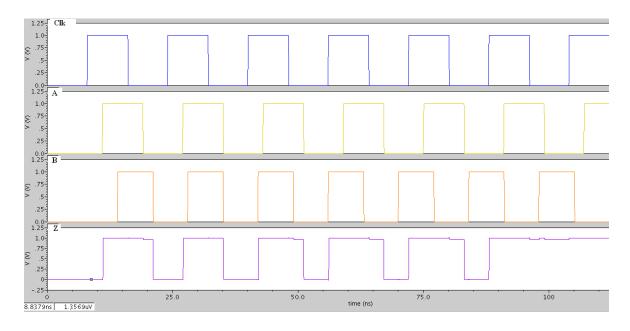

| Fig. 3.5 Wide fan-in Domino OR gate-Diode footed scheme                             | 37 |

| Fig. 3.6 Domino 2-input OR gate-Diode footed scheme simulation                      | 38 |

| Fig. 3.7 Wide fan-in Domino OR gate-Replicated evaluation scheme                    | 40 |

| Fig. 3.8 Domino 2-input OR gate-Replicated evaluation scheme simulation             | 40 |

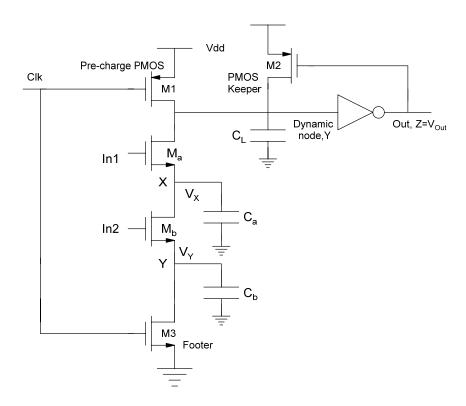

| Fig. 3.9 Wide fan-in Domino OR gate-Dynamic node footed scheme                      | 41 |

| Fig. 3.10 Domino 2-input OR gate-Dynamic node footed scheme simulation              | 42 |

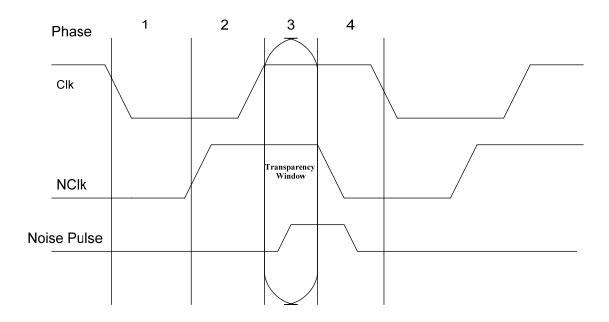

| Fig. 3.11 Transparency Window-phase3 waveform                                       | 43 |

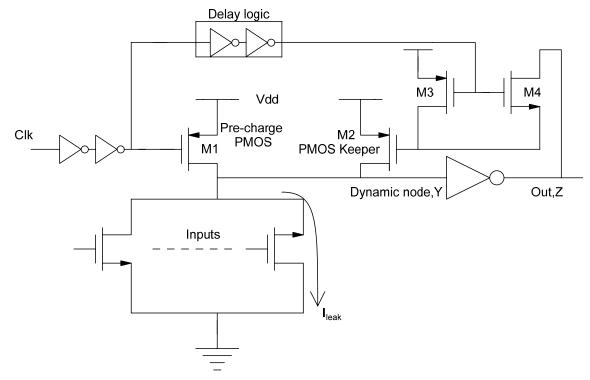

| Fig. 3.12 Wide fan-in Domino OR gate-Clock delayed single keeper scheme             | 44 |

| Fig. 3.13 Domino 2-input OR gate-Clock delayed single keeper scheme simulation      | 45 |

| Fig. 3.14 Wide fan-in Domino OR gate-Clock delayed dual keeper scheme               | 45 |

| Fig. 3.15 Domino 2-input OR gate-Clock delayed dual keeper scheme simulation        | 46 |

| Fig. 3.16 Wide fan-in Domino OR gate-Skew tolerant high speed scheme                | 47 |

| Fig. 3.17 Domino 2-input OR gate-Skew tolerant high speed scheme simulation         | 47    |

|-------------------------------------------------------------------------------------|-------|

| Fig. 3.18 Wide fan-in Domino OR gate-Source following evaluation gate (SFEG) scher  |       |

|                                                                                     | 49    |

| Fig. 3.19 Domino 2-input OR gate -Source following evaluation gate (SFEG) scheme    | 40    |

| simulation                                                                          | 49    |

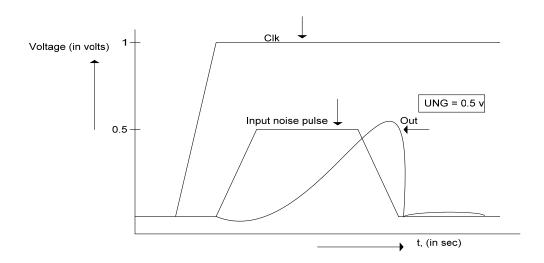

| Fig. 3.20 Typical UNG measurement wave form                                         |       |

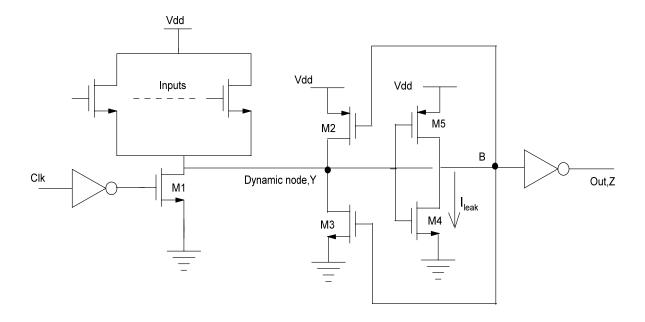

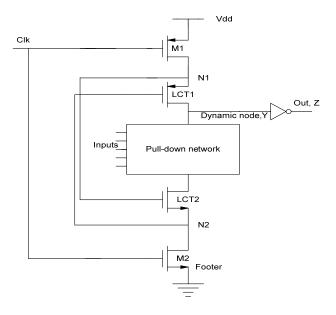

| Fig. 3.21 Wide fan-in domino OR gate with proposed technique-1                      |       |

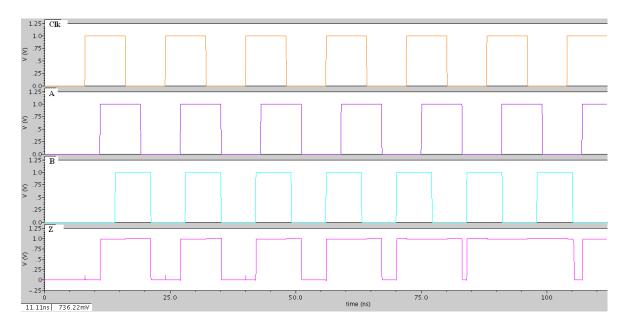

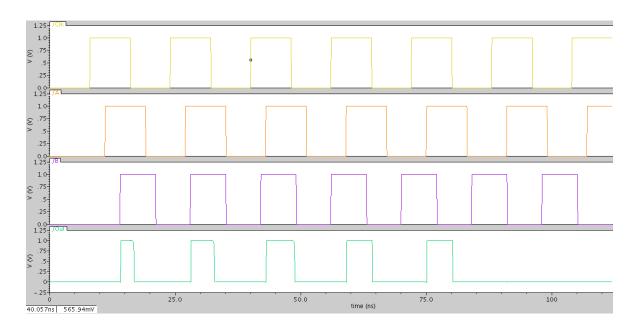

| Fig. 3.22 Domino 2-input OR gate with proposed technique-1 simulation               |       |

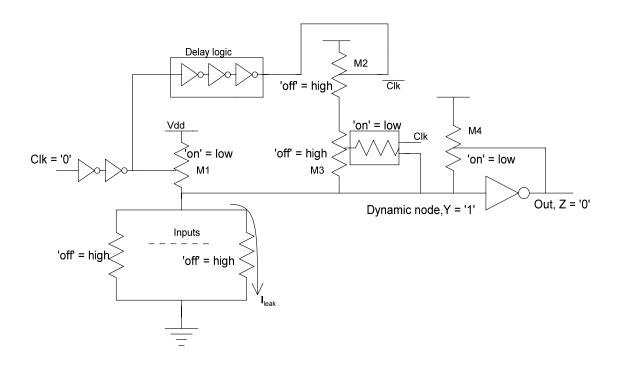

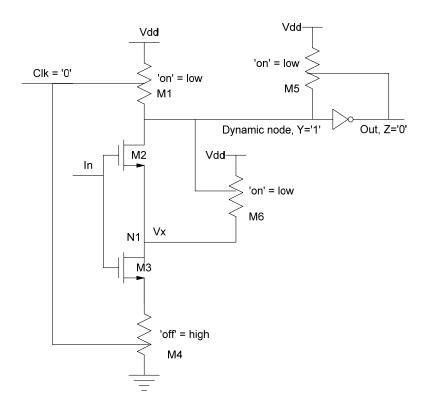

| Fig. 3.23 Pre-charge operation of proposed technique-1                              |       |

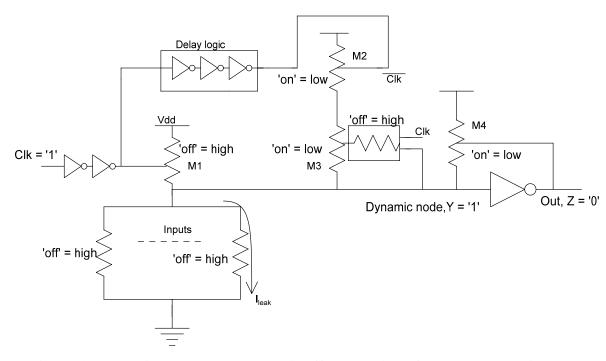

| Fig. 3.24 Evaluation phase when PDN is off - operation of proposed technique-1      |       |

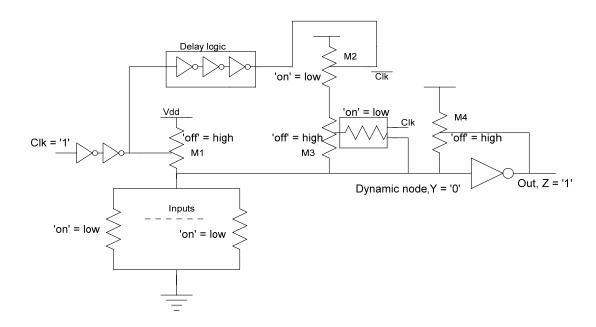

| Fig. 3.25 Evaluation phase when PDN is on - operation of proposed technique-1       |       |

| Fig. 3.26 Wide fan-in domino OR gate with proposed technique-2                      | 60    |

| Fig. 3.27 Domino 2-input OR gate with proposed technique-2 simulation               |       |

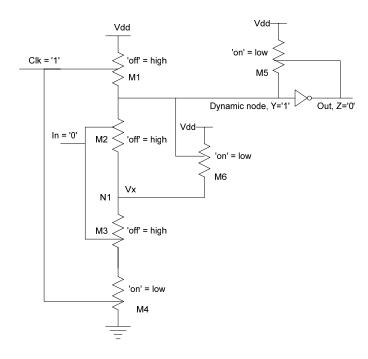

| Fig. 3.28 Pre-charge operation of proposed technique-2                              | 62    |

| Fig. 3.29 Evaluation phase when PDN is off - operation of proposed technique-1      | 63    |

| Fig. 3.30 Evaluation phase when PDN is on - operation of proposed technique-2       | 64    |

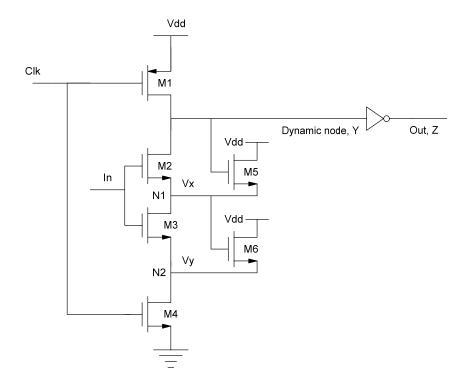

| Fig. 3.31 Wide fan-in domino OR gate with proposed technique-3                      | 65    |

| Fig. 3.32 Domino 2-input OR gate with proposed technique-3 simulation               | 65    |

| Fig. 3.33 A Transmission logic gate circuit                                         | 66    |

| Fig. 3.34 A 2:1 Multiplexer using transmission logic gate circuit                   | 67    |

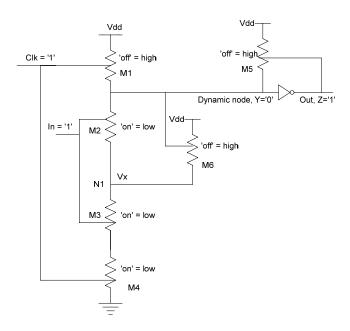

| Fig. 3.35 Pre-charge operation of proposed technique-3                              | 68    |

| Fig. 3.36 Evaluation phase when PDN is off - operation of proposed technique-3      | 69    |

| Fig. 3.37 Evaluation phase when PDN is on - operation of proposed technique-3       | 70    |

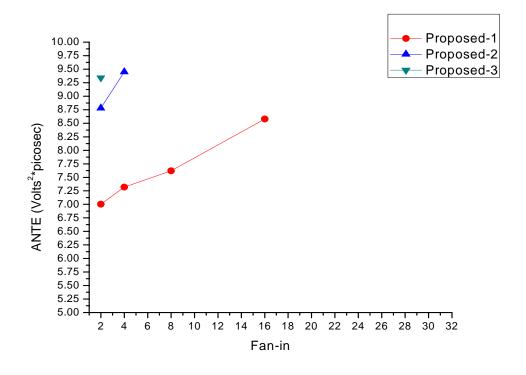

| Fig. 3.38 ANTE Vs Fan-in for Process corner=NN                                      | 75    |

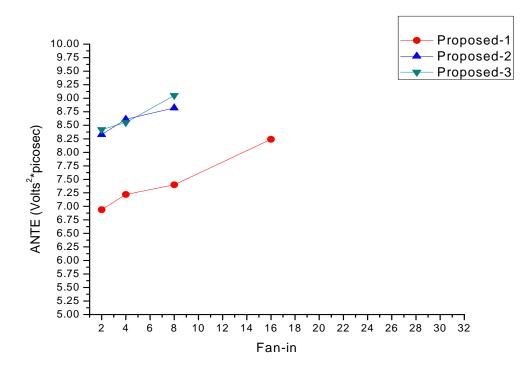

| Fig. 3.39 ANTE Vs Fan-in for Process corner=FF                                      | 76    |

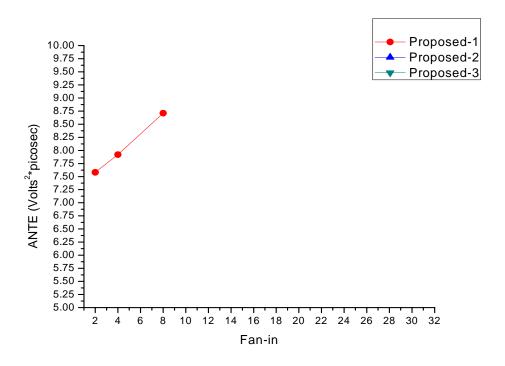

| Fig. 3.40 ANTE Vs Fan-in for Process corner=SS                                      | 76    |

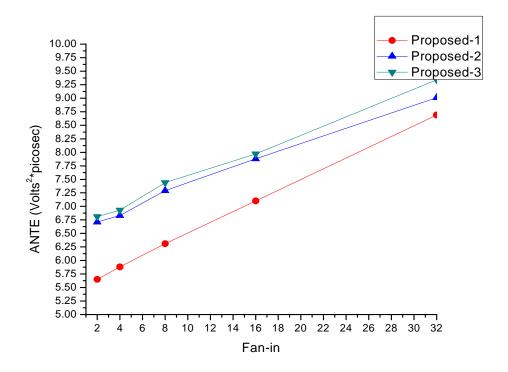

| Fig. 3.41 ANTE Vs Fan-in for Process corner=FS                                      | 77    |

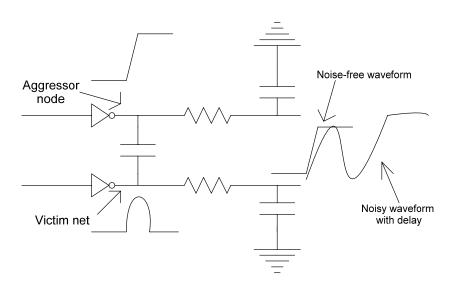

| Fig. 4.1 Cross talk noise effect.                                                   | 85    |

| Fig. 4.2 Charge leakages in dynamic logic circuit                                   | 86    |

| Fig. 4.3 Keeper with always ON configuration                                        | 88    |

| Fig. 4.4 Keeper with feedback configuration                                         | 88    |

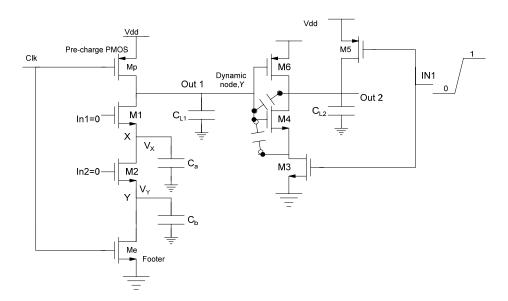

| Fig. 4.5 Charge sharing analysis with 2-input domino AND gate                       | 89    |

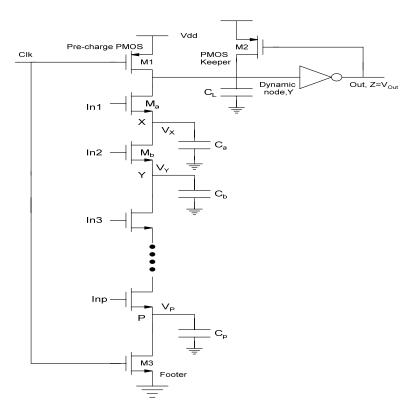

| Fig. 4.6 Charge sharing analysis with wide fan-in (with fan-in=P) domino AND gate   | 93    |

| Fig. 4.7 Capacitive coupling phenomenon in domino logic circuits                    | 94    |

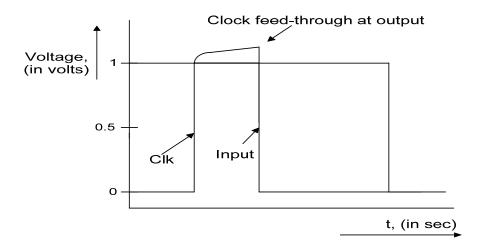

| Fig. 4.8 Clock feed-through phenomenon dynamic logic circuits                       | 96    |

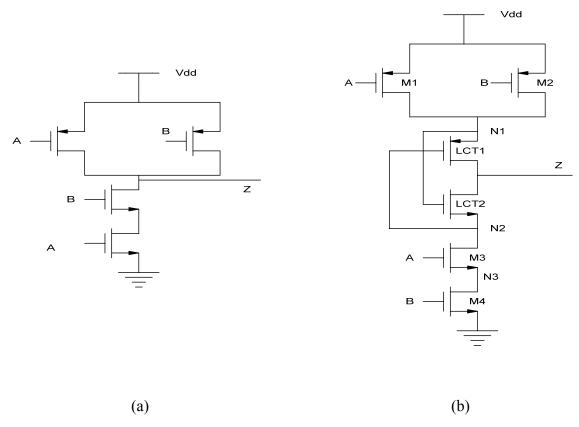

| Fig. 4.9 Implementation of 2-input NAND gate using (a) static CMOS (b) lector schem | ie 99 |

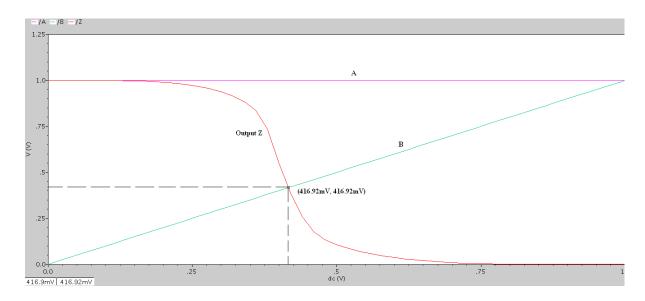

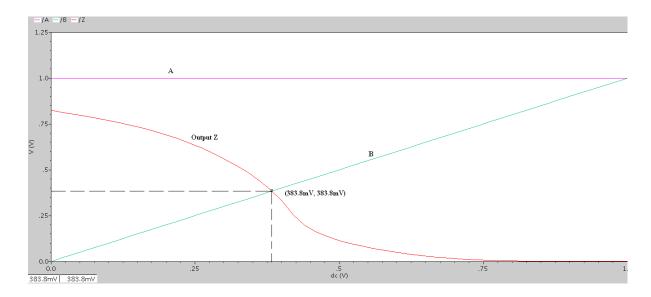

| Fig. 4.10 DC characteristics of 2-input static CMOS NAND gate                       | .100  |

| Fig. 4.11 DC characteristics of 2-input lector NAND gate                            |       |

| Fig. 4.12 Direct method of implementing lector domino logic circuit                 |       |

| Fig. 4.13 Proposed lector domino logic circuit technique                            |       |

| Fig. 4.14 Simulation of Proposed lector 2-input domino OR gate logic circuit        |       |

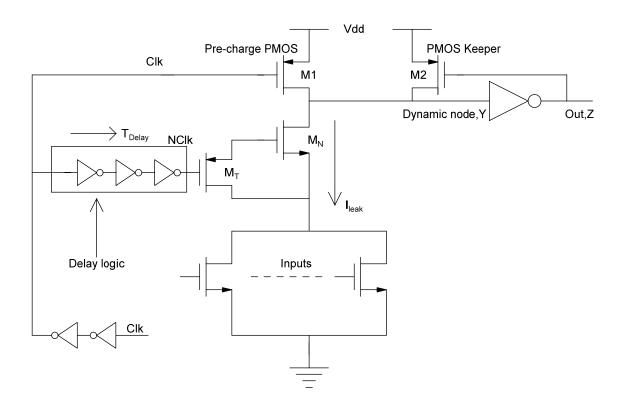

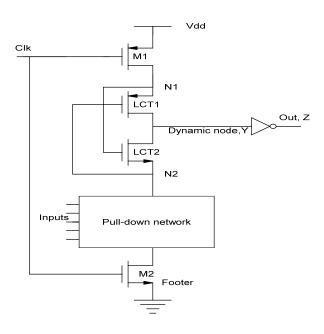

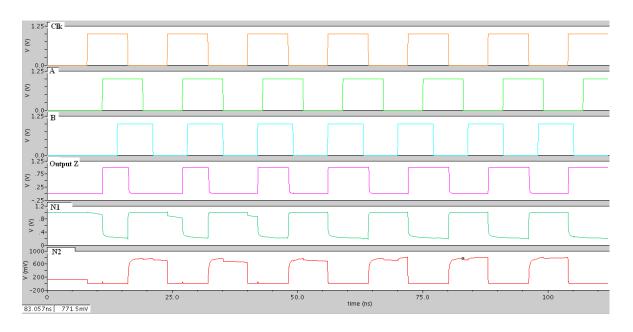

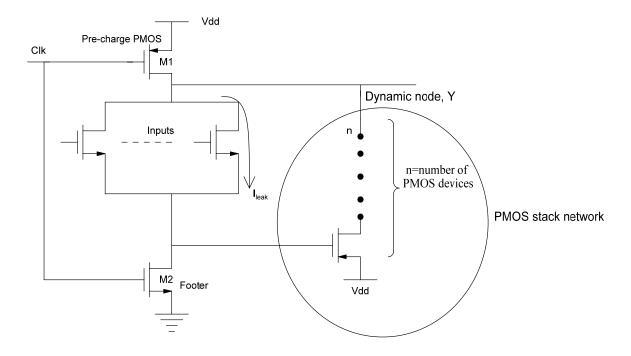

| Fig. 4.15 Proposed dynamic node stabilizing technique                                      | 105 |

|--------------------------------------------------------------------------------------------|-----|

| Fig. 4.16 Proposed dynamic node stabilizing technique applied to basic domino logic        | ;   |

| circuit                                                                                    | 106 |

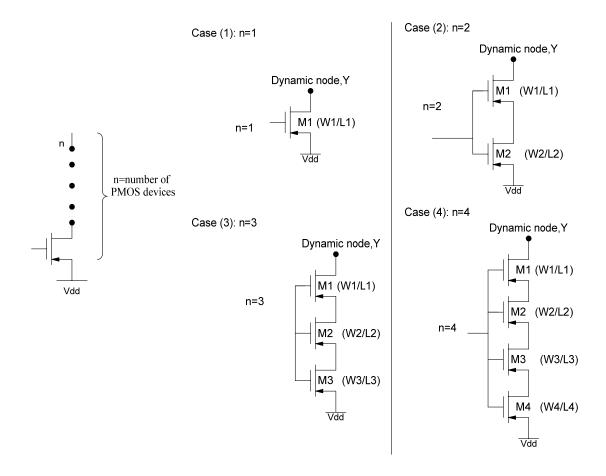

| Fig. 4.17 Impact of PMOS stack network on power consumption                                | 108 |

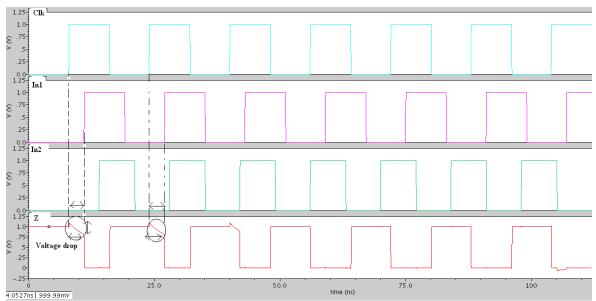

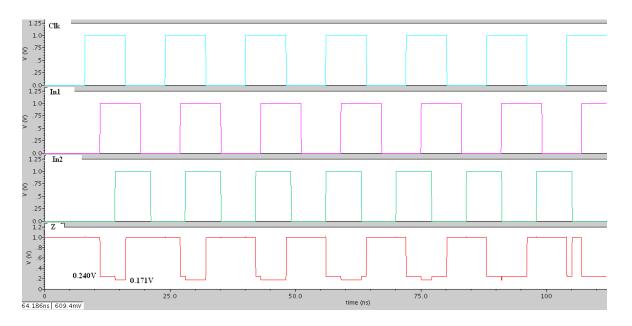

| Fig. 4.18 Dynamic node voltage drop for 2-input dynamic NOR gate                           | 111 |

| Fig. 4.19 Dynamic node voltage drop for 2-input dynamic NOR gate with n=1                  | 112 |

| Fig. 4.20 Dynamic node voltage drop for 2-input dynamic NOR gate with n=8                  | 112 |

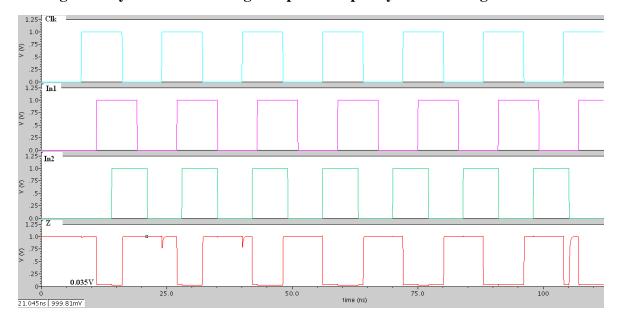

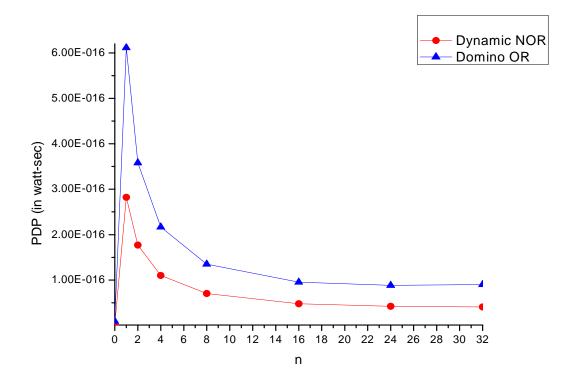

| Fig. 4.21 Variation of Power-delay-product with number (n) of PMOS stack devices           | for |

| proposed dynamic and domino 2-input OR gate                                                | 119 |

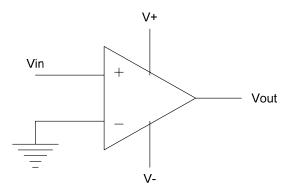

| Fig. 5.1 Basic open-loop polarity indicator                                                | 126 |

| Fig. 5.2 Basic open-loop comparator                                                        | 127 |

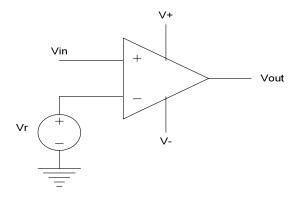

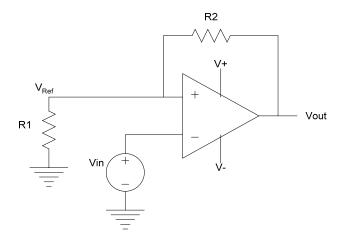

| Fig. 5.3 Op-amp based Schmitt trigger configuration                                        | 128 |

| Fig. 5.4 Output of op-amp based Schmitt trigger with respect to various reference sig      | nal |

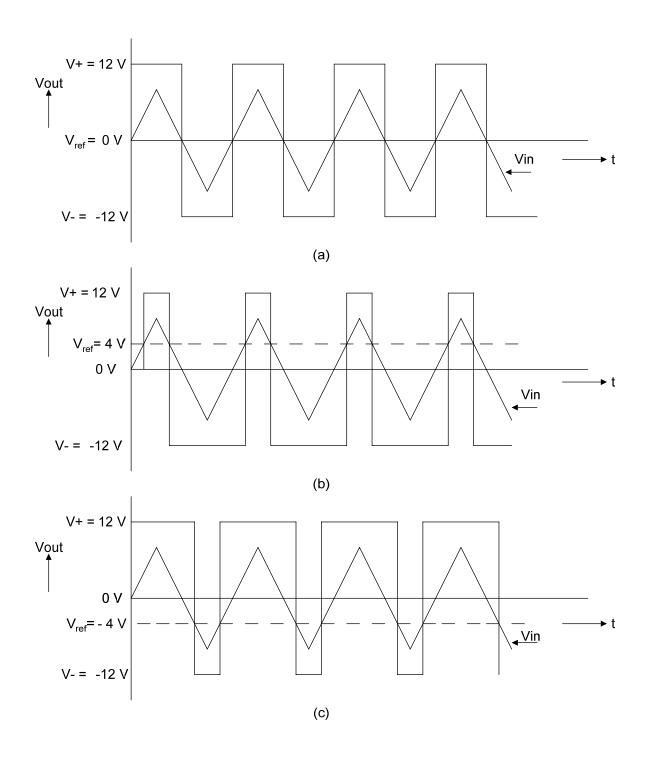

| voltages When $V_{ref} = 0 V$ , (b) When $V_{ref} = 4 V$ and (c) When $V_{ref} = -4 V [5]$ | 129 |

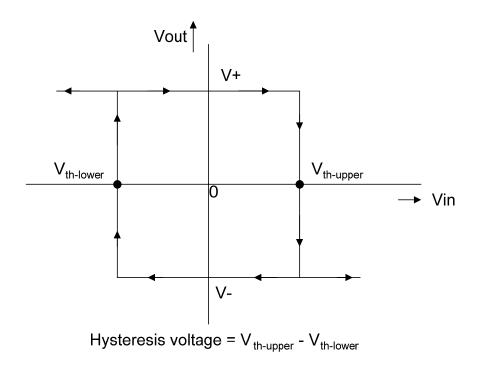

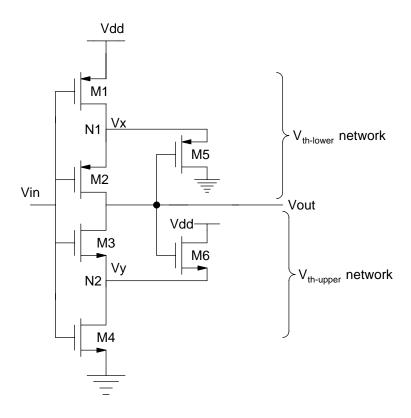

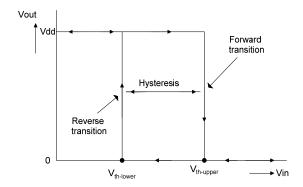

| Fig. 5.5 Hysteresis of op-amp based Schmitt trigger                                        | 130 |

| Fig. 5.6 CMOS Schmitt trigger (ST)-1                                                       | 132 |

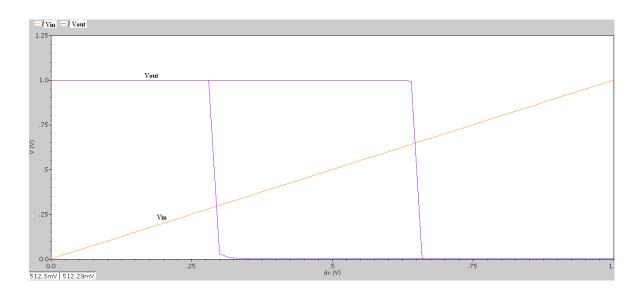

| Fig. 5.7 Voltage Transfer Characteristic (VTC) curve of CMOS Schmitt trigger-1             | 133 |

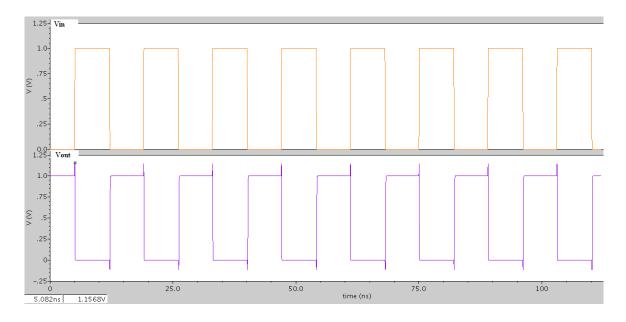

| Fig. 5.8 Simulation of transient response of CMOS Schmitt trigger (ST)-1                   | 135 |

| Fig. 5.9 Simulation of DC response (VTC) of CMOS Schmitt trigger (ST)-1                    | 135 |

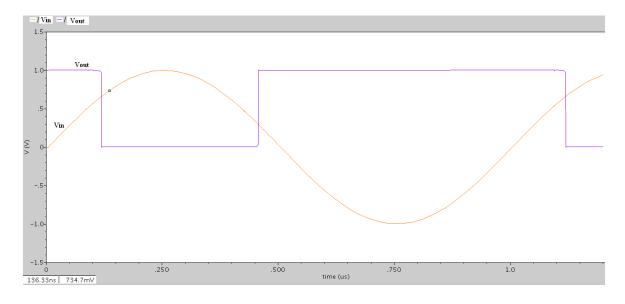

| Fig. 5.10 Simulation of sinusoidal response of CMOS Schmitt trigger (ST)-1                 | 136 |

| Fig. 5.11 CMOS Schmitt trigger (ST)-2                                                      | 137 |

| Fig. 5.12 Simulation of DC response (VTC) of CMOS Schmitt trigger (ST)-2                   | 137 |

| Fig. 5.13 Simulation of transient response of CMOS Schmitt trigger (ST)-2                  | 138 |

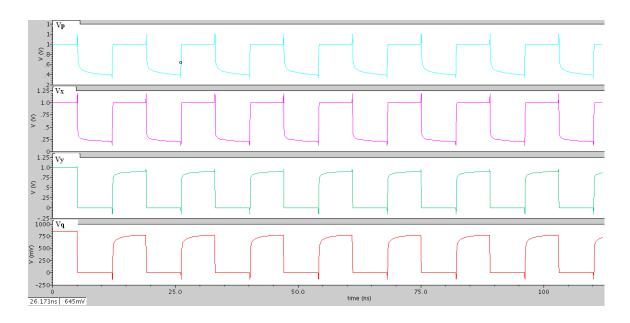

| Fig. 5.14 Node voltages of CMOS Schmitt trigger (ST)-2                                     | 138 |

| Fig. 5.15 Simulation of sinusoidal response of CMOS Schmitt trigger (ST)-2                 | 139 |

| Fig. 5.16 Schmitt trigger (ST)-3 Fig. 5.17 Schmitt trigger (ST)-4                          | 140 |

| Fig. 5.18 Schmitt trigger (ST)-5                                                           | 140 |

| Fig. 5.19 Transient and DC response of Schmitt trigger (ST)-3                              | 141 |

| Fig. 5.20 Transient and DC response of Schmitt trigger (ST)-4                              | 141 |

| Fig. 5.21 Transient and DC response of Schmitt trigger (ST)-5                              | 142 |

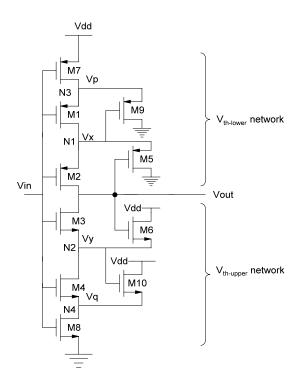

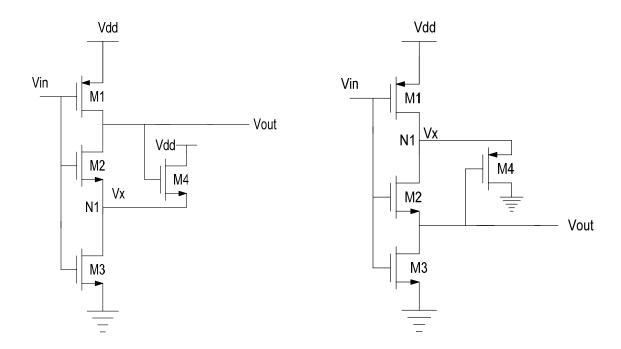

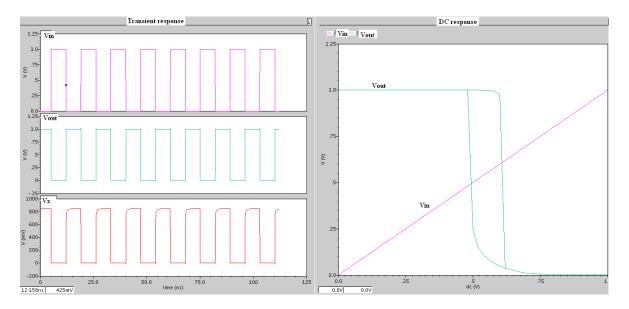

| Fig. 5.22 Proposed domino Schmitt trigger-1                                                | 143 |

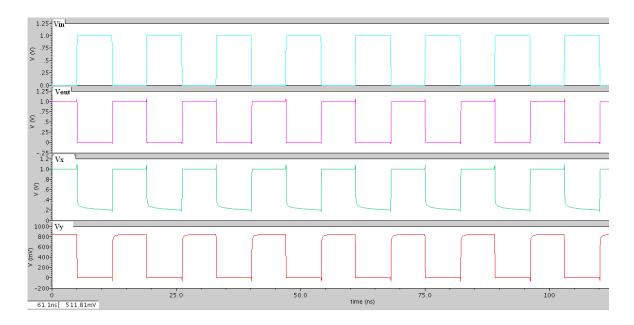

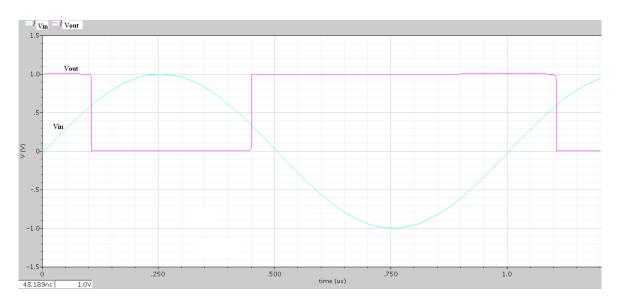

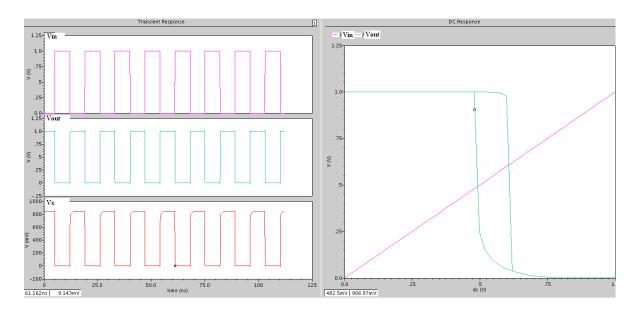

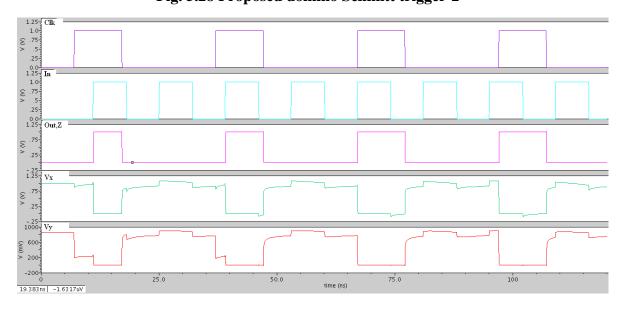

| Fig. 5.23 Simulation of transient response of domino Schmitt trigger-1                     | 143 |

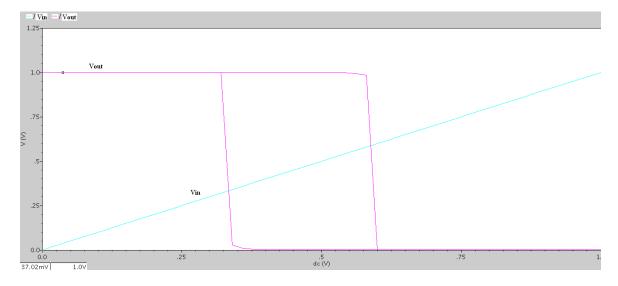

| Fig. 5.24 Simulation of DC response (VTC) of domino Schmitt trigger-1                      | 144 |

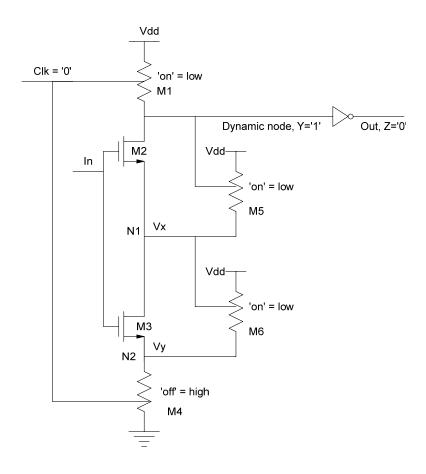

| Fig. 5.25 Pre-charge operation of proposed domino Schmitt trigger-1                        | 145 |

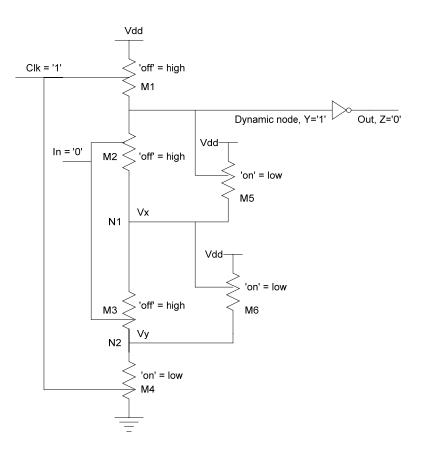

| Fig. 5.26 Evaluation phase when PDN is off - operation of proposed domino Schmitt          |     |

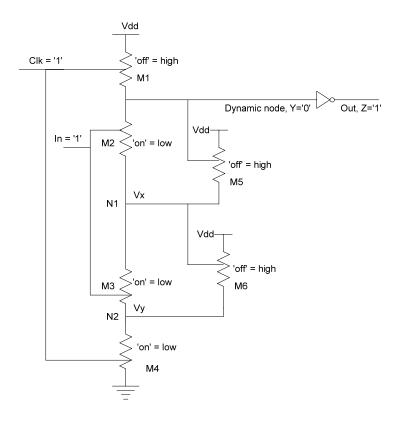

| trigger-1                                                                                  | 146 |

| Fig. 5.27 Evaluation phase when PDN is on - operation of proposed domino Schmitt           |     |

| trigger-1                                                                                  |     |

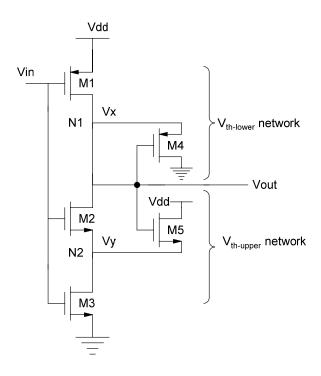

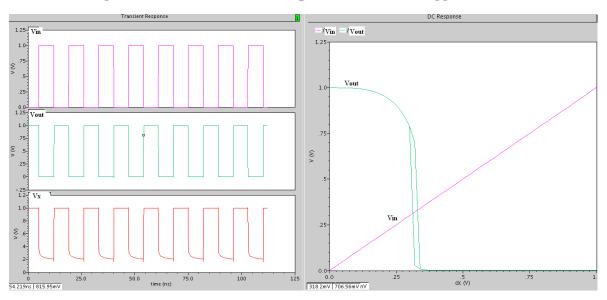

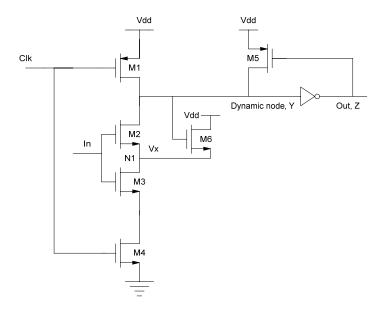

| Fig. 5.28 Proposed domino Schmitt trigger-2                                                | 148 |

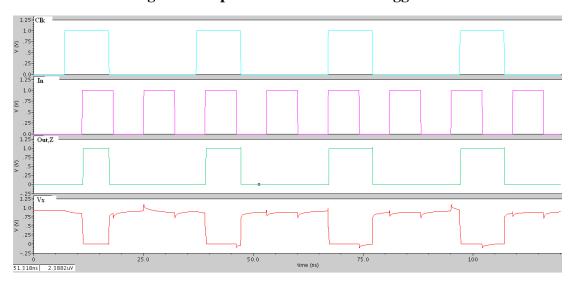

| Fig. 5.29 Simulation of transient response of domino Schmitt trigger-2                     | 148 |

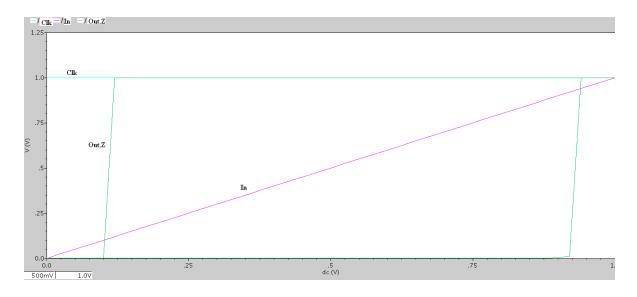

| Fig. 5.30 Simulation of DC response (VTC) of domino Schmitt trigger-2                      |     |

| Fig. 5.31 Pre-charge operation of proposed domino Schmitt trigger-2                      | 149   |

|------------------------------------------------------------------------------------------|-------|

| Fig. 5.32 Evaluation phase when PDN is off - operation of proposed domino Schmitt        |       |

| trigger-2                                                                                | 150   |

| Fig. 5.33 Evaluation phase when PDN is on - operation of proposed domino Schmitt         |       |

| trigger-2                                                                                | 151   |

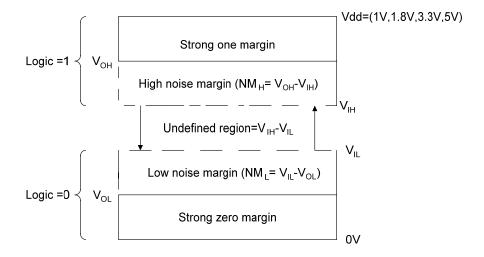

| Fig. 5.34 Noise Margin levels                                                            | 155   |

| Fig. 6.1 Flow chart of basic VLSI design flow                                            | 157   |

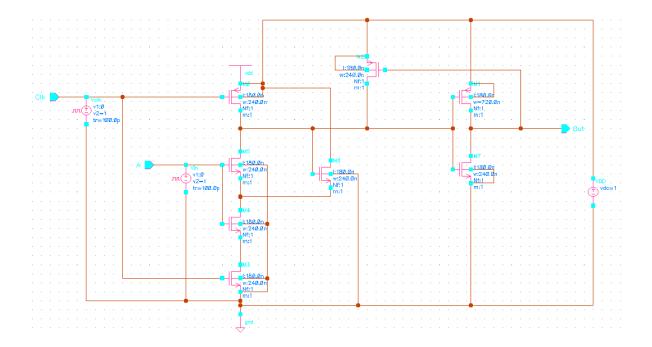

| Fig. 6.2 Schematic implementation of proposed domino Schmitt trigger-1                   | 161   |

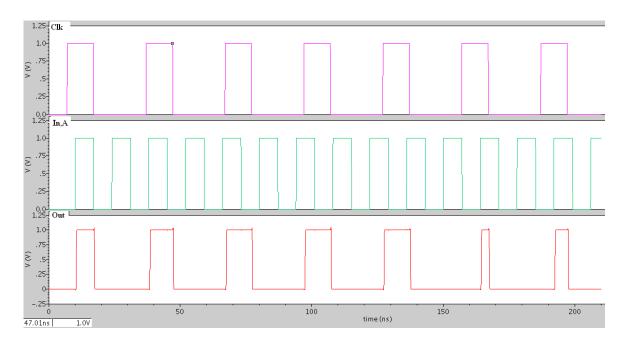

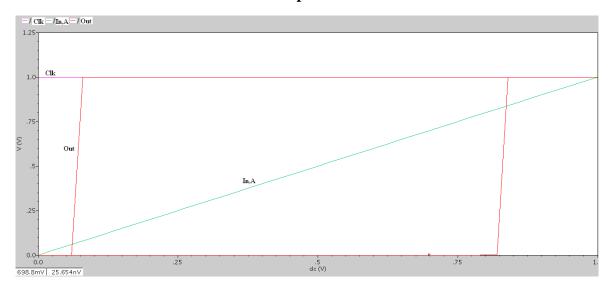

| Fig. 6.3 Transistor level simulation of proposed domino Schmitt trigger-1-transient      |       |

| response                                                                                 | 162   |

| Fig. 6.4 Transistor level simulation of proposed domino Schmitt trigger-1-DC response    | e 162 |

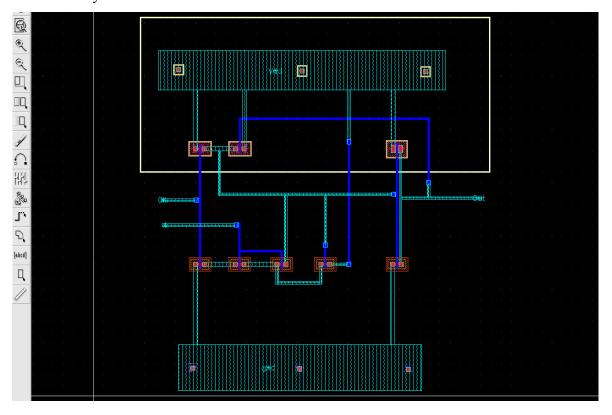

| Fig. 6.5 Schematic layout of proposed domino Schmitt trigger-1                           | 163   |

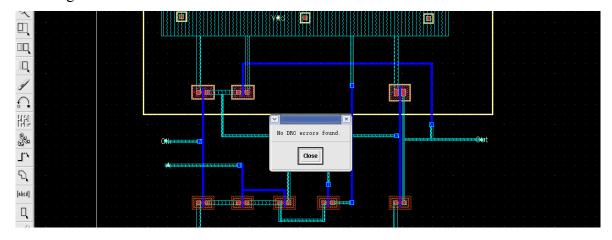

| Fig. 6.6 DRC report of proposed domino Schmitt trigger-1                                 | 163   |

| Fig. 6.7 Parasitic extraction report of proposed domino Schmitt trigger-1                | 164   |

| Fig. 6.8 Parasitic components (resistors and capacitors) of extracted layout of proposed | 1     |

| domino Schmitt trigger-1                                                                 | 164   |

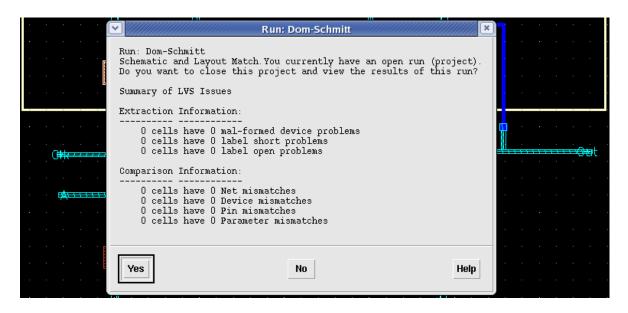

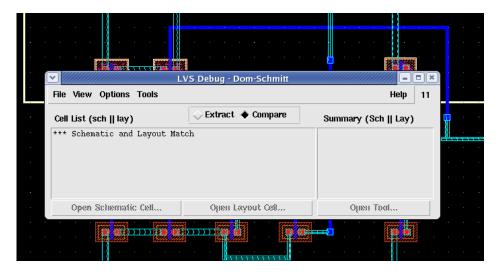

| Fig. 6.9 Summary report after LVS check for proposed domino Schmitt trigger-1            | 165   |

| Fig. 6.10 Report of LVS check for proposed domino Schmitt trigger-1                      | 165   |

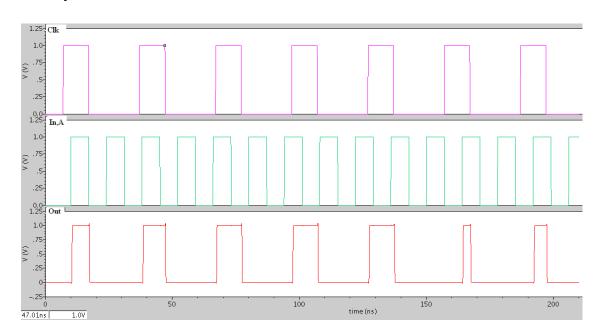

| Fig. 6.11 Post-layout simulation of proposed domino Schmitt trigger-1-transient respon   | nse   |

|                                                                                          | 166   |

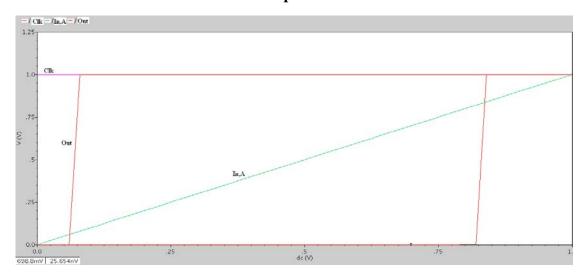

| Fig. 6.12 Post-layout simulation of proposed domino Schmitt trigger-1-DC (VTC)           |       |

| response                                                                                 | 166   |

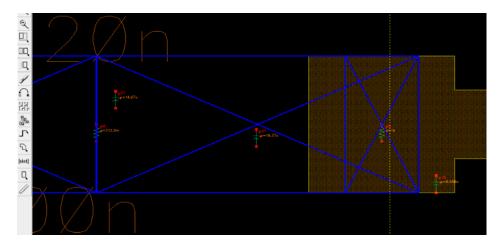

| Fig. 6.13 Final chip tape-out of proposed domino Schmitt trigger-1 circuit               | 167   |

## LIST OF TABLES

| Table 2.1 Comparison of parameters with technology scaling for Domino CMOS 2-input      |

|-----------------------------------------------------------------------------------------|

| AND gate24                                                                              |

| Table 2.2 Comparison of parameters with technology scaling for Domino CMOS 2-input      |

| AND gate with PMOS keeper30                                                             |

| Table 3.1 Comparison of typical power parameters and power-delay-product for standard   |

| and proposed domino logic techniques71                                                  |

| Table 3.2 UNG and ANTE comparison of standard and proposed domino logic techniques      |

| with Fan-in 272                                                                         |

| Table 3.3 UNG comparison of proposed domino logic techniques with Fan-in=2 at           |

| different Process Corner analysis                                                       |

| Table 3.4 UNG comparison of proposed domino logic techniques with Fan-in=4 at           |

| different Process Corner analysis                                                       |

| Table 3.5 UNG comparison of proposed domino logic techniques with Fan-in=8 at           |

| different Process Corner analysis                                                       |

| Table 3.6 UNG comparison of proposed domino logic techniques with Fan-in=16 at          |

| different Process Corner analysis                                                       |

| Table 3.7 UNG comparison of proposed domino logic techniques with Fan-in=32 at          |

| different Process Corner analysis                                                       |

| Table 4.1 Condition of all transistors of lector 2-input NAND gate for all possible     |

| combinations of inputs                                                                  |

| Table 4.2 Comparison of various parameters for Static CMOS NAND and Lector NAND         |

| techniques                                                                              |

| Table 4.3 Comparison of various parameters for domino lector-direct method and proposed |

| domino lector technique                                                                 |

| Table 4.4 UNG and ANTE comparison of domino lector-direct method and proposed           |

| domino lector technique with Fan-in=2                                                   |

| Table 4.5 UNG comparison of proposed domino logic techniques with Fan-in=2 at           |

| different Process Corner analysis                                                       |

| Table 4.6 UNG comparison of proposed domino logic techniques with Fan-in=4 at           |

| different Process Corner analysis                                                       |

| Table 4.7 UNG comparison of proposed domino logic techniques with Fan-in=8 at           |

| different Process Corner analysis                                                       |

| Table 4.8 UNG comparison of proposed domino logic techniques with Fan-in=16 at          |

| different Process Corner analysis                                                       |

| Table 4.9 UNG comparison of proposed domino logic techniques with Fan-in=32 at          |

| different Process Corner analysis                                                       |

| Table 4.10 Comparison of power and delay parameters of proposed technique for 2-input   |

| dynamic NOR gate with variable n (number of PMOS stack devices)117                      |

| Table 4.11 Comparison of power and delay parameters of proposed technique for 2-input   |

| domino OR gate with variable n (number of PMOS stack devices)                           |

| Table 4.12 UNG and ANTE comparison of proposed technique applied for de     | omino 2-input  |

|-----------------------------------------------------------------------------|----------------|

| OR gate for various stack devices                                           | 118            |

| Table 5.1 Comparison of typical power parameters and power-delay-product    | of various     |

| CMOS and proposed domino Schmitt trigger circuits                           |                |

| Table 5.2 Comparison of noise margin, hysteresis voltage and undefined regi | ons of various |

| CMOS and proposed domino Schmitt trigger circuits                           | 153            |

| Table 6.1 Comparison of design parameters of domino Schmitt trigger-1 at C  | MOS 90 nm      |

| and CMOS 180 nm process technology                                          | 169            |

| Table 6.2 Comparison of design parameters of domino Schmitt trigger-1 at pr | re-layout and  |

| post-layout simulation stages                                               | 169            |

|                                                                             |                |

## **ABBREVIATIONS**

MOSFET Metal Oxide Semiconductor Field Effect Transistor

CMOS Complementary Metal Oxide Semiconductor

NMOS N-channel Metal Oxide Semiconductor

PMOS P-Channel Metal Oxide Semiconductor

GND Ground

VLSI Very Large Scale Integration

DCVSL Differential Cascode Voltage Swing Logic

PTL Pass Transistor Logic

DPTL Differential Pass Transistor Logic

TTL Transistor-Transistor Logic

CML Current Mode Logic

CLK Clock

PDP Power-Deley-Product

UNG Unity Noise Gain

ANTE Average Noise Threshold Energy

STHD Skew Tolerant High Speed Domino

FEL Front-End of Line

BEL Back End of Line

PUD Pull-Up Device

PDN Pull-Down Device

LCT Leakage Control Transistor

NN Normal-Normal

FF Fast-Fast

SS Slow-Slow

FS Fast-Slow

SF Slow-Fast

ST Schmitt Trigger

VTC Voltage Transfer Characteristics

NM Noise Margin

DRC Design Rule Check

LVS Layout Versus Schematic

RCX Parasitic Extraction

Op-Amp Operational Amplifier

## CHAPTER 1 INTRODUCTION

#### 1.1 Introduction

Complementary Metal Oxide Semiconductor for wide variety of applications in VLSI field became the logic style of choice for the design of digital semiconductor domain because of its low power dissipation and ease of design with increased robustness [1-6]. This became the major advantage of CMOS logic over the other available manufacturing processes then, which suffered from flow of leakage currents or constant dissipation of bias currents. The rapid development of VLSI technology made a remarkable shift in the fabrication industry with its emerging qualities like high speed, low power, increased robustness and low area overhead. Scaling brought impeccable change in the recent trends. The evolution of various logic families like pseudo NMOS, DCVSL, PTL, and DPTL changed the ongoing market trend in manufacturing field.

Then speed and overhead area became the primary parameters of choice for fabrication industry that led to invention of clocked logic styles named as Dynamic logic and Domino logic families. Power consumption, noise immunity, speed of operation, area and cost are the predominant parameters that have to be taken into consideration before designing any kind of digital logic circuit technique. There may be a requirement for the effective trade-off between any two parameters depending on the situation and application of design. Sometimes, the design techniques might not meet all the mentioned requirements in their application, but still an optimization may be followed in order to proceed further in research areas.

Because of its high speed and low overhead area domino logic became process of choice for many digital circuits. The concerning issues are large power consumption and high sensitivity towards noise. Hence, there is a need for designing new domino methodology or improving existing techniques to meet the requirements by overcoming the drawbacks which led to ample opportunities for diversified research in this field. Therefore, the outcome of research must be able to handle the primary design parameters efficiently. Besides this, the designed circuit must exhibit high degree of robustness towards noise.

In this thesis, few domino logic circuit techniques are proposed to deal with noise and sub-threshold leakages. Furthermore, few existing circuits have also been modified to improve response. Proposed logic techniques are effective in increasing the immunity of system towards noise and sub-threshold leakage issues. This logic is further modified using various types of conditional keepers to design an energy-efficient circuit. Schmitt trigger, using proposed technique, is designed and investigated for its operation. A test chip for domino based Schmitt trigger is done in UMC 180 nm technology.

#### 1.2 History

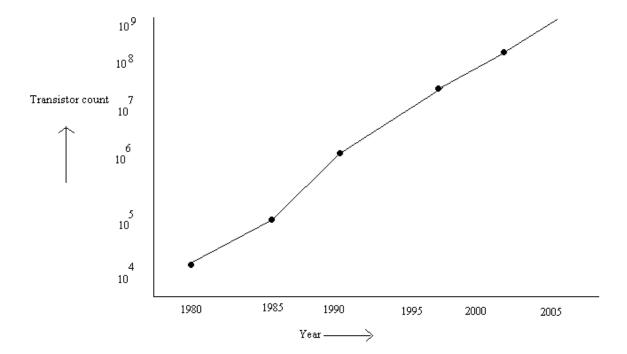

The revolution in integration industry and IC design made an impeccable shift in VLSI industry in the 1960s. According to Moore's law, the number of transistors that can be accommodated or integrated on a single die would exponentially grow with time [1]. Figure 1.1 shows Moore's prediction. It is observed that the complexity of integration doubles approximately every year. In the early 1970s, the microprocessor has begun to grow up in integration complexity and high performance.

Fig. 1.1 Moore's law

#### 1.3 Motivation

Besides its classical advantage of high speed operation, Domino logic family suffers from low noise sensitivity and large power consumption [5-10]. Significant research has been going in this field in order to stabilize this domino with reference to designing parameters. Several techniques have been proposed to overcome the mentioned drawbacks and most of them, however, partially improve the design parameters in various applications.

## 1.4 Objectives of the research work

The main aim is to design and implement domino logic circuit techniques to deal with noise issues and enhance the primary design parameters like power, speed, leakages, noise, area and cost. [1, 2]

The main objectives of this thesis are

- (1) Study of existing domino logic circuit techniques,

- (2) Simulating the benchmark circuits for analyzing the overall functionality,

- (3) Improving the existing methodologies by modifying the topologies or if possible introducing novel techniques,

- (4) Making the comparison of improved circuits with existing ones and

- (5) Designing of application based circuit (Schmitt Trigger) techniques based on improved methods.

#### 1.5 Thesis structure and over all contribution

## Chapter 1: Introduction

We present a generalized introduction about the broad area of research from the very basic level. In this chapter we also present the organization of the thesis and chapter wise contribution.

## Chapter 2: Overview of logic styles and related work

Here the research area is primarily focused on present working environment from a broader angle to this field. This chapter gives overview of standard logic styles in brief and introduces the dynamic logic followed by domino logic circuits with description. The research area is primarily focused on present working environment-Domino logic from a broader angle. Description of various circuit styles along with their advantages and disadvantages is illustrated with corresponding figures. In addition to this, the functioning

of domino logic with the encroachment of down scaling of process technology is investigated with analysis. Technique, which uses a PMOS keeper at dynamic node, to alleviate inevitable charge lost is reviewed and corresponding simulation result is presented in Table 2.2. A brief review on domino logic is conducted and issues related to domino logic are brought out that facilitated us proceeding to the next chapter.

## Chapter 3: Novel Domino logic topologies

This chapter gives general introduction to domino logic family with detailed literature survey. Standard benchmark domino logic circuit schemes followed by the analysis of their functionality with simulation results are thoroughly investigated. In addition to this, novel domino logic circuit techniques are proposed and are analyzed in detail with equivalent circuit diagrams in all operating phases along with simulation results. Moreover, analysis of benchmark circuits and proposed techniques includes variation on all the design parameters at different ambient conditions. Furthermore, noise analysis is carried out which includes the need for robustness, various noise metric parameters for measuring noise immunity or robustness of domino circuits such as UNG, ANTE along with the method of calculations, various sources of noise in domino logic circuits and their role on operating region. Besides this, description of process corner analysis and various corners involved in it along with their significant role on the overall functionality of the designed domino logic circuit is presented. Also the consequences of subjecting the device to the extreme corners with the boundary limitations are discussed. Result section shows the calculations and comparisons of all the parameters of standard benchmark circuits and proposed domino techniques. The primary design parameters such dynamic power, leakage or static power, total power, PDP (power-delay-product), UNG and ANTE for wide fan-in circuits of existing and proposed techniques are measured. The comparisons along with graphical analysis and tabulations are made and discussed the functionality with pros and cons.

## Chapter 4: Signal integrity issues and modified circuit techniques

This chapter gives general introduction to need for power reduction and leakage minimization. It discusses signal integrity issues in detail with simulations. A review on prior works related to leakage power reduction schemes and the lector technique is

presented. Also, modified lector domino scheme and dynamic node stabilizing technique are proposed in this chapter. All the simulations are done at CMOS 90 nm process technology with 1 V power supply. Process corner and noise analyses are carried out for proposed schemes. Also, the primary design parameters such dynamic power, leakage or static power, total power, PDP (power-delay-product), UNG and ANTE for various fan-in circuits of existing and proposed techniques are measured and comparisons are made and conclusions are drawn in result section.

## Chapter 5: Design of various domino based Schmitt trigger circuits

This chapter briefly explains conventional Schmitt triggers using op-amp and CMOS logic. Next, it demonstrates proposed domino Schmitt trigger circuits along with analysis. A novel domino logic based noise tolerant Schmitt trigger circuit is designed and simulated. The simulation results with discussion are presented from which concluding remarks are made.

### Chapter 6: Chip tape-out

This chapter explains complete VLSI design flow which includes the process of chip tape-out. It compares overall functionality of domino based Schmitt trigger in 180 nm and 90 nm technologies. The difference between pre-layout and post-layout simulation is investigated. The chip tape-out of proposed domino Schmitt trigger circuit is done in CMOS 180 nm process technology.

## Chapter 7: Conclusion and future work

The total work is concluded in this chapter and it also discussed future scope briefly for further improvements based on this work.

#### 1.6 Conclusion

Therefore, the need for high speed, low power, less area and more noise tolerant qualities is briefly discussed. As technology is growing with rapid improvements in VLSI fields with diversified applications, there is need to achieve these target applications with up-coming research outcomes. For that purpose, updating these present technological library files is mandatory so as to coagulate the quality of research methodologies. This chapter is presenting overall idea behind this work from very basic level. It briefed up the generalized introduction, related history behind this work, motivation and main objectives of this work. Thesis structure along with overall chapter wise contribution is also given.

# CHAPTER 2 OVERVIEW OF LOGIC STYLES AND RELATED WORK

#### 2.1 CMOS AND NMOS

FrankWanlass was the first person who in the year 1963 proposed Complementary Metal Oxide Semiconductor which for wide variety of applications became the logic style of choice for the design of digital semiconductor domain because of its low power dissipation (almost no power) when the gate inputs are not altered [6]. This is implied from the fact that CMOS structure consists of both PMOS field effect transistors which can expeditiously drive a strong one and NMOS field effect transistors which can adequately drive a strong zero at the output node. Therefore this peculiar combination of complementary transistors allows CMOS logic gate circuits which are to be implemented in such a way that the output node voltage level is always connected to either supply voltage rail or ground rail but not both simultaneously, which there by implies that as long as the logic inputs of CMOS circuit are not altered, there is no power dissipation by the circuit. This became the major advantage of CMOS logic over the other available manufacturing processes then, which suffered from flow of leakage currents or constant dissipation of bias currents.

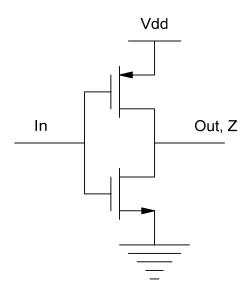

Fig. 2.1 Static CMOS logic Inverter

Fig. 2.1 shows the schematic representation of a static CMOS NAND gate. The logic gate has two inputs A and B with an output Z. A logic high voltage level at both the input nodes A and B turns on the NMOS transistors in the pull down device MN1 and MN2, while turning off the PMOS transistors in the pull up device MP1 and MP2 which results the output node Z to be a logic low voltage level. When either input A or B is off, however, the path for discharge of output node to the ground rail is broken, with an existing path to the power supply rail (Vdd) being established. This causes the output node Z to reach a logic high voltage level. While the NAND gate represents a simple logic function, it shows how contention current between the power supply rail and ground rail can effectively be avoided in static CMOS circuits. This lack of contention current implies that when the inputs to the CMOS circuit are not changing, often referred as a ideal state of operation or standby mode, almost no power dissipation occurs, except for a small but finite amount of leakage current which flows through the transistors present in the circuit due to the imperfect structural manner in which the MOSFET device itself acts as a switch due to the persistent scaling in the physical dimensions of CMOS processes, actively driven by the cost advantages of having a very smaller silicon wafer areas for digital logic functional circuits, MOS transistors had become imperfect switches, leading to the flow of greater leakage currents.

Fig. 2.2 Static CMOS 2-input NAND gate

Fig. 2.3 Static CMOS 2-input NAND gate simulation

It is known fact that the CMOS logic family which resulted in significant power savings was apparent to Frank Wanlass who in the year 1963 proved the practicality of CMOS logic and other technical advantages of CMOS design with the technology of a massive monolithic implementation for the very first time. But when this idea of implementation proved unfeasible, Frank demonstrated the same concept with discrete transistors. So, here these particular CMOS implementations alleviated standby power effectively by six orders of magnitude over the other PMOS logic and bipolar logic implementations available. Besides giving impressive results, this advantage related to CMOS logic would not prove decisive for so many years. The former monolithic designs were very small, with the small amount of standby power. Due to the deficient maturity of MOS transistors, in the 1960s, the bipolar logic family raced ahead of MOS technology in various applications. Then the Transistor-transistor logic (TTL) developed in 1962, and Emitter-Coupled Logic (ECL) also referred as Current Mode Logic (CML) developed in 1966 provided effective techniques for the digital design of bipolar logic transistors in the semiconductor industry which is rapidly increasing. There was a point of time in the early years where prime user of CMOS logic was the watch industry. In that era of time battery life was given highest priority than speed. After that MOS technology had begun to mature in the 1970s rapidly, by the contribution of Intel Corporation limited with much of its early

and advanced industrial development. Then the first and foremost world's microprocessor 4004 was released by Intel.

The Intel microprocessor 4004 was invented with a 10 µm line width of PMOS transistor and it used around 2300-2400 transistors running at the chip speed of 108 kHz [8]. Again after having contributed a great research in this field Intel released an 8-bit 8080 microprocessor in the year 1974 which was manufactured with a 6 µm line width of NMOS transistor and used 6000 transistors at the chip speed of 2MHz. Due to the higher mobility of electrons over holes NMOS logic became faster than PMOS logic and hence NMOS obviously started to become the choice of selection.

#### **Advantages of CMOS Logic:**

- (1) Robustness(less sensitive to noise).

- (2) Simple approach for implementing logic gates.

- (3) Easy to translate logic to FETs.

- (4) Good noise margins since FETs are in cut off & sizing not critical

- (5) No static power dissipation.

- (6) Low power consumption.

#### **Disadvantages of CMOS Logic:**

- (1) Complexity of circuits increases with increased Fan-in.

- (2) For a M-input logic gate, 2M-transistors are required which resulted in relatively large implementation area.

- (3) Propagation delay of CMOS logic gates deteriorates rapidly as a function of the Fan-in.

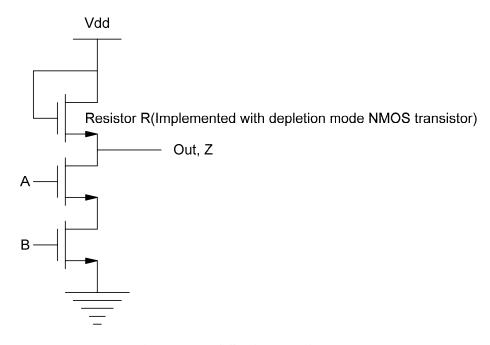

Fig. 2.4 gives the schematic implementation of a 2 input NAND gate only with NMOS transistors. The PMOS transistors shown in Fig.2.2, MP1 and MP2 are now removed in this implementation of logic and replaced by a resistor, R as shown. In fact the conceptual resistor is implemented by a NMOS transistor with depletion mode. Now when either input A or B is low, the output Z is at Vdd. When both the inputs A and B are at logic high state then the output Z is completely discharged which resulted in logic low value. If one wants this logic to function properly then there is a condition to be satisfied which is related to the current-driving capability of NMOS transistors present in the pull down network which needs to be much greater than the current-driving capability of the resistor in the pull up network. Now this concept demonstrated that the output can be driven to a logic low

voltage level but at the cost of higher power dissipation due to inclusion of the resistor in the pull up network. Besides this standby power dissipation, NMOS logic is a bit slower than CMOS logic due to the presence of weak pull up resistor that functions very slowly when a low to high transition takes place. However the observed drawbacks might have made the NMOS logic appear to be unappealing, still NMOS logic designs are much more compact than CMOS logic circuits. The implementation in Fig. 2.4 has only two NMOS transistors and a resistor R, in comparison with CMOS logic design which has four transistors required to implement its logic. In this way the NMOS logic uses fewer transistors and it is simpler process than CMOS logic design. Then the need to move to CMOS technology had therefore arisen only when the advanced level of integration on integrated circuits (ICs) made the huge standby power dissipation on the NMOS logic circuit design unacceptable. When the 8086/8088 family of microprocessors was released in market in the year 1978 by Intel Corporation Limited, this period of transition occurred since all those implemented designs were almost identical to the family of 8088 microprocessors with an 8-bit bus while the family of 8086 microprocessors with a 16-bit bus only. The power dissipation of 8086 family of microprocessors was 1.5 W with 29,000 transistors at the clock rate of 5-10 MHz, which crossed the nominal 1 W per chip power limit for processing of plastic packaging. The increments in integration levels meant that a 32-bit microprocessor would nominally dissipate 5-6 W, leading to few severe reliability obstacles. Only 250 mW was the power consumption of the CMOS version of the 8086 and 80C86 [9].

Fig. 2.4 NMOS 2-input NAND gate

Fig. 2.5 NMOS 2-input NAND gate simulation

The capability of CMOS logic to minimize the total power consumption with increasing large scale integration made it to be best technology which could effectively utilize the advancements in the field of fabrication industry in the recent trends [10]. Also this peculiar CMOS logic maintained till today the advantage of manufacturing large number of digital IC designs using this technology.

With the progression of the manufacturing of semiconductor devices, the biggest challenge was the ability to design and verify all the circuit designs using the increased

number of transistors available then. This demand was achieved by Electronic Design Automation (EDA) software which was developed in the hardware industry in early years. In early days of industry, there might have been an assumption that all the existing techniques for the implementation of digital CMOS logic would be replaced by the ASIC design and its methodologies. That has not happened since many digital IC designs have got their own specific needs that cannot be achieved by standard ASIC techniques. There is a rapid and notable advancement regarding the capabilities of ASIC technology tools in the recent years.

The important common benefits of custom IC design [13-20]:

- (1) The ability to optimize across distinctly separate levels of abstractions in the ASIC design methodologies available which leads to the development of standard cell library used by ASIC design through sequential approach and the opportunity which is provided by custom IC design for using logic families other than standard static logic.

- (2) Also it can utilize certain type of logic families, specifically dynamic logic families (also referred as clocked logic families), which automated the specific design frameworks.

### 2.2 Different static logic styles

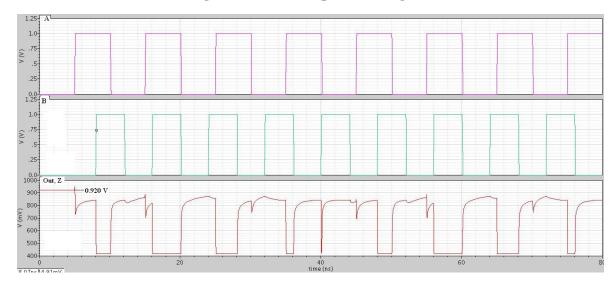

#### 2.2.1 Pseudo N-MOS

Fig. 2.6 Pseudo N-MOS Logic

#### **Advantages:**

For N-input logic gate implementation, only (N+1) transistors are needed. This count is less when compared with Static CMOS Logic.

#### **Disadvantages:**

- (1) Noise Margin reduces.

- (2) Static power dissipation increases.

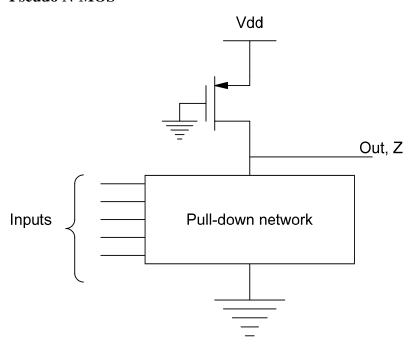

#### 2.2.2 Differential Cascode Voltage Swing Logic (DCVSL)

Fig. 2. 7 Differential Cascode Voltage Swing Logic

Pull-down network 1 (PDN1) and Pull-down network 2 (PDN2) are mutually exclusive, i.e. PDN2 = Complement of (PDN1)

#### **Advantages:**

- (1) Provides rail-to-rail swing.

- (2) Completely eliminates static currents, thus static power dissipation is eliminated.

- (3) A functional logic and its inverse can simultaneously be implemented.

#### **Disadvantages:**

- (1) Exhibits the problem of increased design complexity.

- (2) Power dissipation problem due to cross-over currents.

- (3) During the transition, there is a period of time when PMOS & PDN are turned 'ON' simultaneously, producing a short-circuit path.

#### 2.2.3 Pass Transistor Logic

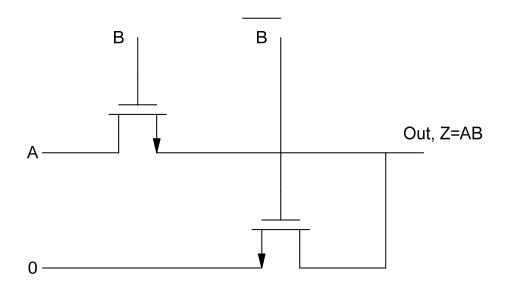

Fig. 2.8 Pass Transistor Logic implementation of 2-input AND gate

#### **Advantages:**

- (1) Effective reduction of number of transistors required for implementing a combinational functional logic is the main advantage of PTL family. This could be achieved by driving all the three terminals of MOSFET, Gate, Source and Drain, by active inputs.

- (2) The process of reducing the number of devices has the additional advantage of lowering capacitance.

## **Applications:**

This logic is used in Multiplexers and Latches.

PTL gates cannot be cascaded by connecting the output of a gate to the input of another Pass Transistor.

### 2.2.4 Differential / Complementary Pass Transistor Logic

Fig. 2.9 Differential/Complementary Pass Transistor Logic implementation of 2-input AND gate

#### **Advantages:**

- (1) Adders, sub tractors and other complex gates such as XNOR, XOR can efficiently be realized using significantly small number of transistors in this DPT Logic.

- (2) This logic is belonging to the family of Static gates, since all the output nodes are always connected to either Vdd rail or ground rail through an existing low resistance path which is an advantage for Noise resiliency.

#### **Disadvantages:**

- (1) Static power dissipation is present.

- (2) Reduced Noise Margins.

#### Remedy for drawbacks:

- (1) Using Level restoration circuit techniques.

- (2) Multiple threshold transistor techniques.

- (3) Implementing Transmission-Gate logic.

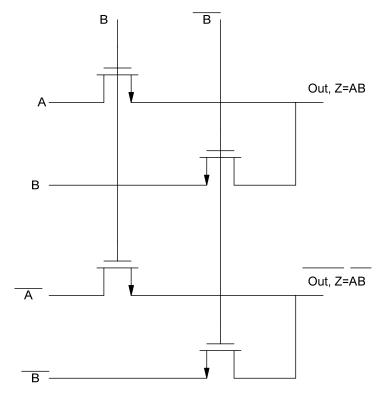

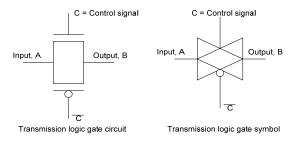

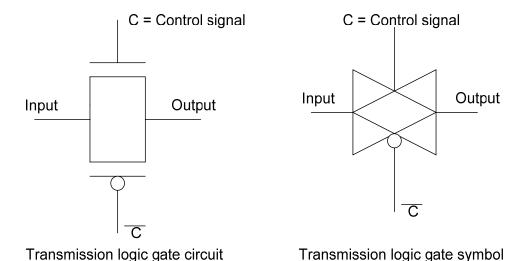

Here is a particular type of logic technique called "Transmission Gate logic" which is most widely used technique to deal with problems like voltage drop.

#### • Transmission-Gate logic:

- ➤ It is built on the basis of the complementary properties of NMOS & PMOS transistors.

- ➤ It combines both device flavors by replacing a PMOS in parallel with a NMOS as shown in Fig.1.10.

Fig. 2.10 Transmission Gate

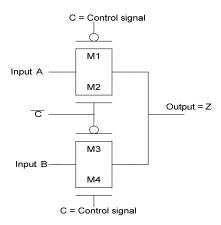

Transmission Gate is acting as a Bi-directional switch which is controlled by a control signal-'C' through Gate terminal of MOSFET transistor. If C='1', then both the MOSFETs are on, so they allow signal to pass through the gate. Therefore A=B, while in other case if C='0', then both the MOSFETs are off, so they are in cut-off mode, Thus there is an open circuit between the nodes A and B.

#### **Advantages:**

- ➤ It enables rail-to-rail swing although it requires 2-transistors & more control signals.

- ➤ Using these Transmission gates, complex gates can efficiently be built.

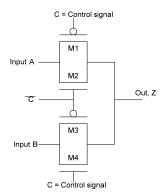

Here is the implementation of 2:1 Multiplexer using Transmission Gate Logic.

Fig. 2.11 2:1 Multiplexer using Transmission Gate

• When C='0', then transistors M1 and M2 will be ON, and there by output Z is taking signal A.

• When C='1', then transistors M3 and M4 will be ON, thus they are passing signal B to the output node Z.

## 2.3 Dynamic CMOS logic design

In the Integrated Circuit design industry, by late 1970s, Dynamic logic also referred as the "Clocked logic" was popular in the digital logic design. It can be distinguished from the static logic family with the usage of a driving signal called clock signal in the implementation of Combinational functional logic circuit designs. The use of clock signal in Dynamic logic is to evaluate the combinational function but a sequential logic circuit has also got its own clock signal where it is used to synchronize the transitions in sequential logic circuits.

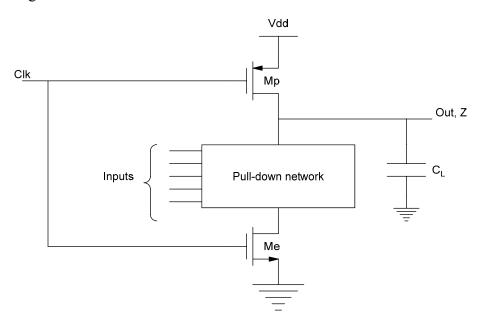

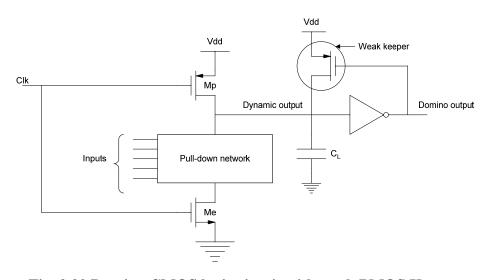

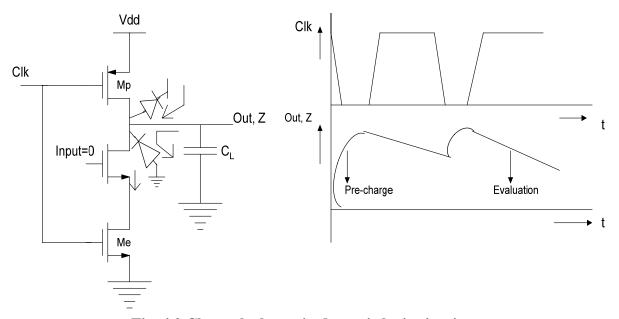

Fig. 2.12 Dynamic CMOS logic

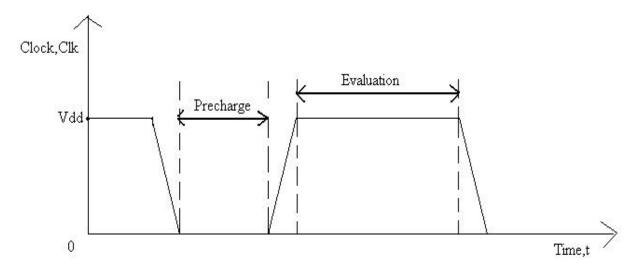

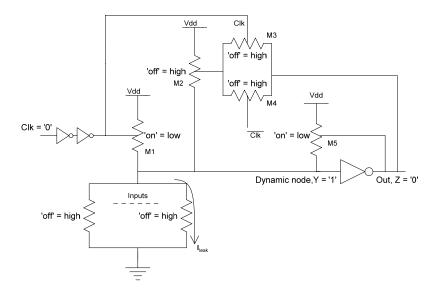

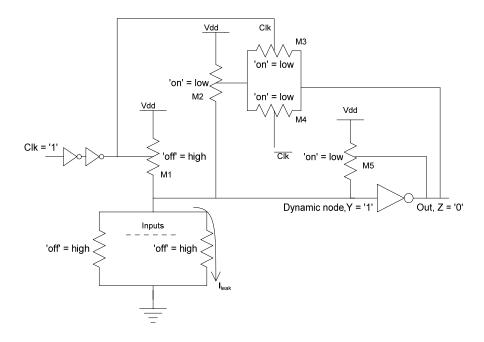

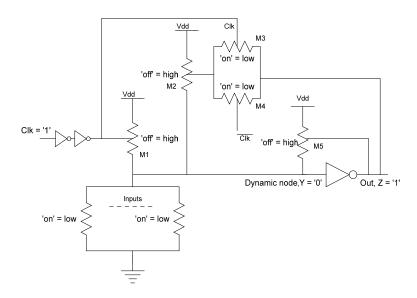

As it has a clock signal which is of a pulse type with two levels '0' (logic low) and '1' (logic high), the basic operation is divided into 2 phases: Pre-charge and Evaluation.

When Clk goes low, pre-charge transistor Mp will be turned 'ON' and transistor Me will be 'OFF'. Thus irrespective of condition of inputs applied to Pull Down Network (PDN), node 'Output' gets charged to 'Vdd' and other nodes may pre-charge to (Vdd – Vth.n) depending on values of inputs.

When Clk is high, transistor Mp will be turned 'OFF' and transistor Me will be 'ON'. Since the actual combinational functional logic will be evaluated through Pull Down Network (PDN) in this phase, this is referred as Evaluation phase. If the input combination to PDN has configured a conducting path then Output nodal voltage may be discharged to 'Gnd'; else Output node stays at logic high. Importantly the inputs must be stable before Clk signal goes to logic high since once the output node has been discharged to gnd, it won't go to logic high again until the next cycle arrives. Thus glitches (dynamic hazards), noise pulses on input signals, cannot exceed the threshold voltage of Me transistor, which is a stringent condition to be highly required for domino logic gates than for static CMOS logic gates.

#### **Advantages:**

- (1) There is no static power consumption with an addition of a clock signal input which uses a sequence off phases called Pre-charge and Evaluation.

- (2) Increased speed and reduced implementation area.

- (3) This dynamic logic is twice as fast as the nominal static CMOS logic since it uses only fast NMOS transistors in its evaluation phase in Pull Down Network.

- (4) It is amenable to transistor sizing optimizations.

- (5) Glitches (Dynamic Hazards), due to gates which have non-zero propagation do not occur in dynamic logic.

#### **Glitches (Dynamic Hazards):**

The finite propagation delay from one logic block to next logic block when a signal is passing through a gate from input node to output node causes spurious or abrupt transitions at the output node, which are known as Glitches. All the gates have a non-zero propagation delay.

#### **Disadvantages:**

- (1) More power consumption because this dynamic logic significantly increases the number of transistors required which are switching at any given instant of time.

- (2) Problems will arise when cascading one gate to next gate. Thus the straightforward cascading of gates is not possible.

#### **Signal Integrity Issues in Dynamic Design:**

There are several important considerations that must be taken into account if one wants Dynamic circuits to function properly. They are

- (1) Charge leakage

- (2) Charge sharing

- (3) Capacitive coupling and

- (4) Clock feed through

Charge leakage and Charge sharing occur in Evaluation phase.

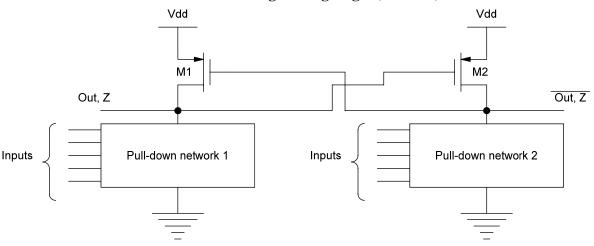

#### 2.4 Domino logic circuits

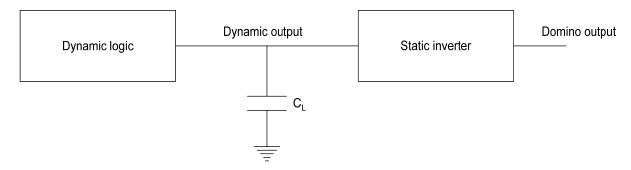

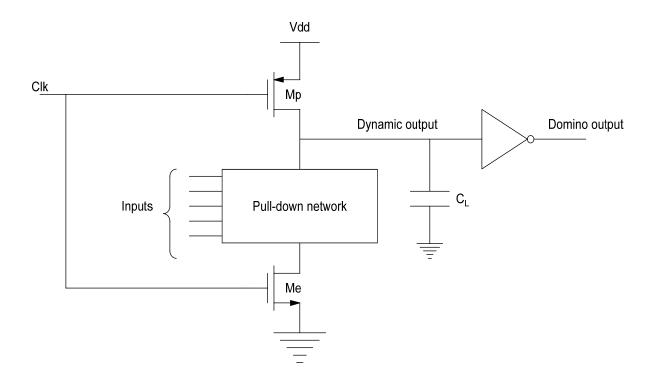

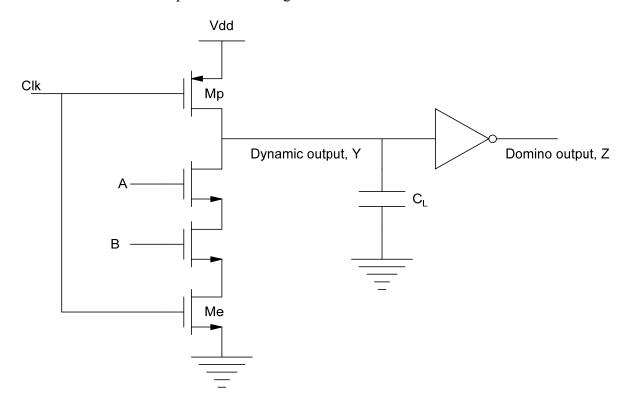

Dynamic logic with an addition of a static inverter at the output node results in a complete domino logic block. This is nothing but a CMOS based exploitation of dynamic CMOS logic circuit techniques which are established on either NMOS or PMOS logic transistors. This particular logic was initially developed to achieve high speed operation in the logic circuits [25-27].

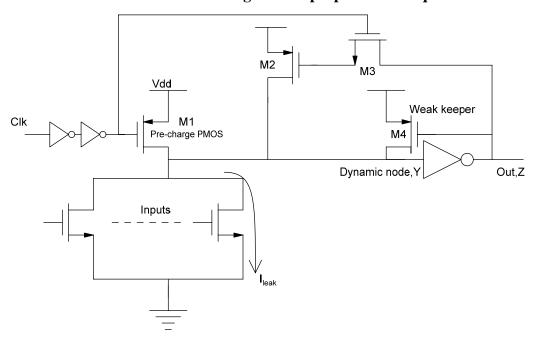

Fig. 2.13 Block diagram of Domino logic

Fig. 2.14 Domino CMOS logic

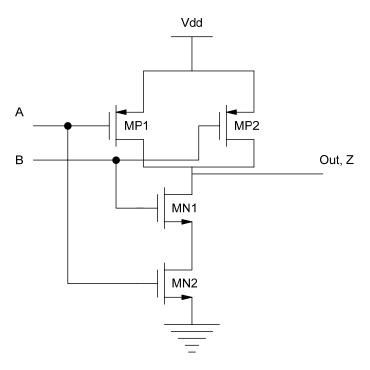

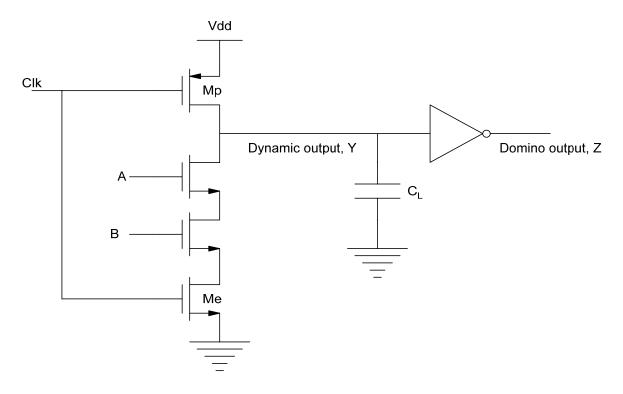

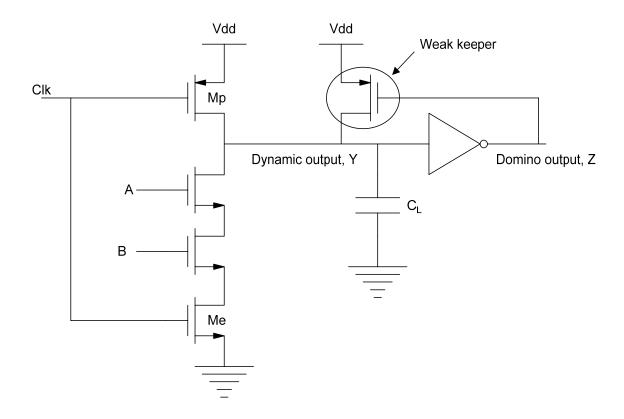

Fig. 2.15 Domino CMOS 2-input AND gate

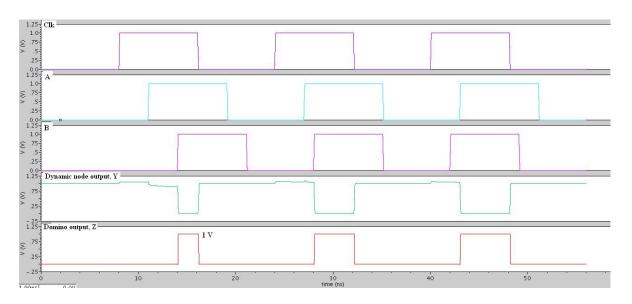

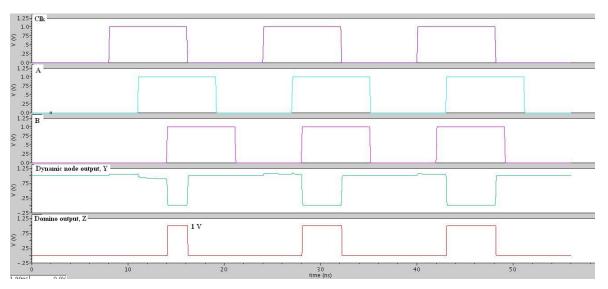

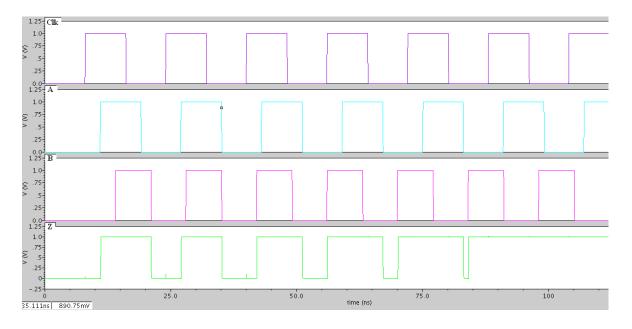

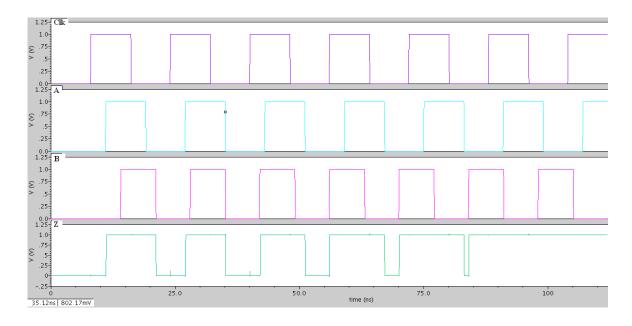

Fig. 2.16 Domino CMOS 2-input AND gate simulation

The 2-input domino AND gate shown in Fig. 2.15 is used to illustrate the logical functionality, the advantage of increased speed, and few challenges involved in using this Domino CMOS logic family. It is observed that there are two inputs, A and B, along with the driving element clock signal, Clk. Since it is an implementation of purely a combinational circuit-AND gate which does not require any clock signal, unlike sequential logic circuits, the presence of clock signal makes it strange. Domino CMOS logic like dynamic logic is also a clocked type of logic family in which every single logic gate has presence of clock signal. If the clock becomes low, then the dynamic node gets charged to supply voltage, causing the domino output, Z to go low due to the presence of inverter between these two nodes. Now this mechanism represents that the gate output to go low logic level once it has been driven high logic level. So this operating period of the block when the clock signal and output are low is known as the Pre-charge phase. Next phase is Evaluation phase which starts when clock signal is high. During this Evaluation phase the actual functional logic is evaluated through Pull Down Network. Therefore the output, Z may go high if both inputs A and B are high, which results the evaluation or dynamic node to be driven to a low logic value. The Evaluation phase as mentioned earlier is the actual functional operating cycle in domino logic circuits with the Pre-charge phase enabling the succeeding Evaluation phase to occur. The significant application of the presence of clock

signal in domino logic ensures that the critical path only traverses through NMOS transistors of Pull Down Network present in the Evaluation phase. One of the advantages of domino cell is that there is no need for the input signals to drive any PMOS transistor present in Pull Up Network as the domino cell only switches from low logic level to high logic level direction.

Now, for a particular instant of current drive, the lack of a PMOS transistor implies that the effective width of PMOS transistor which loads down its previous stage logic favors this domino logic over the static logic. Here it is very critical because the key to very high speed is ensuring that the advantage of high speed can be acquired without loading down the logic block greatly.

#### **Advantages:**

- (1) Domino logic circuits allow nominal rail-to-rail swing.

- (2) Domino logic circuits comparatively have smaller areas than static CMOS logic circuits.

- (3) Higher operating speeds are possible since parasitic capacitances in cells are reliably smaller.

- (4) Domino logic ensures free glitch operation as each gate can make only single transition.

#### **Disadvantages:**

- (1) There is relatively deterioration of noise immunity due to the presence of problems like unavoidable leakage currents and charge sharing issues.

- (2) Relatively large power consumption when compared to the static CMOS logic.

- (3) Only non inverting functional structures can be built since there is an inverting buffer at the dynamic node.

- (4) Charge distribution may also be taken care off.

## **List of Important Logic Families**

- Resistor Transistor Logic (RTL)

- Resistor Capacitor Transistor Logic (RCTL)

- Diode Transistor Logic (DTL)

- Transistor Transistor Logic (TTL)

- Direct Coupled Transistor Logic (DCTL)

- Integrated Injection Logic (IIL)

- High Threshold Logic (HTL)

- Emitter Coupled Logic/Current Mode Logic (ECL/CML)

- Metal Oxide Semiconductor Logic (MOSL)

- Complementary Metal Oxide Semiconductor Logic (CMOSL)

- Pseudo NMOS Logic

- Enhancement NMOS Logic

- Differential Cascode Voltage Swing Logic (DCVSL)

- Pass Transistor Logic (PTL)

- Differential Pass Transistor Logic (DPTL)

- Dynamic CMOS Logic

- Domino CMOS Logic/Domino Logic

#### 2.4.1 Impact on power consumption

Power consumption is the one of the predominant constraints which plays a vital role in the process of designing any digital dynamic logic circuit. Most of the versatile applications in the microprocessors, digital signal processors and dynamic RAM are based on the technology platform provided by domino CMOS logic family due to their advantage of achieving high speed operation with relatively low device count. Of course there might be inevitable problems like leakage currents and charge sharing issues which normally degrade the degree of robustness in terms of noise immunity or levels of noise margin of the domino CMOS logic family. Nevertheless there is significantly huge power dissipation, in comparison with the other existing static CMOS logic circuits. The continuous down scaling trend of CMOS technology is making the situation even bitterer from genesis to genesis. This chapter investigates the functioning of domino logic circuits with the

encroachment of scaling of process technology. A simple Domino AND gate is designed and simulated at different process technologies.

Fig. 2.17 Domino CMOS 2-input AND gate

Table 2.1 Comparison of parameters with technology scaling for Domino CMOS 2-input AND gate

| Technology<br>(in nm) | Dynamic power<br>dissipation<br>(in W) | Vth,n<br>(in V) | Vth,p<br>(in V) |

|-----------------------|----------------------------------------|-----------------|-----------------|

| 1200                  | 3.260E-12                              | 0.607           | -0.832          |

| 500                   | 3.276E-12                              | 0.708           | -0.918          |

| 350                   | 3.375E-12                              | 0.549           | -0.680          |

| 250                   | 11.663E-12                             | 0.365           | -0.562          |

| 180                   | 14.538E-12                             | 0.372           | -0.394          |

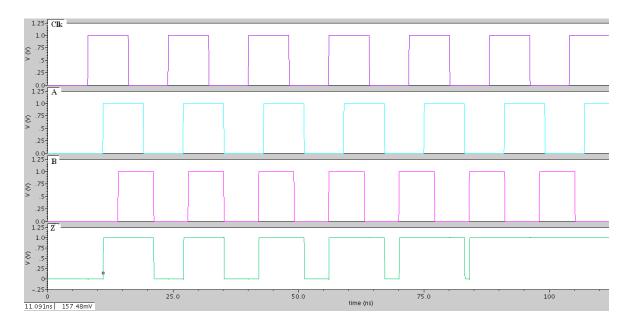

Fig. 2.18 Domino CMOS 2-input AND gate simulation

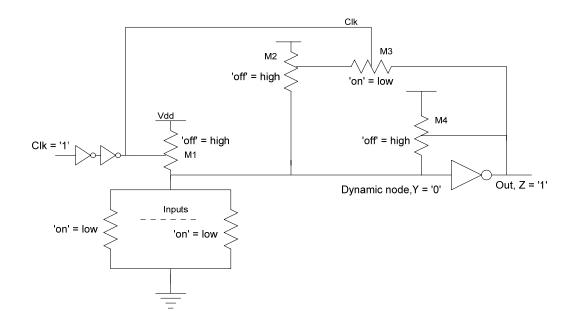

From the above tabulations, it is evident that the power consumption increases with the down scaling of process technology. Particularly, the logic designer is forced to go for a lower bias voltage or supply voltage so as to reduce the dynamic power consumption. This again demands the minimization of sub threshold voltage to achieve required functional execution of logic along with the consorted increment in the sub threshold leakage current. Therefore an adequately sized parallel PMOS device keeper needs to be inserted to deal with the leakage current issue. Secondly the most important factor of domino CMOS logic, for which it is being preferred mostly over the other logic styles, is speed which will also degrade with the down scaling trend of CMOS process technology due to the presence of inevitable keeper current.

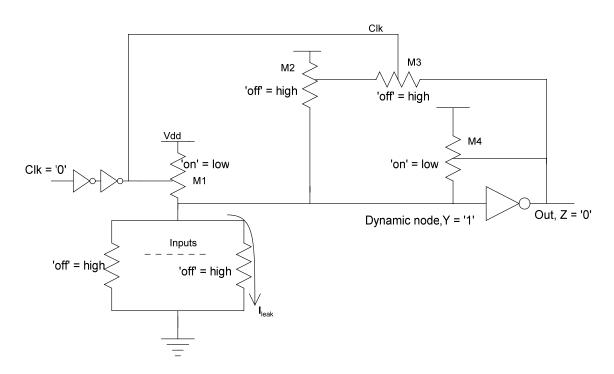

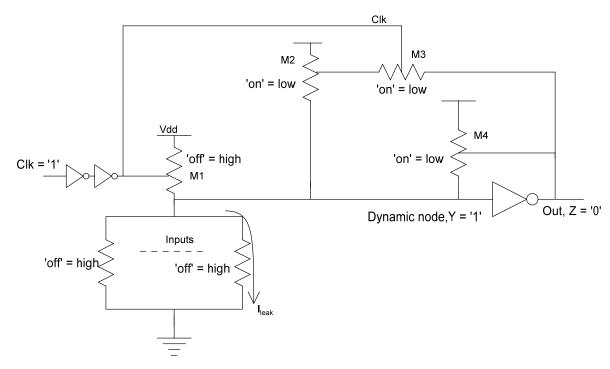

Fig. 2.17 shows domino CMOS 2-input AND gate. In this implementation there is a pull down network (PDN) for realizing the actual functional logic along with clock signal that periodically operates the two phases called pre-charge and evaluation as shown in Fig. 2.19. The total parasitic capacitance at the dynamic node is represented by C<sub>L</sub>. If clock is at logic low level, then pull up transistor Mp will turn on which will result the total circuit in pre-charge phase where the dynamic node will get charged to supply voltage through pull up transistor. And also in this phase, the input signals applied to the PDN may be allowed to switch and may get settled to their fixed values. As the evaluation transistor Me is in off state, the discharging path to ground is now disrupted. Now when the Clk is at logic high level, then Mp will turn off and immediately Me will turn on which is known as evaluation phase.

Let's look at the evaluation phase where in, two possible conditions exist for the dynamic nodal voltage to get stabilized. If the current combination of input signals corresponds to a low logic level domino output voltage, then the dynamic node voltage should maintain its nodal potential at supply voltage Vdd, in the form of charge stored by load capacitor. Similarly, if the same input combination leads to a high logic level domino output voltage, then the dynamic nodal voltage ought to be discharged to ground level through the conducting path provided by the NMOS transistors present inside the Pull Down Network..

Fig. 2.19 Clock signal in Domino logic Circuit

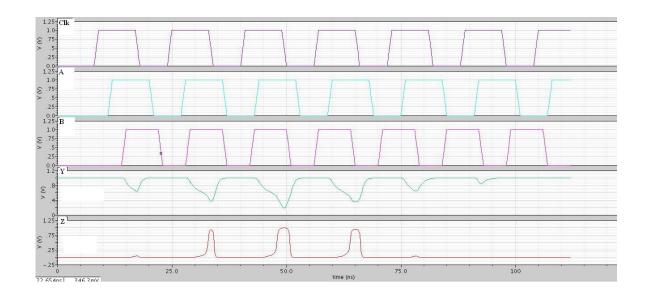

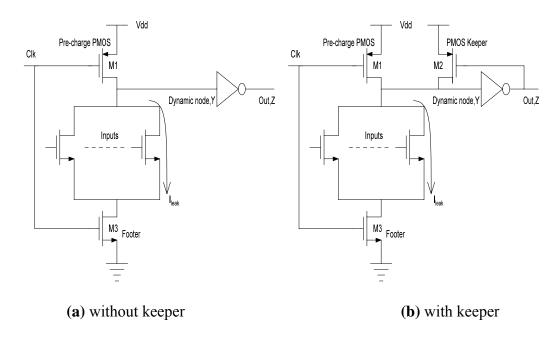

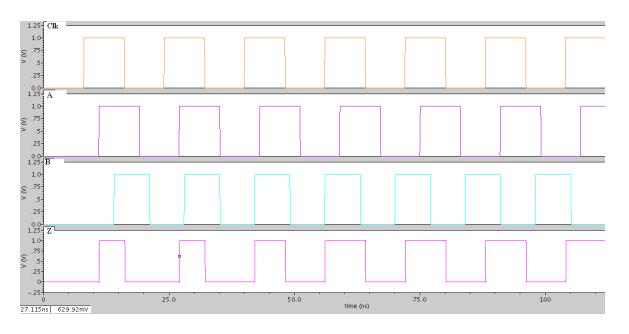

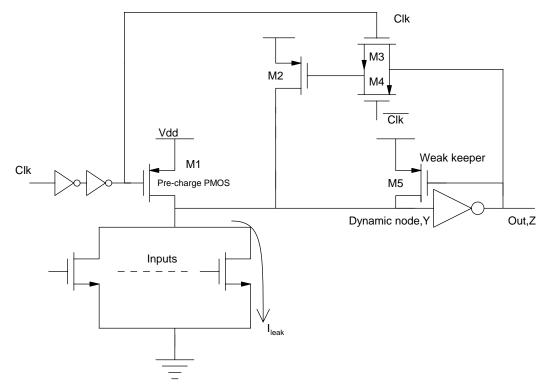

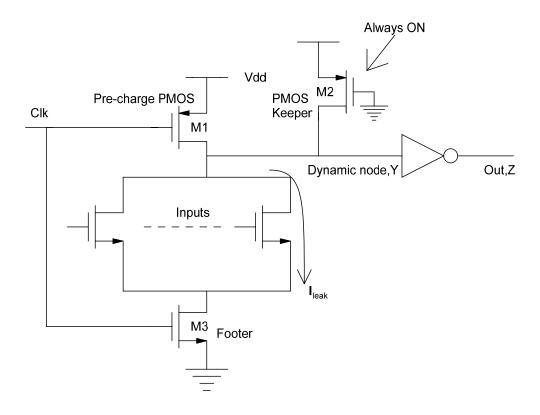

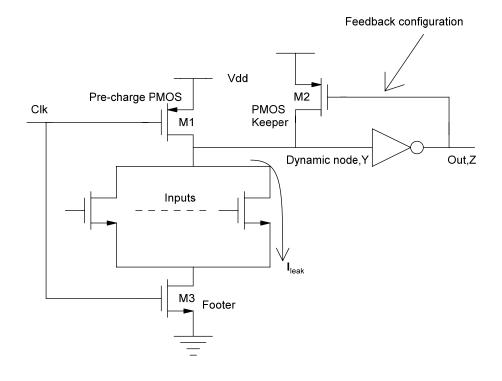

#### 2.4.2 Technique to compensate charge lost, through PMOS keeper

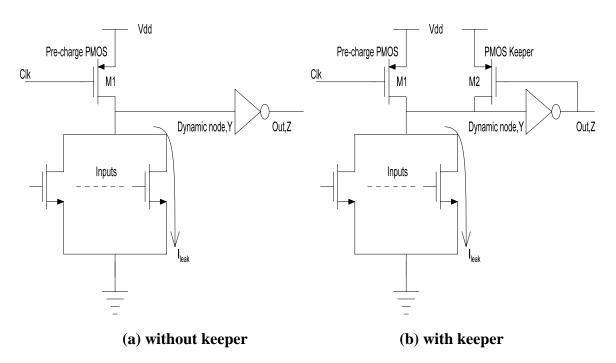

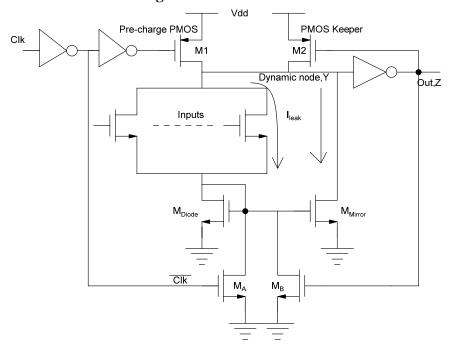

However, in the previous session there is an assumption that there exists no charge leakage from the dynamic nodal capacitor,  $C_L$ . But in real time conditions, however, leakages are found during the clock's evaluation phase through copious provisions, like the sub threshold leakage currents, the gate terminal tunneling currents..., etc despite the fact that the input combination of Pull Down Network is not allowing the dynamic load capacitor  $C_L$ , to discharge from Vdd to ground. Although the leakage current is an inevitable parameter in MOS devices, it is very small but finite. Due to concentration gradient between source and drain terminals of MOSFET, absolute temperature, and other conditions like inappropriate doping concentration it flows. It is an inevitable problem in dynamic circuits. Besides the above issues there may a problem with charge sharing because of which the charge of load capacitor,  $C_L$  might be shared with the consorted drain

capacitors of the NMOS devices in the Pull Down Network. Therefore, a PMOS keeper as given in Fig.2.4 has to be introduced in order to refill the unavoidable charge lost from the dynamic load capacitor  $C_L$ , so that the noise margin levels could be maintained at an operating controlled ambient. So a weak PMOS keeper device is always advisable in parallel with pre-charge transistor as shown in figure since during the clock's evaluation phase, eventually the load capacitor  $C_L$ , if the charge stored on it is to discharge through the conducting PDN, will slowly discharge due to the presence of contention keeper current.

Fig. 2.20 Domino CMOS logic circuit with weak PMOS Keeper

$$P_d = SfC_L V dd^2 (2.1)$$

The above equation explains that the dynamic power consumption, P<sub>d</sub> is varying proportionally with the square of the bias voltage, Vdd.

Here S denotes switching scale activity factor, f gives the rate at which the device switches called switching rate and C<sub>L</sub> represents the dynamic load capacitor.

From this equation it can mathematically be concluded that the effective reduction in the parameter Vdd, results in prominent minimization of the dynamic power consumption  $P_d$ . Added to this, it must also be taken into account that the time delay  $t_d$ , will get affected with power supply voltage Vdd, and threshold voltage Vth from the following equation.

$$t_d = \frac{C_L V dd^2}{K (V dd - V_{TH})^{\alpha}}$$

(2.2)

Here  $\alpha$  gives the velocity saturation index whose value is 1.3(approximately 1) for a short channel device and 2 for a long channel device [11-20]. K denotes the parameter which is described by the process of CMOS technology. Now let's take an ideal case from the equation that in order make time delay t<sub>d</sub>, independent of Vdd, the threshold voltage  $V_{TH}$ , must be set to zero for a short channel device whose approximated value of  $\alpha$  is 1. Thus it gives a striking effect on minimizing the time delay t<sub>d</sub> with the reduction of Vdd irrespective of V<sub>TH</sub>. But this assumption is highly impossible as each device possesses nonzero threshold voltage. Therefore this case is to be optimized. The threshold voltage V<sub>TH</sub>, is to be decreased in such a way that time delay t<sub>d</sub>, must not get affected by any means. This operation again results in the subsequent exponential increment in the sub threshold leakage current I<sub>leak</sub>. Hence in order to compensate this difficulty of getting higher leakages, the logic design engineer is any way forced to go for a PMOS keeper which is a bit larger than earlier minimum sized keeper device. Now with this, it gives two possible conditions for the process of discharging of dynamic load capacitor C<sub>L</sub> during the evaluation phase of the clock signal. Firstly, if load capacitor C<sub>L</sub> is to discharge, then the entire process will be decelerated due to the keeper device contention current. Secondly, as long as the contention keeper current is maintaining a greater value than the discharging current, the load capacitor C<sub>L</sub> will never get discharged to ground level at all.

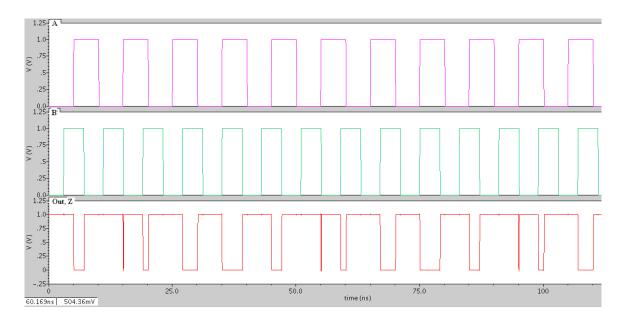

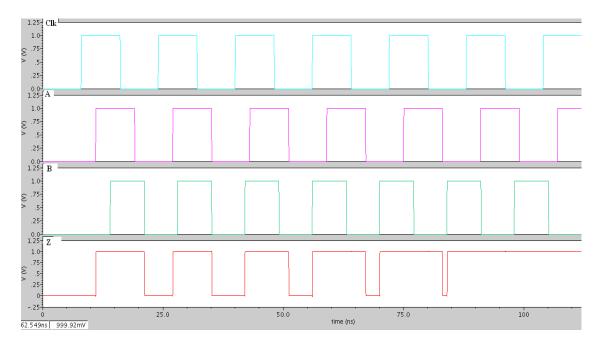

Fig. 2.21 Domino CMOS 2 Input AND gate with weak PMOS Keeper

Fig. 2.22 A Domino CMOS 2 Input AND gate with weak PMOS Keeper simulation

Table 2.2 Comparison of parameters with technology scaling for Domino CMOS 2input AND gate with PMOS keeper

| Technology<br>(in nm) | Power dissipation (in W) | Vth,n<br>(in V) | Vth,p<br>(in V) |

|-----------------------|--------------------------|-----------------|-----------------|

| 1200                  | 21.896E-12               | 0.607           | -0.832          |

| 500                   | 21.880E-12               | 0.708           | -0.918          |

| 350                   | 22.086E-12               | 0.549           | -0.680          |

| 250                   | 38.682E-12               | 0.365           | -0.562          |

| 180                   | 60.856E-12               | 0.372           | -0.394          |

#### **Observations from PMOS keeper circuit:**

- (1) The motivation for the reduction of the dynamic power consumption  $P_d$ , demands the logic designer to choose relatively small power supply voltage Vdd along with an effective lower threshold voltage ( $V_{TH}$ ), so as to maintain the performance and reliability of logic circuits.

- (2) The process of reducing the threshold voltage (V<sub>TH</sub>), results in the increment of the sub threshold leakage current, exponentially which demands the entrepreneur to select a greater than the small sized device keeper. This, during the clock's evaluation phase, will in turn increase the contention keeper current of the parallel PMOS transistor which will gradually decelerate the process of discharging of dynamic load capacitor.

- (3) Also it is concluded that in comparison with other existing logic styles, this particular domino CMOS logic technology loses its basic and fundamental advantage of high speed operation with the down scaling trend of the CMOS technology which became an essential requirement and imperative solution for all the applications where large number of faster NMOS devices are used in parallel inside the Pull Down Network (PDN), with the subsequent increment in the sub threshold leakage current of devices.