# DESIGN AND IMPLEMENTATION OF A NOVEL FLASH ADC FOR ULTRA WIDE BAND APPLICATIONS

A Thesis report submitted in partial fulfillment of the requirement for the degree of

# **Doctor** of Philosophy

In

### **ELECTRONICS AND COMMUNICATION ENGINEERING**

By

#### GEORGE TOM VARGHESE

(Roll no: 511EC102)

Under the guidance of

# Prof. KAMALAKANTA MAHAPATRA

Department of Electronics & Communication Engineering NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA

राष्ट्रीय प्रौदयोगिकी संस्थान, राउरकेला

**ODISHA, INDIA**

2014

# DESIGN AND IMPLEMENTATION OF A NOVEL FLASH ADC FOR ULTRA WIDE BAND APPLICATIONS

A Thesis report submitted in partial fulfillment of the requirement for the degree of

# **Moctor of Philosophy**

In

### **ELECTRONICS AND COMMUNICATION ENGINEERING**

By

#### GEORGE TOM VARGHESE

(Roll no: 511EC102)

Under the guidance of

# Prof. KAMALAKANTA MAHAPATRA

Department of Electronics & Communication Engineering NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA

राष्ट्रीय प्रौद्योगिकी संस्थान, राउरकेला

**ODISHA, INDIA**

2014

## Department of Electronics and Communication Engineering National Institute of Technology Rourkela-769008

# **CERTIFICATE**

This is to certify that the thesis entitled "Design and Implementation of a Novel Flash ADC for Ultra Wide Band Applications" submitted by Mr. George Tom Varghese in partial fulfillment of the requirements for the award of Doctor of Philosophy Degree in Electronics and Communication Engineering with specialization in "VLSI Design and Embedded Systems" during the session 2011-2014 at National Institute of Technology, Rourkela is an authentic work carried out by him under my supervision and guidance.

To the best of my knowledge, the matter embodied in the thesis has not been submitted to any other University/Institute for the award of any Degree or Diploma.

| Date:  | Prof. Kamalakanta Mahapatra                           |

|--------|-------------------------------------------------------|

| Place: | Department of Electronics & Communication Engineering |

|        | National Institute of Technology, Rourkela            |

# Dedicated To

Chachen, Amma & Achu

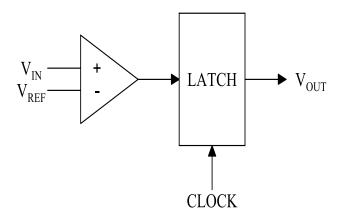

# **ACKNOWLEDGEMENTS**

This project is by far the most significant accomplishment in my life and it would have been impossible without the people who supported me and believed in me. I would like to extend my gratitude and my sincere thanks to my mentor, esteemed supervisor **Prof.**Kamala Kanta Mahapatra, H.O.D of Department of Electronics & Communication Engineering. I sincerely thank for his exemplary guidance and encouragement. His trust and support inspired me in the most important moments of making right decisions and I feel proud of working under his supervision.

I am also grateful to my Doctoral Scrutiny Committee Members, Prof. Sukadev Meher, Prof. S K. Patra, Prof. D. P. Acharya and Prof. Sanjeeb Mohanty. I am very much thankful to Prof. A. K. Swain for helping me in chip tape out design as well as in my lab duties. I am thankful to all the faculties of department of Electronics and Communication. I want to thank Mr. K. Venkata Ratnam with whom I shared my difficulties and as a special friend he helped a lot during this period. I want to thank Mr. Vijay Kumar Sharma (for helping me in doing corner analysis), Mr. Sudeendra Kumar (for sharing good thoughts in both technical as well as non technical), Mr. Jaganath Prasad Mohanty (For creating my cadence account), Mr Srinivasa V S Sarma D( For providing me accommodation in the interview time), Mr Sauvagya Ranjan Sahoo (For helping me in crucial junction), Mr. Venkata Ramakrishna (For providing me rfflow software), Mr. Rajesh Patjoshi ( My tea partner), Mr. Govind Rao, Mr. Gokulananada Sahoo, Dr. Karuppanan, Dr. Kanhu Charan Bhuyan and Mrs. Preethy Sudha Meher. Special thanks to my lovable friends and everybody who has helped me to complete the thesis work successfully. I am thankful to all my malayalee friends in NIT Rourkela.

Finally, and most importantly, I would like to express my deep appreciation to my Chachen, Amma, Chechimma, Cuckoochechi, Valiyaliyan, Kunjaliyan, Ryan, Rhys, Kevin and Jojy. Last but not least I am very much thankful to my Achu who supported me continuously in my final thesis submission time.

At last but above all, I owe this work to my much revered **GOD** for giving me such a chance to work among these scholastic people and scholastic environment.

#### **GEORGE TOM VARGHESE**

#### **ABSTRACT**

This dissertation presents a design and implementation of a novel flash ADC architecture for ultra wide band applications. The advancement in wireless technology takes us in to a world without wires. Most of the wireless communication systems use digital signal processing to transmit as well as receive the information. The real world signals are analog. Due to the processing complexity of the analog signal, it is converted to digital form so that processing becomes easier. The development in the digital signal processor field is rapid due to the advancement in the integrated circuit technology over the last decade. Therefore, analog-to-digital converter acts as an interface in between analog signal and digital signal processing systems. The continuous speed enhancement of the wireless communication systems brings out huge demands in speed and power specifications of high-speed low-resolution analog-to-digital converters.

Even though wired technology is a primary mode of communication, the quality and efficiency of the wireless technology allows us to apply to biomedical applications, in home services and even to radar applications. These applications are highly relying on wireless technology to send and receive information at high speed with great accuracy. Ultra Wideband (UWB) technology is the best method to these applications. A UWB signal has a bandwidth of minimum 500MHz or a fractional bandwidth of 25 percentage of its centre frequency. The two different technology standards that are used in UWB are multiband orthogonal frequency division multiplexing ultra wideband technology (MB-OFDM) and carrier free direct sequence ultra wideband technology (DS-UWB). ADC is the core of any UWB receiver. Generally a high speed flash ADC is used in DS-UWB receiver.

Two different flash ADC architectures are proposed in this thesis for DS-UWB applications. The first design is a high speed five bit flash ADC architecture with a sampling rate of 5 GS/s. The design is verified using CADENCE tool with CMOS 90 nm technology. The total power dissipation of the ADC is 8.381 mW from power supply of 1.2 V. The die area of the proposed flash ADC is 186  $\mu$ m  $\times$  210  $\mu$ m (0.039 mm²). The proposed flash ADC is analysed and compared with other papers in the literature having same resolution and it is concluded that it has the highest speed of operation with medium power dissipation.

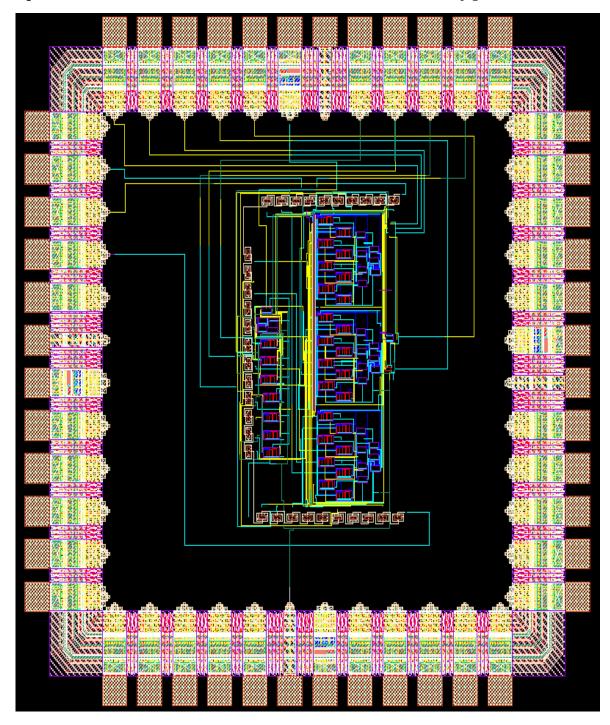

The second design is a reconfigurable five bit flash ADC architecture with a sampling rate of 1.25 GS/s. The design is verified using CADENCE tool with UMC 180 nm technology. The total power dissipation of the ADC is 11.71 mW from power supply of 1.8 V. The die area of the implementation is 432  $\mu$ m  $\times$  720  $\mu$ m (0.31104 mm²). The chip tape out of the proposed reconfigurable flash ADC is made for fabrication.

## Contents

| ACKN    | OWLEDGEMENTS                                                         | i   |

|---------|----------------------------------------------------------------------|-----|

| ABSTF   | RACT                                                                 | ii  |

| LIST C  | OF FIGURES                                                           | xi  |

| LIST C  | OF TABLES                                                            | xv  |

| ABBRI   | EVIATION                                                             | xvi |

| СНАРТ   | TER 1                                                                | 1   |

| OVERV   | VIEW                                                                 | 1   |

| 1.1     | Introduction to research                                             | 1   |

| 1.2     | Motivation                                                           | 1   |

| 1.3     | Research aims and objectives                                         | 2   |

| 1.4     | Design methodology                                                   | 3   |

| 1.5     | Thesis Organization                                                  | 4   |

| 1.6     | Thesis Contributions                                                 | 5   |

| 1.7     | Conclusion                                                           | 5   |

| СНАРТ   | TER 2                                                                | 7   |

| Introdu | uction to UWB and Selection of ADC architecture for UWB applications | 7   |

| 2.1     | Introduction to UWB                                                  | 7   |

| 2.2     | Applications of UWB                                                  | 8   |

| 2.2     | 2.1 Military Applications                                            | 8   |

| 2.2     | 2.2 Biomedical health monitoring system                              | 8   |

| 2.2     | 2.3 In-home wireless connectivity                                    | 9   |

| 2.2     | 2.4 Collision avoidance system                                       | 9   |

| 2.3     | Characterization of UWB                                              | 9   |

| 2.4     | Comparison with other communication schemes                          | 10  |

| 2.4     | 4.1 WiFi (802.11 x)                                                  | 10  |

| 2.4     | 4.2 Zig-Bee and Bluetooth                                            | 11  |

| 2.5     | Ultra Wideband Standards                                             | 12  |

| 2.5.1     | Multi Band Orthogonal Frequency Division Multiplexing Ultra Wide Band |    |

|-----------|-----------------------------------------------------------------------|----|

| Technolo  | gy (MB-OFDM)                                                          | 12 |

| 2.5.2     | Direct Sequence UWB standard                                          | 13 |

| 2.6 Intro | duction to Analog to Digital Converter                                | 15 |

| 2.6.1     | Flash ADC                                                             | 16 |

| 2.6.2     | Pipeline ADC                                                          | 18 |

| 2.6.3     | Successive Approximation Register (SAR) ADC                           | 18 |

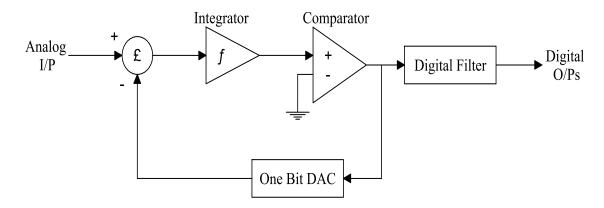

| 2.6.4     | Sigma-delta ADC                                                       | 20 |

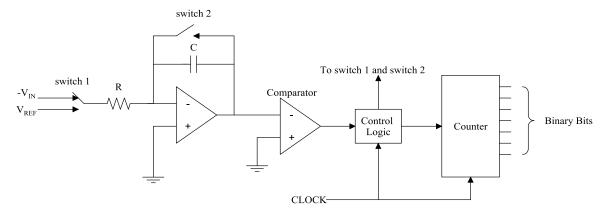

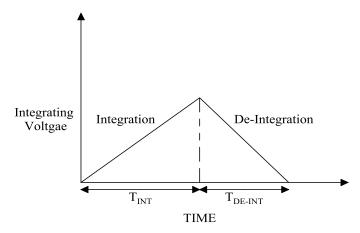

| 2.6.5     | Dual slope ADC                                                        | 21 |

| 2.7 Com   | parison of different ADC architectures                                | 22 |

| 2.8 ADC   | Characterization parameters                                           | 24 |

| 2.8.1     | Static characteristics                                                | 24 |

| 2.8.1.1   | Resolution                                                            | 24 |

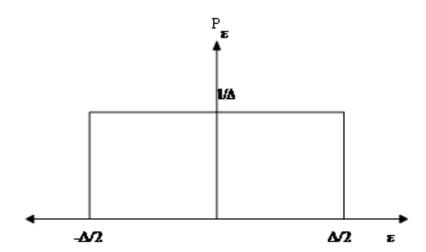

| 2.8.1.2   | Quantization error                                                    | 24 |

| 2.8.1.3   | Conversion speed                                                      | 26 |

| 2.8.1.4   | Offset error                                                          | 26 |

| 2.8.1.5   | Gain error                                                            | 26 |

| 2.8.1.6   | Differential Nonlinearity (DNL)                                       | 27 |

| 2.8.1.7   | Integral Nonlinearity (INL)                                           | 28 |

| 2.8.2     | Dynamic characteristics                                               | 28 |

| 2.8.2.1   | Signal to quantization ratio (SQNR) or SNR                            | 28 |

| 2.8.2.2   | Signal to noise distortion ratio (SNDR)                               | 28 |

| 2.8.2.3   | Effective number of bits (ENOB)                                       | 29 |

| 2.8.2.4   | Spurious free dynamic range (SFDR)                                    | 29 |

| 2.9 Selec | etion of ADC architecture                                             | 29 |

| 2.10 Conc | clusion                                                               | 30 |

| CHAPTER 3 |                                                                       | 32 |

| COMPARATOR DESIGN                                                        | 32           |

|--------------------------------------------------------------------------|--------------|

| 3.1 Introduction to comparator                                           | 32           |

| 3.2 Comparator characteristics                                           | 33           |

| 3.2.1 Static Characteristics                                             | 33           |

| 3.2.1.1 Gain                                                             | 33           |

| 3.2.1.2 Offset voltage                                                   | 34           |

| 3.2.1.3 Input common mode range                                          | 35           |

| 3.2.1.4 Noise                                                            | 35           |

| 3.2.2 Dynamic characteristics                                            | 35           |

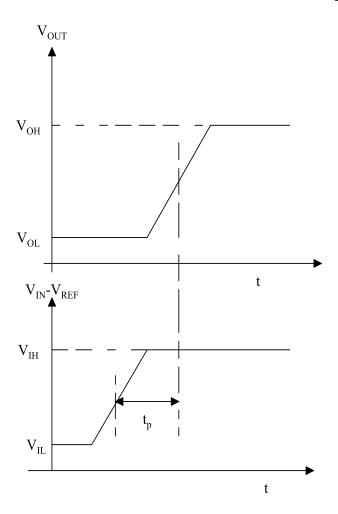

| 3.2.2.1 Propagation delay                                                | 35           |

| 3.2.2.2 Slew rate                                                        | 36           |

| 3.2.2.3 Comparator sensitivity                                           | 37           |

| 3.3 Different types of comparators                                       | 37           |

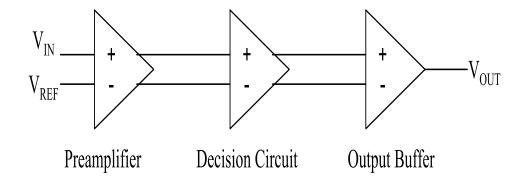

| 3.3.1 Open loop comparators                                              | 37           |

| 3.3.2 Regenerative comparators                                           | 37           |

| 3.3.2.1 Non-clocked comparators                                          | 37           |

| 3.3.2.2 Clocked Comparators                                              | 38           |

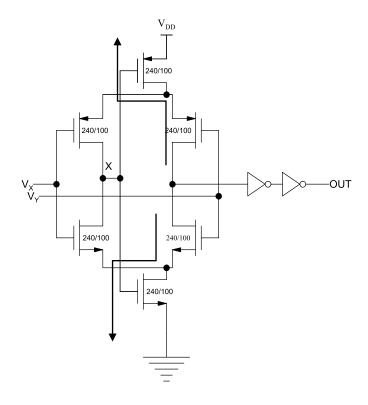

| 3.4 Design of a high speed preamplifier based pseudo dynamic latched con | nparator for |

| high speed ADCs                                                          | 39           |

| 3.4.1 Preamplifier design                                                | 41           |

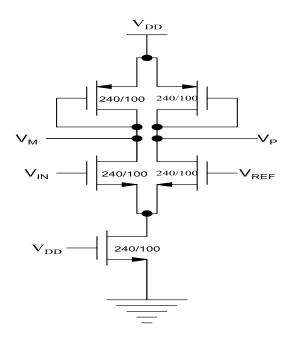

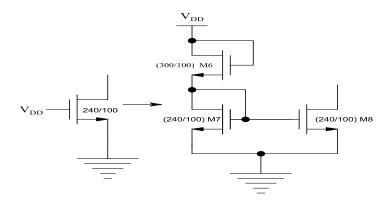

| 3.4.1.1 Existing preamplifier                                            | 42           |

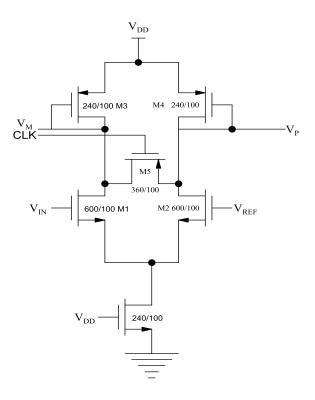

| 3.4.1.2 Modified preamplifier                                            | 42           |

| 3.4.1.3 Modified current source architecture                             | 43           |

| 3.4.2 Latch stage design                                                 | 44           |

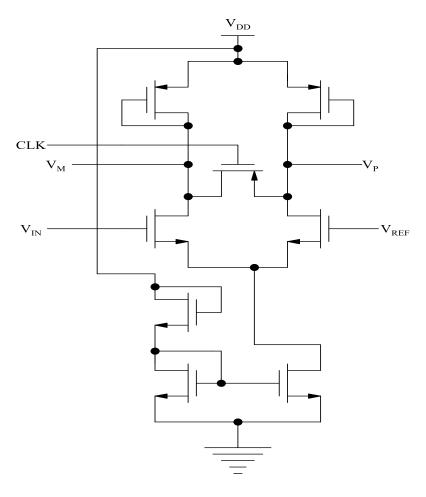

| 3.4.2.1 Existing dynamic latch                                           | 45           |

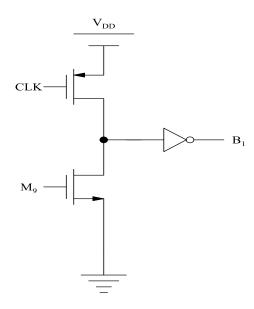

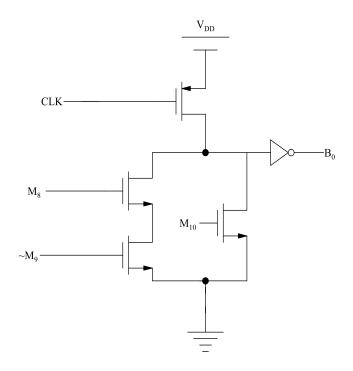

| 3.4.2.2 Proposed pseudo dynamic latch                                    | 46           |

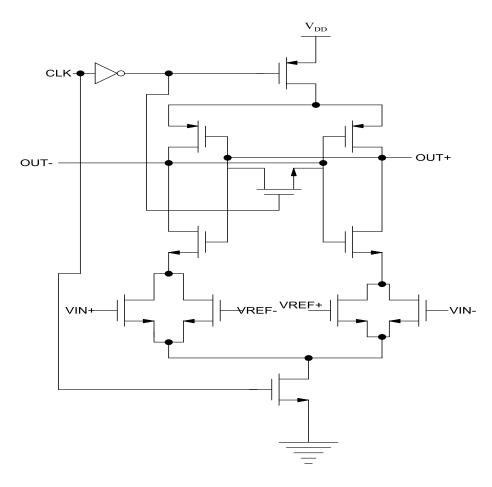

| 3.4.3 Output buffer                                                      | 47           |

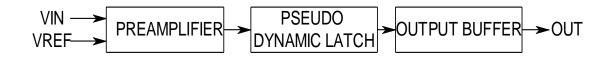

| 3   | .5 BI  | ock diagram of comparator                                            | 48  |

|-----|--------|----------------------------------------------------------------------|-----|

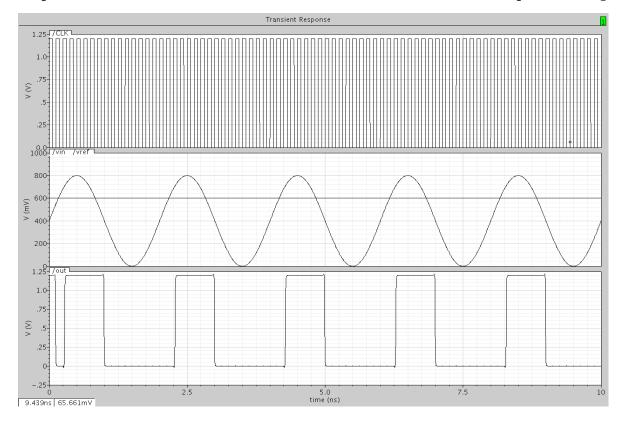

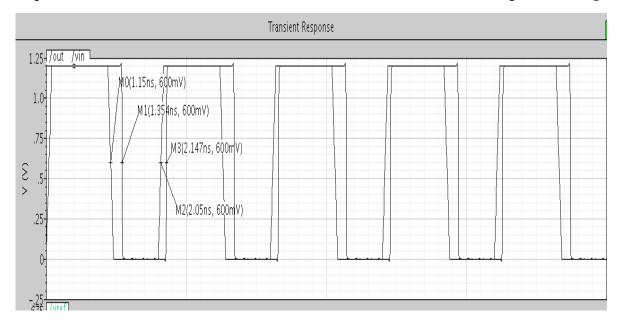

| 3   | .6 Tr  | ansient analysis of the proposed comparator                          | 48  |

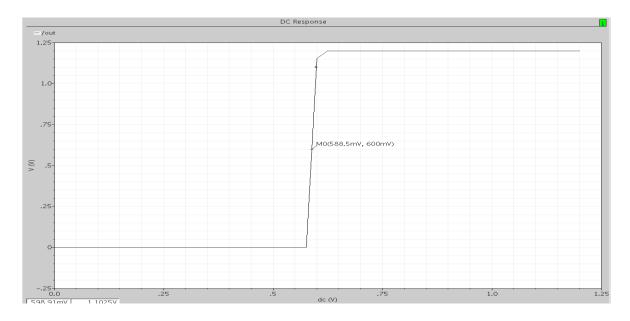

| 3   | .7 Pr  | operties of the proposed comparator                                  | 49  |

|     | 3.7.1  | Offset voltage                                                       | 49  |

|     | 3.7.2  | Maximum gain                                                         | 50  |

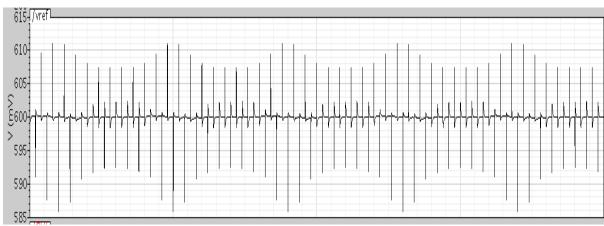

|     | 3.7.3  | Kick back noise                                                      | 51  |

|     | 3.7.4  | Hysteresis                                                           | 52  |

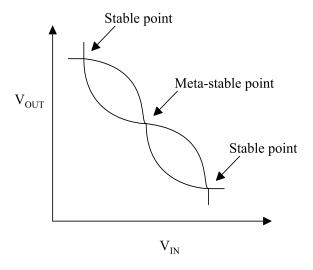

|     | 3.7.5  | Meta-stability error                                                 | 52  |

|     | 3.7.6  | Propagation delay                                                    | 53  |

| 3   | .8 Pr  | e-layout process corner simulation results                           | 54  |

| CH. | APTER  | 4                                                                    | 60  |

| EN  | CODER  | DESIGN FOR FLASH ADC                                                 | 60  |

| 4   | .1 In  | roduction                                                            | 60  |

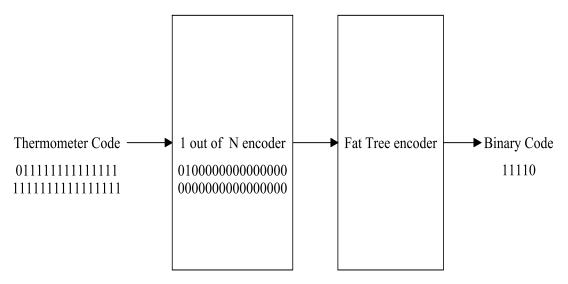

| 4   | .2 Di  | fferent types of thermometer to binary code encoders                 | 60  |

|     | 4.2.1  | ROM encoder                                                          | 60  |

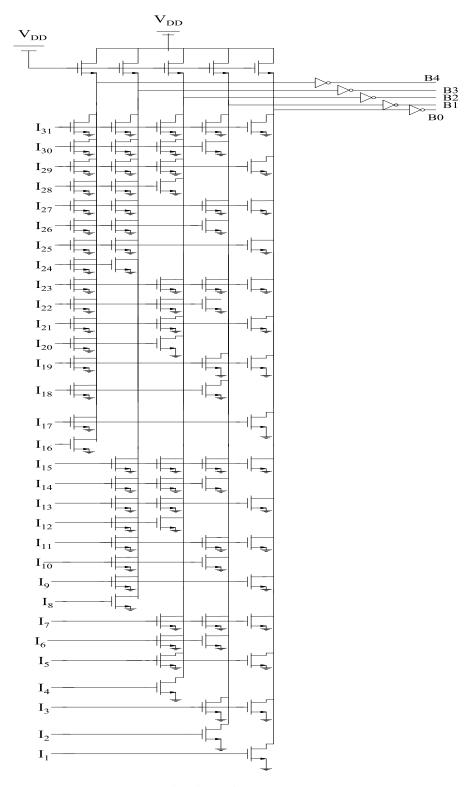

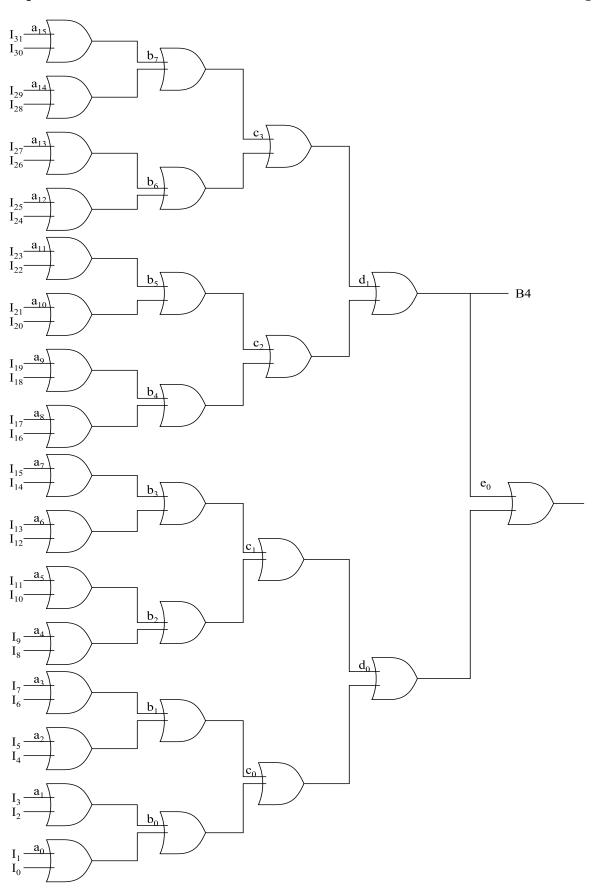

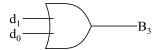

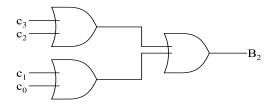

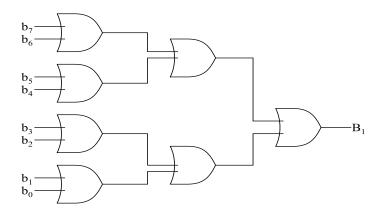

|     | 4.2.2  | Fat tree encoder                                                     | 62  |

|     | 4.2.3  | Wallace tree encoder                                                 | 65  |

|     | 4.2.4  | Modified five bit Wallace tree encoder for low power application     | 66  |

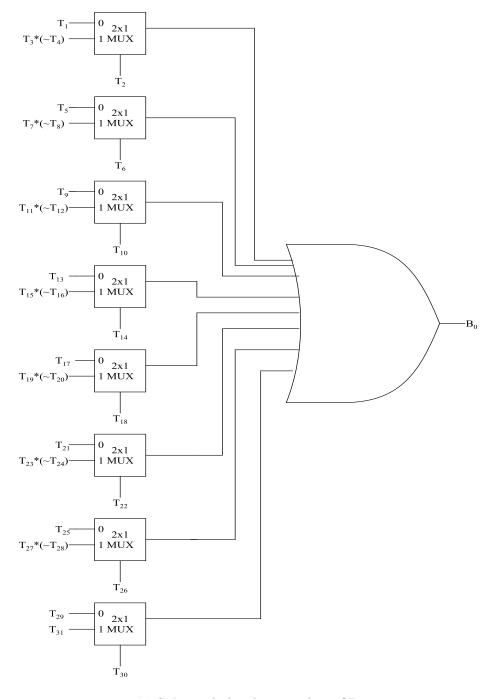

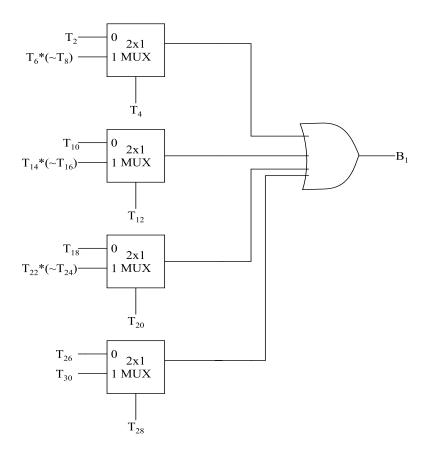

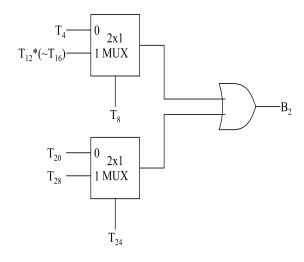

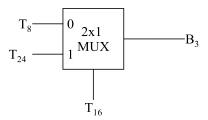

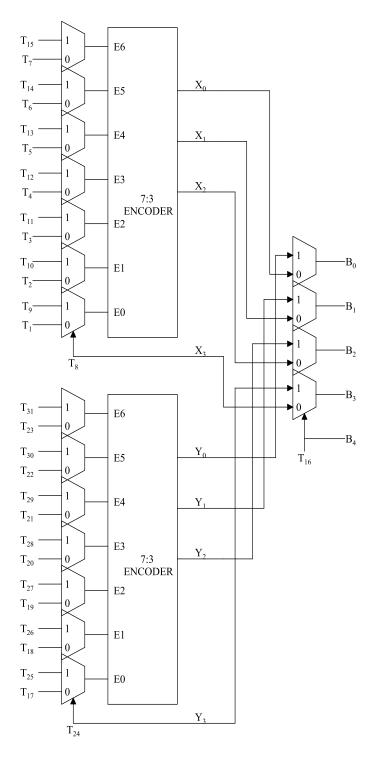

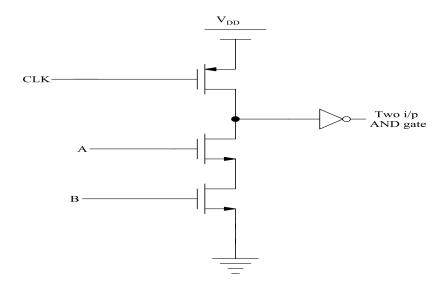

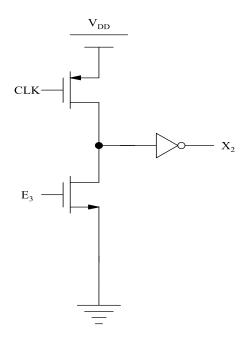

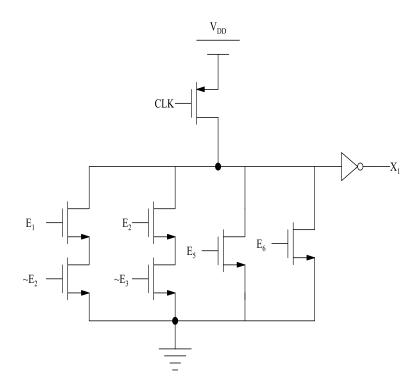

|     | 4.2.5  | Multiplexer based encoder                                            | 75  |

|     | 4.2.6  | Modified low power multiplexer based encoder for five bit flash ADCs | 76  |

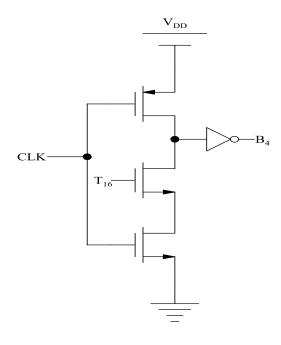

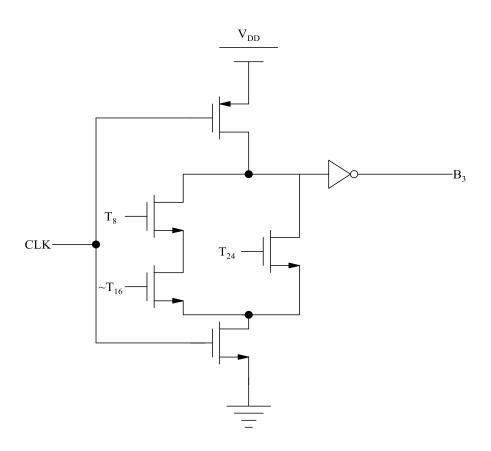

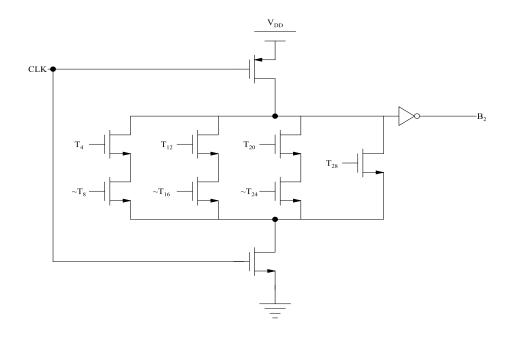

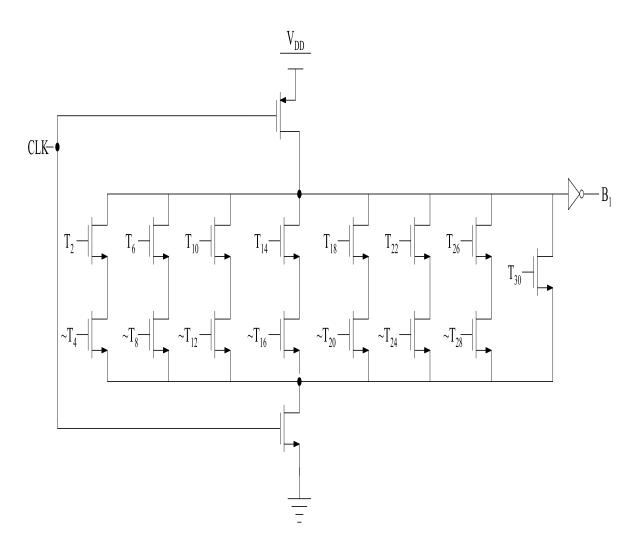

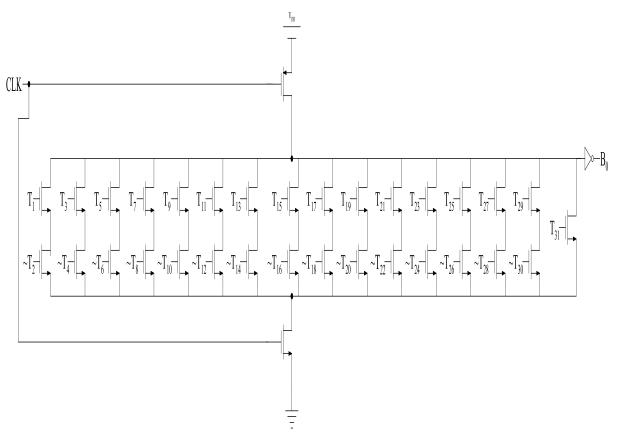

|     | 4.2.7  | High speed reconfigurable encoder for five bit flash ADCs            | 82  |

|     | 4.2.8  | High speed low power reconfigurable encoder for five bit flash ADCs  | 84  |

|     | 4.2.9  | Performance Comparison of five bit Thermometer code to Binary code   |     |

|     | Conve  | rsion using Different Logic Styles                                   | 92  |

|     | 4.2.10 | A High speed noise tolerant encoder for a 5 GS/s five bit flash ADC  | 109 |

|     | 4.2.11 | Layout of the proposed encoder                                       | 117 |

|     | 4.2.12 | Post layout simulation                                               | 118 |

| 4.2.13   | Post layout corner simulation results of proposed encoder   | 118 |

|----------|-------------------------------------------------------------|-----|

| 4.2.14   | Comparison with other encoders                              | 119 |

| 4.3 Co   | nclusion                                                    | 119 |

| CHAPTER  | 5                                                           | 122 |

| FLASH AD | C IMPLEMENTATION                                            | 122 |

| 5.1 Int  | roduction                                                   | 122 |

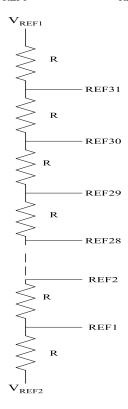

| 5.2 Re   | sistor ladder                                               | 122 |

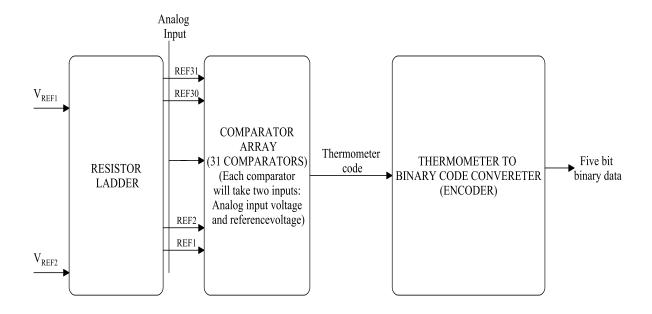

| 5.3 Co   | mparator                                                    | 126 |

| 5.4 En   | coder                                                       | 126 |

| 5.5 Fla  | ash ADC top level implementation                            | 126 |

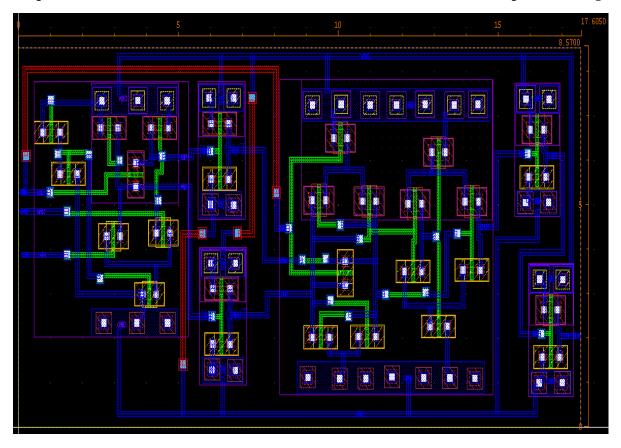

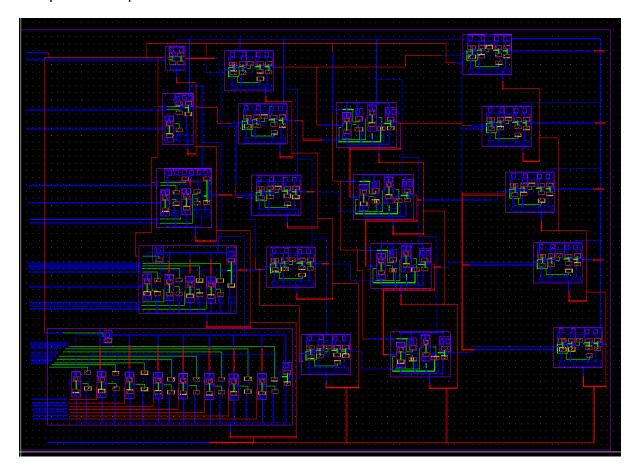

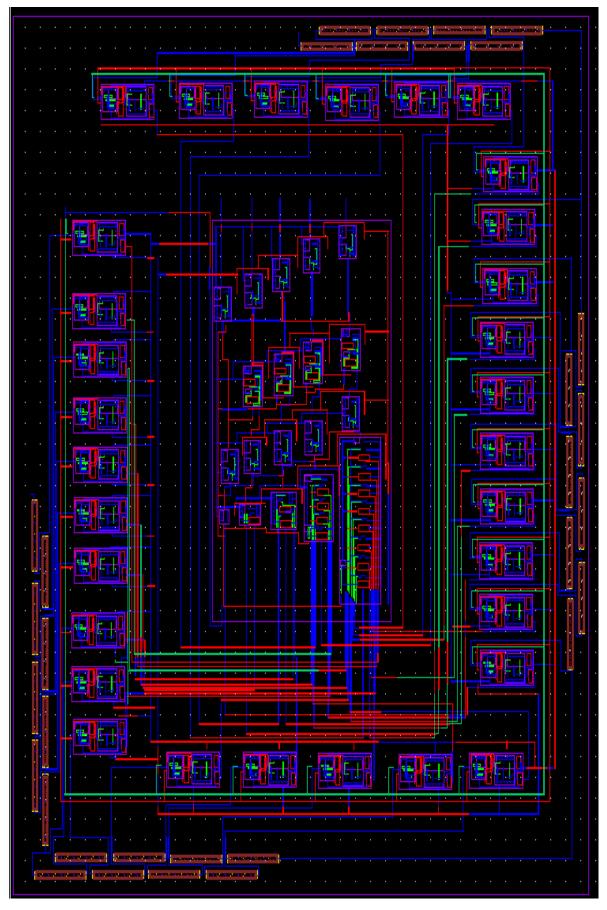

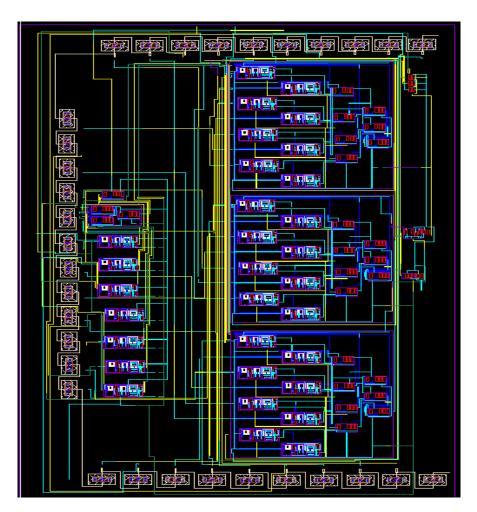

| 5.6 La   | yout of ADC                                                 | 127 |

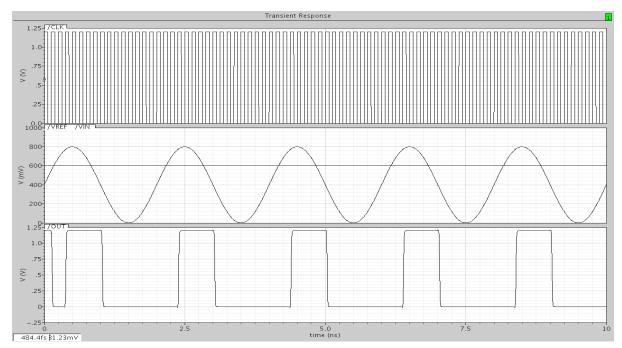

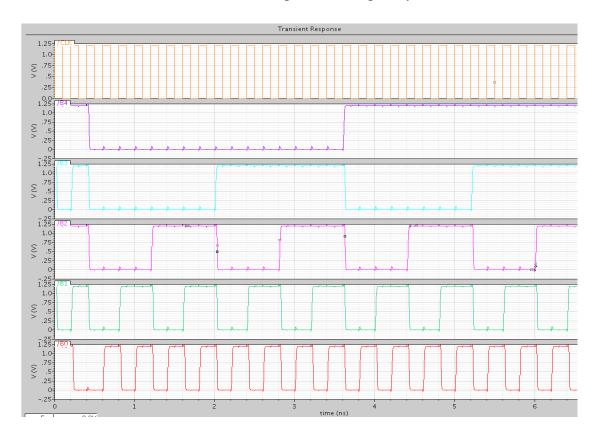

| 5.7 Po   | st layout simulation                                        | 129 |

| 5.8 Per  | rformance metrics of proposed flash ADC                     | 130 |

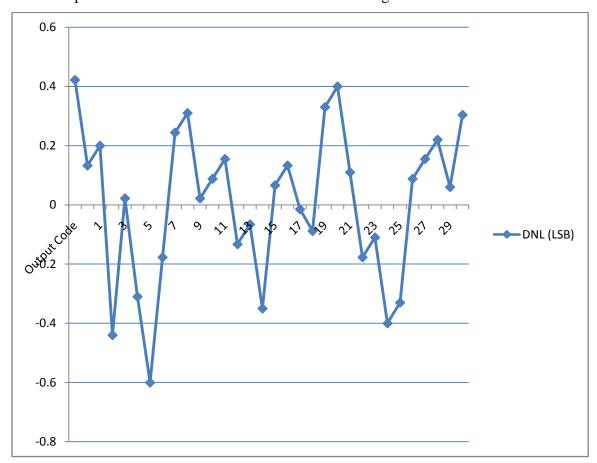

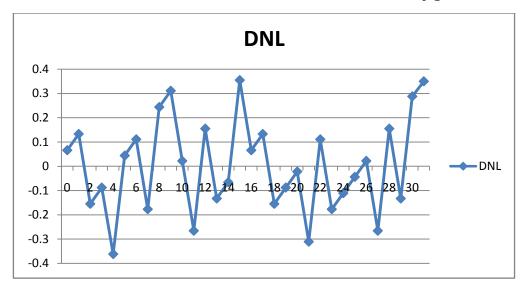

| 5.8.1    | DNL                                                         | 130 |

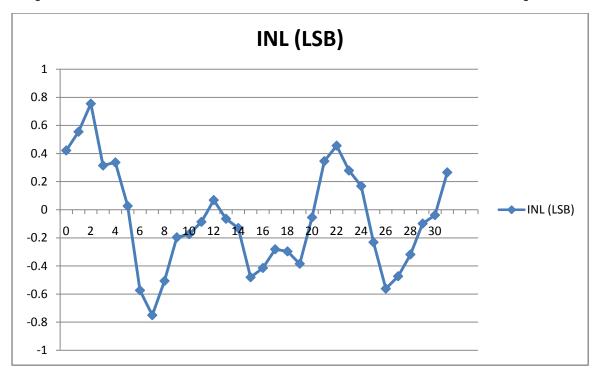

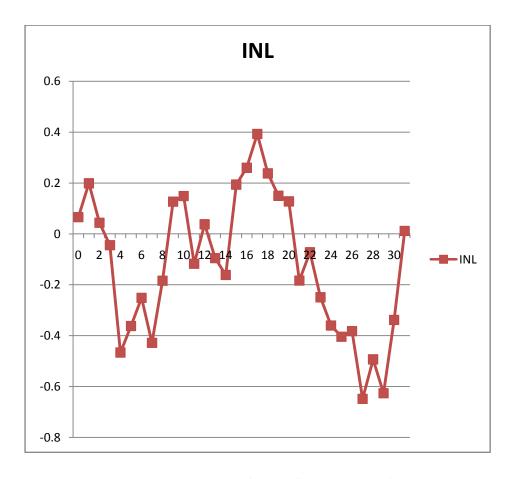

| 5.8.2    | INL                                                         | 130 |

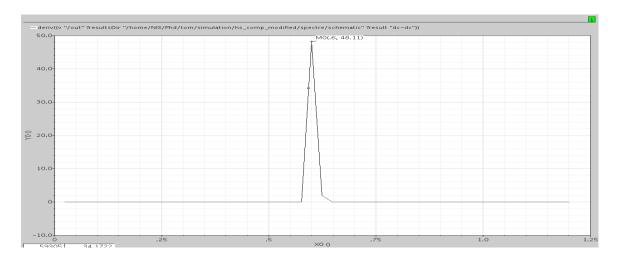

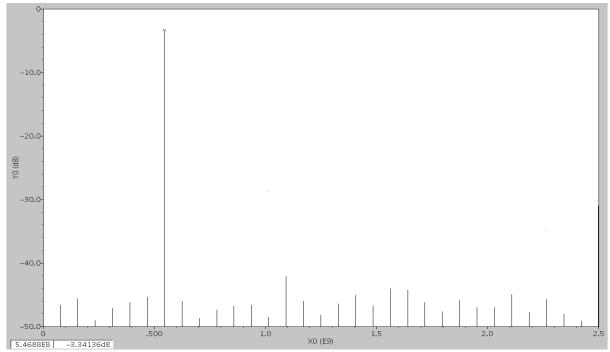

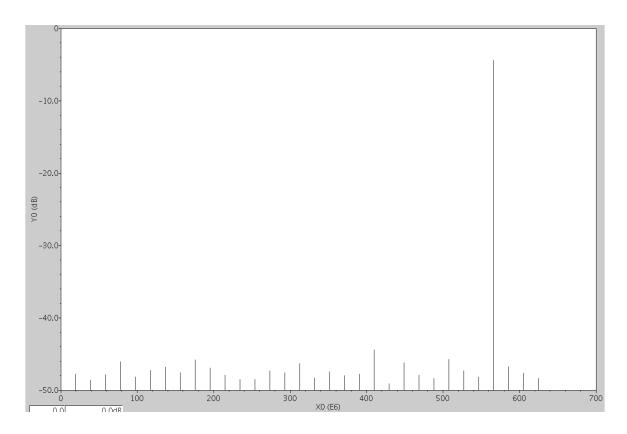

| 5.8.3    | Frequency spectrum                                          | 131 |

| 5.8.4    | SNDR                                                        | 132 |

| 5.8.5    | ENOB                                                        | 132 |

| 5.8.6    | Figure of merit (FoM)                                       | 132 |

| 5.9 Co   | rner analysis of proposed flash ADC                         | 132 |

| 5.10 Ch  | aracteristic curves of proposed flash ADC                   | 133 |

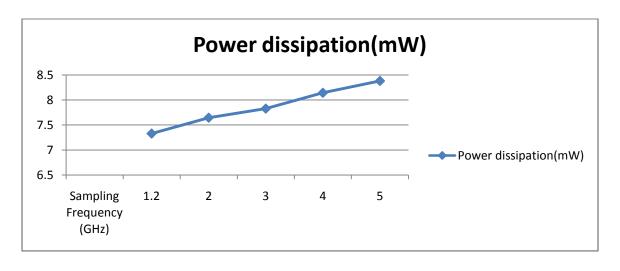

| 5.10.1   | Power dissipation Vs Sampling frequency                     | 133 |

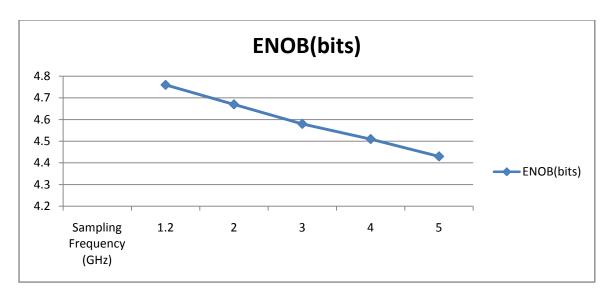

| 5.10.2   | ENOB Vs Sampling Frequency                                  | 134 |

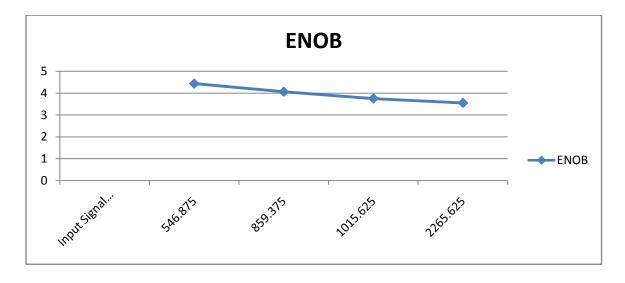

| 5.10.3   | ENOB Vs input signal frequency                              | 134 |

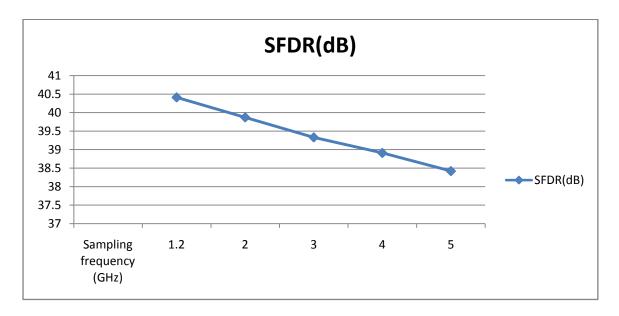

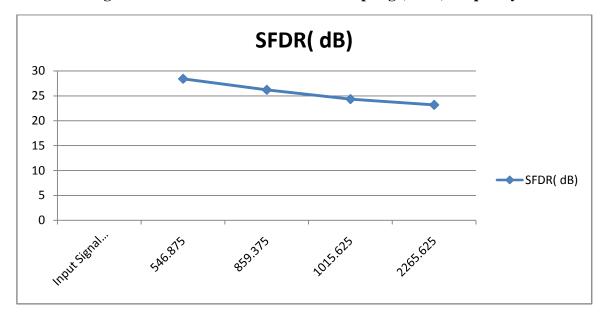

| 5.10.4   | SFDR Vs clock frequency and SFDR Vs input signal frequency  | 135 |

| 5.11 Su  | mmary of the performance of the proposed five bit flash ADC | 136 |

| 5.12 Co  | mparison with other works                                   | 137 |

| 5.13  | Conclusion                                               | 138      |

|-------|----------------------------------------------------------|----------|

| СНАРТ | ΓER 6                                                    | 139      |

| DESIG | N OF A RECONFIGURABLE FIVE BIT FLASH ADC AND ITS CHIP    | TAPE OUT |

|       |                                                          | 139      |

| 6.1   | Introduction                                             | 139      |

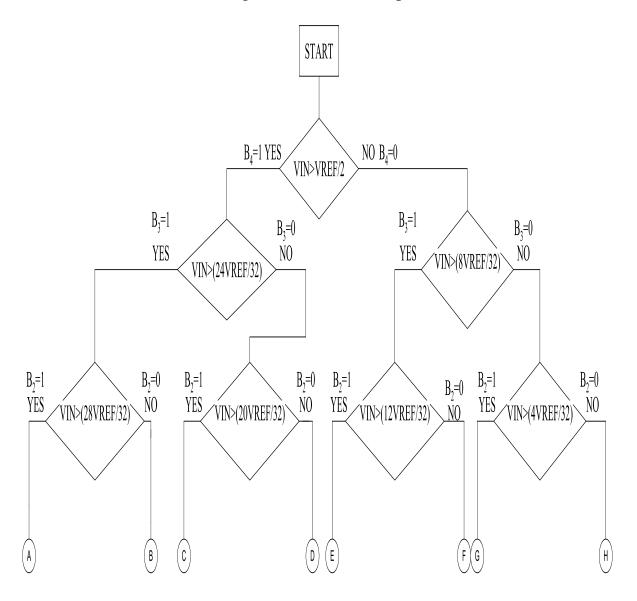

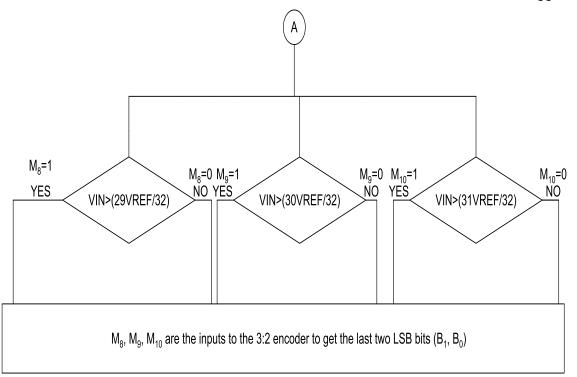

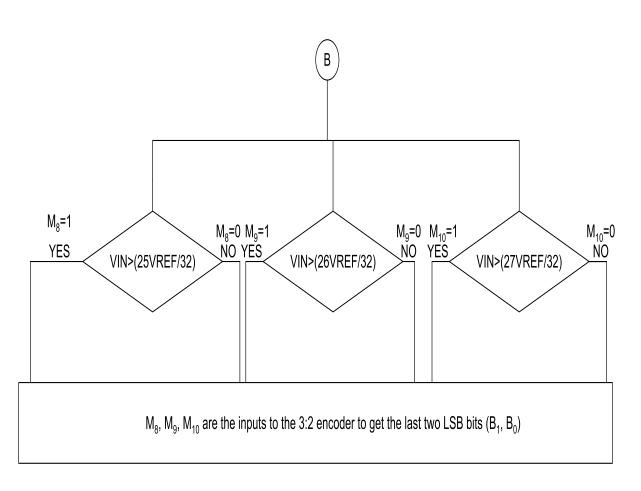

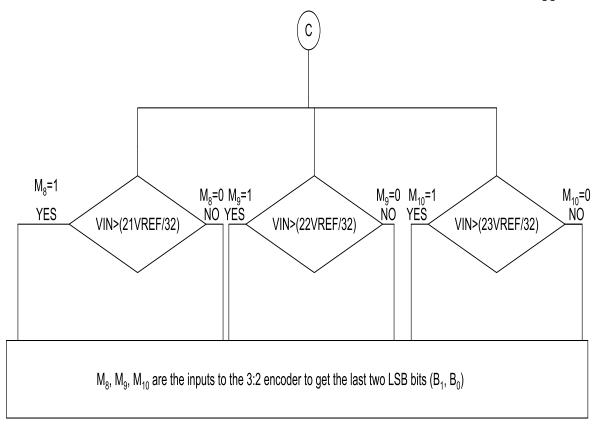

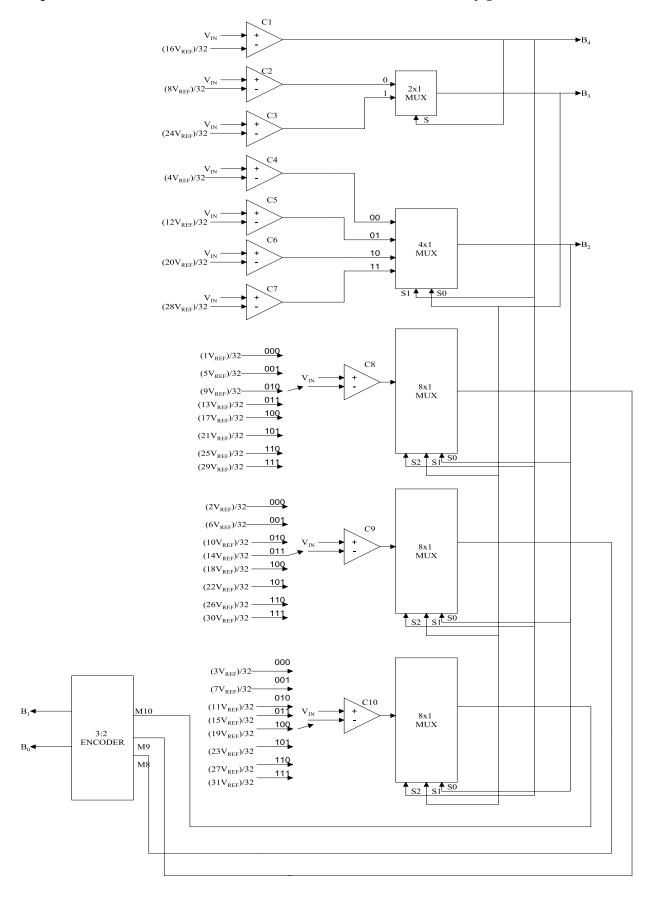

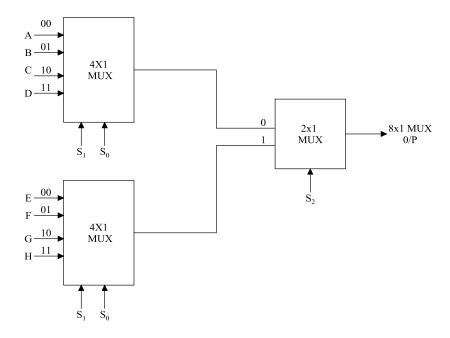

| 6.2   | Architecture of reconfigurable flash ADC.                | 140      |

| 6.3   | Implementation of the reconfigurable block               | 142      |

| 6.3   | 3.1 Comparator                                           | 142      |

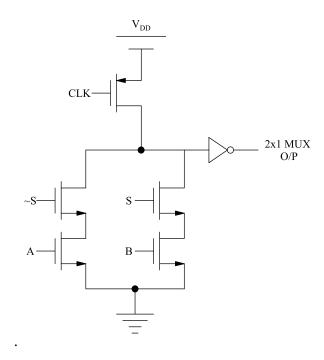

| 6.3   | 3.2 2X1 multiplexer                                      | 142      |

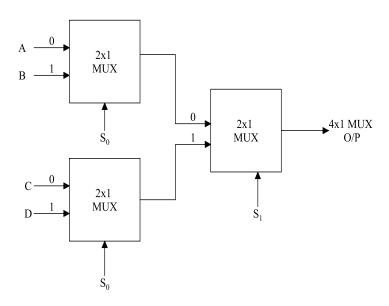

| 6.3   | 3.3 4X1 multiplexer                                      | 143      |

| 6.3   | 8.4 8X1 multiplexer                                      | 144      |

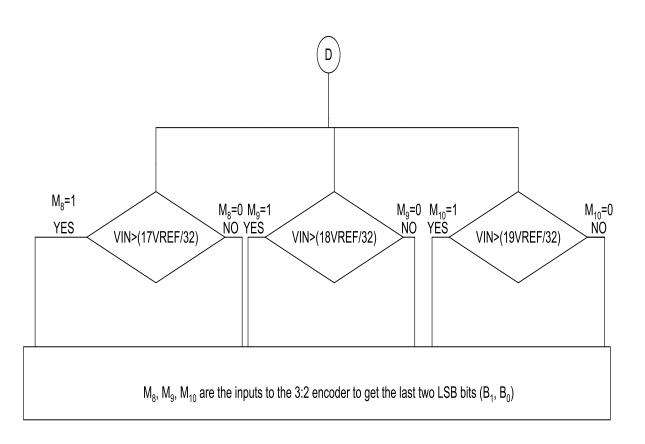

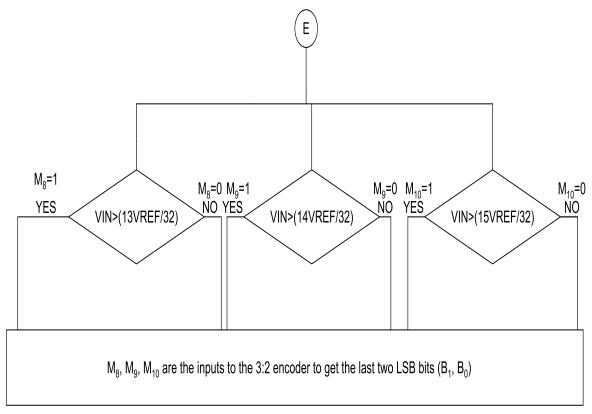

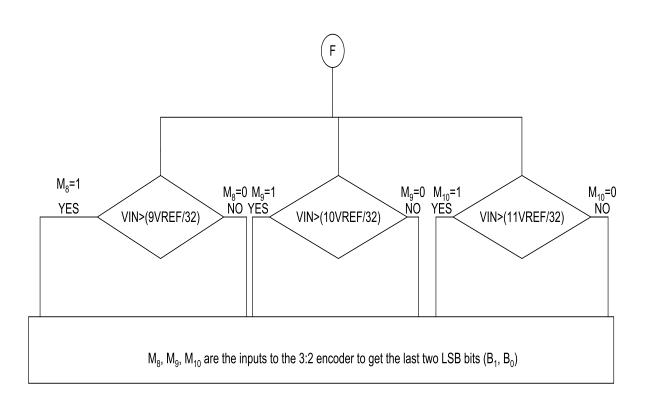

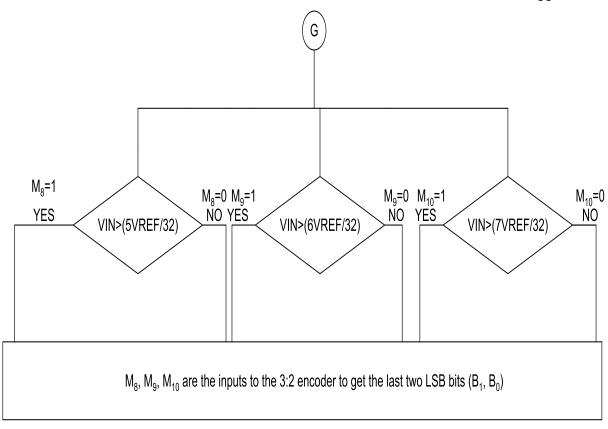

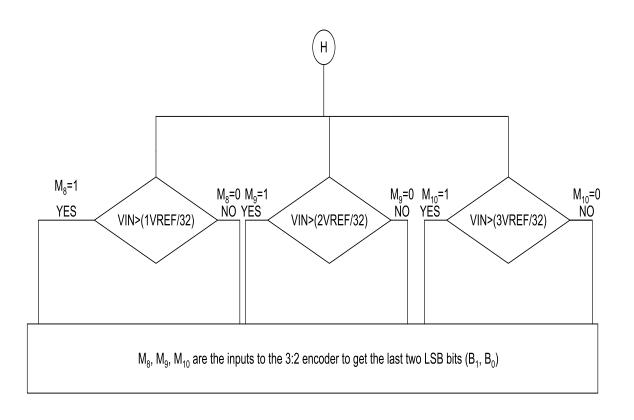

| 6.3   | 3.5 3:2 Encoder implementation                           | 144      |

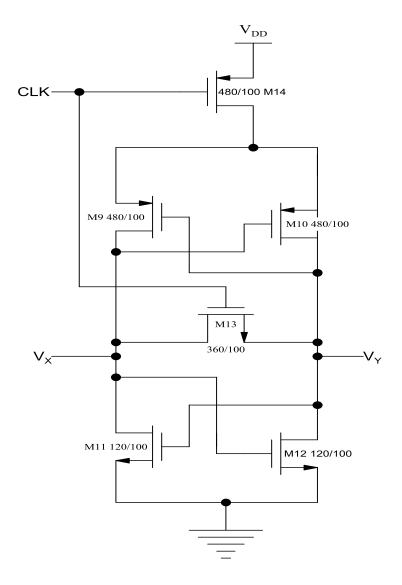

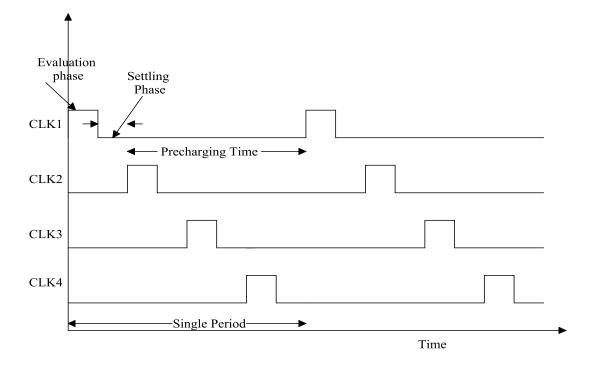

| 6.4   | Clocking mechanism in the proposed flash ADC             | 145      |

| 6.5   | Layout of the implementation                             | 146      |

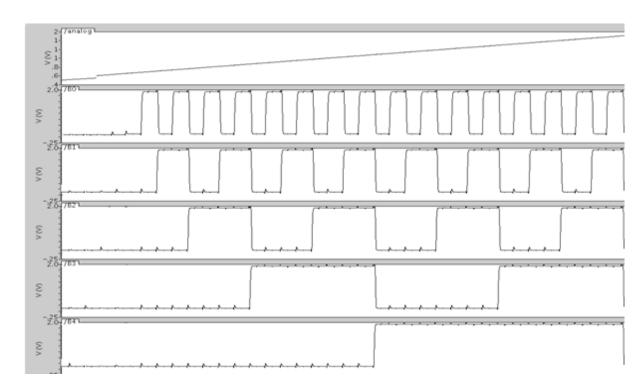

| 6.6   | Post layout simulation                                   | 147      |

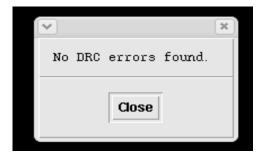

| 6.6   | DRC check                                                | 147      |

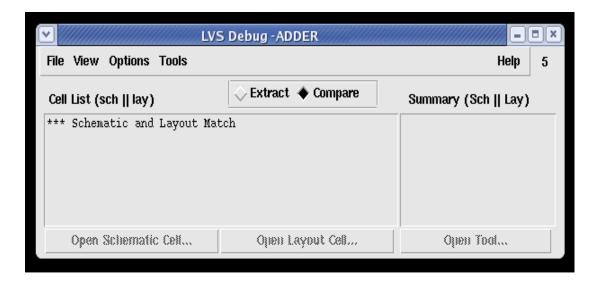

| 6.6   | 5.2 LVS Check                                            | 147      |

| 6.6   | 5.3 RCX extraction                                       | 148      |

| 6.7   | Performance metrics of proposed reconfigurable ADC       | 148      |

| 6.7   | '.1 DNL                                                  | 148      |

| 6.7   | 7.2 INL                                                  | 149      |

| 6.7   | 7.3 Frequency spectrum                                   | 150      |

| 6.7   | '.4 SNDR                                                 | 150      |

| 6.7   | 7.5 ENOB                                                 | 150      |

| 6.7   | 7.6 Figure of merit (FOM)                                | 151      |

| 6.8   | Corner analysis of the proposed reconfigurable flash ADC | 151      |

| 6.9   | Reconfigurable operation                                 | 152      |

| 6.10 Performance summary of the proposed reconfigurable ADC  | 152 |

|--------------------------------------------------------------|-----|

| 6.11 Comparison with other works                             | 153 |

| 6.12 Chip Tape out implementation of reconfigurable ADC      | 154 |

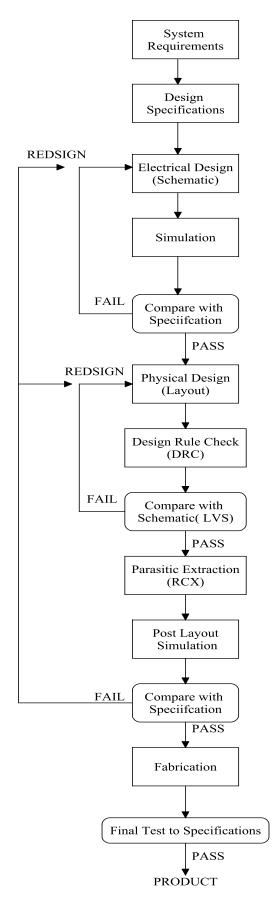

| 6.12.1 System requirements and design specifications         | 155 |

| 6.12.2 Schematic capture                                     | 155 |

| 6.12.3 Simulation                                            | 155 |

| 6.12.4 Physical design                                       | 155 |

| 6.12.5 Design rule check (DRC)                               | 155 |

| 6.12.6 LVS (Layout Vs Schematic matching)                    | 157 |

| 6.12.7 Parasitic capacitance and resistance extraction (RCX) | 157 |

| 6.12.8 Post layout simulation                                | 157 |

| 6.12.9 Fabrication                                           | 157 |

| 6.12.10 Final testing                                        | 157 |

| 6.13 Conclusion                                              | 158 |

| CHAPTER 7                                                    | 160 |

| CONCLUSION & FUTURE SCOPE                                    | 160 |

| 7.1 Conclusion                                               | 160 |

| 7.1.1 Research contributions                                 | 161 |

| 7.2 Future Scope                                             | 161 |

| Bibliography                                                 | 162 |

| List of Publications                                         | 168 |

| APPENDIX                                                     | 169 |

# LIST OF FIGURES

| Fig. 1.1 Block diagram of UWB receiver                                      | 2  |

|-----------------------------------------------------------------------------|----|

| Fig. 1.2 Block diagram of proposed flash ADC                                | 3  |

| Fig. 2. 1 MB-OFDM UWB receiver topology                                     | 12 |

| Fig. 2.2 Block diagram of DS-UWB receiver                                   | 14 |

| Fig. 2.3 Block diagram of analog to digital converter                       | 16 |

| Fig. 2.4 Generic block diagram of flash ADC                                 | 17 |

| Fig. 2.5 Basic architecture of pipeline ADC                                 | 18 |

| Fig. 2.6 Block Diagram of SAR ADC                                           | 19 |

| Fig. 2.7 Block Diagram of Sigma delta ADC                                   | 20 |

| Fig. 2.8 Architecture of Dual slope ADC                                     | 21 |

| Fig. 2.9 Timing diagram of dual slope ADC                                   | 22 |

| Fig. 2.10 Probability density function of the quantization noise            | 25 |

| Fig. 2.11 (a) ADC characteristics with offset (b) Ideal ADC characteristics | 26 |

| Fig. 2. 12 Gain error in ADC                                                | 27 |

| Fig. 2. 13 Non ideal ADC with DNL and INL                                   | 27 |

| Fig. 3. 1 Block diagram of basic comparator                                 | 32 |

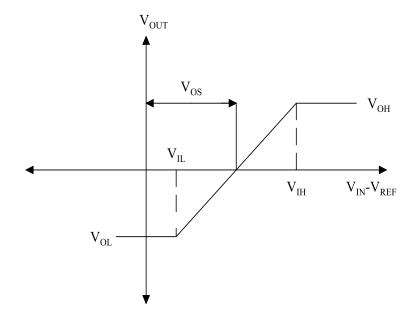

| Fig. 3.2 Transfer characteristics of ideal comparator                       | 33 |

| Fig. 3.3 Transfer curve of a comparator with a finite gain                  | 34 |

| Fig. 3.4 Comparator transfer characteristics with offset voltage            | 35 |

| Fig. 3.5 Propagation delay time of comparator                               | 36 |

| Fig. 3.6 Block diagram of non-clocked comparator                            | 38 |

| Fig. 3.7 Block diagram of clocked comparator                                | 38 |

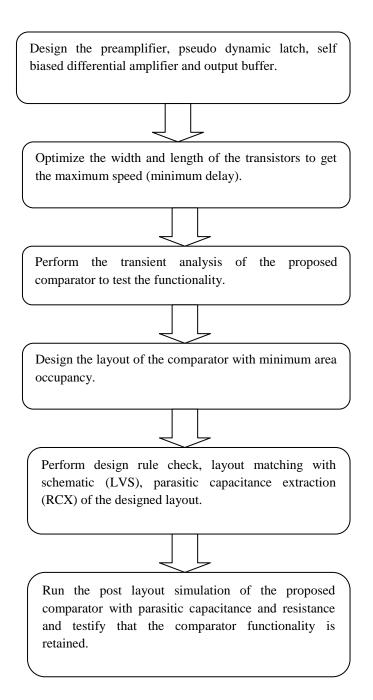

| Fig. 3.8 Flowchart of the design of the proposed comparator                 | 40 |

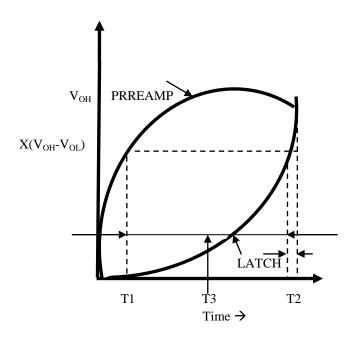

| Fig. 3.9 Response of preamplifier and latch                                 | 41 |

| Fig. 3.10 Existing preamplifier                                             | 42 |

| Fig. 3.11 Modified preamplifier                                             | 43 |

| Fig. 3.12 Modified current source                                           | 44 |

| Fig. 3.13 Complete preamplifier circuit                                     | 44 |

| Fig. 3.14 Existing dynamic latch                                            | 45 |

| Fig. 3.15 Proposed pseudo dynamic latch                                     | 46 |

| Fig. 3.16 Output buffer                                                     | 48 |

| Fig. 3.17 Block diagram of Comparator                                       | 48 |

| Fig. 3.18 Transient analysis of the proposed comparator                                                                      | 49    |

|------------------------------------------------------------------------------------------------------------------------------|-------|

| Fig. 3.19 Transfer curve of the comparator                                                                                   | 49    |

| Fig. 3.20 Maximum gain of the comparator                                                                                     | 50    |

| Fig. 3.21 Kick back noise simulation.                                                                                        | 51    |

| Fig. 3.22 VTC of back to back connected two inverters                                                                        | 52    |

| Fig. 3.23 Propagation delay                                                                                                  | 54    |

| Fig. 3. 24 Layout of the proposed Comparator                                                                                 | 56    |

| Fig. 3. 25 Post Layout Simulation of the proposed comparator                                                                 | 57    |

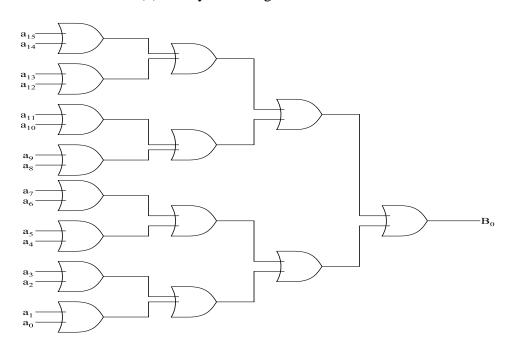

| Fig. 4.1 ROM encoder                                                                                                         | 61    |

| Fig. 4.2 Block diagram of fat tree encoder                                                                                   | 62    |

| Fig. 4. 3 Binary code generation circuit using fat tree encoder                                                              | 64    |

| Fig. 4.4 Five bit Wallace tree encoder                                                                                       | 65    |

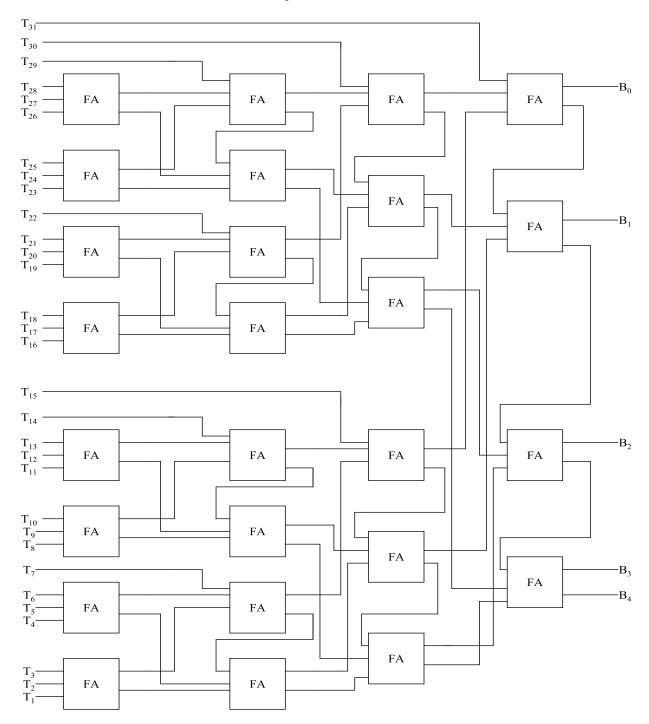

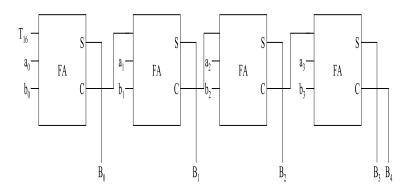

| Fig .4.5 Final stage implementation using full adders                                                                        | 69    |

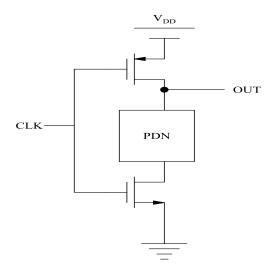

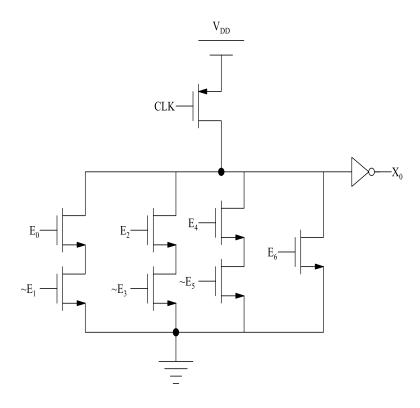

| Fig. 4.6 Basic structure of dynamic logic                                                                                    | 70    |

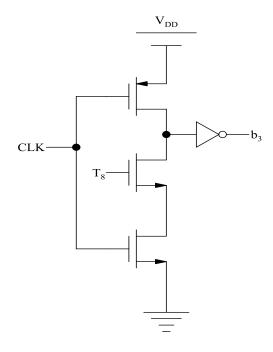

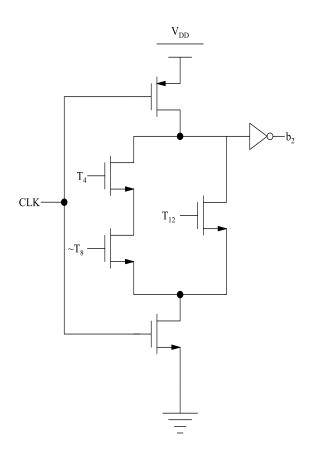

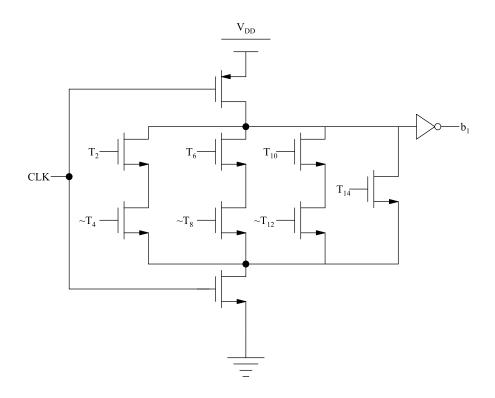

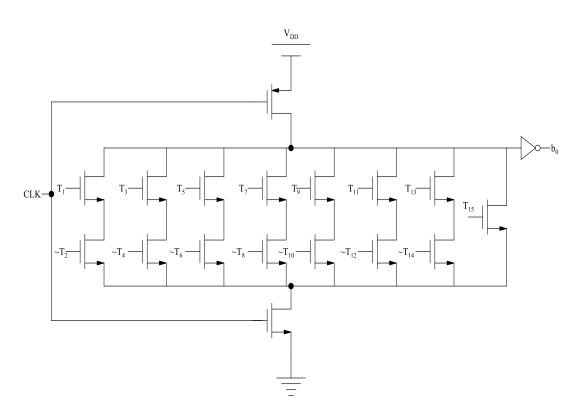

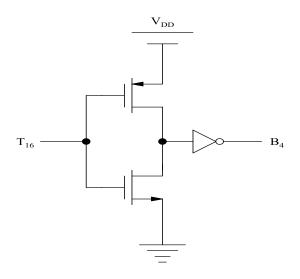

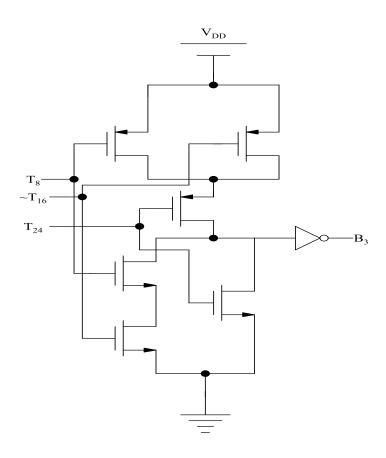

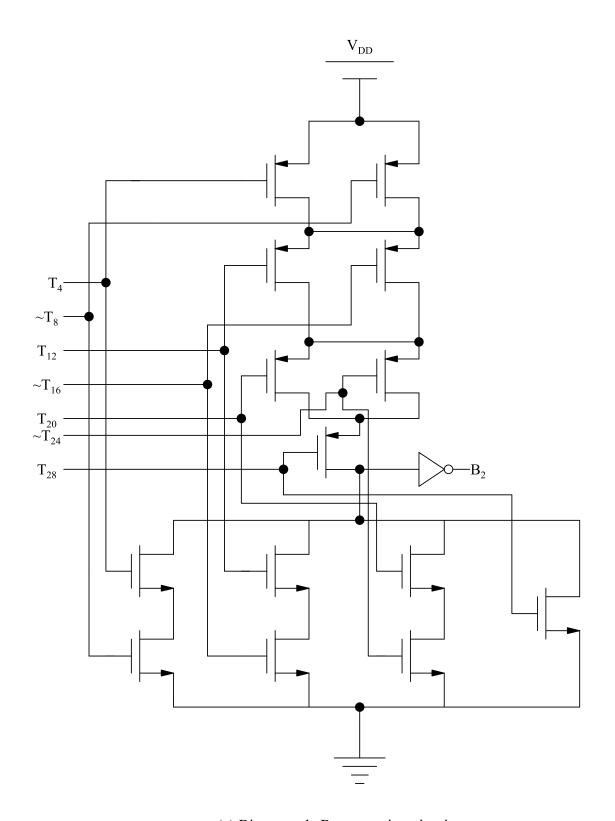

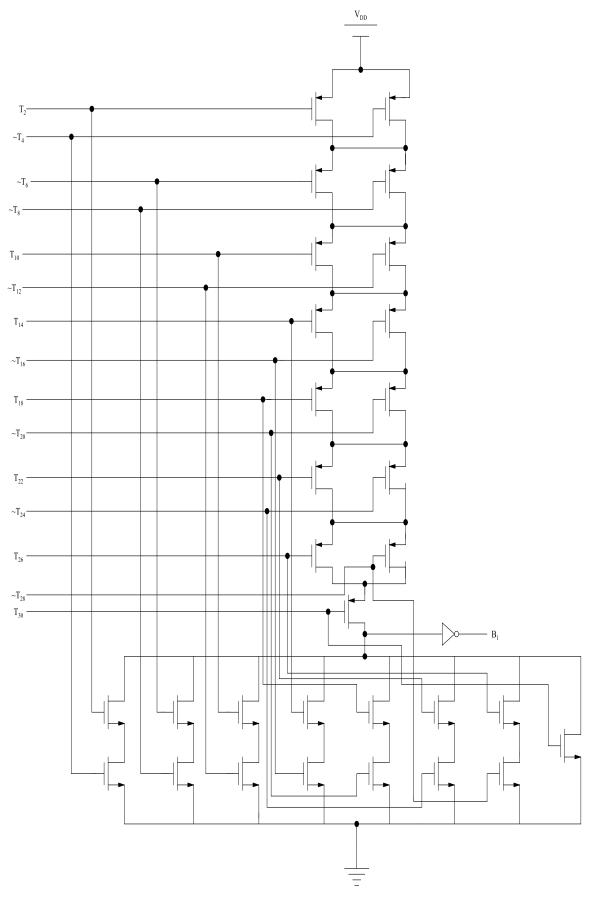

| Fig. 4.7 Schematic implementation of b <sub>3</sub> , b <sub>2</sub> , b <sub>1</sub> and b <sub>0</sub> using dynamic logic | 72    |

| Fig. 4.8 Schematic implementations of sum and carry in a full adder using dynamic logic                                      | 73    |

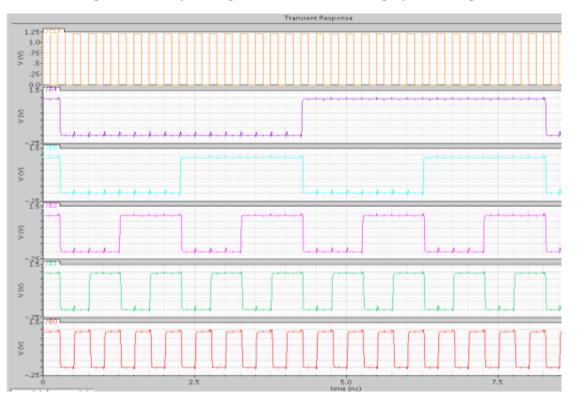

| Fig. 4.9 Proposed encoder simulation                                                                                         | 74    |

| Fig. 4.10 Regular multiplexer based encoder                                                                                  | 76    |

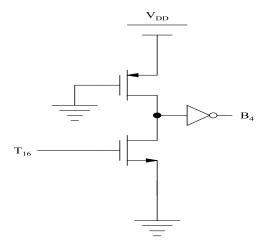

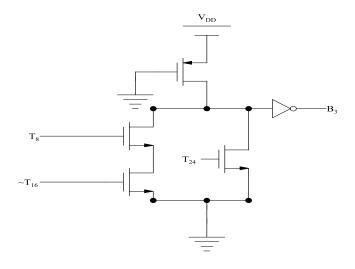

| Fig. 4.11 Schematic implementations of B <sub>4</sub> , B <sub>3</sub> , B <sub>2</sub> , B <sub>1</sub> , B <sub>0</sub>    | 80    |

| Fig. 4.12 Schematic implementation of multiplexer using dynamic logic                                                        | 80    |

| Fig. 4.13 Proposed encoder Simulation                                                                                        | 81    |

| Fig. 4.14 Final stage implementation using multiplexers                                                                      | 82    |

| Fig. 4.15 Proposed encoder simulation                                                                                        | 83    |

| Fig .4.16 Proposed multiplexer based encoder                                                                                 | 85    |

| Fig. 4.17 Schematic of two input AND gate using pseudo dynamic CMOS logic                                                    | 87    |

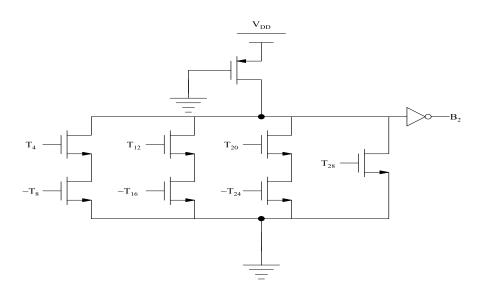

| Fig. 4.18 Schematic implementations of $X_2$ , $X_1$ and $X_0$ using pseudo dynamic CMOS log                                 | ic 89 |

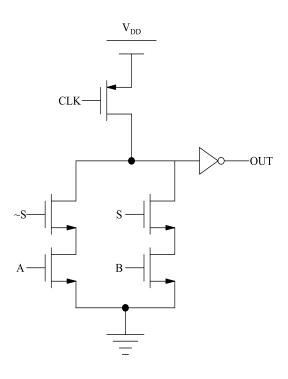

| Fig. 4.19 Multiplexer implementation using pseudo dynamic CMOS logic                                                         | 89    |

| Fig. 4.20 Bubble error correction circuit                                                                                    | 90    |

| Fig. 4.21 Proposed encoder simulation.                                                                                       | 91    |

| Fig. 4.22 Binary code generation circuit using static CMOS logic                                                             | 98    |

| Fig. 4.23 Simulation of binary encode using static CMOS                                                                      | 98    |

| Fig. 4.24 Binary code generation circuit using dynamic logic                                                                 | 101   |

| Fig. 4.25 Simulation of binary encoder using dynamic logic                                                                   | 101   |

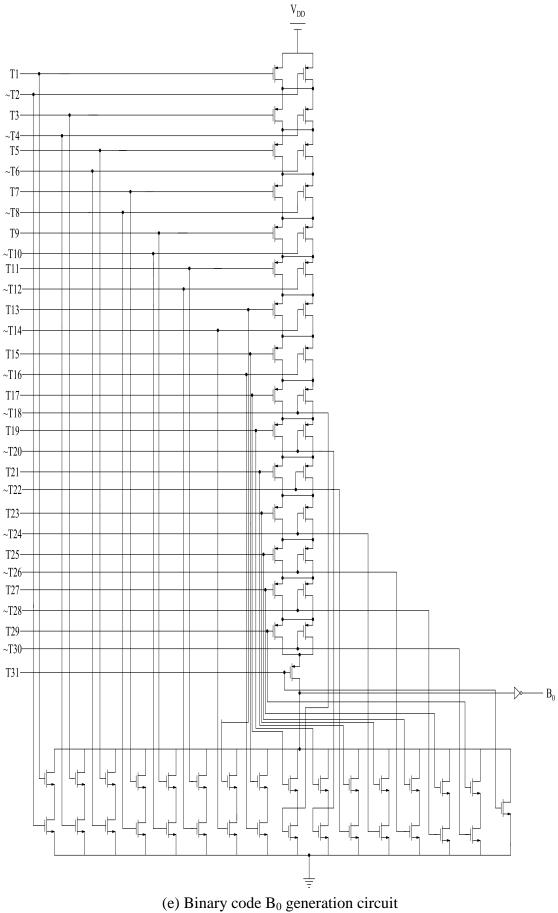

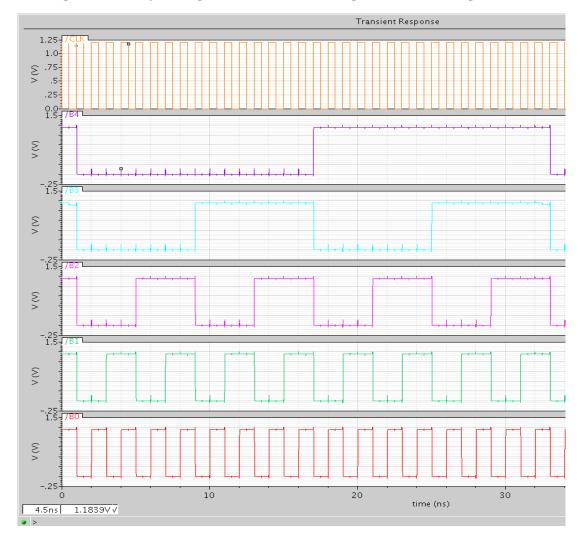

| Fig. 4.26 Binary code B <sub>0</sub> generation circuit using pseudo NMOS logic                                              | 104   |

| Fig. 4.27 Simulation of binary encode using pseudo NMOS                         | 104 |

|---------------------------------------------------------------------------------|-----|

| Fig. 4.28 Binary code generation circuit using pseudo dynamic CMOS logic        | 107 |

| Fig. 4.29 Simulation of binary encoder using pseudo dynamic CMOS logic          | 107 |

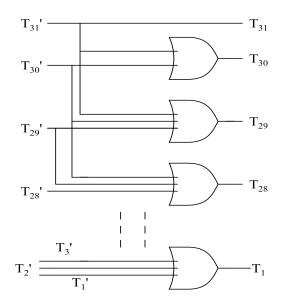

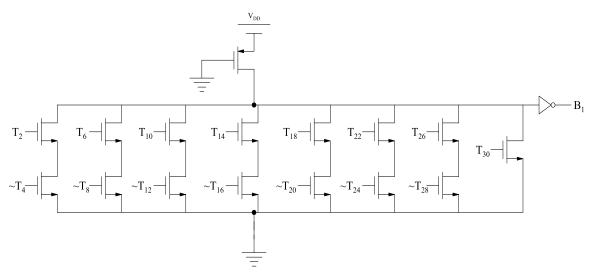

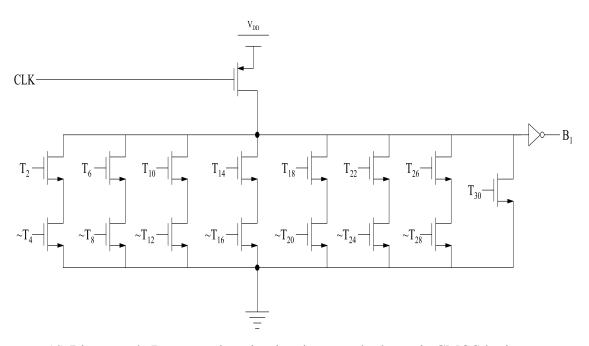

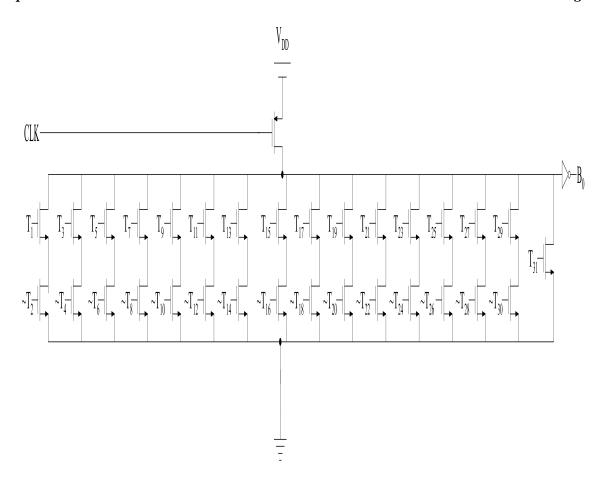

| Fig. 4.30 Gray code generation circuit using pseudo dynamic logic               | 114 |

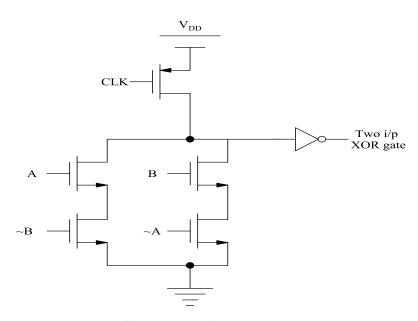

| Fig. 4.31Schematic of two input XOR gate                                        | 114 |

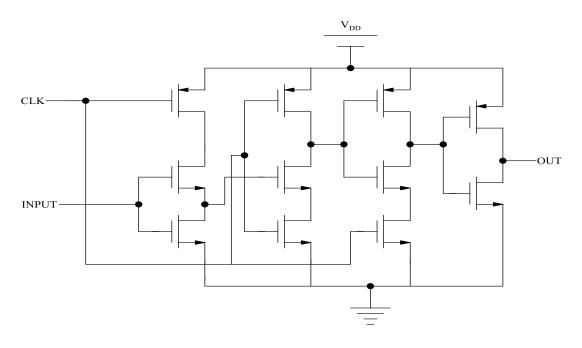

| Fig. 4.32 Schematic of D flip-flop                                              | 115 |

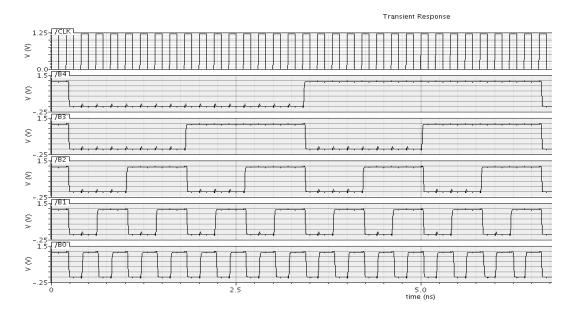

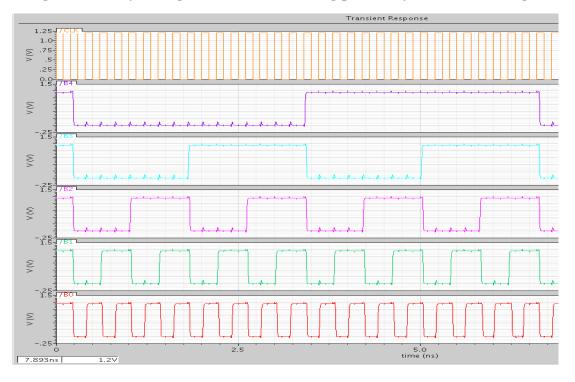

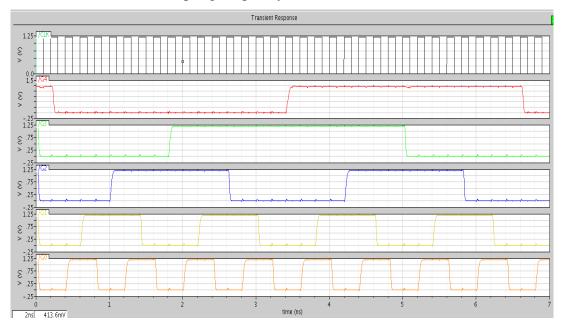

| Fig. 4.33 Simulation of gray code encoder                                       | 115 |

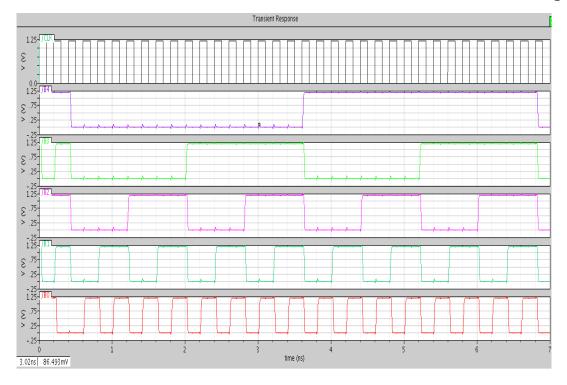

| Fig .4.34 Simulation of binary code encoder                                     | 116 |

| Fig. 4.35 Layout of the proposed encoder                                        | 117 |

| Fig. 4.36 Post layout simulation of the proposed encoder                        | 118 |

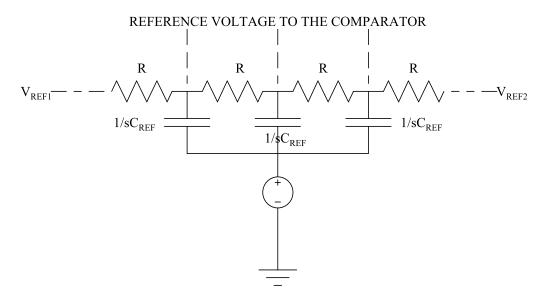

| Fig. 5. 1 Resistor ladder                                                       | 122 |

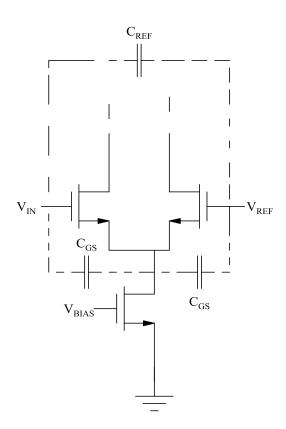

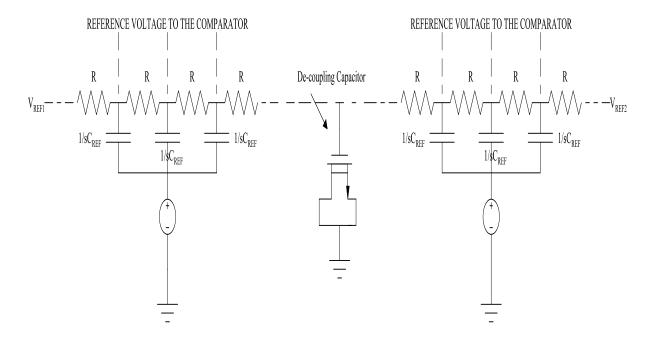

| Fig. 5.2 Input feed through effect in the comparator                            | 124 |

| Fig. 5.3 Small signal model of the input feed through effect of resistor ladder | 125 |

| Fig. 5.4 De-coupling the resistor ladder                                        | 126 |

| Fig. 5. 5 Block diagram representation of five bit flash ADC                    | 127 |

| Fig. 5.6 Layout of complete five bit flash ADC.                                 | 128 |

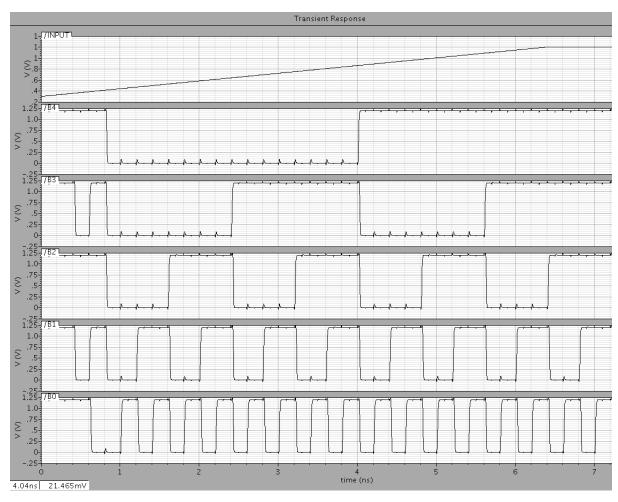

| Fig. 5.7 Post layout simulation of proposed five bit flash ADC                  | 129 |

| Fig. 5.8 DNL plot of proposed flash ADC                                         | 130 |

| Fig. 5.9 INL plot of proposed flash ADC                                         | 131 |

| Fig. 5.10 Frequency spectrum of proposed ADC                                    | 132 |

| Fig. 5.11 Curve between power dissipation and sampling frequency                | 133 |

| Fig. 5.12 Curve between ENOB and Sampling frequency                             | 134 |

| Fig. 5.13 Curve between ENOB and input signal frequency                         | 134 |

| Fig. 5.14 Curve between SFDR and sampling (clock) frequency                     | 135 |

| Fig. 5.15 Curve between SFDR and input signal frequency                         | 135 |

| Fig. 6. 1 Reconfigurable block architecture                                     | 141 |

| Fig. 6.2 Implementation of 2X1 multiplexer using pseudo dynamic logic           | 143 |

| Fig. 6.3 4X1 multiplexer using 2X1 multiplexers                                 | 143 |

| Fig. 6.4 8X1 multiplexer using 4X1 multiplexer and a 2X1 multiplexer            | 144 |

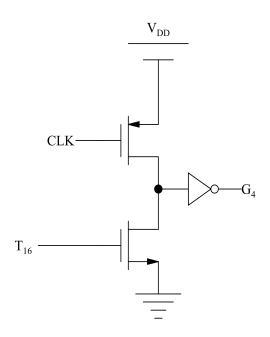

| Fig. 6.5 Implementation of B <sub>1</sub> using pseudo dynamic logic            | 144 |

| Fig. 6.6 Implementation of B <sub>0</sub> using pseudo dynamic logic            | 145 |

| Fig. 6.7 Time shifted skewed clocking mechanism in Reconfigurable ADC           | 145 |

| Fig. 6.8 Layout of the reconfigurable flash ADC                                 | 146 |

| Fig. 6. 9 DRC error window                                                      | 147 |

| Fig. 6.10 LVS run window                                           | 147 |

|--------------------------------------------------------------------|-----|

| Fig. 6.11 Post layout simulation of reconfigurable flash ADC       | 148 |

| Fig. 6.12 DNL plot of reconfigurable ADC                           | 149 |

| Fig. 6.13 INL plot of reconfigurable ADC                           | 149 |

| Fig. 6.14 Frequency spectrum of reconfigurable ADC                 | 150 |

| Fig. 6.15 Analog IC design flow                                    | 156 |

| Fig. 6.16 Final chip tape out of proposed reconfigurable flash ADC | 158 |

# LIST OF TABLES

| Table 2.1 Comparison of the Bluetooth, UWB, Zig-Bee and Wi-Fi Protocols    | 11  |

|----------------------------------------------------------------------------|-----|

| Table 2.2 Summary of MB-OFDM UWB receiver requirements                     | 13  |

| Table 2.3 Summary of DS-UWB receiver requirements                          | 14  |

| Table 2.4 Comparison of different ADC architectures                        | 22  |

| Table 2.5 Summary of the proposed ADC specification                        | 30  |

| Table 3.1 Corner specifications                                            | 55  |

| Table 3.2 Pre-layout simulation with process corner simulations            | 55  |

| Table 3.3 Post layout corner simulation results of the comparator          | 57  |

| Table 3.4 Comparison with previous architectures                           | 58  |

| Table 4.1 Five bit binary encoder truth table                              | 68  |

| Table 4.2 Summary and comparison with other encoders                       | 75  |

| Table 4.3 Comparison with other encoders                                   | 81  |

| Table 4.4 Summary and comparison with other encoders                       | 84  |

| Table 4.5 Truth table of 7:3 encoder                                       | 86  |

| Table 4.6 Comparison with other encoders                                   | 92  |

| Table 4.7 Comparison of different logic styles                             | 108 |

| Table 4.8 Transistor Sizes                                                 | 109 |

| Table 4.9 Gray code encoder truth table                                    | 110 |

| Table 4.10 Corner specifications                                           | 116 |

| Table 4.11 Pre-layout simulation with process corner simulations           | 117 |

| Table 4.12 Post-layout simulation with process corner simulations          | 118 |

| Table 4.13 Comaparison with different encoders                             | 119 |

| Table 5.1 Reference voltage generated by resistor ladder                   | 123 |

| Table 5.2 Summary of the performance of the proposed flash ADC             | 136 |

| Table 5.3 Comparison with other works                                      | 137 |

| Table 6.1 Design target of proposed ADC architecture                       | 140 |

| Table 6.2 3:2 Encoder truth table                                          | 142 |

| Table 6.3 Process corners of reconfigurable five bit flash ADC             | 151 |

| Table 6. 4 Corner analysis of the proposed reconfigurable flash ADC        | 151 |

| Table 6. 5 Performance summary of reconfigurable five bit flash ADC        | 153 |

| Table 6. 6 Comparison table of reconfigurable ADC with other similar works | 154 |

# **ABBREVIATION**

UWB - Ultra Wide Band

SAR - Successive Approximation Register

ADC - Analog to Digital Converter

LNA - Low Noise Amplifier

BPF - Band Pass Filter

CMOS - Complementary Metal Oxide Semiconductor

ROM - Read Only Memory

SS - Spread Spectrum

RF - Radio Frequency

WPAN - Wireless Personal Area network

FCC - Federal Communication Commission

DS-UWB - Direct Sequence UWB

OFDM - Orthogonal Frequency Division Multiplexing

MB-OFDM - Multiband OFDM

QPSK - Quadrature Phase Shift Keying

BPSK - Binary Phase Shift Keying

PPM - Pulse Position Modulation

CDMA - Code Division Multiple Access

DSP - Digital Signal Processing/Processor

DAC - Digital to Analog Converter

CCD - Charge Coupled Device

HDTV - High Definition Television

SNR - Signal to Noise Ratio

MSB - Most Significant Bit

SQNR - Signal to Quantization Ratio

SNDR - Signal to Noise Distortion Ratio

ENOB - Effective Number of Bits

SFDR - Spurious Free Dynamic Range

Op-Amp - Operational Amplifier

LSB - Least Significant Bit

LVS - Layout Vs Schematic

DRC - Design Rule Check

MOSFET - Metal Oxide Semiconductor Field Effect Transistor

NMOS - N-Type Metal Oxide Semiconductor

PMOS - P-Type Metal Oxide Semiconductor

RCX - Resistance Capacitance Extraction

INL - Integral Non Linearity

DNL - Differential Non Linearity

FoM - Figure of Merit

GND - Ground

LAN - Local Area Network

FFT - Fast Fourier Transform

DSSS - Direct Sequence Spread Spectrum

FHSS - Frequency Hopping Spread Spectrum

CCK - Complementary Code Keying

# CHAPTER 1

## **OVERVIEW**

#### 1.1 Introduction to research

The advancement in wireless technology takes us in to a world without wires. Most of the wireless communication systems use digital signal processing to transmit as well as receive the information. The real world signals are analog. Due to the processing complexity of the analog signal, it is converted to digital form so that processing is easier. The development in the digital signal processor field is rapid due to the advancement in the integrated circuit technology over the last decade. Moreover, advantage of digital processing is that it is more immune to noise. So analog-to-digital converter plays an interface role in between analog signal and digital signal processing system. The continuous speed enhancement of the wireless communication systems have bring out huge demands in speed and power specifications of high speed low resolution analog-to-digital converters.

Even though wired technology is primary mode of communication, the quality and efficiency of the wireless technology allows us to apply to biomedical applications, in home services and even to radar applications. These applications rely heavily on wireless technology to send and receive information at high speed with great accuracy. The restricted availability of commercially available communication frequency spectrum limits the application range. Commercial radio frequency bands use bandwidths of the order of 100 MHz to few GHz [1]. This leads wireless technology may be applied to only narrow band applications.

Up to 2002, the frequency spectrum from 3.1 GHz to 10.6 GHz is used for military applications in United States. However in 2002, the federal communication commission (FCC) deregulated the use of this frequency spectrum and made it available for commercial applications. Subsequently other countries also deregulate this frequency spectrum for commercial purposes. This range of frequencies is widely known as ultra wideband spectrum (UWB). Due to this, large frequency band distributes over 3.1 GHz to 10.6 GHz can be used for commercial applications.

#### 1.2 Motivation

Conventional radio transmissions transmit data by changing power level, phase or frequency of a sinusoidal signal. But UWB communication transmits each slice of information over a

wide frequency band [2, 3]. The pulses which are using for the UWB communications are very short. Due to high data transmission rate and resistance to multipath fading, UWB technology becomes more and more popular.

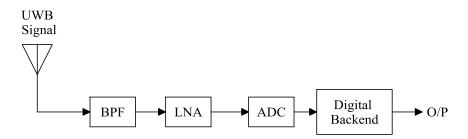

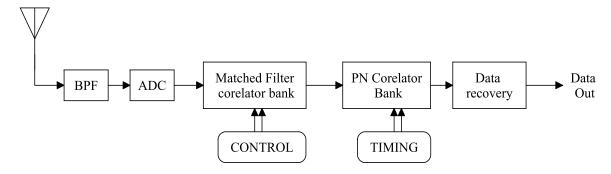

Fig. 1.1 shows the typical block diagram of UWB receiver [14]. It consists of mainly three parts.

- Radio frequency front end

- ADC

- Digital backend

ADC is the core of any UWB receiver. Since UWB signals are widely distributes over a large frequency range [4], the selection of an ADC is crucial in the design of UWB receiver. The types of ADCs used may be varied in accordance with different applications. It is determined mainly based on the sampling frequency, power consumption and resolution. For example, flash ADCs can be utilized in low resolution high speed applications. Due to its parallel operation, all the conversions are done in a single clock cycle. But a successive approximation register (SAR) ADC uses in high resolution low speed application. So the selection of an ADC is determined by the application where it is used. High sampling frequency ADCs are widely used for UWB applications.

Fig. 1.1 Block diagram of UWB receiver

The prime focus of the research is to design a high speed medium power ADC used in UWB receiver architecture [5]. This UWB receiver mainly targets applications such as in home wireless connectivity and biomedical devices.

#### 1.3 Research aims and objectives

The prime focus of this research is to develop a high speed flash ADC used in UWB applications of in-home wireless systems and biomedical devices. The main aims of this research are

To inspect UWB receiver architecture and identify its requirement and specification of an ADC for the application.

- Design and implement a high speed pseudo dynamic logic based CMOS comparator for the specific application.

- Develop and implement a high speed pseudo dynamic logic based encoder which converts thermometer code to binary code in flash ADC.

- Implement a high speed ADC for the application by combining resistor ladder, comparators and encoder.

- Analyse and compare the results with other types of similar ADCs.

- Design and implement a reconfigurable flash ADC used for similar applications with lower frequency of operation. Characteristics of the proposed ADC is figured out and explained. Comparisons have been made with other similar architectures.

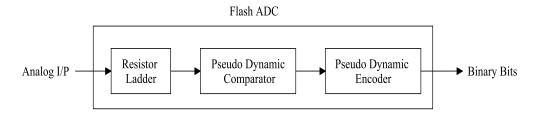

The proposed flash ADC block diagram is shown in Fig. 1.2.

Fig. 1.2 Block diagram of proposed flash ADC

#### 1.4 Design methodology

The design methodology followed in the research is shown below

- To inspect UWB receiver architecture and identify its requirement and specification of an ADC for the application.

- A wide range study of two different UWB receiver architectures is carried out. Specification of flash ADC used in the receiver architecture is also suggested.

- Design and implement a high speed pseudo dynamic logic based CMOS comparator. Since comparators play a crucial role in the design of a flash ADC, this research includes detailed study of different architectures. To enhance the speed of comparator, pseudo dynamic logic based comparator is proposed and analysed.

- Develop and implement a high speed encoder which converts thermometer code to binary code in flash ADC.

- There are different methods with which the implementation of thermometer code to binary code can be done. Wallace tree encoder, multiplexer based encoder, logic

based encoder, fat tree encoder and ROM based encoder are some of the different methods. A detailed study of different encoders are carried out and proposed the most apt pseudo dynamic logic based encoder for the conversion of thermometer to binary code.

- Implementation of a high speed ADC used for the application.

Integrating resistor ladder, comparators and thermometer to binary code encoder, flash ADC is designed. All the parameters of ADCs are tested and trade off between speed and power is made.

- Analyze and compare the results with other types of ADCs

A detailed analysis of the implementation is done and compared the proposed ADC with other types of ADCs used for the specific application. The complete ADC is designed and implemented using CMOS 90 nm technology using CADENCE environment.

- Implementation of a reconfigurable five bit flash ADC

The output bits of a reconfigurable flash ADC is not constant. It can be varied according to the operating conditions. In this design, MSB of the flash ADC is found out first and with the help of MSB bit, flash ADC's remaining bits are calculated. Finally it is compared with other similar flash ADCs and performance is evaluated. The chip tape out of the proposed reconfigurable flash ADC has made in the last stage.

#### 1.5 Thesis Organization

The thesis is structured into seven chapters. Following to the overview, chapter two demonstrates a literature survey of UWB communication standards. The different standards are described in detail with their advantages and disadvantages and finally conclude with the selection of the standard used for this application. It also describes about different architectures of ADC such as flash, pipeline, successive approximation register, sigma delta and dual slope. Different ADCs are used for different applications. Sampling frequency, power dissipation and resolution of ADCs are determined on the basis of specific application. Five bit flash ADC is taken as the appropriate one for the specific application. Chapter three illustrates different comparator architectures and proposes a high speed pseudo dynamic logic based comparator used for the application and analyses its properties. Chapter four portrays different methods of converting thermometer to binary code. The methods are presented in detail with advantages and disadvantages and finally propose a pseudo dynamic logic based

encoder used for the application. Chapter five represents the implementation of the complete flash ADC by integrating the blocks such as resistor ladder, comparators and thermometer to binary code encoder. It also discusses about the parameters of the specific ADC, layout and post layout simulation of the total module. The chapter also compares the implemented ADC with other ADCs with the same resolution and describes about the advantages and disadvantages of the implementation. Chapter six describes about implementation of a reconfigurable flash ADC. The chapter compares the results of the proposed ADC with other ADCs and finally chip tape out has been made for the reconfigurable ADC. Chapter seven concludes the total work and briefly discusses about the future work.

#### **1.6** Thesis Contributions

- A five bit flash ADC with a sampling rate of 5GS/s is designed and tested the functionality.

- It consists of a high speed preamplifier based pseudo dynamic latch comparator. In order to reduce the overdrive recovery time, a pas transistor is added to the preamplifier circuit.

- An improved multiplexer based implementation is done in order to convert thermometer code to binary code. To meet the sampling rate of 5GS/s, the implementation is done using pseudo dynamic logic.

- A bubble tolerant thermometer code to binary code converter is implemented by using an intermediate step of adding a gray code encoding before producing the desired binary code.

- An improved reconfigurable five bit flash ADC is also realized with the help of high speed comparators, multiplexers and 3:2 encoders.

#### 1.7 Conclusion

In reality, digital signal has the benefits of effortless processing, testing and storage. So we convert the analog signal to the digital signal for processing. The way to implement this is with the help of analog-to-digital converter as the interface. Researchers are exploring new design techniques for an ADC with the aim of drop off power consumption and to enhance the speed of operation. In all the other types of ADCs, flash ADC design turns out to be more significant as a result of the reality that it frequently plays a crucial role in other types of ADCs such as multi bit sigma delta ADC and pipelined ADC. Based on sampling frequency, power dissipation and resolution, the research proposes a high speed pseudo dynamic based five bit flash ADC for UWB receiver that uses in biomedical as well as in home wireless

applications. In the similar manner, a reconfigurable five bit flash ADC is also designed and implemented for similar application with lower sampling frequency of operation. The proposed ADC is having better performance characteristics in comparison with previously designed flash ADC, when it is operating in a lower frequency of operation. Chip tape out is made for the reconfigurable flash ADC in the final stage of implementation.

## CHAPTER 2

# Introduction to UWB and Selection of ADC architecture for UWB applications

#### 2.1 Introduction to UWB

Ultra Wideband (UWB) is a means of communication that's historically as old as Morse code but is new in its potential for far reaching applications. It is a communication scheme that primarily uses the frequency spectrum from 3.1 GHz to 10.6 GHz for short range, low power and high speed-high bandwidth communications. Communication is based on the use of sharp pulses with coded data represented by each of these pulses hovering about a centre axis frequency at very low emission levels minus the use of a high frequency carrier. Each pulse is miniscule in its time frame such that its energy is spread over the entire frequency range.

In the 1960s, UWB was primarily harnessed for its potential use in military applications. In 2002, when the FCC in USA deregulated its use, it brought with it a host of issues and challenges. A UWB signal has a bandwidth of at least 500 MHz or a fractional bandwidth of 25 percent of its centre frequency. Ultra Wideband brings with it unique properties of non-interference with other systems, immunity to multi-path fading, frequency and bandwidth adaptive, simple system architecture, low cost digital solutions and being extremely difficult to detect. UWB signal spectrum occupies a wide frequency range and sits at a very low power level (-41.3 dBm/MHz) [6] as compared to other communication systems. This is because the FCC has placed a limit on the amount of power that can be used by UWB device to minimise interference to other frequency devices. The limit means that only very low power can be used for transmission and reception of UWB signals thereby effectively restricting the use of UWB to indoor, short-range communications for high data rates or very low data rates at substantial distances.

The advantages of UWB [7] make it more useful for consumer communications applications. Especially, UWB systems have the following advantages.

- Improved channel capacity

- Ability to share the frequency spectrum with narrowband signals

- Less sensitive to multipath effects

- High immunity to detection and interception

- Extremely high data rates possible

- Simple transceiver structure

- Fine time resolution

#### 2.2 Applications of UWB

Applications of UWB systems include military applications, biomedical health monitoring systems, In-home wireless connectivity and collision avoidance systems. This research mainly focuses on UWB applications of in-home wireless connectivity and biomedical systems.

#### 2.2.1 Military Applications

Potential military applications include

- Inter vehicle short range limited mobility wireless network

- Intra-vehicle wireless network

- Obstacle detection

- Range finding and self location

- Terrain mapping

In manned and unmanned military vehicles, intra vehicle wireless network is highly used because it abolishes the problems related with cable weight and cost. In order to operate different vehicle subsystems away from the vehicle, inter vehicle short range wireless network is used. Range determination is crucial for tracking and recognizing of both potential targets and friendly elements. Self location is highly used in autonomous applications. Object sensing and identification is used in unmanned systems which needs the capability to sense and recognize the objects in a variety of surroundings. Terrain mapping is used in specified military applications which involve sensing accuracy and plotting of different features of terrain from moderately small ranges. ). It is used to sense, evade or deactivate hidden items (explosives, mines) and unpredicted objects (debris, rubbles). UWB is a superior option for terrain mapping due to its resistance to hostile jamming, hostile detection, and effective penetration ability through different materials, radio frequency interference, and good delay resolution capability.

#### 2.2.2 Biomedical health monitoring system

Low power, non-invasiveness, biocompatibility, non-contact remote operation biological easiness, environmental friendliness and the accurate detection of UWB makes it appropriate for medical monitoring application [8]. Highly strong pulses are used in UWB technology.

UWB radar helps in supervising and evaluating patient's movements in the medical field. The usage of UWB in observing the patient in emergency unit could stay away from the using of too many wires near the patient. The application can be used to observe the patients whether he is moving in the specified time.

#### 2.2.3 In-home wireless connectivity

Home network application is a critical feature to create pervasive home network environment. Within the home environment, UWB technology can possibly be suitable nomine to enable different applications. The wireless connectivity of different home electronic systems gets rid of the wiring mess in living room. In-home wireless connectivity permits a user sitting in a room at home to examine and be aware of the situation of the TV, desktop and security system there inside the house.

#### 2.2.4 Collision avoidance system

UWB technology is highly used in detecting the vehicle speed and informs the driver about the accident that can occur [9]. The idea of the intelligent car consists of providing the vehicle with best possible number of sensors with the intention of monitor the environment which encloses it to make sure an automatic guidance control of the vehicle and to be in touch with the external medium. The originality of this radar is its capability to sense easily various barriers and to provide their signatures. High power efficiency, fine range resolution, low probability of detection and low probability of interference make UWB outstanding candidate technology in collision avoidance applications.

#### 2.3 Characterization of UWB

Ultra-Wideband (UWB) offers an attractive new technology for small range high speed communications in the range from 3.1 GHz to 10.6 GHz. It maintains a bit rate larger than 100 Mbps inside a 10-meter radius for wireless personal area communications [2].

Since the communications channel capacity in a non fading surroundings is expressed as

$$C = B * \log_2(1 + S/N)$$

Where

C = channel capacity (bit/s)

S = signal power (watts)

N = noise power (watts)

B = channel bandwidth 'BW' (Hz)

In relation to above equation, the capacity can be enlarged by either raising channel bandwidth or signal to noise ratio. It is understandable that the capacity can be enlarged more

by raising the bandwidth rather than signal to noise ratio. UWB systems could also experience interference from different wireless technologies that are present in the neighbourhood of operation, but the problem can be diminished by using adaptive frequency bands selection in multi band UWB systems.

Ultra wideband technology has been approved for short range communication, except with constraints on the frequencies over which the transmission can spread and the power limits. This permits the ultra wideband transmissions to communicate effectively, but without influencing active narrowband transmissions. To attain these prerequisites, ultra wideband transmissions can officially work in the range 3.1 GHz up to 10.6 GHz at a transmit power of -41 dBm/MHz. In addition to the transmissions have to reside in a bandwidth of at least 500 MHz [10] and having a fractional bandwidth of not less than 25 % of the centre frequency. A typical representation of the statement can be written as

$$f_B = \frac{2(f_H - f_L)}{f_H + f_L} \ge 25 \%$$

Where  $f_B$  is the fractional bandwidth of the UWB signal,

$f_{L}$  and  $f_{H}$  are the lower and upper bounds of the frequency spread.

Subsequently, UWB offers remarkable channel capacity at small range which limits interference.

#### 2.4 Comparison with other communication schemes

The main challenge to UWB in terms of competing wireless technologies for in-home wireless connectivity and Bio-Medical applications are Wi-Fi LAN, Bluetooth and Zig-Bee. Taking a closer look at these specific communications standards;

#### 2.4.1 WiFi (802.11 x)

Wireless LAN as a means of network connectivity technology has been around for a number of years. It has progressed effectively enough to replace cable based Ethernet in providing internet and data connectivity. However it has struggled to provide the same amount of data rate as compared to cable Ethernet until the emergence of the 802.11n standard. Cable based Ethernet provides 100 Mega bits per second (Mbps) connection while Gigabit Ethernet provides more, whereas Wi-Fi is restricted to 11 Mbps for 802.11b, 22 Mbps for 802.11a, 54 Mbps for 802.11g and 300 Mbps maximum for 802.11n. These rates are still relatively low compared to the potential of minimum 500 Mbps data rate acquirable through UWB communication [29, 30].

#### 2.4.2 Zig-Bee and Bluetooth

Zig-Bee and Bluetooth are recent communication standards with communication ranges of 20 feet for Zig-Bee and 30 feet for Bluetooth. They are serious contenders for short range wireless communications. The comparison in terms of cost leads Zig-Bee to march ahead of Bluetooth, however Bluetooth has a far superior and established data standard. These two standards are typically applicable to non-bandwidth intensive uses as the comparable data rates do not match even close to Wi-Fi LAN. Zig-Bee has a maximum efficient data rate of around 500 Kilo bits per second (Kbps) and Bluetooth of about 1 Mbps [29, 30]. Table 2.1 provides the comparison between Bluetooth, Zig-Bee, UWB and Wi-Fi.

Table 2.1 Comparison of the Bluetooth, UWB, Zig-Bee and Wi-Fi Protocols

| Standard                     | Bluetooth   | Zig-Bee                 | Wi-Fi             | UWB                 |

|------------------------------|-------------|-------------------------|-------------------|---------------------|

| IEEE Spec                    | 802.15.1    | 802.15.4                | 802.11a/b/g       | 802.15.3a           |

| Frequency Band               | 2.4 GHz     | 869/915 MHz;<br>2.4 GHz | 2.4 GHz; 5 GHz    | 3.1-10.6 GHz        |

| Max Signal Rate              | 1Mb/s       | 250Kb/s                 | 54Mb/s            | 500Mb/s             |

| Nominal Range                | 10 m        | 10-100m                 | 100m              | 10 m                |

| Normal<br>Transmission Power | 0-10<br>dBm | -25 to 0 dBm            | 15-20 dBm         | -41.3 dBm/MH        |

| Channel Bandwidth            | 1 MHz       | 0.3/0.6 MHz;<br>2MHz    | 22 MHz            | 500 MHz- 7.5<br>GHz |

| Number of RF channels        | 79          | 1/10,16                 | 14 (2.4 GHz)      | 1-15                |

| Spreading                    | FHSS        | DSSS                    | DSSS,<br>CCK,OFDM | DS-UWB,<br>MB-OFDM  |

In brief, Zig-Bee and Bluetooth are appropriate for low data rate applications with restricted battery power (such as battery operated sensor networks and mobile devices) caused by their low power consumption steering to an extensive lifetime. Alternatively, for high data rate operations (such as wireless in home connectivity, audio/video inspection systems, military application and bio medical application) Wi-Fi and UWB would be superior solutions because of their low standardized energy consumption. The data rate of Wi-Fi is still low compared to minimum 500 Mbps which is attainable by UWB communication.

#### 2.5 Ultra Wideband Standards

The two different technology standards used in UWB are carrier free direct sequence ultra wideband technology (DS-UWB) and multiband orthogonal frequency division multiplexing ultra wideband technology (MB-OFDM) [15]. The two different standards are having different signalling scheme. This leads to different transceiver configuration that determines the type of ADC (architecture, resolution) which uses in the transceiver [11]. Since the main scope of the work is dealing with ADC, the transmitter section in neglected and more importance is given to receiver section [12].

# 2.5.1 Multi Band Orthogonal Frequency Division Multiplexing Ultra Wide Band Technology (MB-OFDM)

The MB-OFDM group was initially started by Intel and later on grew to include a number of other industry partners including Samsung, Panasonic, Texas Instruments and others. The industry groups were commonly referred to as the Multi-Band OFDM UWB Alliance (MBOA). The MBOA approach utilised the 7.5 GHz of frequency spectrum from 3.1 GHz to 10.6 GHz, by splitting them into 15 individual non-overlapping frequency bands, each occupying a little over 500 MHz of frequency spectrum.

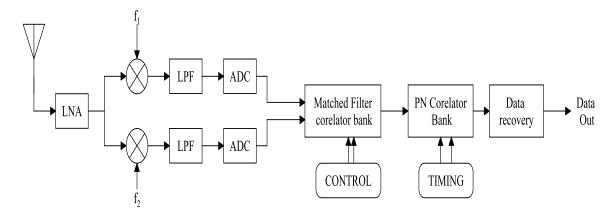

MB-OFDM UWB receiver (Fig. 2.1) consists of low noise amplifier, low pass filter, ADC, matched filter bank, PN co-relator bank and data recovery circuits. The system is based on OFDM or Quadrature Phase Shift Keying technique (QPSK). The ADC requires high resolution with low sampling rates and low bandwidth. So generally time interleaved ADCs are used in this receiver. Each converter feeds into matched filter circuit and the output is given to PN co-relator bank for correcting the timing. The output of the PN co-relator bank is given to data recovery circuit to get the final data. As the date rate increases, the number of ADC used in the operation also increases. This increases the complexity of the receiver. Summary of MB-OFDM UWB receiver requirements are given in Table 2.2.

Fig. 2. 1 MB-OFDM UWB receiver topology

Bandwidth 500-528 MHz

Bands 13-15 Bands

Signalling Scheme OFDM( N-Point), QPSK

Pulse Interval More than 100 ns

N time interleaved sigma delta

High resolution (5-8 bits)

Low sampling rates

Table 2.2 Summary of MB-OFDM UWB receiver requirements

#### 2.5.2 Direct Sequence UWB standard

The DS-UWB group was consisted of Xtreme Spectrum/Motorola and Freescale Semiconductor who were the leading proponents for this standard. The group grew to include other alliances such as Philips and Samsung.

UWB is an innovative wireless technology which permits data to be transmitted at a speed greater than 100 Mbps. Gaussian pulses with low power are generally used in this standard. The transmissions widen out over a large bandwidth normally in the range of 100 MHz to even some GHz. Each of the DS-UWB pulses is particularly small duration which is normally in the range of 10 to 1000 picoseconds. Because of the short duration pulse, multipath effects can be disregarded which provides a large amount of flexibility in the transmission when the signal path is surrounded by the building.

DS-UWB utilizes the frequency spectrum of 7.5 GHz from 3.1 GHz to 10.6 GHz for operation. It is done by splitting the band into two non overlapping bands (Lower band and Upper band). The lower band ranges from 3.1 to 4.7 GHz and the upper band ranges from 5.8 to 10.6 GHz. The band from 4.8 to 5.7 is kept free for wireless LAN to eliminate any chances of narrow band interference.

The well accepted modulation methods for DS-UWB are Pulse Position Modulation (PPM) and Binary Phase Shift Keying (BPSK). Modulation efficiency and spectral performance are the two important parameters for the modulation schemes which are remarkable for these two modulation schemes. PPM encodes the data by altering the time interval and hence the pulse

position. BPSK reverses the pulse phase (180 degree) to indicate the transmitted data. As the pulses contain an initial upward or downward voltage, it is effortless to change the phase of the pulse by 180 degree. In addition to this, the transmission can be done with the help of direct sequence codes. The received signal should be compared with the exact direct sequence code which is to be demodulated. The advantage of this technique is only the specified receiver can demodulate it. Normally all the transmission methods uses carrier based approach. But UWB technology presents the opportunity of very large data rate transmissions with very low power.

Fig. 2.2 shows the block diagram description of a DS-UWB receiver [13, 15]. In comparison with MB-OFDM UWB technology, DS-UWB uses a single analog-to-digital converter with high sampling rate and low to medium resolution. So generally a high speed flash ADCs are used in these types of receivers. This topology is having the advantage of having lesser number of ADCs in comparison with MB-OFDM UWB. This effectively reduces the device count in the receiver thereby saving area and power consumption.

Fig. 2.2 Block diagram of DS-UWB receiver

Summary of DS-UWB receiver requirements are given in Table 2.3.

Table 2.3 Summary of DS-UWB receiver requirements

| Bandwidth          | 2 GHz to 5 GHz                      |  |  |

|--------------------|-------------------------------------|--|--|

| Bands              | 2 (Lower and Upper)                 |  |  |

| Signalling Scheme  | BPSK, PPM                           |  |  |

| Access Methodology | Spread spectrum CDMA                |  |  |

| Pulse Interval     | 1 ns (max)                          |  |  |

|                    | High speed Flash                    |  |  |

| ADC used           | Low to medium resolution (3-5 bits) |  |  |

|                    | High sampling rate                  |  |  |

Because of the reduced area and less complexity involved in the design, DS-UWB technology based applications are considered in this thesis. So in-home wireless connectivity and biomedical applications are taken as the examples. The next section describes about different ADCs architectures used in different applications.

#### 2.6 Introduction to Analog to Digital Converter

Digital signal has the benefits of easier processing, analysis and storage. Nowadays, a lot of applications make use of digital signal processing (DSP) to demodulate the transmitted information. Over the years, improvement of digital integrated circuit has strongly followed Moore's Law. As a result, transistor size has significantly reduced in size and the speed of digital circuit has been exponentially boosted. This trend broadens the gap between the digital circuit and its analog counterpart, for which the technology progress is not as beneficial. On one hand, there exists high speed digital circuit with its ever growing processing power and efficiency. On the other hand, analog circuit struggles and largely falls short to maintain pace. Most of systems require communication with the real analog world at some point or other. For that purpose analog interface circuit, is a crucial factor in the whole system. It is attractive to push the analog digital border nearer to the real world, where the system can acquire enhanced advantage of the high speed digital circuit. This development places high pressure on analog circuit designers to build up very high speed interface circuits, analog-todigital and digital to analog converters (ADCs and DACs) that can sustain with the digital world by maintaining other desirable attributes like small chip area and low power consumption.

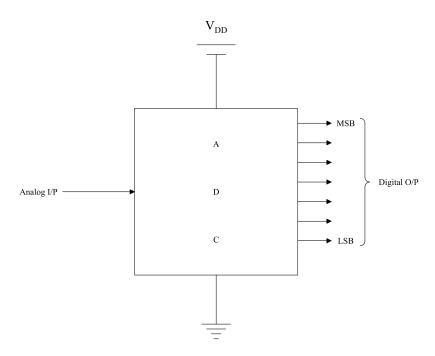

The continuous speed enhancement of serial links and emergence of new communication technologies such as ultra wideband (UWB) have begins greater demands on the speed and power requirements of high speed (3 to 5 GHz) low to medium resolution (4 to 6 bits) analog to digital converters (ADCs). ADCs are the fundamental building blocks that provide a border between the digital domain and analog world. As it is the major block in mixed signal applications, it plays a crucial role in data processing applications and that limits the performance of the overall system. The basic block diagram of analog-to-digital converter is depicted in Fig. 2.3. An analog signal is applied to the input of the converter which converts it into digital data which is used for further processing. ADCs can be categorized into different types mainly based on sampling rate, resolution and power dissipation and target

#### Chapter 2

application. Based on the applications, ADC architecture can be mainly classified into three types.

- Low speed high resolution

- Medium speed medium resolution

- High speed low resolution

The different types of ADCs are flash, pipeline, successive approximation, dual slope and sigma delta [16]. The chapter deals with different analog-to-digital converter architectures and concludes with the selection of the ADC architecture which can be appropriately used for UWB applications. The next section gives detail description about each ADC used in different applications.

Fig. 2.3 Block diagram of analog to digital converter

#### **2.6.1 Flash ADC**

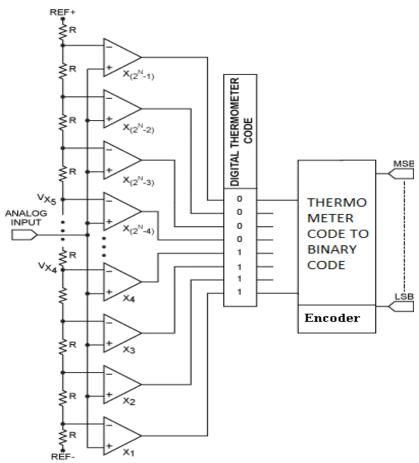

Flash ADCs utilize massive parallelism in its architectures and hence the name parallel ADC. The results of the conversion are available at the end of one clock cycle. Due to the parallel structural design it is the fastest ADC among all the other types and is appropriate for large bandwidth applications such as radar processing data acquisition, high density disk drives, satellite communication, data communications and real time oscilloscopes. It is also highly used in other types of ADCs such as pipeline ADCs and multi bit sigma delta ADCs. Flash ADC is limited to a resolution of six to eight bits because the numbers of comparators utilized in these ADCs are doubled if the resolution is enhanced by one bit. Due to this, it consumes a lot of power and becomes costly, as the resolution increases [17].

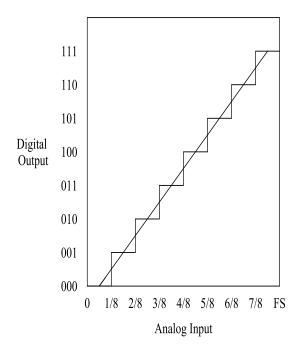

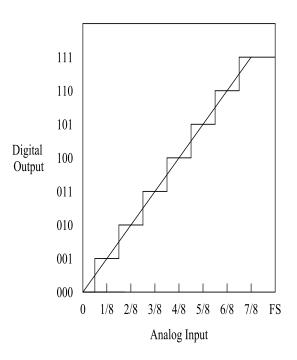

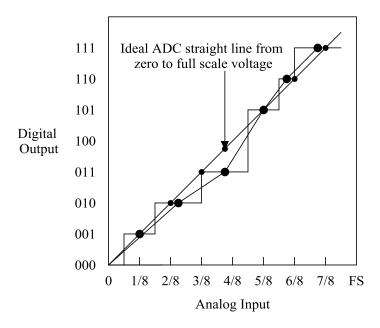

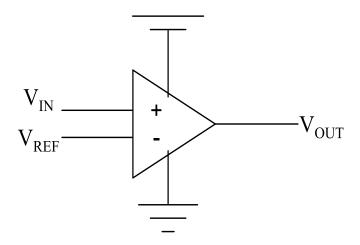

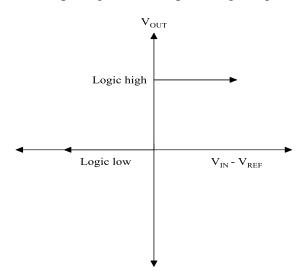

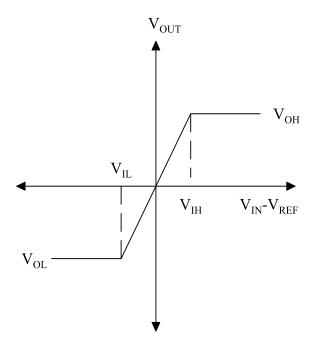

Fig. 2.4 shows the generic flash ADC block diagram. From the figure, it is clear that 2<sup>N</sup> -1 comparators are needed for N bit flash ADC. Each comparator is connected with one input to an analog input and another to a reference voltage. The reference voltage for the comparator is generated with the help of a resistor ladder. The resistor ladder consists of 2<sup>N</sup> resistors. The reference voltages are uniformly spaced by least significant voltage between the smallest reference voltage and the largest reference voltage. When the input voltage is less than the reference voltage of comparator it produces logic low otherwise, the comparator output is logic high. The outputs of the comparators are coming in a specific fashion which is known as thermometer code. It's named because it is like a mercury thermometer, where the mercury column always rises to the suitable temperature and no mercury is available beyond that temperature. This thermometer code is further translated into a binary data with the assist of a thermometer to binary code converter. Flash ADC requires a huge number of comparators when the resolution increases. For example, a 6-bit flash ADC requires 63 comparators, but 1023 comparators are required for a 10-bit flash ADC. This exponential increase of comparators needs a large die size which leads to huge amount of power consumption.

Fig. 2.4 Generic block diagram of flash ADC

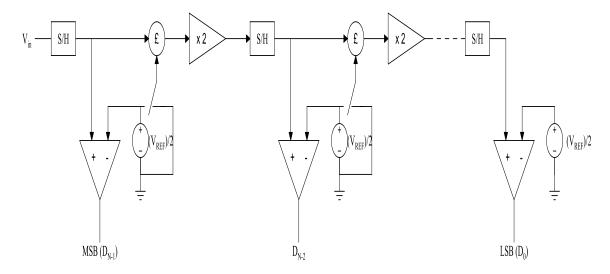

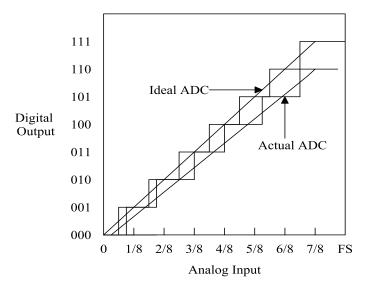

#### 2.6.2 Pipeline ADC

Pipeline ADC is the one of the popular ADC architecture [18]. It can work from few mega samples to above hundred of mega samples with resolution ranging from 8 bit to 16 bits. Due to its high resolution and medium sampling rate, it is commonly used in medical and communication applications such as, CCD imaging, digital receiver, digital video (HDTV), ultrasonic medical imaging, cable modem, base station and fast Ethernet. Pipeline ADCs are also used in data acquisition systems, where frequency and time domain features are both important. Pipeline ADCs are useful in configurations where latency is not critical and for applications where latency is critical, flash ADC is preferred. Design complexity grows linearly (not exponentially) with the resolution, thus providing converters with medium speed, low power and high resolution at the same time.

The basic pipelined architecture is shown in Fig. 2.5. The pipeline ADC consists of serially connected N stages. Each stage includes one bit ADC, sample and hold circuit and an amplifier with a gain of two. Once the input signal is sampled, it is compared with  $(V_{REF}/2)$ . The output of the each one bit ADC (comparator) generates the binary bit. If analog input voltage is larger than  $(V_{REF}/2)$ , comparator output is logic high and  $V_{REF}/2$  is deducted from the held signal and transfer it to the amplifier. If the input voltage is less than  $V_{REF}/2$ , then transfer the original signal to the amplifier. The last step of operation is to multiply the summation result by two and transfer it to the next stage sample and hold circuit. The total time taken for the conversion of the analog input to digital data is time of N clock cycles. The one of the main disadvantage of this converter is a small error in the first stage transmits through the converter and results in a large amount of error at the end of conversion.

Fig. 2.5 Basic architecture of pipeline ADC

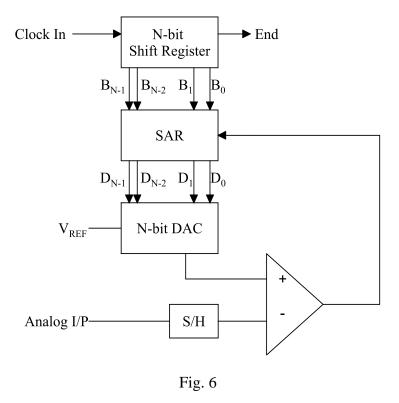

# 2.6.3 Successive Approximation Register (SAR) ADC

Successive approximation register (SAR) analog-to-digital converters (ADCs) are commonly used in low sampling rate and medium to high resolution applications [18]. The resolution is in the range between 8 to 16 bits. It also offers low power consumption and small form factor. Since its power consumption is low therefore it is a better alternative for low power applications such as industrial controls, data acquisition systems, portable/battery powered devices and pen digitizers. For a three bit SAR ADC, three comparisons are needed for the complete operation but at the same time flash ADC requires seven comparisons are required with seven different comparators. The power consumption is reduced by a large amount in SAR ADC in comparison with flash ADC because of the reduced number of comparators.

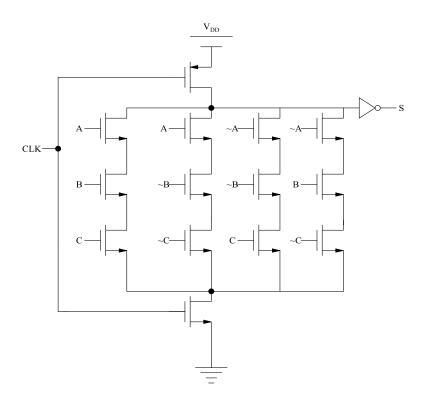

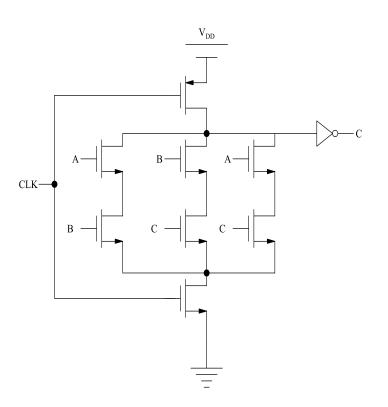

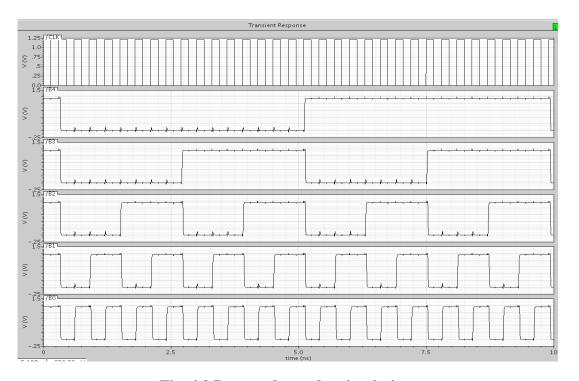

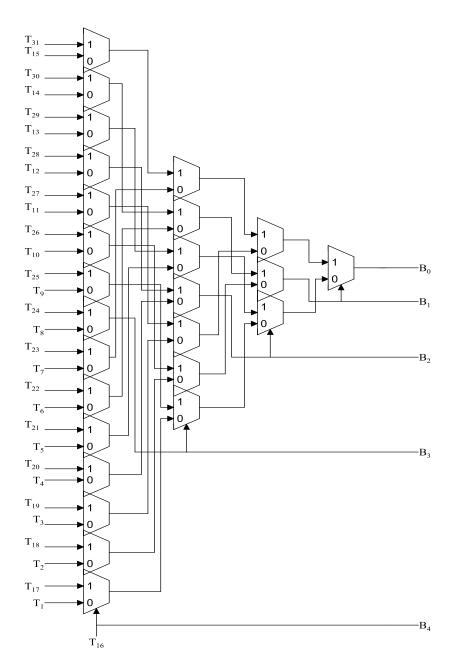

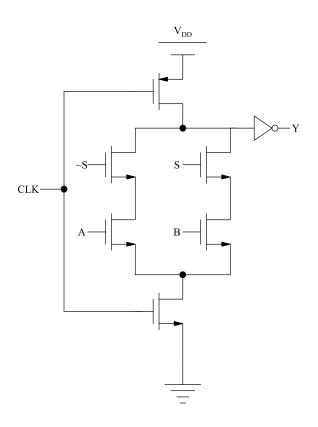

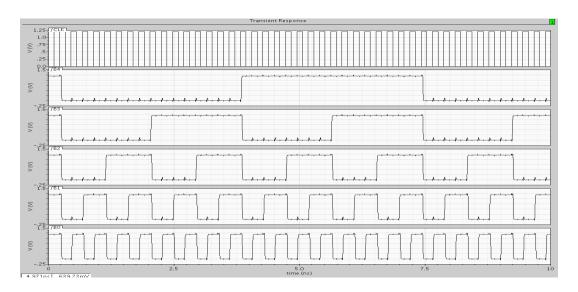

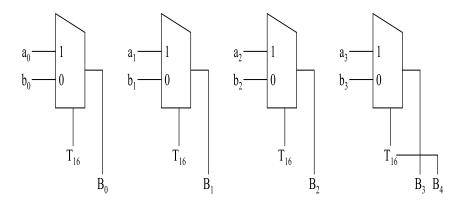

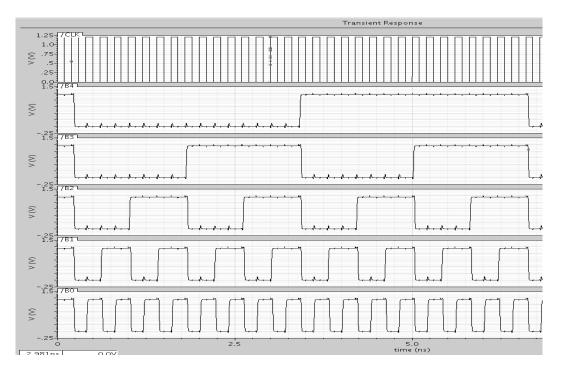

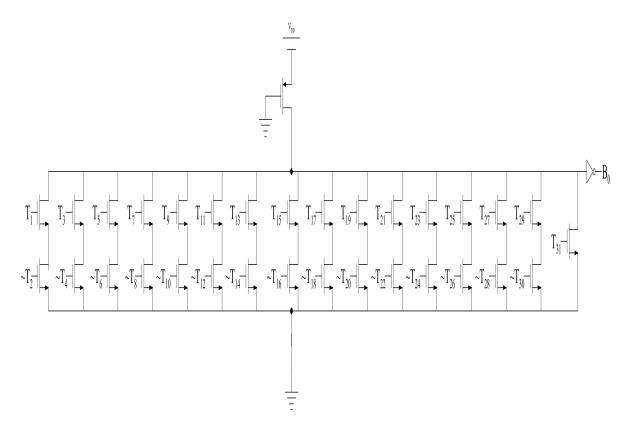

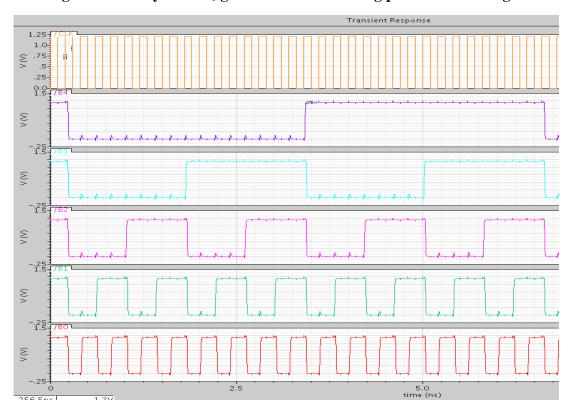

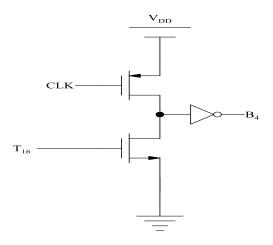

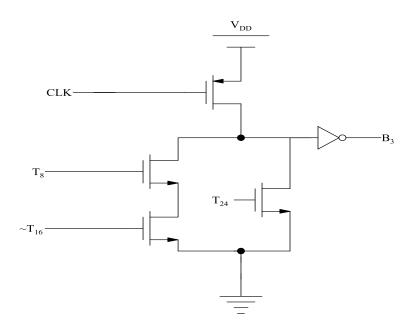

Fig. 2.6 Block Diagram of SAR ADC