# Fast and Robust Design of CMOS VCO for Optimal Performance

Dissertation submitted in partial fulfillment of the requirements for the award of Doctor of Philosophy

by

### PRAKASH KUMAR ROUT

Under the supervision of

Prof. (Dr.) D. P. Acharya Prof. (Dr.) G. Panda

ELECTRONICS AND COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY

ROURKELA

INDIA

### **ACKNOWLEDGEMENTS**

I take this opportunity to express my reverence to my supervisors Prof. (Dr.) D. P. Acharya and Prof. (Dr.) G. Panda for their guidance, inspiration and innovative technical discussions all during the course of this work. I find words inadequate to thank them for enabling me to complete this work in spite of all obstacles.

I am also thankful to all faculty members and research students of ECE Department, NIT Rourkela. Special thanks go to Prof.(Dr.) K.K.Mohapatra, Prof.(Dr.) S.K.Patra and Prof.(Dr.) S.Meher for their constructive criticism and motivation during the course of my work.

I am thankful to Prof.A.K.Swain, Prof.A.K.Sahoo and Prof.U.K.Sahu for their support and help at times of need. It is my pleasure to show my indebtedness to my friends at NIT like Umakanta, Debasish, Dandpat Sir, Vijay Sharma, Tom, Sudheendra, Srinivas, Pallab, Soubhagya and Jagannath for their help during the course of this work.

I am also thankful to my colleagues at Silicon Institute of Technology, Bhubaneswar for their kind help and support at times of need.

I find words inadequate to express any form of acknowledgement to my father, mother, brothers and sisters who have been an emblem of blessings in all my steps of life.

(Prakash Kumar Rout)

### **TABLE OF CONTENTS**

| 1.                                | Introduction                                                          | 1          |

|-----------------------------------|-----------------------------------------------------------------------|------------|

| 1.1                               | Motivation                                                            | 1          |

| 1.2                               | Scope of the Thesis                                                   | 2          |

| 1.3                               | Structure and Chapter wise Contribution of the Thesis                 | 3          |

| 1.4                               | List of Publications Related to Thesis                                |            |

| 1.5                               | Summary of Publications Related to Thesis                             |            |

| 2.                                | Advances in Analog Integrated Circuit Optimization: A Brief Overview  |            |

| 2.1                               | Introduction                                                          |            |

| 2.2                               | Analog IC Design Flow                                                 |            |

| 2.3                               | Scope for Analog IC Design Optimization                               |            |

| 2.4                               | Methodologies for Analog IC Optimization                              |            |

| 2.5                               | Conclusion                                                            |            |

| 3.                                | Rapid Prototyping Methodology for High Performance Nano-CMOS VCO      |            |

|                                   | based on NSGA-II Optimization                                         |            |

| 3.1                               | Introduction                                                          |            |

| 3.2                               | Design Objectives for the Nano-CMOS VCO                               | 33         |

|                                   | 2.1 CMOS Ring Oscillator                                              |            |

|                                   | 2.2 Current Starved VCO                                               |            |

|                                   | 2.3 Differential VCO                                                  |            |

| 3.3                               | NSGA – II Optimization Kernel                                         | 44         |

| 3.4                               | Design Flow of Energy Efficient Low Phase Noise CMOS Voltage          |            |

|                                   | trolled Oscillator                                                    |            |

| 3.5                               | Performance Analysis                                                  |            |

| 3.6                               | Conclusion                                                            | 63         |

| 4.                                | IDEA Based Fast Design Methodology of Nano-CMOS VCO for               |            |

| 4 1                               | Performance Optimization                                              |            |

| 4.1                               | Introduction                                                          |            |

| 4.2                               | Infeasibility Driven Evolutionary Algorithm (IDEA)                    | 66         |

| 4.3                               | IDEA based Parasitic Aware Design Methodology of VCO for              | <b>~</b> 0 |

|                                   | Formance Optimization                                                 |            |

| 4.4                               | Performance Analysis                                                  |            |

|                                   | 4.1 CMOS Ring Oscillator                                              |            |

|                                   |                                                                       | 77         |

|                                   | 4.3 Differential VCO                                                  |            |

| 4.5                               | Conclusion                                                            | 84         |

| 5.                                | Process Variation Aware Fast Design of VCO with Performance           | 07         |

| <i>5</i> 1                        | Optimization                                                          |            |

| 5.1                               | Introduction Fabrication Process Variations                           |            |

| <ul><li>5.2</li><li>5.3</li></ul> |                                                                       |            |

|                                   | Fast Design Methodology for Optimized Parasitic and Process Variation |            |

| 5.4                               | are (PPVA) VCO  Performance Analysis                                  |            |

|                                   | · · · · · · · · · · · · · · · · · · ·                                 |            |

| 3                                 | .4.1 CMOS Ring Oscillator                                             | 71         |

| 5.          | .4.2 CMOS Current Starved VCO                                      | 95  |

|-------------|--------------------------------------------------------------------|-----|

| 5.          | .4.3 Differential VCO                                              | 100 |

| 5.5         | Conclusion                                                         | 105 |

| 6.          | Design of Robust Analog Integrated Circuit based on Process Corner |     |

|             | Performance Variability Minimization                               | 107 |

| 6.1         | Introduction                                                       | 107 |

| 6.2         | Manufacturing Process Fluctuation Robust Design Methodology        | 109 |

| 6.3         | Performance Analysis of the Proposed PCPVM based Robust            |     |

| Methodology |                                                                    | 113 |

| 6.3.        | 1 Current Starved VCO                                              | 113 |

| 6.3.        | 2 Differential VCO                                                 | 119 |

| 6.4         | Conclusion                                                         | 123 |

| <b>7.</b>   | Conclusions and Scope for Future Research                          | 125 |

| 7.1         | General Conclusions                                                | 125 |

| 7.2         | Scope for Future Research                                          | 126 |

|             | References                                                         | 129 |

### LIST OF FIGURES

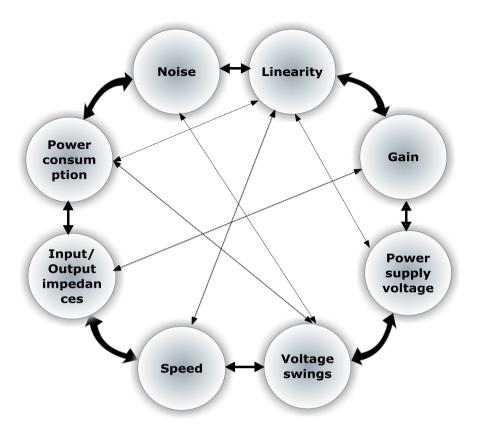

| Figure 2. 1 Analog IC Design Performance Octagon                              | 15   |

|-------------------------------------------------------------------------------|------|

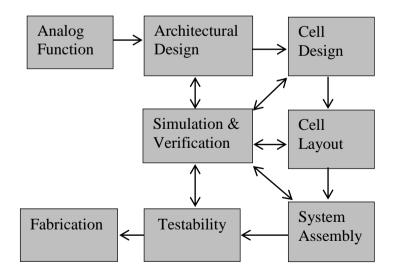

| Figure 2. 2 Analog IC Design Flow                                             | 15   |

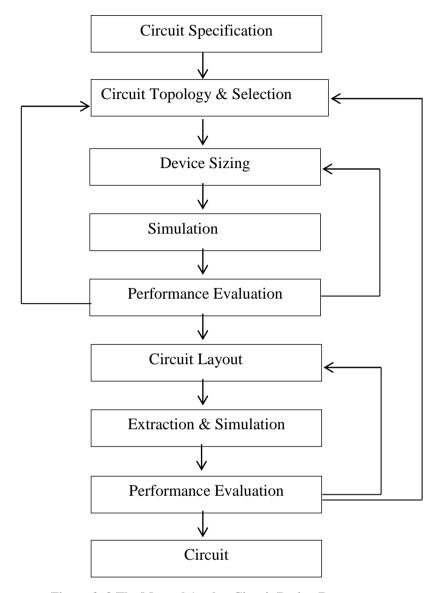

| Figure 2. 3 The Manual Analog Circuit Design Process                          | 18   |

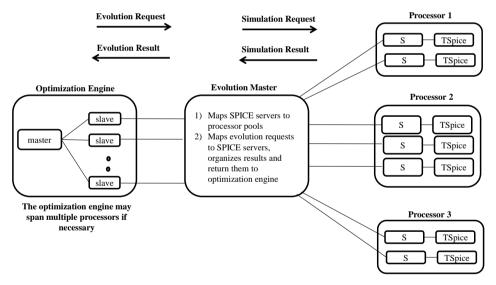

| Figure 2. 4 The Anaconda Synthesis Architecture                               | 26   |

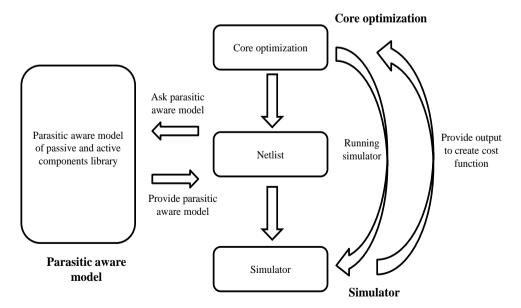

| Figure 2. 5 Parasitic Aware Optimization                                      |      |

|                                                                               |      |

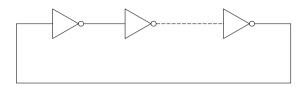

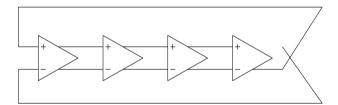

| Figure 3. 1 General Structure of ring oscillator                              |      |

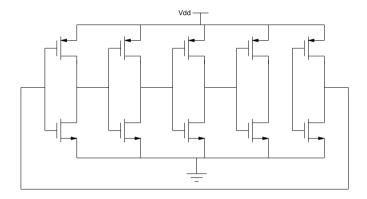

| Figure 3. 2 A five stage CMOS ring oscillator                                 |      |

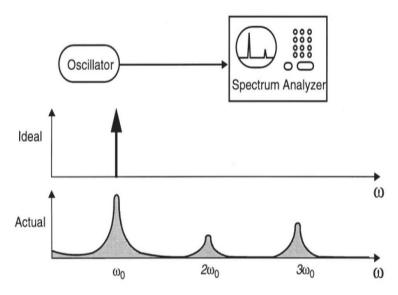

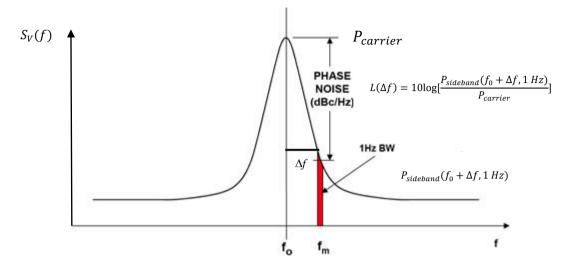

| Figure 3. 3 The Frequency Spectrum of an Ideal and Actual Oscillator          |      |

| Figure 3. 4 The Phase Noise calculation per unit bandwidth                    |      |

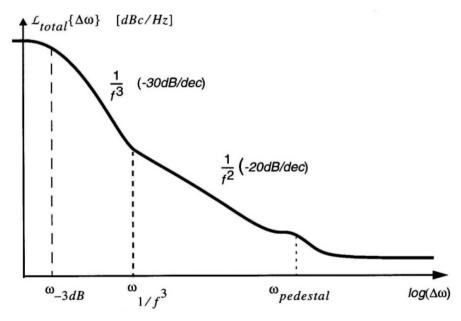

| Figure 3. 5 A typical phase noise plot for a free running oscillator          |      |

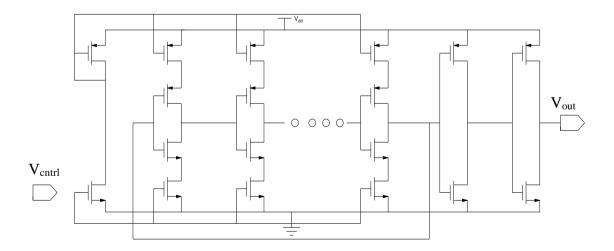

| Figure 3. 6 Circuit schematic of CSVCO                                        |      |

| Figure 3. 7 A four-stage Differential Voltage Controlled Oscillator           | 41   |

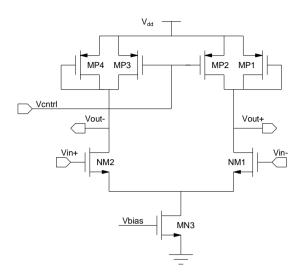

| Figure 3. 8 Circuit Schematic of the Delay Cell of Differential VCO           | 42   |

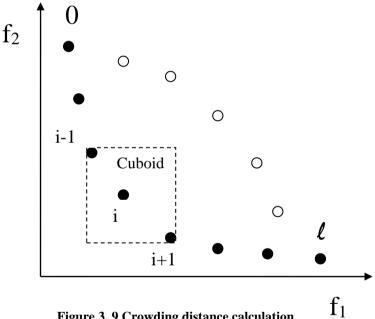

| Figure 3. 9 Crowding distance calculation                                     | 45   |

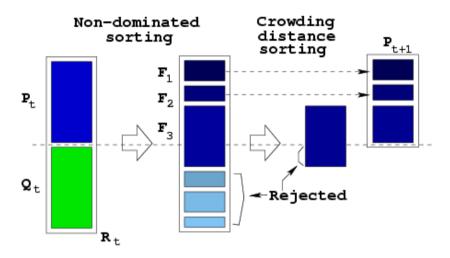

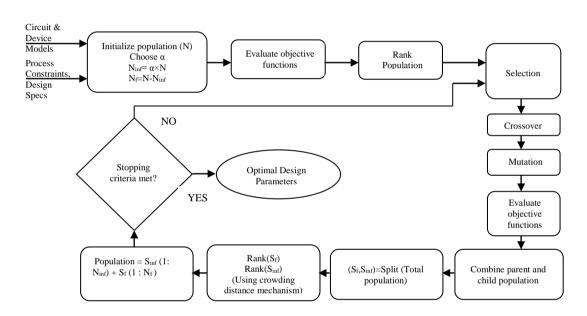

| Figure 3. 10 The NSGA – II Optimization Routine                               | 47   |

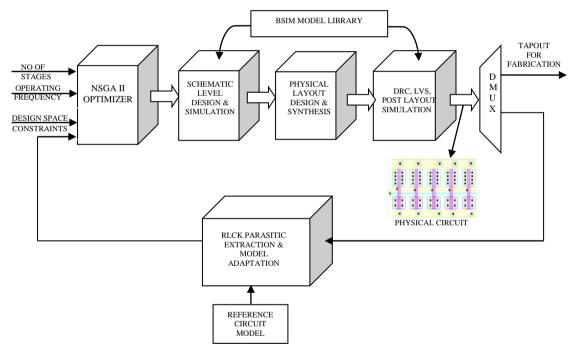

| Figure 3. 11 The Design Flow for Optimal CMOS VCO                             | 48   |

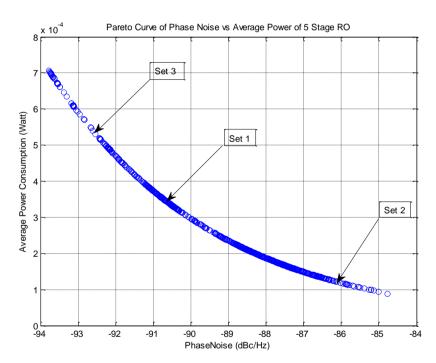

| Figure 3. 12 Pareto Curve of Phase Noise and Power Consumption for 5-stage    |      |

| Parasitic Aware Ring Oscillator                                               | 50   |

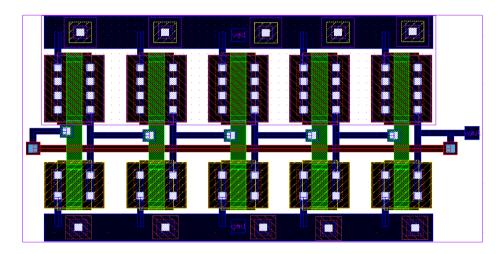

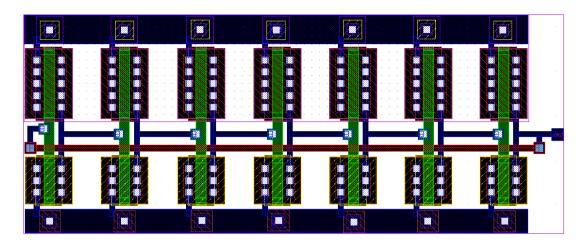

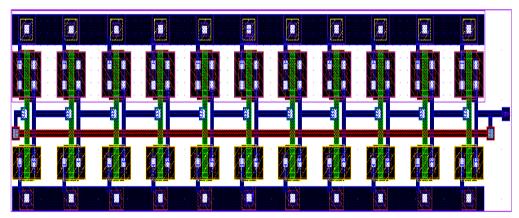

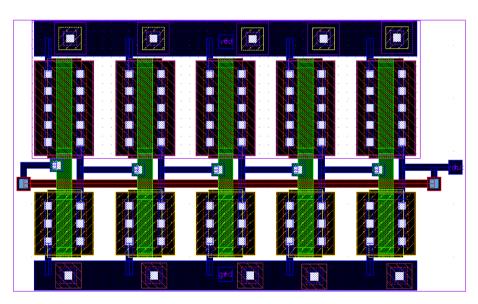

| Figure 3. 13 Physical Layout of Parasitic Aware Five stage CMOS Ring Oscillat | tor  |

|                                                                               |      |

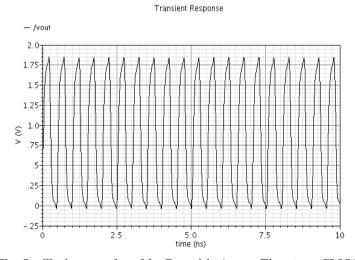

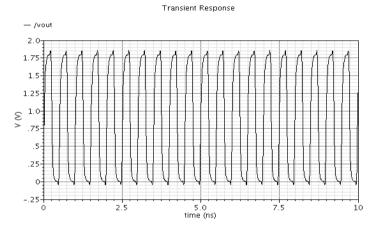

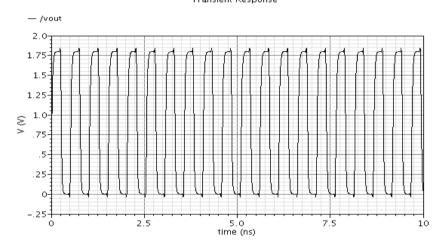

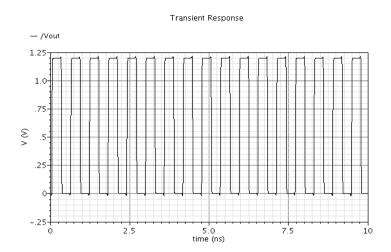

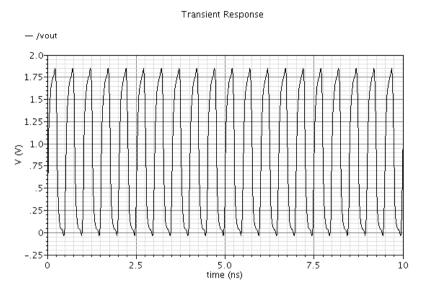

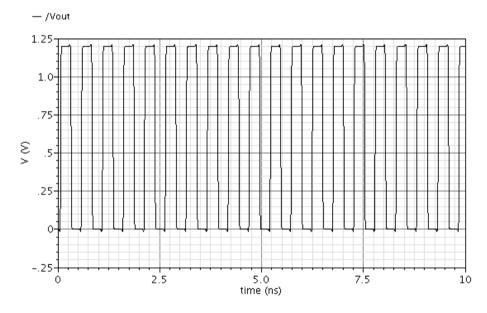

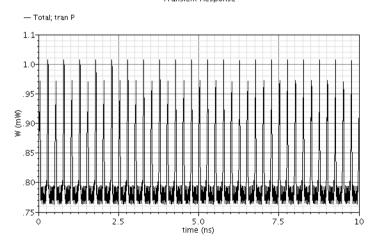

| Figure 3. 14 The Oscillations produced by Parasitic Aware Five stage CMOS Ri  | ing  |

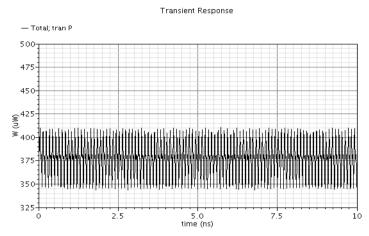

| Oscillator                                                                    | 51   |

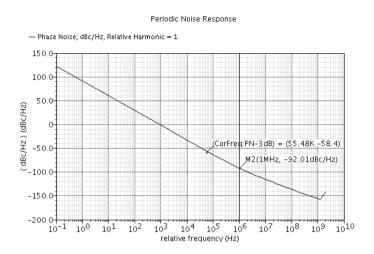

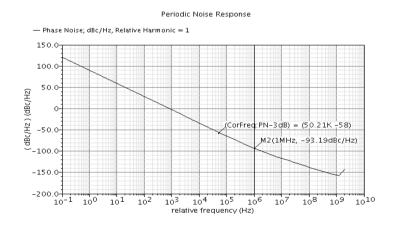

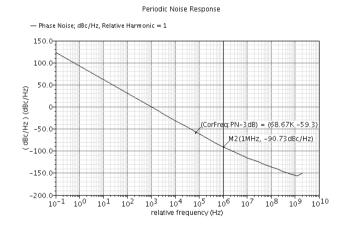

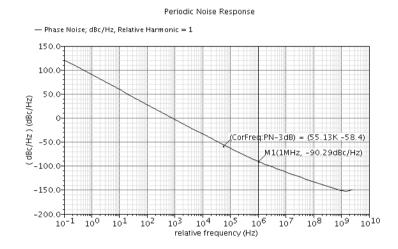

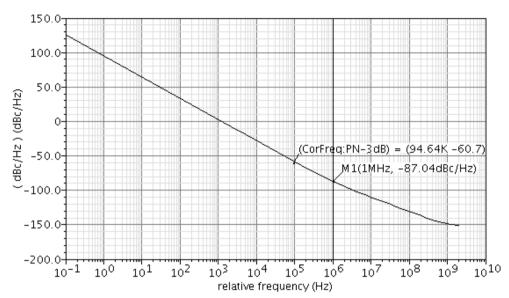

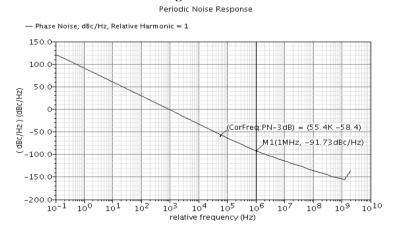

| Figure 3. 15 Phase Noise plot for Parasitic Aware Five stage CMOS Ring Oscill | ator |

|                                                                               | 52   |

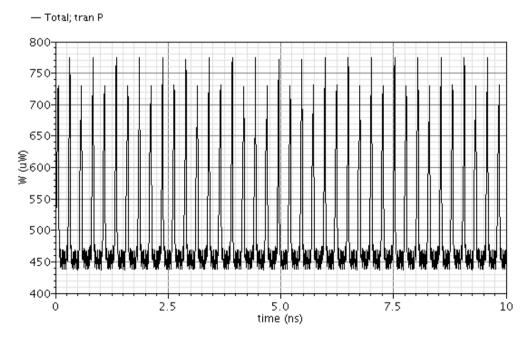

| Figure 3. 16 Power Estimation plot for Parasitic Aware Five stage CMOS Ring   |      |

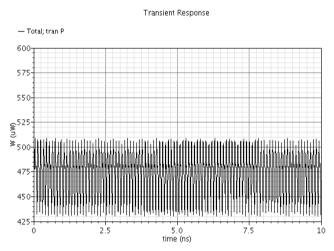

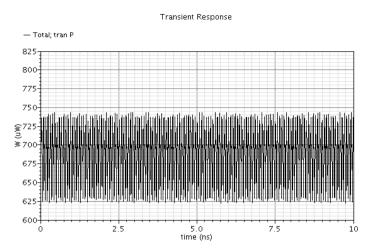

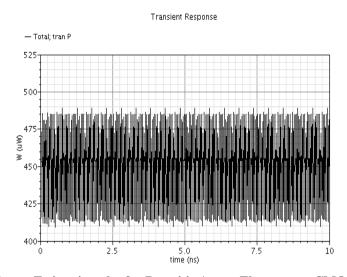

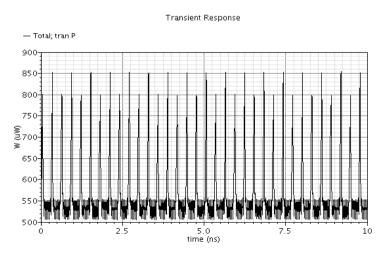

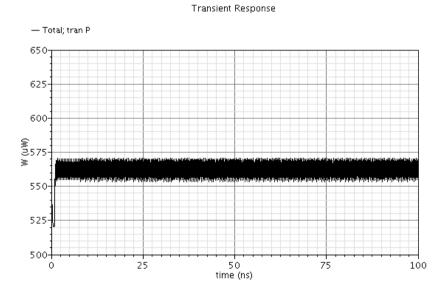

| Oscillator                                                                    |      |

| Figure 3. 17 Physical Layout of Parasitic Aware Seven stage CMOS Ring Oscill  |      |

|                                                                               |      |

| Figure 3. 18 The Oscillations produced by Parasitic Aware Seven Stage CMOS    | Ring |

| Oscillator                                                                    | 54   |

| Figure 3. 19 Phase Noise plot for Parasitic Aware Seven Stage CMOS Ring       |      |

| Oscillator                                                                    |      |

| Figure 3. 20 Power Estimation plot for Parasitic Aware Seven Stage CMOS Ring  | _    |

| Oscillator                                                                    |      |

| Figure 3. 21 Physical Layout of Parasitic Aware Eleven stage CMOS Ring        |      |

| Figure 3. 22 The Oscillations produced by Parasitic Aware Eleven Stage CMOS   |      |

| Ring Oscillator                                                               | 56   |

| Figure 3. 23 Phase Noise plot for Parasitic Aware Eleven Stage CMOS Ring      |      |

| Oscillator                                                                    |      |

| Figure 3. 24 Power Estimation plot for Parasitic Aware Eleven stage CMOS Rin  | _    |

| Oscillator                                                                    | 57   |

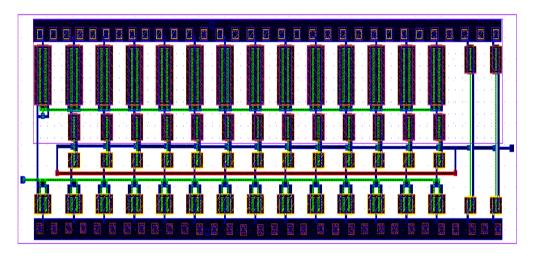

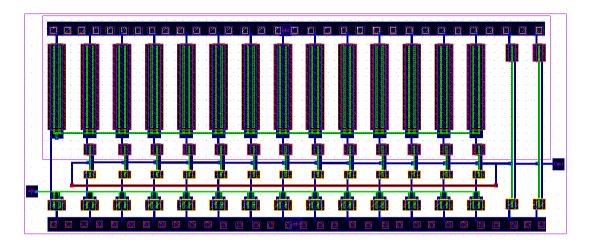

| Figure 3. 25 Physical Layout of Parasitic Aware Thirteen Stage Current Starved      |

|-------------------------------------------------------------------------------------|

| VCO58                                                                               |

| Figure 3. 26 Oscillations generated from the Parasitic Aware Current Starved VCO    |

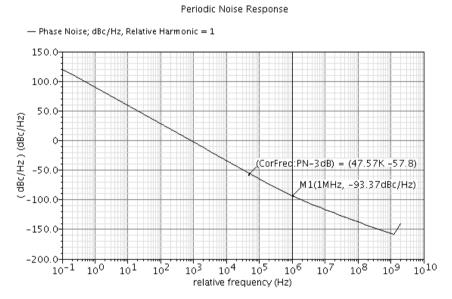

| Figure 3. 27 Phase Noise Plot of the Parasitic Aware Current Starved VCO59          |

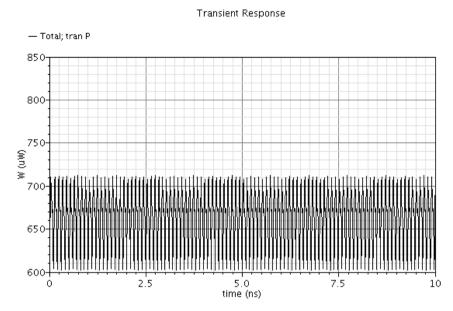

| Figure 3. 28 Power Consumption of the Parasitic Aware Current Starved VCO 59        |

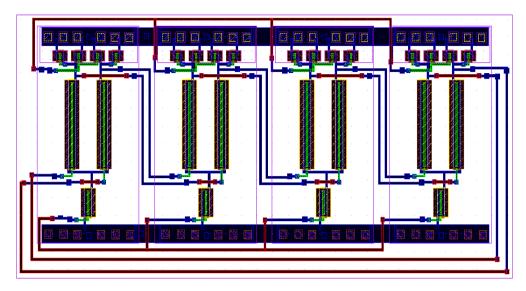

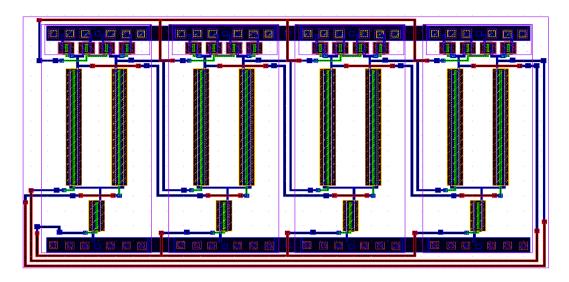

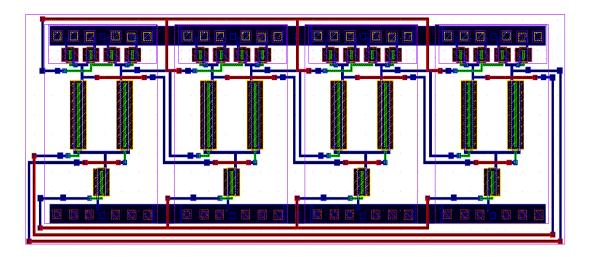

| Figure 3. 29 Physical Layout of Parasitic Aware CMOS DVCO61                         |

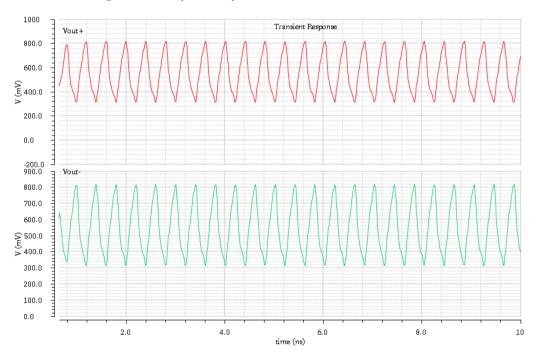

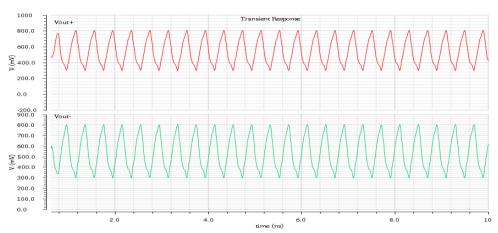

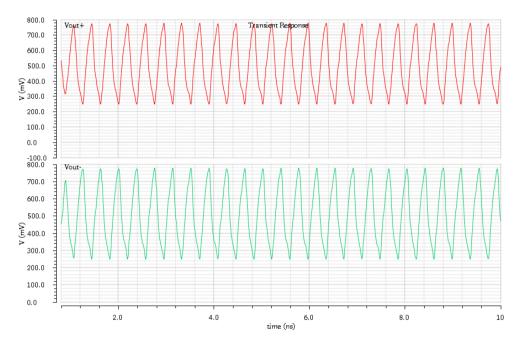

| Figure 3. 30 Oscillations generated from the Parasitic Aware CMOS DVCO61            |

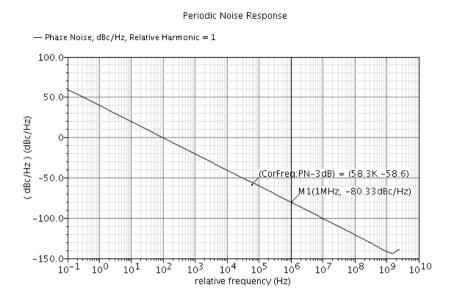

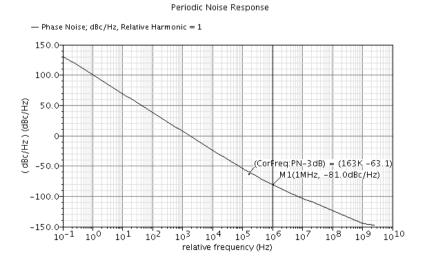

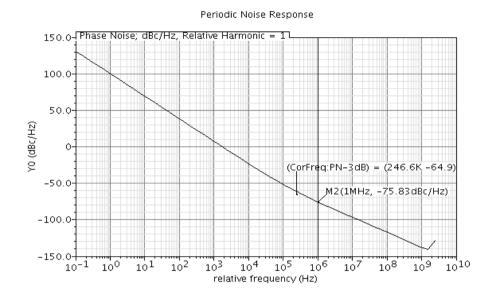

| Figure 3. 31 Phase Noise Plot of the Parasitic Aware CMOS DVCO62                    |

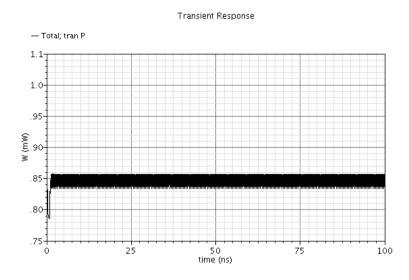

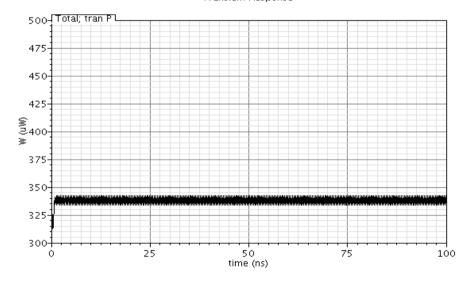

| Figure 3. 32 Power Consumption of the Parasitic Aware CMOS DVCO62                   |

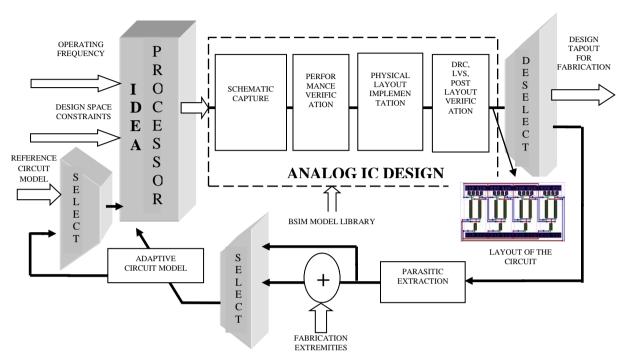

| Figure 4. 1 The IDEA based Parasitic Aware VCO design flow72                        |

| Figure 4. 2 Physical Layout of Five-Stage Parasitic Aware Ring Oscillator designed  |

| using IDEA                                                                          |

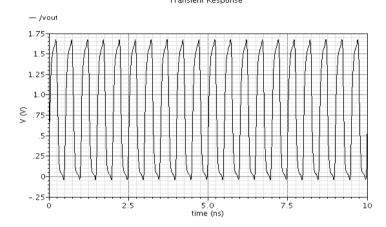

| Figure 4. 3 Oscillations generated from the Five-Stage Parasitic Aware Ring         |

| Oscillator designed using IDEA74                                                    |

| Figure 4. 4 Phase Noise plot of the Five-Stage Parasitic Aware Ring Oscillator      |

| designed using IDEA                                                                 |

| Figure 4. 5 Power Estimation plot of the Five-Stage Parasitic Aware Ring Oscillator |

| designed using IDEA                                                                 |

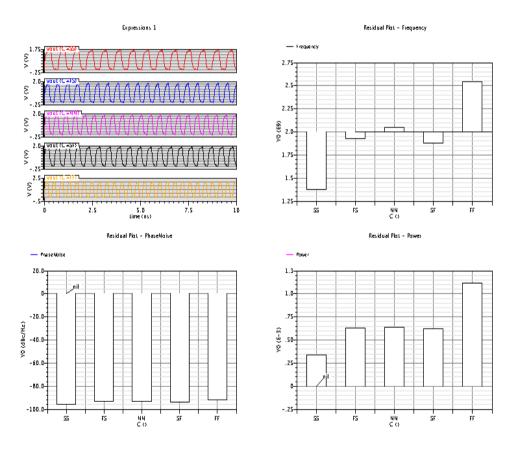

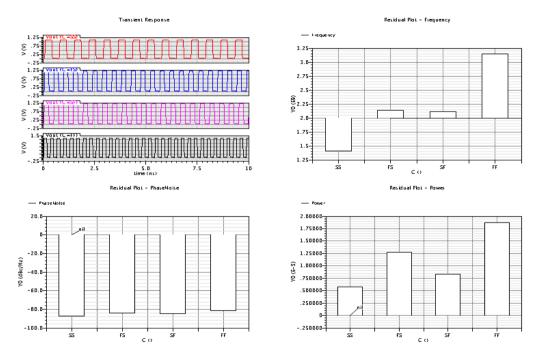

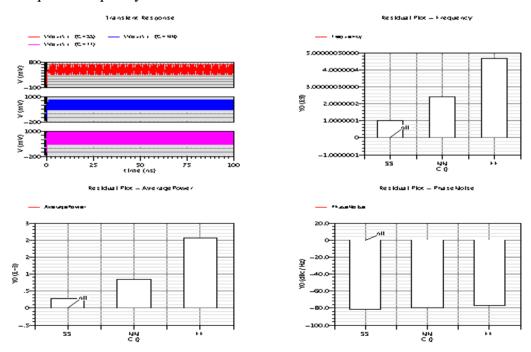

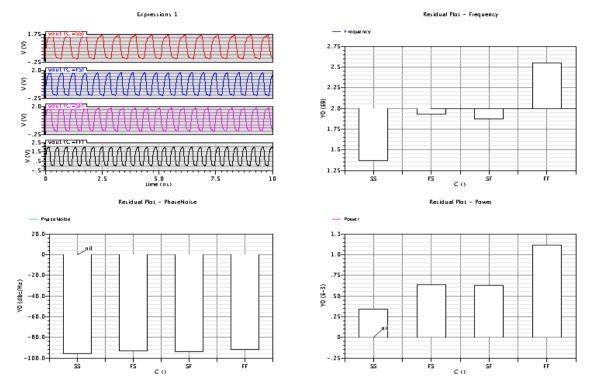

| Figure 4. 6 Corner Analysis plots for Frequency, Phase Noise and Power of IDEA      |

| Optimized Five-Stage RO                                                             |

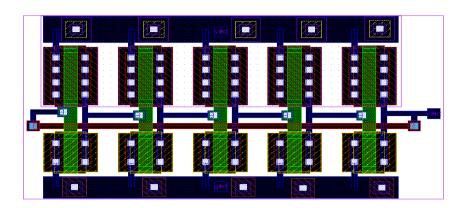

| Figure 4. 7 The optimized parasitic and process variation aware physical layout of  |

| 13 stage CSVCO                                                                      |

| Figure 4. 8 Oscillations produced by Parasitic Aware CSVCO (IDEA based)78           |

| Figure 4. 9 Phase Noise plot for Parasitic Aware CSVCO (IDEA based)79               |

| Figure 4. 10 Power Estimation plot of the Parasitic Aware CSVCO (IDEA based).79     |

| Figure 4. 11 Corner analysis of the final Parasitic Aware CSVCO80                   |

| Figure 4. 12 Physical Layout of the Parasitic Aware DVCO (IDEA based)82             |

| Figure 4. 13 Oscillations generated from the Parasitic Aware DVCO (IDEA based)      |

| 82                                                                                  |

| Figure 4. 14 Phase Noise plot of the Parasitic Aware DVCO (IDEA based)82            |

| Figure 4. 15 Power Estimation plot of the Parasitic Aware DVCO (IDEA based)83       |

| Figure 4. 16 Corner analysis plots for oscillations, frequency, power consumption   |

| and phase noise83                                                                   |

|                                                                                     |

|                                                                                     |

| Figure 5. 1 Design flow of IDEA based Parasitic and Process Variation Aware VCO     |

| 89                                                                                  |

| Figure 5. 2 Physical Layout of Parasitic & Process Variation Aware CMOS Ring        |

| Oscillator                                                                          |

| Figure 5. 3 Oscillations generated from the Parasitic & Process Variation Aware     |

| CMOS Ring Oscillator                                                                |

| Figure 5. 4 Phase Noise Plot of the Parasitic & Process Variation Aware CMOS        |

| Ring Oscillator                                                                     |

| Figure 5. 5 Power Consumption of the Parasitic & Process Variation Aware                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | -             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| CMOS Ring Oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

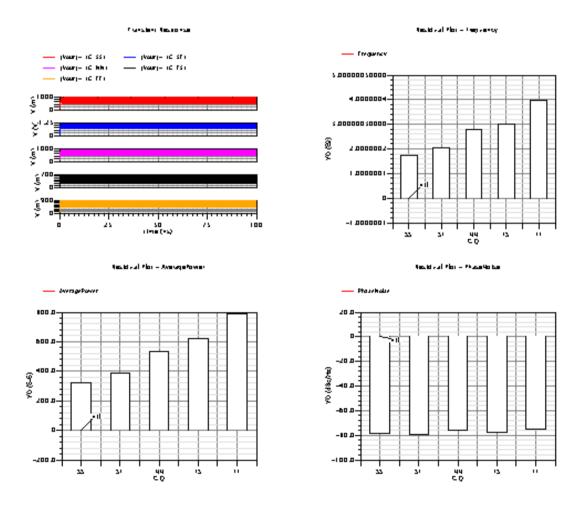

| Figure 5. 6 The manufacturing process corner variation analysis of waveford                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| frequency, phase noise and power of parasitic and process variation aware r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _             |

| oscillator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

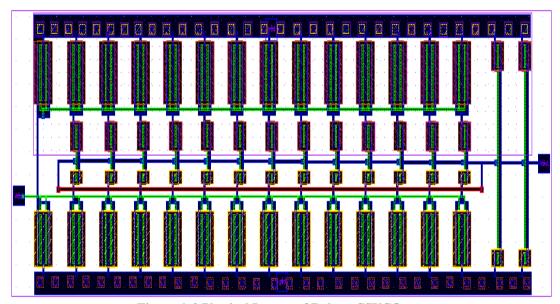

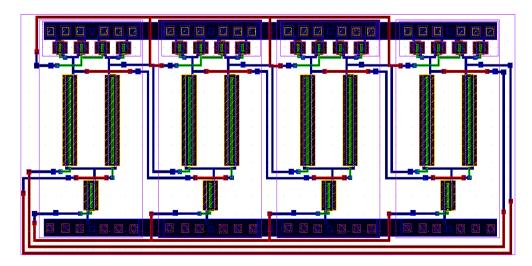

| Figure 5. 7 Physical Layout of the Optimized Parasitic and Process Variatio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| Thirteen-Stage CSVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |

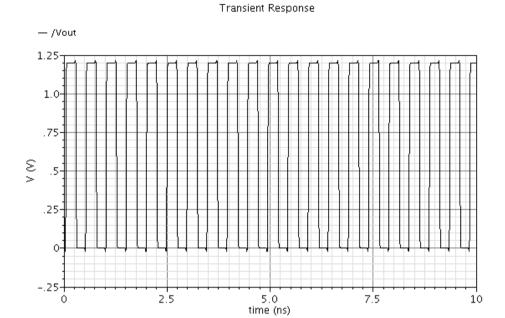

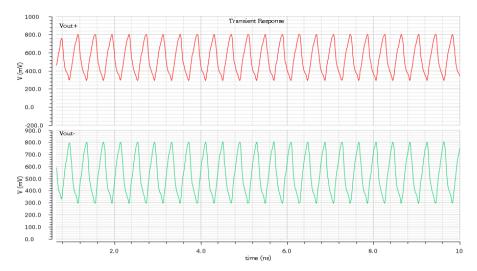

| Figure 5. 8 Oscillations produced by the Optimized Parasitic and Process Va                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| Aware CSVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

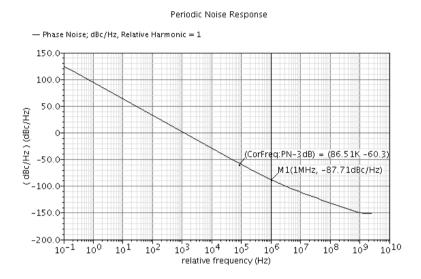

| Figure 5. 9 Phase Noise plot of the Optimized Parasitic and Process Variation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| CSVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |

| Figure 5. 10 Power estimation of the Optimized Parasitic and Process Varia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |

| Aware CSVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

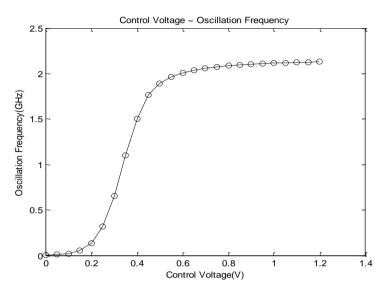

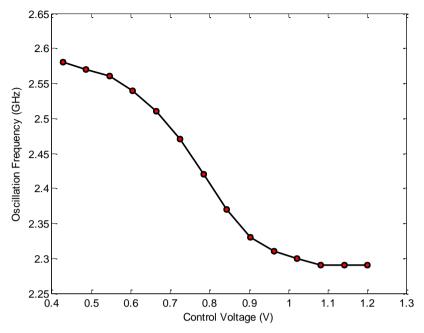

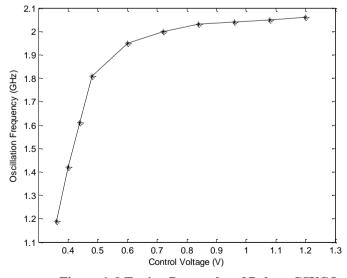

| Figure 5. 11 Variation of oscillation frequency with control voltage of the O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               |

| Parasitic and Process Variation Aware CSVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

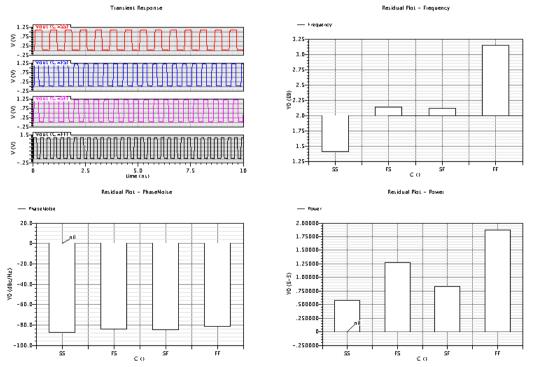

| Figure 5. 12 Corner analysis of the Parasitic and Process Variation Aware C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 98            |

| Figure 5. 13 Physical Layout of Parasitic & Process Variation Aware DVCC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | D 101         |

| Figure 5. 14 Oscillations generated from the Parasitic & Process Variation A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>A</b> ware |

| DVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 101           |

| Figure 5. 15 Phase Noise plot of the Parasitic & Process Variation Aware D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | VCO 102       |

| Figure 5. 16 Power Consumption of the Parasitic & Process Variation Awar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | e DVCO        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

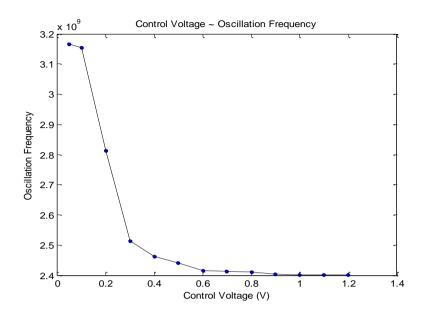

| Figure 5. 17 Control Voltage versus Oscillation Frequency plot of the Paras                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |

| Process Variation Aware DVCO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |

| Figure 5. 18 Corner Analysis plots for oscillations, frequency, power consumptions of the control of the contro |               |

| and phase noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 104           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

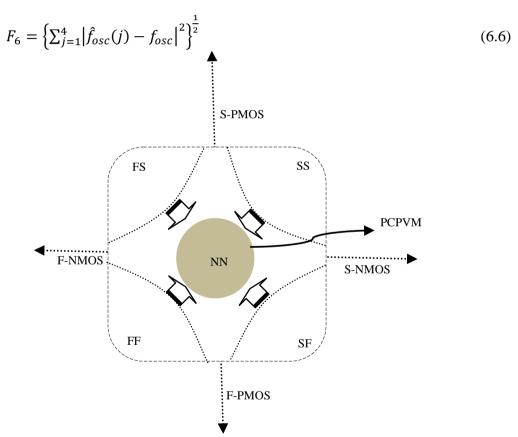

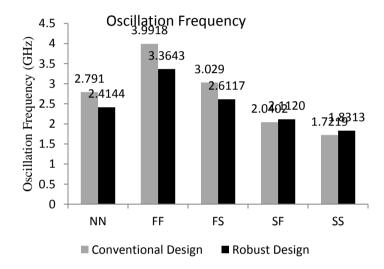

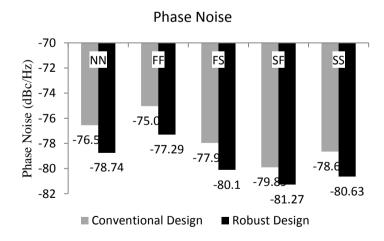

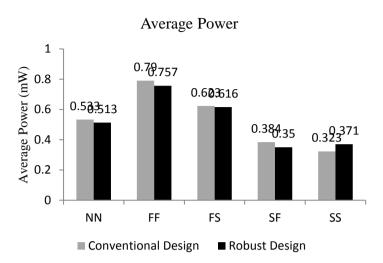

| Figure 6. 1 Fabrication Process Corner Performance Variability Minimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               |