# DESIGN AND ANALYSIS OF IMPROVED DOMINO LOGIC WITH NOISE TOLERANCE AND HIGH PERFORMANCE

#### PREETISUDHA MEHER

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA

ODISHA, INDIA

APRIL, 2015

# DESIGN AND ANALYSIS OF IMPROVED DOMINO LOGIC WITH NOISE TOLERANCE AND HIGH PERFORMANCE

A Thesis report submitted in partial fulfillment of the requirement for the degree of

# Doctor of Philosophy

In

**Electronics and Communication Engineering**

By

#### PREETISUDHA MEHER

Roll no: 509EC102

Under the guidance of

PROF. K. K. MAHAPATRA

DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

NATIONAL INSTITUTE OF TECHNOLOGY, ROURKELA

ODISHA, INDIA

APRIL, 2015

#### Department of Electronics and Communication Engineering National Institute of Technology Rourkela-769008

# **CERTIFICATE**

This is to certify that the thesis entitled "DESIGN AND ANALYSIS OF IMPROVED DOMINO LOGIC WITH NOISE TOLERANCE AND HIGH PERFORMANCE" submitted to National Institute of Technology, Rourkela by Mrs. Preetisudha Meher, bearing Roll No. 509EC102 for the award of the degree of DOCTOR OF PHILOSOPHY in Electronics and Communication Engineering is a bonafide record of research work carried out by her under my supervision and guidance.

This candidate has fulfilled all the prescribed requirements.

This thesis is based on candidate's own work, has not submitted elsewhere for the award of degree/diploma.

In my opinion, the thesis is in standard fulfilling all the requirements for the award of the degree of **DOCTOR OF PHILOSOPHY** in Electronics and Communication Engineering.

Prof. Kamalakanta Mahapatra

**Supervisor**

Department of Electronics & Communication Engineering

National Institute of Technology, Rourkela, 769008

Odisha (INDIA)

# Dedicated To

# My Family

### **ACKNOWLEDGEMENTS**

This project is by far the most significant accomplishment in my life and it would have been impossible without the people who supported me and believed in me. I would like to extend my gratitude and my sincere thanks to my honorable, esteemed supervisor **Prof. Kamala Kanta Mahapatra**, Department of Electronics & Communication Engineering. He is not only a great professor with deep vision but also most importantly a kind person. I sincerely thank for his exemplary guidance and encouragement. His trust and support inspired me in the most important moments of making right decisions and I feel proud of working under his supervision.

I am very much thankful to our director, **Prof. Sunil Kumar Sarangi**, for providing us with best facilities in the department. I am very much thankful to all my Professors **Prof. A. K. Swain**, **Prof. S. Meher**, **Prof. U. C. Pati**, **Prof. S K. Patra**, **Prof. D. P. Acharya**, **Prof. S. K. Das** and all the professors of the department for providing me their valuable suggestions during my thesis work and for providing a solid background for my studies. I want to thank **Prof. K. K. Khatua** of civil department who has been great source of inspiration to me and I thank him from the bottom of my heart.

I want to thank research scholar Mr. Vijay Sharma and Mr. Sauvagya Sahoo for all thoughtful and mind stimulating discussions we had, which prompted me to think beyond the obvious. I would like to show my gratitude to all my friends and especially to research scholars Karuppanan, Jaganath, Srinivas, Tom, Sudindra, Govind, Ramakrishna, Rajesh and Venkatratnam for all the supports and help.

I would like to thank my parents and elder brother who taught me the value of hard work by their own example and who have prayed for me for last 4 years. I want to thank my husband for providing me enormous support being apart during the whole tenure of my stay in NIT Rourkela. My loving thanks to my daughter Mokshita for a lot of compromise she did during my Ph. D. At last but above all, I owe this work to my much revered LORD for giving me such a chance to work among these scholastic people and scholastic environment.

Preetisudha Meher

# **TABLE OF CONTENTS**

| ACKNOWLEDGEMENTS                      | i    |

|---------------------------------------|------|

| LIST OF FIGURES                       | VII  |

| LIST OF TABLES                        | XIV  |

| ABSTRACT                              | XVI  |

| ABBREVIATION                          | XVII |

| 1. INTRODUCTION                       | 1    |

| 1.1 INTRODUCTION                      | 1    |

| 1.2 PARAMETERS OF ENHANCEMENT         | 2    |

| 1.2.1 POWER                           | 2    |

| 1.2.2 PROPAGATION DELAY               | 4    |

| 1.2.3 NOISE                           | 5    |

| 1.3 MOTIVATION FOR THE WORK           | 5    |

| 1.3.1 NEED FOR LOW-POWER              | 5    |

| 1.3.2 NEED FOR HIGH SPEED             | 5    |

| 1.3.3 NEED FOR NOISE-IMMUNITY         | 5    |

| 1.3.4 NEED FOR LESS-AREA              | 6    |

| 1.4 OBJECTIVE OF THE RESEARCH WORK    | 6    |

| 1.5 THESIS ORGANIZATION               | 6    |

| 2. BACKGROUND LOGIC STYLES            | 8    |

| 2.1 DIFFERENT LOGIC STYLES            | 8    |

| 2.1.1 STATIC CMOS LOGIC               | 8    |

| 2.1.2 DIFFERENT TYPES OF STATIC LOGIC | 10   |

| 2.2 DYNAMIC CMOS LOGIC                | 14   |

| 2.2.1 ISSUES IN DYNAMIC LOGIC         | 15   |

| 2.3 DOMINO LOGIC                      | 12   |

|    | 2.3.1 RACE CONDITION IN DOMINO LOGIC                       | 19 |

|----|------------------------------------------------------------|----|

|    | 2.4 OVERVIEW OF PREVIOUS WORKS                             | 19 |

|    | 2.4.1 KEEPER IMPLEMENTATION                                | 21 |

|    | 2.4.2 PRECHARGE OF INTERNAL NODES                          | 26 |

|    | 2.4.3 SOURCE VOLTAGE RAISING                               | 26 |

|    | 2.4.4 COMPLEMENTARY P-NETWORK                              | 31 |

|    | 2.5 OTHER MODIFICATIONS                                    | 35 |

|    | 2.5.1 SFEG (SOURCE FOLLOWING EVALUATION GATE) TECHNIQUE    | 35 |

|    | 2.5.2 MENDOZA'S DOMINO LOGIC                               | 36 |

|    | 2.5.3 MODIFIED SFEG                                        | 36 |

|    | 2.5.4 DIODE-FOOTED DOMINO                                  | 38 |

|    | 2.6 CONCLUSION                                             | 39 |

| 3. | PROPOSED DOMINO LOGIC                                      | 40 |

|    | 3.1 INTRODUCTION                                           | 40 |

|    | 3.2 BASIC DOMINO GATE                                      | 41 |

|    | 3.3 PROBLEM DESCRIPTION IN DOMINO LOGIC                    | 42 |

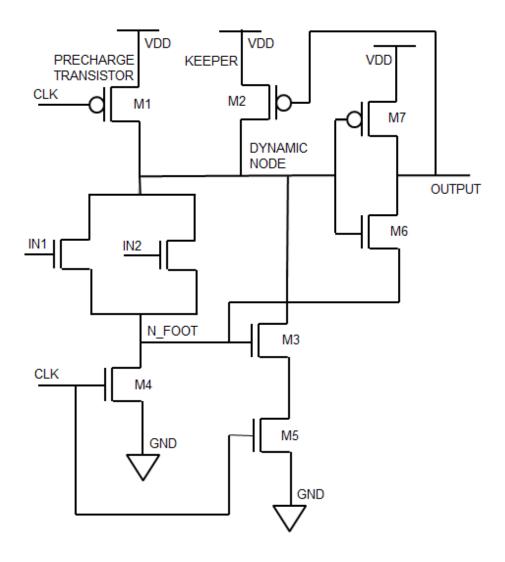

|    | 3.4 THE NOVEL APPROACH                                     | 45 |

|    | 3.4.1 CIRCUIT DESCRIPTION                                  | 45 |

|    | 3.4.2 CIRCUIT ANALYSIS                                     | 46 |

|    | 3.4.3 NOISE ANALYSIS                                       | 48 |

|    | 3.4.4 POWER ANALYSIS                                       | 48 |

|    | 3.4.5 CHARGE SHARING ANALYSIS                              | 57 |

|    | 3.5 OR GATE IN PROPOSED LOGIC                              | 64 |

|    | 3.5.1 CIRCUIT DESCRIPTION AND OPERATION                    | 64 |

|    | 3.6 COMPARISON OF THE PROPOSED OR GATE WITH DOMINO OR GATE | 66 |

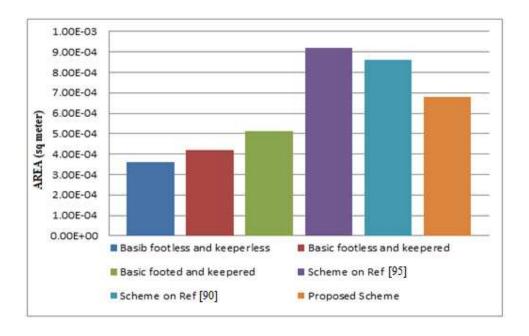

|    | 3.6.1 COMPARISON WITH NUMBER OF DEVICES USED               | 67 |

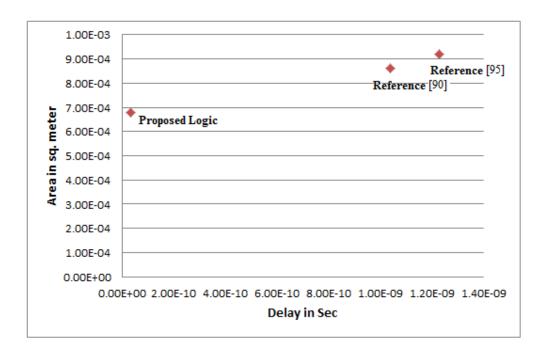

|    | 3.6.2 AREA PERFORMANCES                                    | 67 |

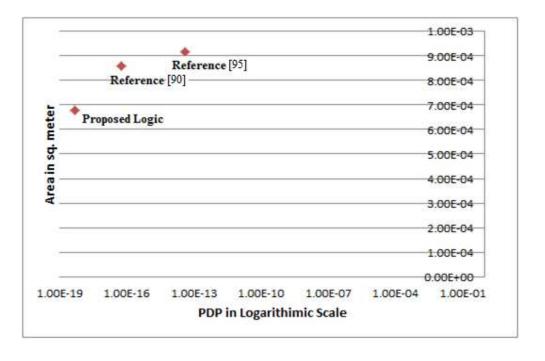

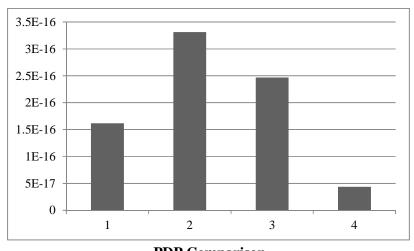

|    | 3.6.3 PDP PERFORMANCE                                                     | 70  |

|----|---------------------------------------------------------------------------|-----|

|    | 3.6.4 SIMULATION RESULTS USING 65 nm TECHNOLOGY                           | 73  |

|    | 3.7 LEAKAGE CURRENT COMPARISON                                            | 74  |

|    | 3.8 KEEPER OPTIMIZATION                                                   | 76  |

|    | 3.9 IMPLEMENTATION OF PROPOSED LOGIC IN DIFFERENT LOGIC FUNCTIONS         | 78  |

|    | 3.10 COMPARISON IN DIFFERENT CORNER PROCESSES                             | 81  |

|    | 3.10.1 CORNERS                                                            | 81  |

|    | 3.10.2 PDP ANALYSIS OF THE PROPOSED CIRCUIT BY DIFFERENT CORNER PROCESSES | 82  |

|    | 3.11 STATISTICAL ANALYSIS OF PROPOSED CIRCUIT                             | 83  |

|    | 3.11.1 WORKING OF MONTE-CARLO SIMULATION                                  | 83  |

|    | 3.11.2 POWER DISSIPATION ANALYSIS BY MONTE-CARLO METHOD                   | 85  |

|    | 3.11.3 DELAY ANALYSIS BY MONTE-CARLO METHOD                               | 86  |

|    | 3.11.4 POWER DISSIPATION VS. DELAY WITH MONTE-CARLO SIMULATION            | 88  |

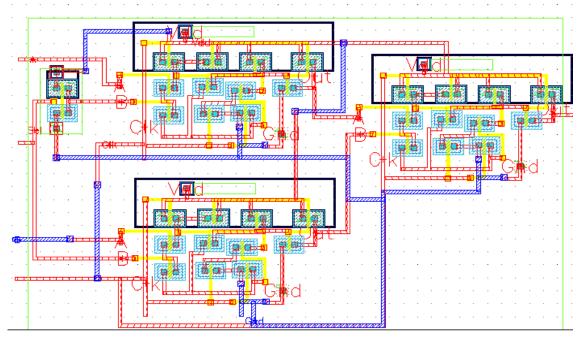

|    | 3.12 SEQUENTIAL CIRCUIT IMPLEMENTATION USING PROPOSED LOGIC               | 89  |

|    | 3.12.1 BASIC CMOS FLIP-FLOP                                               | 89  |

|    | 3.12.2 SDER FLIP-FLOP                                                     | 90  |

|    | 3.12.3 SCCER FLIP-FLOP                                                    | 91  |

|    | 3.12.4 PROPOSED FF                                                        | 91  |

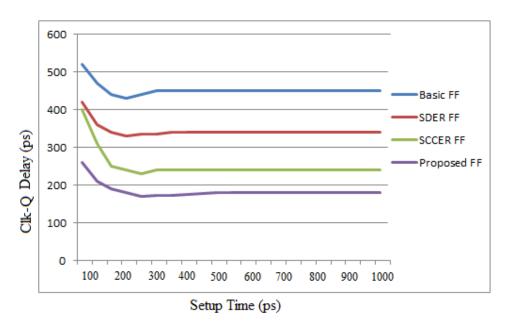

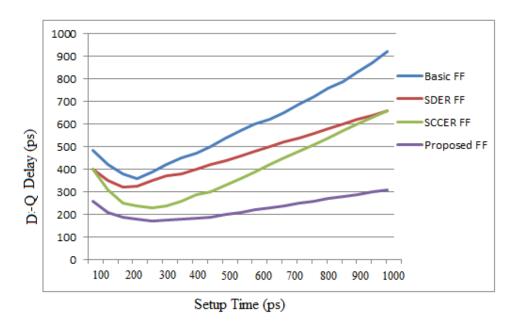

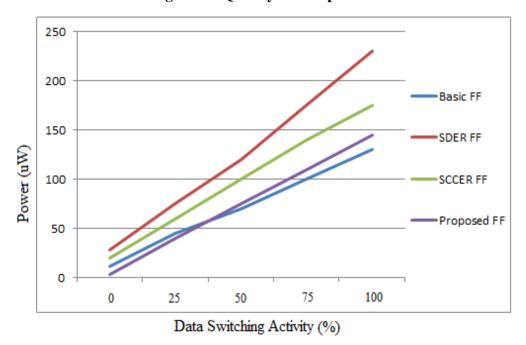

|    | 3.12.5 SIMULATION RESULT FOR PROPOSED FF                                  | 92  |

|    | 3.12.6 SIMULATION RESULTS AND COMPARISON OF PROPOSED FF WITH OTHER FFS    | 93  |

|    | 3.13 CONCLUSION                                                           | 96  |

| 4. | NOISE ANALYSIS                                                            | 98  |

|    | 4.1 INTRODUCTION                                                          | 98  |

|    | 4.2 SOURCES OF NOISE IN DOMINO CMOS LOGIC CIRCUITS                        | 99  |

|    | 4.2.1 INTERNAL GATE NOISES                                                | 99  |

|    | 4.2.2 EXTERNAL NOISES                                                     | 99  |

|    | 4.3 OR GATE IMPLEMENTATION IN PROPOSED DOMINO LOGIC                       | 100 |

|    | 4.3.1 DESCRIPTION                                                 | 101 |

|----|-------------------------------------------------------------------|-----|

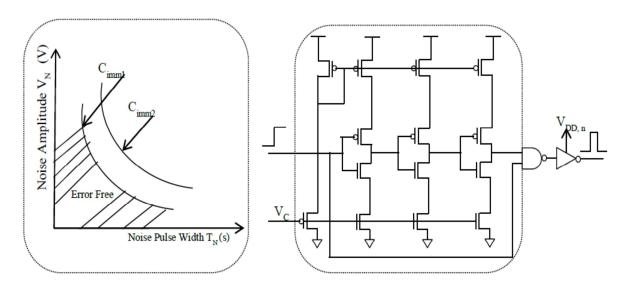

|    | 4.4 NOISE TOLERANCE PERFORMANCE                                   | 102 |

|    | 4.4.1 NOISE INJECTION CIRCUIT (NIC)                               | 102 |

|    | 4.5 UNITY NOISE GAIN (UNG)                                        | 103 |

|    | 4.5.1 UNG COMPARISON UNDER DIFFERENT CORNER PROCESSES             | 107 |

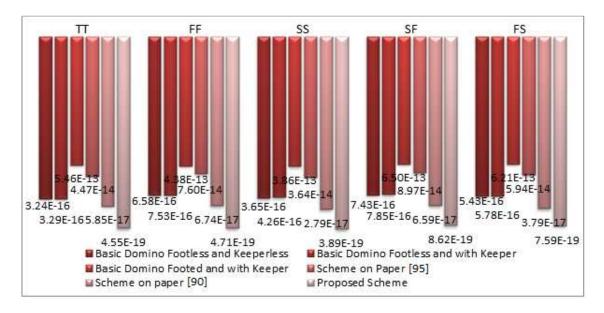

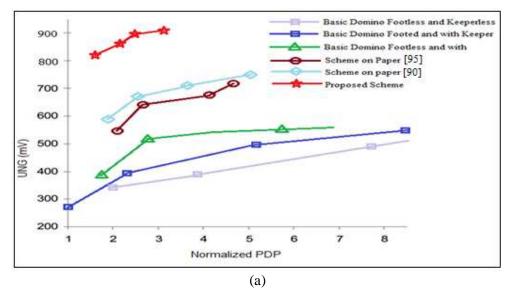

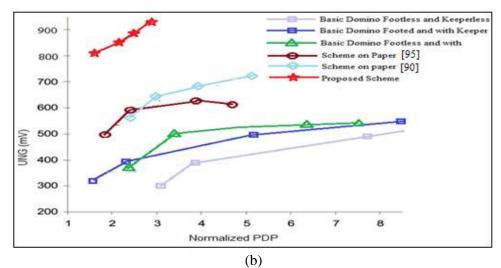

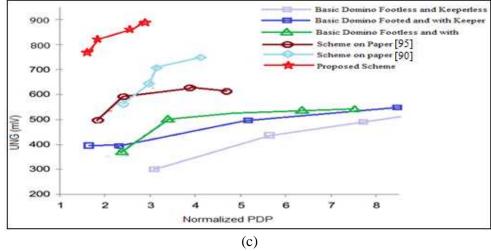

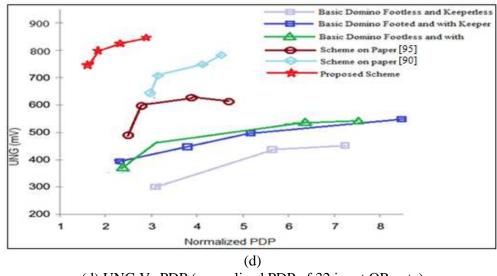

|    | 4.5.2 UNG COMPARISON AGAINST PDP                                  | 108 |

|    | 4.6 AVERAGE NOISE THRESHOLD ENERGY (ANTE)                         | 110 |

|    | 4.6.1 AVERAGE NOISE THRESHOLD ENERGY NOISE REJECTION CURVES       | 112 |

|    | 4.7 CONCLUSION                                                    | 112 |

| 5. | . APPLICATIONS OF PROPOSED DOMINO LOGIC                           | 114 |

|    | 5.1 ADDERS                                                        | 114 |

|    | 5.2 PREVIOUS PROPOSED ADDERS                                      | 115 |

|    | 5.2.1 CONVENTIONAL STATIC CMOS FULL ADDER CELL                    | 115 |

|    | 5.2.2 CONVENTIONAL DYNAMIC FULL ADDER CELL                        | 116 |

|    | 5.2.3 COMPLEMENTARY PASS-TRANSISTOR LOGIC (CPL) FULL ADDER CELL   | 117 |

|    | 5.2.4 TRANSMISSION-GATES CMOS (TGCMOS) FULL ADDER CELL            | 117 |

|    | 5.2.5 14 TRANSISTORS (14T) ADDER CELL                             | 118 |

|    | 5.2.6 TRANSMISSION FUNCTION FULL ADDER CELL (TFA)                 | 119 |

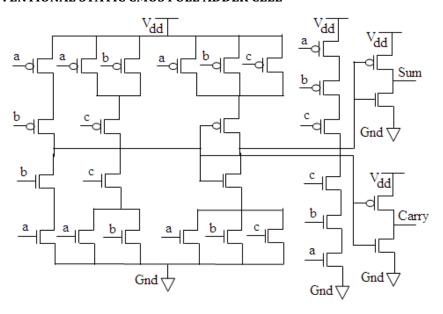

|    | 5.3 PROPOSED ADDER                                                | 120 |

|    | 5.4 COMPARISON RESULTS                                            | 124 |

|    | 5.4.1 POWER-DELAY PRODUCT (PDP) PERFORMANCE                       | 124 |

|    | 5.4.2 UNITY NOISE GAIN (UNG)                                      | 127 |

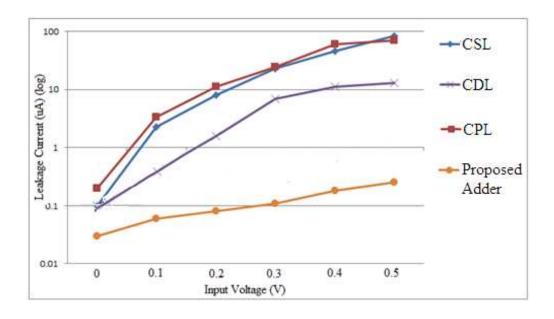

|    | 5.4.3 LEAKAGE CURRENT COMPARISON                                  | 128 |

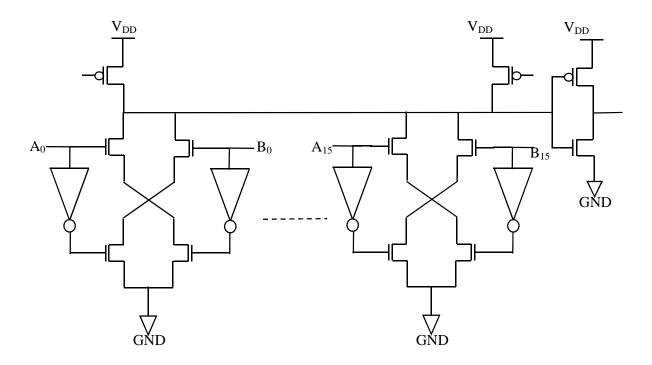

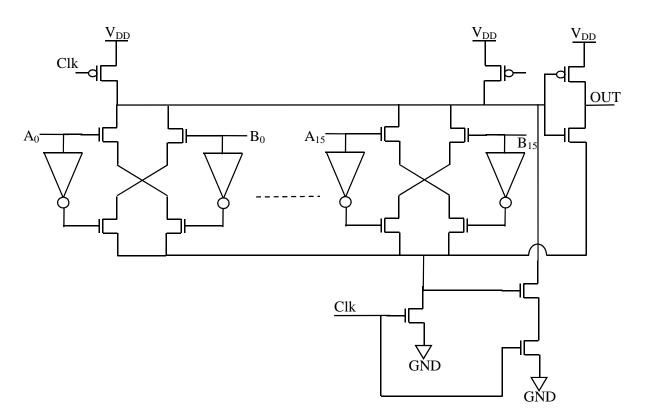

|    | 5.5 DIGITAL COMPARATOR DESIGN BY PROPOSED LOGIC DESIGN            | 129 |

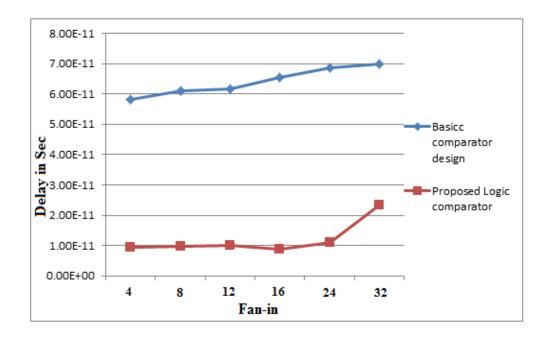

|    | 5.5.1 COMPARISON OF THE PROPOSED COMPARATOR WITH BASIC COMPARATOR | 131 |

|    | 5.6 CONCLUSION                                                    | 135 |

| 6  | LAYOUT OF TEST CHIP                                               | 136 |

|    | 6.1 INTRODUCTION                                    | 136 |

|----|-----------------------------------------------------|-----|

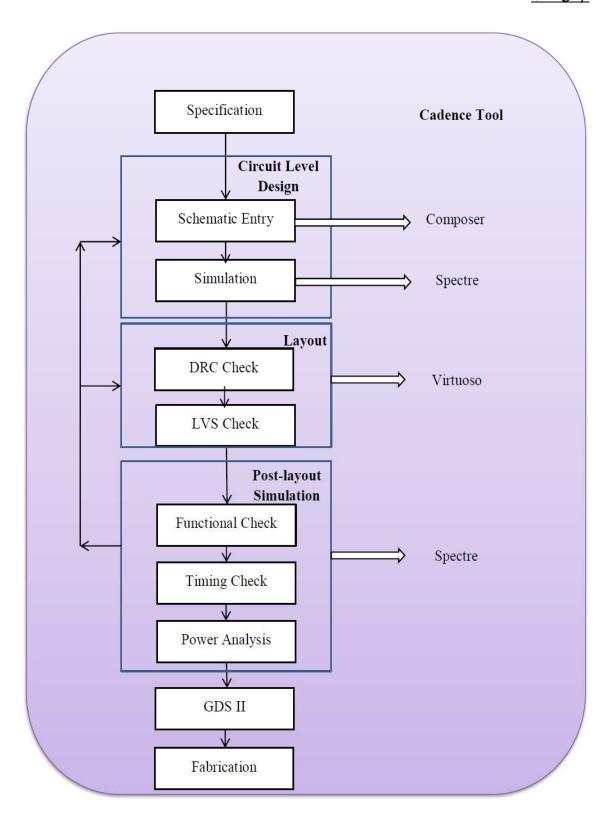

|    | 6.2 ANALOG IC DESIGN FLOW                           | 136 |

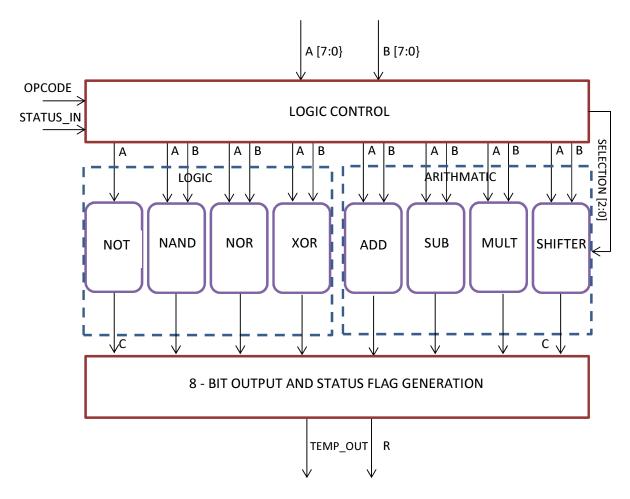

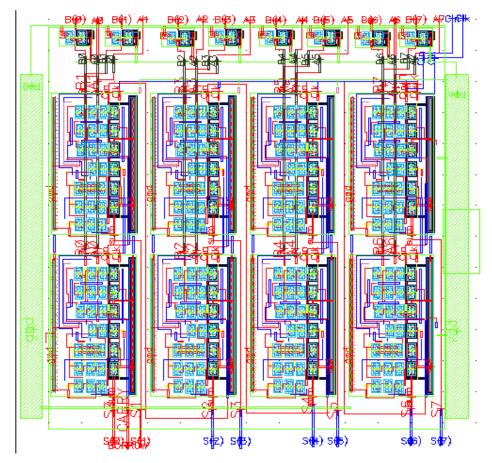

|    | 6.3 ALU ARCHITECTURE:                               | 138 |

|    | 6.3.1 DESIGN SPECIFICATIONS:                        | 138 |

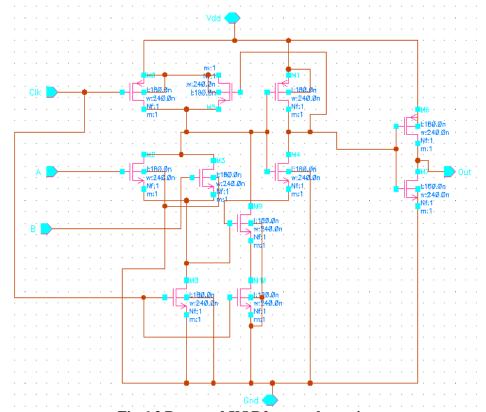

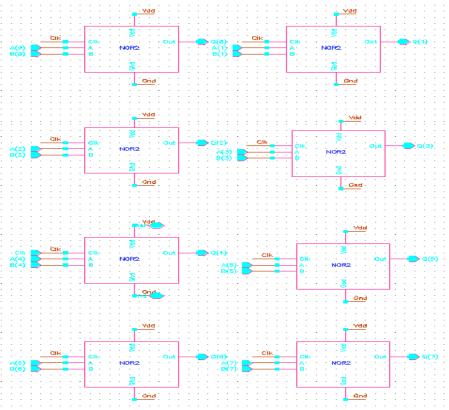

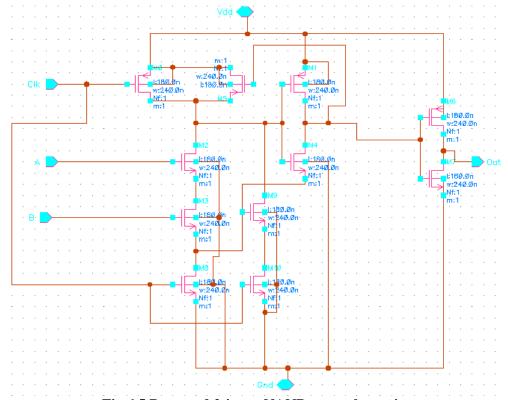

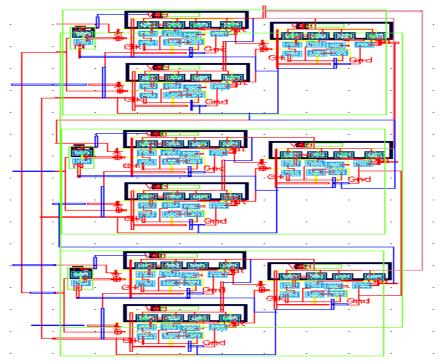

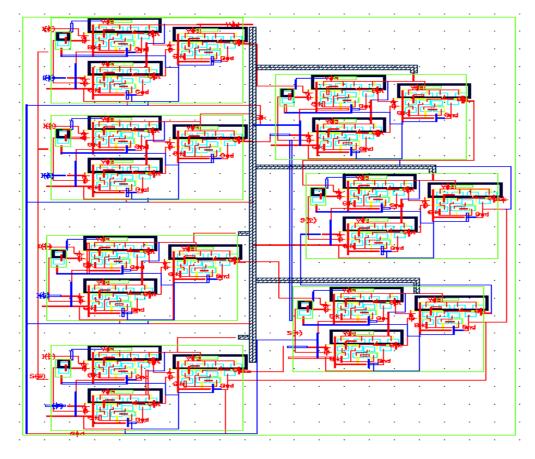

|    | 6.3.2 SCHEMATIC & SIGNAL OF ALL THE INTERNAL BLOCKS | 139 |

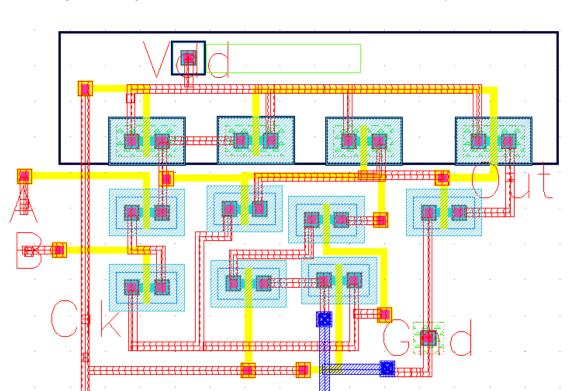

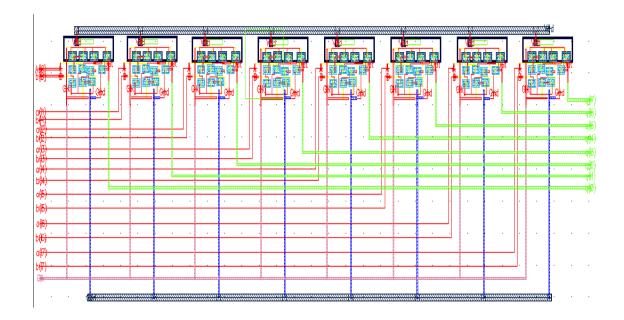

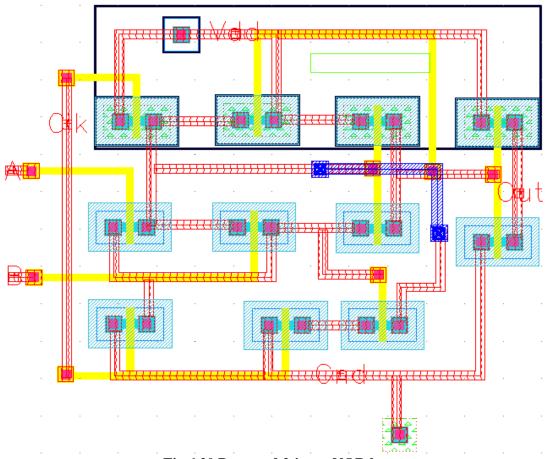

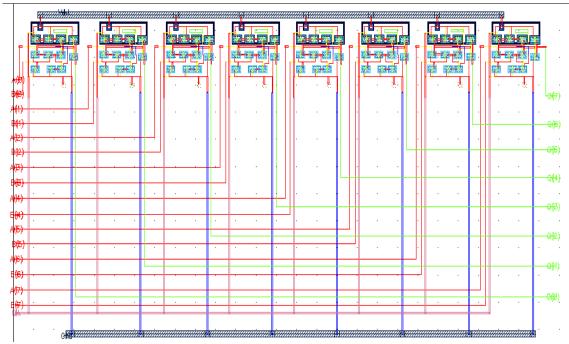

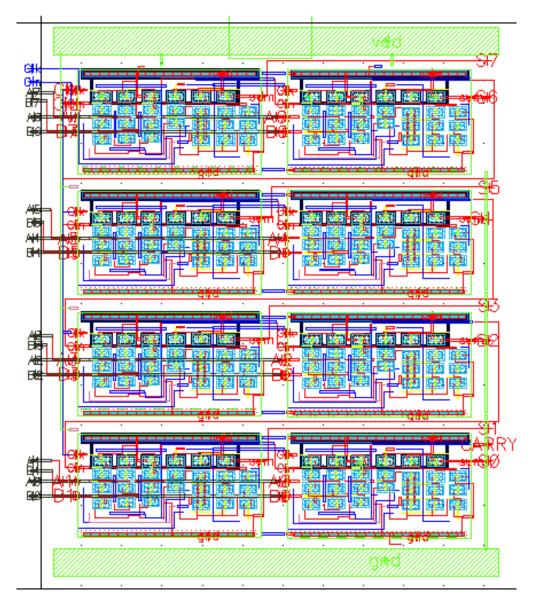

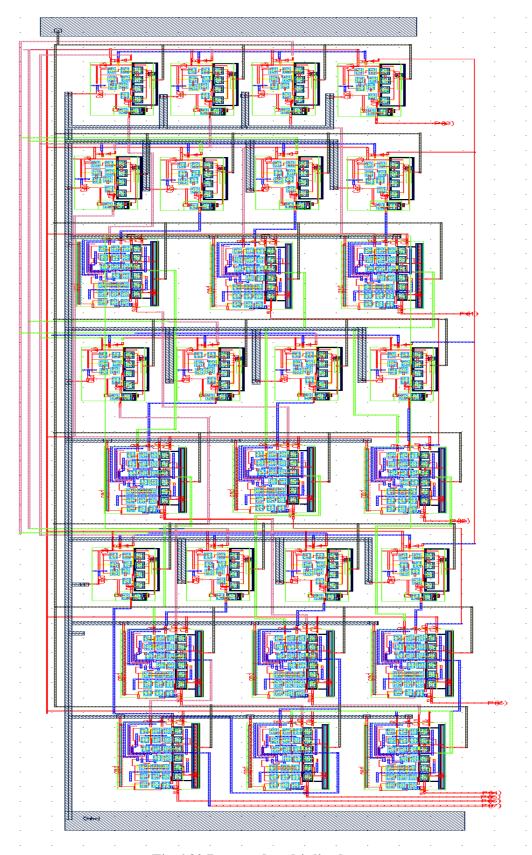

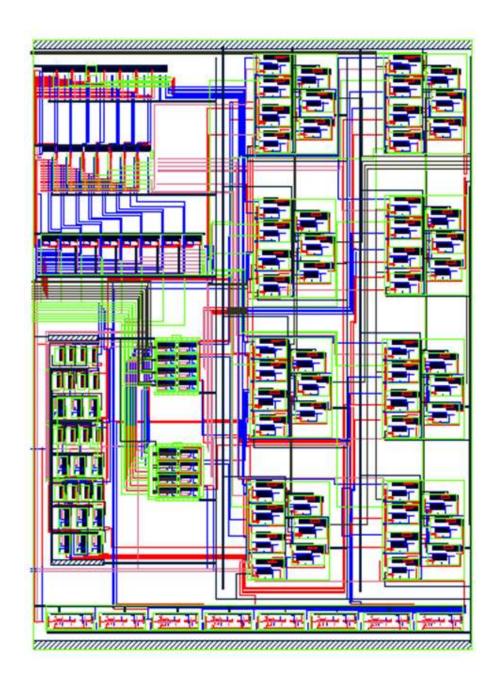

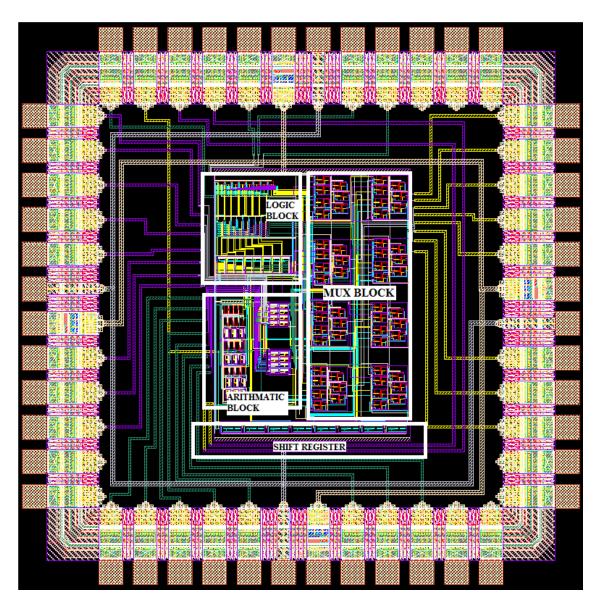

|    | 6.3.3 LAYOUT OF PROPOSED ALU                        | 149 |

|    | 6.3.4 CREATING I/O PINS                             | 158 |

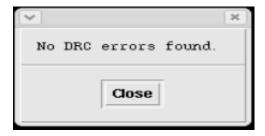

|    | 6.3.5 DRC CHECK                                     | 159 |

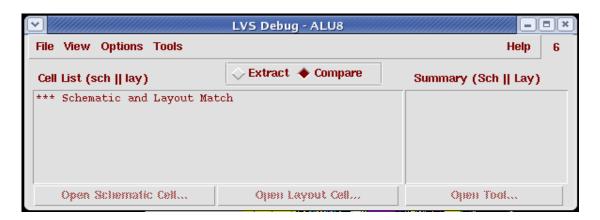

|    | 6.3.6 LVS CHECK                                     | 159 |

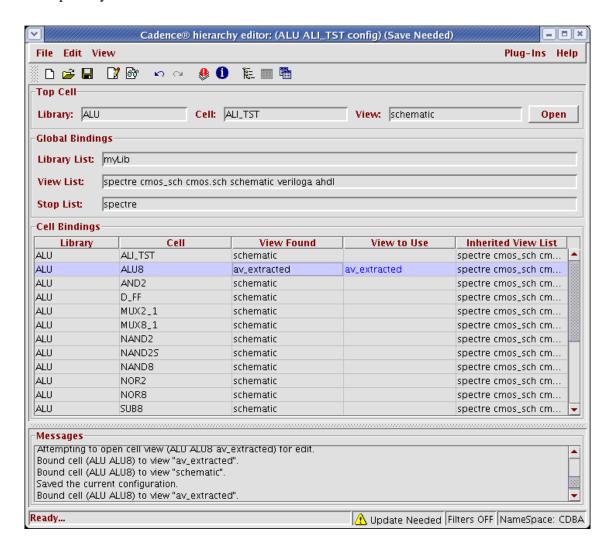

|    | 6.3.7 PARASITIC EXTRACTION                          | 160 |

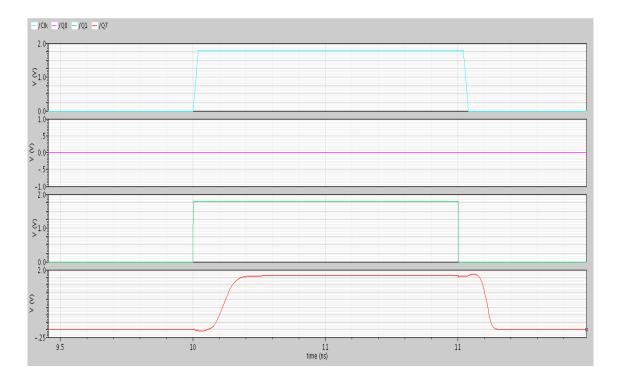

|    | 6.3.8 POST LAYOUT SIMULATION & PERFORMANCE ANALYSIS | 160 |

|    | 6.3.9 PADDING AND CONNECTIONS                       | 166 |

|    | 6.4 CONCLUSION                                      | 166 |

| 7. | CONCLUSIONS AND FUTURE WORK                         | 168 |

|    | 7.1 SUMMARY OF CONTRIBUTIONS                        | 168 |

|    | 7.2 FUTURE WORK                                     | 169 |

| ВІ | BLIOGRAPHY                                          | 171 |

| DI | IRLICATIONS                                         | 100 |

# **LIST OF FIGURES**

| Fig.1.1 Switching and short-circuit current elements in static CMOS                              | 3     |

|--------------------------------------------------------------------------------------------------|-------|

| Fig. 2.1(a) CMOS logic gates as a combination of PUN and PDN (b) CMOS inverter [25]              | 9     |

| Fig. 2.2 Pseudo-NMOS logic                                                                       | 10    |

| Fig. 2.3 Static Pass-transistor logic                                                            | 11    |

| Fig.2.4 Static Complementary-PTL                                                                 | 12    |

| Fig.2.5 Gate-Diffusion-Input logic                                                               | 13    |

| Fig.2.6 Dynamic logic                                                                            | 14    |

| Fig.2.7 Charge leakage                                                                           | 16    |

| Fig.2.8 Charge sharing                                                                           | 16    |

| Fig.2.9 Capacitive coupling                                                                      | 17    |

| Fig. 2.10 Clock feed-through                                                                     | 18    |

| Fig.2.11 Domino CMOS Logic                                                                       | 19    |

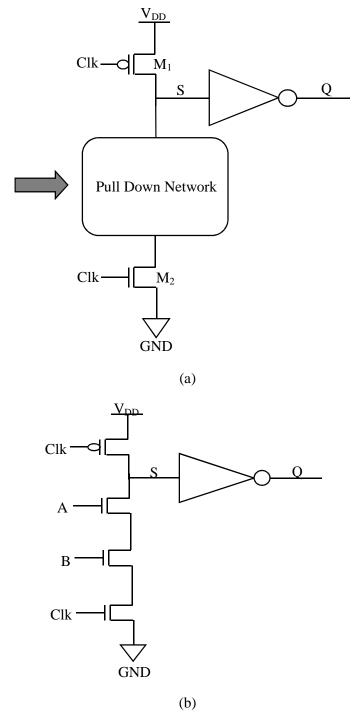

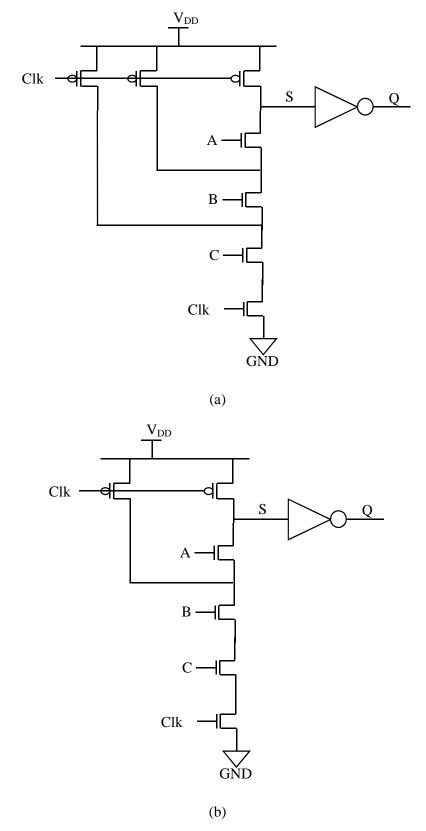

| Fig.2.12 CMOS domino logic (a) Schematic of domino circuit (b) Schematic of 2 - input domino A   | ND    |

| gategate                                                                                         | 20    |

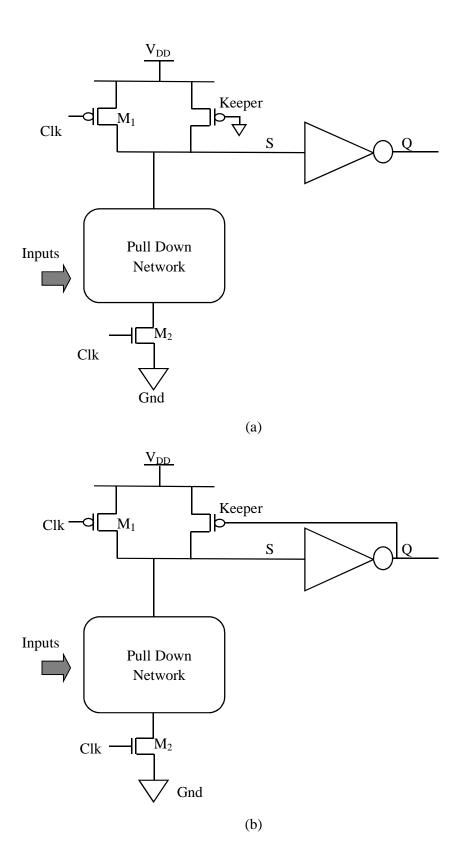

| Fig.2.13 Keeper implementation (a) Implemented as constantly ON keeper [71](b) Implemented       | as    |

| feedback keeper [72] (c) High Speed feedback keeper implementation [73](d) Conditional keeper    |       |

| implementation [75]                                                                              | 23    |

| Fig. 2.14 Implementation of optimized keeper (a) Implemented as inverter feedback (b) Implement  | nted  |

| as pseudo PMOS inverter feedback                                                                 | 24    |

| Fig.2.15 Precharging internal nodes implemented on AND3 gate, (a) Precharging every internal i   | nodes |

| [78], (b) Precharging some internal nodes [79]                                                   | 25    |

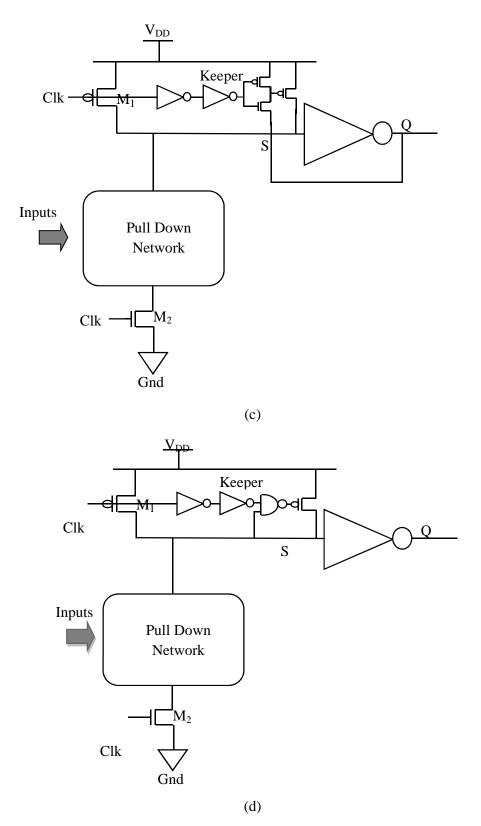

| Fig.2.16 Raising source voltage of AND2 gate, (a) PMOS pull up technique [80], (b) NMOS pull up  | )     |

| technique with feedback [81], (c) Mirror technique [82], (d) Twin transistor technique [83]      | 29    |

| Fig. 2.17 Twin transistor technique with short circuit problem, (a) A OR-AND gate, (b) OR-AND ga | ite   |

| showing direct conducting path                                                                   | 30    |

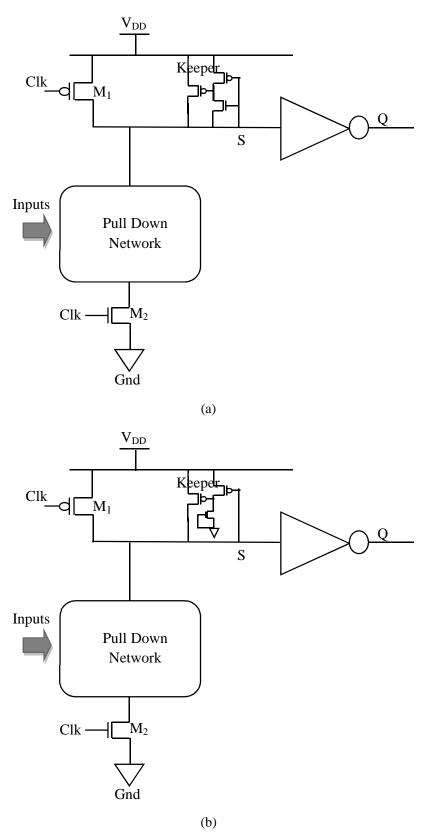

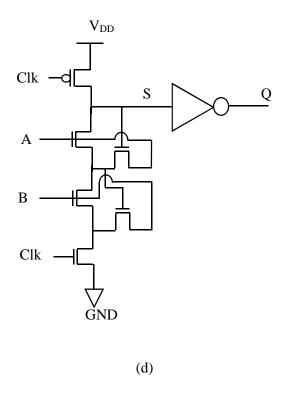

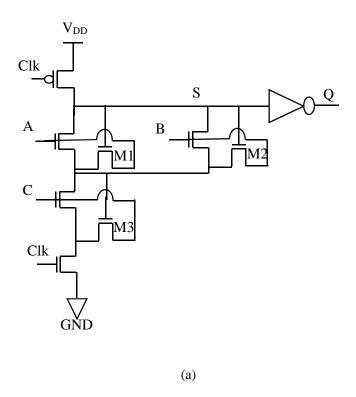

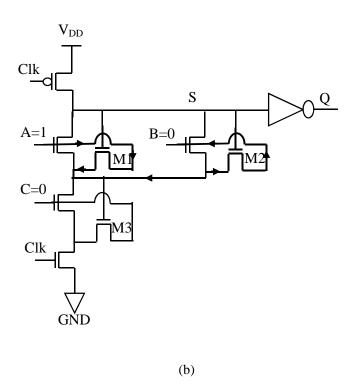

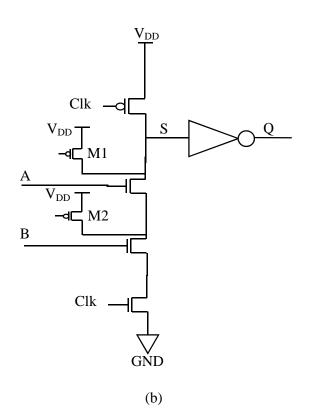

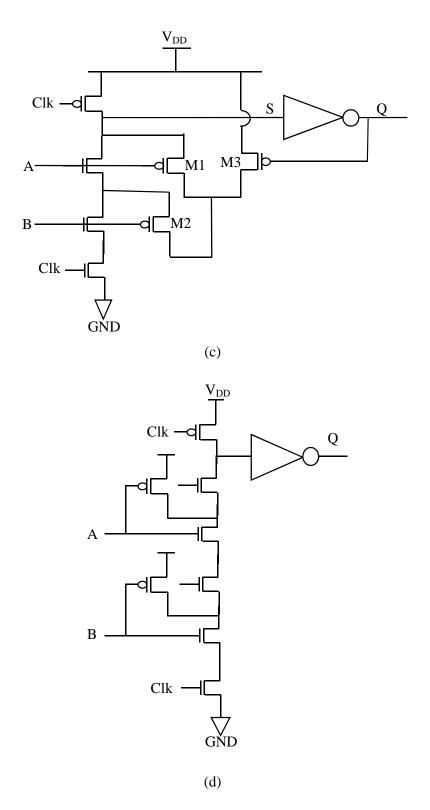

| Fig.2.18 Constructing complementary PMOS networks for AND2 gate, (a) Construction of                                                                                                                    |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| complementary PMOS network technique [85], (b) CMOS inverter technique [87], (c) Gated CMOS                                                                                                             |

| inverter technique [88], (d) Triple transistor technique [89]                                                                                                                                           |

| Fig.2.19 Short circuit problems in inverter technique, (a) A 3-input OR-AND gate, (b) Direct conducting path                                                                                            |

| Fig.2.20 SFEG dynamic logic circuit design [91] [92]36                                                                                                                                                  |

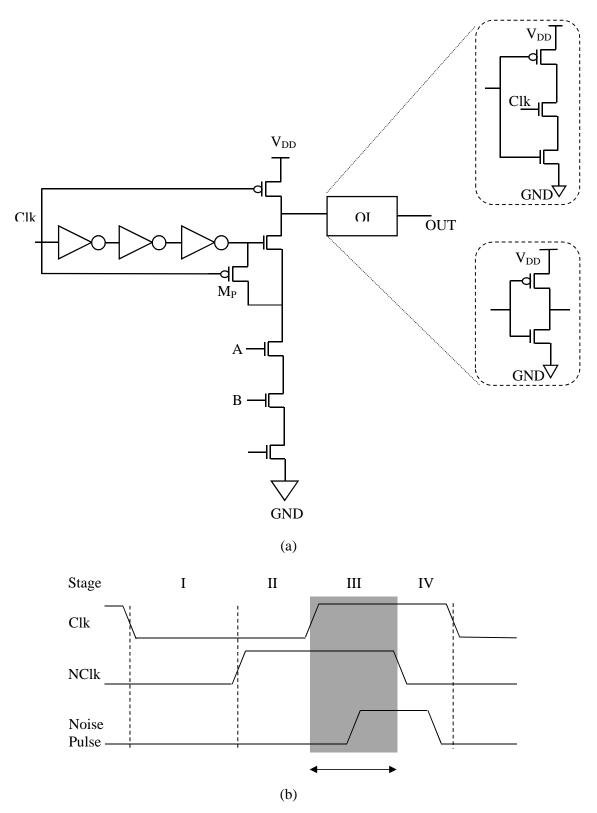

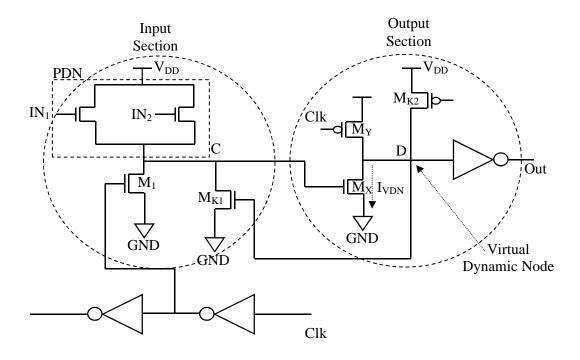

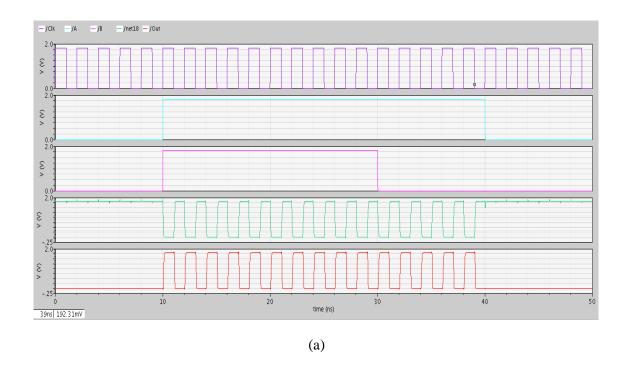

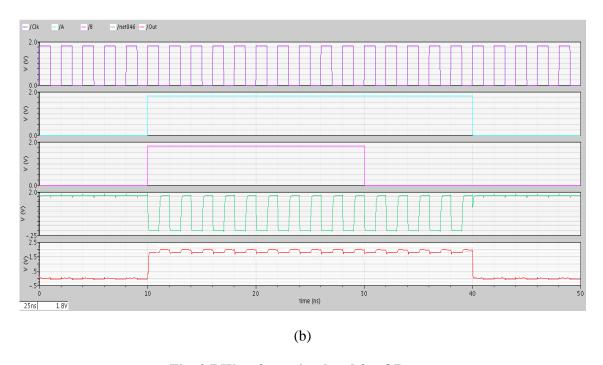

| Fig.2.21 Two-input dynamic AND-gate implemented with noise-tolerant dynamic circuit method, (a)  Gate can be domino [static output inverter (OI)] or TSPC (NC2MOS output inverter), (b) Timing  diagram |

| Fig.2.22 Modified SFEG circuit design                                                                                                                                                                   |

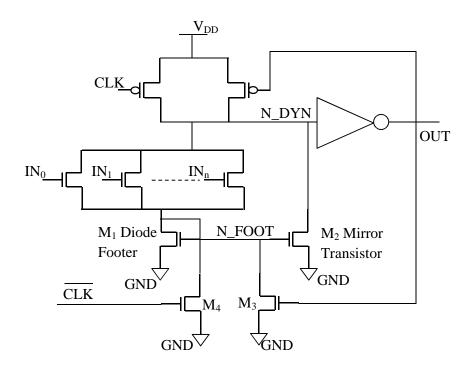

| Fig. 2.23 Diode footed Domino [95]                                                                                                                                                                      |

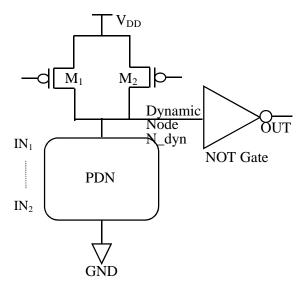

| Fig.3.1 A typical footless Domino gate41                                                                                                                                                                |

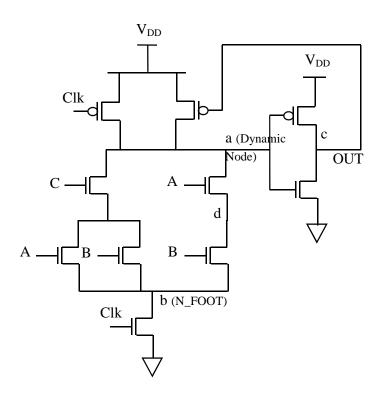

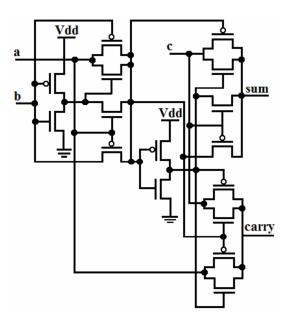

| Fig.3.2 Logic function realized with conventional domino logic                                                                                                                                          |

| Fig.3.3 Output waveforms of Clk and node a, b, c for the circuit described in Fig.3.243                                                                                                                 |

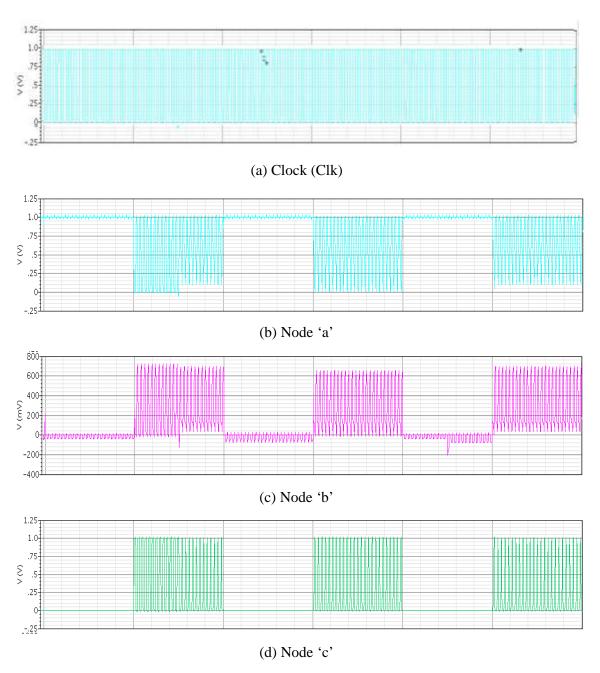

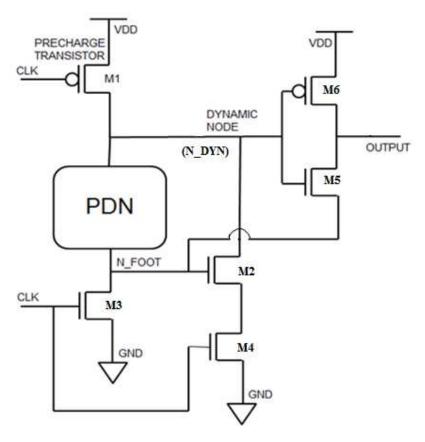

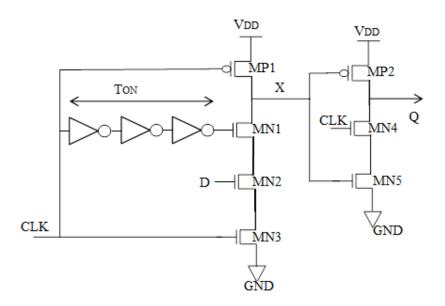

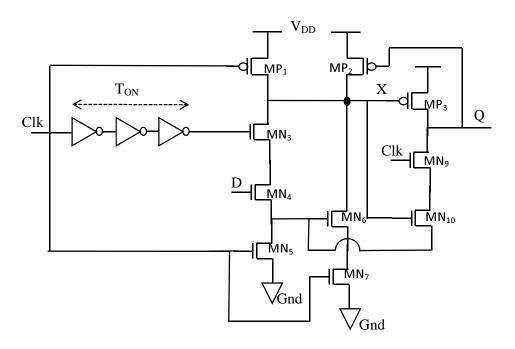

| Fig. 3.4 Proposed Circuit                                                                                                                                                                               |

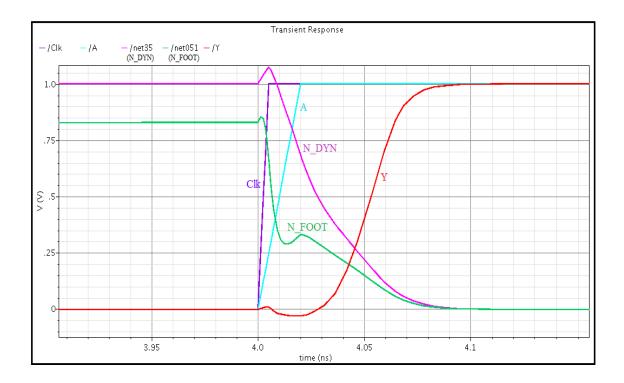

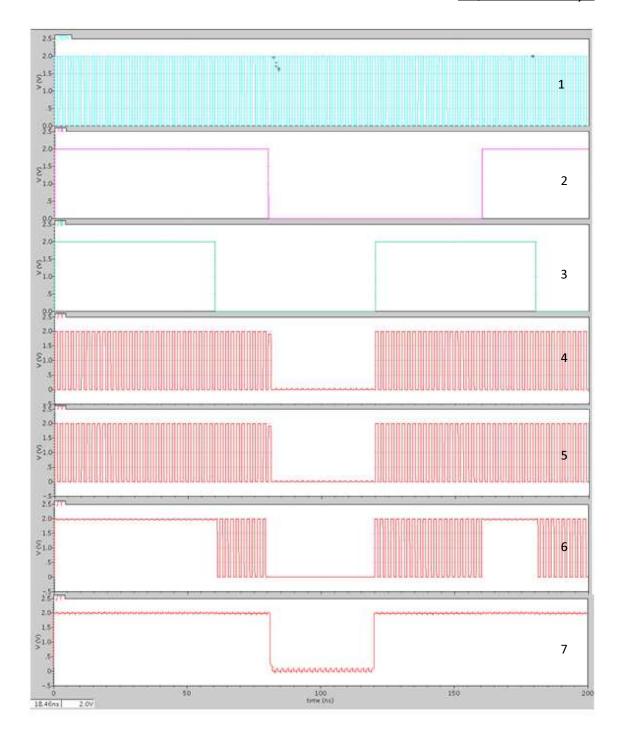

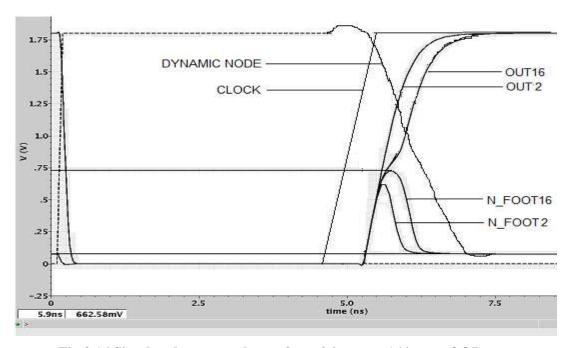

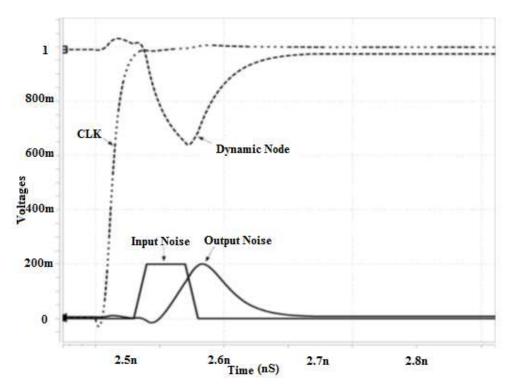

| Fig.3.5 Simulated waveform of proposed scheme                                                                                                                                                           |

| Fig.3.6 Waveform simulated for OR gate49                                                                                                                                                                |

| Fig. 3.7 Waveform simulated for OR gate50                                                                                                                                                               |

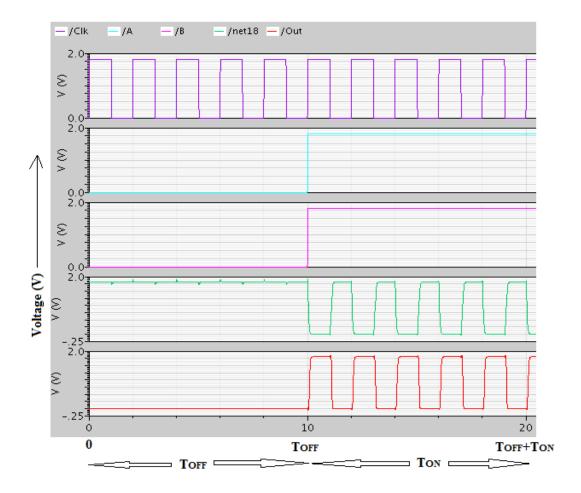

| Fig. 3.8 Waveform simulated for the basic OR gate demonstrating $T_{OFF}$ and $T_{ON}$                                                                                                                  |

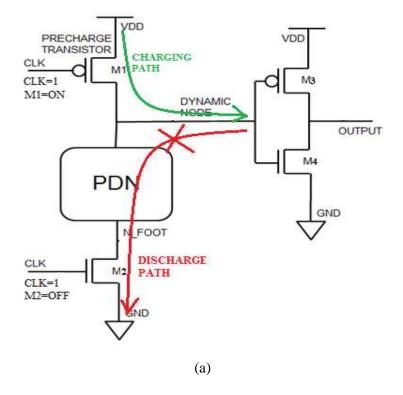

| Fig. 3.9 Domino logic circuits showing charging and dis-charging paths (a) precharging stage (b)                                                                                                        |

| evaluation stage when PDN is conducting (c) evaluation stage when PDN is non conducting                                                                                                                 |

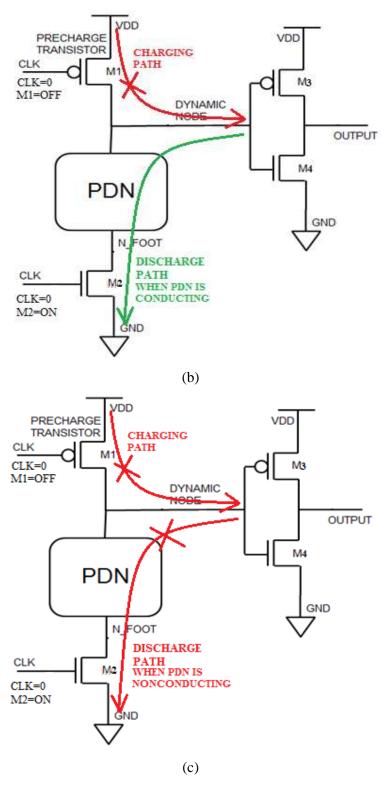

| Fig. 3.10 Current waveform simulated for 2-input OR gate                                                                                                                                                |

| Fig. 3.11 Charge sharing Problem in Domino gate58                                                                                                                                                       |

| Fig.3.12 Charge sharing problem in the proposed work59                                                                                                                                                  |

| Fig.3.13 (a) Dual $V_{DD}$ implementation (b) Increasing the channel length (c) Increasing load                                                                                                         |

| capacitance (d) Increasing the width of M <sub>3</sub> 61                                                                                                                                               |

| Fig.3.14 Keeper implementation63                                                                                                                                                                        |

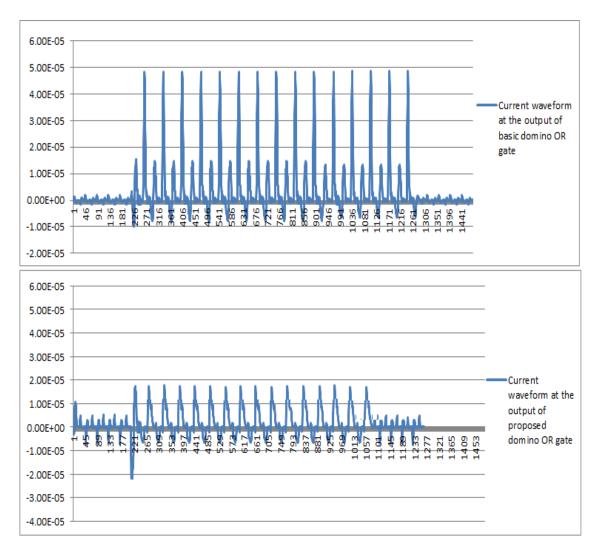

| Fig. 3.15 Proposed 2-input OR gate64                                                                                                                                                                    |

| Fig.3.16 Simulated output voltages from 2-input to 16 input of OR gate                                                                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig.3.17 Chart showing area comparison of all the logic styles with proposed logic (Simulated with 2-                                               |

| input OR- gate)68                                                                                                                                   |

| Fig.3.18 Delay vs area where the lowest point refers the proposed logic, higher and middle points                                                   |

| refer scheme on [95] and [90]69                                                                                                                     |

| Fig.3.19 PDP (logarithmic scale) vs area where the lowest point refers the proposed logic, higher and middle points refer scheme on [95] and [90]69 |

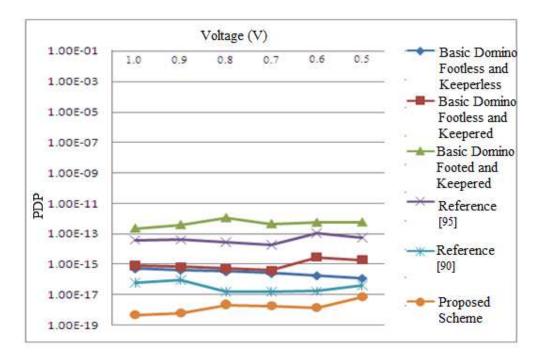

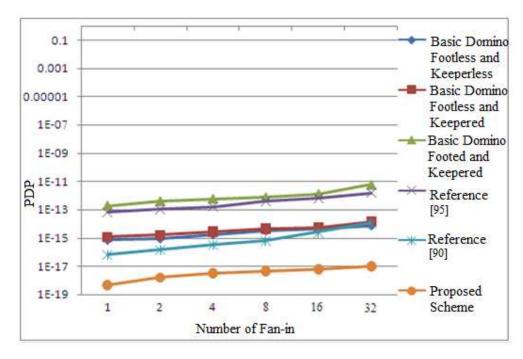

| Fig.3.20 PDP Plot for the proposed scheme with the other schemes by reducing $V_{DD}$ from 1.0 V to 0.5V                                            |

| Fig.3.21 Simulation of OR-gate PDP Plot comparision for the proposed scheme with the other                                                          |

| schemes by increasing the fan-in upto 32 bit                                                                                                        |

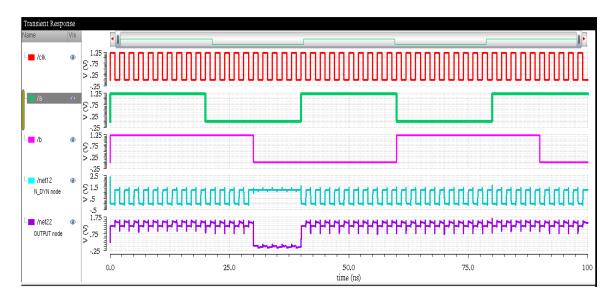

| Fig. 3.22 Simulation output of 2-input OR gate using $V_{\rm DD}$ =1.2 V and in 65 nm technology73                                                  |

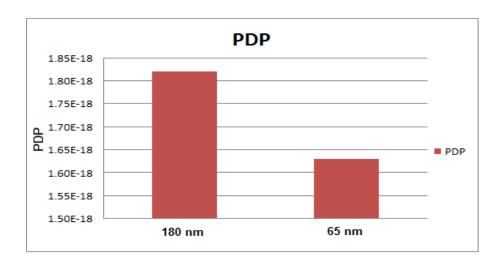

| Fig. 3.23 PDP performance of 2-input OR gate using 180 and 65 nm technologies74                                                                     |

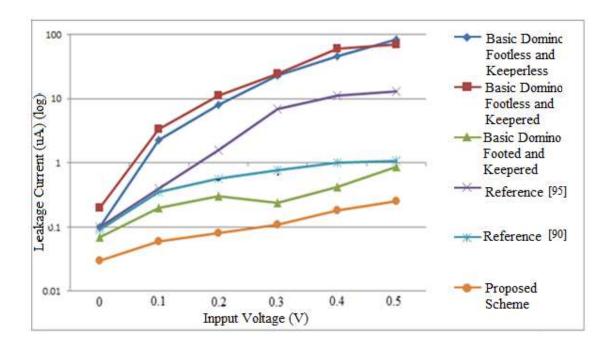

| Fig.3.24 Leakage currents of the analyzed techniques as a function of input voltage for 16-input OR-                                                |

| gate                                                                                                                                                |

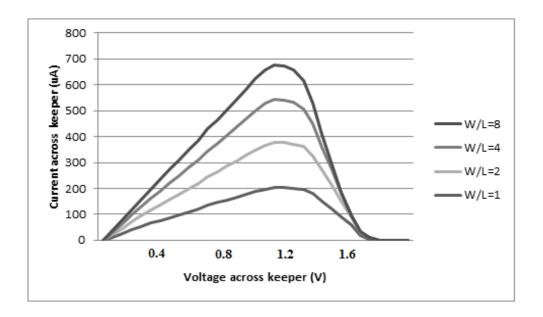

| Fig.3.25 I-V characteristics of feedback keeper with different W/L ratio77                                                                          |

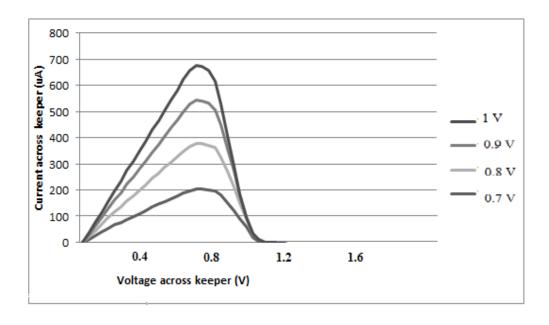

| Fig. 3.26 I-V characteristics of feedback keeper with different value of $V_{DD}$                                                                   |

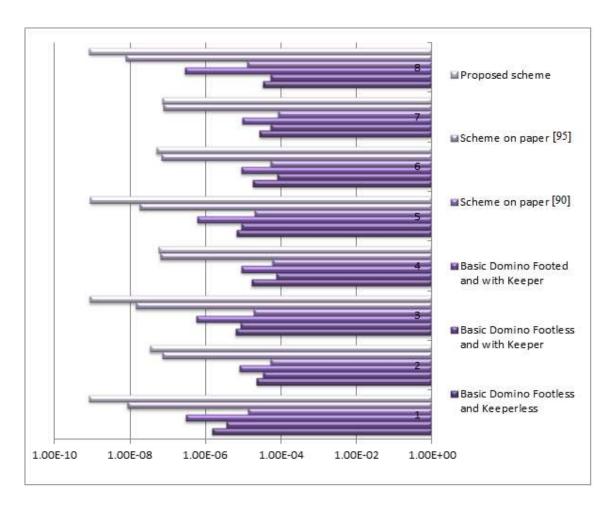

| Fig.3.27 Graphical representation of power dissipation comparison with different logic function and                                                 |

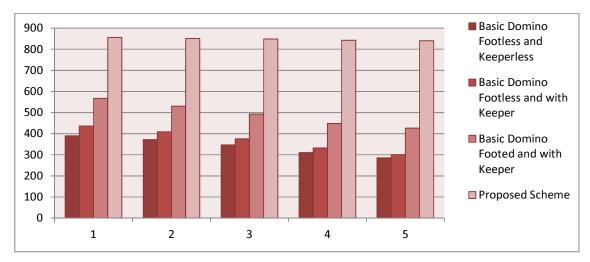

| proposed scheme                                                                                                                                     |

| Fig.3.28 Graphical representation of circuit delay comparison with different logic functions and the                                                |

| proposed scheme                                                                                                                                     |

| Fig.3.29 Simulated PDP output of different logic style compared with the proposed logic style in                                                    |

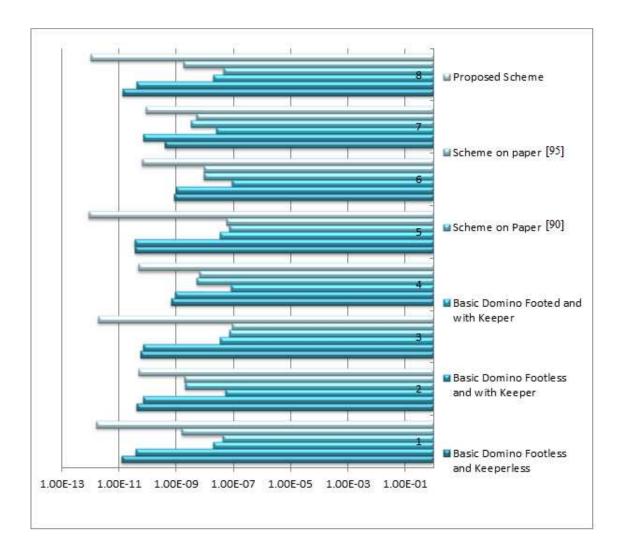

| different corner Processes (Simulated with 2-input OR gate)82                                                                                       |

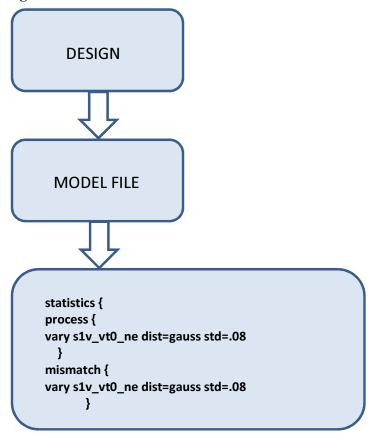

| Fig.3.30 Difference between normal simulation and Monte-Carlo simulation84                                                                          |

| Fig. 3.31 Procedure of Monte Carlo on cadence84                                                                                                     |

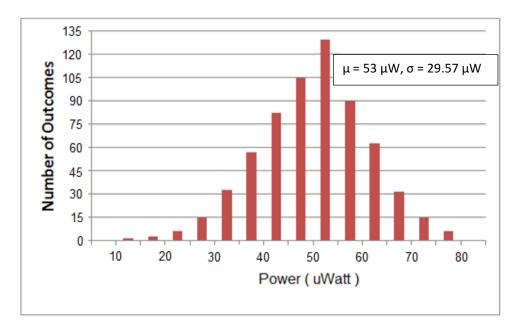

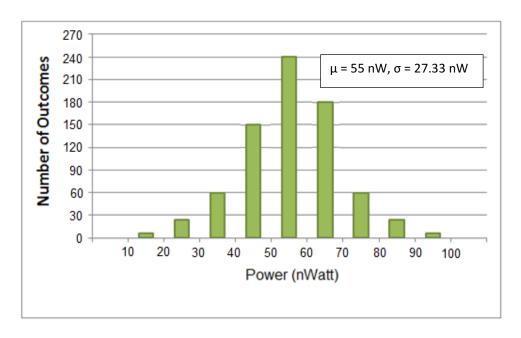

| Fig.3.32 The histogram of power dissipation of basic domino logic simulated with 2-input OR-gate and 1.8 V for N = 1000                             |

| Fig.3.33 The histogram of power dissipation of proposed domino logic simulated with 2-input OR-                                                     |

| gate and 1.8 V for N = 100086                                                                                                                       |

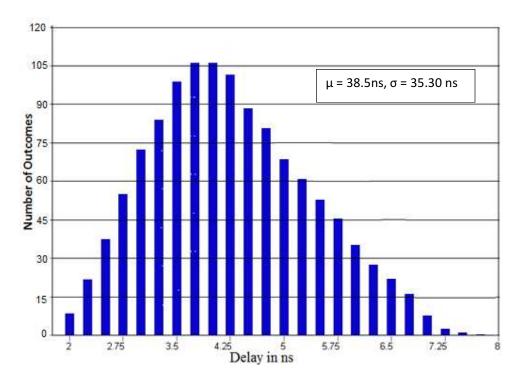

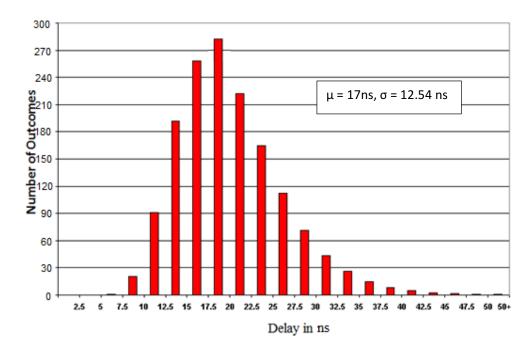

| Fig.3.34 The histogram of delay of basic domino logic simulated with 2-input OR-gate and 1.8 V j           | for N |

|------------------------------------------------------------------------------------------------------------|-------|

| = 1000                                                                                                     | 87    |

| Fig.3.35 The histogram of delay of proposed domino logic simulated with 2-input OR-gate and 1.             |       |

| for N = 1000                                                                                               | 87    |

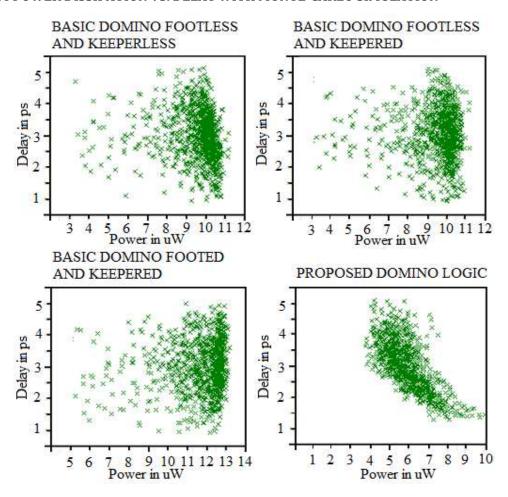

| Fig.3.36 The scattered output of power dissipation Vs. Delay for basic domino logics and propose           |       |

| domino logic simulated with 2- input OR - gate and 1.8 V for N = 10000                                     | 88    |

| Fig.3.37 Basic dynamic FF [118]                                                                            | 89    |

| Fig. 3.38 SDER FF [119]                                                                                    | 90    |

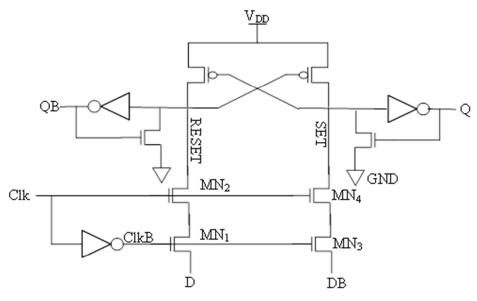

| Fig. 3.39 SCCER FF [119]                                                                                   | 90    |

| Fig. 3.40 Proposed FF                                                                                      | 91    |

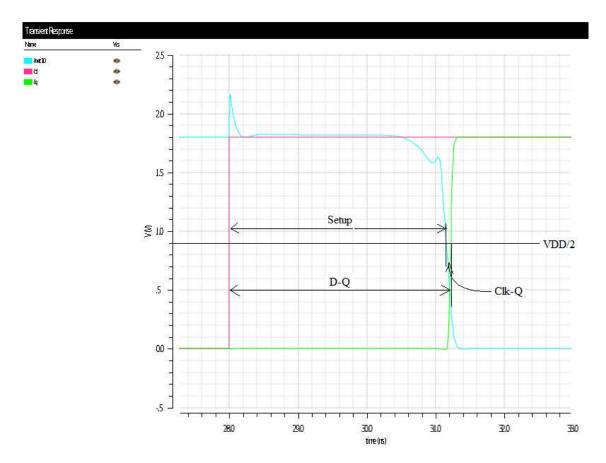

| Fig.3.41 Proposed FF output illustrating timing definitions                                                | 93    |

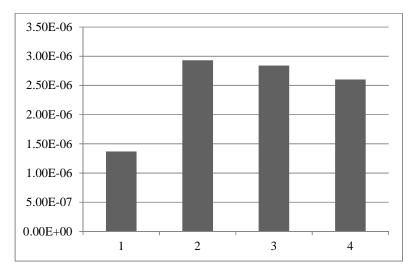

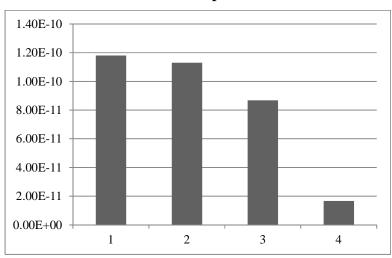

| Fig.3.42 Power, delay and PDP comparison of all FFs                                                        | 94    |

| Fig.3.43 Clk-Q Delay Vs Setup Time                                                                         | 95    |

| Fig.3.44 D-Q Delay Vs Setup Time                                                                           | 96    |

| Fig.3.45 Power Vs Data Switching Activity at 50 MHz                                                        | 96    |

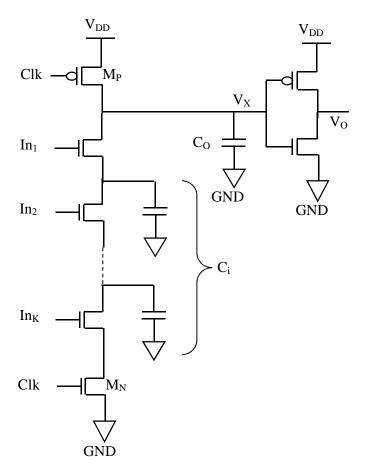

| Fig.4.1 Novel 2-input OR gate designed with the proposed domino logic                                      | 100   |

| Fig.4.2 (a) Noise immunity curve [124] (b) NIC [87]                                                        | 102   |

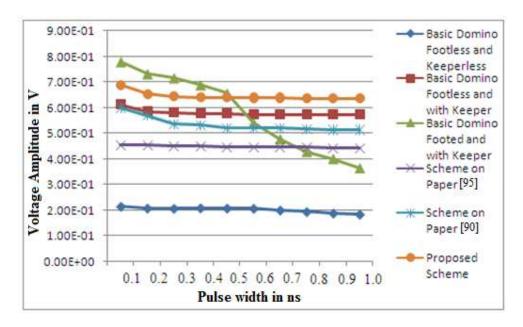

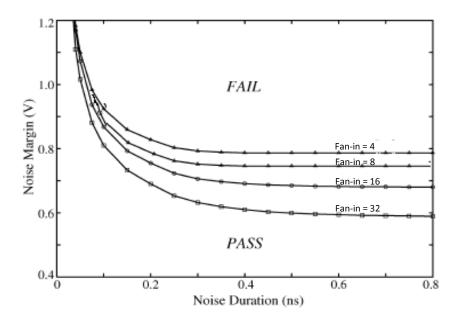

| Fig.4.3 UNG-delay curves for domino 2-input OR gates                                                       | 103   |

| Fig.4.4 UNG comparison in case of different fan-in for wide dynamic OR gates                               | 105   |

| Fig.4.5 UNG Vs. PDP for all the techniques with different number of fan-in                                 | 110   |

| Fig.4.6 Plot for Noise Voltage Vs Noise Pulse Width for 2-input OR gate with $V_{\rm DD}$ =1 for different |       |

| domino logic along with the proposed scheme                                                                | 110   |

| Fig.4.7 Plot for calculated ANTE Vs Noise Pulse Width for 2-input OR gate with $V_{DD}$ =1 for different   | t     |

| domino logic along with the proposed scheme                                                                | 111   |

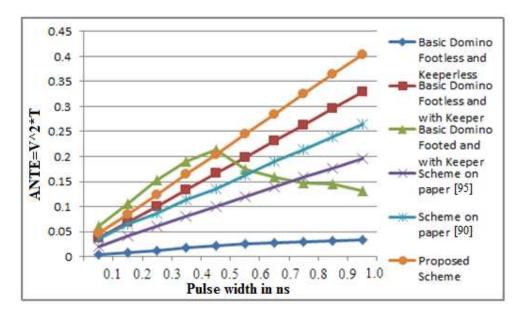

| Fig.4.8 The dynamic noise rejection curves of proposed circuit with different fan-in                       | 112   |

| Fig.5.1 Conventional static logic full adder circuit (CSL) [134]                                           | 115   |

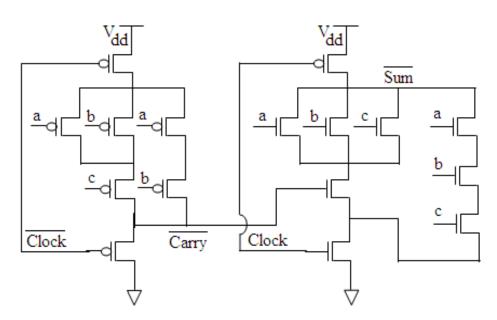

| Fig.5.2 Conventional dynamic logic full adder circuit (CDL) [29]                                           | 116   |

| Fig.5.3 Complementary passtransistor logic (CPL) [1]                                                       | 117   |

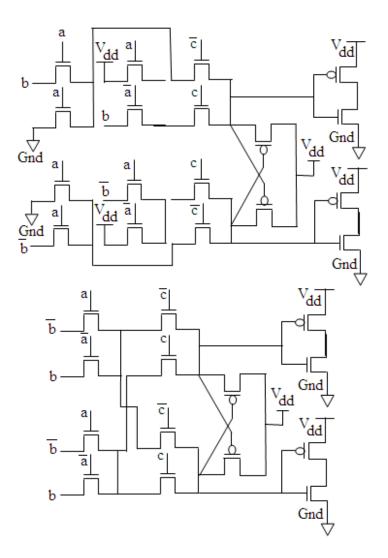

| Fig.5.4 Transmission gate CMOS full adder circuit (TGCMOS) [127]                      | 118             |

|---------------------------------------------------------------------------------------|-----------------|

| Fig.5.5 14 Transistor CMOS full adder circuit (14TCMOS) [128]                         | 118             |

| Fig.5.6 Transmission function full adder circuit (TFA) [129]                          | 119             |

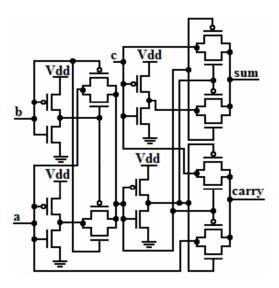

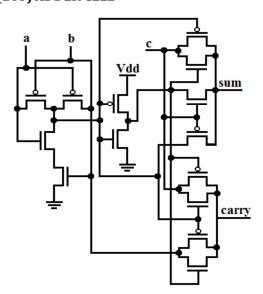

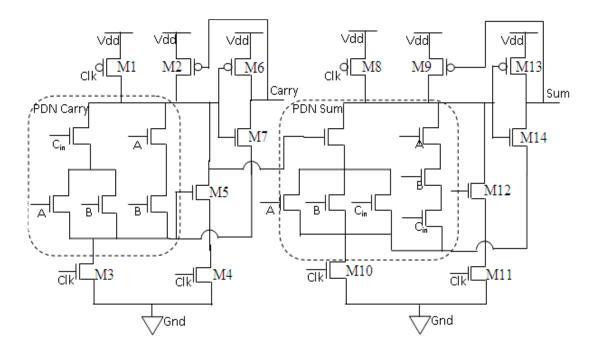

| Fig. 5.7 Proposed full adder                                                          | 121             |

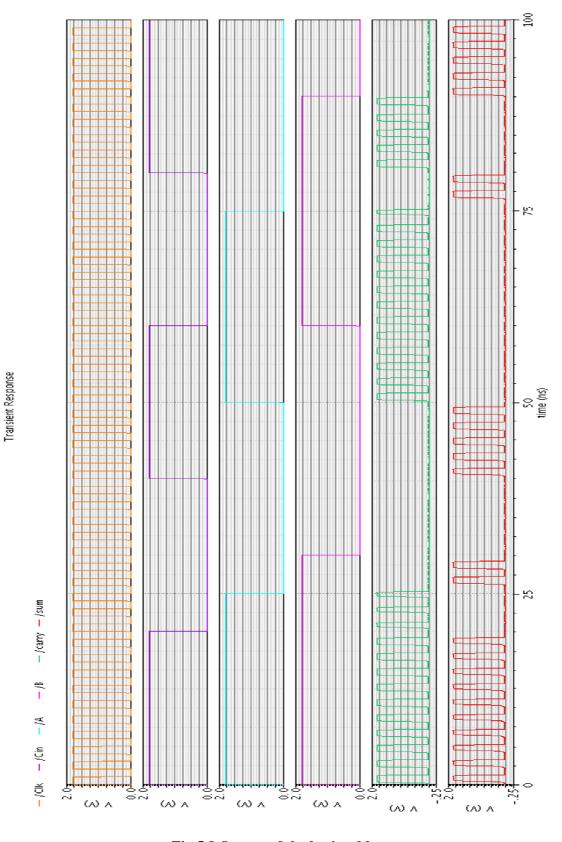

| Fig.5.8 Output of the basic adder                                                     | 122             |

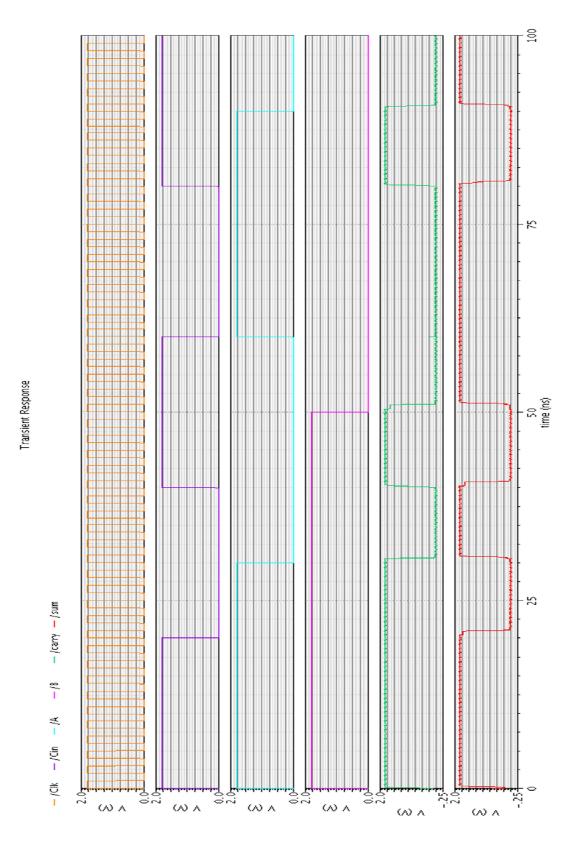

| Fig.5.9 Output of the proposed adder                                                  | 123             |

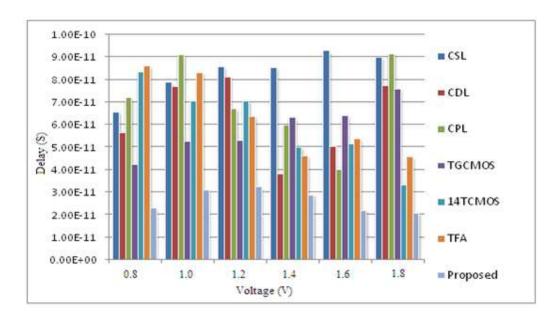

| Fig.5.10 Delay comparison (Varying the supply voltage)                                | 124             |

| Fig.5.11 Power comparison (Varying the $V_{DD}$ )                                     | 125             |

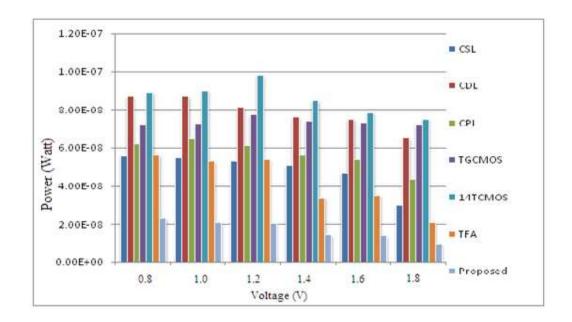

| Fig.5.12 Power-delay product (PDP) comparison (Varying the supply voltage)            | 125             |

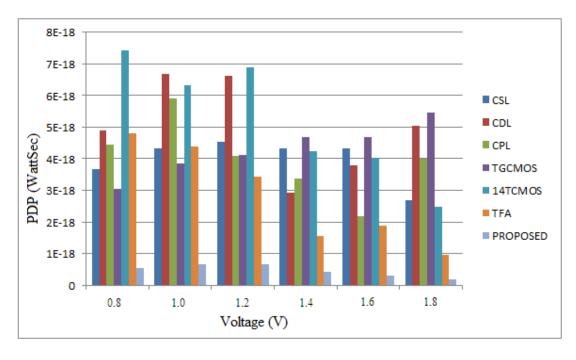

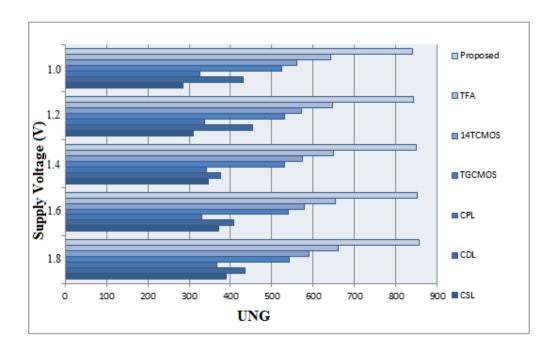

| Fig.5.13 UNG comparison (Varying supply voltage)                                      | 127             |

| Fig.5.14 Leakage currents comparison of the analyzed techniques with conventional tec | chniques for 1- |

| bit adderbit adder                                                                    | 128             |

| Fig.5.15 Basic 16-bit comparator design                                               | 129             |

| Fig.5.16 16-bit Comparator designed with the proposed logic                           | 130             |

| Fig.5.17 Delay comparison (Varying the fan-in)                                        | 132             |

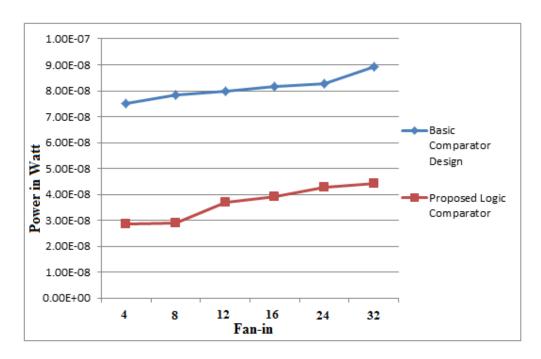

| Fig.5.18 Power comparison (Varying fan-in)                                            | 132             |

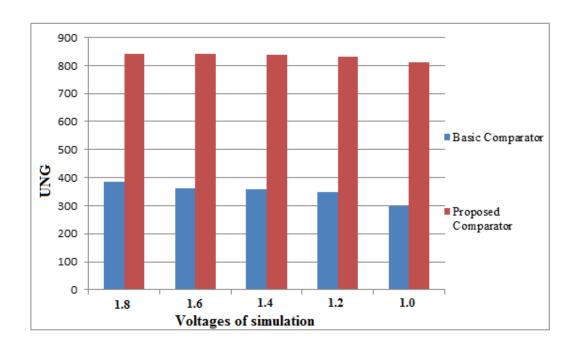

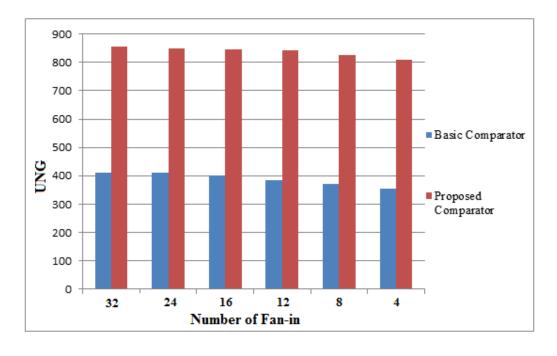

| Fig.5.19 UNG comparison with fan-in of 16 bit (Varying the supply voltage)            | 133             |

| Fig.5.20 UNG comparison using supply voltage of 1.8 V (Varying the fan-in)            | 133             |

| Fig.6.1 Analog IC design Flow                                                         | 137             |

| Fig.6.2 ALU block diagram                                                             | 138             |

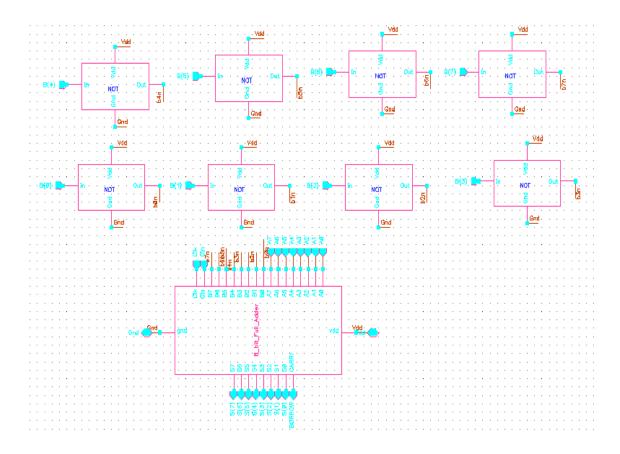

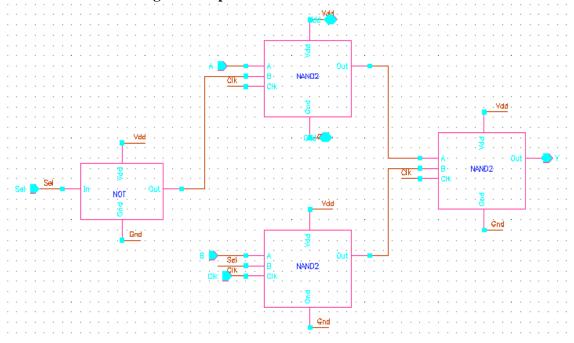

| Fig.6.3 Proposed XOR2 gate schematic                                                  | 140             |

| Fig.6.4 Proposed 8-bit XOR2 gate schematic                                            | 140             |

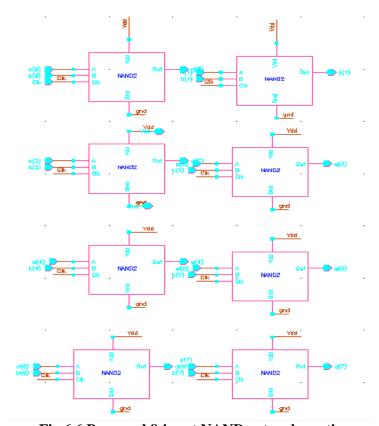

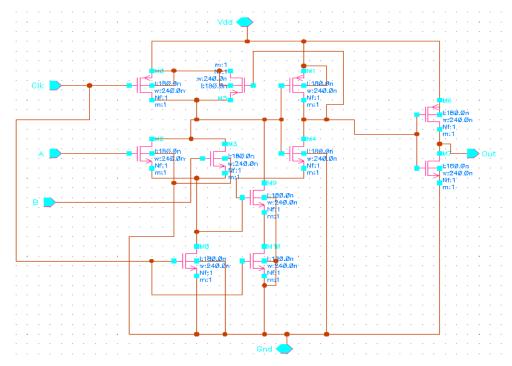

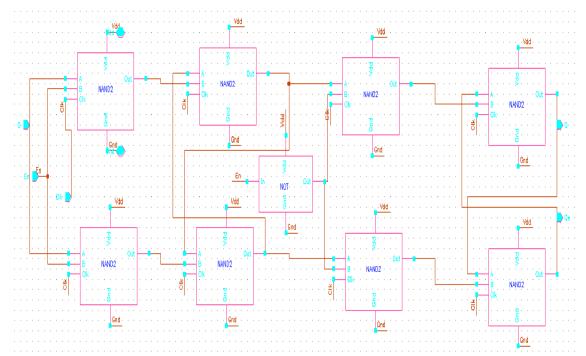

| Fig. 6.5 Proposed 2-input NAND gate schematic                                         | 141             |

| Fig.6.6 Proposed 8-input NAND gate schematic                                          | 141             |

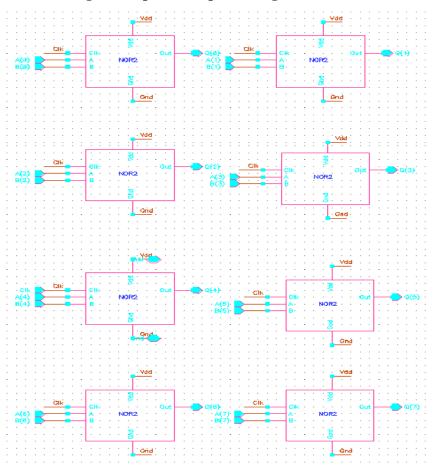

| Fig. 6.7 Proposed 2-input NOR gate schematic                                          | 142             |

| Fig. 6.8 Proposed 8-input NOR gate schematic                                          | 142             |

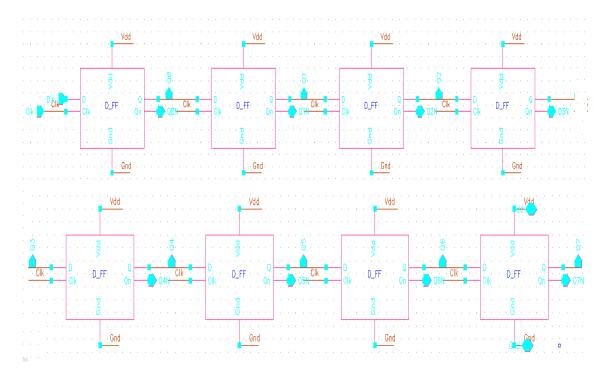

| Fig.6.9 Proposed D-FF schematic                                                       | 143             |

| Fig.6.10 Proposed Shifter schematic                          | 143 |

|--------------------------------------------------------------|-----|

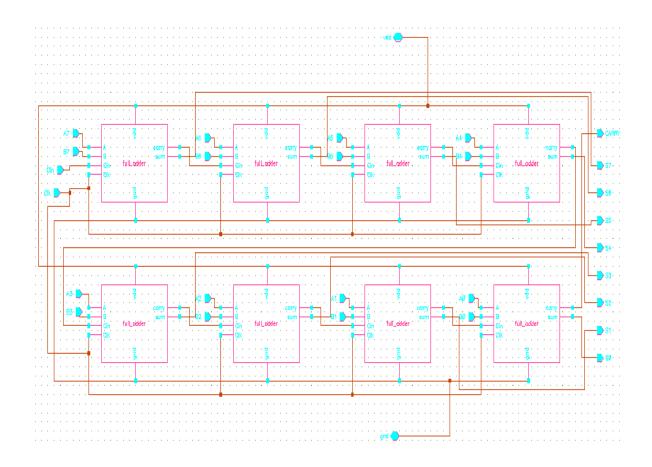

| Fig.6.11 Proposed 1-bit adder schematic                      | 144 |

| Fig.6.12 Proposed 8-bit adder schematic                      | 144 |

| Fig.6.13 Proposed 8-bit substractor schematic                | 145 |

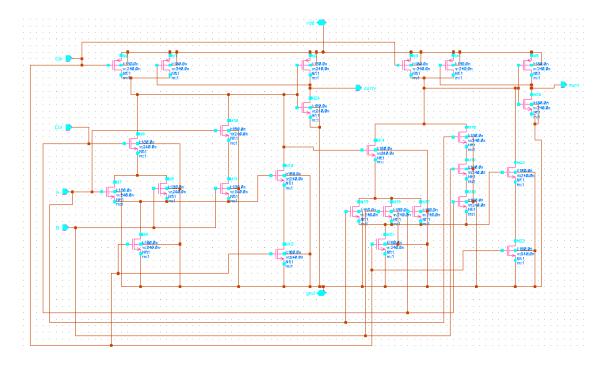

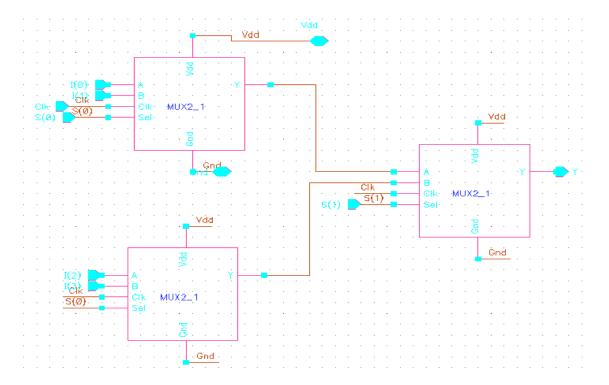

| Fig.6.14 Proposed 2-bit mux schematic                        | 145 |

| Fig.6.15 Proposed 4-bit mux schematic                        | 146 |

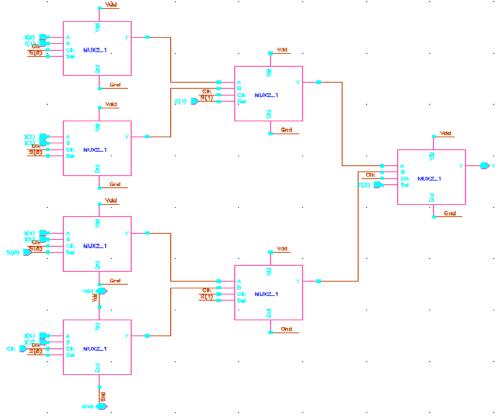

| Fig.6.16 Proposed 8-bit mux schematic                        | 146 |

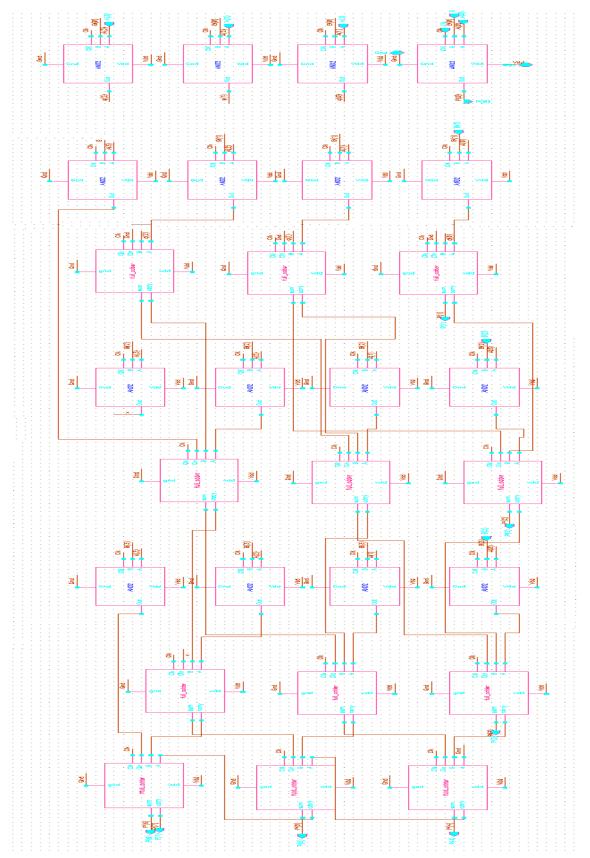

| Fig.6.17 Proposed 4-bit multiplier schematic                 | 147 |

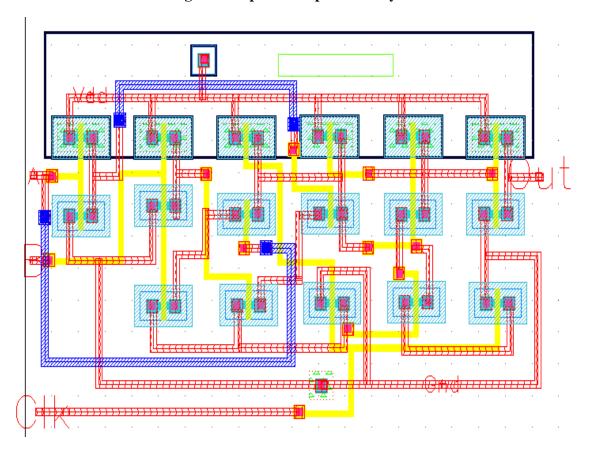

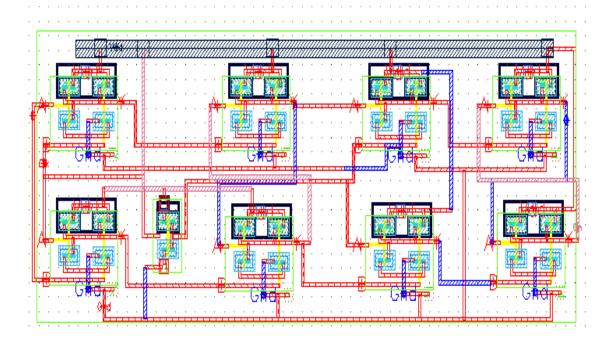

| Fig.6.18 Proposed 2-input NAND layout                        | 149 |

| Fig.6.19 Proposed 8-input NAND layout                        | 150 |

| Fig.6.20 Proposed 2-input NOR layout                         | 150 |

| Fig.6.21 Proposed 8-input NOR layout                         | 151 |

| Fig.6.22 Proposed 2-input XOR layout                         | 151 |

| Fig.6.23 Proposed 8-input XOR layout                         | 152 |

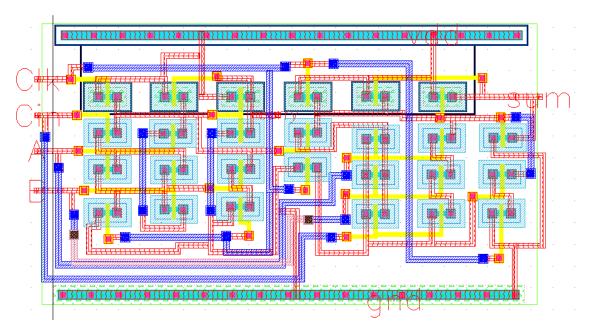

| Fig.6.24 Proposed 2-bit adder layout                         | 152 |

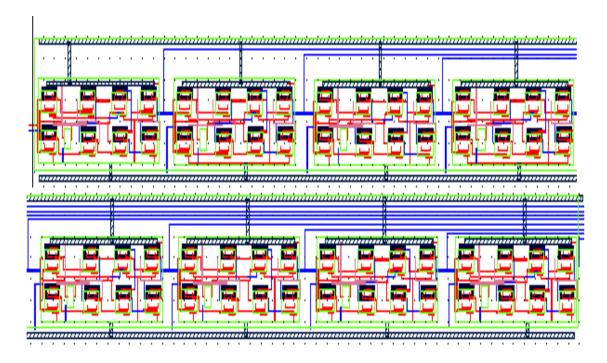

| Fig.6.25 Proposed 8-bit adder layout                         | 153 |

| Fig.6.26 Proposed D-FF layout                                | 154 |

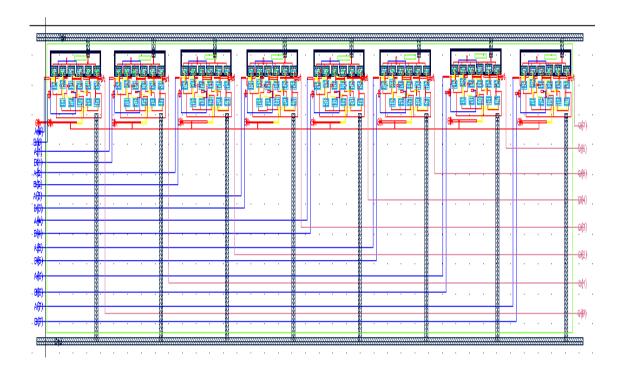

| Fig. 6.27 Proposed 8-bit shifter layout                      | 154 |

| Fig. 6.28 Proposed 8-bit Substractor layout                  | 155 |

| Fig.6.29 Proposed 2:1 mux layout                             | 155 |

| Fig. 6.30 Proposed 4:1 mux layout                            | 156 |

| Fig.6.31 Proposed 8:1 mux layout                             | 156 |

| Fig. 6.32 Proposed multiplier layout                         | 157 |

| Fig. 6.33 Layout of proposed ALU                             | 158 |

| Fig.6.34 DRC error window                                    | 159 |

| Fig.6.35 LVS run window                                      | 159 |

| Fig.6.36 Configure window of 1-bit ALU for av_extracted view | 160 |

| Fig. 6.37 Multiplication output of ALU161                                                        |

|--------------------------------------------------------------------------------------------------|

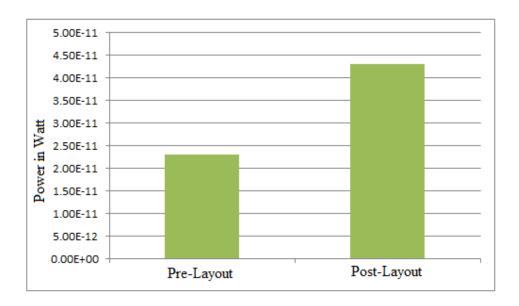

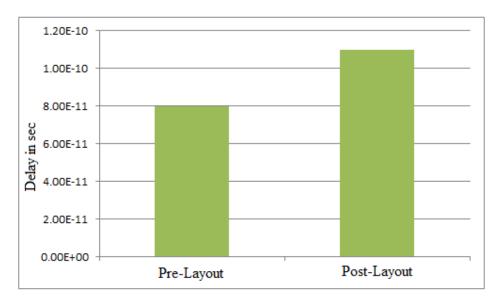

| Fig. 6.38 Pre-layout and post-layout power comparison for multiplication operation162            |

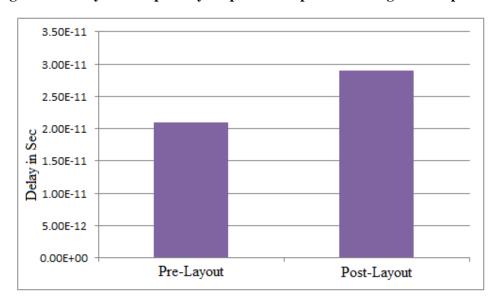

| Fig. 6.39 Pre-layout and post-layout delay comparison for multiplication operation162            |

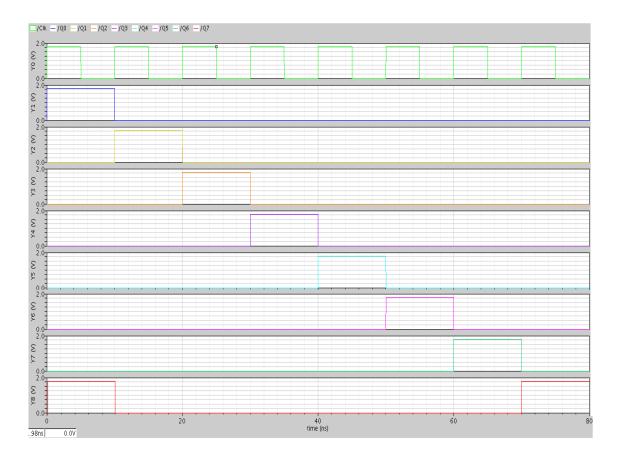

| Fig. 6.40 Right shift operation of ALU                                                           |

| Fig. 6.41 Pre-layout and post-layout power comparison for right shift operation164               |

| Fig. 6.42 Pre-layout and post-layout delay comparison for right shift operation164               |

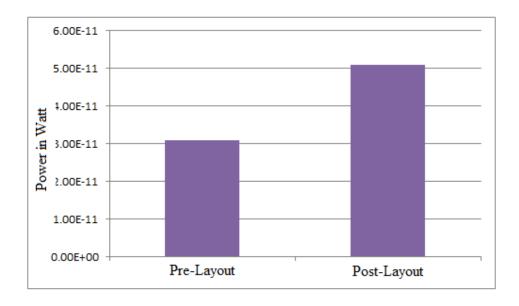

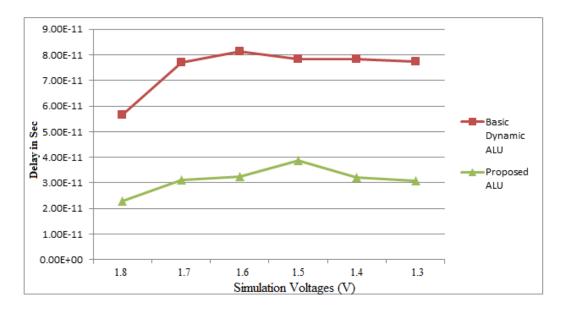

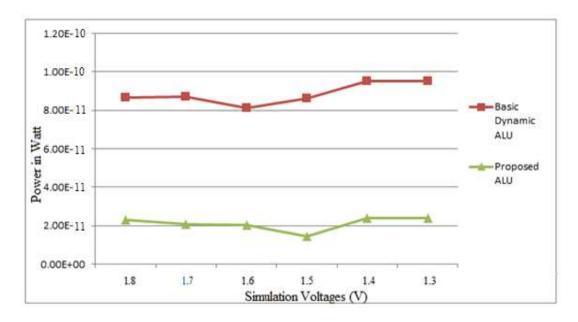

| Fig.6.43 Post-layout delay comparison of proposed ALU with ALU designed with basic dynamic logic |

|                                                                                                  |

| Fig.6.44 Post layout power comparison of proposed ALU with ALU designed with basic dynamic logic |

|                                                                                                  |

| Fig. 6.45 ALU Testchip                                                                           |

# **LIST OF TABLES**

| Table 3.1 Power consumption of the proposed circuit with and without keeper6                     | 52        |

|--------------------------------------------------------------------------------------------------|-----------|

| Table 3.2 Comparasion of the proposed domino with previous proposed domino logic styles by       |           |

| number of transistors used for implementing 2-input OR gate6                                     | 57        |

| Table 3.3 Comparison of power and delay for OR gate designed with proposed domino logic with OR  | ?         |

| gate designed with Basic circuit and other reference circuits (Varying the supply voltage)       | 70        |

| Table 3.4 Comparison of PDP for OR gate designed with proposed domino logic with OR gate         |           |

| designed with Basic circuit and other reference circuits (Varying the supply voltage)            | 70        |

| Table 3.5 Comparison of power and delay for OR gate designed with proposed domino logic with OR  | ?         |

| gate designed with Basic circuit and other reference circuits (Varying the number of fan-in)     | 71        |

| Table 3.6 Comparison of PDP for OR gate designed with proposed domino logic with OR gate         |           |

| designed with Basic circuit and other reference circuits (Varying the number of fan-in)          | 71        |

| Table 3.7 Power and delay performance of 2-input OR gate using 180 and 65 nm technologies        | 74        |

| Table 3.8 PDP performance of 2-input OR gate using 180 and 65 nm technologies                    | 74        |

| Table 3.9 Power saving comparison with different logic functions and the proposed scheme         | 30        |

| Table 3.10 Circuit delay with different logic functions and the proposed scheme                  | 30        |

| Table 3.11 PDP performance of different logic style compared with the proposed logic style in    |           |

| different corner processes (Simulated with 2-input OR gate)                                      | <i>82</i> |

| Table 3.12 Power, delay and PDP comparison of all the flip-flops9                                | 95        |

| Table 4.1 UNG of the proposed domino logic compared to other basic domino logic styles under Sam | пе        |

| Delay (UNG Numbers Normalized to V = 1V)10                                                       | 94        |

| Table 4.2 UNG ratio for Different fan-in of OR gates under the same Condition10                  | <i>)5</i> |

| Table 4.3 UNG ratio for Different fan-in of OR gates under the same Condition10                  | <i>97</i> |

| Table 5.1 Delay comparison (Varying the supply voltage)12                                        | 26        |

| Table 5.2 Power comparison (Varying the supply voltage)                                          | 26        |

| Table 5.3 UNG comparison (Varying supply voltage)12                                              | 28        |

| Table 5.4 Delay comparison (Varying the fan-in)13                                                | 31        |

| Table 5.5 Power comparison (Varvina the fan-in)                                                  | 31        |

| <u>List</u> | 06 | 7 | rbles | , |

|-------------|----|---|-------|---|

|             |    |   |       |   |

| Table 5.6 UNG comparison with fan-in of 16 bit (Varying the supply voltage) | 134 |

|-----------------------------------------------------------------------------|-----|

| Table 5.7 UNG comparison with supply voltage of 1.8 V (Varying the fan-in)  | 134 |

| Table 6.1 Functionality of ALU                                              | 139 |

### **ABSTRACT**

The demands of upcoming computing, as well as the challenges of nanometer-era of VLSI design necessitate new digital logic techniques and styles that are at the same time high performance, energy efficient and robust to noise and variation. Dynamic CMOS logic gates are broadly used to design high performance circuits due to their high speed. Conversely, the vital demerit of dynamic logic style is its high noise sensitivity. The main reason for this is the sub-threshold leakage current flowing through the pull down network. With continuous technology scaling, this problem is getting more and more severe.

In this thesis, a new noise tolerant dynamic CMOS circuit technique is proposed. In the proposed work, we have enhanced the behavior of the domino CMOS logic. This technique also gets benefit in terms of delay and power. This thesis describes the new low power, noise tolerant and high speed domino logic technique and presents a comparison result of this logic with previously reported schemes. Simulation results prove that, in 180 nm CMOS technology when we used this logic style to realize wide fan-in logic gates, it could achieve maximum level of noise robustness as compared to its basic counterpart. In addition, the logic also works efficiently with sequential circuits.

The feasibility of this new technique is demonstrated by means of a real hardware, we have built a custom test-chip in the UMC 180 nm process technology with an ALU core, using the proposed domino logic style for each design block. In this thesis, we have also described the design and implementation of this chip. In addition to this, we have also presented initial power and delay performance comparisons between the circuit level simulated ALU and test-chip implemented in the proposed domino logic style.

Finally we conclude that, the thesis contributes a very efficient logic style for wide fan-in gates, which is not only noise robust but also energy efficient and high speed.

## **ABBREVIATION**

14TCMOS - 14 transistor complementary metal—oxide—semiconductor

ALU - Arithmetic logic unit

ANTE - Average noise threshold energy

CDL - Conventional dynamic logic

CLK - Clock

CMOS - Complementary metal–oxide–semiconductor

CPL - Conventional pass transistor logic

CSL - Conventional static logic

DC - Direct current

DRC - Design rule check

ERC - Electrical rule check

FF - Flip-flop

GDI - Gate diffusion input

GND - Ground

LVS - Layout versus schematic

NIC - Noise injection circuit

NMOS - N-type metal-oxide-semiconductor

OUT - Output

PDN - Pull-down network

#### **Abbreviation**

PDP - Power delay product

PMOS - P-type metal-oxide-semiconductor

PUN - Pull up network

SFEG - Source following evaluation gate

TFA - Transmission function full adder

TGCMOS - Transmission gate complementary metal—oxide—semiconductor

UMC - United Microelectronics Corporation

UNG - Unity noise gain

VLSI - Very large scale integration

# Chapter 1

## INTRODUCTION

#### 1.1 INTRODUCTION

The modern technologies move towards smaller, faster, and cheaper computing systems. This has been facilitated by exponential increase in device density and operating frequency through VLSI technology scaling. This has led to an increase in power consumption that has reached limits of reliability and cost. In addition, continued scaling into the nanometer system has brought design robustness issues such as soft error, signal integrity, and process variability. In addition, the issues of power consumption and robustness are affected with time. This has created a predicament in computer system design that intimidated to be an uncertain block to future advancement.

Researchers of pioneer computing systems have found that power consumption and design robustness must be taken into account at every level of design. For any design in circuit level, the choice of logic styles is very significant as it directly affects power, performance, and robustness. Static CMOS and domino logic do not fully meet the needs of future computing. Two basic CMOS circuit designs are static logic and dynamic logic. Static CMOS is better energy-efficient and robust but is very slow to be used in critical and massive designs. Domino logic is fast but consumes loads of power and is not at all robust. Also, domino logic scales poorly so that its speed advantage is much narrowed. Its power and robustness are worst and having a lot of inconvenience. We therefore require improved digital logic technique and style which is at the same time energy efficient, fast and noise robust.

In this thesis, we have proposed semi-domino logic for footed logic circuit implementation. Using this logic, unwanted pulses of the dynamic node, which are generated during the precharge process, are prevented to pass to the output node, as is in the conventional case. As a result a lot of power is saved as compared to other domino gate logic circuits. This logic is again modified using keeper and some footer transistors to get a better energy-efficient, robust and high speed logic.

In this thesis, this logic gate is peer analyzed and compared with the same circuit designed with other logic styles. This logic design is also applied to comparator and adder. To demonstrate advantages of the proposed logic in real hardware, we built a custom test-chip using a full custom design with UMC 180 nm process.

#### 1.2 PARAMETERS OF ENHANCEMENT

CMOS technology is the dominant logic style in today's IC design because of its high speed, low power and high packaging density. With continuous technology scaling i.e. reduction in feature size leads to high packaging density which leads to increase in current density as well as power density. Large increase in current or power density causes serious reliability problems for scaled transistors like oxide breakdown, hot carrier injection [1] [2] [3] [4]. This increase in power density can be reduced by supply voltage (V<sub>DD</sub>) scaling because of the quadratic relationship between power and V<sub>DD</sub>, but rate of supply voltage scaling is not as fast as rate at which device dimensions are scaled because of various physical limitations like built in junction potential or silicon band gap which can't be scaled further.

#### **1.2.1 POWER**

Ideally, in CMOS circuits the output node is either connected to  $V_{DD}$  or GND. Due to absence of direct path between  $V_{DD}$  and GND CMOS circuits dissipates zero static power. But practically MOS transistor never acts as perfect switch. There is always a leakage current which leads to static power dissipation. The various sources of power dissipation [5] [6] in CMOS are,

- > Static Power Dissipation

- > Dynamic power Dissipation

The total power in a static CMOS is given by [5]

$$P_{Total} = P_{Static} + P_{Switching} + P_{ShortCircuit}$$

(1.1)

#### 1.2.2.1 STATIC POWER DISSIPATION (PSTATIC)

It is the power dissipated when there is no switching activity within a circuit. Ideally, CMOS circuit dissipates no static power, since there is no direct path from  $V_{DD}$  to GND. But practically MOS transistor never acts as perfect switch. There is always leakage current which flows when the input(s) to and the outputs of a gate are not changing, leads to static power dissipation. But as the supply voltage is being scaled down to reduce dynamic power, low  $V_{TH}$  transistors are used to maintain performance. Reduction in  $V_{TH}$  of transistor leads to greater leakage current [5].

Static power dissipation is given by

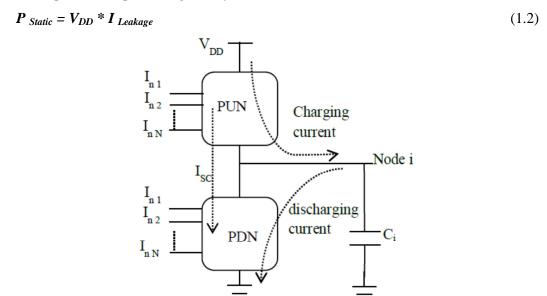

Fig.1.1 Switching and short-circuit current elements in static CMOS

#### 1.2.2.2 DYNAMIC POWER DISSIPATION

It is the dominant portion of power dissipation which occurs due to transit ion at gate outputs. It consist two components of power dissipation.

- 1) Switching Power dissipation (P<sub>Switching</sub>)

- 2) Short Circuit Power Dissipation (P<sub>ShortCircuit</sub>)

#### 1) Switching Power dissipation (P<sub>Switching</sub>)

As the nodes in a digital CMOS circuit transition back and forth between two logic levels, the capacitance associated with the nodes gets charged and discharged. Power

dissipated during this process is called as switching power and it is a major source of power dissipation in CMOS circuits. For a static CMOS circuit with N switching nodes operating at clock frequency  $f_{clk}$ , the switching power is given by [7].

$$P_{Switching} = \sum_{i=1}^{N} \alpha_i C_i V_{DD} V_{Swing} f_{clk}$$

(1.3)

Where  $\alpha_i$  = switching activity at node i

V<sub>DD</sub> = supply voltage

Vswing = Voltage swing at node i

αiCi is the effective switch capacitance per cycle at node i

#### 2) Short Circuit Power Dissipation (P<sub>ShortCircuit</sub>)

This is due to short circuit current ( $I_{SC}$ ) which flows directly from  $V_{DD}$  to GND when both PMOS and NMOS transistor are ON. When input to the gate gets stable at either logic level only PMOS or NMOS transistors are ON. Hence no short circuit current flows. But when output of a gate switches in response to change in inputs, both PMOS and NMOS transistors conduct simultaneously for a short interval of time. This interval of time depends upon rise or fall time of input signal and causes short circuit power dissipation.

$$P_{ShortCircuit} = V_{DD} * I_{SC}$$

(1.4)

#### 1.2.2 PROPAGATION DELAY

The dependency of propagation delay on circuit parameter is given by [8]

$$T_d \alpha \frac{C_L V_{DD}}{k(V_{DD} - V_{TH})^{\alpha}} \tag{1.5}$$

Where  $\alpha$  is the velocity saturation index

k depends upon W/L

From equation 1.3 and 1.5, the power dissipation and propagation delay both depends upon the supply voltage ( $V_{DD}$ ). The scaling of supply voltage causes the reduction in power whereas the propagation delay significantly increases. So for each design depending upon its application there exist a tradeoff between power and delay.

#### **1.2.3 NOISE**

Continuous scaling of CMOS technology makes noise become an equally important metric like power, performance and area. To maintain performance with the scaling of supply voltage threshold voltage is also scaled down, resulting in reduction of noise margin. In current CMOS technology with reduced spacing between interconnect and higher operating frequency makes capacitive and inductive coupling [9] to increase significantly resulting in severe side effects on signal integrity.

Hence various logic styles are used to construct logic gates depending upon its application in terms of power, speed, noise robustness and area.

#### 1.3 MOTIVATION FOR THE WORK

#### 1.3.1 NEED FOR LOW-POWER

Fast advancement of VLSI CMOS circuit technology is satisfied by increased use of small sized and wireless systems with very low power consumption. Due to the continued scaling of supply/threshold voltage and technology, leakage power is becoming very significant in power dissipation of nano-scale CMOS circuits. Consequently, the total power consumption is a critical factor while designing low power digital circuits [10].

#### 1.3.2 NEED FOR HIGH SPEED

Rapidly increasing demand for higher speeds in the areas of signal processing, high-speed computing, communication, and related instrumentation includes an urgent requirement for very high-speed integrated circuits. Availability of sub-100-ps VLSI circuits and volume production are having great impact on these areas. The time delay related with interconnections is becoming an important factor for the calculation of total chip delay per gate in high-speed VLSI circuits [11].

#### 1.3.3 NEED FOR NOISE-IMMUNITY

Now-a-days technology is scaled down into the deep sub-micron system, due to which, noise immunity is becoming a significant issue in VLSI chips design [12] [13] [14]. Noise in the digital circuit design is defined as any possible event which can cause the voltage at node to vary from actual value. Various sources of noise like crosstalk, variation in charge sharing, leakage current and supply voltage are present in VLSI chip design [15] [16]

[17] [18] [19] [20]. The leakage current through the transistors of a digital circuit is increasing exponentially with technology scaling.

#### 1.3.4 NEED FOR LESS-AREA

Size minimization with increased application is now the major demand in recent world. This demand has really given rise to VLSI [21] [22] [23]. In every field like wireless systems, mobile systems to the daily use equipment, there is an aggressive need of minimizing area or size.

#### 1.4 OBJECTIVE OF THE RESEARCH WORK

Recent technology scaling and use of various logic families provides techniques to achieve power consumption at the cost of performance. Power, speed and robustness are so critical to leading edge designs that they need to be taken care of each level of design. The choice of logic styles is a very important constraint at the circuit level. Logic styles differ in terms of energy, delay, area and robustness. Because every design requires compromises and trade-offs, designers need to pick and choose circuits from different points on an energy-delay-robustness envelope to meet each circuit need. Among other things, meeting the needs of future computing will require logic style that satisfies high-performance, low-power, high-robustness in the form of noise and variability, ease of implementation and verification. In addition to that, we want to use logic styles that are compatible for all types of logic implementation for further improvement in robustness. In the following chapters we will show why existing logic styles do not meet these needs and how the proposed logic can fill the void. The objective of this research work is to modify and improve domino logic that can provide further improvement in power consumption, performance, noise margin and area overhead.

#### 1.5 THESIS ORGANIZATION

This thesis is organized in such a way as to properly layout a detail investigation and results of the research work.

In chapter 1 objective of the thesis with a summary of thesis organization are presented.

Chapter 2 provides the background of CMOS logic styles and recent proposed works to upgrade dynamic logic.

In Chapter 3 the proposed logic has been described. A peer analysis of the proposed logic is presented. Furthermore, we have to compare the same with previous logic styles recently proposed by other researchers and conclude with merit and demerit of the proposed circuit.

Chapter 4 shows the noise analysis of the proposed circuit. In this chapter, we have simulated and compared the proposed logic style with various logic styles and shown how the proposed logic proves to be noise tolerant as compared to the other logic styles.

Chapter 5 describes some applications of proposed domino logic. Comparator and adder circuits are designed with the proposed logic and are analyzed with respect to the previous proposed comparator and adder circuits.

Chapter 6 demonstrates advantages of proposed logic in real hardware; we built a custom test-chip in the UMC 180nm process with the proposed logic styles. We describe the design, implementation, operation, and testing of this chip. We also present initial energy delay performance comparisons between the simulated one and the real hardware.

Chapter 7 summarizes the contributions of this thesis and discusses possible perspectives for future work.

# Chapter 2

## **BACKGROUND LOGIC STYLES**

#### 2.1 DIFFERENT LOGIC STYLES

#### 2.1.1 STATIC CMOS LOGIC

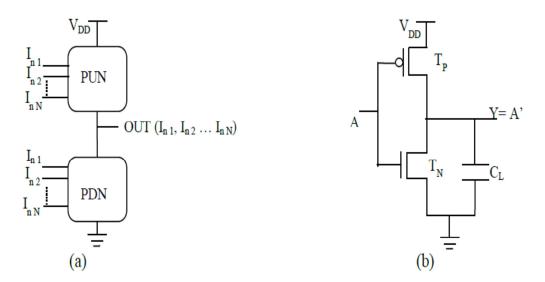

Static CMOS circuits consist of a pull up network (PUN) and a pull down network (PDN) as depicted in Fig.2.1(a) [1], [24]. The PUN block consists of PMOS transistors, which pull up the output node (OUT) to  $V_{DD}$  and the PDN block consist of NMOS transistors, which pull down the OUT node to GND. At any instant of time either the pull up or pull down block is on; so that the OUT node remains either at  $V_{DD}$  or GND. The size of PMOS devices is larger than NMOS devices, because the mobility of PMOS is lower than the mobility of NMOS. The structure of a CMOS inverter is shown in Fig.2.1 (b). It consists of a PMOS and a NMOS transistor. The operation of the circuit is as follows; when INPUT A is HIGH  $(V_{DD})$ ,  $T_N$  is ON and  $T_P$  is OFF. A direct path exists from node Y to ground, resulting 0 V at the output node Y. When A is LOW (0 V),  $T_P$  is ON and  $T_N$  is OFF, resulting in a steady voltage of  $V_{DD}$  at node Y.

#### **Properties**

- 1. A transistor operates as a 'switch' controlled by its gate.

- 2. PMOS transistors are used to construct the PUN; while the NMOS devices construct the PDN.

- 3. Parallel connected NMOS transistors represent an OR function; series connected NMOS transistors represent an AND function.

- 4. 2N numbers of transistors are required to implement an N-input logic.

Fig.2.1(a) CMOS logic gates as a combination of PUN and PDN (b) CMOS inverter [25]

**Advantages**

# In static logic, the voltage swing at node OUT is equal to either the supply voltage V<sub>DD</sub> or GND [1]. Such characteristic of the CMOS circuits result in high noise margin [2].

- 2. The logic levels of static CMOS logics are independent of relative size of the transistors, so that the transistors can have minimum size [26]. Logic circuits having this property are known as 'Ratio-less Logic circuits', where the relative dimensions of the composing transistors do not determine logic levels of the circuit.

- 3. In steady state, a path always remains with finite resistance between either output node (OUT) to  $V_{DD}$  or GND. Therefore, CMOS inverter has low output impedance.

- 4. Low impedance of the circuit makes the circuit noise tolerant [1].

- 5. As the gate of a CMOS transistor works as an insulator, the input resistance becomes very high. Therefore, it consumes no DC current. The input of inverter is only connected to a gate of the transistor. In the steady state input current is nearly zero.

- 6. There is absence of direct path between  $V_{DD}$  and GND. This means that, the gate does not consume any static power.

- 7. Switching threshold of the circuit is  $V_{DD}/2$ . Therefore the circuit becomes more robust.

#### Limitations

- 1. When the input signal is having finite rise or fall time, both the NMOS and PMOS transistors are ON during a very short interval of time leads to short circuit current [1] [26].

- 2. In this logic a fan-in of N requires 2N devices results in larger circuit area.

#### 2.1.2 DIFFERENT TYPES OF STATIC LOGIC

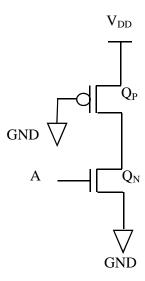

#### 2.1.2.1 PSEUDO N-MOS

Fig. 2.2 shows a modified form of CMOS inverter. Here only  $Q_N$  is driven by the input voltage. The gate of  $Q_P$  is grounded and acts as an active load for  $Q_N$ . The load is called as the "Pseudo NMOS Load" [1] [24] as depicted in Fig. 2.2. This inverter circuit is another form of NMOS logic that consists of a driver transistor  $Q_N$  and a load transistor  $Q_P$ . Hence the name is 'Pseudo NMOS'.

Fig.2.2 Pseudo-NMOS logic

#### Advantage

In Pseudo-NMOS logic a fan-in of N requires only N+1 number of transistors. This transistor count is nearly half to the static logic.

#### Disadvantage

- 1. This circuit has less noise margin so it is very sensitive to noise.

- 2. It consumes more static power compared to static CMOS because of the presence of a PMOS transistor which is always ON.

#### 2.1.2.2 PASS TRANSISTOR LOGIC

Pass transistor logic is a widely used option of complementary-CMOS, because it tries to minimize transistor count needed for implementing a function by letting the inputs to drive gate terminals as well as source or drain terminals. This phenomenon is very much different than other logic styles that we have discussed in the above literature, which the gate terminals of MOSFETs are only driven by the primary inputs [27] [28] [29] [30] as depicted in Fig.2.3.

#### **Advantages**

- 1. It reduces the transistor count required to implement the same logic which allows the inputs to drive the gate, source and drain terminals of MOSFET [27].

- 2. Reduction in the number of devices also reduces the output capacitance of the circuit.

Fig.2.3 Static Pass-transistor logic

#### Disadvantage

1. Pass transistor logic cannot be cascaded.

#### 2.1.2.3 COMPLEMENTARY PASS-TRANSISTOR LOGIC

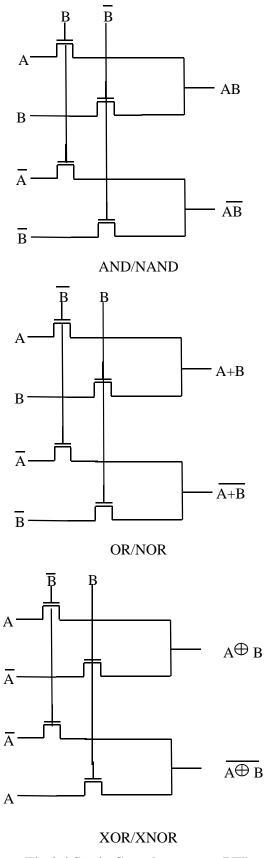

In high performance logic design this logic family, called Complementary-PTL or Differential-PTL, is generally used [31] [32] [33] [34]. The basic idea is to accept the complementary input and produce complementary output as depicted in Fig.2.4.

#### Advantages

- 1. With this logic complex CMOS gates like XOR, XNOR and adders with less numbers of transistors can be implemented [31].

- 2. In this logic gates, as the output nodes are either connected to  $V_{DD}$  (power supply) or GND over a low resistance path [32].

Fig.2.4 Static Complementary-PTL

#### **Disadvantages**

- 1. In complementary pass transistor logic, there is a presence of static power dissipation [31].

- 2. Noise margin is reduced as compared to static pass transistor logic [1].

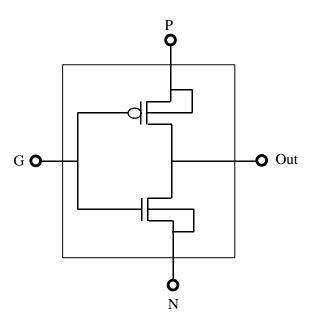

#### 2.1.2.4 GATE-DIFFUSION-INPUT (GDI)

GDI is a new technique of realizing CMOS static logic technique, which is based on the use of a simple cell structure. A first look towards the basic cell looks like standard CMOS inverter. Important properties of GDI cell are: GDI cell contains inputs G (common gate input of NMOS and PMOS), N (input to the source/drain of NMOS) and P (input to the source/drain of PMOS) [35] [36] [37] [38] [39] as depicted in Fig.2.5.

Fig.2.5 Gate-Diffusion-Input logic

#### **Advantages**

- 1. This gate diffusion input circuit technique requires very less number of transistors [35].

- 2. Due to presence of less number of devices, the circuit requires less power to operate [36].

#### Disadvantage

This circuit technique is not convenient for large logic designs [37].

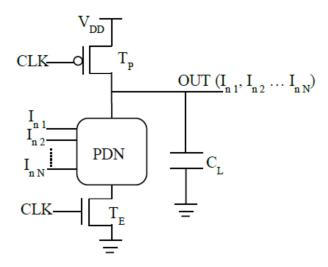

#### 2.2 DYNAMIC CMOS LOGIC

The pseudo NMOS logic style needs N + 1 number of transistors for realizing an N-input logic gate. This logic has more static power dissipation. Dynamic logic uses a clock input, by which it experiences a series of precharge and conditional evaluation phases as shown in Fig.2.6 [1] [40] [41] [42] [43].

#### Precharge phase:

When the CLK is 0, the node OUT precharges to  $V_{DD}$  through  $T_P$ , PDN is disabled because  $T_E$  is OFF.

Fig.2.6 Dynamic logic

#### **Evaluation phase:**

When CLK=1,  $T_P$  is OFF and  $T_E$  is ON. The node OUT conditionally discharges based upon input value to the pull down network. Throughout evaluation phase, the only possible path from node OUT is only ground (GND). The output node (OUT) can only discharge in evaluation phase and charges to  $V_{DD}$  during precharge phase [41].

#### **Advantages**

1. The logic function is result of the parallel and series arrangements of NMOS pull down network.

- 2. N + 2 number of transistors required to implement dynamic logic, which is less than that of static logic [1].

- 3. This logic is non-ratioed. The size of the PMOS devices is not important for realizing correct functionality of the circuit.

- 4. This logic gates consume only dynamic power. In ideal condition, the static current path never exists between the supply voltage  $V_{DD}$  and GND.

- 5. Gates designed with this logic have faster switching speeds [42]. This is because of reduced load capacitance attributed to the lower number of transistors per gate absence of short circuit current in the dynamic gate.

#### Limitations

- 1. It has low noise margin due to reduction in switching threshold.

- 2. Output is in high impedance state, if PDN is turned off during evaluation phase.

- 3. This logic circuit suffers from charge leakage and charge sharing.

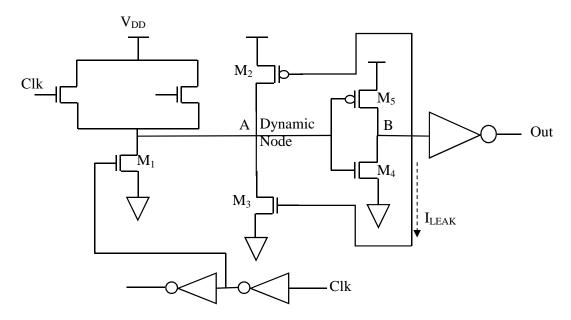

#### 2.2.1 ISSUES IN DYNAMIC LOGIC

The dynamic logic results in high performance solutions as compared to its static counterpart. If one needs dynamic circuits to operate properly, there are numerous important things that must be considered. This includes charge sharing, charge leakage, back gate or capacitive coupling, and clock feed through. In this section we have discussed these issues briefly.

#### 2.2.1.1 CHARGE LEAKAGE

The operations of dynamic gate depend on charge stored in dynamic node capacitor [1]. If pull down network is conditionally off, the output should ideally remain at high in evaluation phase. But, charge of the dynamic node gradually leaks away due to leakage currents, eventually resulting in a malfunctioning of the gate. Fig.2.7 depicts the source of leakage for the basic dynamic logic circuit. This phenomenon is also presented in [44] [45] [46] [47] [48].

The reverse-biased diode and sub-threshold leakage of the NMOS pull-down device  $M_1$  are responsible for the charge leakage in dynamic circuits. The charge of the output capacitor  $C_L$  leaks away due these above mentioned sources of leakage. This phenomenon degrades the circuit performances. It can be noted that the PMOS precharge device also contributes some leakage current due to the reverse bias diode and the subthreshold

conduction. The leakage current of the PMOS counteracts the leakage of the pull down path to some extent.

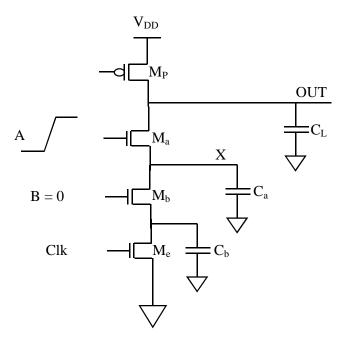

Fig.2.7 Charge leakage

## 2.2.1.2 CHARGE SHARING

Fig.2.8 Charge sharing

Charge sharing in dynamic logic is a vital concern in dynamic logic [48] [49] [50] [51] [52] [53]. Assuming output node is precharged to V<sub>DD</sub> during the precharge phase. Let's consider that, during precharge all the inputs are set to logic zero so the capacitance C<sub>a</sub> gets discharged. Let's further consider that, input B stays at zero during the evaluation, while input A makes a transition from 0 to 1. By doing this, M<sub>a</sub> will get on [1]. When M<sub>a</sub> will get ON, the charge stored at C<sub>L</sub> will be distributed over C<sub>L</sub> and C<sub>a</sub>. this results in drop in the output voltage and cannot be recovered due to the dynamic nature of the circuit as depicted in Fig.2.8.

#### 2.2.1.3 CAPACITIVE COUPLING

The high impedance of output node makes the circuit very sensitive towards crosstalk noise as shown in Fig.2.9. A wire routed over a dynamic node may couple capacitively and destroy the state of the floating node i.e. Out<sub>1</sub>. One more important form of capacitive coupling is back gate (or output-to-input) coupling [54] [55] [56] [57] [36] [37] [38] [39] [58].

Fig.2.9 Capacitive coupling

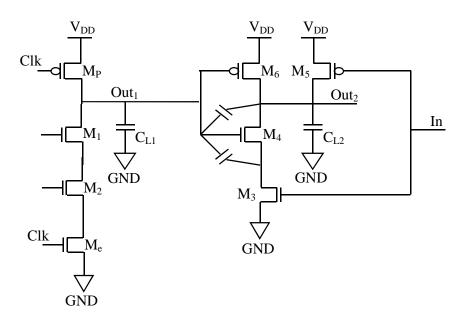

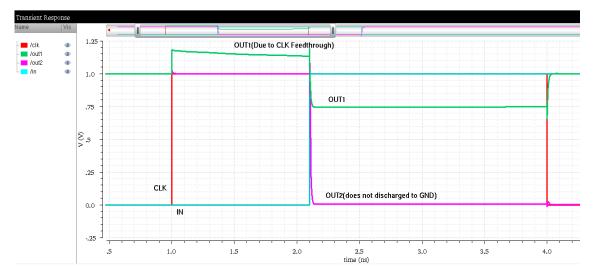

## 2.2.1.4 CLOCK-FEEDTHROUGH

This is a special case of capacitive coupling, which is called as clock feedthrough [59] [60] [61] as depicted in Fig.2.10. During precharge phase (Clk = 0) the output node goes to  $V_{DD}$ . By assuming evaluation transistors are in OFF state, when Clk makes a transition from

low to high, due to the coupling capacitance between gate of  $M_P$  and output node (Out<sub>1</sub>); the output of the dynamic node to rise above  $V_{DD}$ . This is depicted as clock feed through [1].

Fig.2.10 Clock feed-through

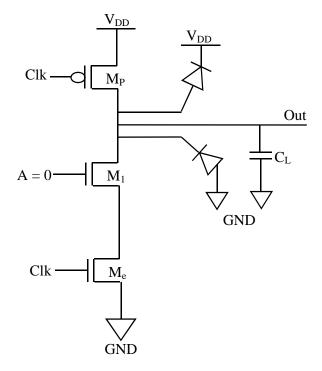

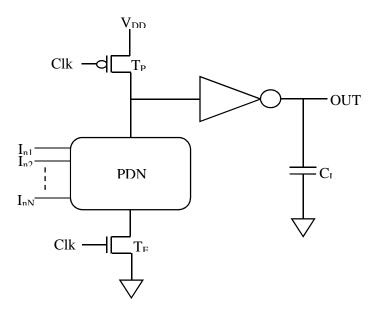

## 2.3 DOMINO LOGIC

The domino logic [62] [21] [63] [64] [65] [66] [41] [67] [68] structure is similar to that of dynamic logic along with a static CMOS inverter that is used to avoid cascading problem as shown in Fig.2.11. During precharge phase (CLK = 0), output is charged to  $V_{DD}$  and output of inverter becomes zero. In the evaluation phase (CLK = 1), the node OUT makes only transition from 0 to 1. Since in the precharge phase the node OUT discharges to logic 0, hence the false evaluation is avoided during cascading of various domino blocks. As it uses static inverter only non-inverting logic can be realized and it increases propagation delay.

## **Property**

The domino gate contains a static inverter, so, non-inverting logic can only be implemented using this logic [1] [63].

#### Advantage

Domino logic gates can achieve very high speed. The inverters can be sized to match the fan-out, which are much smaller than in complimentary static CMOS, as only the gate capacitance has to be accounted for per fan-out gate [66].

## Limitation

Only the non-inverting logic can be implemented [66].

Fig.2.11 Domino CMOS Logic

## 2.3.1 RACE CONDITION IN DOMINO LOGIC

The possibility of race conditions is high in domino logic, when clock is slow. The slow clocks, in domino logic based sequential circuits there present a time window where NMOS and PMOS are conducting. This will lead to path between input and output, which can disturb the functionality of the circuit.

Not only in slower clocks, the race conditions also occur for long rise time and fall times. The domino logic based sequential circuit functionality and performance will be intact as long as the clock rise time and fall time is smaller than 3 to 5 times of the propagation delay of the application circuit. This criterion is easy to achieve in larger circuits and in smaller circuits, designer has to take care propagation delay, rise time, fall time and frequency of the clock to avoid race condition.

## 2.4 OVERVIEW OF PREVIOUS WORKS

Noise in digital integrated CMOS circuit is becoming one of the principal problems in deep submicron technology [69] [70]. In past three decades, researchers have developed many circuit techniques to develop the noise tolerance of domino logic gates. For discussing most of the previous proposed techniques, in this section we have presented a summary of some of the significant methods. In this section, we have classified all previous proposed techniques into four main groups depending upon their circuit modifications and principle of operations:

- 1. Keeper implementation

- 2. Precharge of internal nodes

- 3. Source voltage raising

- 4. Complementary p-network

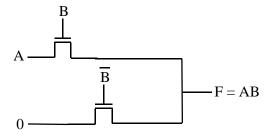

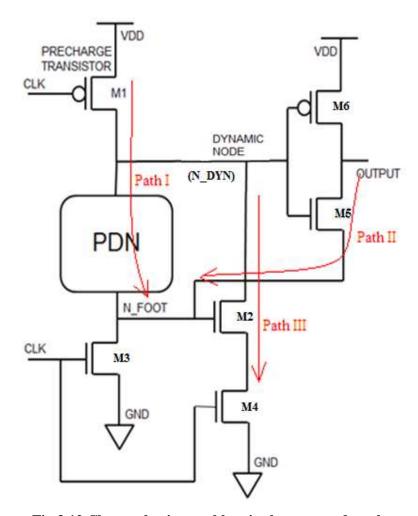

Fig.2.12 CMOS domino logic (a) Schematic of domino circuit (b) Schematic of 2 - input domino AND gate

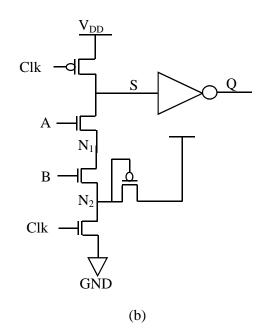

#### 2.4.1 KEEPER IMPLEMENTATION

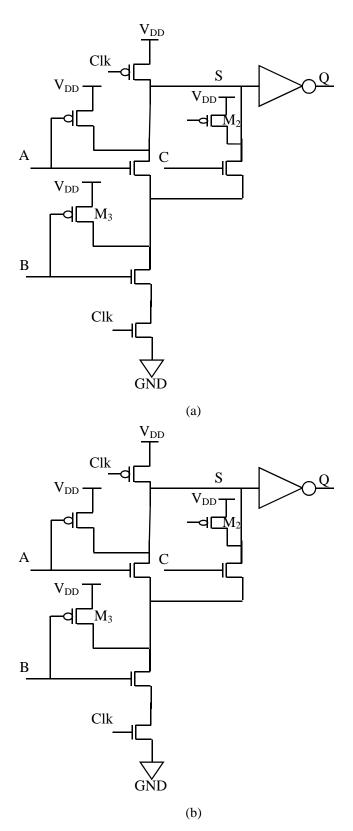

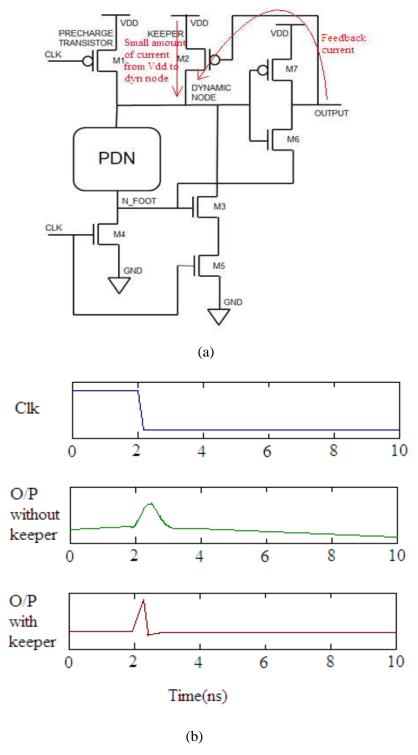

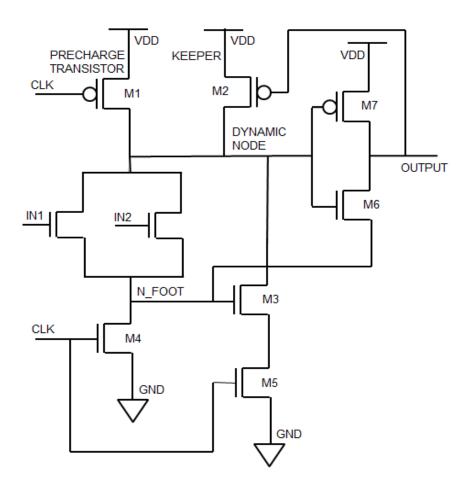

This technique is the easiest method for domino CMOS logic circuit to improve its noise tolerance performance. This technique was based on employing a weak transistor, which is called as "keeper transistor", connected from V<sub>DD</sub> to dynamic node as depicted in Fig.2.12. To maintain charge stored in the dynamic logic, keeper transistor provides a small amount of current from V<sub>DD</sub> to dynamic node of the domino logic. In basic domino logic circuit [71], gate of keeper transistor was connected to the GND, as depicted in Fig.2.13(a). This type of connection keeps the keeper transistor in always ON state. After some years, feedback keeper technique was used, which is depicted in Fig.2.13(b). This technique was more broadly used because it could be able to eliminate a potential dc power consumption problem, which was a vital problem in the evaluation phase of always-on keeper of domino logics [72].

Keeper transistor causes lots of contention problem, when the PDN gets ON through evaluation phase, which results in slower gate performance. When we design a high fan-in gate with deep submicron technology; we need a very strong keeper transistor to compensate the large amount of leakage current flowing through the PDN of the logic gate. These strong keeper transistors have serious contention problem. Anis et al. in [73] and [74] as depicted in Fig.2.13(c) and Alvndpour et al. in [75] and [76] as depicted in Fig.2.13(d) have proposed two new types of keeper design techniques. Both the circuit techniques operate on the same basic principle, (i.e. they temporarily disable the keeper transistor for a very small time, when switching takes place at dynamic gate). Both the methods are extremely effective in noise tolerance enhancement of the dynamic logic gates against leakage noise. Still, these gates with large keepers are very much effective to external noise as dynamic node is not protected when the gate switches.

To reduce the internal and external noise P. Mazumder et. al in [77] as depicted in Fig.2.14(a,b) have designed a noise tolerant circuit technique using circuitry having an effect of negative differential resistance. An inverter is places to produce feedback signal instead of straight connecting it to output. This result in response time of feedback keeper transistor becomes independent upon output load. In this way, this technique independently optimizes the feedback inverter without concerned about the gate output.

Fig.2.13 Keeper implementation (a) Implemented as constantly ON keeper [71](b) Implemented as feedback keeper [72] (c) High Speed feedback keeper implementation [73](d) Conditional keeper implementation [75]

Fig.2.14 Implementation of optimized keeper (a) Implemented as inverter feedback (b) Implemented as pseudo PMOS inverter feedback

Fig.2.15 Precharging internal nodes implemented on AND3 gate, (a) Precharging every internal nodes [78], (b) Precharging some internal nodes [79]

#### 2.4.2 PRECHARGE OF INTERNAL NODES

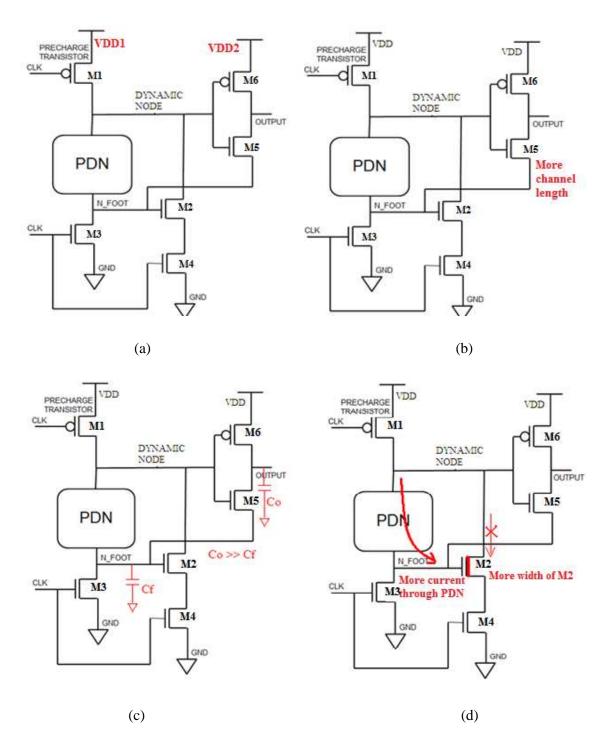

Logic gates having large fan-in have charge sharing among internal nodes in the PDN and dynamic node which results in false gate switching and output logic change. To avoid this charge sharing problem we can precharge the internal nodes along with dynamic node. [78] [79]. A dynamic AND3 gate designed with this technique has been shown in Fig.2.15(a). This technique could eliminate charge sharing problem in an expense of huge chip area, when all internal nodes get precharged. Partial precharge can also be done to the circuits as depicted in Fig.2.15(b), where not all but some of the internal nodes are precharged along with the dynamic node. This technique is a tradeoff between over chip area and noise immunity. If cost of inverter to produce the complementary clock signal can be justified, then to precharge all internal nodes, NMOS transistors can also be used. Meanwhile as the internal nodes are precharged, thus NMOS precharge transistors can decrease the dynamic power consumption of the logic gate and also reduce the discharging time. Thus it can be said that precharging internal node technique is not a very effective technique against noise.

## 2.4.3 SOURCE VOLTAGE RAISING

Raising source voltage is one of the very efficient ways to minimize both external and internal noises. As the sum of transistor threshold voltage and source voltage should be lesser than the gate voltage to turn on a transistor, thus increase in source voltage can directly increase turn-on voltage of the gate. Furthermore, the threshold voltage of the transistor is increases with increase in the source voltage due to body effect,. This also contributes towards improvement of turn on voltage of the gate.

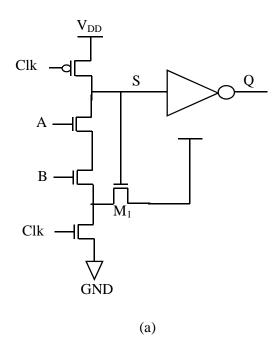

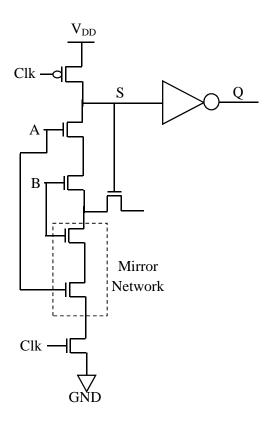

The PMOS pull up method of raising source voltage [80] as depicted in Fig.2.16(b). In this technique one PMOS transistor is employed at the internal node N<sub>2</sub> which forms a voltage divider having a clock controlled transistor. Switching threshold voltage of the domino gate is controlled by the voltage level of node N<sub>2</sub>. Voltage level of node N<sub>2</sub> can be controlled with the size of PMOS pull up transistor. Due to the presence of resistive voltage divider this circuit consumes a large amount of DC power. It can be seen that, the voltage of the dynamic node cannot be less than the node N<sub>2</sub> voltage level, so there is no rail to rail voltage swing at node N<sub>2</sub>. Gate output may also do not comprise a rail to rail swing if the PMOS pull-up transistor is large in size which actually raises noise immunity of the gate.

The method shown in Fig.2.16(c) is an improved method to control noise. In this method a feedback controlled pull-up transistor is employed in the circuit [81]. To make the internal node voltage high, an NMOS transistor is used. Gate of that transistor is connected to dynamic node of the logic circuit. When voltage of the dynamic node becomes low, the pull-up transistor becomes off; then, the dynamic node experiences rail to rail voltage swing. Similarly, up to some extent the DC power consumption is minimized. This happens only under some combinations of input which do not turn on PDN. In this technique, one PMOS transistor can also be used in similar way with a condition that gate of PMOS transistor should be connected to output.

A feedback NMOS transistor is employed in the mirror technique. This feedback transistor is employed in exactly similar way like the NMOS pull up technique [82]. This duplicates the PDN to decrease the power consumption and increase the noise tolerance performances. In Fig.2.16(d) a domino AND2 gate was designed with the above mentioned mirror technique. The mirror network is OFF whenever the pull down network goes OFF, which cuts off DC conducting path from the NMOS pull up transistor through the clocked transistor. In this manner, this circuit totally eliminates the DC power consumption. But, this mirror technique stretches the discharge path significantly in the PDN, this condition probably slows the circuit operation. This logic style sufficiently increases circuit active area which leads to increase the size of the circuit.

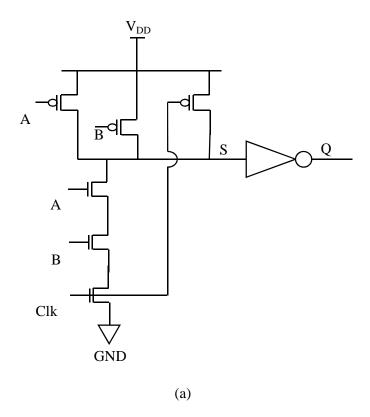

Fig.2.16 Raising source voltage of AND2 gate, (a) PMOS pull up technique [80], (b) NMOS pull up technique with feedback [81], (c) Mirror technique [82], (d) Twin transistor technique [83]

The twin transistor technique [83] [84] is a method to raise the source voltage of the dynamic gate. This technique contains a NMOS pull up transistor at each internal node for improvement of noise immunity of dynamic logic. Furthermore, the drain of each of the NMOS pull up transistor is connected to input in place of  $V_{DD}$ , as explained in