1

# Analytic and Simulation Results about a Compact, Reliable and Unbiased 1-bit Physically Unclonable Constant

Riccardo Bernardini and Roberto Rinaldo DIEGM – University of Udine Via delle Scienze 208, 33100 Udine, Italy Email: {riccardo.bernardini,rinaldo}@uniud.it}

*Abstract*—Physically Unclonable Constants (PUC) are circuits used to embed unique secret bit-words in chips. We propose a simple PUC, with a complexity comparable with an SRAM cell. The proposed scheme is studied both theoretically and by means of simulations and it is shown that the proposed PUC is both unbiased and very stable. In particular, its intra-distance is predicted to be from 10 to 100 times smaller than competitor schemes. Simulations allow to conclude that the advantages of the proposed scheme are relevant enough to make it competitive even if the actual performance of a real implementation, not considered in this paper, will turn out to be an order of magnitude worse than predicted.

*Index Terms*—security, physically unclonable functions, chip authentication

This copy of the manuscript shows in blue the most important changes done to the manuscript. This copy is provided for reviewers' convenience and submitted as *Supporting Documentation*. An official, non-marked copy is submitted as *Main Document*.

#### I. INTRODUCTION

The necessity of verifying the authenticity of a chip in a simple and secure way gave rise to the introduction of Physically Unclonable Functions (PUFs) [1]–[6]. A PUF is a circuit that implements a map from bit-words to bit-words, with the actual map very sensitive to the exact values of process parameters (e.g., the exact channel length of a MOSFET or the exact doping level). As a consequence of such dependence, the map implemented by a specific chip will be unique to that chip and this can be used to verify the identity of the chip [7], [8]. Moreover, such a sensitivity makes it very difficult to replicate the PUF of a specific chip. In a sense, a PUF is like a fingerprint: as each person has a unique fingerprint whose minutiae are the result of casual variations during the fetal development, every chip has its own PUF that is the result of casual variations during chip production.

A special type of PUF is a PUF with no input arguments, that is, a constant. For this special type of PUF are called *weak PUFs*, *Physically Obfuscated Keys* (POK) or Physically Unclonable Constant (PUC). PUCs can be used to embed in chips secret bit-strings that can be used, for example, as private keys for encryption or authentication or as source of randomness in special applications [10].

The ideal PUC is a *random constant* [11], [12] in the sense that at production time a random bit value (called in the following the *preferred outcome*) is uniformly selected and every time the PUC is queried said selected value is returned. Real PUCs, however, can depart from ideality in two respects: (i) sometimes the PUC can make an *error*, not returning the preferred outcome and (ii) the selection of the preferred outcome could be not uniform. These two forms of non-idealities suggest two PUC quality indices: *stability* (a stable PUC always returns the preferred outcome with overwhelming probability) and *unbiasedness* (in an unbiased PUC the preferred outcome is uniformly selected at construction time). It is clear that reliability is very important since in many security applications a single wrong bit can render the whole system useless.

The problem of improving the reliability of a PUC stimulated research in the field of *PUC stabilizers* [7], [9], [13]– [16]. It is worth observing that every stabilizer proposed in the literature introduces some kind of "redundancy," (e.g., syndrome bits in helper-based schemes [7], [13]–[15], spare cells or repeated turn-ons in helper-less schemes [9], [16]) and that less reliable PUCs require more redundancy to be stabilized. Therefore, there is interest in designing reliable PUC schemes that can be used with low-redundancy stabilizers or, better, so reliable that no stabilizer is required.

#### A. Prior Work

Among the PUCs the most popular schemes are based on SRAM or similar structures [17]–[22]. In [17] the initial state of a non-initialized SRAM is used as the PUC outcome. In [18], [20] a latch-like structure is used to amplify an offset voltage. A different approach based on the measure of the data retention voltage of an SRAM is described in [21]. In [23] a PUC amplifying the difference in the threshold voltage of two NMOS is described; an approach very similar to [18], [20], [23] is described in [24] where the variations in the threshold voltage of MOSFETs are used to generate voltages that are mapped to 0 or 1 by a comparator made with two inverters; an approach based on Flash memory is proposed in [25]; [26] exploits the antenna effect in order to randomly break the gate oxide. The schemes based on uninitialized SRAM or latches [17], [18], [20] have the drawback that the underlying structure has two stable states and it can happen that the PUC ends in

the "wrong" state. For example, according to [20], 4% of the latch-based cells are "unstable." According to [6], a similar result holds also for SRAM-based schemes. SRAM schemes gave rise also to some work about counteracting aging. In [27] presents some anti-aging techniques which are based on data-dependent aging effects, while [28] develops new metrics to analyze the relationship of reliability between neighboring SRAM cells. Said metrics are used to examine in detail the impact of environment.

Schemes based on comparators fed with random voltages like [23] and [24] have the drawback that, given the continuity of the transfer function of a real comparator, there is a non negligible probability of having cells whose output is sensitive to noises. In [24] a 5% of unstable bits is reported.

Although the scheme of [26] is interesting because of its stability and low power consumption, it is suggested the overvoltage used to break the oxide could cause chip degradation [23].

# B. Our contribution

The very simple 1-bit PUC described in this paper originated from the analysis of the causes of the mediocre stability (i.e., an intra distance  $\mu_{intra}$  [29] ranging from 3% to 12% [6], [19], [24]) that characterizes the schemes that are more similar to our proposal, namely, memory-based approaches (e.g., SRAM and latch) [17]–[20] and comparator-based approaches [23], [24]. As said above, such a stability is due to the presence of two stable states (memory-based PUCs) or to the continuity of the implemented map (comparator-based PUCs).

This observation suggested us to search for a system that (i) has one and only one stable state and (ii) the position of the stable state is a discontinuous function of the circuit "unbalance." The existence of only one equilibrium state makes the system very robust: *independently* on the initial condition or any initial transitory noise, the system will evolve, sooner or later, to the unique equilibrium point. The result is a PUC whose intra-distance  $\mu_{intra}$  [29] is predicted to be 10 to 100 times smaller than the intra-distance of similar schemes.

In this paper we describe our PUC proposal, together with a thorough analysis of its behavior, first in a qualitative way, then in a more analytic way and, finally, by means of simulations. The simulations show that the theoretical predictions still hold even when the simple models used for the theoretical analysis are replaced by the more complex and precise models used in the simulations, making the theoretical predictions quite convincing.

We choose this approach, rather than directly measuring the circuit behavior, because we wanted to achieve a good understanding of how the circuit behavior is affected by the circuit parameters, in order to determine some design guidelines. Some of the guidelines (e.g., use "long and thin" transistors) are actually not obvious and difficult to find by only experimental analysis.

Of course the final confirmation of the performance of the proposed scheme can only come from experiments that will also allow to analyze some aspects (local biasing [30], aging, temperature dependence) not considered in detail here for the

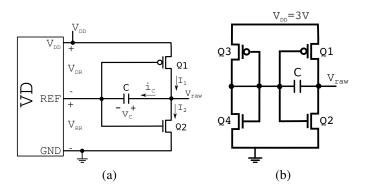

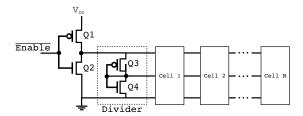

Figure 1. (a) The proposed 1-bit PUC (b) The instance used in the simulations, with a MOSFET-based voltage divider

lack of suitable models. The experimental assessment of the behavior of the proposed PUC will be the subject of future investigation.

# C. Structure of this paper

In Section II we introduce some preliminary remarks about nomenclature, quality measure and security discussion. In In Section III we introduce the proposed scheme and do a first, qualitative analysis. Before moving to a more analytic study in Section V, Section IV introduces some notation and some strategies that will be used for the analysis. Section V presents an analytic study of our solution. Noise impact is studied in Section VI and the results are used in Section VII to determine the quality of our scheme. Other issues, like the dependence of the behavior from the temperature, aging and cell size, are analyzed in Section VIII. The study is completed with some simulations whose results are given in Section IX. Finally, Section X gives the conclusions and describes future research directions.

## D. Summary of Results

In this section we briefly summarize the main results in this paper. In order to do this, it is convenient to anticipate briefly how our scheme works. Consider the scheme of Fig. 1a where transistors Q1 and Q2 are designed to be *nominally* matched. Call  $I_0$  the current on C at t = 0. Symmetry considerations suggest that if Q1 and Q2 were exactly matched, it would be  $I_0 = 0$ . However, Q1 and Q2 will never be exactly matched and this will cause a current  $I_0 \neq 0$  on C. It will be shown in the following that the outcome of the PUC depends only on the sign of  $I_0$ .

We will denote with  $I_s$  the saturation current of Q1 and Q2, with  $V_{eq}$  the value of  $v_C$  at equilibrium and with  $\overline{I}_0 = I_0/I_s$ an adimensional version of  $\overline{I}_0$ . It turns our that  $\overline{I}_0$  is the most important quantity in our scheme.

The main results of this paper are the following

• The key result is that the circuit of Fig. 1a has one and only one equilibrium point (stable) whose position is a discontinuous function of  $\bar{I}_0$ . If the channel length modulation can be neglected ( $\lambda \approx 0$ ), it is  $|V_{eq}| > V_T$  even for very small  $|I_0|$ . This makes our scheme robust to noise. If  $\lambda > 0$  the results remain qualitatively the same, with the difference that in order to have  $|V_{eq}| > V_T$  it is necessary to have  $|\bar{I}_0| > 2\lambda V_T$ . See Sections III, V-A and V-B for more details.

- Current  $\overline{I}_0$  is a convenient "quality measure" of a specific instance. Not only cells with larger  $|\overline{I}_0|$  are more insensitive to noise, but they are also less sensitive to temperature changes (Section VIII-A) and aging (Section IX-C). This can be exploited to disable at the first turn-on the less reliable cells, i.e., with small  $|\overline{I}_0|$ . See Section VIII-C3.

- We give an *analytical statistical characterization* of our scheme, including the *power of noise* affecting the cell (Section VI and (27)), the *Probability Density Function* (*pdf*) of  $\bar{I}_0$  and the *pdf of V<sub>eq</sub>* (Section VII-B, equations (31) and (32)). This allows us to predict analytically that our scheme can have an *intra distance as small as*  $10^{-4}$  and an *inter-distance* pratically *equal to* 1/2. See Sections VII-C and IX-D.

- We provide some *design guidelines*. For example, C should be choosed as small as possible, compatibly with the load, while the transistors should be "long and thin." See Section VIII-C

- We estimate the cost in terms of *silicon area* and predict that our scheme is quite *competitive*, taking into account that the very small intra-distance allows us to use smaller error-correction codes o no correction at all. See Section IX-D2 and tables III, IV and V.

- It is possible to implement this scheme so that the *energy required* is a fraction of nJ/bit. See Section V-E.

- Our scheme is *stable* with respect *aging* (Section IX-C) and *temperature variation* (Sections VIII-A and IX-A). Moreover, property  $|V_{eq}| > V_T$  makes our scheme *robust with respect to power variations*, since  $V_T$  does not depend on the supply voltage. See Section IX-B and Fig. 8.

1) Limit of the analytic/simulation approach: Although the analytic study of the circuit allows us to understand better the impact of the different variables on the final outcome, they are nevertheless based on models. It is clear that only actual experiments on prototypes can say the final word about the performance of the proposed scheme. One could wonder how much likely is that the results described in this paper will be confirmed by experiments.

- The main characteristic of our scheme (*only one stable equilibrium point*) is expected to hold in every case, since it depends only on the "saturating" and monotone behaviour of the transistors.

- Also that the *discontinuity property*  $|V_{eq}| > V_T$  is expected to hold since it is a direct consequence of said saturating behaviour. Also the *stability* against *supply voltage variations* is expected to hold.

- The *statistical characterization* in Section VII-B are expected to hold qualitatively, since the hypothesis used to derive them are quite weak (basically, the distribution of the characteristics of the transistors is approximately Gaussian). Of course, the quantitative details can change, they could even depend on the specific foundry.

- The difference of *performance* between the proposed

scheme and schemes in the literature (Section IX-D2) is so large that we expect that the proposed scheme will maintain its competitiveness.

• Because of the loss of suitable models, the predictions that are on a shaker ground and that can be verified only experimentally are those relative to the *temperature dependence* (Sections VIII-A and IX-A), *aging* (Section IX-C) and *local bias* (Section VII-E).

Summarizing, we expect that most of the characteristics described in this paper will qualitatively hold also in an actual silicon prototype, although there can be deviations on a quantitative level.

#### **II. PRELIMINARY REMARKS**

# A. Nomenclature

Depending on the context, "PUC" can mean both the nominal circuit (e.g., the circuit in Fig. 1) or a specific implementation of it (e.g., a specific cell in a specific chip). This double use makes discussion difficult and introduces ambiguities. Therefore, we will say *PUC scheme* to refer to the abstract scheme and *PUC instance* to refer to a specific physical implementation [31].

Observe that a PUC can be modeled as a two-step experiments: (i) when a PUC instance is built, the instance *preferred outcome* (*PO*) and the corresponding probability is determined, successively (ii) when the instance is queried, an outcome is randomly drawn according to the probability selected at construction time.

Informally, a PUC *instance* is said to be *stable* if every time it is queried it gives PO with overwhelming probability. A PUC *scheme* is said to be *stable* if its instances are reliable with large probability. Finally, a PUC scheme is said to be *independent* if the POs of different instances are independent random variables (r.v.). These concepts are made more precise in the following section.

## B. Quality measures

Two standard quality measures for PUF are the *inter*distance  $\mu_{inter}$  (the distance between the two responses resulting from applying the same challenge to two different PUFs) and the *intra-distance*  $\mu_{intra}$  (the distance between the two responses resulting from applying the same challenge twice to the same PUF) [29]. However, since a PUC has no inputs, these two measures are not directly applicable and another approach is required [9], [31].

Let  $p_1$  be the probability that a specific instance will return "1" when queried and let  $O_{\text{pref}}$  be the corresponding PO, that is,  $O_{\text{pref}} = 1 \Leftrightarrow p_1 > 1/2$ . Note that  $p_1$  and  $O_{\text{pref}}$  are r.v. drawn at construction time. The *stability* of the *instance* is defined in [9], [31] as

$$R(p_1) \stackrel{\text{def}}{=} 2|p_1 - 1/2| \tag{1}$$

Note that R(0) = R(1) = 1 (perfect stability) and R(1/2) = 0 (instability). Function *R* measures the stability of an *instance*, in order to measure the stability of a *scheme*, one can use the *Stability Distribution Function* (SDF) [9], [31]

$$F_r(x) = \mathbf{P}[R(p_1) \le x] \tag{2}$$

Finally, we define the *bias* of a PUC scheme as  $\varepsilon_P = |P[O_{\text{pref}} = 1] - 1/2|$ . If  $\varepsilon_P = 0$  the scheme is *unbiased*.

1) Relationship between the SDF,  $\mu_{intra}$  and  $\mu_{inter}$ : It possible to show by basic algebra (see Appendices A-A and A-B) that from the SDF one can compute  $\mu_{intra}$  amd  $\mu_{inter}$  as follows

$$\mu_{\text{intra}} = \int_0^1 F_r(x) \, x \, dx \lesssim \int_0^1 F_r(x) \, dx \tag{3a}$$

$$\mu_{\text{inter}} = 2(m_p - m_p^2) = \frac{1}{2} - 2\eta^2$$

(3b)

where  $m_p = 1/2 + \eta = \mathbb{E}[p_1]$  is the mean of  $p_1$  and the approximation in (3a) is good when the PUC scheme is stable.<sup>1</sup>

# Remark II.1

Both  $\varepsilon_P = 0$  and  $\mu_{inter} = 1/2$  are indications of the unbiasedness of a PUC scheme. Curiously, they are not equivalent and it can happen that one condition holds, while the other does not. However, it is easy to see that they are practically equivalent when the scheme is *stable*, that is, when the pdf of  $p_1$  is concentrated around 0 and 1.

#### C. Security Discussion

A detailed security analysis would require to know how the secret outcome of the PUC is used. However, on a general level, we can say that there are two possible attacks: (i) attack the cryptographic protocol employed, or (ii) use a (smart) brute-force attack to guess the outcome of the PUC. Note that the probability of success of the first kind of attack depends mostly on the protocol employed, not on the quality of the PUC. Therefore, a discussion about this type of attack is out of scope here.

The quality of the PUC determines the probability of success of the second kind of attack. Brute-force search could be done, possibly, in a smart way by trying first the most probable outcomes [36]. Clearly, the effort of the attacker is maximized when the outcomes are uniformly distributed. This happens *if and only if* the PUC is *independent* and *unbiased*. Therefore, employing a PUC with small  $\mu_{intra}$  and large  $\mu_{inter}$  together with a good cryptographic protocol guarantees the maximization of security.

#### **III. QUALITATIVE DISCUSSION**

The objective of this section is to give some intuition about our solution by means of a qualitative description. In order to keep the discussion simple, some hypothesis of ideality will be done. A more precise and analytic description, with the ideality hypothesis removed, is given in Section V.

Fig. 1 shows the proposed PUC. The block marked with VD is a *voltage divider* that, in the ideal case considered here, splits in half the supply voltage  $V_{DD}$  so that  $V_{DR} = V_{RR} = V_{DD}/2$ , independently from the current drawn from its terminals (a more realistic model is introduced later). Transistors Q1 and Q2 are designed to be *nominally* matched (that is, the nominal values of their threshold voltage and transconductance parameters are equal) and in saturation when the capacitor is uncharged. Of course, in a real instance Q1

and Q2 will never be exactly matched and, indeed, our scheme actually *exploits* this unavoidable mismatch.

#### Remark III.1

It would seem that the proposed scheme is a comparator-based scheme [23], [24] that "amplifies"  $V_{RR}$ , relying on the fact that it will always be  $V_{RR} \neq V_{DD}/2$ . This would be correct if Fig. 1 did not include capacitor C whose duty is to introduce a feedback that forces at equilibrium  $|V_{raw} - V_{RR}| > V_T$  as soon as the two MOSFETs are not perfectly balanced, differently from comparator-based schemes [23], [24].

The circuit is turned on at t = 0 with C uncharged (it will be clear in the following that any initial charge on C has no effect on the equilibrium). After a time  $t_{\text{max}}$  the value of  $V_{\text{raw}}$  is acquired and mapped to "0" or "1". We are interested in understanding qualitatively how  $V_{\text{raw}}$  is related to the asymmetries of a specific instance of Fig. 1.

Consider first the impossible case where all the components have their nominal values. Since the MOSFETs are matched,  $I_{D,1} = I_{D,2}$ , no current flows in the capacitor branch, the capacitor remains uncharged and  $V_{\text{raw}} = V_{RR}$  forever.

Suppose now that the components have not their nominal value, so that one of the MOSFETs, say Q1, conducts more, that is,  $I_{D,1} > I_{D,2}$ . It follows that  $i_C > 0$  which causes  $v_C$  to increase. As long as  $v_C$  is smaller than the threshold voltage  $V_T$  of Q1, both Q1 and Q2 remain in saturation, currents  $I_{D,1}$ ,  $I_{D,2}$  and  $i_C$  remain constant and C charges linearly with time. However, when  $v_C > V_T$ , Q1 enters the triode region,  $I_1$  decreases and  $i_C$  decreases, too. The system reaches an equilibrium when the  $v_C$  is equal to a value  $V_{eq} > V_T$  such that  $I_{D,1} = I_{D,2}$ . A similar reasoning would show that if Q2 conducts more at the equilibrium,  $v_C < -V_T$ . Note that in both cases we are granted that  $|V_{eq}| > V_T$  since in order to have equilibrium one of the two MOSFETs must be in the triode region.

We can summarize the results of this qualitative analysis in the following observation.

**Observation 1.** The absolute value  $|V_{eq}|$  of equilibrium voltage is larger than  $V_T$  and the sign of  $V_{eq}$  is equal to the sign of the difference of the saturation currents  $I_{D,i}$ , i = 1, 2.

It follows that the region  $[-V_T, V_T]$  is *forbidden* for  $V_{eq}$  since map  $(I_{D,1} - I_{D,2}) \mapsto V_{eq}$  is *discontinuous*, jumping from  $-V_T$  to  $V_T$  at  $I_{D,1} - I_{D,2} = 0$ . This is very different from comparatorbased schemes [23], [24] that are continuous functions that map small deviations into small output differences.

#### **IV. PRELIMINARY REMARKS**

Before moving to a more quantitative analysis of Fig. 1, it is useful to summarize few conventions used in the paper.

#### A. A model for the voltage divider

As said before, the block marked with  $\forall D$  in Fig. 1 represents a generic "voltage divider." In the ideal case, the block  $\forall D$  is characterized by having always  $V_{DR} = V_{RR}$  for every value of the currents drawn from its terminals. In practice we expect two deviations from ideality: (i)  $V_{DR}$  and  $V_{RR}$  will not be equal (but their sum will be always equal to  $V_{DD}$ ) and (ii) the value of  $V_{RR}$  will depend on  $i_C$ . In this paper we will use the following very general model for  $\forall D$  (see also Fig. 2):

<sup>&</sup>lt;sup>1</sup>A stable scheme has  $F_r(x) \approx 0$  as soon as x is slightly less than 1.

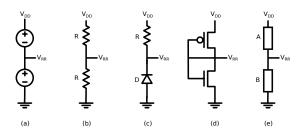

Figure 2. Examples of dividers that agree with the model considered in this paper. (a) An ideal and unbiased divider (b) A resistor-based divider. (c) A zener-based divider. (d) The MOSFET based divider used in the simulations. (e) A generic divider using two dipoles with positive differential resistance.

**Hypothesis 1.** With the conventions used in Fig. 1,  $V_{RR}$  is a monotone non-decreasing function of  $i_C$ . The value of  $V_{RR}$  when  $i_C = 0$  will be written  $V_{RR}^{\circ}$ . If  $V_{RR} = V_{RR}^{\circ}$  for every value of  $i_C$ , the divider is ideal; if  $V_{RR}^{\circ} = V_{DD}/2$ , the divider is unbiased.

## B. Notation

In the following we will use the common convention of using lowercase letters for time-varying values and uppercase letters for constant values. About the MOSFETs, we will use the convention that makes the voltages and currents associated with the MOSFETs always positive [37]. For example, we will consider the gate-source voltage of Q2 (denoted as  $V_{GS,2}$ ), but the source-gate voltage of Q1 (denoted as  $V_{GS,1}$ ). Note that with this convention both transistors have a positive threshold voltage and their I-V characteristic can be written as [37]

$$I_{D,i} = \begin{cases} \frac{\beta_i}{2} \left[ 2(V_{GS,i} - V_{Ti}) - V_{DS,i} \right] V_{DS,i} & V_{DS,i} < V_{DSS} \\ \frac{\beta_i}{2} V_{DSS}^2 \left[ 1 + \lambda (V_{DS,i} - V_{DSS}) \right] & V_{DS,i} \ge V_{DSS} \end{cases}$$

(4)

where  $V_{DSS} = V_{GS,i} - V_{Ti}$  and  $\lambda$  is the channel length modulation parameter. Finally,  $W_i$ ,  $L_i$ ,  $\mu_i$  and  $N_{d,i}$  denote, as usual, the width, the length, the mobility and the nominal doping of Qi. Oxide capacity and nominal thickness will be denoted as  $C_{\text{ox}}$  and  $t_{\text{ox}}$ . When discussing deviations from nominal values, we will use  $\tilde{N}_{d,i}$  and  $\tilde{t}_{\text{ox}}$  to denote the actual doping levels and oxide thickness.

We will denote the *nominal* values of transconductance parameter and threshold voltage as  $\beta$  and  $V_{\rm T}$ , while the corresponding *actual* values for transistor Qi, i = 1, 2, will be denoted as  $V_{\rm Ti}$  and  $\beta_i$ . It is convenient to have a notation for  $V_{\Delta} = V_{DD}/2 - V_{\rm T}$  and for the saturation currents (actual and nominal)

$$I_{s,i} = \frac{\beta_i}{2} (V_{GS,i} - V_{Ti})^2 \qquad i = 1,2 \qquad (5a)$$

$$I_s = (\beta/2)(V_{DD}/2 - V_{\rm T})^2 = \beta V_{\Delta}^2/2$$

(5b)

Finally, a special role will be played by the difference of the saturation currents

$$I_0 \stackrel{\text{def}}{=} I_{s,1} - I_{s,2} = \frac{\beta_1}{2} (V_{DR} - V_{T1})^2 - \frac{\beta_2}{2} (V_{RR} - V_{T2})^2 \qquad (6)$$

that will be shown to represent the "unbalance" of the circuit. Note that  $V_{\rm T}$ ,  $\beta$  and  $I_s$  are design parameters, while  $V_{\rm Ti}$ ,  $\beta_i$ ,  $I_{s,i}$  and  $I_0$  are r.v., since they depend on construction time variations.

#### C. Adimensional Equations

It will be convenient to write most of the equations in an adimensional form, obtained by dividing tensions, currents, ... by suitable reference values. The reference values for voltages and currents will be, respectively, the nominal threshold voltage  $V_{\rm T}$  and the nominal saturation current  $I_s = \beta V_{\Delta}^2/2$ , while the reference value for times will be  $\tau = CV_{\rm T}/I_s$  that can be interpreted as a "time constant" of the circuit. The adimensional version of a variable will be denoted with a line above. For example, the adimensional version of  $v_C$  is  $\bar{v}_{\rm C} = v_C/V_{\rm T}$ . We will also use  $\theta = 2\lambda V_{\rm T}$ .

#### Remark IV.1

It is convenient to select some typical parameter values (e.g.,  $W_i$ ,  $L_i$ ,  $t_{\text{ox}}$ , ...) in order to have an idea of the order of magnitude of the values involved. Table I shows the values used in this paper. Parameters  $S_V$ ,  $S_\beta$  and  $S_X$  are defined in Section VII.

## V. QUANTITATIVE ANALYSIS

In this section we do a more quantitative analysis of the proposed circuit. Our first step will be to find an analytic expression for map  $v_C \mapsto i_C$ . This will be instrumental to find the equilibrium voltage  $V_{eq}$  and a suitable value of  $t_{max}$ . For the sake of simplicity we will first suppose VD ideal, but not necessarily unbiased (see Hypothesis 1). The case of a non-ideal VD is analyzed in Section V-C1.

#### A. Map $v_C \mapsto i_C$

By writing  $I_{D,1}$  and  $I_{D,2}$  as functions of  $v_C$  and taking their difference, it is possible to show by basic algebra that (see Appendix B-A)

$$\bar{i}_{\rm C}(\bar{v}_{\rm C}) = \begin{cases} \bar{I}_0 - \operatorname{sgn}\bar{v}_{\rm C} \left[ \theta - \frac{\theta}{2} (1 - |\bar{v}_{\rm C}|) + \frac{(1 - |\bar{v}_{\rm C}|)^2}{\bar{v}_{\Delta}^2} \right] & |\bar{v}_{\rm C}| > 1\\ \bar{I}_0 - \theta\bar{v}_{\rm C} & |\bar{v}_{\rm C}| < 1 \end{cases}$$

(7)

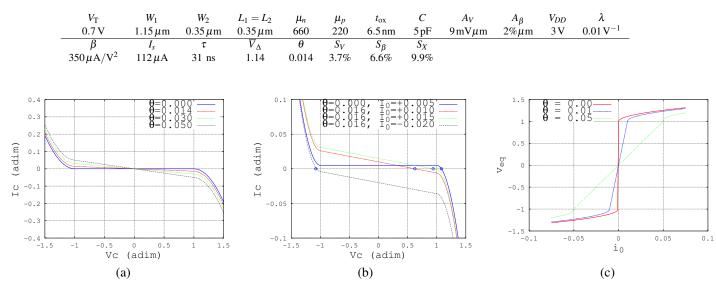

Fig. 3 shows some examples of function  $\bar{i}_{\rm C}(\bar{v}_{\rm C})$ . Function  $\bar{i}_{\rm C}(\bar{v}_{\rm C})$  can be described as an odd function with an offset  $\bar{I}_0$ . Function  $\bar{i}_{\rm C}$  has three segments: two quadratic ones (for  $|\bar{v}_{\rm C}| > 1$ ) and a linear one with slope  $\theta = 2\lambda V_{\rm T}$ . In the ideal case  $\lambda = 0$ , the segment is horizontal. Note that all the asymmetries of the circuit are collected inside  $\bar{I}_0$  that can be interpreted as a measure of the asymmetry of the circuit.

# B. Equilibrium analysis

It is obvious that  $v_C$  evolves according to

$$C \dot{v}_C(t) = i_C(v_C(t)) \qquad t \ge 0 \tag{8}$$

with  $v_C(0) = 0$ . In (8), as usual,  $\dot{v}_C$  denotes the time derivative of  $v_C$ . The circuit is at equilibrium if and only if  $i_C = 0$ . Therefore, in order to find  $V_{eq}$  we need to find the zeros of  $i_C(v_C)$ . A key property of our scheme is that  $i_C(v_C)$  has only one zero, so the cell has only one equilibrium point.

**Property 1.** Map  $i_C(v_C)$  is monotone non-increasing and it is strictly decreasing if and only if  $\lambda > 0$ . If  $\lambda = 0$ ,  $i_C(v_C)$  is constant for  $v_C \in [-V_{T2}, V_{T1}]$  and strictly decreasing otherwise.

Table I

Reference values used in the paper and in the simulations. Mobilities  $\mu_p$  and  $\mu_n$  are in cm<sup>2</sup>/V s. Parameters  $\overline{V}_{\Delta}$ ,  $\theta$ , ...,  $S_X$  are adimensional.

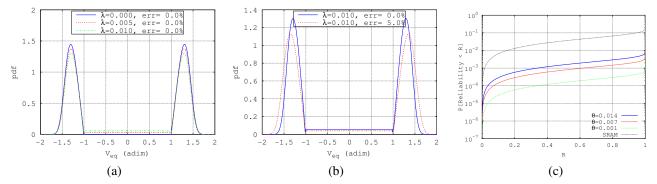

Figure 3. (a) Curves  $\bar{i}_C$  vs  $\bar{v}_C$  for several values of  $\theta$ ,  $\bar{V}_{\Delta} = 1.14$  and  $\bar{I}_0 = 0$ . (b) Curves  $\bar{i}_C$  vs  $\bar{v}_C$  for several values of  $\theta$ ,  $\bar{V}_{\Delta} = 1.14$  and different values of  $\bar{I}_0$ . The little circles mark the equilibrium values of  $\bar{V}_{eq}$ . Note the large value of  $\bar{V}_{eq}$  for the case  $\theta = 0$ , despite it has the smallest  $|\bar{I}_0|$ . (c) Plots of  $\bar{V}_{eq}$  vs  $\bar{I}_0$  for different values of  $\theta$ .

Figure 4. Examples of time evolution for several values of  $\theta$ ,  $\overline{V}_{\Delta} = 1.14$  and  $\overline{I}_0 = \pm 0.015$

*Proof.* It suffices to observe that  $i_C = I_{D,1} - I_{D,2}$ , and that  $I_{D,1}$  ( $I_{D,2}$ ) is monotone decreasing (increasing) with  $v_C$ .

An immediate consequence of monotonicity is the following corollary that, albeit simple, is a cornerstone result.

**Corollary 1.** If  $I_0 \neq 0$  there is one and only one  $V_{eq}$  such that  $i_C(V_{eq}) = 0$ . Moreover,  $i_C'(V_{eq}) < 0$ , so  $V_{eq}$  is a stable equilibrium point.

Indeed, the fact that our cell has only one equilibrium point grants that every time the cell is turned on *it will always evolve toward the same value* of  $V_{eq}$ , independently on any temporary disturbance such as a turn-on noise at t = 0 or some residual charge on C at t = 0. This is to be compared with the behavior of the SRAM which, having *two* equilibrium points, can sometimes end in the "wrong" one.

It is possible to write explicitly  $V_{eq}$  as a function of  $I_0$

$$\overline{V}_{eq}(\overline{I}_0) = \begin{cases} \overline{I}_0/\theta \\ \operatorname{sgn}\overline{I}_0 \left[ (R+1) + \sqrt{R^2 + \overline{V}_{\Delta}^2(|\overline{I}_0| - \theta)} \right] |\overline{I}_0| \le \theta \\ |\overline{I}_0| \ge \theta \end{cases}$$

(9)

where  $R = \theta \overline{V}_{\Delta}^2/4$ . As for (7), the proof is simple but long and given in detail in Appendix B-B. Equation (9) in the special case  $\lambda = 0$  becomes

$$\overline{V}_{eq}(\overline{I}_0) = \operatorname{sgn}(\overline{I}_0) \left( 1 + \overline{V}_\Delta \sqrt{|I_0|} \right)$$

(10)

A graph of (9) can be found in Fig. 3c for some values of  $\theta$  and  $\overline{V}_{\Delta} = 0.8/0.7 \approx 1.14$ . Note that for  $\lambda = 0$  function (9) is discontinuous in  $\overline{I}_0 = 0$ , as anticipated in Section III. If  $\lambda > 0$ , function (9) is continuous with a central part which is linear and with a slope proportional to  $1/\lambda$ . Note that if  $\overline{I}_0 > \theta$ ,  $|\overline{V}_{eq}| > 1$ , that is  $|V_{eq}| > V_T$ . This suggests the following definition

**Definition 1.** An almost balanced instance has  $|\overline{I}_0| < \theta$ .

#### C. Time evolution

Now we solve (8) in order to find an expression for  $v_C(t)$  that will be used in Section V-D to find  $t_{\text{max}}$ . First, rewrite (8) in adimensional form.

**Lemma 1.** Let  $\tau = CV_T/I_s$  and let

$$u(\bar{t}) = \bar{v}_C(\tau \bar{t}) \tag{11}$$

be the version of  $\bar{v}_C$  with adimensional time. Function u satisfies the following adimensional form of (8) with u(0) = 0.

$$\dot{u} = \bar{i}_C(u; \bar{I}_0, \theta, \bar{V}_\Delta) \tag{12}$$

*Proof.* Bring (8) in adimensional form by dividing by  $I_s$  and *and, moreover, the following inequalities hold*  $V_{\rm T}$  to obtain

$$\begin{cases} \tau \, \dot{\bar{v}}_C(t) = \bar{i}_C(\bar{v}_C(t)) \\ \bar{v}_C(0) = 0 \end{cases}$$

(13)

By rewriting (11) for  $t = \tau \bar{t}$  and observing that  $\dot{u}(\bar{t}) = \tau \, \dot{\bar{v}}_C(\tau \bar{t})$ , (13) becomes (12).

Remark V.1

According to (11),  $\bar{v}_{\rm C}(t)$  can be obtained by time-stretching by a factor  $\tau$  the solution of (12). In a sense,  $\tau$  can be interpreted as a "time constant" of the proposed scheme.

**Property 2.** Suppose  $\lambda > 0$  and define

$$R = \frac{\theta \overline{V}_{\Delta}^2}{4} \approx 0 \tag{14a}$$

$$A = \sqrt{(|\bar{I}_0| - \theta)\overline{V}_{\Delta}^2 + R^2} \approx \overline{V}_{\Delta} \sqrt{|\bar{I}_0|}$$

(14b)

$$B = \frac{A}{\overline{V}_{\Delta}^2} = \sqrt{\frac{|\overline{I}_0| - \theta}{\overline{V}_{\Delta}^2}} + \frac{\theta^2}{16} \approx \sqrt{|\overline{I}_0|} / \overline{V}_{\Delta} \quad (14c)$$

$$C = \tanh^{-1}\left(\frac{R}{A}\right) = \tanh^{-1}\left(\frac{\theta}{4B}\right) \approx 0$$

(14d)

$$U = \frac{1}{\theta} \left( \bar{I}_0 + \frac{\theta(\bar{I}_0 - \bar{\Delta}_\nu)}{2} \right) \approx \frac{\bar{I}_0}{\theta}$$

(14e)

$$\bar{t}_{sw} = \begin{cases} -\frac{1}{\theta} \ln\left(1 - \frac{\theta}{|\bar{I}_0|}\right) \approx \frac{1}{|\bar{I}_0|} & |\bar{I}_0| > \theta \\ \infty & |\bar{I}_0| \le \theta \end{cases}$$

(14f)

where the approximations are valid when  $\lambda \to 0$ . Let also  $w : \mathbb{R}_+ \to \mathbb{R}$  be defined as

$$w(t; \overline{I}_0, \theta, \overline{V}_\Delta) \stackrel{def}{=} A \tanh(Bt + C) + R \qquad t \ge 0 \qquad (15)$$

With the notation above, the solution of (12) can be written as

$$u(\bar{t}) = \begin{cases} U[1 - \exp(-\theta \bar{t})] & 0 \le \bar{t} < \bar{t}_{sw} \\ \operatorname{sgn} \bar{I}_0 \left[ w(\bar{t} - \bar{t}_{sw}; |\bar{I}_0|, \theta, \overline{V}_\Delta) + 1 \right] & \bar{t}_{sw} \le \bar{t} \end{cases}$$

(16)

The proof is just basic algebra, but very long and it is given in detail in Appendix B-C. By taking the limit  $\lambda \to 0$  one obtains the evolution in the ideal case

$$u(\bar{t}) = \begin{cases} \bar{I}_0 \bar{t} & 0 \le \bar{t} < \bar{t}_{sw} = 1/|\bar{I}_0 \\ \overline{V}_\Delta \sqrt{\bar{I}_0} \tanh\left(\frac{\sqrt{\bar{I}_0}}{g}(\bar{t} - \bar{t}_{sw})\right) & 1/|\bar{I}_0| \le \bar{t} \end{cases}$$

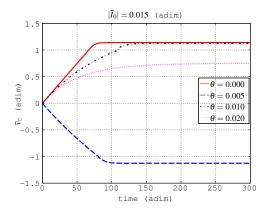

Fig. 4 shows few examples of time evolution for several values of  $\theta$ ,  $\overline{V}_{\Delta} = 1.14$  and  $\overline{I}_0 = \pm 0.015$ .

1) The case of a non-ideal divider: The main results of the non-ideal voltage divider is contained in this Property.

**Property 3.** Let  $i_C(v_C)$  be the current on C when an ideal divider with open voltage  $V_{RR}^{\circ}$  is employed, let  $V_{eq}$  be the corresponding equilibrium voltage and let  $\hat{i}_C(v_C)$  be the current on C when a non-ideal divider, with the same  $V_{RR}^{\circ}$ , is employed. Moreover, define  $R_{max} = \sup dV_{RR}/dI \ge 0$  and  $\Gamma = \sup(-\partial i_C/\partial V_{RR})$ .

**Thesis:** Function  $\hat{i}_C(v_C)$  is monotone non-increasing it has the same zero as  $i_C$ , that is,

$$\hat{\imath}_C(V_{eq}) = i_C(V_{eq}) = 0 \tag{17}$$

$$\frac{1}{1+\Gamma}i_C(x) \le i_C(x) \le i_C(x) \qquad x \le V_{eq}$$

(18a)

$$\frac{1}{1+\Gamma}i_C(x) \ge \hat{\iota}_C(x) \ge i_C(x) \qquad x > V_{eq}$$

(18b)

Property 3 can be informally summarized by saying that a non-ideal divider does not change the equilibrium point (because of (17)), but it increases the time to reach it (because of (18b) that shows that  $i_C$  is smaller in the non-ideal case). The proof is elementary and involves some standard inequality arguments. See Appendix B-D for the details.

#### D. Transient length

The criterion for choosing  $\bar{t}_{max}$  is that a large fraction of the instances is very close to the equilibrium value at  $\bar{t}_{max}$ . More precisely, denote with  $t_{\varepsilon,\bar{t}_0}$  the time required for a circuit to reach the equilibrium value within  $\varepsilon$ , that is

$$\overline{v}_{\mathcal{C}}(t_{\varepsilon,\overline{I}_0}) = (1 - \varepsilon)\overline{V}_{eq}(\overline{I}_0)$$

(19)

Fix  $\varepsilon, \eta \in (0, 1)$  and search for  $\overline{t}_{max}$  such that

$$\mathbf{P}[t_{\varepsilon,|\bar{I}_0|} > \bar{t}_{\max}] \le \eta \tag{20}$$

It can be easily shown (see details in Appendix B-E) that

$$\bar{t}_{\max} \ge t_{\varepsilon} \left( \overline{\sigma}_{I} \Phi^{-1} \left( \frac{1+\eta}{2} \right) \right) \approx t_{\varepsilon} \left( \sqrt{\frac{\pi}{2}} \, \overline{\sigma}_{I} \, \eta \right) \tag{21}$$

where

$$t_{\varepsilon}(\bar{I}_{0}) = \begin{cases} -\frac{\ln\varepsilon}{\theta} & \text{if } |\bar{I}_{0}| < \theta\\ \frac{\tanh^{-1}\left(-\varepsilon + \frac{1-\varepsilon}{\overline{V}_{\Delta}\sqrt{I_{0}}}\right)}{\sqrt{I_{0}}} + \frac{1}{\bar{I}_{0}} & \text{if } |\bar{I}_{0}| \ge \theta \end{cases}$$

(22)

It turns out that typically  $\bar{t}_{max}$  is approximately few hundreds (see also Fig. 4) that with the values in Table I corresponds to  $t_{max} \approx 10 \ \mu$ s.

#### E. Energy consumption

The proposed circuit at steady state consumes a current approximately equal to  $I_s$ . In order to minimize power consumption, the cell is powered only for  $t_{max}$  seconds, successively the outcome is copied to an SRAM cell<sup>2</sup> (for example) and the cell turned off. The energy required is

$$E = t_{\max} V_{DD} I_s = \overline{t}_{\max} \tau V_{DD} I_s = \overline{t}_{\max} C V_T V_{DD}$$

(23)

Since  $I_s$  is of the order of  $\mu A$  and  $t_{max}$  is of the order of tens of  $\mu s$ , E is a fraction of nJ/bit.

$^2$  Of course, it is advisable that the SRAM cell is on the same chip of the PUC, in order to avoid the obvious security issues related to the transfer of the outcome to an external SRAM.

#### VI. NOISE ANALYSIS

So far we supposed the system noiseless. In practice, however, the currents of the two MOSFETs will be affected by noise that will be integrated by the capacitance C and this will affect the value of  $V_{\text{raw}}$  acquired at  $t_{\text{max}}$ . Note that any noise of temporary nature (such as a turn-on noise at t = 0) has no effect on the outcome, due to the fact that the circuit evolves toward the unique equilibrium point. Therefore, the only noise that is necessary to consider is the combination of pink and white noise affecting the MOSFET currents.

At room temperature the Power Spectrum Density (PSD) of the noise of Qi can be modeled as [38]

$$R_i(f) = K_1 \frac{I_i}{C_{\text{ox}} L_i^2} \frac{1}{f} + K_0 g_m (1 + g_{mbs}/g_m) = \frac{a_{i,1}^2}{f} + a_{i,0} \quad (24)$$

where  $K_0 = 0.0094$  eV,  $K_1 = 10^{-28}$  F·A. Since the noises of Q1 and Q2 are independent, the PSD of the noise on  $i_C$  is

$$R_C(f) = \frac{a_{1,1}^2 + a_{2,1}^2}{f} + (a_{1,0} + a_{2,0}) = \frac{a_1^2}{f} + a_0$$

(25)

A useful parameter is the frequency  $f_K = a_1^2/a_0$  where the two components of (25) (pink and white) are equal. With the values in Table I,  $a_0 \approx 4.6 \cdot 10^{-25} \text{ A}^2/\text{Hz}$ ,  $a_1^2 \approx 1.7 \cdot 10^{-17} \text{ A}^2$  and  $f_K \approx 36.5$  MHz.

Since the analysis is complicated by the fact that the differential equation (8) is non linear, we consider the approximate problem of determining the variance  $\sigma_{\xi}^2$  of the voltage  $\xi$  across a capacitor with capacity *C* charged, during a time  $t_{\text{max}}$ , by a current with PSD (24). In Appendix C-A it is shown by elementary means (taking into account the peculiarities of pink noise) that

$$\sigma_{\xi}^2 \approx 0.045 \cdot a_1^2 \, \frac{t_{\text{max}}^2}{C^2} + a_0 \frac{t_{\text{max}}}{C^2} \approx 0.045 \cdot a_1^2 \, \frac{t_{\text{max}}^2}{C^2} \tag{26}$$

where the last approximation is valid when  $t_{\text{max}} \gg 1/f_K = a_0/a_1^2$ , that is, as soon as  $t_{\text{max}}$  is more than few microseconds. From  $t_{\text{max}} = \tau \bar{t}_{\text{max}}$  one deduces

$$\overline{\sigma}_{\xi} = 0.212 \cdot \overline{t}_{\max} \overline{a}_1 \tag{27}$$

where  $\overline{a}_1 = a_1/I_s$ . Note that  $\overline{\sigma}_{\xi}$  does not depend on *C*.

# VII. QUALITY FIGURES

The objective of this section is to predict the quality indexes of the proposed cell, namely, its *unbiasedness*, its *stability* and its *independence* and derive from them a prediction for  $\mu_{intra}$  and  $\mu_{inter}$ . We will achieve this by first determining the statistical distributions of  $\overline{I}_0$  and  $\overline{V}_{eq}$ . Symmetry properties of the distribution of  $\overline{I}_0$  will allow us to show unbiasedness, while stability will be obtained by using the distribution of  $\overline{V}_{eq}$  together with result (27) of Section VI. Finally, at the end of this section we will discuss briefly the *local biasing* effect that can be induced by process gradients.

We will write  $X \sim \mathcal{N}(m, \sigma^2)$  when X is normally distributed with mean *m* and variance  $\sigma^2$  and  $\phi_{m,\sigma}$  will denote the corresponding density. For notational convenience we will write  $\phi(x)$  in place of  $\phi_{0,1}(x)$ .

#### A. Statistical model

The parameters that can be modeled as r.v. are  $V_{Ti}$ ,  $\beta_i$  and  $V_{RR}$ . According to the literature [41]

$$V_{\mathrm{T}i} \sim \mathcal{N}(V_{\mathrm{T}}, \sigma_{V}^{2})$$

;  $\beta_{i} \sim \mathcal{N}(\beta, \sigma_{\beta}^{2})$  (28)

where  $\sigma_V^2 = A_V^2/(L_iW_i)$  and  $\sigma_\beta^2 = \beta^2 A_\beta^2/(L_iW_i)$ . Although  $V_{\text{T}i}$  and  $\beta_i$  depend on the same physical parameters, it has been seen in practice that they can be considered independent [41]. We will need the zero-mean versions of  $\beta_i$ ,  $V_{\text{T}i}$  and  $V_{RR}$  as

$$\delta_{\beta,i} \stackrel{\text{def}}{=} \beta_i - \beta \; ; \; \delta_{V,i} \stackrel{\text{def}}{=} V_{\text{T}i} - V_{\text{T}} \; ; \; \delta_R \stackrel{\text{def}}{=} V_{RR} - V_{DD}/2 \tag{29}$$

the adimensional values

$$S_{\beta}^{2} = \frac{\sigma_{\beta,p}^{2} + \sigma_{\beta,n}^{2}}{\beta^{2}} = A_{\beta}^{2} \left(\frac{1}{L_{1}W_{1}} + \frac{1}{L_{2}W_{2}}\right)$$

$$S_{V}^{2} = \frac{\sigma_{V,p}^{2} + \sigma_{V,n}^{2}}{V_{\Delta}^{2}} = \frac{A_{V}^{2}}{V_{\Delta}^{2}} \left(\frac{1}{L_{1}W_{1}} + \frac{1}{L_{2}W_{2}}\right)$$

(30)

and their combination  $S_X^2 = S_\beta^2 + 4S_V^2$ . With the values given in Table I,  $S_\beta$ ,  $S_V$  and  $S_X$  are approximately 6%, 3% and 10%. Finally, it is reasonable to assume  $V_{RR}$  independent from both  $V_{Ti}$  and  $\beta_i$  and  $V_{RR} \sim \mathcal{N}(V_{DD}/2, \sigma_R^2)$ , for some  $\sigma_R$ .

# B. Probability density of $\overline{I}_0$ and $\overline{V}_{eq}$

The key result is the following property.

**Property 4.** Let  $f_{\delta_R}$  and  $f_{I_0}$  be the probability density functions of, respectively,  $\delta_R$  and  $I_0$ . The following claims hold (1) If  $f_{\delta_R}$  is even, then  $f_{I_0}$  is even as well and (2) if  $\delta_R \sim \mathcal{N}(0, \sigma_R^2)$ , then

$$\overline{I}_0 \sim \mathcal{N}\left(0, \, S_X^2 + 16(\overline{\sigma}_R/\overline{V}_\Delta)^2\right) \tag{31}$$

with  $\sigma_I^2 = I_s^2 S_X^2 + 4\beta^2 V_\Delta^2 \sigma_R^2 = I_s^2 (S_X^2 + 16\sigma_R^2/V_\Delta^2).$

The proof involve some standard approximation and conditioning. The details can be found in Apendix D, Proof D.1.

From the pdf (31) of  $I_0$  one obtains the pdf of  $\overline{V}_{eq}$  as

$$f_{eq}(v) = h'(v) \ \phi_{0,\overline{\sigma}_I^2}(h(v)) = \frac{1}{\overline{\sigma}_I} h'(v) \ \phi(h(v/\overline{\sigma}_I))$$

(32)

where h is the inverse of (9) and h' its derivative, namely

$$h(\overline{V}_{eq}) = \begin{cases} \theta \overline{V}_{eq} & |\overline{V}_{eq}| < 1\\ \operatorname{sgn} \overline{V}_{eq} \frac{(|\overline{V}_{eq}| - R - 1)^2 - R^2 + 4R}{\overline{V}_{\Delta}^2} & |\overline{V}_{eq}| \ge 1 \end{cases}$$

(33a)

$$h'(\overline{V}_{eq}) = \begin{cases} \theta & |\overline{V}_{eq}| < 1\\ 2\frac{|\overline{V}_{eq}| - 1 - R}{\overline{V}_{\Delta}^2} & |\overline{V}_{eq}| \ge 1 \end{cases}$$

(33b)

Note that if  $\lambda = 0$ , h'(v) = 0 if |v| < 1 and this implies, via (32),  $f_{eq}(v) = 0$  for |v| < 1, coherently with the fact that if  $\lambda = 0$ map  $\overline{I}_0 \mapsto \overline{V}_{eq}$  is discontinuous and the anti-image of (-1, 1)is empty. Fig. 5 shows some examples of  $f_{eq}$ , for different values of  $\lambda$  and  $\sigma_R$ . The following result is obvious

**Property 5.** The probability of having an almost balanced instance (see Definition 1) is equal to  $\operatorname{erf}(\theta/(\sqrt{2}\overline{\sigma}_I))$ ).

Figure 5. Some examples of probability density  $f_{eq}$  of  $\overline{V}_{eq}$  and RDF. (a)  $\sigma_R = 0$  and different values of  $\lambda$ . (b)  $\lambda = 0.010$  and different values of  $\sigma_R$  (c) Comparison of the RDF for several values of  $\theta$  and the RDF of the SRAM

#### C. Performance measures

From the knowledge of  $f_{eq}$  is possible to predict the stability of the proposed scheme. Let  $\overline{\xi}$  be the noise affecting the output  $\overline{V}_{raw} \approx \overline{V}_{eq}$  of the cell at  $t = t_{max}$ , let  $F_{\xi}$  be the distribution of  $\overline{\xi}$  and suppose that the density of  $\overline{\xi}$  is even. (From Section VI we know that  $\overline{\xi} \sim \mathcal{N}(0, \sigma_{\xi}^2)$ , so that  $F_{\xi}(x) = \Phi(x/\sigma_{\xi})$ , but we will not need this). Since the PUC outcome is "1" when  $\overline{V}_{eq} + \overline{\xi} > 0$  one can write

$$p_1 = F_{\xi}(\overline{V}_{eq}) = F_{\xi}(\overline{V}_{eq}(\overline{I}_0))$$

(34)

By using (34) we can derive the quality measures for our cell. 1) SDF and  $\mu_{intra}$ : In order to derive the SDF, observe that

$$R(\overline{V}_{eq}) = 2F_{\xi}(|\overline{V}_{eq}|) - 1 \tag{35}$$

Define, for notational convenience,  $W_x = R^{-1}(x) = F_{\xi}^{-1}((1 + x)/2)$ . By using (32) and the fact that *h* is odd it is easy to show that the SDF is (see Appendix D-A for details)

$$F_r(x) = 2F_I\left(\frac{h(W_x)}{\overline{\sigma}_I}\right) - 1 = 2\Phi\left(\frac{h\left(F_{\xi}^{-1}\left(\frac{1+x}{2}\right)\right)}{\overline{\sigma}_I}\right) - 1 \quad (36)$$

where  $F_I$  is the distribution of  $\overline{I}_0$  and where we used the fact that  $\overline{I}_0 \sim \mathcal{N}(0, \overline{\sigma}_I^2)$ .

# Example VII.1

Fig. 5c shows few examples of SDF (36) for several values of  $\theta$ , together with the SDF of the SRAM, according to [6]. Note that the SDFs for the proposed scheme are always below the SDF of the SRAM and this means that unreliable cells are less probable and that reliability improves as  $\theta$  decreases.

By using (35) in (3a) one can obtain  $\mu_{intra}$  of the proposed PUC. An observation that helps in estimating  $\mu_{intra}$  is that in Fig. 5c the SDF curves for the proposed PUC can be obtained by lowering the SRAM curve. Since Fig. 5c is in logarithmic scale, this implies that the SDF for our solution can be approximately<sup>3</sup> obtained by multiplying the SDF of the SRAM by a constant  $\alpha < 1$ . This, together with (3a), implies  $\mu_{intra}^{ours} = \alpha \mu_{intra}^{SRAM}$ . According to Fig. 5c, our solution is 10 to 100 times better than the SRAM (result confirmed by simulations in Section IX).

2) Inter distance  $\mu_{inter}$ : The following property (proved in Appendix D, Proof D.2) is instrumental to determine  $\mu_{inter}$ .

**Property 6.** If the pdfs of noise  $\overline{\xi}$  and  $\overline{I}_0$  are even, then the pdf  $f_p$  of  $p_1$  is symmetric around 1/2.

From the symmetry of  $f_p$  one predicts  $P[O_{\text{pref}} = 1] = 1/2$ ,  $m_p = 1/2$  and (via (3b))  $\mu_{\text{inter}} = 1/2$ . Therefore, our PUC is predicted to be perfectly unbiased in both senses of Remark II.1.

### D. Independence

Remember that a scheme is independent if the POs of different instances are independent. In the proposed scheme, the PO is a function of  $I_0$  which depends on  $V_{\text{T}i}$  and  $\beta_i$ , i = 1, 2, that in turn depend on  $N_{d,i}$  and  $t_{\text{ox}}$ . It is commonly accepted that variations in  $N_{d,i}$  can be modeled as a consequence of the 2D Poisson process associated with doping [41]. Since there is no overlap between the areas of different transistors, the r.v.  $N_{d,i}$  are independent. About oxide thickness  $t_{\text{ox}}$ , according to [42], it can be considered uncorrelated after few nanometers of distance. Therefore we can predict that the PO associated with different cells will be independent.

# E. Process Gradients and Local Biasing

The results above show that the proposed scheme is unbiased in the sense that if one selects at random a cell from a pool of cells, the probability of selecting a cell with PO "1" is 1/2. However, some mechanisms (e.g., gradients in dopant density) together with the intrinsic asymmetry of the cell could induce some local biasing, i.e., it may happen that the PO of the cells implemented in a specific area are biased toward "1" or "0" [30].<sup>4</sup> Local biasing is quite a general issue and every PUC scheme can be expected to be subject to it. Its impact can be studied in a general setting [30]. In the specific case of our scheme, a local biasing will cause  $\overline{I}_0$  to have a nonnull average  $\overline{m}_I \stackrel{\text{def}}{=} \mathbb{E} \left[ \overline{I}_0 \right] \neq 0$ . It is trivial to show that the corresponding bias is  $p_1 - 1/2 = \Phi(\overline{m}_I/\overline{\sigma}_I) - 1/2$ . It follows that a large  $\overline{\sigma}_{I}$  counteracts the impact of local bias. The actual impact of local biasing is very dependent on process details and it can be measured only by experimental means.

<sup>&</sup>lt;sup>3</sup>It cannot be exact since any SDF is equal to 1 in R = 1.

<sup>&</sup>lt;sup>4</sup>Local biasing should not be confused with statistical dependence.

# VIII. OTHER CONSIDERATIONS

# A. Temperature Dependence: Crossover Temperature

A key characteristic that a PUC must have is the stability of its behavior with respect to changes in the temperature. On a qualitative level, since both MOSFETs are affected in the same way by changes in the temperature, we expect that if, say,  $I_0 > 0$  at room temperature  $T_0$ , then  $I_0$  will maintain the same sign also at other temperatures. Against this qualitative reasoning one could object that even if the effect of temperature change on both MOSFETs is *qualitatively* the same (e.g., both  $I_s$  increase), it could be that one transistor changes more and it "catches up" with the other. A more quantitative reasoning is, therefore, required.

Observe that in our case we are not interested in the actual value of  $I_0$ , but only in its sign. Therefore, the "critical" case that we would like to avoid is that  $I_0$  at some temperature T has a sign different from the sign that it has at  $T_0$ . If this happens, we know that there will be a *crossover temperature*  $T_X$  between  $T_0$  and T where  $I_0(T_X) = 0$ . Note that in the neighborhood of  $T_X$ ,  $I_0$  will be close to zero, so that the cell becomes unstable when the temperature is near  $T_X$ .

It turns out that the validity range of analytic results obtained by using simple temperature dependency models [37] is not sufficient to cover a wide range of temperatures. Therefore, we decided to study the behavior of  $T_X$  by means of simulations. Results and details are given in Section IX-A with other simulation results. Here we can anticipate that it turns out that  $T_X$  is a function almost deterministic of  $\overline{I}_0$  and that most temperature-sensitive cells are those that are *almost balanced* (Definition 1). This allows us to recognize and disable the temperature-sensitive instances. See Section VIII-C3 for a detailed discussion about this.

# B. Power supply variations

An advantage of our scheme is that non-*almost balanced* cells are insensitive to power supply variations. Indeed, if a cell is not almost balanced, its equilibrium value  $V_{eq}$  is larger in absolute value than  $V_T$  and  $V_T$  is a characteristic of the MOSFET, independent on the power supply. This reasoning is confirmed by the simulations described in Section IX-B.

#### C. Design Guidelines

1) Transistor size: A key requirement in the design is keeping  $\lambda$  small, in order to have a small probability of almost balanced instances (Property 5). In order to have  $\lambda$  small one must use large values of *L*. This not only increases the size of the cell, but also reduces the variability of  $V_{\rm T}$  and  $\beta$ .

In order to reduce the area one can reduce W. This reduces  $I_0$ , making the charging of C slower. This can be compensated with a smaller C and/or a larger  $t_{max}$ . Reducing  $I_0$  also increases the noise, according to (27), since  $\overline{a}_1 = a_1/I_s$ , but the impact of the increased noise turns out to be negligible. Simulations show that one can reduce the area of the cell down to<sup>5</sup> 1  $\mu m^2$  by using a "long and thin" transistor without reducing the performance, taking into account the noise too.

Table II DIMENSIONS (IN  $\mu m$ ) OF THE MOSFET USED IN THE SIMULATIONS.

| Label   | L    | $W_p$ | $W_n$ | Label                          | L    | $W_p$ | $W_n$ |

|---------|------|-------|-------|--------------------------------|------|-------|-------|

| 0.5/0.5 | 0.5  | 0.3   | 0.1   | 0.5/20                         | 20.0 | 1.1   | 0.5   |

| 0.5/1   | 1.0  | 0.7   | 0.3   | 1/20                           | 20.0 | 2.2   | 1.0   |

| 1.5/5   | 5.0  | 3.3   | 1.5   | 3/20                           | 20.0 | 6.2   | 2.8   |

| 1.5/10  | 10.0 | 3.3   | 1.5   | 0.5/20<br>1/20<br>3/20<br>7/50 | 50.0 | 16.5  | 6.9   |

Table III PREDICTED  $\mu_{\text{INTRA}}$  AND  $\sigma_{\text{INTRA}}$  FOR THE PROPOSED PUC (128-BIT PUCS).  $\mu_{\text{INTER}} \approx 50\%$  FOR ALL THE SCHEMES.

| PUC      | $\mu_{ m intra}$ | PUC            | $\mu_{ m intra}$ | PUC        | $\mu_{ m intra}$ |

|----------|------------------|----------------|------------------|------------|------------------|

| SRAM [6] | 12%              | Butterfly [19] | 6%               | Latch [20] | 3%               |

| 0.5/0.5  | 1.2%             | 0.5/1          | 0.4%             | 1.5/5      | 0.05%            |

Note that although the proposed cell could be larger than other PUC cells, the stability of our proposal is such that one does not need costly (in terms of area) error-correction circuits.

2) Load effect and the choice of C: According to the analysis above and the results of Section VI, the value of C impacts only  $\tau$  and the energy consumption. This suggests to choose C as small as possible, but large enough to make the effect of any load negligible.

3) Handling almost balanced cells: It turns out that  $\bar{I}_0$  can be consider a "quality measure" of a specific instance. Almost balanced cells (that is, with  $\bar{I}_0$  smaller than a threshold) are "bad" in many senses: their smaller  $\bar{V}_{eq}$  (see (9)) makes them more sensitive to noise, they are more sensitive to temperature (Section IX-A) and more sensitive to aging (Section IX-C). This suggests to measure  $|\bar{I}_0|$  (or, equivalently,  $\bar{V}_{eq}$ ) at enrollment phase and "disable" those cells with small  $|\bar{I}_0|$ . This procedure requires, of course, a surplus of cells that grows when the probability of having an almost balanced cell grows.

#### IX. SIMULATION RESULTS

We run several simulations in order to verify that the results predicted by the analysis above – done using simple models suitable for theoretical analysis – still hold when the circuit is simulated using more complex and realistic models. More precisely, we verified the results about stability (SDF and  $\mu_{intra}$ ) and unbiasedness ( $\mu_{inter}$ ), and what happens when temperature and power supply change. We also take into account the effects of aging.

#### A. Temperature Dependence

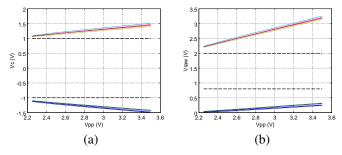

We simulated the proposed circuit by using transistors of different sizes varying, for every size, doping  $\tilde{N}_d$  and  $\tilde{t}_{ox}$  around their nominal values. More precisely, for  $t_{ox}$  we scanned the interval  $\pm \sigma_{ox} = \pm 2$ Å, while for  $\tilde{N}_d$  we scanned the interval  $\pm 3\sigma_N$ , where  $\sigma_N = \sqrt{N_d/(WLd)}$  where *d* is the doping depth and  $N_d$  is the nominal doping (see Remark IX.1 in Section IX-D for an explanation of  $\sigma_{ox}$  and  $\sigma_N$ ). For every choice of  $t_{ox}$  and  $N_d$ , the circuit was simulated at temperatures ranging from -150 °C to 100 °C in order to find  $T_X$ . We repeated the simulations with supply voltages 3.5 V and 5 V in order to increase  $\overline{V}_{\Delta}$  without changing the transistors.

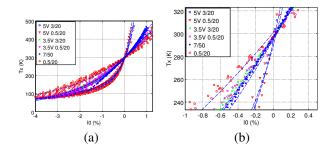

The results can be seen in Fig. 7 that shows the scatter plot of  $T_X$  vs  $\overline{I}_0$  (shown as percentage of  $I_s$ ) at  $T_0 = 300$  K.

<sup>&</sup>lt;sup>5</sup>Maybe the area can be further reduced, but with smaller transistor the BSIM3 model used in the simulations becomes unreliable.

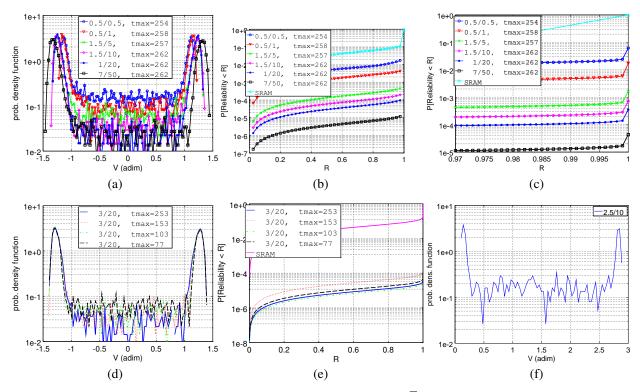

Figure 6. Results for different cell sizes and  $\bar{t}_{max} \approx 260$ . (a) Density probability function of  $\bar{V}_{eq}$  (b) RDFs compared with the RDF of the SRAM, (c) is (b) with the x-axis expanded. (d) and (e) are like (a) and (b), but for different  $\bar{t}_{max}$  and fixed cell size. (f) Example of behavior of a cell scaled down at  $V_{DD} = 1.5V$ .

$\label{eq:table_to_table_to_table_to_table} Table \ IV \\ Total number of bit required and relative complexity of FEC implementation for an N-bit PUC and error probability <math display="inline">\leq \eta$ . The area required for power control is  $\approx 10\%$  the area required by the PUC.

|           |     | SRAM    | Butt   | erfly | Lat  | ch   | 0.5/ | 0.5  | 0.5  | /1   | 1.5  | 5/5  | 1.5/ | /10  | 1.5/ | 20   | 7/5  | 50   |

|-----------|-----|---------|--------|-------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| η         | Ν   | Bits Co | t Bits | Cost  | Bits | Cost | Bits | Cost | Bits | Cost | Bits | Cost | Bits | Cost | Bits | Cost | Bits | Cost |

|           | 64  | 184 30  | 0 116  | 13.0  | 92   | 7.0  | 80   | 4.0  | 72   | 2.0  | 68   | 1.0  | 64   | 0    | 64   | 0    | 64   | 0    |

| $10^{-2}$ | 128 | 324 49  | 0 208  | 20.0  | 172  | 11.0 | 148  | 5.0  | 140  | 3.0  | 132  | 1.0  | 132  | 1.0  | 128  | 0    | 128  | 0    |

|           | 256 | 588 83  | 0 388  | 33.0  | 324  | 17.0 | 288  | 8.0  | 276  | 5.0  | 260  | 1.0  | 260  | 1.0  | 260  | 1.0  | 256  | 0    |

|           | 64  | 216 38  | 0 128  | 16.0  | 100  | 9.0  | 84   | 5.0  | 76   | 3.0  | 68   | 1.0  | 68   | 1.0  | 68   | 1.0  | 64   | 0    |

| $10^{-4}$ | 128 | 364 29  | 5 224  | 12.0  | 180  | 6.5  | 156  | 3.5  | 144  | 2.0  | 136  | 1.0  | 132  | 0.5  | 132  | 0.5  | 128  | 0    |

|           | 256 | 636 95  | 0 412  | 39.0  | 336  | 20.0 | 296  | 10.0 | 280  | 6.0  | 264  | 2.0  | 260  | 1.0  | 260  | 1.0  | 260  | 1.0  |

|           | 64  | 304 60  | 0 168  | 26.0  | 124  | 15.0 | 100  | 9.0  | 88   | 6.0  | 76   | 3.0  | 72   | 2.0  | 72   | 2.0  | 68   | 1.0  |

| $10^{-6}$ | 128 | 464 84  | 0 272  | 36.0  | 208  | 20.0 | 176  | 12.0 | 156  | 7.0  | 140  | 3.0  | 136  | 2.0  | 136  | 2.0  | 132  | 1.0  |

|           | 256 | 760 126 | 0 468  | 53.0  | 372  | 29.0 | 320  | 16.0 | 296  | 10.0 | 272  | 4.0  | 268  | 3.0  | 264  | 2.0  | 260  | 1.0  |

Table V Number of iterations required for a PUC  $(\eta, \delta)$ -stable [9]

| $1 - \eta$ | δ                 | SRAM      | Butterfly | Latch | 0.5/0.5 | 0.5/1 | 1.5/5 | 1.5/10 | 1.5/20 | 7/50 |

|------------|-------------------|-----------|-----------|-------|---------|-------|-------|--------|--------|------|

| $10^{-2}$  | $5 \cdot 10^{-3}$ | 536       | 130       | 29    | 1       | 1     | 1     | 1      | 1      | 1    |

|            |                   | 138 298   |           |       |         |       |       |        |        |      |

|            |                   | 3 457 758 |           |       |         |       |       |        |        |      |

Figure 7. (a) Scatter plots of  $T_X$  vs  $\overline{I}_0$ . (b) Zoom of (a).

Figure 8. (a)  $V_{eq}$  vs. supply voltage for differently unbalanced PUCs. (b)  $V_{raw}$  vs. supply voltage.

The curves are labeled with the *plot labels* in Table II. It is interesting to observe that  $T_X$  is almost a function of  $\overline{I}_0$  in the sense that for every  $\overline{I}_0$  there is a limited range of possible  $T_X$ , especially for small  $\overline{I}_0$ . Observe that  $|\overline{I}_0|$  can be used as a measure of quality of the cell also from the viewpoint of insensitivity to temperature variations (see Section VIII-C3).

Of special interest is the slope of the curves in Fig. 7 at  $\overline{I}_0 = 0$ , since a large slope implies that  $T_X$  is far from  $T_0$  even for small  $|\overline{I}_0|$ . It is clear that the slope increases with  $\overline{V}_{\Delta}$ .

## B. Power supply variations

In order to verify the analysis of Section VIII-B, we simulated the circuit behavior for several values of  $V_{DD}$  and measured  $V_{eq}$  after 1 ms of simulated evolution. The results are shown in Fig. 8a. The different slanted lines correspond to differently unbalanced instances of the circuit, while the two dashed horizontal lines show the values  $\pm V_T$  (in this case  $V_T \approx 1$ V). It is clear that  $|V_{eq}| \ge V_T$  for every supply voltage, as predicted. Therefore, our scheme preserves its reliability also for different supply voltages.

It is also of interest to check that  $V_{raw}$  remains outside the transition region of a possible logic gate fed by the PUC. This can be seen in Fig. 8b that shows the behavior of  $V_{raw}$  when the supply voltage is changed. The horizontal dashed lines show the typical guaranteed values of  $V_{IL} = 0.8$  V and  $V_{IH} = 2$  V for a 3V-CMOS inverter. It is clear that  $V_{raw}$  never enters the transition region.

# C. Aging

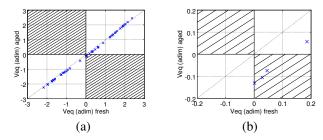

Aging is another important issue since it could happen that with time the cell will change its PO [27], [28]. We carried out some aging simulations with Relxpert. We generated several cells of different unbalance and determined  $\overline{V}_{eq}$  at the first turn-on and after 10 years of usage (with 50 turn-on/day). Fig. 9 shows  $\overline{V}_{eq}$  of the "fresh" device vs the  $\overline{V}_{eq}$  after aging. Note that the PO of a cell changes when the corresponding point in Fig. 9 is in the second or in the fourth quadrant (hatched). It is clear the PO changes only if the cell is very balanced, that is, its  $|\overline{I}_0|$  is small. See Section VIII-C3 for a discussion about handling almost balanced cells.

# D. Stability, Unbiasedness, Consumption

We simulated the scheme of Fig. 1b with the voltage divider of Fig. 2d. Both NMOS have size  $W_n \times L$  and both PMOS have size  $W_p \times L$ .  $W_n$ ,  $W_p$  and L can be found in Table II together with the labels used in the plots. We used ngspice-26 (based on spice3f5) with model BSIM3 nominal values  $t_{ox} = 9.3$  nm and  $N_d = 1.7 \cdot 10^{17}$  cm<sup>-3</sup>.

For every MOSFET in the scheme, we randomly changed the  $N_{d,i}$  and  $t_{\text{ox}}$  according to  $\tilde{N}_{d,i} \sim \mathcal{N}(N_{d,i}, N_{d,i}/(d_i W_i L_i))$ , and  $\tilde{t}_{\text{ox}} \sim \mathcal{N}(t_{\text{ox}}, 0.04 \text{ nm}^2)$ . In this way we account also for the variations of VD.

# Remark IX.1

Doping pdf  $\mathcal{N}(N_{d,i}, N_{d,i}/(d_i W_i L_i))$  has been chosen by observing that the number *M* of doping atoms in a  $d_i \times W_i \times L_i$  cube is a Poisson r.v. with parameter  $\Lambda = N_{d,i} d_i W_i L_i$ . By approximating the distribution of *M* with  $\mathcal{N}(\Lambda, \Lambda)$  one deduces that the dopant concentration is a r.v.  $\mathcal{N}(N_{d,i}, N_{d,i}/(d_i W_i L_i))$ . About the the oxide thickness, we did the pessimistic<sup>6</sup> choice  $\sigma_{\text{ox}} = 0.2 \text{ nm} = 2 \text{ Å}$  ( $\approx$  the diameter of a silicon atom).

Fig. 6 shows the results of some simulations done with different cells and<sup>7</sup>  $\bar{t}_{max} \approx 260$ . Fig. 6a shows in logarithmic scale the pdf of  $\bar{V}_{eq}$ , while Fig. 6b and Fig. 6c show the corresponding SDFs and compares them with the SDF of the SRAM PUC. Fig. 6d and e are similar to Fig. 6a and b, but with fixed size and variable  $\bar{t}_{max}$ . The energy required ranges from 1 to 2 nJ/cell (for  $\bar{t}_{max} = 100$ ).

1) Discussion: It is clear from the plots that the pdf of the adimensional voltage  $\overline{V}_{eq}$  is almost zero in [-1,1] (i.e.,  $[-V_T, V_T]$  in dimensional units), confirming the prediction that  $|V_{eq}| > V_T$ , even for small unbalances. Note also that the density relative to smaller transistors assumes larger values in [-1,1], probably because to a larger  $\lambda$  makes more probable to have almost balanced cells (Section V-B). Moreover, Fig. 6c and 6d show that increasing  $\bar{t}_{max}$  lowers the pdf around  $\overline{V}_{eq} = 0$ , as expected, since when  $\bar{t}_{max}$  is larger more cells reach the equilibrium.

From Fig. 6 it is clear that stability improves with the cell size. However, even the smallest cell is still an order of magnitude more stable than the SRAM (see Table III and Section IX-D2). Fig. 6f shows an example of the behavior of a cell scaled for  $V_{DD} = 1.5$  V. Note that the adimensional plot is almost invariant. This suggests a nice scalability of the solution.

<sup>&</sup>lt;sup>6</sup>It is unlikely that the actual standard deviation will be smaller and a larger value would improve the dispersion of  $\overline{I}_0$  and the SDF of our solution.

<sup>&</sup>lt;sup>7</sup>The  $\bar{t}_{max}$  of the different cells are not exactly equal since  $\bar{t}_{max}$  depends on  $\tau$  which in turn depends on  $I_s$  and  $V_{\rm T}$ .

Figure 9. (a) Variation of  $\overline{V}_{eq}$  after 10 years. (b) Zoom of (a).

Figure 10. A possible power control solution

2) Comparison with other proposals: Table III compares the predicted performance of the proposed scheme with other schemes in the literature. The value of  $\mu_{intra}$  for our solution has been computed using (3a) and the results in Fig. 6, while  $\mu_{inter} = 50\%$  has been obtained from Property 6 and the fact that the pdf of  $V_{eq}$  is even (Fig. 6).

Table IV shows the number of bits (information + redundancy) used by the optimal<sup>8</sup> Reed-Solomon code necessary to stabilize an *N*-bit PUC with a failure probability smaller than  $\eta$ , together with the estimated *relative*<sup>9</sup> cost (in terms of silicon area) of the decoder. The area required by the decoder has been obtained by [43, Table III], see Appendix E-A2 for details. The cases where no correction code is necessary are marked in bold. These cases are interesting because, beyond not requiring any redundancy cell, they do not require error-correction circuits, nor a Non Volatile Memory (NVM). The predicted advantage of the proposed solution is clear. The details of the procedure used to compute Table IV are described in Appendix E-A.

### Remark IX.2 (Gating cost)

As suggested in Section V-E, power consumption can be reduced by powering the cell only for the time required to reach the equilibrium, then turning them off. In order to make a farier comparison, it is necessary to take into account also the area required by the circuit required to power the cells. A possible solution for a group of *N* cells is shown in Fig. 10. Since the cells are powered through Q1, the size of Q1 must be proportional to *N*. In order to estimate the required area, we determined, by means of simulations and for several different cell sizes, the minimum size of Q1. It turned out that an indicative planning figure for the area of the best Q1 is approximately 10% of the area used by the cells. For example, in the case of N = 64, the area required for power control is equivalent to 6–7 additional cells. 13

required to implement an  $(\eta, \delta)$ -stable helper-less stabilizer using the approach of [9]. The entries in bold are relative to the case when no iteration is required. Also in this case the advantage is clear.

Although these results need to be verified experimentally, the margin over other solutions is high enough that we expect that the proposed PUC will maintain its competitiveness.

*a) Environmental Variations:* The results in Table III are relative to fixed environmental conditions. Because of the results of Section IX-B, we predict that the same figures will hold even in the presence of power supply variations.

Because of the lack of suitable models, it is more difficult to predict the actual impact of temperature. If the selection procedure in Section VIII-C3 is *not* employed, we expect, from the results of Section IX-A, that over an extended range of temperatures  $\mu_{intra}$  could increase by approximately 1%. The precise impact of the temperature needs to be verified in an actual circuit implementation.

# X. CONCLUSIONS AND FUTURE DIRECTIONS

We proposed a 1-bit PUC with a single equilibrium point that depends discontinuously on cell asymmetry. The behavior of the cell has been analyzed both analytically and by simulations. From the theoretical analysis some design guidelines were derived. We predict that  $\mu_{inter} = 50\%$ ,  $\mu_{intra}$  can be as small as  $10^{-3}$  or  $10^{-4}$ , and that the cell is insensitive to power supply variations. Preliminary analysis show a limited sensitivity to temperature variations, but the lack of suitable models requires that a definitive answer is obtained experimentally. Although the predicted performance need to be confirmed experimentally, the margin over other solutions is such that the we expect that the proposed PUC will maintain its advantage.

Further research will aim to verify the predictions and to investigate in more detail the effect of temperature and aging.

#### REFERENCES

- B. Gassend, D. Clarke, M. van Dijk, and S. Devadas, "Silicon physical random functions," in *Proceedings of the 9th ACM conference on Computer and communications security*, CCS '02, (New York, NY, USA), pp. 148–160, ACM, 2002.

- [2] D. Lim, J. Lee, B. Gassend, G. Suh, M. van Dijk, and S. Devadas, "Extracting secret keys from integrated circuits," *Very Large Scale Integration (VLSI) Systems, IEEE Transactions on*, vol. 13, no. 10, pp. 1200–1205, 2005.

- [3] D. Lim, "Extracting secret keys from integrated circuits," Master's thesis, MIT, May 2004.

- [4] G. Suh and S. Devadas, "Physical unclonable functions for device authentication and secret key generation," in *Design Automation Conference*, 2007. DAC '07. 44th ACM/IEEE, pp. 9–14, 2007.

- [5] D. E. Holcomb, W. P. Burleson, and K. Fu, "Initial SRAM state as a fingerprint and source of true random numbers for rfid tags," in *In Proceedings of the Conference on RFID Security*, 2007.

- [6] R. Maes, P. Tuyls, and I. Verbauwhede, "A soft decision helper data algorithm for SRAM PUFs," in *Information Theory*, 2009. ISIT 2009. IEEE International Symposium on, pp. 2101–2105, 2009.

- [7] Z. Paral and S. Devadas, "Reliable and efficient PUF-based key generation using pattern matching," in *Hardware-Oriented Security and Trust* (HOST), 2011 IEEE International Symposium on, pp. 128–133, 2011.

- [8] J. Delvaux and I. Verbauwhede, "Fault injection modeling attacks on 65nm arbiter and ro sum PUFs via environmental changes." Cryptology ePrint Archive, Report 2013/619, 2013. http://eprint.iacr.org/.

<sup>&</sup>lt;sup>8</sup>In the sense of minimum number of total bits employed

<sup>&</sup>lt;sup>9</sup>*Relative* means that all the costs have been normalized to the smallest one for a specific combination of *N* and  $\eta$ . For example, for *N* = 64 and  $\eta = 0.01$ , the decoder for an SRAM-based PUC will take approximately an area 30 times larger than the decoder for the 1.5/5 cell.

- [10] R. Bernardini and R. Rinaldo, "Physically unclonable random permutations," in *Recent Advances in Electrical and Electronic Engineering*, (Florence, Italy), pp. 148–154, Nov. 2014.

- [11] M. Bellare and P. Rogaway, "Random oracles are practical: A paradigm for designing efficient protocols," in *Proceedings of the 1st ACM Conference on Computer and Communications Security*, CCS '93, (New York, NY, USA), pp. 62–73, ACM, 1993.

- [12] O. Goldreich, S. Goldwasser, and S. Micali, "How to construct random functions," J. ACM, vol. 33, pp. 792–807, Aug. 1986.

- [13] Y. Dodis, L. Reyzin, and A. Smith, "Fuzzy extractors: How to generate strong keys from biometrics and other noisy data," in *Advances in Cryptology - EUROCRYPT 2004* (C. Cachin and J. Camenisch, eds.), vol. 3027 of *Lecture Notes in Computer Science*, pp. 523–540, Springer Berlin Heidelberg, 2004.

- [14] B. Skoric and N. de Vreede, "The spammed code offset method." Cryptology ePrint Archive, Report 2013/527, 2013. http://eprint.iacr.org/.

- [15] M.-D. M. Yu and S. Devadas, "Secure and robust error correction for physical unclonable functions.," *IEEE Design & Test of Computers*, vol. 27, no. 1, pp. 48–65, 2010.

- [16] E. Öztürk, G. Hammouri, and B. Sunar, "Towards robust low cost authentication for pervasive devices," in *Sixth Annual IEEE International Conference on Pervasive Computing and Communications (PerCom* 2008), 17-21 March 2008, Hong Kong, pp. 170–178, 2008.

- [17] D. E. Holcomb, W. P. Burleson, and K. Fu, "Power-up SRAM state as an identifying fingerprint and source of true random numbers," *IEEE Transactions on Computers*, 2009.

- [18] Y. Su, J. Holleman, and B. P. Otis, "A 1.6pj/bit 96% stable chip-id generating circuit using process variations," in 2007 IEEE International Solid-State Circuits Conference, ISSCC 2007, Digest of Technical Papers, San Francisco, CA, USA, February 11-15, 2007, pp. 406–611, 2007.

- [19] E. S. Kumar, J. Guajardo, R. Maesyz, G. jan Schrijen, and P. Tuyls, "Extended abstract: The butterfly puf protecting ip on every fpga," in *in Hardware-Oriented Security and Trust. HOST, 2008. IEEE International Workshop on*, pp. 67–70, 2008.

- [20] Y. Su, J. Holleman, and B. Otis, "A digital 1.6 pJ/bit chip identification circuit using process variations," *Solid-State Circuits, IEEE Journal of*, vol. 43, pp. 69–77, Jan 2008.

- [21] X. Xu, A. Rahmati, D. Holcomb, K. Fu, and W. Burleson, "Reliable physical unclonable functions using data retention voltage of SRAM cells," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, 2015. doi: 10.1109/TCAD.2015.2418288.

- [22] J. Lee, D. Lim, B. Gassend, G. Suh, M. van Dijk, and S. Devadas, "A technique to build a secret key in integrated circuits for identification and authentication applications," in VLSI Circuits, 2004. Digest of Technical Papers. 2004 Symposium on, pp. 176–179, June 2004.

- [23] K. Matsunaga, S. Oshima, T. Minotani, T. Kondo, and H. Morimura, "Automatic identification number generation circuit using NMOS pair current mismatch," *Japanese Journal of Applied Physics*, vol. 54, no. 4S, p. 04DE12, 2015.

- [24] K. Lofstrom, W. Daasch, and D. Taylor, "Ic identification circuit using device mismatch," in *Solid-State Circuits Conference*, 2000. Digest of *Technical Papers. ISSCC. 2000 IEEE International*, pp. 372–373, Feb 2000.

- [25] P. Prabhu, A. Akel, L. Grupp, W.-K. Yu, G. Suh, E. Kan, and S. Swanson, "Extracting device fingerprints from flash memory by exploiting physical variations," in *Trust and Trustworthy Computing* (J. McCune, B. Balacheff, A. Perrig, A.-R. Sadeghi, A. Sasse, and Y. Beres, eds.), vol. 6740 of *Lecture Notes in Computer Science*, pp. 188–201, Springer Berlin Heidelberg, 2011.

- [26] F. Tang, D. Chen, B. Wang, A. Bermak, A. Amira, and S. Mohamad, "CMOS on-chip stable true-random ID generation using antenna effect," *Electron Device Letters, IEEE*, vol. 35, pp. 54–56, Jan 2014.

- [27] R. Maes and V. van der Leest, "Countering the effects of silicon aging on sram pufs," in *Hardware-Oriented Security and Trust (HOST)*, 2014 IEEE International Symposium on, pp. 148–153, May 2014.

- [28] A. Hosey, M. T. Rahman, K. Xiao, D. Forte, and M. Tehranipoor, "Advanced analysis of cell stability for reliable sram pufs," in 2014 IEEE 23rd Asian Test Symposium, pp. 348–353, Nov 2014.