# Fabrication of single-electron tunneling transistors with an electrically formed Coulomb island in a silicon-on-insulator nanowire

Dae Hwan Kim, Suk-Kang Sung, Kyung Rok Kim, Jong Duk Lee, and Byung-Gook Park

Citation: Journal of Vacuum Science & Technology B **20**, 1410 (2002); doi: 10.1116/1.1491551 View online: http://dx.doi.org/10.1116/1.1491551 View Table of Contents: http://scitation.aip.org/content/avs/journal/jvstb/20/4?ver=pdfcov

Published by the AVS: Science & Technology of Materials, Interfaces, and Processing

### Articles you may be interested in

Tunable aluminium-gated single electron transistor on a doped silicon-on-insulator etched nanowire Appl. Phys. Lett. **101**, 103504 (2012); 10.1063/1.4750251

Single-electron tunneling in a silicon-on-insulator layer embedding an artificial dislocation network Appl. Phys. Lett. **88**, 073112 (2006); 10.1063/1.2176849

Single-electron transistor structures based on silicon-on-insulator silicon nanowire fabrication by scanning probe lithography and wet etching J. Vac. Sci. Technol. B **20**, 2824 (2002); 10.1116/1.1523017

Silicon single-electron tunneling device fabricated in an undulated ultrathin silicon-on-insulator film J. Appl. Phys. **90**, 3551 (2001); 10.1063/1.1392959

Enhancement of Coulomb blockade and tunability by multidot coupling in a silicon-on-insulator-based singleelectron transistor Appl. Phys. Lett. **75**, 566 (1999); 10.1063/1.124443

# Fabrication of single-electron tunneling transistors with an electrically formed Coulomb island in a silicon-on-insulator nanowire

Dae Hwan Kim,<sup>a)</sup> Suk-Kang Sung, Kyung Rok Kim, Jong Duk Lee, and Byung-Gook Park<sup>b)</sup> Inter-University Semiconductor Research Center (ISRC) and School of Electrical Engineering, College of Engineering, School of Electrical Engineering No. 016, Kwanak, P. O. Box 34, Seoul National University, San 56-1, Shinlim-dong, Kwanak-gu, Seoul 151-742, Korea

(Received 24 October 2001; accepted 13 May 2002)

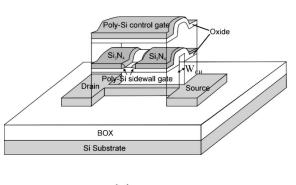

For the purpose of controllable characteristics, silicon single-electron tunneling transistors with an electrically formed Coulomb island are proposed and fabricated on the basis of the sidewall process technique. The fabricated devices are based on a silicon-on-insulator (SOI) metal-oxidesemiconductor (MOS) field effect transistor with the depletion gate. The key fabrication technique consists of two sidewall process techniques. One is the patterning of a uniform SOI nanowire, and the other is the formation of *n*-doped polysilicon sidewall depletion gates. While the width of a Coulomb island is determined by the width of a SOI nanowire, its length is defined by the separation between two sidewall depletion gates which are formed by a conventional lithographic process combined with the second sidewall process. These sidewall techniques combine the conventional lithography and process technology, and guarantee the compatibility with complementary MOS process technology. Moreover, critical dimension depends not on the lithographical limit but on the controllability of chemical vapor deposition and reactive-ion etching. Very uniform weakly p-doped SOI nanowire defined by the sidewall technique effectively suppresses unintentional tunnel junctions formed by the fluctuation of the geometry or dopant in SOI nanowire, and the Coulomb island size dependence of the device characteristics confirms the good controllability. A voltage gain larger than one and the controllability of Coulomb oscillation peak position are also successfully demonstrated, which are essential conditions for the integration of a single-electron tunneling transistor circuit. Further miniaturization and optimization of the proposed device will make room temperature designable single-electron tunneling transistors possible in the foreseeable future. © 2002 American Vacuum Society. [DOI: 10.1116/1.1491551]

### I. INTRODUCTION

Recently, single-electron tunneling phenomena in silicon nanostructures have been extensively studied in terms of future low-power nanoelectronic device applications. In comparison with GaAs heterostructures, the possibility of the integration with the conventional complementary metal– oxide–semiconductor (CMOS) devices is a unique merit of silicon nanostructures.

Up to now, various single-electron tunneling transistors (SETTs) based on silicon-on-insulator (SOI) nanowires have been demonstrated. In the case of highly doped SOI nanowire,<sup>1-4</sup> Coulomb blockade oscillation is attributed to the formation of randomly distributed Coulomb islands separated by tunnel junctions formed by dopant fluctuations, and its dependence on the gate voltage is quite complicated. On the other hand, SETTs based on the undoped SOI nanowire (i.e., weakly p doped)<sup>5,6</sup> show relatively controllable characteristics originated from the device geometry due to the exclusion of a dopant fluctuation effect. Therefore, from the viewpoint of reproducibility of device characteristics, the undoped SOI film is a promising material for the implementation of the SETT circuit.

In most SETTs based on the undoped SOI nanowire, tunnel junctions have been defined using lateral patterning by electron-beam lithography.<sup>5,6</sup> However, its low throughput, high cost, and incompatibility with conventional CMOS technology provides a motivation to pursue an alternative nanoscale lithography technique.

As another technique to form tunnel junctions, a depletion or split gate structure has been used in SETTs based on the bulk silicon metal–oxide–semiconductor field effect transistor (MOSFET),<sup>7–9</sup> in which the Coulomb island is incorporated into the inversion channel at the Si/SiO<sub>2</sub> interface and the tunneling conductance is controlled by the depletion gate voltage.

In this article, we present the fabrication method for SETTs based on a weakly *p*-doped SOI MOSFET with depletion gates. In our process, two sidewall process techniques are used. One is the patterning method for the definition of an SOI nanowire. The other is the formation method of two depletion gates with narrow line and space. These techniques combine the conventional lithography, chemical vapor deposition (CVD), and reactive ion etching (RIE), and guarantee the compatibility with CMOS process technology. Very uniform weakly *p*-doped SOI nanowire defined by the sidewall technique effectively suppresses unintended tunnel junctions formed by the fluctuation of the geometry or dop-

<sup>&</sup>lt;sup>a)</sup>Electronic mail: drlife@smdl.snu.ac.kr

<sup>&</sup>lt;sup>b)</sup>Electronic mail: bgpark@snu.ac.kr

ant in SOI nanowire. A Coulomb island in the inversion channel of the SOI MOSFET is electrically formed by the sidewall depletion gate voltage, and its size is estimated to be smaller than 13.2 nm.

In addition to the idea of device fabrication, we focus on the formation mechanism of the Coulomb island and tunnel junctions in terms of the island size dependence of device characteristics.

#### **II. EXPERIMENT**

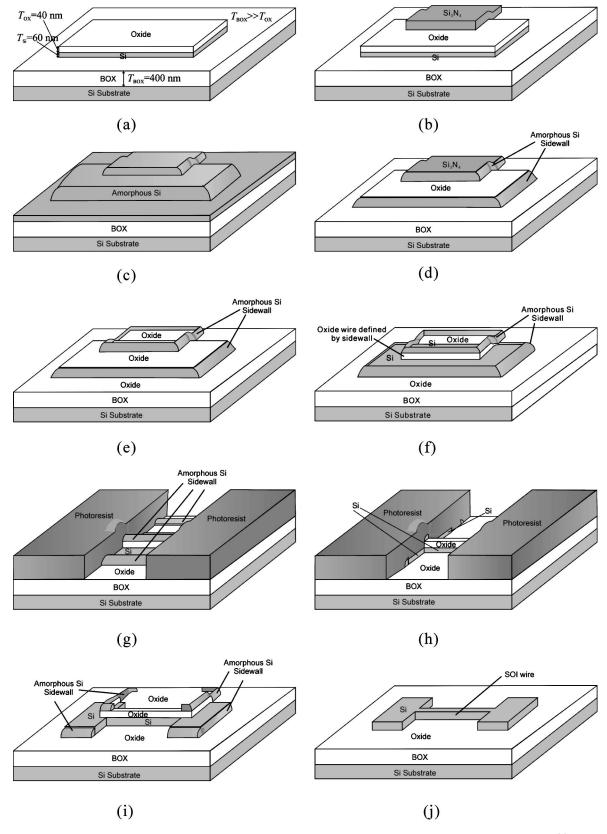

The devices were fabricated on  $4 \times 10^{15}$  cm<sup>-3</sup> boron doped (100) SOI wafers prepared by the separation by implanted oxygen technique. The top Si layer is separated from the Si substrate by 400-nm-thick buried oxide. In the fabrication of our SETTs, two sidewall process techniques are used. First is the patterning method for the formation of a SOI nanowire. The thickness of the top Si layer is thinned to 60 nm by thermal oxidation, and the 40-nm-thick  $SiO_2$  is deposited, and the device region is defined by the conventional photolithography and RIE [Fig. 1(a)]. Then an 80-nmthick  $Si_3N_4$  layer is deposited on the SOI wafer at 750 °C using a low pressure CVD (LPCVD) system and defined by the conventional photolithography and RIE, which covers a part of the device region and a part of the buried oxide region as shown in Fig. 1(b). Then, 35-nm-thick amorphous silicon is deposited at 550 °C using an LPCVD system and annealed at 800 °C for 30 min, so that the edge of Si<sub>3</sub>N<sub>4</sub> layer is fully covered [Fig. 1(c)]. This amorphous silicon layer is anisotropically etched in Cl<sub>2</sub> reactive-ion plasma, resulting in the 30-nm-wide amorphous silicon sidewall around the corner of both the Si<sub>3</sub>N<sub>4</sub> layer and the device region [Fig. 1(d)]. After the selective chemical etching of the  $Si_3N_4$  layer in  $H_3PO_4$  solution [Fig. 1(e)], 40-nm-thick  $SiO_2$ layer is anisotropically etched in CHF<sub>3</sub>/CF<sub>4</sub> reactive-ion plasma using the amorphous silicon sidewall as an etch mask, resulting in 30-nm-wide SiO<sub>2</sub> wire on the device region, and the silicon surface is exposed except underneath this  $SiO_2$  wire as shown in Fig. 1(f). Then, the source and drain region are covered with the photoresist by photolithography [Fig. 1(g)], and the top silicon is etched in  $Cl_2$ reactive-ion plasma using the 30-nm-wide SiO<sub>2</sub> wire as a hardmask, forming the 30-nm-wide SOI nanowire [Fig. 1(h)]. During this step, the exposed amorphous silicon sidewall is also etched in Cl<sub>2</sub> plasma, but the SiO<sub>2</sub> wire is a useful hardmask during the pattern transfer due to a good selectivity between Si and SiO<sub>2</sub> in Cl<sub>2</sub> reactive-ion plasma. Adequate chemical etching of the silicon oxide in HF solution enables the preparation of a damage-free surface of SOI nanowire and the lift-off process of the remnant amorphous silicon sidewall [Figs. 1(i)-1(j)]. In reality, there may be amorphous silicon sidewall residue around the source/drain region even after wet etching of the silicon oxide, as shown in Fig. 1(i), but this residue has no influence on the device operation, thus this residue is left out hereinafter in Fig. 1(j).

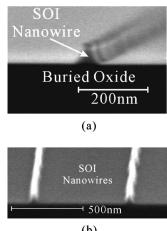

Figure 2 shows the scanning electron microscope (SEM) image of the SOI nanowire formed by our sidewall patterning technique. Uniform 30-nm-wide SOI wire with no ir-

regularities can be defined by our technique, which eliminates unintended tunnel junctions formed by the fluctuation of the width of SOI wire. The uniformity of nanowire defined by the sidewall patterning technique was better than that of nanowire defined by electron-beam lithography.<sup>10</sup> Although it may depend on the performance of electron-beam lithography facilities, irregularity with the size of electronbeam diameter is an inherent problem regardless of the facilities and may be the origin of unintended tunnel junctions formed by the fluctuation of the geometry.<sup>6,11</sup>

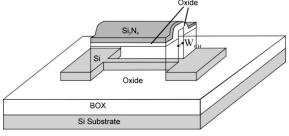

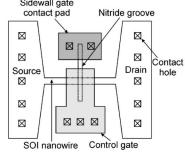

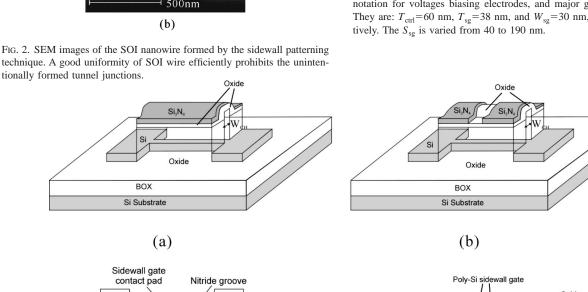

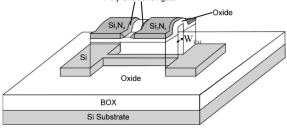

For the electrically formed Si island, two polycrystalline silicon (poly-Si) depletion gates are subsequently formed on the SOI wire, which is our second sidewall process technique. After stripping the remnant oxide on the SOI wire in HF solution, 55-nm-thick SiO<sub>2</sub> is deposited by a plasma enhanced CVD (PECVD) system and etched in CHF<sub>3</sub>/CF<sub>4</sub> reactive-ion plasma, forming the oxide spacer around SOI wire. This spacer plays an important role in the step coverage of the poly-Si sidewall which will act as the depletion gate, by substituting a smoothly curvilinear shape for the step-like shape around the SOI wire. Then, 30-nm-thick SiO<sub>2</sub> is deposited by a PECVD system, and 80-nm-thick Si<sub>3</sub>N<sub>4</sub> is deposited using the LPCVD system [Fig. 3(a)]. Then, a groove pattern is transferred into the Si<sub>3</sub>N<sub>4</sub> layer by the lithography and RIE as shown in Fig. 3(b). This nitride groove pattern is designed to overlap with the region which will become the sidewall gate contact pad, as shown in Fig. 3(c). The width of groove  $W_{Gry}$  is varied from 100 to 250 nm in 50 nm steps in the same wafer by electron-beam lithography using poly-(methylmethacrylate) electron-beam resist, but the feature size of this range can be easily obtained by state-of-the-art photolithography. After the formation of the nitride groove, 8-nm-thick oxide is thermally grown in dry O<sub>2</sub> at 800 °C for damage curing, which forms the gate-oxide-quality control gate oxide. During this step, the control gate oxide becomes thicker locally at the nitride groove region as shown in Fig. 3(d). Then, 35-nm-thick phosphorus doped  $n^+$  poly-Si is deposited using LPCVD, and the sidewall gate contact pad region is covered with the photoresist by photolithography [Fig. 3(c)]. Following etching of the  $n^+$  poly-Si in Cl<sub>2</sub> reactive-ion plasma forms the poly-Si sidewall depletion gates [Fig. 3(d)], which is eventually connected into the lowresistance poly-Si region, i.e., the sidewall gate contact pad region. After stripping the photoresist, the formation of the additional intergate oxide using the PECVD system is followed by the formation of the poly-Si control gate by the photolithography and RIE in Cl<sub>2</sub> plasma. The control gate and source/drain regions are doped by As<sup>+</sup> ion implantation [Fig. 3(e)]. Then, the passivation oxide is deposited using LPCVD, and the contact hole is formed by the photolithography and RIE in CHF<sub>3</sub>/CF<sub>4</sub> plasma [Fig. 3(c)]. Finally, the formation of an aluminum electrode is performed using Al sputtering, photolithography, and RIE in Cl<sub>2</sub> plasma, which is compatible with the conventional CMOS process technology. The resultant thickness of SOI wire was 45 nm, and the final width of SOI wire  $W_{CH}$  shrunk to about 23 nm.

Figure 4 shows the cross section of the fabricated device,

FIG. 1. Key process steps to form SOI nanowire by the sidewall patterning technique. These are just schematics, not to the exact scale. (a) The definition of the device region and the oxide layer. (b) The definition of the  $Si_3N_4$  layer overlapped between the device region and the buried oxide region. (c) The deposition of the amorphous silicon layer. (d) The anisotropic etching of the amorphous silicon and the formation of a 30-nm-wide amorphous silicon sidewall around the corner of both the  $Si_3N_4$  layer and the device region. (e) The chemical etching of the  $Si_3N_4$  layer in  $H_3PO_4$  solution. (f) The anisotropic etching of the oxide layer. (g) The blocking of the source and drain region by the photoresist. (h) The anisotropic etching of silicon and the formation of 30-nm-wide SOI wire. (i) The stripping of the photoresist. (j) The chemical etching of the oxide and the lift-off of the remnant amorphous silicon sidewall.

#### J. Vac. Sci. Technol. B, Vol. 20, No. 4, Jul/Aug 2002

Poly-Si Sidewall Depletion Gate W<sub>Grv</sub> Poly-Si Control Gate Si<sub>3</sub>N<sub>4</sub> Si<sub>3</sub>N<sub>4</sub> SiO Drain Source SOI ⊥ d BOX Si Island Si Substrate (V**Back Gate**

FIG. 4. Schematic diagram of the cross section of a fabricated device, the notation for voltages biasing electrodes, and major geometric parameters. They are:  $T_{ctrl}$ =60 nm,  $T_{sg}$ =38 nm, and  $W_{sg}$ =30 nm,  $L_{CH}$ =7  $\mu$ m, respec-

technique. A good uniformity of SOI wire efficiently prohibits the unintentionally formed tunnel junctions.

(e)

FIG. 3. Key process steps to form two sidewall depletion gates and the top control gate on the SOI nanowire. (a) The deposition of the gate oxide and Si<sub>3</sub>N<sub>4</sub> layer. (b) The formation of the groove in the  $Si_3N_4$  layer, whose width  $W_{Grv}$  is varied from 100 to 250 nm on the same wafer. (c) The layout of a fabricated SETT. (d) Thermal oxidation and the formation of n-type doped poly-Si sidewall depletion gates. (e) The deposition of control gate oxide and the formation of the poly-Si control gate.

(d)

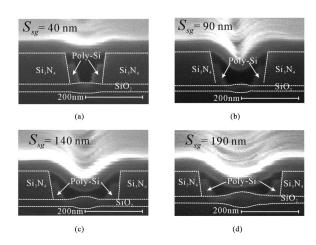

FIG. 5. SEM images of the cross section along the channel length direction of fabricated SETTs having various  $S_{sg}$ 's on the same 4 in. SOI wafer: (a)  $S_{sg}$ =40 nm, (b)  $S_{sg}$ =90 nm, (c)  $S_{sg}$ =140 nm, (d) and  $S_{sg}$ =190 nm.

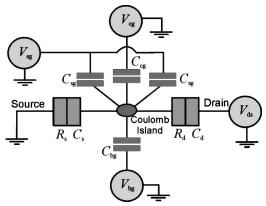

FIG. 6. Equivalent circuit diagram of the fabricated SETTs. The charge of Coulomb island is coupled with five capacitance components. They are: the capacitance between the control gate and island  $C_{\rm cg}$ , the capacitance between the drain electrode and island  $C_d$ , the capacitance between the source electrode and island  $C_s$ , the capacitance between sidewall depletion gate and island  $C_{\rm sg}$ , and the capacitance between the back gate and island  $C_{\rm bg}$ . Tunneling resistances  $R_d$  and  $R_s$  and tunnel junction capacitances  $C_d$  and  $C_s$  are determined by the shape of the potential barrier induced by  $V_{\rm sg}$ .

indicating bias electrodes and major geometric parameters. They are:  $T_{ctrl}$  (thickness of the control gate oxide)=60 nm,  $T_{\rm sg}$  (thickness of the sidewall depletion gate oxide)=38 nm,  $W_{\rm sg}$  (width of the sidewall depletion gate)=30 nm, and  $L_{\rm CH}$ (length of SOI wire)=7  $\mu$ m, respectively. The space between two sidewall gates  $S_{sg}$  is 40, 90, 140, and 190 nm, respectively, because  $S_{sg}$  is given by  $W_{Grv} - 2 \times W_{sg}$ . Thus, the length of the Coulomb island shrank to be smaller than the feature size of state-of-the-art lithography, by a conventional lithographic process (electron-beam lithography in this work) combined with a sidewall process technique. In our devices, the effective size of Coulomb island should be smaller than  $S_{sg} \times W_{CH}$ , due to the electric field effect. Figure 5 shows SEM images of the cross section along the channel length direction of fabricated SETTs having various  $S_{sg}$ 's on the same 4 in. SOI wafer.

The operation of the device is as follows: the formation of the inversion layer (i.e., threshold voltage of SOI MOSFET) is controlled by the back gate voltage  $V_{\rm bg}$ , and two tunnel junctions are formed by poly-Si sidewall depletion gate voltage  $V_{\rm sg}$ . The charge of the electrically formed island is controlled by the control gate voltage  $V_{\rm cg}$ .

The salient feature of our process technique can be summarized as follows: Using the combination of conventional lithography and process technology, the size of the Coulomb island and tunnel junctions can be defined beyond the limit of state-of-the-art lithography.

The first idea for the development of the Si island with the capacitance of a few aF is the formation of a SOI nanowire by the sidewall patterning technique. The next idea is the formation of a sidewall depletion gate in the groove with the feature size of state-of-the-art lithography.<sup>12</sup>  $W_{CH}$  and  $W_{sg}$  defined by the sidewall process technique have a good uniformity, which suppresses unintentional tunnel barriers in the SOI wire effectively, as previously described. Moreover, the proposed sidewall technique has the merit in that its scaling limit depends not on the limit of lithography but on the controllability of CVD and RIE.

#### **III. RESULTS AND DISCUSSION**

## A. Coulomb island size dependence of device characteristics

Figure 6 shows the equivalent circuit diagram of the fabricated SETTs. The charge of the Coulomb island is coupled with five capacitance components. They are: the capacitance between the control gate and island  $C_{\rm cg}$ , the capacitance between the drain and island  $C_d$ , the capacitance between the source and island  $C_s$ , the capacitance between the source and island  $C_{\rm sg}$ , and the capacitance between the back gate and island  $C_{\rm bg}$ . Tunneling resistances  $R_d$  and  $R_s$  and tunnel junction capacitances  $C_d$  and  $C_s$  are determined by the shape of the potential barrier induced by  $V_{\rm sg}$ , and the period of Coulomb oscillation in sweeping  $V_{\rm cg}$  ( $\Delta V_{\rm cg}$ ) is determined by  $C_{\rm cg}$ . The total capacitance of an electrically formed Si island  $C_{\rm total}$  will be the summation of  $C_{\rm cg}$ ,  $C_d$ ,  $C_s$ ,  $2C_{\rm sg}$ , and  $C_{\rm bg}$ .

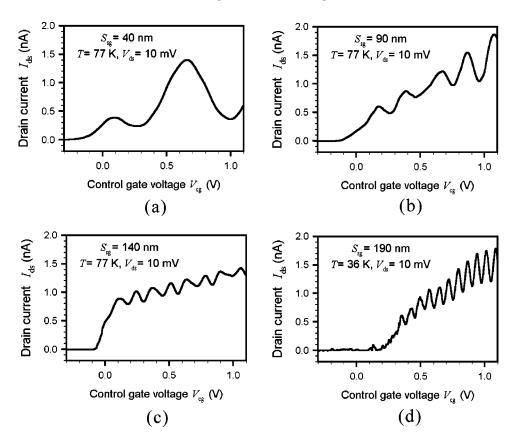

The devices were characterized by a precision semiconductor parameter analyzer HP4155A. Figure 7 shows the drain current  $I_{ds}$  as a function of the control gate voltage  $V_{cg}$ and the size of Coulomb island  $S_{sg}$ . In these  $I_{ds}-V_{cg}$  curves,  $V_{ds}$ ,  $V_{sg}$ , and  $V_{bg}$  are fixed at 10 mV, -0.1 V, and 10 V, respectively. Multiple Coulomb oscillation peaks are clearly observed even at the liquid nitrogen temperature. The period of Coulomb oscillation  $\Delta V_{cg}$  in the  $I_{ds}-V_{cg}$  curve is 675, 210, 123, and 80 mV, respectively, as  $S_{sg}$  is varied from 40 to 190 nm. The clear difference of  $\Delta V_{cg}$  related to  $S_{sg}$  verifies that the oscillation of  $I_{ds}$  stems from single-electron tunneling phenomenon in an electrically formed Coulomb island, and its size is controllable by the process parameter  $S_{sg}$ . This Coulomb oscillation showed reliable single-island characteristics at various temperatures.<sup>13</sup>

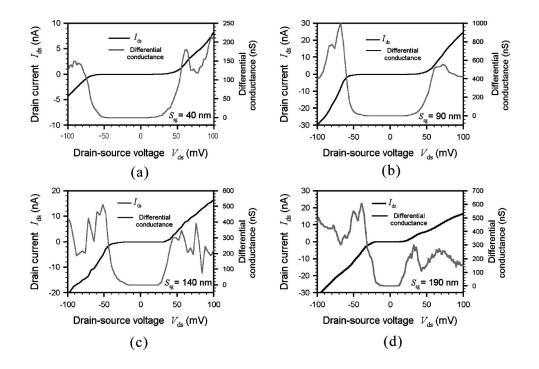

The drain current  $I_{ds}$  and the differential conductance as a function of the drain–source voltage  $V_{ds}$  and the size of Coulomb island  $S_{sg}$  is also measured at 15 K as shown in Fig. 8.

1414

FIG. 7. Drain current  $I_{ds}$  as a function of the control gate voltage  $V_{cg}$  and the size of Coulomb island  $S_{sg}$ . In these  $I_{ds}-V_{cg}$  curves,  $V_{ds}$ ,  $V_{sg}$ , and  $V_{bg}$ were fixed at 10 mV, -0.1 V, and 10 V, respectively. (a)  $S_{sg}$ =40 nm, (b)  $S_{sg}$ =90 nm, (c)  $S_{sg}$ =140 nm, (d) and  $S_{sg}$ =190 nm.

These  $I_{ds}-V_{ds}$  curves are acquired, fixing  $V_{sg}$  and  $V_{bg}$  at -0.1 and 10 V, respectively. Nonlinear relation between  $I_{ds}$  and  $V_{ds}$  by Coulomb blockade phenomenon is clearly observed. When measuring  $I_{ds}-V_{ds}$  characteristics,  $V_{cg}$  is chosen to be the value at the valley of the oscillation in  $I_{ds}-V_{cg}$  curve, i.e., the voltage region showing the zero-differential

conductance is the maximum Coulomb gap voltage  $\Delta V_{\text{MAX}}$ , which is 104, 76, 59, and 45 mV, respectively, as  $S_{\text{sg}}$  is varied from 40 to 190 nm.

The  $S_{sg}$  dependence of device characteristics suggests that our SETTs are based on a clearly artificial formation mechanism of a Coulomb island and tunnel junctions. Moreover,

FIG. 8. Drain current  $I_{ds}$  and the differential conductance as a function of the drain–source voltage  $V_{ds}$  and the size of Coulomb island  $S_{sg}$  measured at 15 K. In these  $I_{ds}-V_{ds}$  curves,  $V_{sg}$  and  $V_{bg}$  were fixed at -0.1 and 10 V, respectively.  $V_{cg}$ was chosen to be the value at the valley of the oscillation in the  $I_{ds}-V_{cg}$  curve, i.e., the voltage region showing the zero-differential conductance is the maximum Coulomb gap voltage  $\Delta V_{MAX}$ : (a)  $S_{sg}$ =40 nm, (b)  $S_{sg}$ =90 nm, (c)  $S_{sg}$ =140 nm, and (d)  $S_{sg}$ =190 nm.

JVST B - Microelectronics and Nanometer Structures

TABLE I. Summary of the device parameters extracted from the electrical characteristics. They are well controlled by the process parameter  $S_{sg}$ , which is miniaturized to be smaller than the limit of state-of-the-art lithography by the combination of the conventional lithography and process technology. The size of the Coulomb island shrank to 50%–80% of the size of the defined island (i.e.,  $S_{sg} \times W_{CH}$ ) by the device geometry, which is originated from the field effect of sidewall depletion gate bias  $V_{sg}$ . In the case of  $S_{sg}=40$  nm, the size of the Coulomb island may be about 13.2 nm.

|                                                                                                                                                                                                        | Defined island size $S_{sg}$ |                 |          |                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|-----------------|----------|------------------|

| Device parameters                                                                                                                                                                                      | 40 nm                        | 90 nm           | 140 nm   | 190 nm           |

| Coulomb oscillation period $\Delta V_{\rm cg}$                                                                                                                                                         | 675 mV                       | 210 mV          | 123 mV   | 80 mV            |

| Coulomb gap voltage at $V_{cg}$<br>at the valley of $I_{ds}$ oscillation $\Delta V_{MAX}$<br>$C_{cg}$ extracted from $\Delta V_{cg}$                                                                   | 104 mV                       | 76 mV           | 59 mV    | 45 mV            |

| $C_{\rm cg} = \frac{e}{\Delta V_{\rm cg}}$                                                                                                                                                             | 0.24 aF                      | 0.76 aF         | 1.30 aF  | 2.0 aF           |

| $C_{\rm cg}$ estimated from the device geometry<br>(two parallel plate approximation)<br>$C_{\rm cg} = \varepsilon_{\rm SiO_2} \times \frac{S_{\rm sg} \times W_{\rm CH}}{T_{\rm ctrl}} \times \alpha$ | 0.49 <i>α</i> aF             | $1.17\alpha$ aF | 1.77α aF | 2.45 <i>α</i> aF |

| Island size shrinkage factor $\alpha$                                                                                                                                                                  | 0.49                         | 0.65            | 0.73     | 0.82             |

| $C_d$ extracted from measured $I_{ds}$ contour                                                                                                                                                         | 1.30 aF                      | 1.34 aF         | 1.42 aF  | 1.54 aF          |

| $C_{\text{total}}$ extracted from measured $I_{\text{ds}}$ contour<br>and $\Delta V_{\text{MAX}}$ at constant $V_{\text{sg}}$ and $V_{\text{bg}}$                                                      | 2.86 aF                      | 3.44 aF         | 4.14 aF  | 5.08 aF          |

| Voltage gain $K_V$<br>Island size $2r$ estimated from the self<br>capacitance $C_{self}$ under assumption of                                                                                           | 0.185                        | 0.57            | 0.92     | 1.3              |

| spherical Coulomb island in a SiO <sub>2</sub> environment $C_{\text{self}}=4\pi\epsilon r$                                                                                                            | 13.2 nm                      | 15.9 nm         | 19.1 nm  | 23.4 nm          |

the process parameter  $S_{sg}$  can be controlled by the conventional lithography with the feature size of 0.1  $\mu$ m and process technology such as CVD and RIE, without a special nanoscale lithography method. In addition, it is confirmed by the electrical characteristics that the good uniformity and low doping level of SOI nanowire effectively suppress tunnel junctions unintentionally formed by the fluctuation of the geometry or dopant.

A few device parameters extracted from the electrical characteristics of fabricated SETTs are summarized in Table I. Comparing  $\Delta V_{cg}$  with  $C_{cg}$  estimated from the device geometry,  $C_{cg}$  extracted from  $\Delta V_{cg}$  is about 50%–80% of that calculated from the device geometry, which implies that the size of the Coulomb island shrank to be smaller than the defined island (i.e.,  $S_{sg} \times W_{CH}$ ) by the field effect of  $V_{sg}$ . Thus, the potential barrier by  $V_{sg}$  penetrates into the region of the defined island. However, the  $\Delta V_{cg}$  is seldom varied when sweeping  $V_{cg}$  at a constant  $V_{sg}$  (see Fig. 7), which confirms that the size of the Coulomb island is dominantly controlled by  $S_{sg}$  and  $V_{sg}$  and immune to  $V_{cg}$ , i.e.,  $V_{cg}$  independently controls the potential of the Coulomb island. These characteristics stem from the three-dimensional structure of the poly-Si sidewall depletion gate wrapping the SOI nanowire.

Since the poly-Si control gate fully covers the SOI wire, fringing capacitance exists as an additional component of the effective  $C_{cg}$ . Therefore, the real size is maybe less than 50% of the defined island. As shown in Table I, if we compare the total capacitance of the Coulomb island  $C_{total}$  ex-

tracted from the  $I_{ds}$  contour with the self capacitance of the spherical conducting island in a SiO<sub>2</sub> environment, the island size of SETT with  $S_{sg}$ =40 nm is about 13.2 nm, which is less than a half of  $S_{sg}$ .

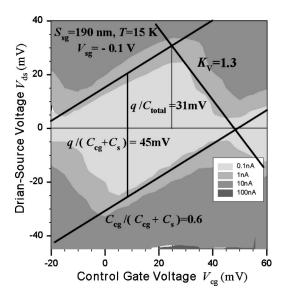

#### B. Voltage gain and peak position control

The  $I_{ds}$  contour of SETT with  $S_{sg}$ =190 nm at 15 K is shown in Fig. 9, whose shape is a well-known parallelogram, the so called Coulomb diamond. The  $C_{total}$  of the island is 5.08 aF, which corresponds to the charging energy of 15.7 meV and the thermal noise of 188 K. From the slope of contour,  $C_{cg}$ ,  $C_d$ , and  $C_s$  are given to be 2.0, 1.54, and 1.33 aF, respectively.

Of importance is the voltage gain  $K_V$  of SETTs in the viewpoint of the application to a practical integrated circuit. It is given as the ratio  $C_{cg}/C_d$  at a constant current.<sup>14</sup> Low current level and small voltage gain are inherent demerits of SETTs. Up to now, technologically oriented research has been primarily focused on the further miniaturization of the basic component of SETTs, while ignoring the voltage gain. A voltage gain larger than unity has been recently reported and discussed.<sup>15–17</sup> Our device shows  $K_V=1.3$  as shown in Fig. 9. On the other hand, the  $K_V$  decreases as the island size is smaller (Table I), because the capacitive coupling between the island and the control gate decreases while  $C_d$  and  $C_s$  are nearly invariant. Therefore, both  $S_{sg}$  and  $T_{ctrl}$  should be scaled down for the application of our SETTs to the room temperature operation. In addition,  $K_V$  is expected to in-

FIG. 9.  $I_{ds}$  contour, i.e., Coulomb diamond of SETT with  $S_{sg}$ =190 nm. The measurement temperature was 15 K and the voltage gain  $K_V$  was 1.3 from the slope of the contour.

crease as the thickness of SOI wire decreases, but the optimization of the concentration of impurities and the thickness of SOI wire is required.

The controllability of the peak position<sup>9,16,18</sup> of Coulomb oscillation is another issue. It is indispensable to most SETT circuits. However, the randomness of background charge makes it difficult to control the position of the oscillation peak. In the case of recently published SETTs, an asymmetric tunnel barrier,<sup>9</sup> additional side gate,<sup>16</sup> or a Si nanocrystal floating gate<sup>18</sup> is used for the peak position control. But these ideas have the demerits of varied current level,<sup>9</sup> large area of device structure,<sup>16</sup> and irreproducible programming characteristics from randomly distributed Si nanocrystals,<sup>18</sup> respectively. In our structure, a sidewall depletion gate can control the sharing of the island charge between the control gate and sidewall depletion gate as shown in Fig. 6.

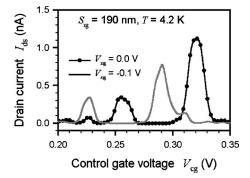

Figure 10 shows the  $V_{\rm cg}$  dependence of  $I_{\rm ds}$  as a function of  $V_{\rm sg}$  at 4.2 K for a SETT with  $S_{\rm sg}$ =190 nm. The position of the oscillation peak is well modulated by  $V_{\rm sg}$ . The slight decrease of  $I_{\rm ds}$  at  $V_{\rm sg}$ =-0.1 V is attributed to the increase of the potential barrier height by negatively larger  $V_{\rm sg}$ . The position of the oscillation peak in the  $V_{\rm cg}$  axis is modulated by 58 mV, when  $V_{\rm sg}$  is changed by 100 mV while  $V_{\rm ds}$  and  $V_{\rm bg}$  are fixed at 10 mV and 18 V, respectively. Quantitatively, the displacement of the oscillation peak in the  $V_{\rm cg}$  axis ( $\Delta V_{\rm cgd}$ ) by the change of the  $V_{\rm sg}$  ( $\Delta V_{\rm sg}$ ) can be analytically derived from the charge sharing of Coulomb island, which is as follows:

$$\left(1 - \frac{C_{\rm cg}}{C_{\rm total}}\right) \times \Delta V_{\rm cgd} = \frac{2C_{\rm sg}}{C_{\rm total}} \times \Delta V_{\rm sg}.$$

(1)

From Eq. (1),  $C_{sg}$  is estimated to be 0.89 aF, assuming  $C_{cg}=2.0$  aF,  $C_{total}=5.08$  aF (see Table I),  $\Delta V_{cgd}=58$  mV, and

FIG. 10.  $V_{cg}$  dependence of  $I_{ds}$  at 4.2 K as a function of  $V_{sg}$  of SETT with  $S_{sg}$ =190 nm.  $V_{ds}$  and  $V_{bg}$  were fixed at 10 mV and 18 V, respectively. The position of oscillation peak is well controlled by  $V_{sg}$ . The slight decrease of  $I_{ds}$  at  $V_{sg}$ =-0.1 V is attributed to the increase of the potential barrier height by negatively larger  $V_{sg}$ .

$\Delta V_{sg}$ =100 mV. The  $C_{sg}$  is estimated from the device geometry by the simple formula as follows:

$$C_{\rm sg} = \varepsilon_{\rm SiO_2} \times \frac{W_{\rm sg} \times W_{\rm CH}}{T_{\rm sg}} = 0.63 \text{ aF.}$$

(2)

This discrepancy means that Eq. (2) underestimates  $C_{sg}$  by neglecting the fringing capacitance component due to the poly-Si sidewall depletion gate wrapping SOI nanowire, as in the case of  $C_{cg}$ . But the error is larger in the case of the calculation of  $C_{sg}$ , because the sidewall depletion gate more closely covers the SOI wire than the control gate.

Finally, from the viewpoint of the SETT circuit, the resistance issue should be discussed. In our SETTs, the cross section of both the SOI nanowire and the sidewall depletion gate is so small that their resistances should be lowered. In the case of the SOI wire, its length should be decreased by the integration of many SETTs because the maximum limit of the cross section of the SOI nanowire manifests itself, in terms of the operation temperature and the theoretical premise about the resistance quantum (tunneling resistance  $\geq$ 26 k $\Omega$ ). Because the sidewall depletion gate is made of highly *n*-doped poly-Si, its resistance issue is less conspicuous. The cross section of the sidewall depletion gate is correlated with both the resistance and the capacitance of electrically induced tunnel junction as is the case in that of the SOI wire, thus, there still exists its maximum boundary. To optimize the resistance issue, the nitride grooves of many integrated SETTs should be efficiently arranged, and the selfaligned doping technique by the ion implantation is necessary.

The properties of our SETTs are summarized as follows. First, scaling down of the size of Coulomb island is easier in comparison with SETTs relying on a special nanoscale lithography, in that the dimension of critical parameters (i.e.,  $W_{\rm CH}$ ,  $S_{\rm sg}$ , and  $W_{\rm sg}$ ) depends on the controllability of CVD and RIE.

Second, the formation of the Coulomb island beyond the feature size of state-of-the-art lithography is possible, by the combination of the conventional lithography and process technology, which guarantees the compatibility with CMOS technology.

#### JVST B - Microelectronics and Nanometer Structures

Third, the control of the position of the Coulomb oscillation peak is possible without additional gate electrode, since the poly-Si sidewall depletion gates play two major roles in the formation of tunnel junctions and the control of peak position. Thus, our device provides a variety of possibilities in the integrated SETT circuit application.

#### **IV. CONCLUSIONS**

We have developed a fabrication method for SETTs, based on a lightly *p*-doped SOI MOSFET with the depletion gate by using the combination of conventional lithography and process technology. The key fabrication method consists of two sidewall process techniques, which are the patterning of a uniform SOI nanowire and the formation of *n*-doped poly-Si sidewall depletion gates. The feature of our technology is that the scaling limit is not influenced by the limit of lithography but by the controllability of CVD and RIE.

Critical device parameters are controlled by the device geometry design, and single-electron tunneling phenomena in an electrically defined single island having various sizes are clearly observed at 77 K. A voltage gain larger than one and the controllability of Coulomb oscillation peak position are also successfully demonstrated, which are essential conditions for the practical integration of SETTs. Further miniaturization and optimization of our SETTs will make it possible to develop controllable and reproducible SETTs operating at room temperature.

#### ACKNOWLEDGMENTS

This work has been supported by the BK 21 program and the national program for "Tera-bit Level Nano Device Project" as a part of the 21st Century Frontier Project. It has also been partially supported by the National Research Laboratory (NRL) Project of the Ministry of Science and Technology.

- <sup>1</sup>R. A. Smith and H. Ahmed, J. Appl. Phys. 81, 2699 (1997).

- <sup>2</sup>A. Tike, R. H. Blick, H. Lorenz, J. P. Kotthaus, and D. A. Wharam, Appl. Phys. Lett. **75**, 3704 (1999).

- <sup>3</sup>R. Augke, W. Eberhardt, C. Single, F. E. Prins, D. A. Wharam, and D. P. Kern, Appl. Phys. Lett. **76**, 2065 (2000).

- <sup>4</sup>A. Tike, R. H. Blick, H. Lorenz, and J. P. Kotthaus, J. Appl. Phys. **89**, 8159 (2001).

- <sup>5</sup>E. Leobandung, L. Guo, Y. Wang, and S. Y. Chou, Appl. Phys. Lett. **67**, 938 (1995).

- <sup>6</sup>L. Zhuang, L. Guo, and S. Y. Chou, Appl. Phys. Lett. 72, 1205 (1998).

- <sup>7</sup>H. Matsuoka and S. Kimura, Appl. Phys. Lett. 66, 613 (1995).

- <sup>8</sup>F. Simmel, D. Abusch-Magder, D. A. Wharam, M. A. Kastner, and J. P. Kotthaus, Phys. Rev. B **59**, R10441 (1999).

- <sup>9</sup>D. H. Kim, J. D. Lee, and B.-G. Park, Jpn. J. Appl. Phys., Part 1 **39**, 2329 (2000).

- <sup>10</sup>S.-K. Sung, J. S. Sim, D. H. Kim, J. D. Lee, and B.-G. Park, Abstracts of 2001 Silicon Nanoelectronics Workshop, Kyoto, June 2001.

- <sup>11</sup>K. R. Kim, D. H. Kim, J. D. Lee, and B.-G. Park, Abstracts of 2001 Silicon Nanoelectronics Workshop, Kyoto, June 2001.

- <sup>12</sup>United States Patent No. 6,211,013 (3 April 2001).

- <sup>13</sup>D. H. Kim, S.-K. Sung, J. S. Sim, K. R. Kim, J. D. Lee, B.-G. Park, B. H.

- Choi, S. W. Hwang, and D. Ahn, Appl. Phys. Lett. 79, 3812 (2001).

- <sup>14</sup>K. K. Likharev, IEEE Trans. Magn. **23**, 1142 (1987).

- <sup>15</sup>R. A. Smith and H. Ahmed, Appl. Phys. Lett. **71**, 3838 (1997).

- <sup>16</sup>Y. Ono, Y. Takahashi, K. Yamazaki, M. Nagase, H. Namatsu, K. Kurihara, and K. Murase, Appl. Phys. Lett. **76**, 3121 (2000).

- <sup>17</sup>K. Nishiguchi and S. Oda, Appl. Phys. Lett. **78**, 2070 (2001).

- <sup>18</sup>N. Takahashi, H. Ishikuro, and T. Hiramoto, Appl. Phys. Lett. **76**, 209 (2000).