## ARCHITECTURES AND DESIGN OF VLSI MACHINE LEARNING SYSTEMS

A Dissertation

by

## QIAN WANG

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Peng Li             |

|---------------------|---------------------|

| Committee Members,  | Gwan Choi           |

|                     | Sam Palermo         |

|                     | Yoonsuck Choe       |

| Head of Department, | Miroslav M. Begovic |

August 2016

Major Subject: Computer Engineering

Copyright 2016 Qian Wang

#### ABSTRACT

Quintillions of bytes of data are generated every day in this era of big data. Machine learning techniques are utilized to perform predictive analysis on these data, to reveal hidden relationships and dependencies and perform predictions of outcomes and behaviors. The obtained predictive models are used to interpret the existing data and predict new data information.

Nowadays, most machine learning algorithms are realized by software programs running on general-purpose processors, which usually takes a huge amount of CPU time and introduces unbelievably high energy consumption. In comparison, a dedicated hardware design is usually much more efficient than software programs running on general-purpose processors in terms of runtime and energy consumption. Therefore, the objective of this dissertation is to develop efficient hardware architectures for mainstream machine learning algorithms, to provide a promising solution to addressing the runtime and energy bottlenecks of machine learning applications. However, it is a really challenging task to map complex machine learning algorithms to efficient hardware architectures. In fact, many important design decisions need to be made during the hardware development for efficient tradeoffs.

In this dissertation, a parallel digital VLSI architecture for combined SVM training and classification is proposed. For the first time, cascade SVM, a powerful training algorithm, is leveraged to significantly improve the scalability of hardware-based SVM training and develop an efficient parallel VLSI architecture. The parallel SVM processors provide a significant training time speedup and energy reduction compared with the software SVM algorithm running on a

general-purpose CPU.

Furthermore, a liquid state machine based neuromorphic learning processor with integrated training and recognition is proposed. A novel theoretical measure of computational power is proposed to facilitate fast design space exploration of the recurrent reservoir. Three low-power techniques are proposed to improve the energy efficiency. Meanwhile, a 2-layer spiking neural network with global inhibition is realized on Silicon.

In addition, we also present architectural design exploration of a brain-inspired digital neuromorphic processor architecture with memristive synaptic crossbar array, and highlight several synaptic memory access styles. Various analog-todigital converter schemes have been investigated to provide new insights into the tradeoff between the hardware cost and energy consumption.

# DEDICATION

To my parents

### ACKNOWLEDGEMENTS

First and foremost, I am very grateful to have had the opportunity to work with a great research advisor Dr. Peng Li and would like to thank him with my deep respect for his valuable advice and consistent support during my doctoral studies at Texas A&M University. Dr. Li has actively encouraged me to move forward with new innovative research ideas and willingly shared his profound knowledge, deep insight and creative inspiration so I could learn the way of research from him. Also, I would like to thank my committee members Dr. Gwan Choi, Dr. Sam Palermo and Dr. Yoonsuck Choe for their constructive discussions and suggestions on my research, making this dissertation possible.

My appreciation goes to all the members in our research group for their knowledge, discussion and friendship. Particular thanks go to Yingyezhe Jin and Youjie Li for the simulation and hard implementation supports. Many friends in the department have made my stay of four years in College Station a pleasurable and unforgettable experience. I also want to acknowledge all my other friends who have consistently helped me at A&M for their considerable assistances.

From deep down in my heart, I would like to thank my parents and other family members for their devotion, support and encouragement.

# TABLE OF CONTENTS

|     |                                               | Η                                                                                                                                                                                                                     | Page                             |

|-----|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| AB  | STR                                           | ACT                                                                                                                                                                                                                   | ii                               |

| DE  | DIC                                           | ATION                                                                                                                                                                                                                 | iv                               |

| AC  | CKNC                                          | OWLEDGEMENTS                                                                                                                                                                                                          | v                                |

| TA  | BLE                                           | OF CONTENTS                                                                                                                                                                                                           | vi                               |

| LIS | ST OI                                         | F FIGURES                                                                                                                                                                                                             | ix                               |

| LIS | ST OI                                         | F TABLES                                                                                                                                                                                                              | xvii                             |

| 1.  | INT                                           | RODUCTION                                                                                                                                                                                                             | 1                                |

|     | 1.1<br>1.2<br>1.3<br>1.4                      | A Parallel Digital VLSI Architecture for Support Vector Machine<br>Energy Efficient Parallel Neuromorphic Learning Systems<br>Emerging Memory Technologies for Neuromorphic Processors<br>Outline of the Dissertation | 7<br>9<br>13<br>15               |

| 2.  | BAC                                           | CKGROUND AND RELATED WORKS                                                                                                                                                                                            | 16                               |

|     | <ul><li>2.1</li><li>2.2</li><li>2.3</li></ul> | Support Vector Machine and Hardware Implementations                                                                                                                                                                   | 27<br>29<br>31<br>37<br>44<br>49 |

| 3.  |                                               | ARALLEL DIGITAL VLSI ARCHITECTURE FOR SUPPORT VEC-<br>R MACHINE                                                                                                                                                       | 55                               |

|     | 3.1<br>3.2                                    | <ul> <li>Cascade SVM Training Algorithm</li></ul>                                                                                                                                                                     | 58                               |

|    |     | 3.2.2   | Multi-layer System Bus Architecture                          | 63  |

|----|-----|---------|--------------------------------------------------------------|-----|

|    |     | 3.2.3   | Design of Flexible SVM Units                                 | 67  |

|    |     | 3.2.4   | Flexible Processing Configurations                           |     |

|    |     | 3.2.5   | Global Convergence Checking and Classification               |     |

|    | 3.3 | Exper   | imental Results                                              |     |

|    |     | 3.3.1   | Layout and Area Breakdown                                    | 77  |

|    |     | 3.3.2   | Comparison between 90nm SVM Designs and a 45nm Gen-          |     |

|    |     |         | eral Purpose Processor                                       | 80  |

|    |     | 3.3.3   | Impact of Cascade SVM Feedbacks                              |     |

|    |     | 3.3.4   | Comparison between Temporal Reuse, Fully Parallel and Hy-    |     |

|    |     |         | brid Configurations                                          | 85  |

|    |     | 3.3.5   | Classification for Different Data Sets                       | 88  |

|    |     | 3.3.6   | Solution for Higher-dimensional Problems                     | 89  |

|    | 3.4 | Summ    | nary                                                         | 91  |

| 4. | ENE | ERGY E  | FFICIENT PARALLEL NEUROMORPHIC ARCHITECTURES                 |     |

|    | FOF | R SPIKI | NG NEURAL NETWORKS                                           | 93  |

|    | 4.1 | Gener   | al Purpose LSM Learning Processor Architecture and Theo-     |     |

|    |     | retical | lly Guided Design Space Exploration                          | 94  |

|    |     | 4.1.1   | Overall Hardware LSM Architecture                            | 95  |

|    |     | 4.1.2   | Implementation of the Digital Neurons                        | 96  |

|    |     | 4.1.3   | Theoretically Guided Design Space Exploration                | 100 |

|    |     | 4.1.4   | Energy Efficient Realization for Multiple Tasks              |     |

|    |     | 4.1.5   | Low-Power Design Techniques for Each Task                    | 107 |

|    |     | 4.1.6   | Proposed Approximate Adder                                   | 108 |

|    |     | 4.1.7   | Summary                                                      | 113 |

|    | 4.2 | A Para  | allel Neuromorphic Architecture for a 2-layer Spiking Neuron |     |

|    |     | Netwo   | ork with Global Inhibition                                   | 115 |

|    |     | 4.2.1   | Serial Baseline Neuromorphic Processor Architecture          |     |

|    |     | 4.2.2   | Parallel Architectures                                       | 122 |

|    |     | 4.2.3   | Experimental Results                                         |     |

|    |     | 4.2.4   | Summary                                                      | 132 |

| 5. | ARC | CHITEC  | CTURAL EXPLORATION OF NEUROMORPHIC PROCESSORS                | 5   |

|    | WIT | TH MEN  | MRISTIVE SYNAPSES                                            | 134 |

|    | 5.1 |         | Pigital Neuromorphic Processor Architecture with Memristor   |     |

|    |     |         | otic Array                                                   |     |

|    | 5.2 |         | roposed Architectures                                        |     |

|    |     | 5.2.1   | Memory Access Styles                                         |     |

|    |     | 5.2.2   | Analog-to-Digital Conversion                                 |     |

|    |     | 5.2.3   | Optimized Storage Strategy for Feedforward Networks          | 147 |

| 5.2.4 The Baseline Building Components of the Propose DNP Ar-    |   |

|------------------------------------------------------------------|---|

| chitectures                                                      | 0 |

| 5.2.5 The Parallel Neuron Integration                            | 3 |

| 5.3 Experimental Results                                         | 4 |

| 5.4 Summary                                                      |   |

| 6. CONCLUSION AND FUTURE WORK                                    | 6 |

| 6.1 Conclusion                                                   | 6 |

| 6.1.1 A Parallel Digital VLSI Architecture for Cascade SVM 16    | 6 |

| 6.1.2 General-purpose LSM Learning Processor on FPGA 16          | 7 |

| 6.1.3 A Parallel Digital Neuromorphic Processor with STDP Learn- |   |

| ing Rule                                                         | 8 |

| 6.1.4 Architectural Exploration of Digital Neuromorphic Proces-  |   |

| sor with Memristive Synaptic Array                               |   |

| 6.2 Future Work                                                  | 9 |

| REFERENCES                                                       | 1 |

# LIST OF FIGURES

# FIGURE

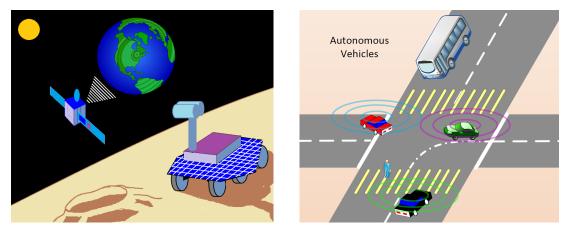

| 1.1  | The scenarios, in which the devices may not be continuously con-<br>nected to the network, require edge computing which can enable<br>analytics and knowledge generation to occur at the source of the data.              | 3  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

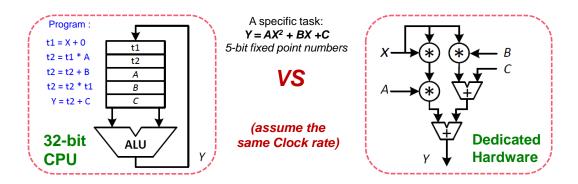

| 1.2  | Comparison of a 32-bit general purpose CPU and a dedicated hard-<br>ware design for a specific task.                                                                                                                      | 4  |

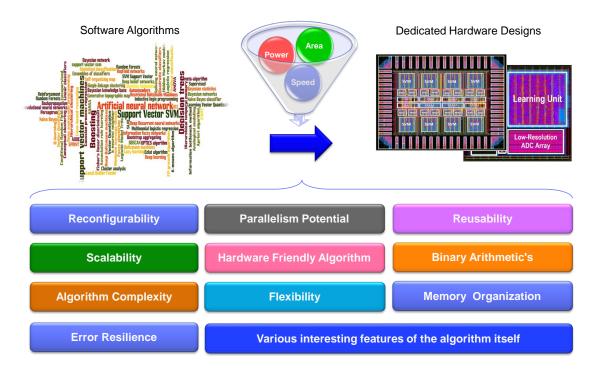

| 1.3  | The critical considerations when mapping a complex software al-<br>gorithm to a dedicated hardware design                                                                                                                 | 5  |

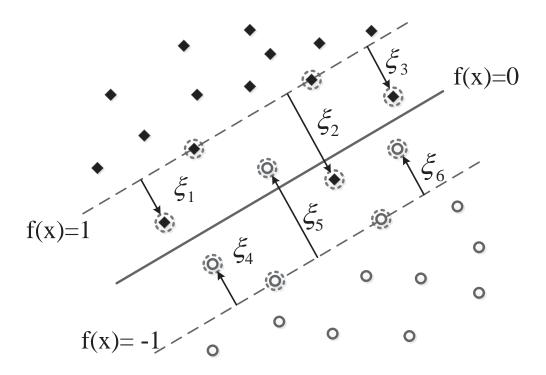

| 2.1  | Soft margin SVM with all support vectors highlighted by dashed circles. ©IEEE 2014                                                                                                                                        | 18 |

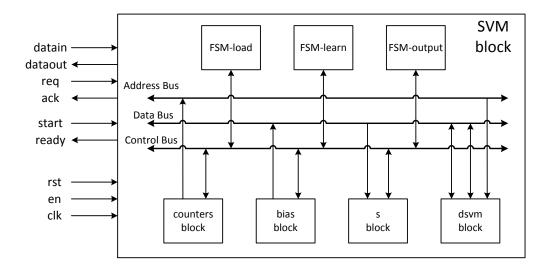

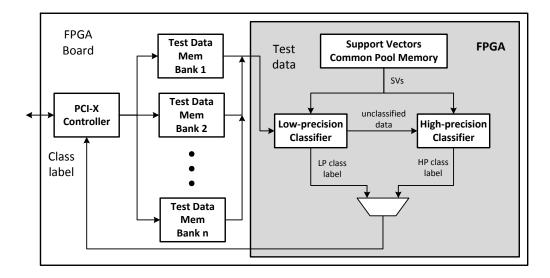

| 2.2  | Overall digital SVM architecture presented in [17]                                                                                                                                                                        | 21 |

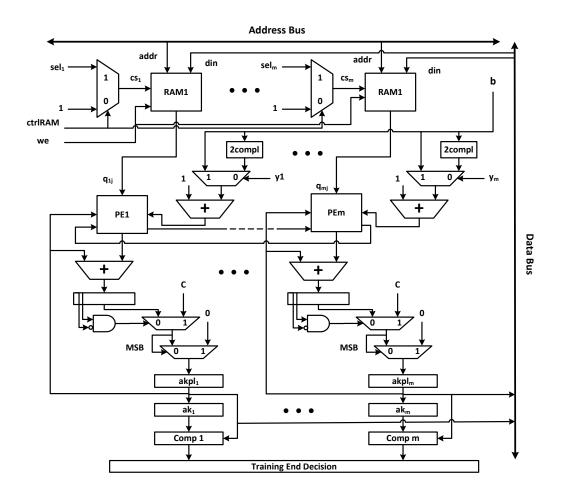

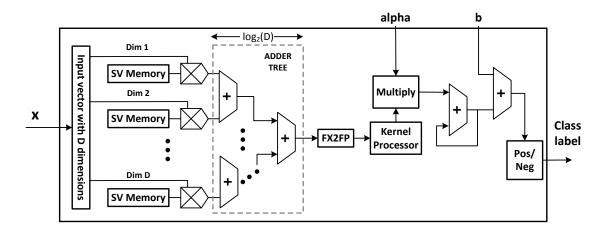

| 2.3  | The implementation of the dsvm block                                                                                                                                                                                      | 22 |

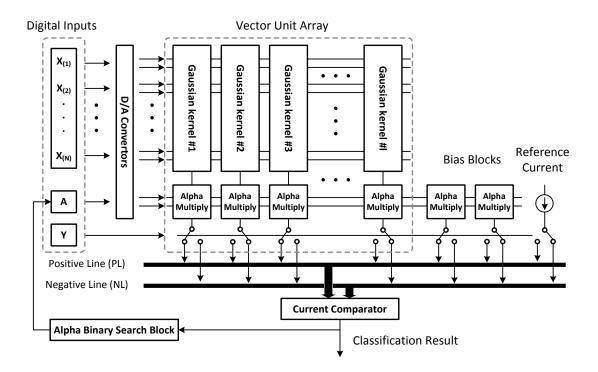

| 2.4  | Overall block diagram of the analog SVM architecture in [20]                                                                                                                                                              | 23 |

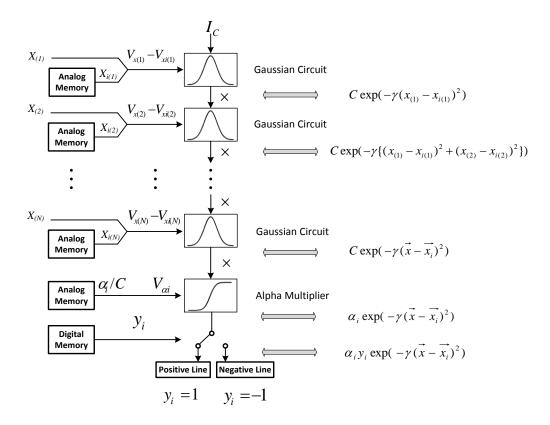

| 2.5  | The block diagram of a single vector unit. The input current $I_C$ represents the regularization parameter $C$ . The Gaussian and exponential functions are realized by MOS circuits working in the sub-threshold region. | 24 |

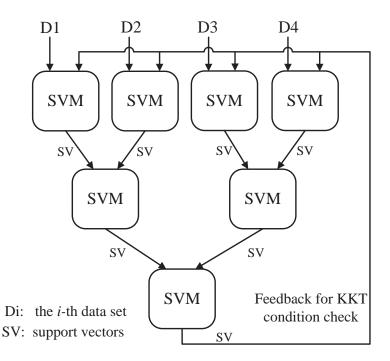

| 2.6  | The cascade SVM classifier proposed by [19].                                                                                                                                                                              | 26 |

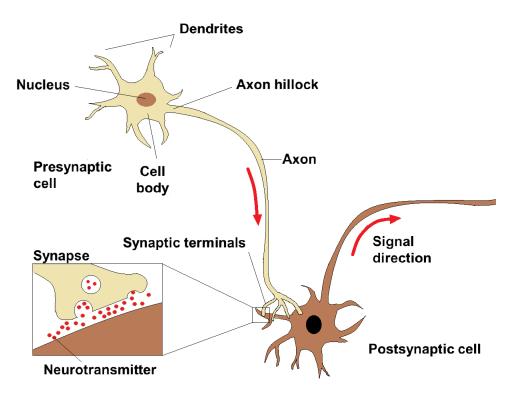

| 2.7  | Biological neuron anatomy [59]                                                                                                                                                                                            | 30 |

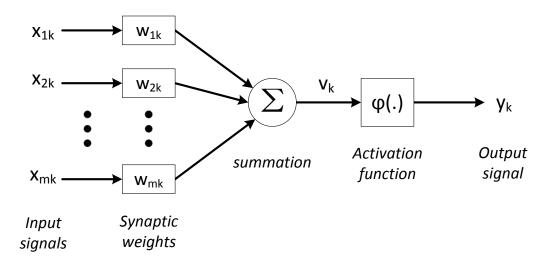

| 2.8  | Artificial neuron model. The input signals are first multiplied with<br>the corresponding synaptic weights. Then the summation of these<br>products is converted to the output signal by an activation function.          | 33 |

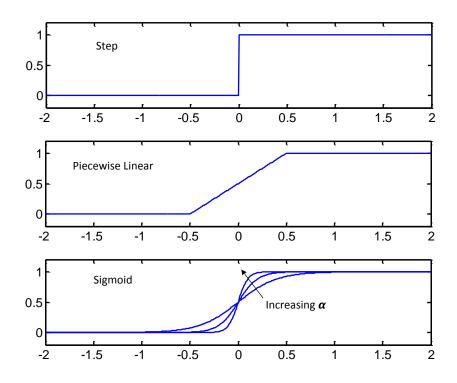

| 2.9  | Popular activation functions used in artificial neuron models                                                                                                                                                             | 34 |

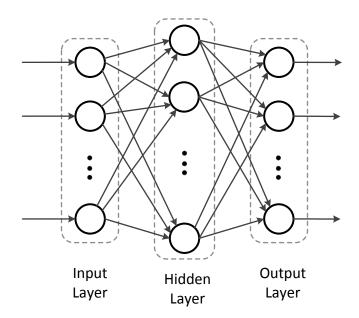

| 2.10 | ) Feedforward artificial neural network architecture                                                                                                                                                                      | 36 |

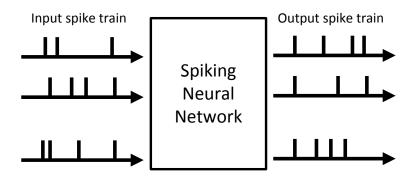

| 2.11 | Overview of the spiking neural network.                                                                                                                                                                                   | 38 |

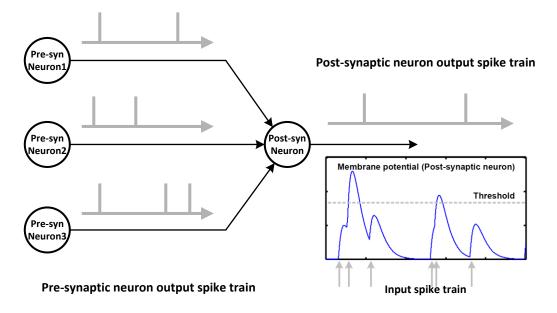

| 2.12 | Behavior of the spiking neural network.                                                                                                                                                                                                                                                                                                                                                                                             | 39 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

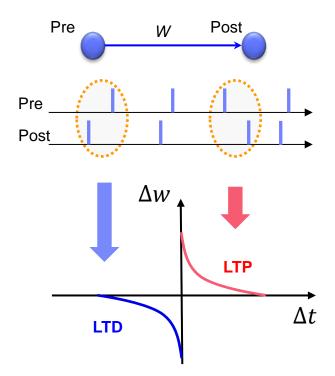

| 2.13 | Spike timing dependent plasticity.                                                                                                                                                                                                                                                                                                                                                                                                  | 41 |

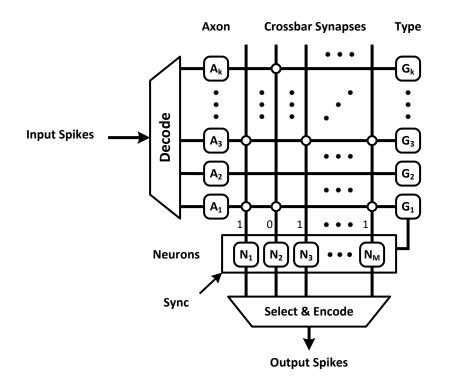

| 2.14 | Block diagram of neuromorphic chip proposed by [46]                                                                                                                                                                                                                                                                                                                                                                                 | 43 |

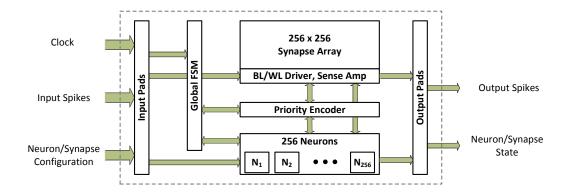

| 2.15 | Block diagram of neuromorphic chip proposed by [47]                                                                                                                                                                                                                                                                                                                                                                                 | 44 |

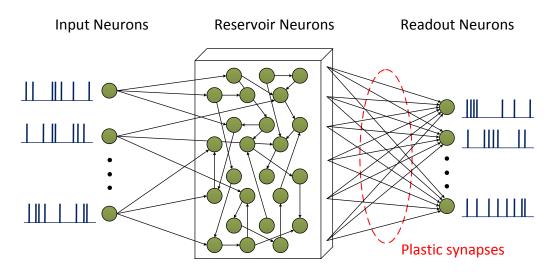

| 2.16 | The structure of a typical LSM. ©IEEE 2015                                                                                                                                                                                                                                                                                                                                                                                          | 45 |

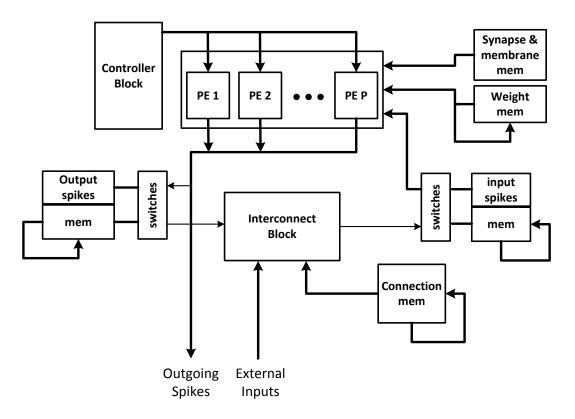

| 2.17 | Block diagram of the neuromorphic architecture in [37]. PE represents the Processing Element.                                                                                                                                                                                                                                                                                                                                       | 46 |

| 2.18 | Block diagram of the neuromorphic architecture in [38]. PE represents the Processing Element.                                                                                                                                                                                                                                                                                                                                       | 48 |

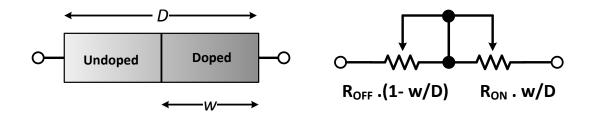

| 2.19 | Memristive device structure (left) and variable resistance model (right)                                                                                                                                                                                                                                                                                                                                                            | 50 |

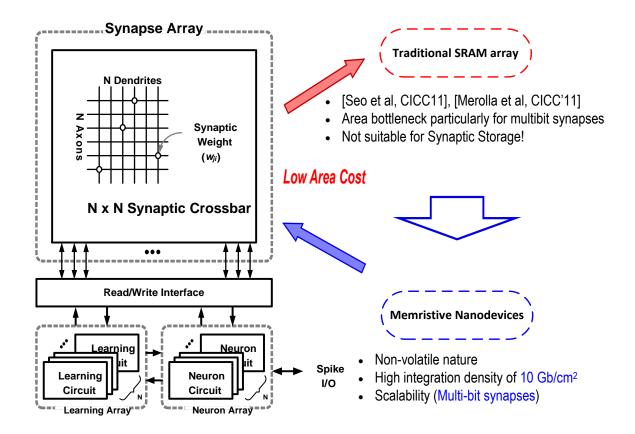

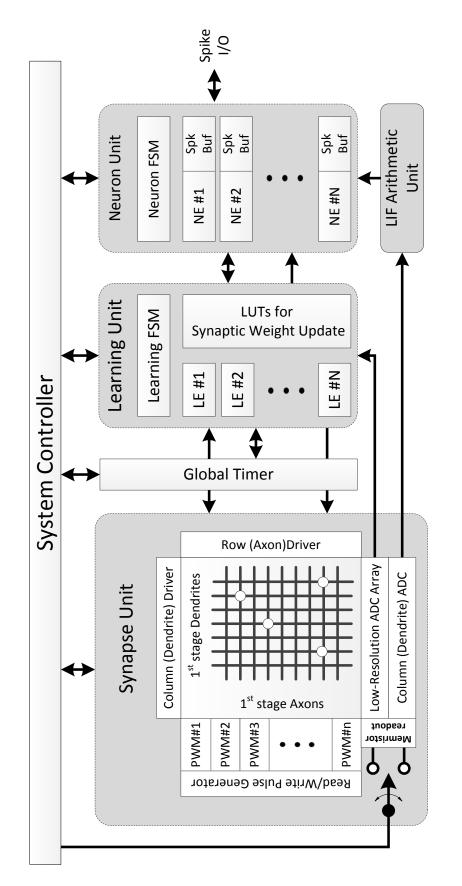

| 2.20 | Block diagram of neuromorphic chip with memristor crossbar array.                                                                                                                                                                                                                                                                                                                                                                   | 52 |

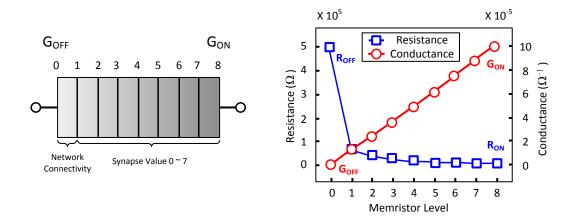

| 2.21 | Memristor level partitions by equal conductance                                                                                                                                                                                                                                                                                                                                                                                     | 53 |

| 2.22 | Block diagram of neuromorphic chip with memristor crossbar array.                                                                                                                                                                                                                                                                                                                                                                   | 54 |

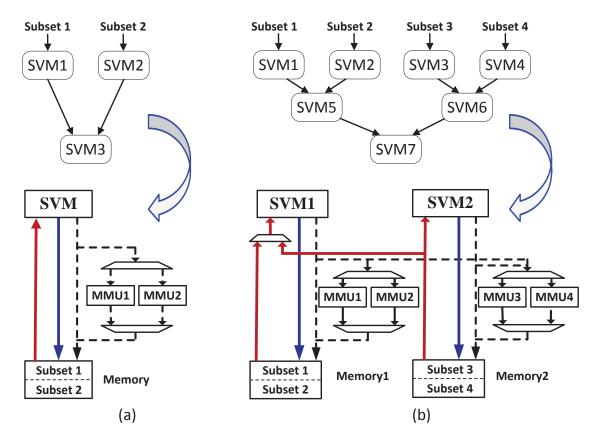

| 3.1  | Schematic of a binary Cascade SVM. The whole data set is split into smaller subsets and each one is fed as the inputs to the SVMs in the first layer. Then the results (support vectors) will be combined two by two and fed as the inputs to the following layers. The SVMs can be seen as filters which extract support vectors from the input data set. A feedback path is added to guarantee the global convergence. ©IEEE 2015 | 56 |

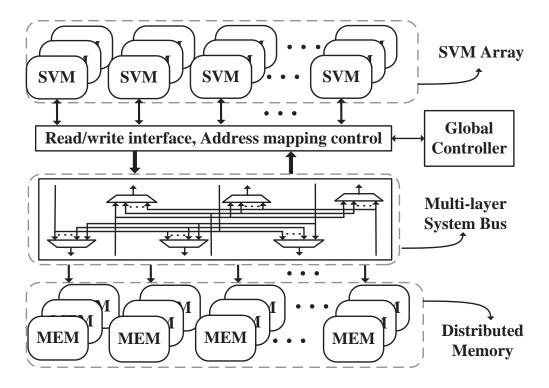

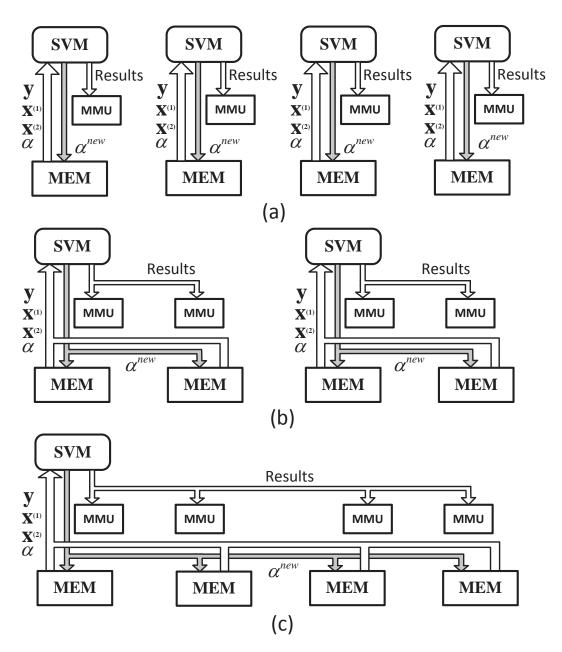

| 3.2  | The proposed architecture of cascade SVM.©IEEE 2015                                                                                                                                                                                                                                                                                                                                                                                 | 59 |

| 3.3  | An example of SVM processing unit reuse for cascade SVM and the corresponding data flow diagram. (a)-(c) correspond to the training of different layers in the 3-layer cascade tree in Fig. 3.1, respectively. ©IEEE 2015                                                                                                                                                                                                           | 61 |

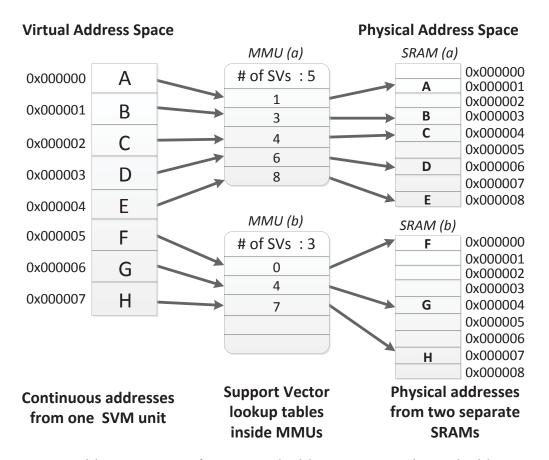

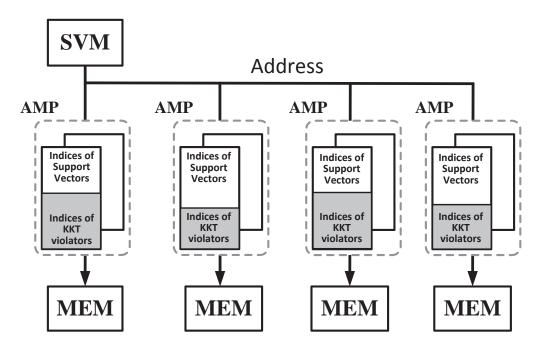

| 3.4  | Address mapping from virtual address space to physical address space with MMUs. ©IEEE 2015                                                                                                                                                                                                                                                                                                                                          | 63 |

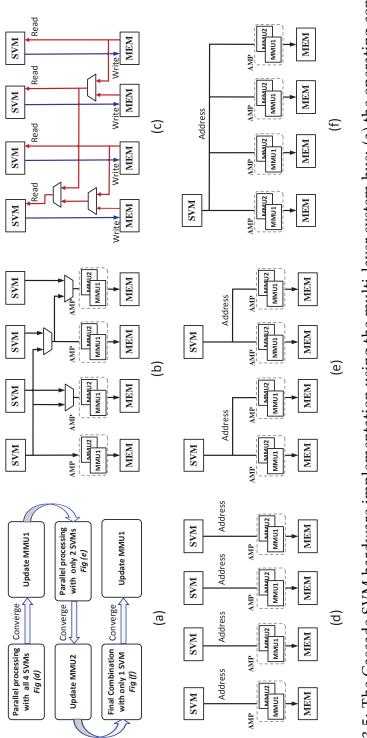

| 3.5  | The Cascade SVM hardware implementation using the multi-layer system bus: (a) the operating control flow for a 4-SVM design, (b) the address bus, (c) the data buses for read and write, respectively, (d)-(f) the configurations of the address bus for different layers. ©IEEE 2015                                                                                               | 64 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

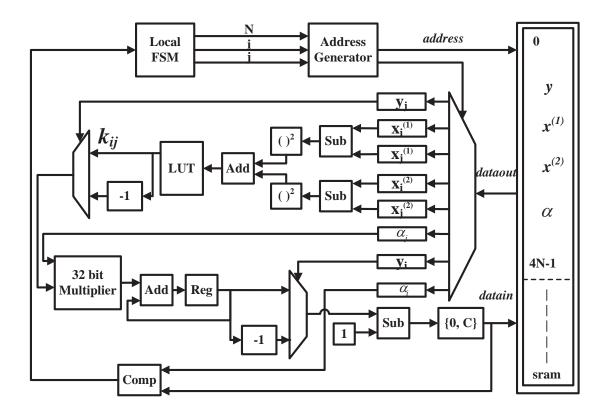

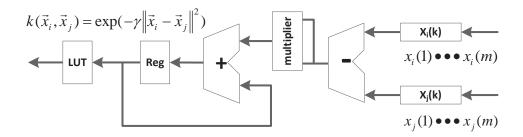

| 3.6  | The proposed flexible SVM processing unit with three 32-bit fixed-<br>point multipliers and one Gaussian function lookup table. ©IEEE<br>2015                                                                                                                                                                                                                                       | 69 |

| 3.7  | Mapping the Cascade SVM algorithm to the temporal reuse design<br>and hybrid design: (a) temporal reuse of one SVM unit, (b) the hy-<br>brid design which involves both parallel processing and temporal<br>reuse. The dashed lines correspond to the address bus. ©IEEE 2015                                                                                                       | 72 |

| 3.8  | The process of KKT checking for global convergence. The addresses of the training results from the previous iteration is stored in the MMU1s or MMU2s. When one pass through the cascade is completed, an SVM processing unit tests each sample for KKT violators based on equations (3.6). The physical addresses of the KKT violators are then saved in the same MMUs. ©IEEE 2015 | 75 |

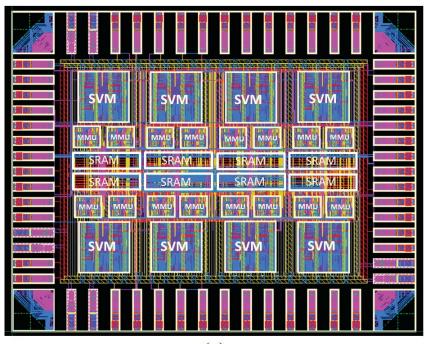

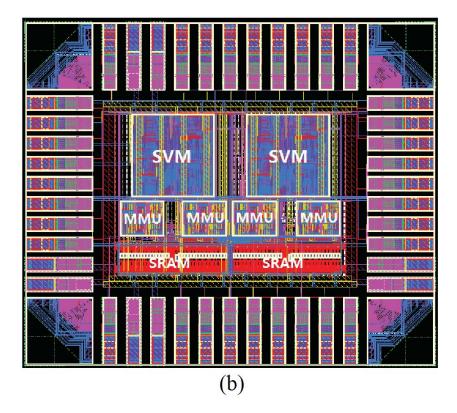

| 3.9  | Layouts of the 8-core SVM design and the hybrid design.©IEEE 2015                                                                                                                                                                                                                                                                                                                   | 78 |

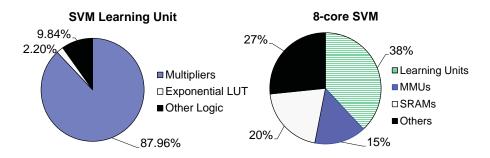

| 3.10 | Area breakdown analysis for two implementations: (left) single SVM unit, and (right) fully parallel 8-core SVM.©IEEE 2015                                                                                                                                                                                                                                                           | 79 |

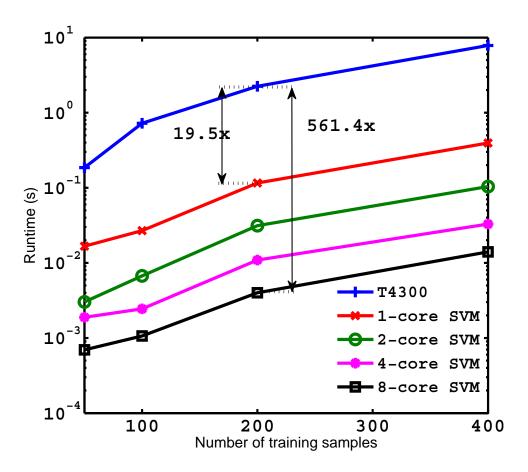

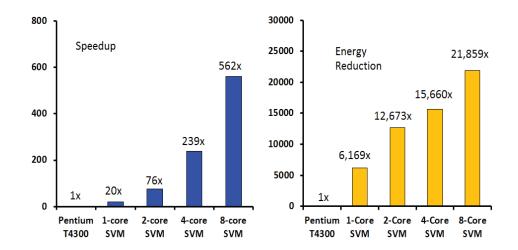

| 3.11 | Comparison of the runtime speedups of the proposed cascade SVM designs. The SVM processing units in the multi-core designs run fully in parallel. ©IEEE 2015                                                                                                                                                                                                                        | 81 |

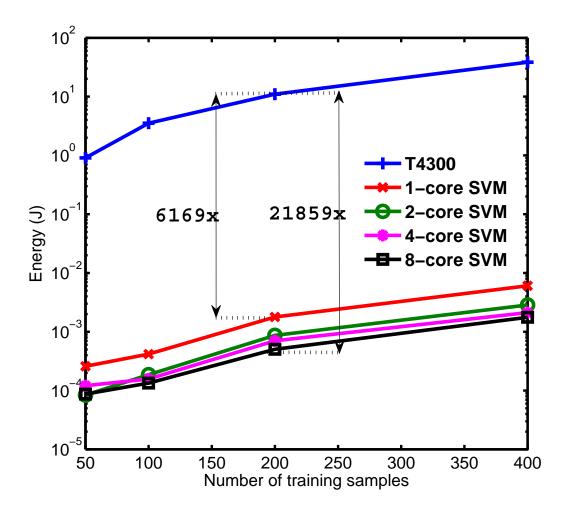

| 3.12 | Comparison of the energy reduction of the proposed cascade SVM designs. The SVM processing units in the multi-core designs run fully in parallel. ©IEEE 2015                                                                                                                                                                                                                        | 83 |

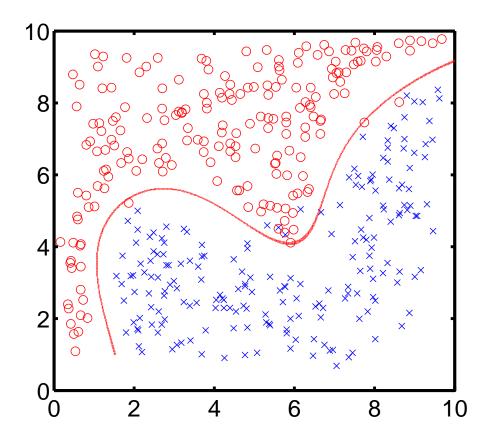

| 3.13 | The decision boundary obtained from the fully parallel 8-Core hard-<br>ware design of Cascade SVM. The training set involves 400 2-D<br>samples. ©IEEE 2015                                                                                                                                                                                                                         | 85 |

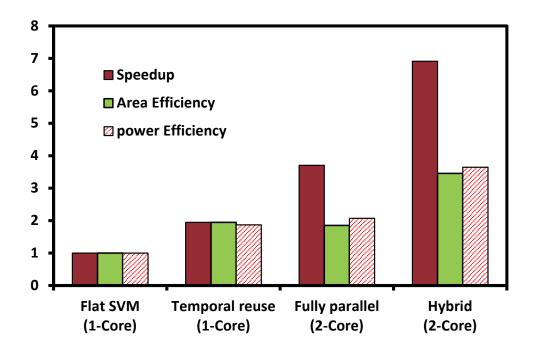

| 3.14 | Comparison between temporal reuse, full parallel, hybrid design<br>and the flat SVM in terms of speedup, area efficiency and power<br>efficiency. ©IEEE 2015                                                                                                                                                                                                                        | 87 |

| 3.15 | The proposed kernel arithmetic logic unit which supports the data set of any dimensions. ©IEEE 2015                                                                                                                                                                                                                            | 39 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.16 | Comparison of the runtime and energy consumption. Left: train-<br>ing runtime speedups. Right: energy reduction of the proposed<br>cascade SVM design. SVM units in the multicore designs run fully<br>in parallel. ©IEEE 2014                                                                                                 | 91 |

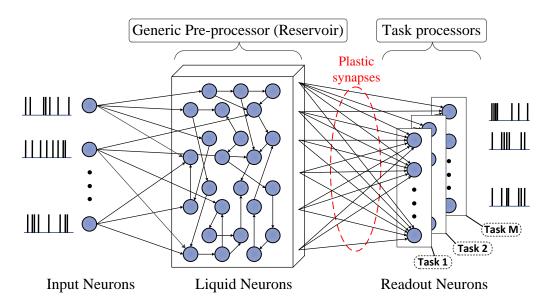

| 4.1  | A liquid state machine supporting multiple tasks. ©IEEE 2015 9                                                                                                                                                                                                                                                                 | 94 |

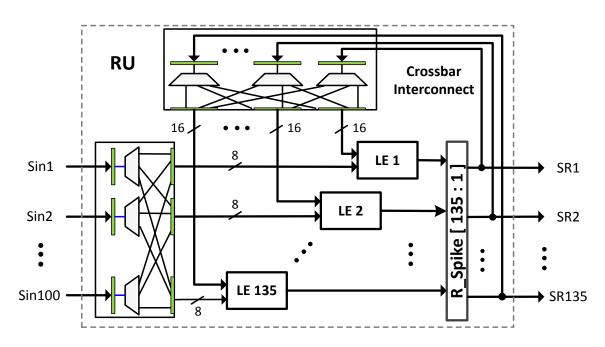

| 4.2  | An exemplary reservoir implementation with 135 digital liquid neurons. In this example, each liquid element (LE) receives up to 8 external input spikes and up to 16 internal spikes. ©IEEE 2015 9                                                                                                                             | 95 |

| 4.3  | An exemplary readout stage with 26 digital output neurons. In this example, each output element (OE) receives all 135 spike trains from the RU. The address space of a BRAM is split into multiple regions for different tasks. <i>W</i> represents the synaptic weight. ©IEEE 2015                                            | 97 |

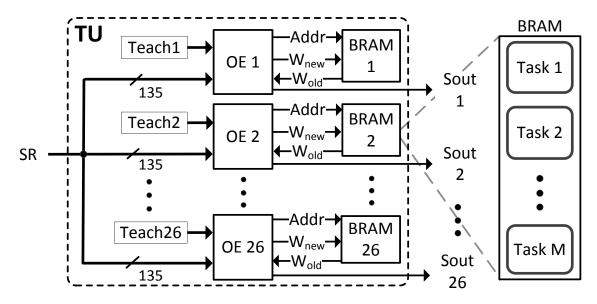

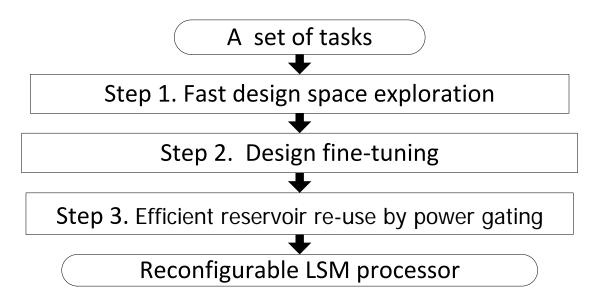

| 4.4  | (a) the digital neuron. The shaded blocks only exist in OE. (b) the implementation of SRU based on (4.3). PISO (Parallel-in and Serial-out) is realized by a shift register. ©IEEE 2015                                                                                                                                        | 99 |

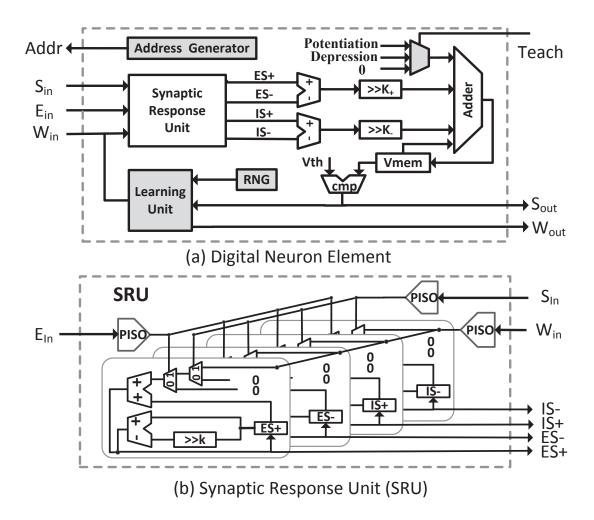

| 4.5  | Illustration of the proposed design methodology. ©IEEE 2015 10                                                                                                                                                                                                                                                                 | )0 |

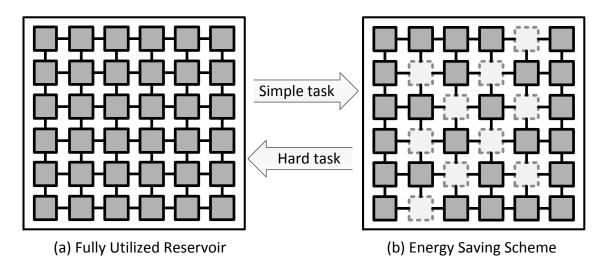

| 4.6  | (a) The full-load operating mode in which the RU is fully utilized for "hard tasks". (2) The light (energy saving) mode in which certain liquid neurons are powered off for "simple tasks". ©IEEE 2015 10                                                                                                                      | )2 |

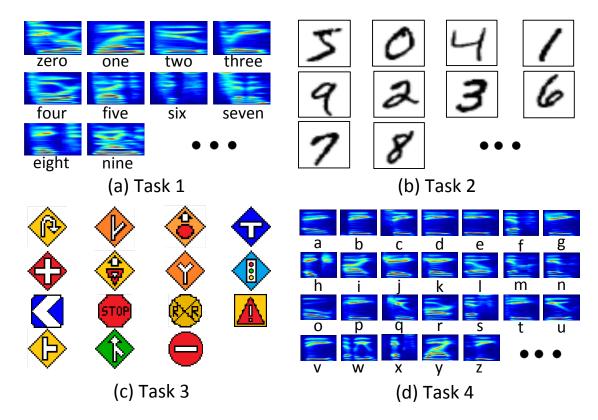

| 4.7  | Benchmarks: (a) speech samples of 10 digits. (b) handwritten dig-<br>its. (c) images of 15 traffic signs. (d) speech samples of 26 letters.<br>©IEEE 2015                                                                                                                                                                      | )3 |

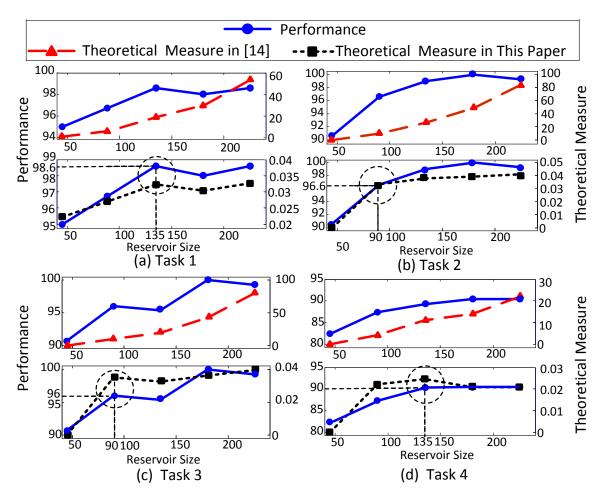

| 4.8  | Comparison between two theoretical measures in terms of their cor-<br>relation with recognition performance of the different tasks. The<br>saturation points of the proposed measure are highlighted with<br>dashed circles, corresponding to the predicted reservoir sizes in<br>Step 1 of the design methodology. ©IEEE 2015 | 05 |

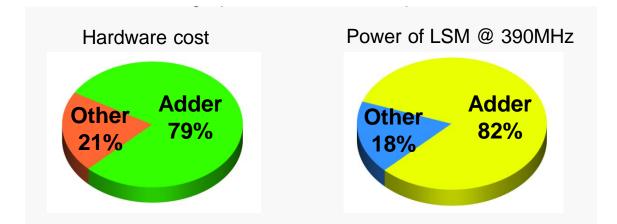

| 4.9  | Area/Power breakdown of the hardware LSM, which demonstrates the digital adders make a large portion in terms of both hardware cost and power consumption.                                                                                                                                                                     | )8 |

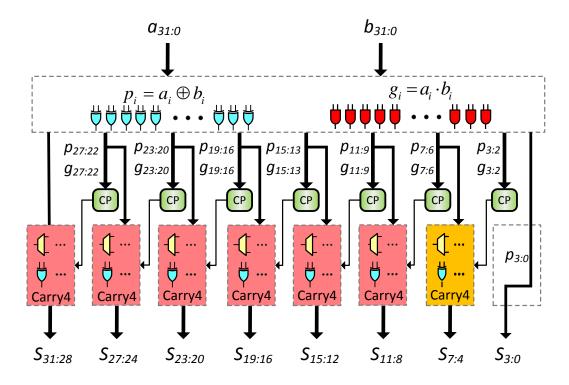

| 4.10 | In addition to $p_i$ , the proposed approximate adder also realizes $g_i$ .<br>The carry-in of each subadder is generated by a simple logic called<br>Carry Prediction (CP) and is based on both $p$ signals and $g$ signals.                                                            | 110 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.11 | Each Carry4 block is made of 4 multiplexers and 4 XOR gates. It receives $p$ , $a$ and $c_{in}$ from the other logics in Fig. 4.10, which are realized by LUTs                                                                                                                           | 111 |

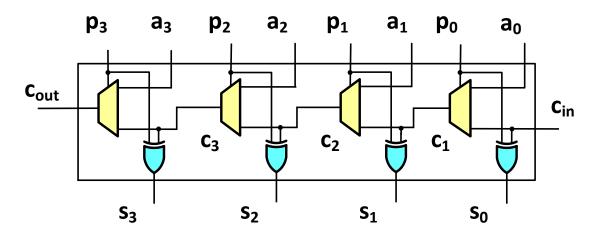

| 4.12 | Energy consumption and recognition rates of different designs. The percentage energy reductions of the proposed technique are same as the percentage power reductions of Table 4.6 as the execution times of all designs are the same.                                                   | 114 |

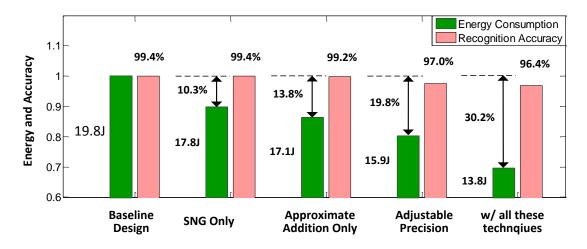

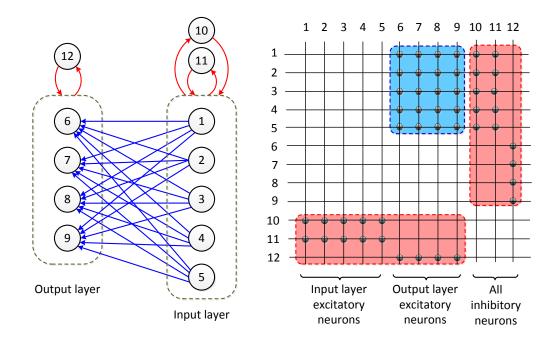

| 4.13 | The neurons labeled 1-784 are the excitatory neurons in the input<br>layer, while the neurons labeled 785-1584 are the excitatory neu-<br>rons in the output layer. The other neurons are the inhibitory neu-<br>rons                                                                    | 116 |

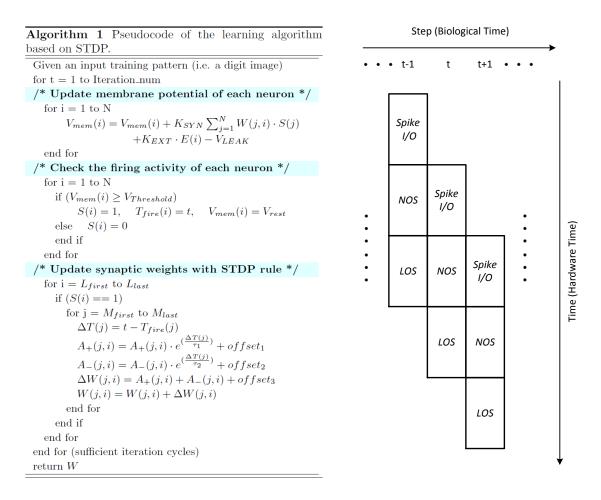

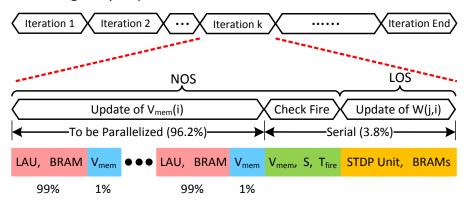

| 4.14 | Pseudocode of the learning algorithm based on STDP (left). Flow diagram of the digital neuromorphic processor (right). NOS represents the neuron operation stage and LOS represents the learning operation stage. The LOS is necessary for training, but not required for recognition.   | 117 |

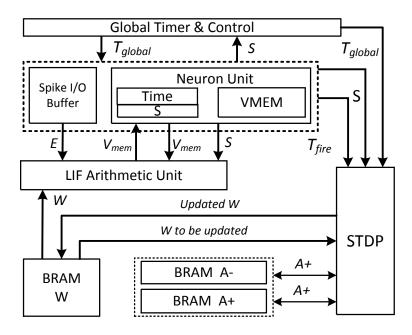

| 4.15 | The block diagram of the serial baseline architecture without paral-<br>lel computing. The synaptic weights $W$ 's are stored in a single-port<br>block RAM, and the synaptic parameters $A$ + and $A$ - are stored in<br>another two block RAMs                                         | 119 |

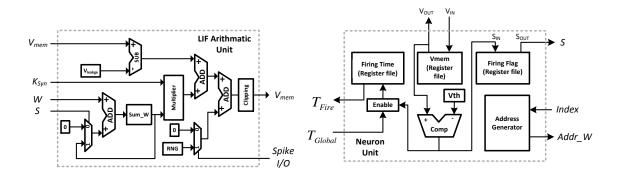

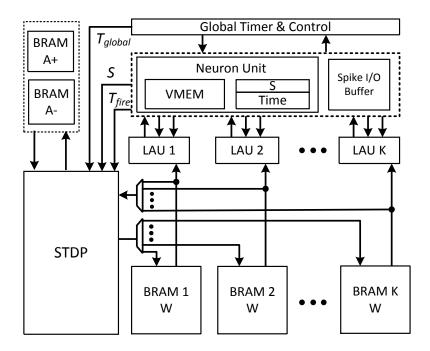

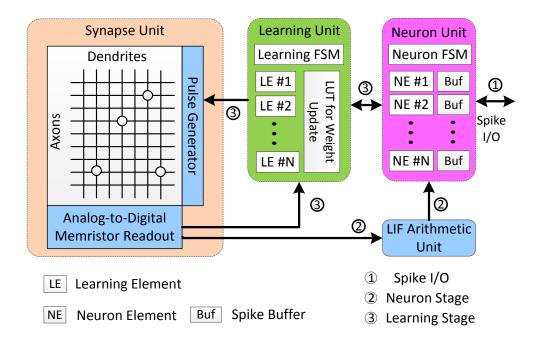

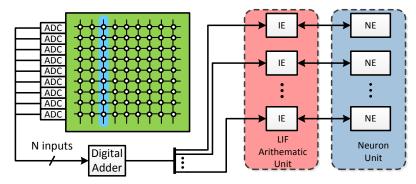

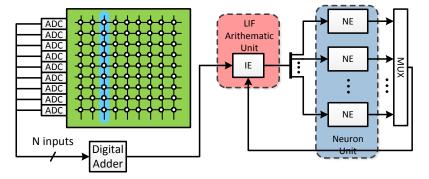

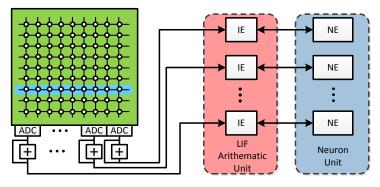

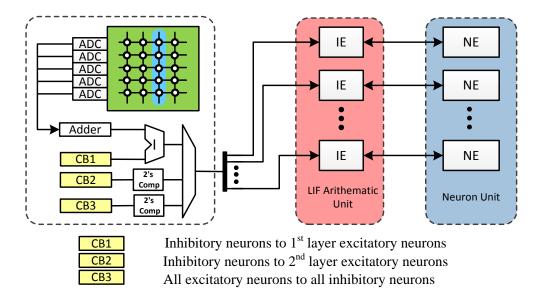

| 4.16 | The proposed LIF Arithmetic Unit (LAU) and Neuron Unit (NU).<br>LAU is used to update the membrane potentials of all the neurons.<br>NU is used to store the membrane potential, firing time and firing<br>activity flag of each neuron. The synaptic weights are stored in the<br>BRAM. | 120 |

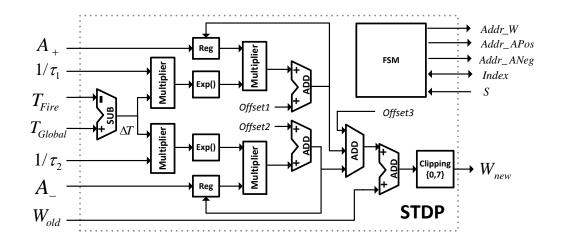

| 4.17 | The proposed STDP unit which is used to update the synaptic weights $T_{fire}$ and $S$ are obtained from the neuron unit. $W$ , $A_+$ and $A$ are from the BRAMs.                                                                                                                        |     |

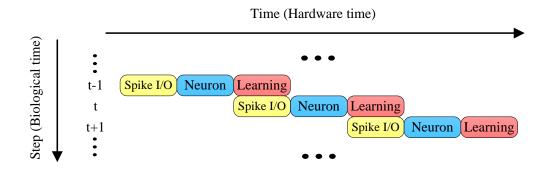

| 4.1 | 8 The detailed timing diagram of the baseline design. A large num-<br>ber of biological time steps need to be processed for a single input<br>pattern (i.e. a handwriting digit image) in the training phase. Each<br>iteration is divided into NOS and LOS. The updating of membrane<br>potentials during NOS is parallelized, which consumes 96.2% of<br>the total runtime. | . 123 |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

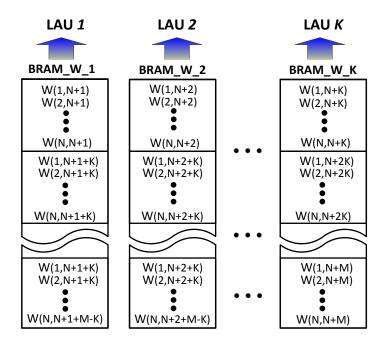

| 4.1 | 9 Parallel processing schemes for N excitatory neurons in the input<br>layer and M excitatory neurons in the output layer: simultaneous<br>updates of K membrane potentials with synaptic weights stored in<br>K parallel block RAMs.                                                                                                                                         | . 124 |

| 4.2 | 0 The proposed parallel neuromorphic processor which develops <i>K</i> -way parallel processing based on LIP. <i>K</i> block RAMs are used to store synaptic weights, and <i>K</i> LAUs work in parallel to update <i>K</i> membrane potentials at the same time.                                                                                                             | . 125 |

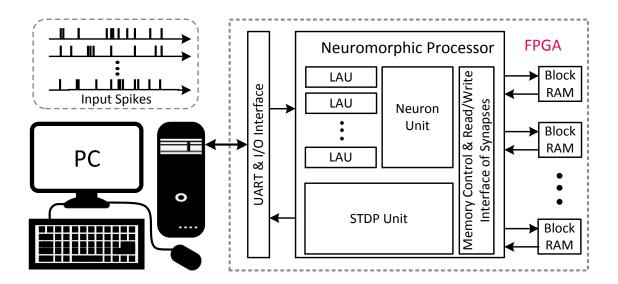

| 4.2 | 1 Top-level schematic of the proposed neuromorphic processor run-<br>ning on Xilinx ML605 evaluation board, with the synaptic weights<br>stored in block RAMs. The communication between PC and FPGA<br>is realized by an UART cable                                                                                                                                          | . 126 |

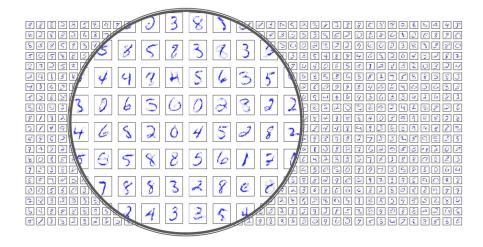

| 4.2 | 2 The 800 receptive fields obtained after the training over 60,000 MNIST images of handwritten digits.                                                                                                                                                                                                                                                                        | . 129 |

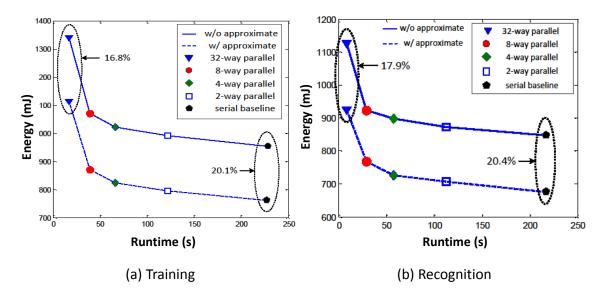

| 4.2 | 3 Comparison of different designs in terms of runtime and energy<br>consumption. The solid curve represents the designs using stan-<br>dard booth multipliers. The dashed curve represents the designs<br>using the approximate multipliers. (a) is for the training mode,<br>while (b) is for the recognition mode                                                           | . 131 |

| 5.1 |                                                                                                                                                                                                                                                                                                                                                                               | . 135 |

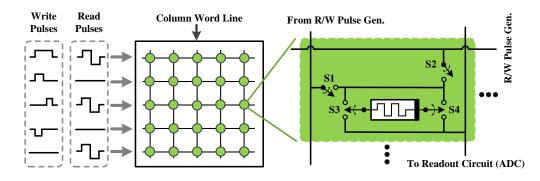

| 5.2 | Proposed synaptic crossbar array and CMOS / memristor hybrid<br>synaptic cell. Parallel voltage pulses are generated by the R/W<br>pulse generator and used for the read and write of all cells in the<br>row (column).                                                                                                                                                       | . 136 |

| 5.3 | Flow diagram of the digital neuromorphic processor                                                                                                                                                                                                                                                                                                                            | . 138 |

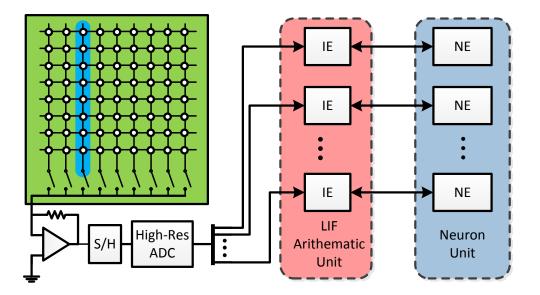

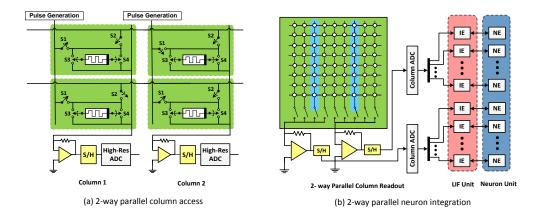

| 5.4  | Different memory access styles for neuron stage: (a) Read out synap-<br>tic weights column by column with $N$ integration elements (IEs);<br>(b) Read out synaptic weights column by column with only one<br>shared IE; (c) Read out synaptic weights row by row with $N$ low<br>resolution ADCs and $N$ accumulators |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

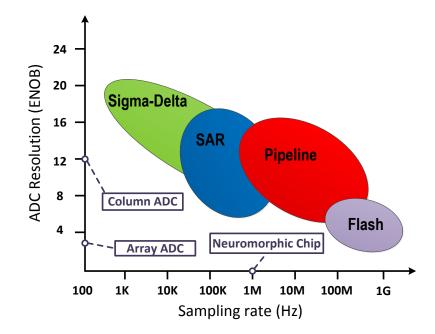

| 5.5  | Comparison of ADC architectures vs. Resolution and Sampling rate. 142                                                                                                                                                                                                                                                 |

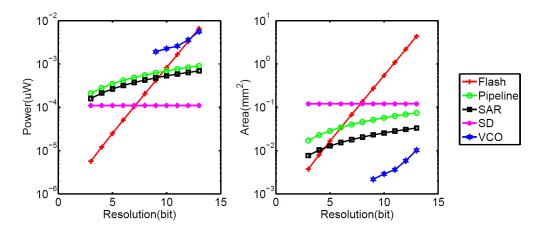

| 5.6  | Power and area for different ADCs of various resolutions                                                                                                                                                                                                                                                              |

| 5.7  | Block diagram of the readout with column ADC                                                                                                                                                                                                                                                                          |

| 5.8  | An example of 2-layer feedforward neural networks and its corresponding crossbar array                                                                                                                                                                                                                                |

| 5.9  | The proposed storage organization optimized for 2-layer feedfor-<br>ward neural network. The constant blocks CB1, CB2 and CB3 are<br>actually constants integrated into the digital design                                                                                                                            |

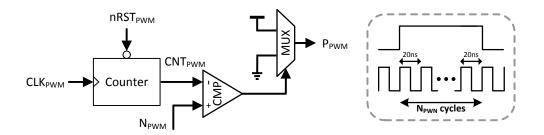

| 5.10 | Digital pulse width modulator: $CLK_{PWM}$ is the 50MHz clock signal for the pulse generator. $N_{PWM}$ is the desired number of clock cycles, which is compared to the output of the counter. The multiplexer outputs the pulse with duration of $N_{PWM}$ clock cycles 151                                          |

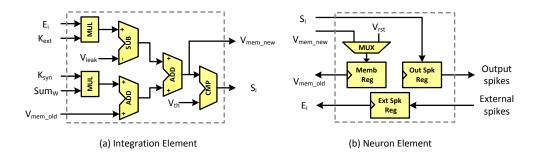

| 5.11 | Data flow of the Integration Element (IE) and the Neuron Element (NE). The signal $SumW$ corresponds to the term $\sum_{j=1}^{M} w_{ji} \cdot S_j[t-1]$ in (5.1), which is calculated by the readout circuits of the Synapse Unit                                                                                     |

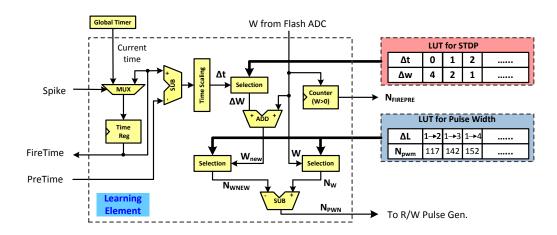

| 5.12 | Data flow of the Learning element (LE). Lookup tables (LUTs) are<br>used to calculate $\Delta W$ based on STDP learning rule. Signal $N_{PWN}$<br>controls the pulse generator to generate the required pulse widths 152                                                                                              |

| 5.13 | Parallel processing with 2 column ADCs: (a) the detailed connec-<br>tion between memristor cells and pulse generators; (b) the simulta-<br>neous access of 2 columns in a design with N digital neurons. Each<br>column ADC accesses N/2 columns sequentially. Two Vmems can<br>be calculated simultaneously          |

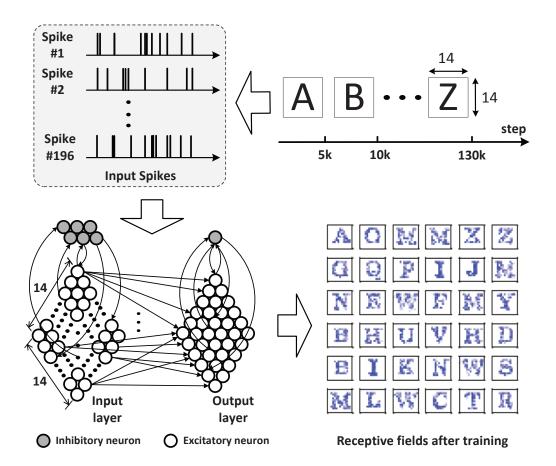

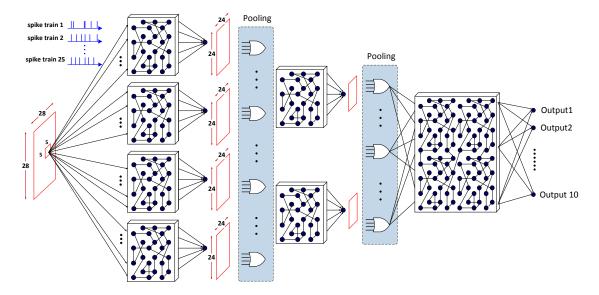

| 5.14 | The 2-layer neural network designed for character recognition and the corresponding learning result. Each pixel input pattern is converted into $14 \times 14$ spike inputs to the input layer of the network 159                                                                                                     |

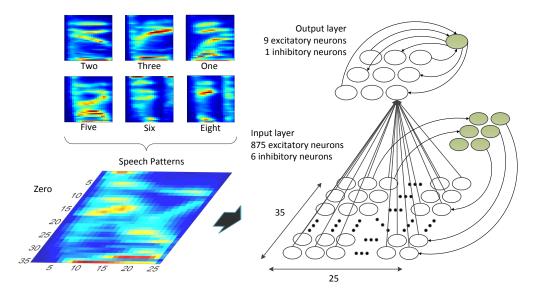

| 5.15 | The 2-layer neural network designed for speech recognition. Each speech pattern is converted into 25x35 spike inputs to the input layer of the network.                                                                                             | . 161 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

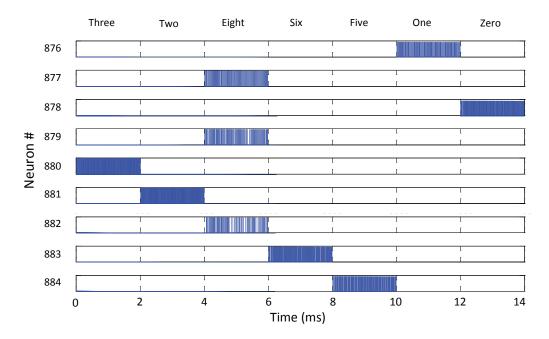

| 5.16 | The spiking events emitted by the output neurons (with neuron index from 876 to 884) as a function of time after training. Each neuron only responds to one particular speech pattern and shows high firing frequency for this speech pattern.      | . 162 |

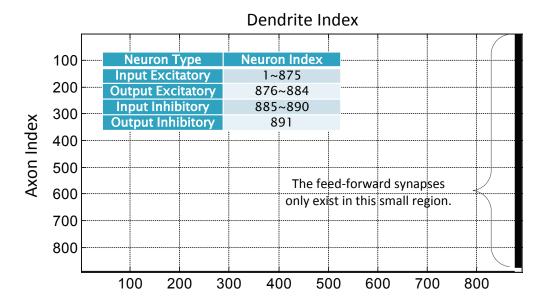

| 5.17 | The synapse distribution of the conceptual 891x891 synaptic array.<br>Since there are only 9 excitatory neurons in the output layer and<br>875 excitatory neurons in the input layer, the feedforward synapses<br>only exist in a very small region | . 164 |

| 6.1  | Block diagram of the a deep spiking neural network architecture                                                                                                                                                                                     | . 170 |

# LIST OF TABLES

| TABLE |                                                                                                                                                                                                           | Pa  | ige |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|

| 3.1   | Pseudocode of the hardware-friendly gradient-ascent algorithm for SVM training.                                                                                                                           |     | 69  |

| 3.2   | Comparison of runtimes of different cascade SVM structures with different C values. The dataset involves 400 samples                                                                                      |     | 71  |

| 3.3   | Comparison of 4 full parallel SVM designs and the software SVM solution on T4300 in terms of runtime for different data sets                                                                              |     | 80  |

| 3.4   | Comparison of 4 fully parallel hardware designs and the software SVM solution on Intel T4300 in terms of power, area, speedup and energy reduction for the data set with 200 points                       |     | 82  |

| 3.5   | The effect of feedback on training accuracies for the data set with 400 samples.                                                                                                                          | •   | 84  |

| 3.6   | Comparison of two fully parallel designs and their temporal reuse version in terms of area, power and runtime                                                                                             |     | 86  |

| 3.7   | Comparison of the classification time for a test data set with 800 samples. The 4 classifiers are obtained from the training over 4 different training sets with 50,100,200 and 400 samples, respectively | y.  | 88  |

| 3.8   | Comparison of power, area and runtime of the designs using the above kernel computation unit. The training set Cod-RNA involves 59,532 8-D samples.                                                       |     | 90  |

| 4.1   | The comparison of the 4 tasks in terms of the runtime, the desired reservoir size and the recognition accuracy.                                                                                           | . 1 | 06  |

| 4.2   | The comparison between the RU and the TU in terms of hardware cost and power consumption. The RU involves 135 liquid neurons and the TU involves 26 readout neurons.                                      | . 1 | 06  |

| 4.3   | Comparison of 3 multitask LSM designs in terms of hardware cost and total energy consumption for all the 4 tasks.                                                                                         | . 1 | 07  |

| 4.4 | Comparison between the Xilinx built-in adder and the proposed<br>approximate adder in terms of delay, hardware cost and power con-<br>sumption. The operands are 32-bit fixed point numbers                                                              |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.5 | Comparison of processors using Xilinx built-in adders vs. approximate adders in RU in terms of hardware cost.                                                                                                                                            |

| 4.6 | Effects of the proposed low-power design techniques on the average power over 50 training iterations and the recognition rate                                                                                                                            |

| 4.7 | Power and resource utilization of the building block components<br>of the baseline architecture, which accumulates the pre-synaptic<br>weights serially for each output layer neuron. All the neurons are<br>processed one by one in a sequential manner |

| 5.1 | Coefficients in power modeling function                                                                                                                                                                                                                  |

| 5.2 | The power consumptions of memristor crossbar arrays in different designs as functions of the size of the arrays. The application specific architectures only store the feedforward synapses in the memristor crossbar array                              |

| 5.3 | Power and area of the baseline components. NU and LU represent neuron stage and learning stage, respectively                                                                                                                                             |

| 5.4 | Fully reconfigurable designs using 256 x 256 memristor array as synapse storage, which can support any network topology involving 256 neurons. Comparison of different architectures in terms of energy, area and enery-area product (EAP)               |

| 5.5 | Application specific designs which store only feed-forward synapses<br>in the memristor array. Comparison of different architectures in<br>terms of energy, area and enery-area product(EAP). All designs are<br>based on the non-shared IE scheme       |

| 5.6 | Power and area of the baseline components. NU and LU repre-<br>sent neuron stage and learning stage, respectively. Since there are<br>891 neurons in this network, the resolution of the column ADC is<br>changed to 13 bits                             |

| 5.7 | Fully reconfigurable designs using 891x891 memristor array for synapse storage. Comparison of different architectures in terms of energy, area and enery-area product (EAP). All designs are based on the non-shared IE scheme                           |

#### 1. INTRODUCTION\*

In this era of big data, IT technology development and scientific research are becoming increasingly data-intensive in recent years [1] [2]. For example, bioinformatics researchers often need to process tens of billions points of data to acquire new insights of diseases and develop diagnostics and therapeutics. Processing such large data can take a huge amount of CPU times (e.g., several weeks or even months) [3]. As another example, to address some of the key problems of astrophysics and cosmology, square kilometer array, the world's quickest radio telescope located in Australia, is collecting up to 30-360 TB of data per day, which requires extremely powerful computational resources [4]. Therefore, time and energy efficient processing of large data is of key importance. Extracting patterns and classifiers from a set of data and using them to interpret the existing data and predict new data information are usually achieved by applying machine learning and data mining techniques. Building embedded machine learning intelligent into silicon can also enable a wide range of low-power smart sensors.

Basically, machine learning techniques enable a computer system or a program to learn from the past experiences to improve the performance of a certain task. Various machine learning techniques have been developed nowadays, and they are widely applied to many aspects of humans life. For example, machine learn-

<sup>\*© 2015</sup> IEEE. Reprinted, with permission, from Q. Wang P. Li Y. Kim A Parallel Digital VLSI Architecture for Integrated Support Vector Machine Training and Classification, Very Large Scale Integration (VLSI) Systems, IEEE Transactions on 23.8 (2015): 1471-1484.

<sup>© 2014</sup> IEEE. Reprinted, with permission, from Q. Wang, Y. Kim, and P. Li. Architectural design exploration for neuromorphic processors with memristive synapses. Nanotechnology (IEEE-NANO), 2014 IEEE 14th International Conference on. IEEE, 2014.

<sup>© 2015</sup> IEEE. Reprinted, with permission, from Q. Wang, Y. Jin and P. Li. General-purpose LSM learning processor architecture and theoretically guided design space exploration. In Biomedical Circuits and Systems Conference (BioCAS), 2015 IEEE (pp. 1-4). IEEE.

ing techniques allow us to integrate human expertise into Artificial Intelligence Systems (AISs). Therefore, the NASA robots such as the Mars Rovers are able to navigate themselves on another planet and even make simple decisions without the help from human [5]. Also, the computer system is enabled to recognize and understand our handwriting and vocal voice. Meanwhile, machine learning techniques can help us to extract some hidden information from complex large data sets. Take social networks as an example. Facebook is using machine learning techniques to help the users to group and categorize their connections, and also detect malicious social activities such as frauds and spams.

Cloud computing provides a good solution for big data processing [6]. In many cases, the data can be transmitted to the cloud and the machine learning is performed by the powerful data centers which might be thousands of miles away from the source of the data. However, there are also many scenarios which have to involve computational power on the edge, as illustrated by Fig. 1.1. For example, the round-trip communication delay between Earth and Mars ranges from 8 to 42 minutes, and the network connection is only available several times during a Martian solar day, due to the movement of both planets [7]. In addition, the data transmission and communication are also important concerns for the autonomous vehicles in the near future. Both of these two scenarios can not reply on the data centers in the distant parts of the world. Therefore, efficient machine learning on the edge is essential for such applications.

However, as the applications becomes more complex and data-intensive, the concerns about data processing speed and energy consumption are becoming increasingly critical. Nowadays, most machine learning tasks are handled by corresponding software programs running on general-purpose processors. Such approaches usually requires a huge amount of CPU time to complete the machine

(a) Artificial Intelligent Mars rover on another planet

(b) Smart traffic system with autonomous vehicles

Figure 1.1: The scenarios, in which the devices may not be continuously connected to the network, require edge computing which can enable analytics and knowledge generation to occur at the source of the data.

learning tasks and results in unbelievably high energy consumption. Take a large human genome as an example, completing the genome sequencing usually requires weeks or months of computation even on a world-class supercomputer. In addition, it is not efficient to run some complex machine learning programs on smart phones or other wearable devices, because not only will it result in a long runtime, but also the battery will run out very fast.

Our solution to these problems, which is also the main focus of this work, is to develop optimized hardware architectures for mainstream machine learning algorithms. As is well known, a dedicated VLSI hardware design is usually much more efficient than the software programs running on general-purpose CPUs, in terms of runtime and energy consumption. This is because unlike a general purpose CPU, a dedicated hardware design is not limited by the instruction set, so only necessary functional blocks for specific tasks are required. Meanwhile, there is no need of instruction memories to store the program codes. This also allows the designers to use flexible arithmetic precisions and operand representations to optimize the design for a particular algorithm. What is more important, the dedicated hardware design allows us to fully exploit hardware parallelism. Fig. 1.2 illustrates the differences between a 32-bit general-purpose CPU and a logic circuit which is optimized for a specific task. In order to compute the value of *Y* based on *X*, *A*, *B* and *C*, a short program with 5 instructions is needed by the 32-bit general-purpose CPU. The program occupies some on-chip storage, and it takes a 32-bit general purpose ALU (Arithmetic Logic Unit), usually a large functional block, about 5 clock cycles to complete the computation. However, if all the operands are 5-bit fixed point numbers, the dedicated hardware design only involves 3 low-resolution multipliers and 2 low-resolution adders to finish the computation in 1 clock cycle. Assuming that the maximum clock rate and the CMOS technology are the same for both, it is quite obvious that the dedicated hardware design is much more efficient than the general purpose CPU in terms of both runtime and hardware cost.

Figure 1.2: Comparison of a 32-bit general purpose CPU and a dedicated hardware design for a specific task.

However, to map complex machine learning algorithms to efficient hardware

architectures with on-chip learning is a very challenging task itself. As illustrated by Fig. 1.3, a lot of critical design issues need to be taken into consideration when developing the hardware architectures. First of all, the hardware designers should carefully investigate the machine learning algorithms and identify the hardwarefriendly properties which are suitable for efficient implementation. Secondly, a lot of important design decisions need to be made during the hardware development on both architecture and circuit level.

Figure 1.3: The critical considerations when mapping a complex software algorithm to a dedicated hardware design.

From the architecture design point of view, both the reconfigurability and scalability issues need to be considered. For example, which part of the algorithm should be parallelized and how much parallelism is needed? Correspondingly, what type of memory (storage) organization should be used to support the data processing in this architecture? Similarly, when should we introduce efficient hardware reuse to reduce the cost? Is it possible to configure the architecture differently to identify some important tradeoffs between throughput and hardware cost? Besides, both the binary arithmetics and the potential error resilience of the hardware architecture need to be investigated thoroughly for efficient hardware implementations.

From the circuit design point of view, the designers should always keep the timing, power consumption and silicon area in mind, in order to satisfy the necessary design constraints. This also requires the designers to be sensitive to the emerging new technologies which might benefit the overall performance of the hardware design.

The kernel methods like SVM (Support Vector Machine) and the ANNs (Artificial Neural Networks) are two of the most successful groups of the recent machine learning methods, which have been successfully applied to a wide range of real-world pattern recognition applications [8]. The corresponding hardware implementations have attracted much research interest from both academia and industry. However, due to the complexity of these algorithms, few earlier works have demonstrated competitive performance for real-world applications and efficient hardware architecture. In this dissertation, we propose a scalable digital architecture for a parallel SVM training algorithm, which achieves significant accelerations and demonstrates high energy efficiency and good performance for public data sets for real-world applications [9]. This dissertation also proposes several energy efficient neuromorphic architectures based on spiking neural networks, which demonstrate efficient parallel computing and error resilience for multiple real-world pattern recognition tasks [10]. Meanwhile, the potential application of memristive nanodevices for efficient synaptic storage in neuromorphic processors is systematically investigated in this dissertation. The remaining part of this section will give detailed introductions to all these works.

### 1.1 A Parallel Digital VLSI Architecture for Support Vector Machine

Support vector machine (SVM) is a learning and classification algorithm, which has been successfully applied to a wide range of real-world pattern recognition problems. An SVM learns by solving a convex constrained quadratic programming problem, whose size is equivalent to the number of training samples [11]. The training phase of SVM is a much more difficult and time consuming task than classification, and its implementation is also more complex.

Cloud computing provides a good solution for the big data processing [12], including the training of SVM. At the same time, some parallel SVM algorithms can also speedup the training phase [13]. However, these software approaches are all based on commercial general purpose CPUs, instead of dedicated application-specific integrated circuit (ASIC) designs optimized particularly for SVM algorithms. Therefore, hardware-based acceleration has not been explored in these works. In practice, having efficient hardware-based training can be quite useful. For example, training an SVM model over a large set of sampled data for big data analysis can be very time consuming. Dedicated hardware acceleration to improve both the training time and power consumption can be very appealing. In addition, in applications, such as smart sensors, where in situ machine intelligence is highly desirable, the ability in performing online training in hardware is essential because the changing environment requires frequent modifications to the existing model.

To facilitate the application of SVMs in embedded systems and develop pro-

cessing acceleration for large data sets, there have been several attempts to implement the algorithm in VLSI hardware. Analog VLSI implementation of the linear kernel SVM and the quadratic kernel SVM is reported in [14] and [15]. Kucher and Chakrabartty [16] adopt the margin propagation principle to design an analog VLSI SVM, whose key limitation is that training is performed offline. A digital architecture was proposed in [17], which enjoyed better precision and resolution compared with analog implementations, but it is not an ASIC solution. Kuan et al. [18] proposed an ASIC solution to sequential minimal optimization algorithm, but this paper is limited to only linear kernels. More recently, an FPGA based accelerator for SVM classification is presented in [19], which speeds up the classification process by cascading trained classifiers of different resolutions. While this architecture is also termed cascade, it differs dramatically from the cascade architecture proposed in this paper. The classification approach of [19] is heuristic in nature. More importantly, it does not deal with the acceleration of SVM training despite the fact that SVM training is typically much more algorithmically complex and compute-intensive than classification. An on-chip trainable Gaussian kernel analog SVM has been developed in [20], which uses an array of Gaussian circuits to support 12 2-D vectors.

Since training an SVM requires the solution of a quadratic programming problem, the required computation and storage increases rapidly with the number of training vectors, presenting a key challenge for learning over large data sets on chip. To this end, a highly scalable digital architecture for both training and classification, amenable to robust large-scale integration in modern VLSI technologies, is lacking, which is the focus of this work.

From a purely algorithmic point of view, an efficient strategy for accelerating SVM is to eliminate nonsupport vectors (SVs) early on during the optimization

process. The cascade SVM algorithm of [21] deals with this challenge by solving multiple smaller optimization problems based on partitioned data while rigorously guaranteeing the global convergence. This process can be viewed as a powerful built-in mechanism for early on filtering of non-SVs. In this work, we use the term cascade to either refer to the training algorithm of [21] or the corresponding VLSI architecture proposed by us. However, there is no prior work that investigates the VLSI implementation of cascade SVM. The main goal of this work is to develop a parallel digital VLSI architecture and the associated design techniques to bring the significantly improved scalability of cascade SVM to silicon. Our digital architecture enables efficient machine learning based on an array of interacting SVM processing units, amenable to implementation in scaled CMOS technologies. Several cascade SVM designs integrating both training and classification have been implemented using a commercial 90-nm CMOS standard cell library. Significant training speedup and energy reduction are demonstrated by our parallel hardware SVM designs. Meanwhile, the implemented SVM processors greatly outperform a 45nm commercial general purpose CPU for SVM training, in terms of both runtime and energy efficiency. These encouraging results suggest the great potential of the proposed architecture and circuit design for building large SVM array processors with high throughput and energy efficiency.

1.2 Energy Efficient Parallel Neuromorphic Learning Systems

The human brain can solve complex tasks such as pattern recognition and language learning with ease and demonstrate much improved energy and space efficiency than supercomputers [22]. Thus, brain-inspired cognitive computing and neuromorphic engineering have attracted much research interest nowadays. Spiking neural networks (SNNs) may be computationally more powerful than traditional rate-based neural networks, because SNNs more accurately resemble the biological neuron behavior. The inherent error resilience of SNNs is an appealing property for large-scale VLSI implementation, in modern technologies for which device reliability and process variation are becoming increasingly challenging. There have been several attempts to implement SNNs in VLSI [23]- [35]. However, these works did not fully exploit the power of SNNs for complex tasks such as speech recognition and handwritten character recognition. This dissertation proposes FPGA-based neuromorphic processor architectures for two spiking neural networks. One is a recurrent neural network called the liquid state machine, while the other is a feedforward spiking neural network with inhibitory neurons feedback loops to provide winner-take-all (WTA) mechanisms to each layer.

Realizing FPGA-based spiking neural networks (SNNs) entails addressing a number of critical issues pertaining to memory organization, parallel processing, hardware reuse for different operating modes and tradeoffs between throughput, area, and power overheads. The proposed neuromorphic system makes use of a large number of available block-RAMs for storing synaptic weights. To support parallel processing, multiple block-RAMs are instantiated in the system which allows multiple synaptic weights to be accessed simultaneously. We systematically demonstrate the tradeoffs between processing speed, power or energy and area overheads as a result of employment of varying levels of parallelisms and/or approximate multiplications.

The liquid state machine (LSM) is a recurrent neural network that recently emerged in theoretical neuroscience [36], and provides a solution to bridge the gap between biological plausibility and practical tractability of recurrent networks. Structurally, the LSM consists of a reservoir of neurons ("Liquid") receiving input spike trains and a group of readout neurons receiving signals from the reservoir.

Recently, [37] proposed an FPGA LSM processor architecture for speech recognition. However, this work did not explore the advantage of distributed computing in the neuromorphic system and its inherent error tolerance. [38] focused on the design of the readout stage for LSMs based on perceptrons and the p-Delta algorithm, which were less biologically inspired and were only applied to simple two-class recognition problems. Neither of these works exploit the potential application of approximate computing.

This work proposes a rather general model and neuromorphic architecture of computation based on the LSM. The main goal of this work is to develop a neuromorphic LSM architecture to support efficient general-purpose processing with integrated training and recognition. To aid the design space exploration of the LSM processor, in particular its complex recurrent reservoir, we propose a theoretical measure of computational power to allow for fast learning performance prediction of multiple applications without incurring timing consuming training. Based upon this, we develop a design methodology that determines the optimized reservoir size for each application and achieves minimal hardware and energy overhead of the general-purpose LSM learning processor for a given set of applications. We demonstrate the application of our processor architecture by mapping four recognition tasks onto a reconfigurable FPGA processor platform.

In addition, in order to fully exploit the unique computational structure and inherent resilience of the liquid state machine, we significantly reduce the energy dissipation of the reservoir by exploring spiking activity dependent power gating and efficient approximate adders. A widely adopted speech recognition benchmark, TI46 speech corpus [39], is used to evaluate the presented FPGA neuromorphic processors demonstrating their and a runtime speedup of 88× over the 2.3 GHz AMD OpteronTM Processor. The proposed LSM hardware design also demonstrates better recognition accuracy than the earlier works. The firingactivity based power gating scheme monitors the runtime activities of the reservoir and turns off inactive reservoir neurons during the training process to reduce power. An optimized approximate adder with adjustable precision is proposed, which significantly reduces power dissipation compared to the Xilinx built-in adders. The proposed techniques combined lead to a 30.2% reduction in both power and energy dissipations without greatly impacting speech recognition performance.

For the 2-layer spiking neural network with global inhibition, parallel digital neuromorphic architectures are developed and this work also investigates the potential application of approximate arithmetic units to reduce hardware cost and power consumption. The proposed architectures are demonstrated under the context of an FPGA based spiking neuromorphic learning system, which fully explores the parallelism in key processing steps. We also integrate a recent approximate Booth multiplier design [40] to replace the relatively bulky full precision multipliers, which contribute significantly to the area and energy estate of the overall system. Importantly, through the use of a real-life pattern recognition application, we show how such arithmetic units can be employed without incurring any significant loss of recognition performance for the end application. In return, the use of approximate computing offers noticeable energy and area benefits. Such reduction in energy dissipation and/or area overhead provides room for further throughput improvement via increased parallelism.

The proposed neuromorphic processor is implemented on a Xilinx Virtex-6 FPGA. The handwritten digits from the MNIST dataset [41] are used to test the recognition performance of the system. The architectures with standard multipliers achieve a recognition rate of 89.1%, and those utilizing the approximate multipliers maintain an excellent recognition rate of 87.7%. The proposed spiking neural network involves 1,591 neurons and 638,208 synapses, which shows comparable performance to a recent software reference [42] although our network has a smaller size. Energy consumption of the architecture without parallel processing is reduced by 20% when the approximate multipliers are used. A promising 13.5× training speedup and a 25.8× recognition speedup are achieved by the parallel architecture whose degree of parallelism is 32.

#### 1.3 Emerging Memory Technologies for Neuromorphic Processors

Traditionally, analog circuits are used to implement the silicon neurons [43] [44]. However, they are difficult to reconfigure and intrinsically sensitive to process, voltage and temperature (PVT) variations. In addition, large-scale integration of spiking neurons is hindered by the use of area-consuming capacitors as to keep synaptic weights [45]. Recently, [46] and [47] have demonstrated two digital reconfigurable neuromorphic chips. These two designs support up to 256 programmable digital neurons as well as  $1024 \times 256$  binary synapses by means of an SRAM crossbar array. However, the corresponding binary synapses are updated by a probabilistic scheme, which may degrade the learning performance. Moreover, the SRAM array occupies a significant portion of the entire chip area.

Memristive nanodevice provides a promising solution for on-chip storage thanks to its nonvolatile nature and high integration density reaching  $10Gb/cm^2$  [23]-[25]. Several recent studies have suggested leveraging memristive nanodevices for building synaptic arrays [26] [27]. A high-density, fully operational hybrid crossbar/CMOS system composed of a memristor crossbar array has been demonstrated in [28], which can reliably store complex binary and multilevel data. [29] proposes a memristor crossbar array system for image processing and demonstrates a good performance for noise reduction. Meanwhile, efficient hardware implementations of neural networks based on RRAM (Resistive Random Access Memory) crossbar arrays have been demonstrated in [30]- [33].

A brain-inspired reconfigurable digital neuromorphic processor (DNP) architecture for large-scale spiking neural networks is presented in [46]- [48], which supports spike timing dependent plasticity (STDP) learning mechanism. This design is implemented in a commercial 90nm CMOS technology and leverages the memristor nanodevice to build a 256 × 256 crossbar array to store multi-bit synaptic weight values with significantly reduced area cost. Realizing memristor array based DNPs entails addressing a number of critical issues pertaining to the memory access styles, analog-to-digital conversion and also the optimized storage organization. However, a systematic analysis of the above issues is lacking in the previous works. The main goal of this work is to investigate critical design decisions and identify key tradeoffs between energy and area for DNPs with different synapse readout schemes and storage organizations.

The memristor crossbar array has many advantages over SRAM and DRAM in terms of high integration density and nonvolatile nature, but the synaptic weight values stored in the memristor array are essentially continuous-valued analog signals (i.e. conductance and current), which can not be directly processed by the digital arithmetic components in the DNP. Typically, in such mixed-signal systems, the ADCs (analog-to-digital converters) make up a large portion of the total power consumption and chip area. Therefore, an efficient analog-to-digital conversion scheme for synapse readout plays an extremely important role in the design of DNPs. Crucial design choices and tradeoffs involving different memory access styles and different types of ADCs are systematically investigated in this work. Two memory access styles are proposed, which are referred to as the column-wise scheme and the row-wise scheme. Hence there exists a large design space for optimization of area and energy consumption. Our analysis highlights the trade-offs involved in various ADC strategies available for synapse readout. In addition, this work proposes an optimized synapse storage scheme for a wide class of feedforward spiking neural networks, which significantly reduces the energy consumption compared with those based on a full  $N \times N$  memristor array, where N is the total number of neurons.

### 1.4 Outline of the Dissertation

The remainder of this dissertation is organized as the follows. Section 2 introduces the mainstream machine learning methods, namely, SVM and ANNs, in order to provide some relevant algorithm background. The related works on hardware SVM, neuromorphic computing and emerging memory technologies are also discussed in this dissertation. Section 3 presents the proposed parallel digital VLSI architecture for Cascade SVM. The proposed general-purpose LSM neuromorphic processor and the parallel neuromorphic architecture for a 2-layer SNN with global inhibition are introduced in Section 4. Section 5 presents he architectural design exploration of the neuromorphic processor with memristive synaptic crossbar. Finally, we conclude this dissertation and discuss the future works in Section 6.

#### 2. BACKGROUND AND RELATED WORKS\*

This section describes an overview of SVM learning and neural networks. It starts with the basic concepts of SVM and Cascade SVM training algorithm, and earlier hardware SVM implementation works are introduced here. Then, we move on to the biological motivation of neuromorphic computing and provides reviews of artificial and spiking neural networks and the corresponding learning algorithms. The existing designs of silicon neurons and neuromorphic VLSI systems are also covered, which mimic the biological brain on silicon. The key design issues and limitations of these existing work are also discussed in this section. At last, the overview of the memristor nanodevice, which can be employed as the onchip storage of the neuromorphic system, is given. Finally, it clarifies the objective of this dissertation.

#### 2.1 Support Vector Machine and Hardware Implementations

The objective of the learning process of SVM classification is to find the structural optimal hyperplane that separates the training data with the largest margin [11]. To deal with the problem that the input data may not be linearly separable, in SVM the data may be nonlinearly mapped to a high dimensional space,