# A SUB-CENTIMETER RANGING PRECISION LIDAR SENSOR PROTOTYPE BASED ON ILO-TDC

A Thesis

by

# CHIH-YUAN CHEN

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# MASTER OF SCIENCE

| Chair of Committee, | Samuel Palermo      |

|---------------------|---------------------|

| Committee Members,  | Eun Jung Kim        |

|                     | Jun Zou             |

|                     | Kamran Entesari     |

| Head of Department, | Miroslav M. Begovic |

August 2016

Major Subject: Electrical Engineering

Copyright 2016 Chih-Yuan Chen

#### ABSTRACT

This thesis introduces a high-resolution light detection and ranging (LIDAR) sensor system-on-a-chip (SoC) that performs sub-centimeter ranging precision and maximally 124-meter ranging distance. With off-chip connected avalanche photodiodes (APDs), the time-of-flight (ToF) are resolved through  $31 \times 1$  time-correlated single photon counting (TCSPC) channels. Embedded time-to-digital converters (TDCs) support 52-ps time resolution and 14-bit dynamic range. A novel injectionlocked oscillator (ILO) based TDC are proposed to minimize the power of fine TDC clock distribution, and improve time precision. The global PVT variation among ILO clock distribution is calibrated by an on-chip phase-looked-loop (PLL) that assures a reliable counting performance over wide operating range. The proposed LIDAR sensor is designed, fabricated, and tested in the 65nm CMOS technology. Whole SoC consumes 37mW and each TDC channel consumes  $788\mu$ W at nominal operation. The proposed TDC design achieved single-shot precision of 38.5 ps, channel uniformity of 14 ps, and DNL/INL of 0.56/1.56 LSB, respectively. The performance of proposed ILO-TDC makes it an excellent candidate for global counting TCSPC in automotive LIDAR.

# DEDICATION

$To \ my \ beloved \ family$

#### ACKNOWLEDGEMENTS

I am enormously grateful for the people who have helped me accomplish the great work presented in this thesis. I thank my advisor, Dr. Sameul Palermo, for his knowledge, advice, and support throughout my studies at Texas A&M. I would like to thank Dr. Cheng Li for his great support in the project.

I would like to thank my committee members, Dr. Kamran Entesari, Dr. Jun Zou, and Dr. Eun Jung Kim for their guidance and support throughout the courses of the research.

Thanks also go to my colleagues and friends for their help in this project. Thanks to Dr. Ayman Shafik and Ashkan Roshan Zamir for their consultation in 65nm CMOS circuit design. Thanks to Shiva Kiran and Shengchang Cai for their supports in digital synthesizing work and FPGA setup. Thanks to Noah Yang for sharing his experience in ILO design. Thanks to Meng-Jie Hsiao and Chao-Hsiuan Tsay for their advice in PCB design.

# NOMENCLATURE

- ADC Analog-to-Digital Converter

- CML Current-Mode Logic

- CTDC Coarse Time-to-Digital Converter

- DFF D Flip-Flop

- DLL Delay-Locked-Loop

- DR Dynamic Range

- FLIM Fluorescence Lifetime Imaging

- FIR finite impulse response

- FTDC Fine Phase Time-to-Digital Converter

- GBW Gain-Bandwidth Product

- ILO Injection-Looked Oscillator

- JKFF J-K Flip Flop

- LIDAR Light Detection and Ranging

- PCB Printed Circuit Board

- PET Positron-Emission Tomography

- PLL Phase-Looked-Loop

- PMT Photomultiplier Tube

- PVT Process Voltage and Temperature

- RADAR Radio Detection and Ranging

- TCSPC Time-Correlated Single Photon Counting

- TDC Time-to-Digital Converter

- RO Ring Oscillator

# TABLE OF CONTENTS

|     |                   | Р                                                                                                                                        | age                                                                                          |

|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| AF  | BSTR              | ACT                                                                                                                                      | ii                                                                                           |

| DE  | EDICA             | ATION                                                                                                                                    | iii                                                                                          |

| AC  | CKNC              | WLEDGEMENTS                                                                                                                              | iv                                                                                           |

| N(  | OMEN              | NCLATURE                                                                                                                                 | v                                                                                            |

| TA  | BLE               | OF CONTENTS                                                                                                                              | vi                                                                                           |

| LIS | ST O              | F FIGURES                                                                                                                                | viii                                                                                         |

| LIS | ST O              | F TABLES                                                                                                                                 | xi                                                                                           |

| 1.  | INTI              | RODUCTION                                                                                                                                | 1                                                                                            |

|     | 1.1<br>1.2<br>1.3 | Applications: Automotive                                                                                                                 | $     \begin{array}{c}       1 \\       3 \\       3 \\       6 \\       8     \end{array} $ |

| 2.  | OVE               | RVIEW OF LIDAR SENSOR                                                                                                                    | 11                                                                                           |

|     | 2.1               | Optical Design                                                                                                                           | 13<br>13<br>15                                                                               |

|     | 2.2               | 2.1.2       Laber Equation         Transmitter       .         2.2.1       Laser Scanning Technique         2.2.2       Laser Wavelength | 16<br>17<br>18                                                                               |

|     | 2.3               | Photodiodes                                                                                                                              | 19<br>20<br>21                                                                               |

|     | 2.4               | Front-End Receiver                                                                                                                       | 22<br>22<br>25                                                                               |

|     | 2.5               | Time-to-Digital Converter (TDC)                                                                                                          | $\frac{20}{27}$                                                                              |

|    | 2.6<br>2.7 | 2.5.3 S<br>Sensor In<br>Advance | ine TDC<br>liding Sca<br>ntegration<br>d Backgro | ule Tecl | hnique  | • •   |      |      |      |     |     |     |    |     |    |   |   |   |   | 32  |

|----|------------|---------------------------------|--------------------------------------------------|----------|---------|-------|------|------|------|-----|-----|-----|----|-----|----|---|---|---|---|-----|

|    |            | Sensor In<br>Advance            | ntegration                                       | ι        |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 0.0 |

|    |            | Advance                         | -                                                |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 36  |

|    | 2.7        |                                 | d Backgro                                        |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 38  |

|    |            | 971 D                           |                                                  | ound L   | ight R  | eject | ion  | Tec  | hni  | que | e.  |     |    |     | •  |   |   |   | • | 41  |

|    |            |                                 | Back-end l                                       |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 41  |

|    |            | 2.7.2 F                         | ront-end                                         | Rejecti  | on Tee  | chnic | ue.  |      | •    | • • |     | •   |    | •   | •  |   |   | • | • | 42  |

| 3. | INJI       | ECTION-                         | LOCKEE                                           | OSCI     | LLAT    | OR (  | (ILC | ) A  | NE   | ) Т | DC  | D D | ES | SIG | IN | • | • |   |   | 44  |

|    | 3.1        | Problem                         | Statemer                                         | nt of E  | xisting | TD    | C A  | rchi | itec | tur | es  |     |    |     |    |   |   |   |   | 44  |

|    | 3.2        |                                 | tion of In                                       |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 45  |

|    | 3.3        |                                 | ed Time t                                        |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 50  |

|    | 3.4        | FTDC P                          | ower Anε                                         | lysis    |         |       | •••• |      |      |     | · · |     |    |     |    |   |   |   |   | 54  |

| 4. | PRO        | POSED                           | LIDAR S                                          | ENSOI    | R       |       |      |      | •    |     |     |     |    |     |    |   |   |   |   | 60  |

|    | 4.1        | Pixel Ch                        | annel Ari                                        | av       |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 62  |

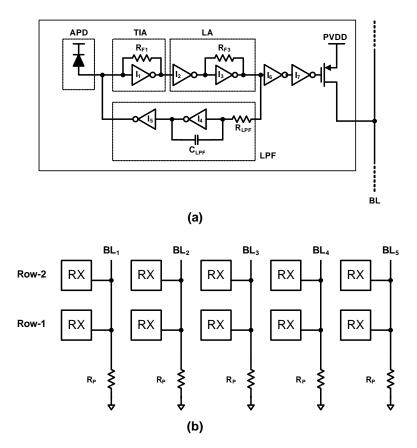

|    | 4.2        |                                 | d Receive                                        | -        |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 63  |

|    | 4.3        |                                 | Buffer                                           |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 64  |

|    | 4.4        |                                 | Digital C                                        |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 66  |

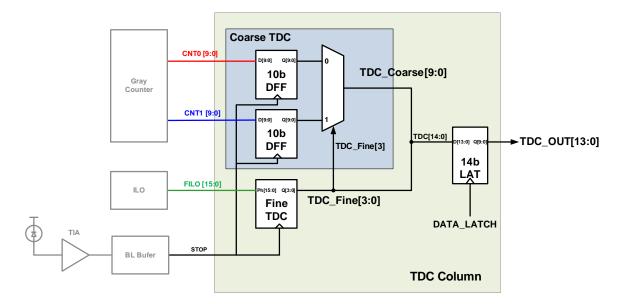

|    |            |                                 | DC Colu                                          |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 68  |

|    |            |                                 | TDC Co                                           |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 69  |

|    |            |                                 | TDC Edg                                          |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 72  |

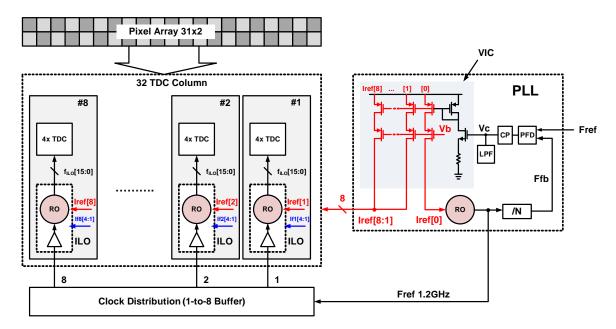

|    | 4.5        |                                 | -locked C                                        |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 73  |

| 5. | EXF        | PERIMEN                         | TAL RE                                           | SULTS    |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 76  |

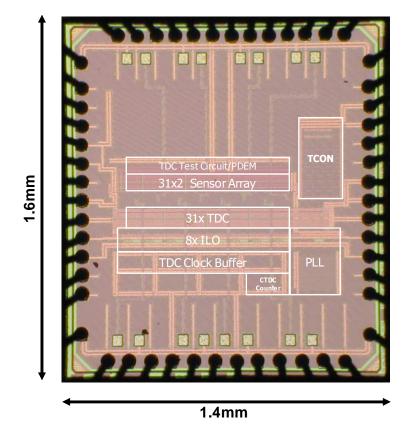

|    | 5.1        | Sensor S                        | оС                                               |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 76  |

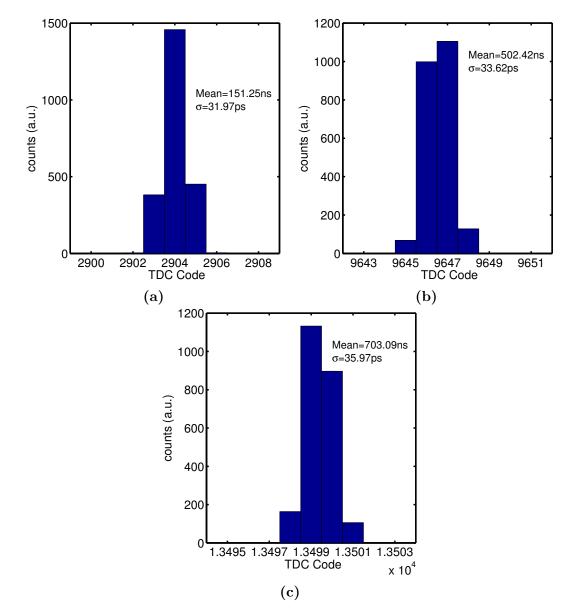

|    | 5.2        | Single-Sl                       | not Precis                                       |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 78  |

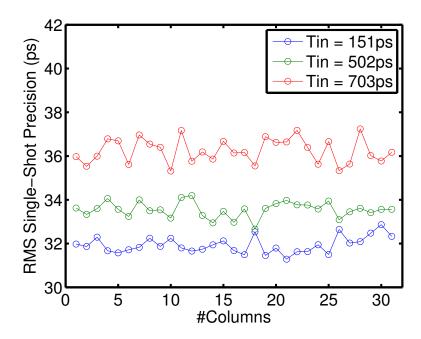

|    | 5.3        |                                 | Uniformi                                         |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 80  |

|    | 5.4        |                                 | ·                                                |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 83  |

| 6. | SUN        | IMARY A                         | AND CON                                          | ICLUS    | IONS    |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 86  |

| RF | EFER       | ENCES .                         |                                                  |          |         |       |      |      |      |     |     |     |    |     |    |   |   |   |   | 88  |

# LIST OF FIGURES

| FIGUR | E                                                                                                                          | Page |

|-------|----------------------------------------------------------------------------------------------------------------------------|------|

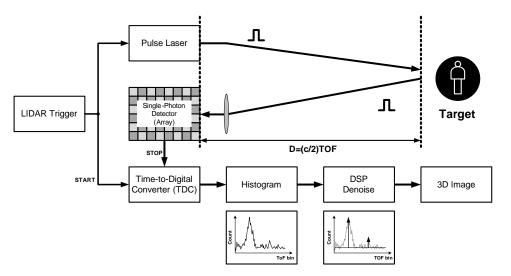

| 1.1   | Pulse-based LIDAR sensor                                                                                                   | 4    |

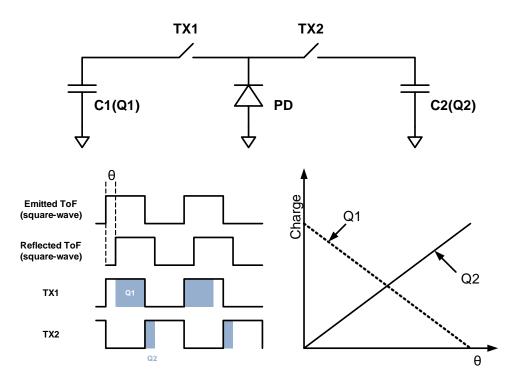

| 1.2   | Demodulation pixel to demodulate phase delay between the emitted<br>and reflected ToF signals into electronic charges [11] | 7    |

| 2.1   | Block diagram of pulse-based LIDAR                                                                                         | 12   |

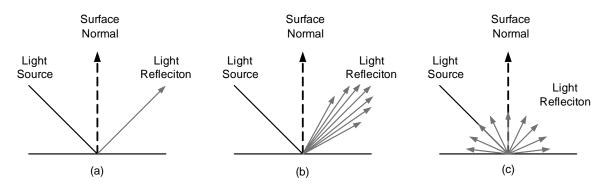

| 2.2   | Surface reflection model: (a) specular, (b) spread, (c) lambertian                                                         | 13   |

| 2.3   | LIDAR equation: received power vs. ranging distance                                                                        | 17   |

| 2.4   | Avalanche process in APD                                                                                                   | 21   |

| 2.5   | Schematic of transimpedance amplifier                                                                                      | 22   |

| 2.6   | Schematic of typical passive quenching circuit (PQC)                                                                       | 26   |

| 2.7   | Schematic of two-step discharging rate active quenching circuit (AQC) [19]                                                 | 27   |

| 2.8   | A 4-bit synchornous up-counter using T (toggle) flip-flops with a 4-bit time memory: (a) schematic, (b) counting waveform. | 31   |

| 2.9   | Schematic of delay-line TDC (DL-TDC) embedded in DLL                                                                       | 33   |

| 2.10  | Tapped delay-line TDC with self-calibrating circuit [25]                                                                   | 33   |

| 2.11  | Gated delay-line TDC [26]                                                                                                  | 34   |

| 2.12  | Gated-ring-oscillator (GRO) TDC [9]                                                                                        | 35   |

| 2.13  | Sliding scale technique in TDC.                                                                                            | 37   |

| 2.14  | Global-based couting architecture: (a) 32×32 imager floorplan, (b) pixel block diagram [7]                                 | 39   |

| 2.15  | Pixel-based counting architecture: (a) 160×128 imager architecture,<br>(b) pixel block diagram [9]                         | 40   |

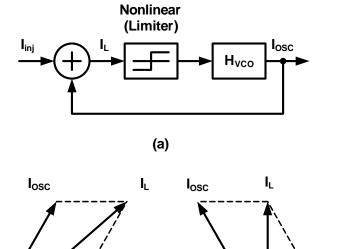

| 3.1  | Injection Locking: (a) oscillator model, (b) phase shift diagram, and (c) phase shift diagram on the boundary of locking range                                                                                                                                                                                            | 47 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | ILO phase shift versus inherent frequency difference $(\Delta \omega_0)$                                                                                                                                                                                                                                                  | 49 |

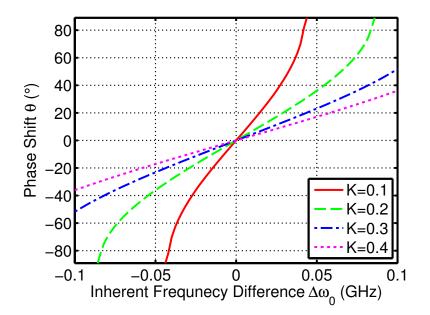

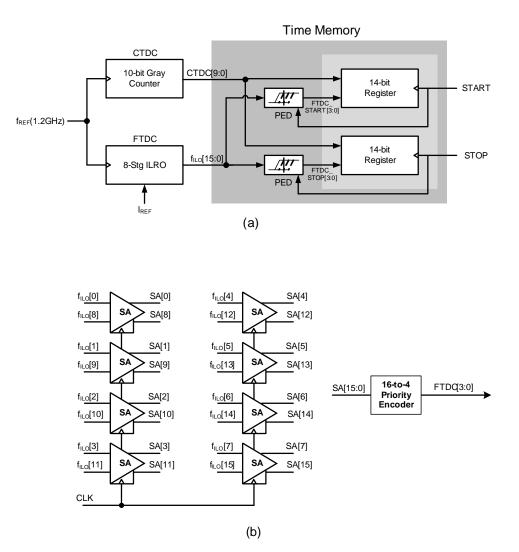

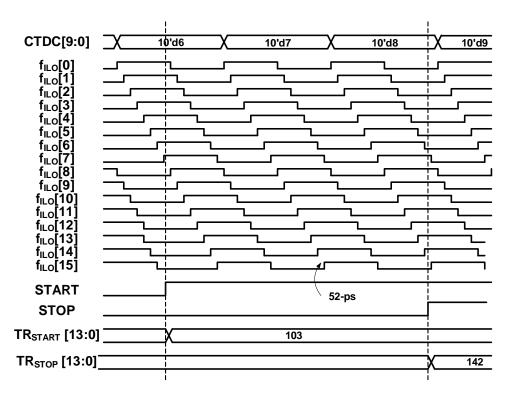

| 3.3  | Single channel ILO-based TDC: (a) block diagram, (b) schematic of phase-edge detector.                                                                                                                                                                                                                                    | 51 |

| 3.4  | Operation waveform of ILO-TDC                                                                                                                                                                                                                                                                                             | 52 |

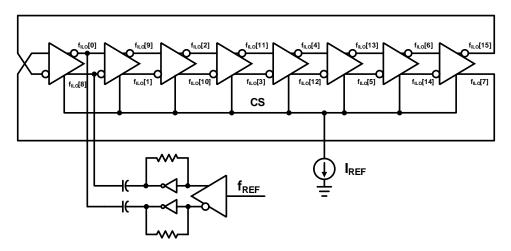

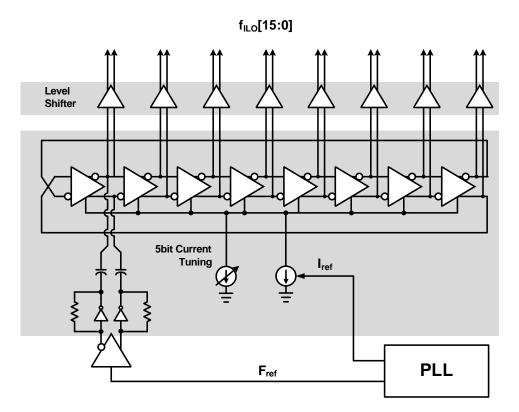

| 3.5  | Schematic of eight-stage ILRO.                                                                                                                                                                                                                                                                                            | 52 |

| 3.6  | 32-channel ILO-TDC array                                                                                                                                                                                                                                                                                                  | 53 |

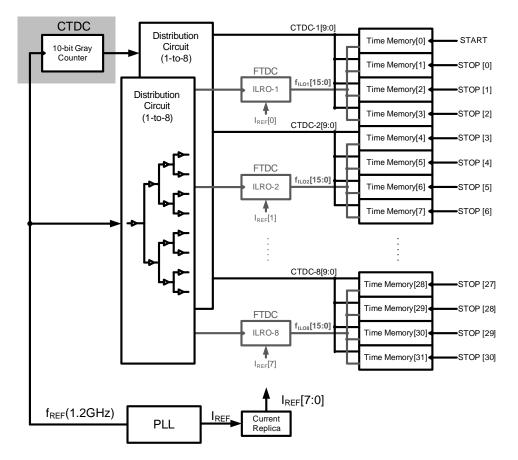

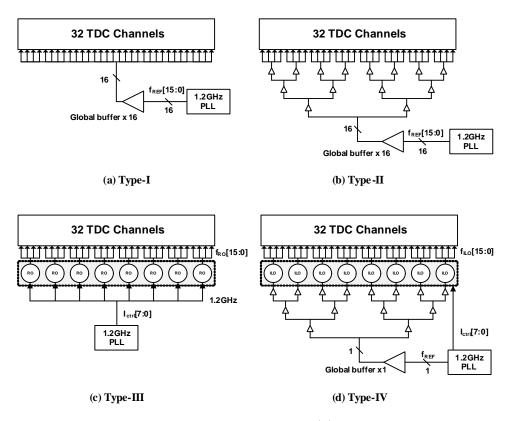

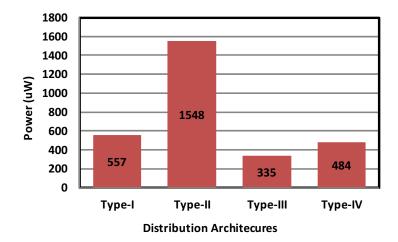

| 3.7  | Four clock distribution architectures: (a) Type-I: global counting driven<br>by single-stage buffer, (b) Type-II: global counting driven by multi-<br>stage buffers, (c) Type-III: local counting driven by ring oscillators<br>(ROs), (d) Type-IV: local counting driven by injection locked ring<br>oscillator (ILROs). | 55 |

| 3.8  | The simulated power/channel of the four clock distribution architectures.                                                                                                                                                                                                                                                 | 57 |

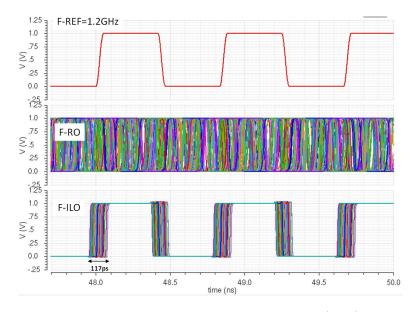

| 3.9  | Oscillation waveform of free-running RO $(f_{RO})$ and IL-RO $(f_{ILO})$<br>locked by an 1.2GHz injection-locked clock in Monte-carlo simulation<br>(number of sample=200)                                                                                                                                                | 58 |

| 3.10 | Statistic distribution of (a) free running RO and (b) ILO with injection locked by an 1.2GHz external clock in Monte-carlo simulation (number of sample = 200).                                                                                                                                                           | 59 |

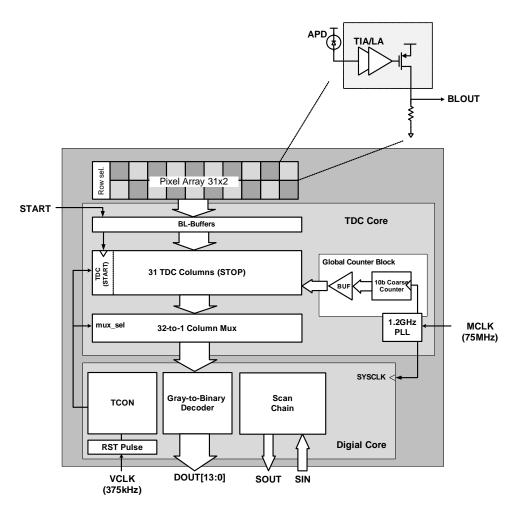

| 4.1  | Block diagram of proposed pulse-based LIDAR sensor prototype                                                                                                                                                                                                                                                              | 61 |

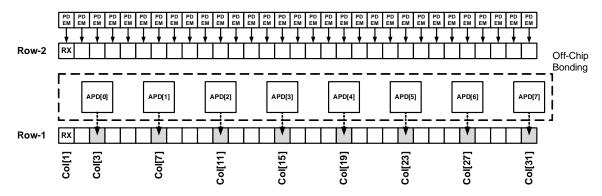

| 4.2  | Floor-plan of the $31 \times 2$ pxiel channel array                                                                                                                                                                                                                                                                       | 62 |

| 4.3  | APD front-end receiver: (a) schematic of single-channel receiver, (b) receiver output with bit-line sharing.                                                                                                                                                                                                              | 64 |

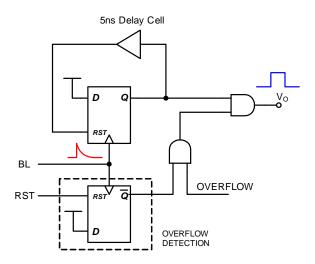

| 4.4  | Schematic of bit-line (BL) buffer.                                                                                                                                                                                                                                                                                        | 65 |

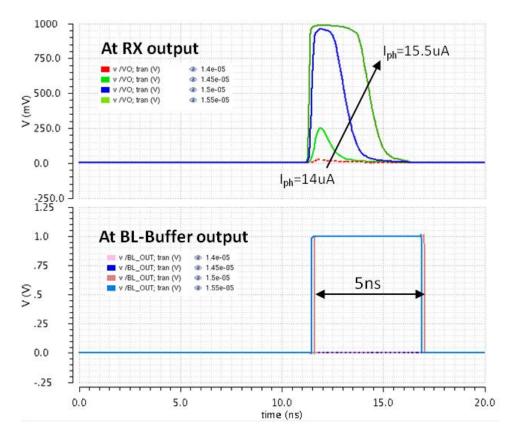

| 4.5  | Pulse regeneration though BL-buffer. The simulated photocurrent is swept around the detection threshold of front-end RX from 14µA to 15.5µA. BL-buffer senses the RX output and regenerates a 5ns pulse when $I_{ph}$ is larger than 15µA and filters out the $I_{ph}$ lower than it                                      | 66 |

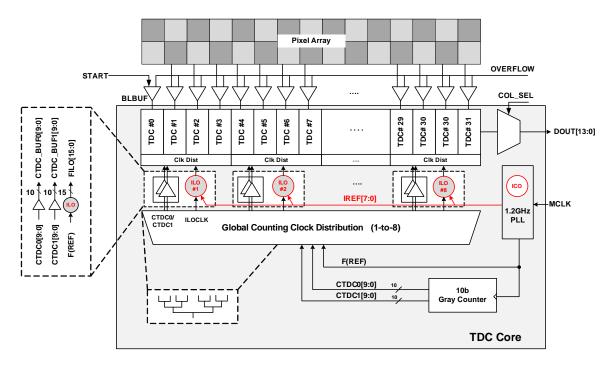

| 4.6  | The block diagram of 32-TDC columns design                                                                                                                                                                                                                                                                                | 67 |

| 4.7  | Schematic of single TDC column circuit.                                                                                                                                                                                                                                                                                                                                       | 68 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

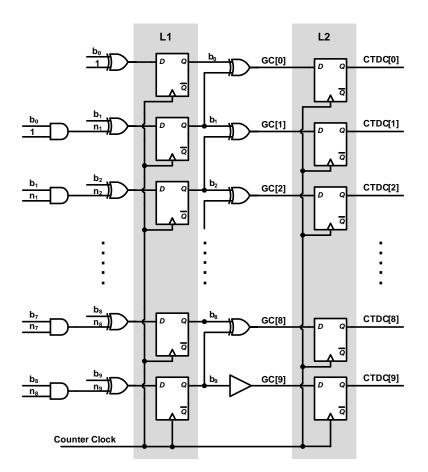

| 4.8  | Schematic of CTDC Gray-code counter.                                                                                                                                                                                                                                                                                                                                          | 70 |

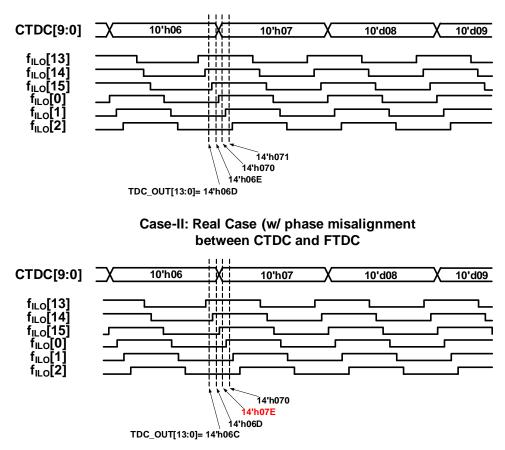

| 4.9  | The example of nonlinear missing code induced by misalignment be-<br>tween CTDC and FTDC                                                                                                                                                                                                                                                                                      | 71 |

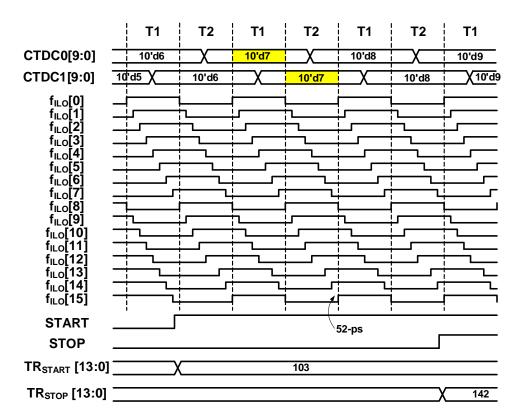

| 4.10 | The timing diagram of CTDC and FTDC. The double counter scheme (CTDC0 and CTDC1) is implemented to solve misalignment issue between coarse and fine counters. If TDC STOP signal triggers at the time during T1 period, CTDC0 [9:0] will be selected as CTDC output. If TDC STOP signal triggers at time during T2 period, CTDC1 [9:0] will be selected as coarse-TDC output. | 72 |

| 4.11 | Schematic of injection locked oscillator (ILO).                                                                                                                                                                                                                                                                                                                               | 74 |

| 4.12 | PVT-calibration in ILO clock distribution.                                                                                                                                                                                                                                                                                                                                    | 75 |

| 5.1  | Photomicrograph of prototype LIDAR SoC in 65nm CMOS                                                                                                                                                                                                                                                                                                                           | 77 |

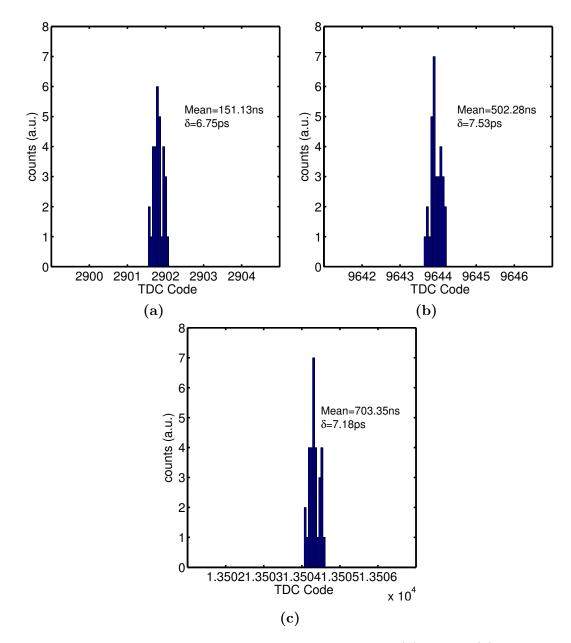

| 5.2  | Single-shot precision of TCSPC channel (front-end RX and TDC) with time input: (a) 151ns, (b) 502ns, and (c) 703ns, corresponding to rms precision of 31.97ps, 33.62ps, and 35.97ps, respectively.                                                                                                                                                                            | 79 |

| 5.3  | RMS single-shot precision of 31 TCSPC channels (front-end RX and TDC) with time input at 151ns, 502ns, and 703ns                                                                                                                                                                                                                                                              | 80 |

| 5.4  | TDC channel uniformity with time input: (a) 151ns, (b) 502ns, and (c) 703ns, corresponding to rms precision of 6.75ps, 7.53ps, and 7.18ps, respectively.                                                                                                                                                                                                                      | 81 |

| 5.5  | TCSPC channel uniformity with time input: (a) 151ns, (b) 502ns, and (c) 703ns, corresponding to rms precision of 11.06ps, 10.75ps, and 10.48ps, respectively.                                                                                                                                                                                                                 | 82 |

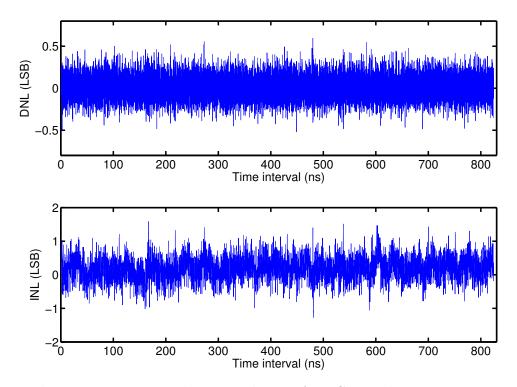

| 5.6  | Measured DNL and INL of TDC over dynamic range                                                                                                                                                                                                                                                                                                                                | 83 |

# LIST OF TABLES

| TABLE |

|-------|

|       |

- 5.1 Power breakdown of main SoC blocks operating at 52-ps time resolution 78

- 5.2 Comparison table of recently published state-of-the-art devices . . . . 85

#### 1. INTRODUCTION

With the emerging growth of three-dimensional (3-D) enhanced computer vision, high-resolution 3-D image sensing technology has gained increasing interest recently. This sensing technology, capable of mapping the geometric information within the surrounding environment and collecting the data for the background analysis, is applied in several applications, including automotive, industrial, health-care and entertainment. In this context, light detection and ranging (LIDAR) with imaging capability or so-called time-of-flight (ToF) technology is one of the fast-growing classes in this field. Comparing with other 3-D imaging techniques such as millimeter-wave (MMW) radars [1], ultrasonic sensors [2], and stereo-vision cameras [3], LIDAR offers fast detection, high spacial resolution and reliable 3-D mapping in uncontrolled illuminance environment.

#### 1.1 Applications: Automotive

With the force of national regulation, safety issue has become as important as fuel economy and engine performance in automotive market. A particular class of safety systems that are proposed among several tier-one car manufactures are so-called advanced driver assistance system (ADAS). This system is aimed at not only preventing traffic accidents in the first place, but also provides adaptive cruise control (ACC). Many features such as forward collision warning (FCW), autonomous emergency breaking (AEB), pedestrian detection, etc. are counted in this system. In the near future, ADAS will be incorporated into not only high-end car market, but the mid- and low-end. Among several 3-D imaging techniques, MMW-radar remains the sensor of choice for now. MMW-radar has been widely used in conventional driving assistance to monitor vehicle driving environment. However, due to the limit of radar wavelength the angular resolution ( $\theta = 1.22\lambda/D$  rad, where  $\lambda$  is the wavelength and D is the diameter of antenna) of MMW-radar is typically in the angle of 2° to 5° that is insufficient for some applications that need detail feature to identify remote sensing objects. To achieve desirable function, many automotive radars are usually combined with stereo-vision cameras in which the 3-D information is constructed from multiple 2-D image frames that were taken simultaneously from different viewing angles. Such technology usually utilizes low-cost CMOS imaging sensors (CISs) but demands intensive computing resources, process time, and power to reconstruct the 3-D information. Also, as stereo-vision camera is passive-mode sensor, it is sensitive to the ambient light condition and work poorly in low illuminance environment.

LIDAR, on the other hand, can offer higher spatial resolution due to the shorter optical wavelength. This characteristic allows LIDAR to detect smaller threaten objects in the environment such as wires, pillar, and defect on the road land. Also, the active optical source embedded in LIDAR provides reliable ranging detection under low background illuminance. The main challenge of automotive LIDAR sensor is the cost. To increase the signal-to-noise ratio (SNR), laser scanning approach is mostly utilized. This approach requires sophisticated mechanical and optical design so the cost is much higher than radar module. The challenges of reducing module complexity and driving down the cost will be the first priority in advanced LIDAR sensor. Undoubtedly, LIDAR will be prevalent in automotive industry in the near future. For example, LIDAR was applied in pseudo-cruise control and pedestrian detection in Texas Instrument's ADAS solutions guide in 2015 [4]. Meanwhile, many car manufacturers such as Toyota and Nisson have started investigating LIDAR technique in their vehicles.

Autonomous driving, a more advanced driving system, is another fact that boosts the development of LIDAR in automotive industry. Comparing with ADAS, the autonomous driving system demands for higher resolution 3-D mapping and more sophisticated computer vision technique to identify different kinds of obstacles and navigate the car safely in the traffic environments. The high demand for the imaging quality makes LIDAR as a major sensor in autonomous vehicles. For instance, the Google's driverless car has a 64-beam laser scanning LIDAR mounted on the top. This LIDAR module provides central navigator a 360-degree 3-D vision.

## 1.2 Range Technique

As known as the optical radar, LIDAR measures the distance by timing how long a light to make a round trip between the senor and the object. The system usually contents two major components: 1) transmitter: an array of light-emitting diodes (LEDs) or laser diodes (LDs), and 2) receiver: a time-correlated single-photon counting (TCSPC). There are many variants of LIDAR systems. According to the modulation of light sources, these systems can be generally classified into two categories: pulse-based LIDAR [5, 6, 7, 8, 9] and modulation-based LIDAR [10, 11].

# 1.2.1 Pulse-based LIDAR

In pulse-based LIDAR sensors (Fig. 1.1), the transmitter emits single light pulse in a rapid frequency. As the light pulse hits remote objects (car, tree, or human being), it gets reflected. The travel time between the pulse being emitted and then returning to the optical sensor is measured by the receiver, and so-called as time-of-flight (ToF). ToF time, along with the speed of light can be used to calculate the distance from the LIDAR module to objects:

$$d = \frac{c \cdot t_{TOF}}{2} \tag{1.1}$$

Figure 1.1: Pulse-based LIDAR sensor.

where c is the speed of light in air and the  $t_{TOF}$  is the round trip travel time. This approach seems straight-forward and the complexity of related optical design is low. However, the pixels in the sensor array have to be very sensitive to capture the low intensity of the returned pulse. Usually, single-photon-level sensitivity is needed in long-range application. Photomultiplier-tubes (PMTs) are traditional devices that are used as single-photon detector. However, PMTs require kilo-volt operating voltage, and device is so bulky that makes it hard to integrated as array-based sensor in a lite module size. This is also the reason why LIDAR is hard to be commercialized in early ages. This bottleneck, fortunately, was been broken in the last decade with the progress in CMOS technology. Semiconductor photodiodes (PDs) such as avalanche photodiodes (APDs) and single-photon avalanche photodiodes (SPADs) are the alternative to PMTs in quantum optics. These solid-state devices, which are typically biased at tens-volt operating voltage, offer better optical responsivity and higher bandwidth. With the improvement in device fabrication, these micro-meterscale PDs are available in conventional CMOS chip-level integration, meaning a lower power, lower cost, and higher resolution LIDAR sensor system-on-a-chip (SoC).

Time-to-digital converter (TDC) is the main component to measure travel time of light in pulse-based LIDAR. Since the depth information is directly converted from TDC results, the specifications of TDC is essential to LIDAR sensors. According to the size of pixel array, multiple TDC channels are usually utilized to increase the conversion rate. Therefore, the TDC block will consume a considerable power as the resolution gets higher and the pixel array becomes larger. In this context, power budget of TDC channels is a critical for the whole systems.

In out-door environment, due to the low intensity of returned pulse, pulsebased LIDAR usually suffers from the background light (i.e. sun-light). Higher signal-to-noise (SNR) can be achieved by increasing the measuring cycles and build a histogram to filer the white noise in the ambient. More advanced LIDAR systems leverage digital-signal-processing to refine histogram and extract accurate ToF value.

Pulse-based LIDAR sensors have several advantages. From the circuit-level perspective, it leverages the benefits of deeply scaled CMOS technology since most of signal processing are in digital-domain. For example, the digital TDCs achieves better resolution and higher precision in advanced technology node since transistor frequency  $(f_T)$  gets higher in short channel devices. From the system-level perspective, pulse-based LIDAR has the advantages of high dynamic range, fast measurement time and capability to deal with multiple echoes in uncontrolled environment. Actually, the multiple-echo capturing is an important feature in pulsed LIDAR and useful in many application. For instance, geometry features beneath the ocean or forest canopy can be mapped through multiple-echo reflection. In driving assistance systems and driverless car, multiple-echo is prevalent in most practical traffic scenarios.

## 1.2.2 Modulation-based LIDAR

In modulation-based LIDARs, the laser power is modulated with a sinusoidal or square-wave signal. The light travel time is measured through phase delay between the received and the transmitted signals:

$$t_{TOF} = \frac{\phi \cdot T}{2\pi} = \frac{\phi}{2\pi f} \tag{1.2}$$

where  $\phi$  is phase delay between the received and the transmitted signals, T and f is the period and frequency of modulation signal. The phase delay can be detected through a demodulation pixel. As shown in Fig. 1.2, the demodulation pixel has two transfer gates  $(TX_1 \text{ and } TX_2)$  that controls the charging time of two integration capacitors  $(C_1 \text{ and } C_2)$  [11]. With a certain amount of repeating cycle, the phase difference can be calculated through the amount of charges integrated on  $C_1$  and  $C_2$ :

$$\phi = \frac{Q(\pi)}{Q(0) + Q(\pi)} \tag{1.3}$$

The amount of integrated charges can be converted into voltage-domain through

front-end amplifier such as capacitive transimpedance amplifier (CTIA), and then digitized by analog-to-digital converter (ADC). Since the depth information is acquired through analog manner, dynamic range of conversion is limited by the ADC input range versus electronic noise in the circuit. A trade-off presents between ranging precision and ranging distance: we can improve ranging precision by increasing modulation frequency but that also reduces ranging distance.

Unlike pulse-based LIDAR sensor where PDs has to be very sensitive to cope with optical pulse signals, the sensitivity requirement for the PDs in modulationbased LIDAR is moderate since the ToF signal is continuous-wave power. A conventional photodiodes such as pin-photodiodes (PPDs) can work properly as Demodulation pixel with a certain amount of integration time. Comparing with SPADs and

Figure 1.2: Demodulation pixel to demodulate phase delay between the emitted and reflected ToF signals into electronic charges [11].

APDs, PPDs are relatively mature and low-cost device that were used in mega-pixel CMOS image sensors for many years. Therefore, modulation-based LIDAR usually has potential for achieving larger pixel array and lowering complexity of fabrication.

The advantage of analog conversions in modulation-based LIDAR is that resolution can be enhanced by increasing voltage-gain in front-end amplifiers, which is hard to implement in time-domain signal processing. Time-domain amplifier usually relies on the device matching and consumes longer process time [12, 13, 14]. This difference makes the sub-centimeter resolution is easily achieved in modulation-based LIDAR but burns a lot of power in pulsed-based LIDAR for boosting high frequency of TDC reference clock.

As we described previously, the downside of modulation-based LIDAR is the limited dynamic range. On the other hand, TDC-based conversion has extensible dynamic range. Moreover, the modulated signals are more vulnerable to the multi-echo reflections, which limit the applications of this technology. In summary, modulation-based LIDARs are typically used in short range-finding that demands high resolution 3-D imaging such as 3-D scanner, 3-D copier, gesturing, and gaming, while the pulse-based LIDARs are used in the long range-finding such as geometric mapping, driving assistance, autonomous vehicle, and out-door surveillance.

# 1.3 Thesis Organization

In this thesis, we demonstrate a pulse-based LIDAR sensor prototype that are targeting at the long-range application such as driving assistance system and autonomous car. The object of this work is to minimize the power consumption of TDC meanwhile achieve sub-centimeter ranging precision. A TDC topology based on injection-locked oscillators (ILOs) is utilized in the prototype to achieve a lowpower clock distribution, which is the novelty in TDC design as well as LIDAR sensor SoC.

In Section 2, an overview of LIDAR sensor is presented. The overview commences with the optical transmitter design. It contents LIDAR power equation, the characteristics of transmitter sources, and scanning technique. We then discuss the properties of two conventional single-photon photodiodes, i.e. APDs and SPADs, and their respective front-end receivers. This will be followed by a general discussions of high-level TDC design. The concept of multi-stage conversion will be illustrated in circuitry level. A literature survey of the current state-or-art TDC designs implemented in LIDAR sensors is presented, commenting on each topology and highlighting the strengths and drawbacks with each architecture. The section concludes with the introduction of advanced back-end rejection technique, which is important for improving signal-to-noise ratio (SNR) and the quality of imaging. The technique was implemented in digital-side or analog-side.

In Section 3, it starts with a statement of the major challenges and con-siderations involved in LIDAR-TDC. A new TDC architecture based on ILO clock distribution is proposed to address the trade-off between the power and timing accu-racy in previous works. We then discuss the theory of injection locking and derived the the locking equation for characterizing the circuitry behavior. This is followed by circuitry level design of ILO-based TDC (ILO-TDC), with single channel and multiple channels. The section is concluded with a comparison of power budget be-tween the ILO-based TDC and the other types of clock distribution. The comparison results show the advantage of ILO-TDC in terms of power budget, time resolution, and time precision.

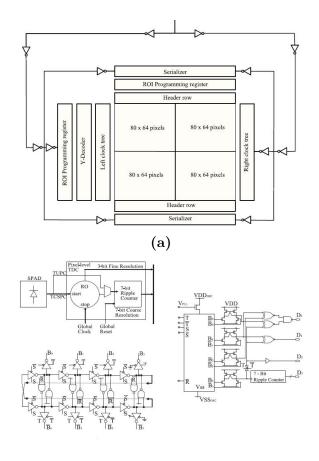

In Section 4, the proposed LIDAR sensor prototype is presented. The proto-type SoC supports  $31 \times 2$  pixel array channels. The estimated distance resolution is 0.78-cm and the maximum detection range is 124-m. The consideration from system-level to circuitry-level will be describe thoroughly. The main core in the SoC is a 14-bit two-stage flash TDC. The Coarse-TDC (CTDC) is implemented by a global 10-bit Gray code counter, and the Fine-TDC (FTDC) is based on the 4-bit ILO-TDC in Section 4. The TDC supports 31 input channels, 52-ps time resolution, and 852-ns measurement range.

In Section 5, SoC electrical measurement results are presented, including power breakdown, single-shot precision (SSP), channel uniformity, and linearity performance. Finally, a table summarizes the performance of the proposed SoC and compares this work against recent state-of-the-art works.

In Section 6, a summary of the work is given, conclusions are made and the nature and scope of future work in this thesis is discussed.

#### 2. OVERVIEW OF LIDAR SENSOR

Applications such as driving assistance and autonomous car demand hundreds of meters of ranging distance within uncontrolled luminance environment. Signal-tonoise ratio (SNR) degrades severely in this condition due to the strong intensity of solar background illuminance. Also, in complicated traffic situations such as that in the urban cities, the effect of multi-echos could be serious due to the surroundings, i.e., buildings, traffic signs, vehicles, and pedestrians. In this context, pulse-based LIDAR is typically preferred due to its high dynamic range, fast measurement time and capability to deal with multi-echos. In this section, we will discuss several considerations in pulse-based LIDAR sensor from the optical design to electrical circuitry.

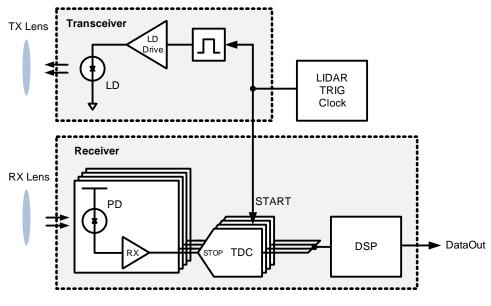

Fig. 2.1 shows the block diagram of pulse-based LIDAR sensor. In the transceiver, a pulse laser emits optical pulses at a repetition frequency. Laser beam is collimated through a focal lens in front of laser head to enhance the power efficiency and SNR. The return pulse, reflected by remote targets, is collected through a receiver lens, and focused on the sensor array in receiver. Single-photon photodiodes (PDs) such as APDs or SPADs are usually utilized here to capture the low intensity of returned pulse. A time-correlated single-photon counting (TCSPC) is cooperated to measure the travel time of light. To get accurate counting results, the transmitter and receiver are synchronized with a global LDIAR trigger clock. This global clock triggers pulse laser emission as well as the start time of time-to-digital converter (TDC). Therefore, TDC counts the time starting from pulse emitted by transceiver. As return pulses are detected by PDs, the optical signal is converter into photocurrent signal that is sensed and amplified by front-end receiver (RX). The output of front-end RX is used as the STOP signal for TDC. The resolved TDC output is:

Figure 2.1: Block diagram of pulse-based LIDAR.

$$t_{TDC} = t_{STOP} - t_{START}$$

$$= t_{detection} - t_{emission}$$

$$(2.1)$$

Multiple TDC channels are designed to support the input of time events from sensor array so that a faster conversion rate can be achieved. Several state-of-art TDC architectures were proposed based on the requirement of power, area and conversion rate in applications. According to those specifications, TDC design can be pixelshared, column-shared, or global.

Finally, DSP is designed to filter out the noise in ambient illuminance, photodiodes, and electrical circuits. Typical filtering technique includes temporal correlation filtering (histogram average, finite-impulse-response) and spatial correlation filtering that will discuss further in the later paragraph.

# 2.1 Optical Design

# 2.1.1 Surface Reflection Model

LIDAR ranging distance is typically limited by the minimum light intensity of returned pulse that can be captured by sensor pixels. The intensity reflected from an object is dependent on the distance, reflection coefficient, and surface roughness of the object. Fig. 2.2 shows three typical reflection models that are used to describe the surface reflection in the nature. The first type is Specular reflection, in which the light from a single incoming direction is reflected into a single outgoing direction. The angle of light reflection follows the Snells law: the angle of reflection is equal to angle of incidence:

$$\theta_i = \theta_o \tag{2.2}$$

Specular model describe the reflection of ideal mirror surface. If surface has a slight roughness, the reflection power tends to spread out along the ideal reflected direction.

Figure 2.2: Surface reflection model: (a) specular, (b) spread, (c) lambertian.

The illuminance of outgoing light detected by viewer can be approximated by Phong equation [15]

$$I(\theta) = k_S \cdot I_{in} (\vec{V} \cdot \vec{R})^n$$

=  $k_S \cdot I_{in} \cos^n \theta$  (2.3)

where  $k_S$  and n are specular reflection constant and shininess constant of surface,  $I_{in}$  is the incident illuminance,  $\vec{V}$  is the vector to viewer,  $\vec{R}$  is the vector of ideal specular reflection, and  $\theta$  is the angle between  $\vec{V}$  and  $\vec{R}$ . Phong equation reflection presents the light reflection of most mirror-like surfaces in the nature, i.e., glass and water.

As the roughness increases, the surface reflection will be more divergent. This diffusely reflecting surface is described as Lambertian surface. In Lambertian reflectance, light from a single incoming direction is reflected isotropically: the same radiance would be detected by viewer from any angle. For example, a white paper has the same brightness no matter the viewer is on perpendicular direction and tilt direction. It is interesting to note that even the reflection radiance is isotropic in Lambertian reflectance, the luminance intensity is not. This is because the solid-angle detected by viewer from a tilt direction ( $\theta$ ) is actually smaller than that from the perpendicular direction by  $cos(\theta)$ . To maintain the same radiance, the intensity needs to decrease by  $cos(\theta)$ . This phenomenon is well-known as Lambert's Cosine Law:

$$I(\theta) = I(0^{\circ})cos(\theta) \tag{2.4}$$

Lambertian reflectance represents most nature surfaces in the world such as woods, stones, and sands. It is also the most adoptive model used in LIDAR equation. In the following, we derive LIDAR equation with the assumption of Lambertian reflectance.

#### 2.1.2 LIDAR Equation

LIDAR equation describes the fundamental relation between the emitted power and received power in LIDAR system. In the transmitter, a pulse laser transmits a narrow beam toward a reflector. The footprint area of the beam at reflector is:

$$A_{laser} = \frac{\pi R^2 \Omega_t^2}{4cos(\theta)} = \frac{A_{laser,0}}{cos(\theta)}$$

(2.5)

where R is the distance to the reflector,  $\Omega_t$  is the laser beamwidth, and  $\theta$  is the incident angle respective to surface normal. Dividing the power by the footprint area, the incident power density  $S_t$  of laser beam at the reflector is:

$$S_t = \frac{P_t}{A_{laser}} = \frac{P_t}{A_{laser,0}} cos(\theta)$$

(2.6)

where  $P_t$  is total transmitted power. The reflection power  $P_r$  can be calculated as:

$$P_r = \rho S_t A_s \tag{2.7}$$

where  $\rho$  is the reflection constant of material, and  $A_s$  is the optical receiving area of the reflector. The reflection pattern is quite complex, but for simplicity we assume that the radiance is reflected uniformly into a cone of solid angle. The reflected power density  $S_r$  is:

$$S_r = \frac{P_r}{\Omega_r R^2} \tag{2.8}$$

where  $\Omega_r$  is the solid angle of reflected beam that is  $\pi$  in Lambertian reflectance. Thus, the reflected power collected by receiver lens is:

$$P_{Lidar} = S_r A_{lens} \tag{2.9}$$

where  $A_{lens}$  is the effective area of the receiver lens. Combining (2.5)-(2.9), we can rewrite (2.9) as:

$$P_{Lidar} = \frac{\rho}{\pi R^2} \frac{P_t}{A_{laser,0}} \cos(\theta) A_s A_{lens}$$

(2.10)

(2.10) can be further simplified by assuming that  $A_s$  is equal to  $A_{laser,0}$ . This is a valid assumption since sensor should cover the over all footprint area at reflector to acquire the maximum power efficiency. In long range detection, we also need to consider the optical absorption in atmosphere which is expressed as  $\exp(-2\alpha R)$  where the  $\alpha$  is the extension rate. Thus, the final LIDAR equation is:

$$P_{Lidar} = \frac{\rho}{\pi R^2} P_T A_s \cos(\theta) e^{-2\alpha R}$$

(2.11)

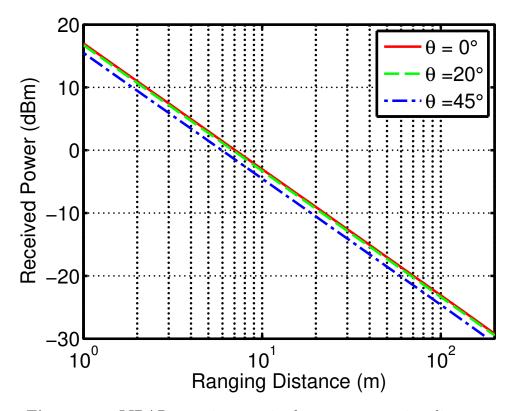

Fig. 2.3 shows the simulation results of (2.11). In this simulation, the laser peak power  $P_t$  is 40W, reflection constant  $\rho$  is 50%, lens area is  $0.00785m^2$  (10-cm diameter focal lens), and extinction rate is 0.227/km. Simulation results shows that the distance R is the dominating factor in this equation, while the incident angle  $\theta$  is minor factor: power degrades 1.5dB as incident angle changing from 0° to 45°.

## 2.2 Transmitter

The transmitter in LIDAR could an array or a single point. The array source utilizes an array of light-emitting diodes (LEDs) or laser diodes (LDs) to diffusely

Figure 2.3: LIDAR equation: received power vs. ranging distance.

illuminate targets. The advantage of array source is the simple optical design and fast measurement speed. However, it usually requires higher power to illuminate multiple targets simultaneously that might induce eye safety issue. This is especially important in consumer and automotive application where the optical power is confined by strict regulation: Class-I eye safety in typical case. In this context, single source with scanning approach can achieve higher SNR but consumes less optical power.

# 2.2.1 Laser Scanning Technique

To date, three major types of laser scanning are proposed in state-of-art LIDAR module. The first type of scanning is by spinning the entire LIDAR module. For example in Ref. [16], the entire module spins at 900 rpm around its vertical axis to generate 360° horizontal field-of-view (H-FoV). The 28.6° vertical field-of-view (V-FoV) is achieved through the well-aligned 64 laser channels. The second type of scanning is based on a fixed laser source and a rotated mirror. In Ref. [5], the laser beam is coaxially targeting at a rotated six-faced polygonal mirror where each facet has a slightly different tilt angle, resulting in a 170° H-FoV and 4.5° V-FoV. The last type of scanning is based on Micro-electro-mechanical systems (MEMS) scanner. In Ref. [17], the laser beam is aimed at a 2-axis MEMS mirror. By electrically driving the facet angle of the MEMS mirror, the laser beam can be aligned with the any desired angle. Although this scanning technique only achieves 15° H-FoV and 11° V-FoV, it demonstrates a possibility for all-in-one LIDAR SoC, manufacturing the transmitter and receiver on a shingle chip. Due to avoiding the mechanical part in module level, this technique has great potential to simplify module design and reduce the cost.

## 2.2.2 Laser Wavelength

The wavelength region utilized in LIDAR is related to the processing technology, fabrication cost, and application. To reduce the possibility of eye damage, almost all LIDAR systems are operated at infrared (IR) region. Typically, two different wavelength regions are considered: 850nm-950nm (near IR) and 1550nm (IR).

NIR (850-950nm): The most common range utilized in LIDAR system since the correlated optical components, i.e., lasers and photodiodes, are easily acquired in conventional CMOS process within this wavelength region. However, because the wavelength region is close to the visible region of human eyes. High power emission is sitll harmful. Therefore, the maximum power at this region is strictly confined for the safety. According to international standard IEC60825-1, the emission limit for Class 1 laser at wavelength 700nm to 1050nm and pulse duration 1-ns to 100-ns is  $2 \times 10^{-7} J$ . Besides, since NIR is the most common used wavelength region, the cross-talk and uncorrelated signal could impact the operation in this region.

IR (~1550nm): a rather common wavelength region because it is out of optical window of silicon. Typical materials that are used to detect this range are InP/InGaAs or germanium (Ge). While InP/InGaAs has higher quantum efficiency, it is very hard to integrated in CMOS technology. On the other side, Ge is compatible with conventional CMOS. However, the optical responsivity of Ge is lower due to its indirect bandgap. Thus, most high-sensitivity PD is InP/InGaAs-based. Since the power at this wavelength is seldom detected by human eye, higher emission power is allowed in Class 1 laser. Also, the atmosphere extinction rate at 1550nm is lower than that at NIR region, which leads the longer detection range.

## 2.3 Photodiodes

Due to the Lambertian reflectance in the nature, intensity of returned pulse is very weak in long-range detection. As depicted in (2.11), with a 40W peak transmitted power, LIDAR can only receives -25dBm return power reflected from object at 100-m distance. To cope with the low intensity power, avalanche photodiodes (APDs) or single-photon avalanche photodiodes (SPADs) are usually utilized as the sensor in receiver.

#### 2.3.1 Avalanche Photodiodes (APDs)

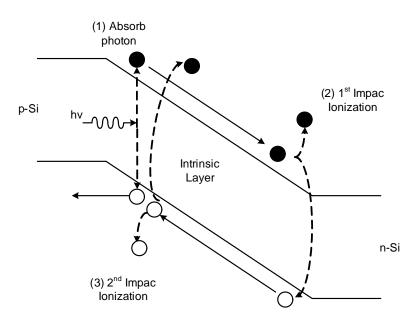

The structure of avalanche photodiodes (APDs) is a conventional p-n junction or p-i-n junction. Through biasing the junction close to breakdown voltage, the avalanche detection can triggered once photon detection. The avalanche process in p-i-n APDs is illustrated in Fig. 2.4. As the photon energy is absorbed, the energy excited electrons from valence to conduction band, creating an electron-hole pair (EHP) in intrinsic region. The electron is accelerated by the high electric field in intrinsic layer, until it gains sufficient energy to excite the second EHP (first impact ionization). The hole generated from first impact ionization is accelerated by electrical field and creates the third EHP (second impact ionization). This positive feedback process amplifies the number of EHPs and generates the optical gain M in the intrinsic layer. The linear relationship between APD's photocurrent and incident optical power is:

$$I_{APD} = M \cdot \eta \frac{q}{h\nu} P_{in} \tag{2.12}$$

where  $\eta$  is quantum efficiency of APDs,  $h\nu$  is photon energy, and  $P_{in}$  is the incident power. Optical gain is proportional to the biasing voltage of APDs. Depending on the device process, the biasing voltage of APD is from 10V to 30V to achieve acceptable optical gain. Operating in such high biasing voltage, a good junction quality is the essential in APD because any non-uniform profile or defects at junction surface would potentially cause diode breakdown and trigger the avalanche mechanism spontaneously.

Figure 2.4: Avalanche process in APD.

## 2.3.2 Single-Photon Avalanche-Photodiodes (SPADs)

Recently, one fast-growing class of APDs, single-photon avalanche-photodiodes (SPADs), are gain increasing interest. Similar to APDs, SPADs amplifier the electrical signal through the avalanche detection in the intrinsic layer. However, since SPADs are biased at Geiger-mode: reverse bias is higher than diode breakdown voltage  $(V_{BD})$ , this device performs a bi-stable output. Only few photons can give rise to a very high number of carriers and induced irreversible avalanche current. Since the gain is very high, the output signal is easily saturated and the intensity information is not preserved at output. Thus, SPAD is a logic photodiodes where its output only records time events of incident photons. The intensity information can be obtained by counting the number of incoming photons during a period of time. Since photocurrent in SPADs is irreversible unless the leakage path is broken, devices need to be quenched every time before the next detection. During this time, SPADs cannot

operate in detection mode. Thus, the time is also called the deadtime of SPADs. Typical length for deadtime is from 10-ns to 100-ns [5, 18] depending on the design of photodiode and quenching circuits.

# 2.4 Front-End Receiver

The purpose of front-end receiver (RX) is to bias photodiodes at proper operating voltage, and convert photocurrent and into a full swing voltage signal. Different PDs need for different RX design. In the following, we will discuss two main RX design: 1) transimpedance amplifier (TIA) that is used in APD-based sensor, and 2) quenching circuit that is used in SPAD-based sensor.

# 2.4.1 Transimpedance Amplifier (TIA)

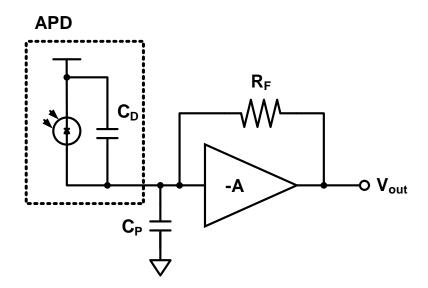

In APD-based sensor, transimpedance amplifier (TIA) is usually utilized for the current-to-voltage conversion through a linear transimpedance gain. Fig. 2.5 shows

Figure 2.5: Schematic of transimpedance amplifier.

one of the most popular TIA: resistor feedback TIA. It contents an operational amplifier (OPAMP) with voltage gain of -A and a feedback resistor  $R_F$ . Assuming an ideal amplifier with unlimited bandwidth, the input impedance  $R_{in}$  of TIA is:

$$R_{in} = \frac{R_F}{A+1} \tag{2.13}$$

and the frequency response of transimpedance  $Z_T$  is:

$$Z_T = -\frac{A}{A+1} R_F \frac{1}{1+sR_{in}C_T}$$

(2.14)

where  $C_T$  is total input capacitance that is the sum of the junction capacitance of APD ( $C_D$ ) and parasitic capacitance at TIA input ( $C_P$ ). Notice that as A increases,  $R_T$  will approach to  $R_F$  and  $R_{in}$  will approach to zero. It is desirable since the bandwidth of TIA is usually dominated by the input pole ( $1/R_{in}C_T$ ). Thus, a higher bandwidth can be achieved with higher amplifier gain. In the real implementation, the gain-bandwidth (GBW) in OPAMP is limited by power consumption and device technology. A trade-off needs to consider between gain and  $\omega_{3dB}$  bandwidth in amplifier. With considering the  $\omega_{3dB}$  of OPAMP, the frequency response of  $Z_T$  is:

$$Z_T(s) = -\left(\frac{A}{A+1}R_F\right) \left(\frac{1}{1+s/(\omega_0 Q) + s^2/\omega_0^2}\right)$$

(2.15a)

$$\omega_0 = \sqrt{\frac{A+1}{R_F C_T T_A}} \tag{2.15b}$$

$$Q = \frac{\sqrt{(A+1)R_F C_T T_A}}{R_F C_T + T_A}$$

(2.15c)

where  $T_A$  is the time constant of amplifier  $(1/\omega_{3dB})$ ,  $\omega_0$  is the resonant frequency, and Q is the quality factor. (2.15) shows that TIA response is a conventional secondorder low-pass response. The maximum flat frequency response is characterized as Butterworth response  $(Q = 1/\sqrt{2})$ . Thus, the optimized  $\omega_{3dB}$  for amplifier is:

$$\omega_{3dB} = 2A/R_F C_T \tag{2.16}$$

The bandwidth requirement for TIA is dependent on the time resolution of timecorrelated single-photon counting (TCSPC). In order to confine power-supply-noise jitter at TIA output within time resolution of TDC channel, the time constant of TIA need to be roughly closed to two significant-bit (LSB). For instance, the TIA bandwidth should be higher than 1.6GHz for a 50-ps time resolution.

Noise performance is another important characteristic in TIA design since it determines the sensitivity of LIDAR sensor. Assuming an ideal photodiode (i.e. noiseless), the optical sensitivity of LIDAR is:

$$\overline{P_{sen}} = \frac{\alpha I_{rms}}{2\rho} \tag{2.17}$$

where  $\alpha$  is random noise margin,  $\rho$  is the responsivity of APD, and  $I_{rms}$  is inputreferred noise of TIA. Generally,  $I_{rms}$  is dominated by resistor thermal noise  $(4kT/R_F)$ over TIA bandwidth. As we recalled the transimpedance response in (2.14), the  $Z_T$ is roughly equal to  $R_F$  as the gain A is much larger than 1. Thus, we can use higher  $R_F$  to increase  $Z_T$  and suppress  $I_{rms}$  in the same time. However, it also reduces the TIA bandwidth. A trade-off among gain, noise, and bandwidth needs to consider in design.

In general RX design, a limiting amplifier (LA) is cascaded after TIA to amplify TIA output signal to a reliable signal level. Bandwidth of LA is larger than the TIA for maintaining the overall bandwidth. Noise performance, however, is not critical since the effective input-refer noise from LA is divided by  $Z_T$ . The overall  $I_{rms}$  of RX is dominated by TIA.

### 2.4.2 Quenching Circuit

In SPAD-based sensor, output of SPADs is inherently a rail-to-rail signal, which can be directly processed with digital circuit. A simple CMOS inverter is cascaded after SPAD for isolating the input noise and parasitic loading. However, due to the bi-stable characteristics (once the photocurrent is trigger by photons, it cannot be terminated), a queching circuit (QC) is applied to disconnect photocurrent path (quench) and reset SPAD each time before next detection.

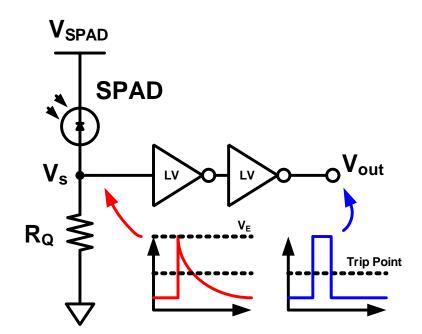

The simplest QC is shown in Fig. 2.6 where a quenching resistor  $(R_Q)$  is in series with SPAD. In dark light condition, SPAD is biased at Geiger-mode: the sensing node  $(V_s)$  is pulled to ground by  $R_Q$ , and SPAD operation voltage  $V_{SPAD}$ is higher than junction breakdown voltage  $V_{BD}$  by an excessive bias voltage  $V_E$ . As a photon is captured, avalanche photocurrent will be triggered, flow through  $R_Q$  and pulls  $V_s$  up until  $V_s$  reaches  $V_E$  and quenches the avalanche current. After SPAD enters quenching mode, RQ start to discharge the excessive carriers in the junction of PD and pull the  $V_s$  back to ground. The discharge rate is dependent on the value of  $R_Q$  that needs to be customized according to the different SPAD design. A fast discharge rate may trigger an unwanted avalanche process or so-called "afterpulse" in SPAD [19]. To prevent afterpulse, PD has to be held-off at a low biasing point (lower than  $V_{BD}$ ) for a sufficient time for releasing carriers trapped in deep level before recharging. After the junction carriers are completely depleted, SPAD is recharged and back to Geiger-mode. During this process (hold-off time and recharging time), SPAD cannot work for detection. So it is also called dead time for

Figure 2.6: Schematic of typical passive quenching circuit (PQC).

SPADs. The passive quenching circuit (PQC) described above usually require long quenching time since it needs a large  $R_Q$  to sustain enough hold-off time. The large  $R_Q$  makes a large time constant in recharging process. Thus, deadtime takes around 40-ns to 100-ns.

The long quenching time can be improved in active quenching circuits (AQC). In ref [19], an AQC is proposed to shorten the quenching time through two-step charge rate (Fig. 2.7). In this design, the charge rate is different between hold-off time and recharge time. Upon photon detection, the  $V_s$  node is pulled-up by SPAD current, making SPAD quenched. Since the NOR gate does not switch at this moment,  $V_s$ is discharged slowly through  $M_1$  to prevent afterpulse effect. During this time, the discharging current  $I_{QCH}$  is set to be smaller than so-called SPAD latching current, it would eliminate the probability of afterpulse and gives time to extract deep-level

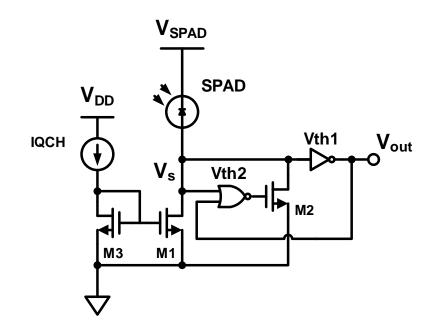

**Figure 2.7:** Schematic of two-step discharging rate active quenching circuit (AQC) [19].

carriers. As  $V_s$  is lower than  $V_{TH2}$ , it would switch the NOR gate and turn on  $M_2$ . A faster discharge rate is presented in recharging time. The proposed active quenching circuit shrinks dead time to 6-ns.

# 2.5 Time-to-Digital Converter (TDC)

Time-to-digital converter refers to a data interface where the input is a timing event and the output is a digital word corresponding to the magnitude of the timing event with quantization error:

$$T_{TDC} = B_{out} \cdot T_{LSB} + \epsilon \tag{2.18}$$

where  $B_{out}$  is the digital output word,  $T_{LSB}$  is the time interval of least significant bit or time resolution, and  $\epsilon$  represents the quantization error. There are many approaches for converting/quantizing a time-event into its digital equivalent. However, in this work we will focus on the digital approach since it typically supports higher dynamic range (DR). In addition, digital TDC leverages the benefits of deeply scaled CMOS technology. Higher TDC resolution can be achieved due to the higher transistor frequency and shorter gate delay in short channel devices.

DR is an important specifications in LIDAR, especially in automotive application. For high performance driving assistance LIDAR, the detection range is up to 100-m distance with the resolution of few centimeters. It is corresponding to 0.667-us maximum counting range and 100-ps time resolution in time-domain (DR > 76dB). In order to reach high DR but also maintain good power efficiency, the multi-stage conversion is typically utilized: front stages are responsible for DR extension while the later stages provide high resolution for TDC. Time resolution of each stage varies with the different specifications and applications. However, a general rule of threestage conversion can be applied:

**Coarse TDC (CTDC):** CTDC is responsible for the highest-level time conversion where its DR represents the DR of whole TDC. Since the fine conversion will be resolved in the later stages, the resolution of CTDC is equal to the dynamic range of the next stage. Counter-based TDCs are the most common CTDC architectures where the counting rate is triggered by an external clock. The resolution of general CTDCs is few nanosecond or more. The simplest and also most prevalent counter-based TDC is ripple counter due to the simple design complexity and high DR (this will be discussed further). In ripple counter, 1-bit DR extension can be simply achieved by adding one additional logic register.

Fine TDC (FTDC): FTDC is responsible for the second-stage conversion. DR

is confined by the LSB of CTDC. Delay-line TDC (DL-TDC) is the most popular FTDC architecture where the time event is measured according to the number of stage of propagation delay. Resolution of FTDC is limited by the gate delay of the delay cell. To compensate variation of delay time due to PVT, the delay line are usually controlled by a feedback loop control such as DLL or PLL.

Sub-Fine TDC (S-FTDC): S-FTDC provides time resolution shorter than the gate delay of technology (sub-ps). Several state-of-art has been proposed in previous literature, including Vernier delay-line TDC [20], Successive Approximation (SAR) TDC [21], and pipelined TDC [22, 23]. The accuracy of resolution in S-FTDC mainly relies on device matching and sizing ratio. Approaching of Feedback-loop control cannot be applied here since the resolution is too high. Thus, S-FTDC demands higher process control and the operation range of the circuit is limited . In addition, sub gate-delay resolution usually achieved through iteration of conversions that takes longer conversion time and consumes higher power than CTDC and FTDC. S-FTDC is mainly used in high-resolution TCSPC such as that used in positron emission tomography (PET) and fluorescence lifetime (FLIM), while the performance and power is not suitable for conventional LIDAR application.

# 2.5.1 Coarse TDC (CTDC) Counting Scheme

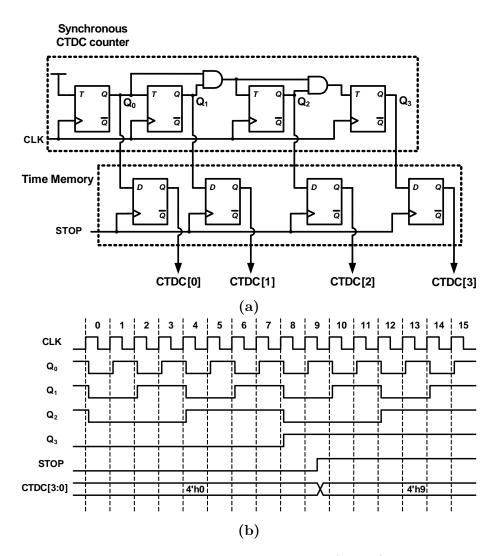

As we described in previous section, the simplest CTDC is a ripple counter. In this design, a N-bit ripple counter contents N cascade logic registers where the clock trigger of each register is connected to the output Q of previous one. The advantage of ripple counter is small layout size and low power consumption. Therefore, it is popular in pixel-based CTDC design. The problem of ripple counter is that the counting signals are not synchronous. It causes ambiguous edges at counting transition and jeopardize time accuracy of counter. A synchronous version is proposed to solve this issue (Fig. 2.8). In the design, the toggle flip-flops (TFFs) are used to generate counting bits. All TFFs are triggered by one clock source. Generally, coarse counter signals ( $Q_0 - Q_3$ ) are sent into a time memory. Once STOP signal rise up, counter signals are latched in time memory as CTDC output CTDC[3:0].

In LIDAR sensor, since the STOP signal comes from the front-end RX, it can be trigger asynchronously once photon detection. Therefore, the design in Fig. 2.8 encounters a serious problem with the asynchronous trigger in time memory. The asynchronous trigger induces inevitable time violation in time memory and causes the probability of missing code at TDC output. For example, if STOP is triggered while counter value transits from 4'b0001 to 4'b0010, time memory could latches counting value as 4'b0000 (if bit[0] transits earlier than bit[1]) or 4'b0011 (if bit[1] transits earlier than bit[0]). The either cases can cause DNL larger than  $\pm 2$ -LSB.

An alternative binary coding approach, the reflected binary code counting, which is also well-known as Gray code counting, is utilized to solve this problem. In Gray code counting, the two successive values differ in only one bit. For example, three and four in decimal is represented as 4'b0001 and 4'b0011 in Gray code. As STOP is triggered during the transition between these two values, there is a 50% probability to latch 4'b0001 and 4'b0011, respectively, and DNL is always smaller than  $\pm 0.5$ -LSB.

In binary system, Gray code and binary code are transferable through a simple logic process. The converting from N-bit binary code to Gray code is:

$$G[N-1] = B[N-1]$$

$$G[i] = B[i+1] \oplus B[i] \ (i < N-1)$$

(2.19)

**Figure 2.8:** A 4-bit synchornous up-counter using T (toggle) flip-flops with a 4-bit time memory: (a) schematic, (b) counting waveform.

And the converting from N-bit Gray to binary code is:

$$B[N-1] = G[N-1]$$

$$B[i] = B[i+1] \oplus G[i] \ (i < N-1)$$

(2.20)

Thus, we can use Gray code counter to void missing code in asynchronous time memory and convert it back to binary code in synchronous readout data circuit.

## 2.5.2 Fine TDC (FTDC) Counting Scheme

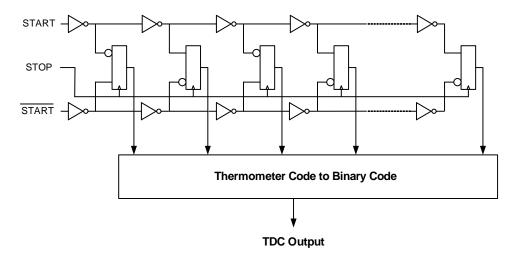

In two-stage TDC architecture, FTDC is responsible for the least significant bit in TDC. To achieve centimeter-level depth resolution in LIDAR, the TDC needs to support time resolution smaller 100-ps. In this context, delay-line based TDCs (DL-TDCs) are generally preferred. In the following, we will discussed several state-of-art DL-TDCs:

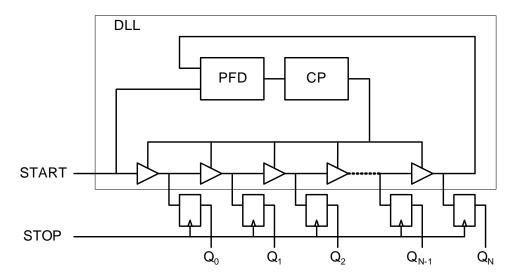

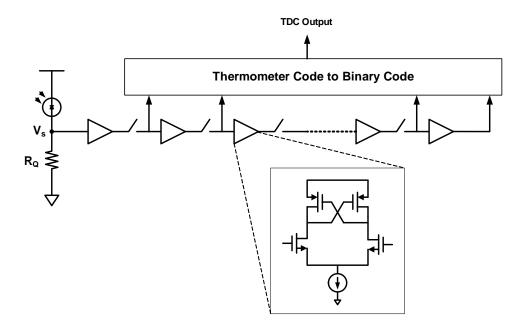

## a. Tapped DL-TDC

Fig. 2.9 shows the schematic of Tapped Delay Line TDC [24]. In the design, a rising edge signal is injected into a delay chain through the START pin that defines the start time of TDC. Assuming the gate delay of each delay cell is  $\Delta t_D$ , the time spends for the START rising edge propagating from the START pin to N-th delay cell output is:

$$T_{TDC} = \Delta t_D \cdot N \tag{2.21}$$

The transition of each node in DL is sensed by digital flip-flops. Once the STOP triggers, state of propagation delay will be latched. Since the signal propagation is from the left to the right, the latched data is a thermometer-code and interpret the time difference between START and STOP.

To avoid PVT variation in delay line, the delay cell is biased with a selfcalibrating scheme. In Fig. 2.9, the calibration is implemented by a delay-looked-loop (DLL). By comparing the phase difference between START and START', the delay time can be adapted trough an periodic START clock. Calibration can be also implemented in digital manner. Fig. 2.10 shows the another state-of-art Tapped DL-TDC, which is applied in am all-digital-PLL (ADPLL) circuit[25]. In this design, a known

Figure 2.9: Schematic of delay-line TDC (DL-TDC) embedded in DLL.

Figure 2.10: Tapped delay-line TDC with self-calibrating circuit [25].

time interval is resolved by TDC. Based on the averaged TDC output (averaging to remove random jitter), the delay time of unit delay cell can be acquired. Notice that differential DLs are utilized here to subtract out common-mode noise. A strongarm sense-amplifier (SA) is used to sense the falling and rising on each node in DLs. Since inverter gates are used as unit delay cell, the polarization of sensing input of flip-flops is also inverted stage-by-stage. This design achieves 20-ps resolution in 90nm technology.

## b. Gated Delay-Line TDC (GDL-TDC)

Fig. 2.11 shows a 4-bit GDL-TDC which is implemented in a pixel-based TDC design [26]. Unlike Tapped delay-line, the GDL latches the propagation delay by gating the signal propagation in DL (disconnecting delay cells). Since no flip-flop is required in the circuit, the smaller layout size is achievable. It is a great appeal to those designs which have stringent area budget, i.e., pixel-based TDC. However, the gating operation might induce metastable nodes in delay line and cause missing code results. This TDC achieves 111-ps time resolution in CMOS 130nm Technology.

This design also introduces a well-known configuration, "reverse start-stop scheme" where the START signal is triggered by photon detection event and the STOP signal

Figure 2.11: Gated delay-line TDC [26].

is triggered by a successive edge of coarse reference clock. The main advantage of the scheme is low power consumption. Since FTDCs are only initiated upon photon detection and stopped by a successive reference clock edge, the power consumption could be minimized. The time is counted from photon detection to the end of one measurement cycle. The TDC output in reverse start-stop scheme is:

$$T_{TDC} = T_0 - (T_{CDTC} + T_{FTDC})$$

(2.22)

where  $T_0$  is the period of one measurement cycle.

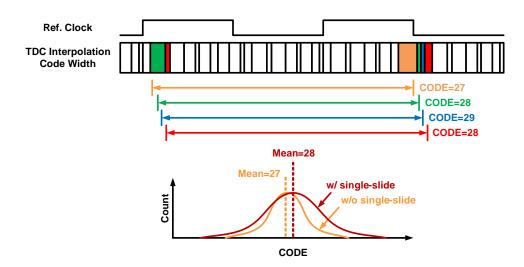

## c. Gated Ring Oscillator TDC (GRO-TDC)

GRO-TDC utilized a gated-ring-oscillator (GRO) as the timing counter. Fig. 2.12 shows a 3-bit four-stage GRO-TDC [9]. The TDC supports reverse start-stop scheme. The four-stage GRO is gated/frozen at the beginning of the operation. Once the photon is detected, it starts the oscillating until the next rising edge of global

Figure 2.12: Gated-ring-oscillator (GRO) TDC [9].

clock arrives. The number of the oscillating cycle is counted by a 7-bit ripple counter, and the GRO itself provides 3-bit fine resolution. The advantage of GRO is that its dynamic range can be doubled by adding an additional bit number in ripple counter, while it needs two times of area for DL-TDC. This TDC achieves 55-ps resolution in 130nm CMOS Technology. The TDC average power is 38uW and the peak power is 275uA.

### 2.5.3 Sliding Scale Technique

Sliding scale technique is first proposed by E. Gatti [27] to improve the linearity performance in ADC systems. This technique is mainly to minimize the DNL that is caused by the unequal quantization through the averaging results. In this design, a random but known analog noise is continuously added to the ADC input signal and subtracted from the digital output. As the same quantity is added and subtracted, the overall results do not change. However, since the conversion of the same input signal is performed in different regions of converter range, depending on the random noise value, the linearity of the averaged output is improved.

In TDC, sliding scale technique is inherently provided if START and STOP signals are asynchronous to the reference clock [20]. As shown in Fig. 2.13, the time events of START and STOP are converted in different interpolator ranges, respectively. The time interval, i.e. gate delay, between START and reference clock results in a random noise, which is added to STOP conversion, but it will be eliminated in

Figure 2.13: Sliding scale technique in TDC.

the final conversion:

$$T_{START,1} = T_{START} + T_{noise}$$

$$T_{STOP,1} = T_{STOP} + T_{noise}$$

$$T_{TDC} = T_{STOP,1} - T_{START,1}$$

$$= T_{STOP} - T_{START}$$

$$(2.23)$$

Since the conversion range is random, the effective DNL is improve due to the averaging effect. The improvement of linearity is paid in terms of higher quantization noise and lower single-shoot precision. In fact, the sliding scale transforms the nonlinearity into measured timing jitter. As we utilize two interpolators to convert START and STOP, the quantization noise is:

$$\rho_q = \sqrt{\frac{LSB_{START}^2}{12} + \frac{LSB_{STOP}^2}{12}} = \frac{LSB}{6}$$

(2.24)

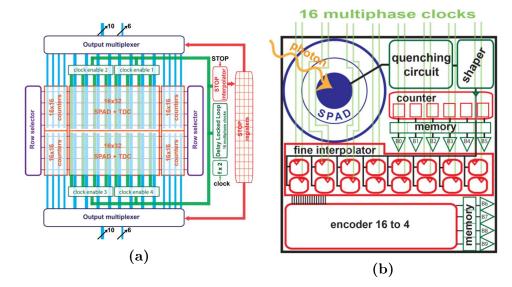

#### 2.6 Sensor Integration