## LOW POWER, HIGH PSR CMOS VOLTAGE REFERENCES

## A Thesis

by

## NASHIRU ALHASSAN

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## MASTER OF SCIENCE

Chair of Committee, Edgar Sánchez-Sinencio

Committee Members, Rainer J. Fink

Kamran Entesari

Harlan Rusty Harris

Head of Department, Miroslav M. Begovic

May 2016

Major Subject: Electrical Engineering

Copyright 2016 Nashiru Alhassan

#### **ABSTRACT**

With integration of various functional modules such as radio frequency (RF) circuits, power management, and high frequency digital and analog circuits into one system on chip (SoC) in recent applications, power supply noise can cause significant system performance deterioration. This makes supply noise rejection of the embedded voltage reference crucial in modern SoC applications. Also the use of resistors in bandgap voltage references makes them less suitable for modern low power and portable applications.

This thesis introduces two resistorless sub-1 V, all MOSFET references. The goal is to achieve a high power supply rejection (PSR) over a wide bandwidth not achieved in previous works. This high PSR over wide bandwidth is achieved by using a combination of a feedback technique and an innovative compact MOSFET low pass filter. The two references were fabricated in a standard 0.18 µm CMOS process.

The first reference uses a composite transistor in subthreshold to produce a proportional-to-absolute temperature (PTAT) voltage which is converted to a current used to thermally compensate the threshold voltage of a MOSFET in saturation. The second references uses *dynamic-threshold voltage MOSFET* (DTMOS) to produce a PTAT voltage which is converted to a current used to thermally compensate the threshold voltage of a MOSFET in saturation.

The measurement shows that both references consumes a sub-1  $\mu$ W power across their entire operating temperatures. The first reference achieves a PSR better than 50 dB for frequencies of up to 70 MHz and a 20 ppm/°C temperature coefficient (TC) for

temperatures from -35 °C — 80 °C. It has a compact area of 0.0180 mm² and operates on a supply of 1.2 V — 2.3 V.

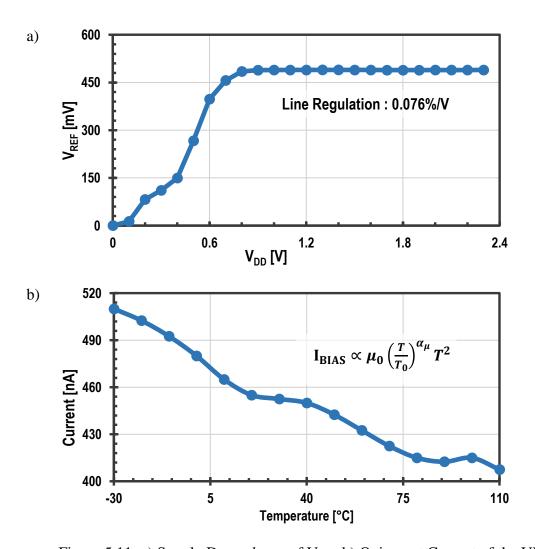

The second reference achieves a PSR better than 50 dB for frequencies of up to 60 MHz. This reference achieves a TC of 9.33 ppm/°C after trimming for temperatures from -30 °C — 110 °C and a line regulation of 0.076 %/V for a step from 0.8 V to 2 V supply voltage with 360 nW power consumption at room temperature. It has a compact area of 0.0143 mm<sup>2</sup>.

#### **ACKNOWLEDGEMENTS**

My foremost gratitude is to the almighty Allah whose mercies have carried me throughout this journey. I will also like to thank my family for the constant love and support they have shown me in these past years. Their endless care and support have made living so far from home bearable.

I am exceedingly thankful to my advisor, Prof. Edgar Sánchez-Sincencio, for the constant guidance and support throughout my time at Texas A&M University. Thank you for being the greatest advisor I could ever wish for.

Thanks also go to Dee Hunter, Tuli Dake, Benjamin Sarpong, and all the pioneers of the Texas Instruments African Analog University Relations Program (TI-AAURP) for making my graduate education possible. It has been an exciting experience.

I also want to extend a special gratitude to Zekun Zhou, for being a teacher and a colleague throughout this research process. I am grateful to all the members of the Analog and Mixed Signal Center of Texas A & M University, for making working with them a pleasure.

Thanks to Patrick for reading and editing this thesis in the midst of all his homework and assignments. I will be remiss not to thank Hubert, Ntiamoah and Umar for their wonderful friendship and for being the best roommates a person could ever ask for.

# TABLE OF CONTENTS

|                                                   | Page |

|---------------------------------------------------|------|

| ABSTRACT                                          | ii   |

| ACKNOWLEDGEMENTS                                  | iv   |

| TABLE OF CONTENTS                                 | v    |

| LIST OF FIGURES                                   | viii |

| LIST OF TABLES                                    | xii  |

| 1. INTRODUCTION TO VOLTAGE AND CURRENT REFERENCES | 1    |

| 1.1 Semiconductor Basics                          | 1    |

| 1.1.1 Basic Semiconductor Effects                 | 2    |

| 1.1.2 Threshold Voltage                           | 6    |

| 1.1.3 Carrier Mobility                            | 10   |

| 1.2 Current References                            | 11   |

| 1.2.1 PTAT Current References                     | 12   |

| 1.2.2 CTAT Current References                     | 14   |

| 1.2.3 Temperature-Independent Current References  | 16   |

| 1.2.4 PTAT <sup>2</sup> Current References        |      |

| 1.3 Voltage References                            | 21   |

| 1.3.1 Types of Voltage References                 | 21   |

| 1.3.2 Curvature-Correction Techniques             | 25   |

| 1.4 Definitions and Metrics                       |      |

| 1.4.1 Initial Accuracy                            | 31   |

| 1.4.2 Temperature Coefficient (TC)                | 32   |

| 1.4.3 Thermal Hysteresis                          | 33   |

| 1.4.4 Long-Term Stability                         | 34   |

| 1.4.5 Power Supply Rejection (PSR)                |      |

| 1.4.6 Line regulation                             |      |

| 2. CMOS BANDGAP VOLTAGE REFERENCES                | 36   |

| 2.1 Bipolar Transistors (BJT) in CMOS             |      |

| 2.2 VEB Temperature Characteristics               |      |

| 2.3 Commercial Voltage Reference ICs              |      |

| 2.4 The Classical CMOS Bandgap Reference          |      |

| 2.5 Design of Sub-1 V CMOS Bandgap Reference      | 46   |

| 2.5.1 Circuit Overview                            | 46   |

| 2.5     | 5.2 Curvature Compensation                       | 47  |

|---------|--------------------------------------------------|-----|

| 2.5     | 5.3 PSR Improvement                              | 50  |

| 2.5     | 5.4 Op-Amp                                       | 52  |

| 2.5     | 5.5 Startup                                      |     |

| 2.5     | 5.6 Experimental Results                         | 55  |

| 2 431   | ALL MOREET VOLTAGE DEFENDICE WITH 70 DD DRD O    |     |

|         | ALL-MOSFET VOLTAGE REFERENCE WITH -50 DB PSR @   | 50  |

| 80 1    | MHZ FOR LOW POWER SOC DESIGN                     | 58  |

| 3.1 N   | Motivation and Overview                          | 58  |

| 3.2 A   | Architecture and Design                          | 59  |

| 3.2     | 2.1 PTAT Voltage Generator                       | 62  |

|         | 2.2 Self-Biased Current Source                   |     |

| 3.2     | 2.3 Loop Compensation                            | 66  |

| 3.2     | 2.4 Reference Generator                          | 66  |

| 3.2     | 2.5 PSR Improvement                              | 69  |

| 3.2     | 2.6 Trimming Circuit                             | 69  |

| 3.3 I   | Design Considerations                            | 70  |

| 3.3     | 3.1 Channel Length Modulation                    | 70  |

| 3.3     | 3.2 Process Variation                            | 71  |

| 3.3     | 3.3 Dynamic Range                                | 72  |

| 3.4 7   | Temperature Compensation                         | 72  |

|         | Design of the Proposed Voltage Reference         |     |

|         | Simulation Results                               |     |

| 4 A N.T | ALL MORPET CLID 1 V VOLTA OF DEFEDENCE WITH A 51 |     |

|         | ALL-MOSFET SUB-1 V VOLTAGE REFERENCE WITH A -51  | 0.1 |

| aВ      | PSR UP TO 60 MHz DESIGN                          | 81  |

| 4.1 N   | Motivation and Overview                          | 81  |

|         | Proposed Reference Voltage Architecture          |     |

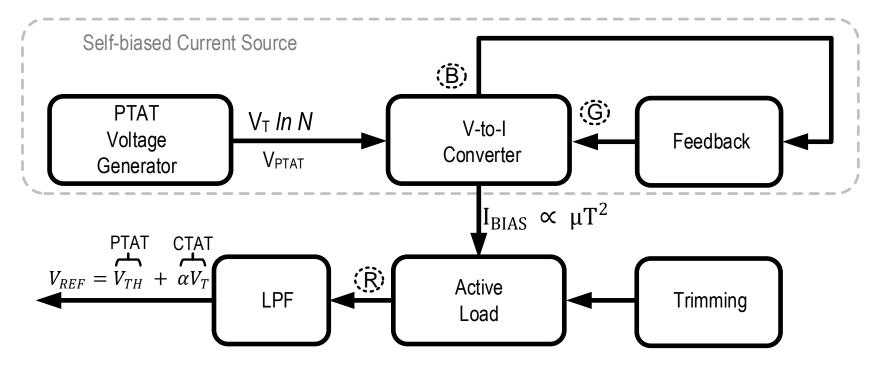

|         | 2.1 Conceptual Block Diagram                     |     |

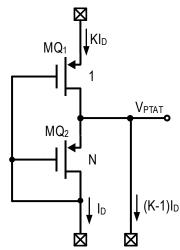

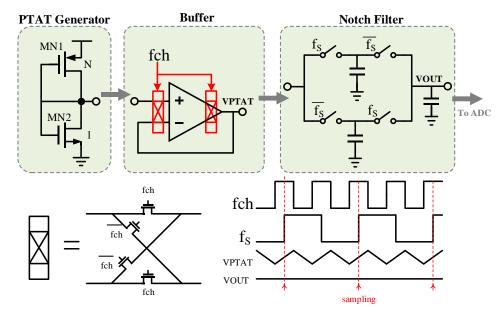

|         | 2.2 PTAT Voltage Generator                       |     |

| 4.2     | 2.3 Self-Biased Current Source                   |     |

| 4.2     | 2.4 Startup Circuit                              |     |

| 4.2     | 2.5 Reference Generator and Leakage Compensation |     |

| 4.2     | 2.6 PSR Improvement                              |     |

| 4.2     | 2.7 Compact MOSFET Low Pass Filter (LPF)         |     |

|         | Design Considerations                            |     |

| 4.3     |                                                  |     |

|         | 3.2 Process Variation                            |     |

| 4.3     | 3.3 Dynamic Range                                |     |

|         | Femperature Compensation                         |     |

|         | Simulation Results                               | 103 |

| 5. EXPERIMENTAL RESULTS                                                                                    | 108 |

|------------------------------------------------------------------------------------------------------------|-----|

| 5.1 Setup for Testing the VRs                                                                              | 108 |

| 5.2 Experimental Results An All-Mosfet Voltage Reference With -50 dB PSR @ 80 Mhz For Low Power Soc Design | 112 |

| 5.3 Experimental for the All-MOSFET Sub-1 V Voltage Reference with a - 51 dB PSR up to 60 MHz              | 116 |

| 6. CONCLUSIONS                                                                                             | 122 |

| REFERENCES                                                                                                 | 124 |

| APPENDIX                                                                                                   | 131 |

# LIST OF FIGURES

|                                                                                                                                                                                                                                                  | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 1.1: Band-gap of Silicon Dependence on Temperature                                                                                                                                                                                        | 3    |

| Figure 1.2: a) Temperature Dependence of Electron Concentration $n_0$ in n-type Si for four values of net doping. Also shown is the Temperature Dependence of $ni$ . b) Temperature Dependence of Normalised Electron Concerntration $n_0/N_D$ . | 5    |

| Figure 1.3: a) Temperature Dependence of Threshold Voltage of NMOS (L=2)                                                                                                                                                                         | 10   |

| Figure 1.4: PTAT Current Generator                                                                                                                                                                                                               | 14   |

| Figure 1.5: CTAT Current Generator using V <sub>BE</sub>                                                                                                                                                                                         | 15   |

| Figure 1.6: Temperature-Independent Current Reference a) Concept and b) Implementation                                                                                                                                                           | 17   |

| Figure 1.7: CMOS PTAT <sup>2</sup> Current Reference                                                                                                                                                                                             | 20   |

| Figure 1.8: Categories of Voltage References                                                                                                                                                                                                     | 22   |

| Figure 1.9: Zener Diode References a) Zener Diode as Shunt Regulator b) Thermally Compensated Breakdown Zener Diode                                                                                                                              | 24   |

| Figure 1.10: Conceptual Implementation of a First-Order Reference a)  Voltage-Mode b) Current-Mode                                                                                                                                               | 27   |

| Figure 1.11: Squared PTAT Curvature-Correction a) Typical Temperature Dependence b) Implementation Concept                                                                                                                                       | 29   |

| Figure 1.12: Temperature Dependence of Piecewise-Linear Curvature Corrected Bandgap                                                                                                                                                              | 30   |

| Figure 1.13: Different Methods for TC Calculation                                                                                                                                                                                                | 33   |

| Figure 2.1: CMOS BJTs a) Lateral NPN b) Vertical PNP                                                                                                                                                                                             | 38   |

| Figure 2.2: Types of Commercial Monolithic Voltage References                                                                                                                                                                                    | 41   |

| Figure 2.3: A CMOS Bandgap Reference (The Brokaw Cell)                                                                                                                                                                                           | 45   |

| Figure 2.4 BGR Curvature Compensation a) Concept b) Implementation                                                                                                                      | 49         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

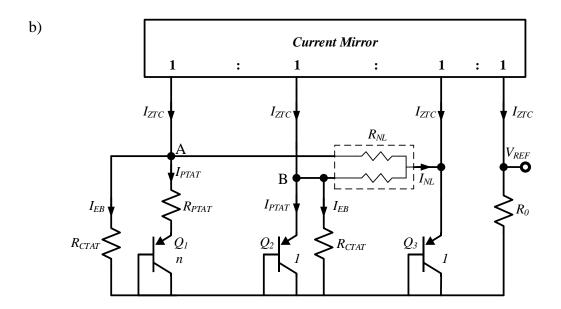

| Figure 2.5: The Proposed Bandgap Reference (BGR)                                                                                                                                        | 50         |

| Figure 2.6: PSR Improvement Concept                                                                                                                                                     | 53         |

| Figure 2.7: Op-Amp for BGR                                                                                                                                                              | 54         |

| Figure 2.8: Measured Temperature Dependence of the Proposed BGR                                                                                                                         | 56         |

| Figure 2.9: Measured PSR of Output BGR                                                                                                                                                  | 56         |

| Figure 3.1: The Conceptual Bock Diagram of the Proposed VR Circuit                                                                                                                      | 61         |

| Figure 3.2: Composite Transistor PTAT Voltage Generator                                                                                                                                 | 63         |

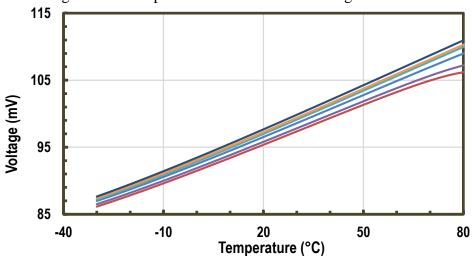

| Figure 3.3: V <sub>PTAT</sub> across Process Corners                                                                                                                                    | 63         |

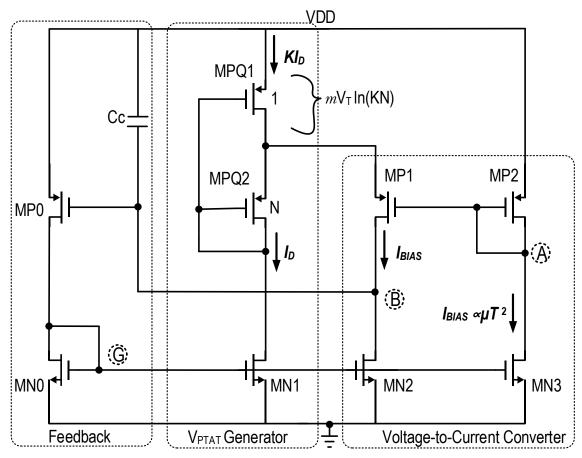

| Figure 3.4: Self-Biased Current Source                                                                                                                                                  | 64         |

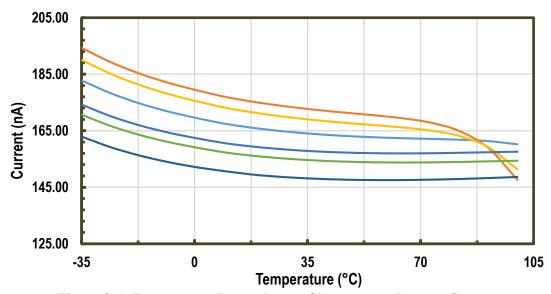

| Figure 3.5: Temperature Dependence of I <sub>BIAS</sub> across Process Corners                                                                                                          | 65         |

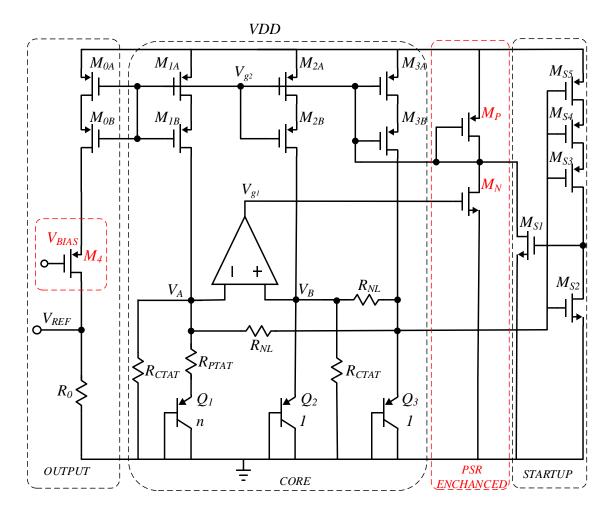

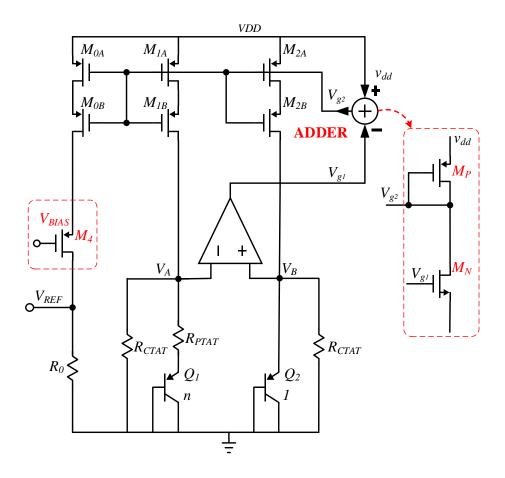

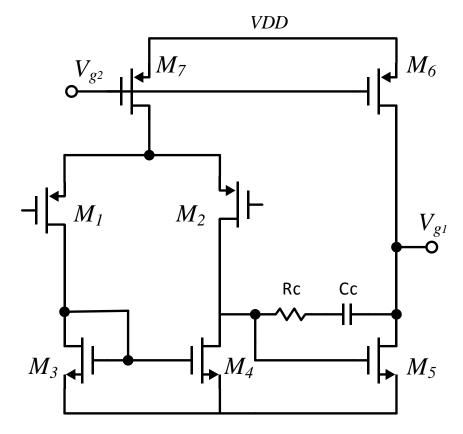

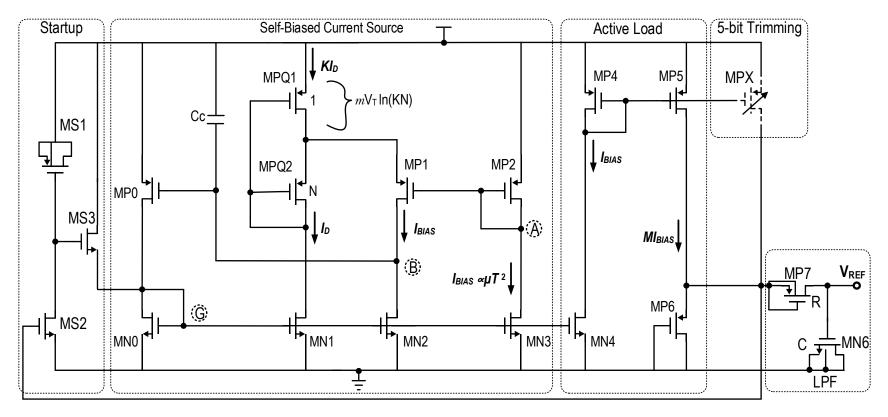

| Figure 3.6: Proposed VR Circuit                                                                                                                                                         | 68         |

| Figure 3.7: Trimming Circuit                                                                                                                                                            | 70         |

| Figure 3.8: Simulation of V <sub>REF</sub> for Various Supply Voltages                                                                                                                  | 76         |

| Figure 3.9: Monte Carlo Simulation for Untrimmed Reference for -20 °C to 100 °C                                                                                                         | 7 <i>6</i> |

| Figure 3.10: Monte Carlo Simulation @27 °C a) Untrimmed b) Trimmed                                                                                                                      | 77         |

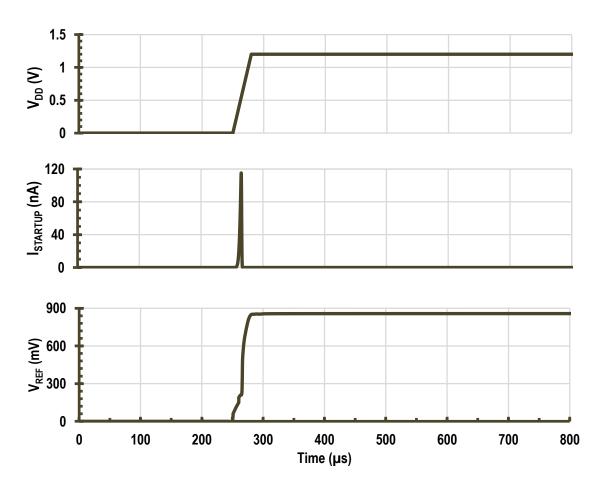

| Figure 3.11: Startup Simulation                                                                                                                                                         | 78         |

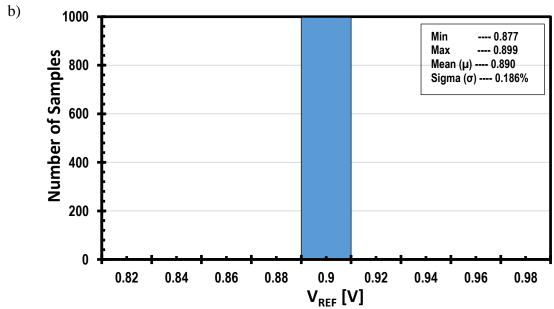

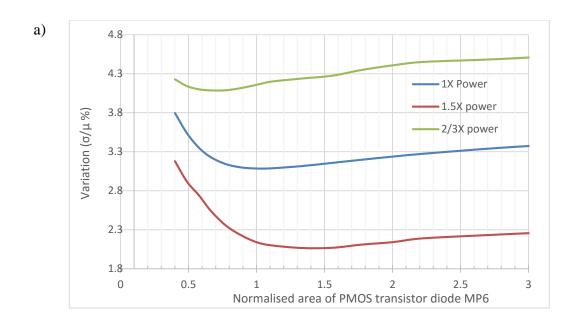

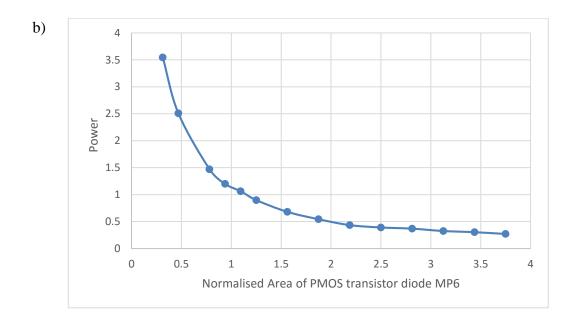

| Figure 3.12: a) Accuracy of Reference Voltage vs. Area at Different Power Levels and b) the area of MP6 and Corresponding Power for 3.15% Accuracy and 19 ppm.                          | 79         |

| Figure 3.13: Simulated PSR of Output VR                                                                                                                                                 | 80         |

| Figure 4.1: The Basic Concept of the Proposed VR                                                                                                                                        | 85         |

| Figure 4.2: Cross Section of a DTMOS Transistor and Schematic Connection b) PTAT Generation from DTMOS c) Simulated Temperature Characteristics of DTMOS and Corresponding PTAT Voltage | 87         |

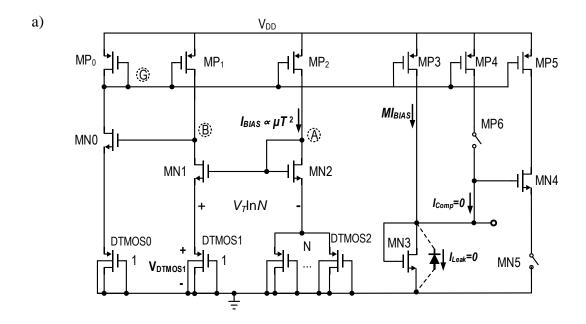

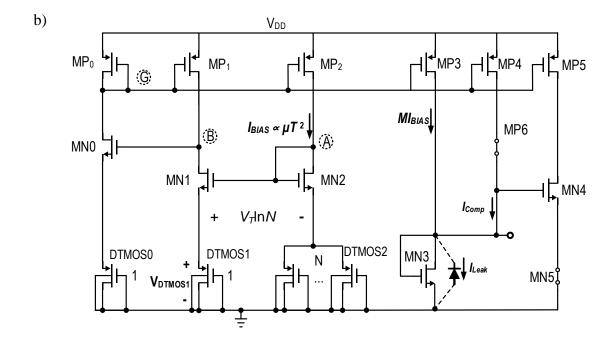

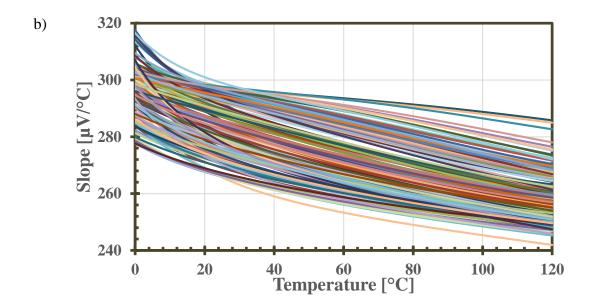

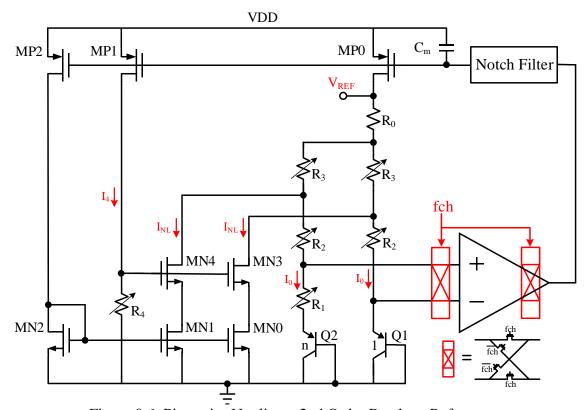

| Figure 4.3: Proposed VR circuit                                                                                          | 90  |

|--------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 4.4: Leakage Compensation Configuration a) Low Temperature and b) High Temperature                                | 94  |

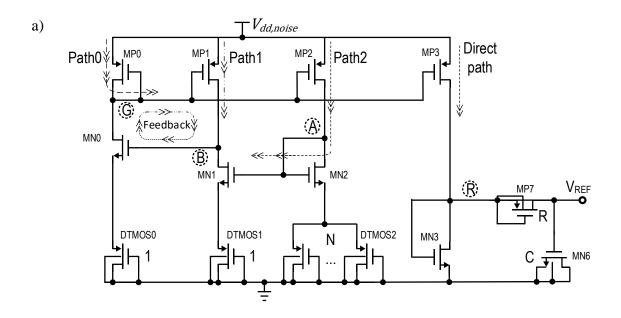

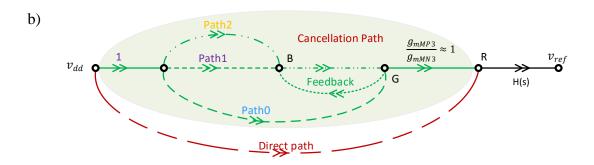

| Figure 4.5: Power Supply noise Paths at (a) and Small Signal Diagram for PSR at (b)                                      | 97  |

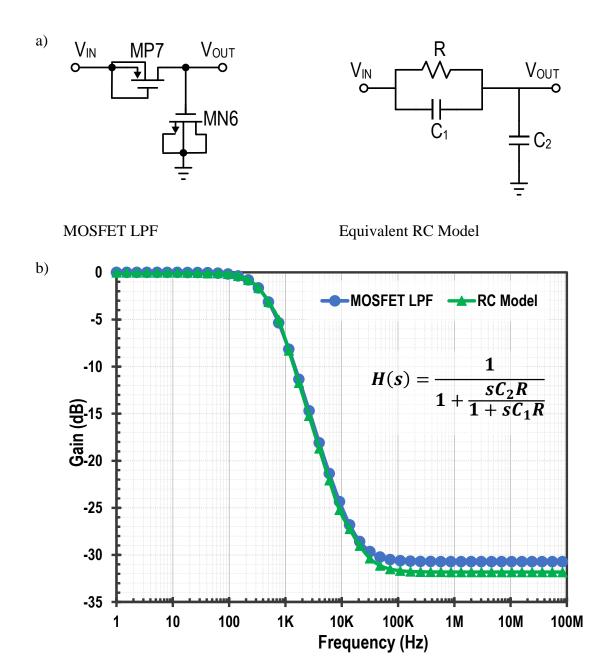

| Figure 4.6: The compact MOSFET LPF and Equivalent RC Model along with b) the MOSFET LPF and Equivalent RC Model Response | 99  |

| Figure 4.7: Simulation of V <sub>REF</sub> for Various Supply Voltages                                                   | 104 |

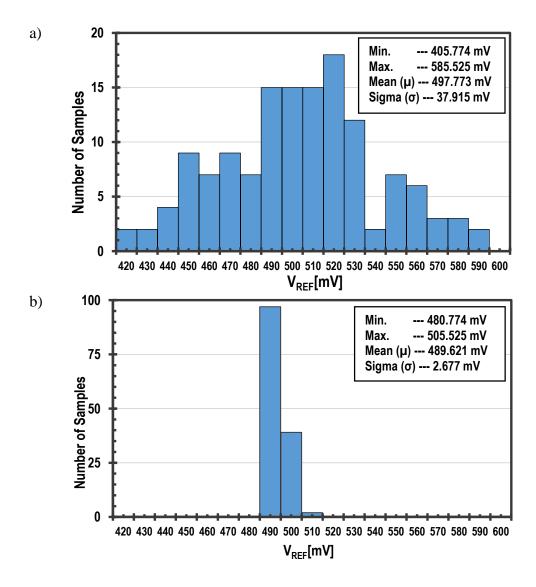

| Figure 4.8: Monte Carlo Simulation for $V_{REF}$ a) Untrimmed VREF @ 27 °C and b) Trimmed VREF @ 27 °C                   | 105 |

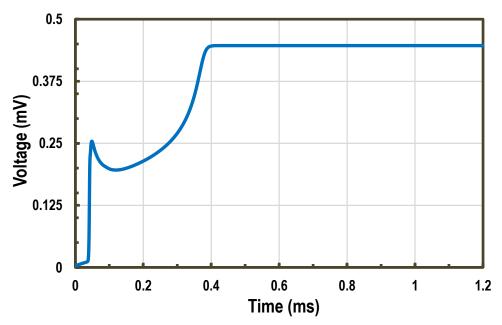

| Figure 4.9: Simulation Results for Start-Up of the VR                                                                    | 106 |

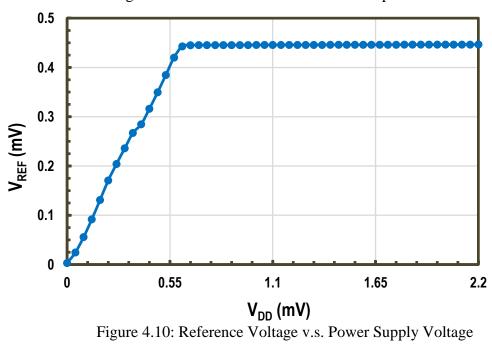

| Figure 4.10: Reference Voltage v.s. Power Supply Voltage                                                                 | 106 |

| Figure 4.11: Simulated PSR of Output VR                                                                                  | 107 |

| Figure 5.1: DC Power Supply for VR                                                                                       | 108 |

| Figure 5.2: The Laboratory Setup for Testing                                                                             | 110 |

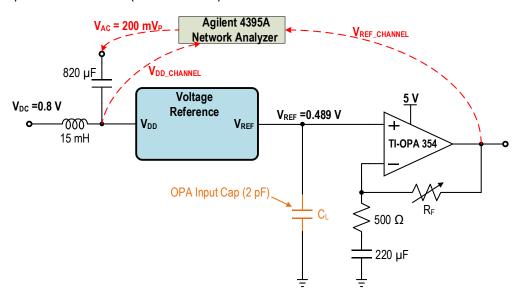

| Figure 5.3: PSR and Temperature Stability Measurement Setup                                                              | 111 |

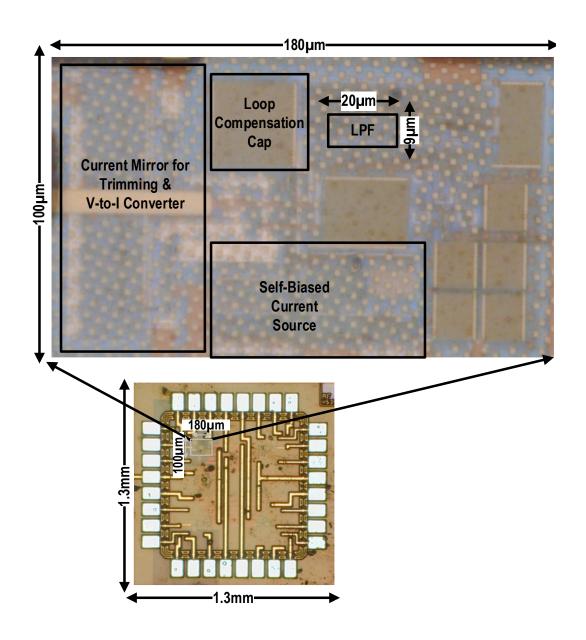

| Figure 5.4: Chip Micrograph of the Proposed VR1                                                                          | 113 |

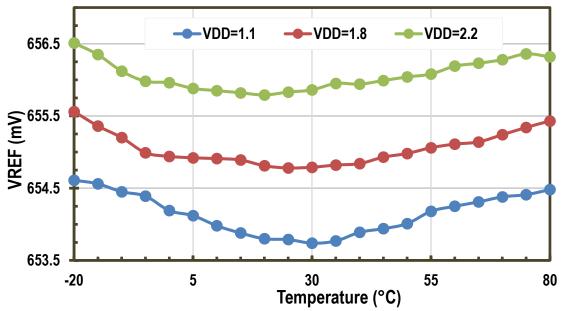

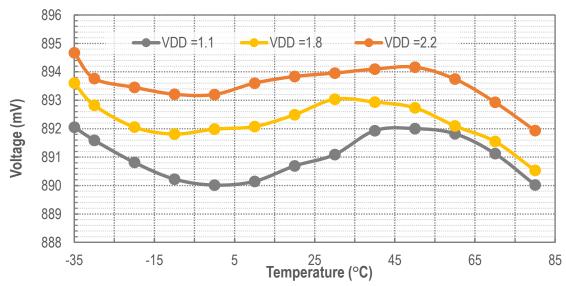

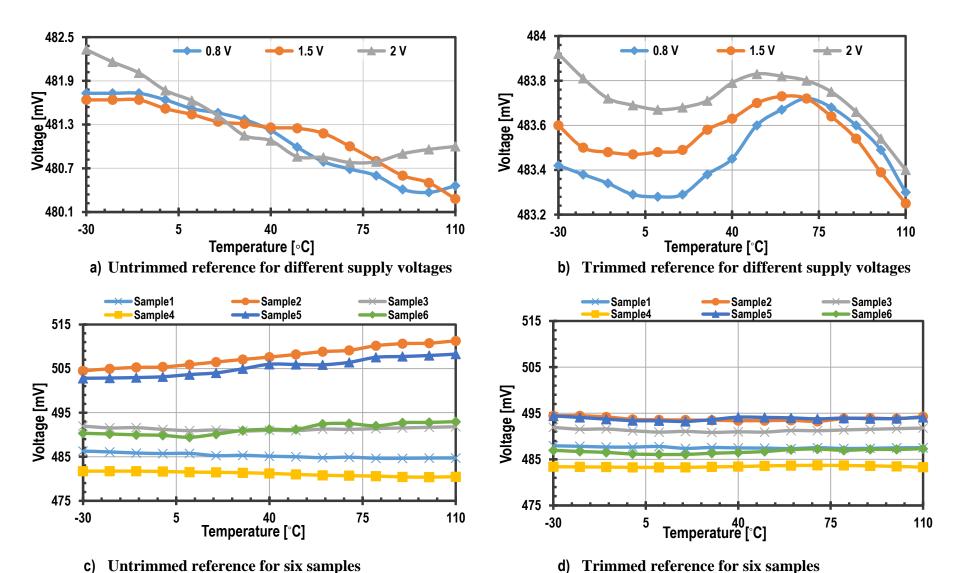

| Figure 5.5: Measured Temperature Dependence of the Proposed VR1                                                          | 114 |

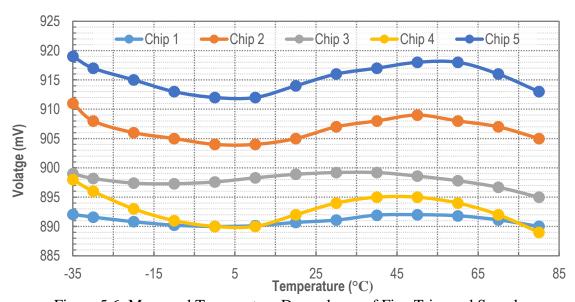

| Figure 5.6: Measured Temperature Dependence of Five Trimmed Samples                                                      | 114 |

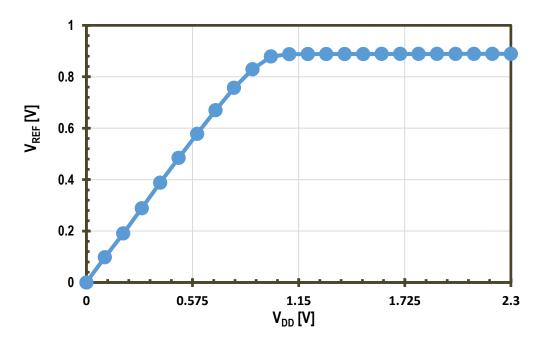

| Figure 5.7: Supply dependence of V <sub>REF</sub>                                                                        | 115 |

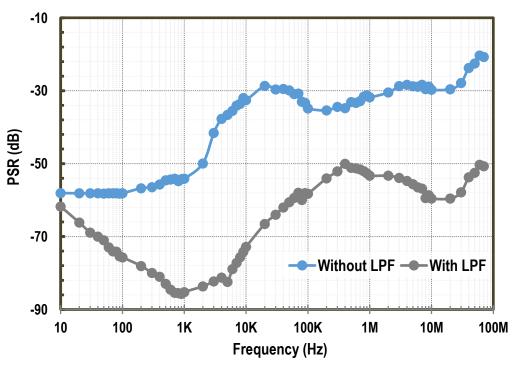

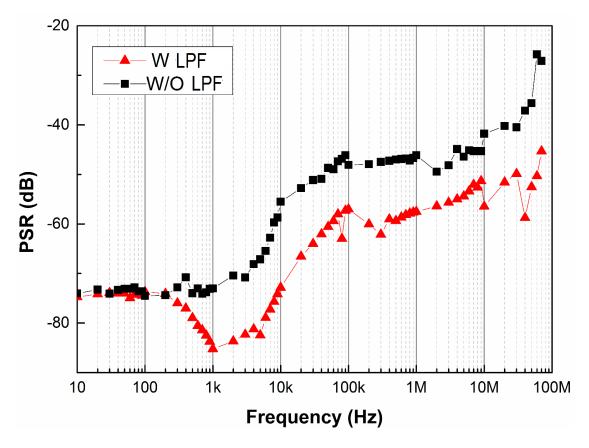

| Figure 5.8: Measured PSR of VR1                                                                                          | 115 |

| Figure 5.9: Chip Micrograph of the Proposed VR2                                                                          | 117 |

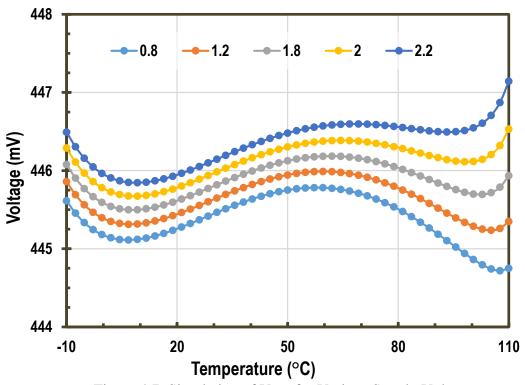

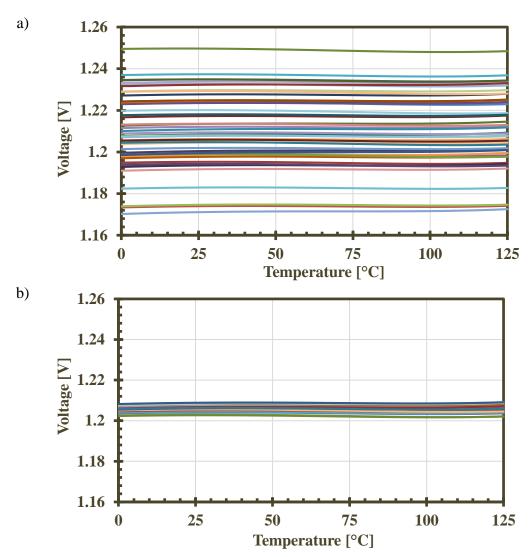

| Figure 5.10: Measured Temperature Dependence of the Output Voltage (V <sub>REF</sub> ) of the Proposed VR                | 118 |

| Figure 5.11: a) Supply Dependence of V <sub>REF</sub> b) Quiescent Current of the VR2                                    | 119 |

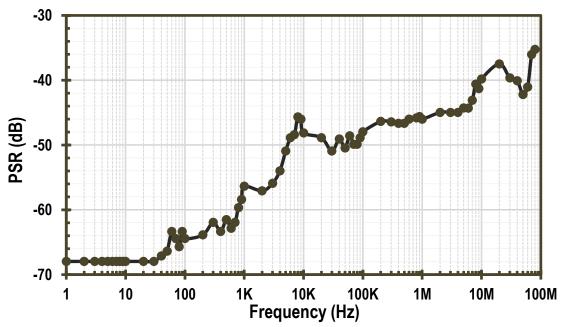

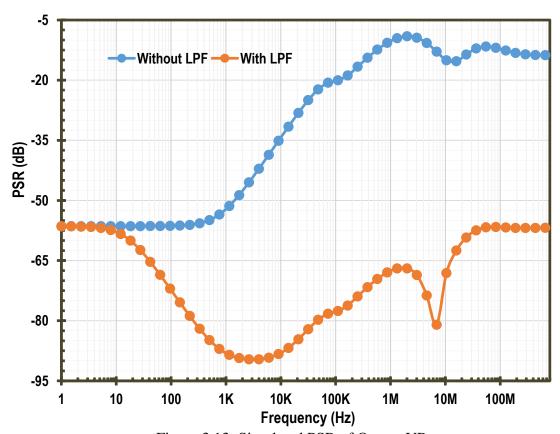

| Figure 5.12: Measured PSR of Output Reference Voltage                                                                    | 120 |

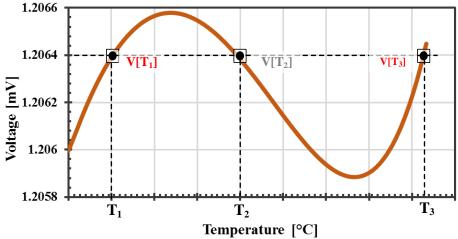

| Figure A.1: Calibration Concept                                                                      | 132 |

|------------------------------------------------------------------------------------------------------|-----|

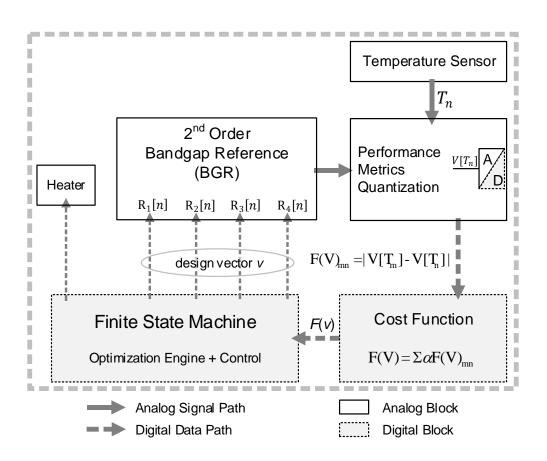

| Figure A.2: Block Diagram of the Proposed Auto-calibration Bandgap Reference System                  | 133 |

| Figure A.3: Temperature Sensor                                                                       | 135 |

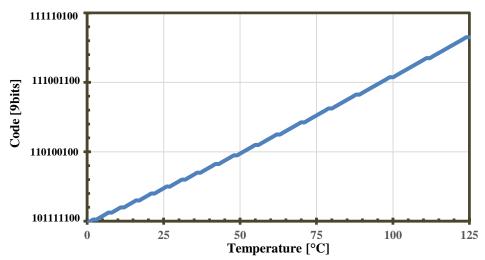

| Figure A.4: ADC Output Code vs. Temperature                                                          | 135 |

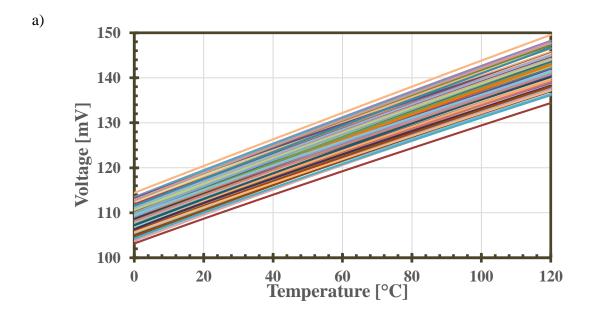

| Figure A.5: Monte-Carlo Simulation a) VPTAT and b) Slope of VPTAT                                    | 136 |

| Figure A.6: Piecewise Nonlinear 2nd Order Bandgap Reference                                          | 138 |

| Figure A.7: Curvature of Proposed 2nd Order Bandgap                                                  | 139 |

| Figure A.8: Folded Cascode Op-amp with Chopping Scheme                                               | 141 |

| Figure A.9: Modular and Non-overlap Clock                                                            | 143 |

| Figure A.10: Temperature Dependence of 2nd Order BGR Output Voltage                                  | 144 |

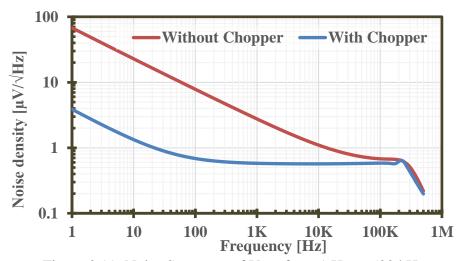

| Figure A.11: Noise Spectrum of V <sub>REF</sub> from 1 Hz to 500 kHz                                 | 144 |

| Figure A.12: Monte Carlo Simulation a) Without Chopper and b) With Chopper                           | 145 |

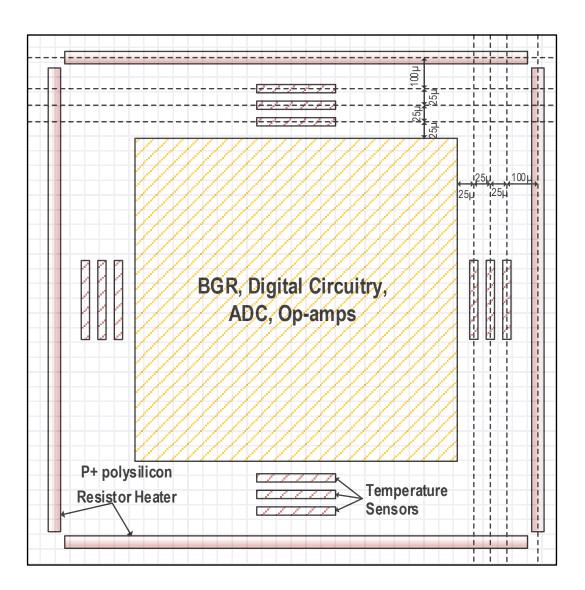

| Figure A.13: Chip Floor Plan which has 12 Sensors and 4 Heaters                                      | 147 |

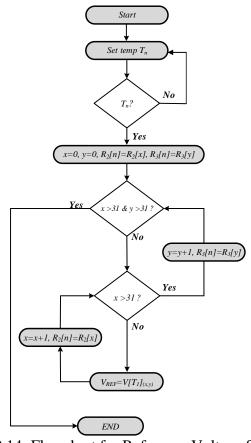

| Figure A.14: Flowchart for Reference Voltage Sampling                                                | 148 |

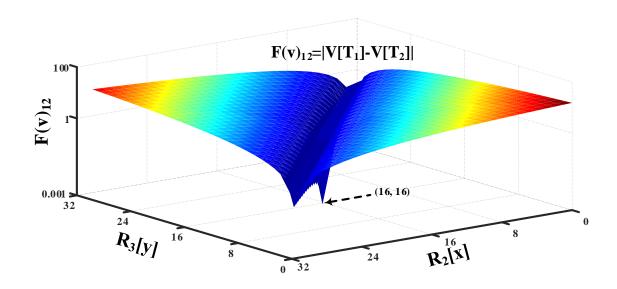

| Figure A.15: $F(V)_{12}$ Contour as well as the Optimal Solution $(x,y)$ of the Calibration Engine   | 150 |

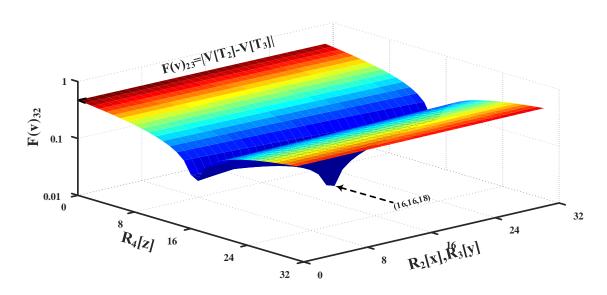

| Figure A.16: $F(V)_{23}$ Contour as well as the Optimal Solution $(x,y,z)$ of the Calibration Engine | 150 |

# LIST OF TABLES

|                                                                                    | Page |

|------------------------------------------------------------------------------------|------|

| Table 2.1: Popular Proprietary Bandgap Based Voltage Reference Products            | 42   |

| Table 2.2: Performance Comparison of Selected Bandgap References in Today's Market | 43   |

| Table 2.3: Performance Comparison of Sub-1 V BGR with Previous Works               | 57   |

| Table 5.1: Performance Summary and Comparison with Previous Works                  | 121  |

| Table 6.1: Main Difference Between the two Proposed VRs                            | 123  |

#### 1. INTRODUCTION TO VOLTAGE AND CURRENT REFERENCES

A crucial part in the design of analog integrated circuits is the creation of reliable and well-defined voltage and current references. A reference in a circuit establishes a stable point which is used by other sub-circuits to generate predictable and repeatable results. It is essential that this reference point does not change significantly under various operating conditions. Temperature is an important parameter which affects the performance of references. To successfully design a CMOS current or voltage reference, one must have thorough understanding of the temperature behavior of MOS transistors.

Therefore, in this section, the temperature dependency of some basic semiconductor physical properties and the effects of temperature on MOS transistor parameters such as threshold voltage and carrier mobility are described. The equations which are generally used to describe the temperature behavior of the CMOS threshold voltage and mobility are presented. This section will further explore the design of different types of current and voltage references and their performance metrics.

#### 1.1 Semiconductor Basics

This section considers some basic properties of semiconductor materials with emphasis on the temperature dependencies of these properties. This is followed by the discussion of the temperature dependency of the threshold voltage and the carrier mobility in a MOS transistor.

### 1.1.1 Basic Semiconductor Effects

In this section, we review the temperature dependencies of some basic properties of semiconductor materials.

## **Band-gap**

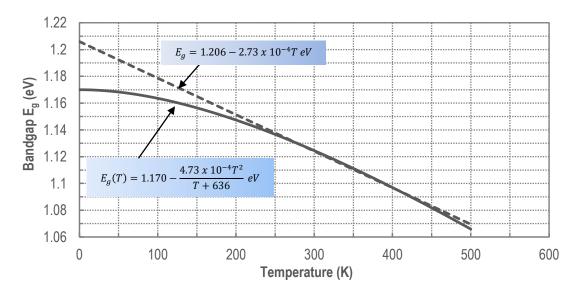

The difference in energy between the valence band and the conduction band is called the band-gap and is denoted by  $E_g$ . The temperature dependence of  $E_g$  for silicon expressed [1].

$$E_g(T) = 1.170 - \frac{4.73 \times 10^{-4} T^2}{T + 636} eV$$

(1.1)

where T is the temperature in kelvin (K).

Above 250 K,  $E_g$  can be approximated by the simpler straight-line [1] expression.

$$E_g = 1.206 - 2.73 \times 10^{-4} T \text{ eV}$$

(1.2)

Figure 1.1 shows the temperature dependency of the silicon band-gap energy (solid line) and its first degree approximation (dashed line). As can be seen, even for the relatively broad military temperature range of -55°C to 125°C (218 K – 398 K), the first degree approximation can be applied.

Figure 1.1: Band-gap of Silicon Dependence on Temperature

## **Intrinsic Carrier Concentration**

The intrinsic concentration,  $n_i$  of electrons and holes depends on the amount of energy needed to break a bond (e.g., the energy band-gap) and on the amount of energy available (e.g., the thermal energy as characterized by the temperature). For silicon,  $n_i$  can be expressed as [2].

$$n_i = \sqrt{1.5x10^{33}T^3e^{-\left(\frac{E_g}{kT}\right)}}cm^{-3}$$

(1.3)

where k is the Boltzmann's constant. At higher temperatures, thermally generated carriers can contribute to concentration of majority carriers.

#### **Carrier Concentration**

When impurity atoms are added and at relatively elevated temperature, most donors and acceptors are ionized. Employing the space charge neutrality and assuming equilibrium condition, carrier concentration,  $n_c$ , can be expressed as [1]

$$n_{c} = \begin{cases} \frac{N_{D} - N_{A}}{2} + \left[ \left( \frac{N_{D} - N_{A}}{2} \right)^{2} + n_{i}^{2} \right]^{\frac{1}{2}} & (nondegenerate \ n - type) \\ \frac{N_{A} - N_{D}}{2} + \left[ \left( \frac{N_{A} - N_{D}}{2} \right)^{2} + n_{i}^{2} \right]^{\frac{1}{2}} & (nondegenerate \ p - type) \end{cases}$$

$$(1.4)$$

Where  $N_D$  and  $N_A$  are donor and acceptor concentration, respectively. As long as the magnitude of the net impurity concentration  $|N_D - N_A|$  is much larger than  $n_i$ , the carrier concentration will be approximately equal to the substrate doping concentration, i.e.  $(N_D - N_A)$  for the n-type and  $(N_A - N_D)$  for the p-type.

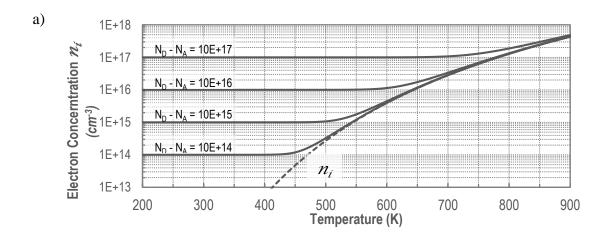

Figure 1.2a shows the variation of electron concentration for an n-type  $(n_0)$  with temperature, with net doping as a parameter, above 200 K, where complete ionization is a good approximation. It can be seen that for  $n_i$  greater than about 20% of  $(N_D - N_A)$ ,  $n_0$  increases appreciably with increasing temperature.

Figure 1.2b shows the carrier concentration in Si as a function of temperature for a donor concentration of  $N_D = 10^{16} cm^{-3}$ . When the temperature is low, the thermal energy is not sufficient to ionize all the impurities and so the carrier density is less than the donor concentration. This region is known as freeze-out region. As the temperature increases, all impurities are ionized and  $n_c = N_D$ . This condition will remain over a wide temperature range and is known as extrinsic region.

However, as the temperature increases further, the intrinsic carrier concentration,  $n_i$ , also increases to a point where the intrinsic carrier concentration becomes comparable to  $N_D$ . The temperature at which the intrinsic carrier concentration becomes equal to  $N_D$ , is called the intrinsic temperature. It is apparent that the intrinsic temperature can be delayed by increasing the impurity density.

Figure 1.2: a) Temperature Dependence of Electron Concentration  $n_0$  in n-type Si for four values of net doping. Also shown is the Temperature Dependence of ni. b) Temperature Dependence of Normalised Electron Concerntration  $n_0/N_D$

#### Fermi Level

For an intrinsic semiconductor, the Fermi level lies about midway between the valence and conduction bands. The Fermi level in n-type materials is closer to the conduction band while for p-type material it is closer to the valence band. The value of the Fermi level depends on temperature due to the temperature dependence of  $n_i$  and the thermal voltage,  $V_T = \frac{kT}{q}$ , and is expressed by

$$\phi_F(T) = \pm V_T \ln \left( \frac{n_c}{n_i(T)} \right) \tag{1.5}$$

where the positive or negative sign refers to n-type or p-type semiconductors, respectively.

## 1.1.2 Threshold Voltage

For all known types of MOSFET devices the threshold voltage relation can be expressed in the general form [3]

$$V_{TH} = \phi_{ms} - \frac{Q_{ox}}{C_{ox}} \pm 2\phi_F + \Delta V_{TH}(N_i)$$

$$\pm \gamma(N_s, t_{ox}, L, W)(|V_{SB}| + 2\phi_F + V_o)^{\frac{1}{2}}$$

(1.6)

where the + and - sign refers to n-channel and p-channel devices, respectively.

In the above equation:  $\phi_{ms}$  is the metal-silicon work function difference,  $\phi_F$  is the Fermi potential of the substrate,  $Q_{ox}$  is the surface-state charge density per unit area,  $C_{ox}$  is the gate-oxide capacitance per unit  $\Delta V_{TH}(N_i)$  is the threshold shift owing to a channel

implant  $N_i$ , with depth  $d_i$ ,  $V_{SB}$  is the source-substrate bias,  $\gamma$  is the substrate body-bias factor, which depends on the substrate doping  $N_s$ , the gate insulator thickness  $t_{ox}$ , and the channel length L and width W,  $V_o(N_i, N_s, d_i)$  is a correction term owing to the threshold shift implant. For enhancement devices with a  $\Delta V_{TH}$  implant of the same type as the substrate,  $V_o$  has a sign opposite to that of  $2\phi_F$ .

The main contributors to the variation of threshold voltage with temperature are Fermi potential,  $\phi_F$ , and the gate-semiconductor work function difference,  $\phi_{ms}$ . The other contributors to the variation of threshold voltage with temperature are the variation in oxide capacitance, as well as the ionization of surface states. For a first-order approximation, these effects are very small and can be safely ignored [4].

For a Si-gate doped oppositely to the substrate, the contact potential is essentially determined by the pn product. Therefore, for an n-type doped gate, the gate-semiconductor work function is expressed as [4],

$$\phi_{ms} = \begin{cases} -V_T \ln\left(\frac{N_s N_p}{n_i^2}\right) & NMOS \\ -V_T \ln\left(\frac{N_s}{N_p}\right) & PMOS \end{cases}$$

$$(1.7)$$

where  $N_p$  is the carrier concentration in the polysilicon gate. As apparent from equation (1.7) the temperature dependence of  $\phi_{ms}$  is determined by temperature dependence of the intrinsic carrier concentration,  $n_i$ , and of the thermal voltage,  $V_T$ .

As a first order approximation, the  $V_{TH}$  decreases linearly with temperature as given by [5]:

$$V_{TH}(T) = V_{TH0} - \alpha_{V_{TH}}(T - T_0)$$

(1.8)

where  $V_{TH0}$  is the threshold at temperature  $T_0$ , and  $\alpha_{V_{TH}} = \frac{\partial V_{TH}}{\partial T}\Big|_{T=T_0}$ .

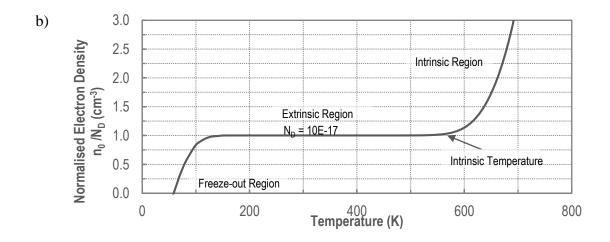

It is apparent from Figure 1.3a that the temperature dependency of threshold voltage can be closely approximated as a linear function of temperature as shown in the equation (1.8). The temperature coefficient of  $V_{TH}$ ,  $\alpha_{V_{TH}}$ , is obtained by differentiating equation (1.6) with respect to temperature. Noting that  $\phi_{ms}$  and  $\phi_F$  are the main factors which may cause a temperature dependence in the threshold voltage,  $\alpha_{V_{TH}}$  is given by

$$\alpha_{V_{TH}} = \left| \frac{\partial V_{TH}}{\partial T} \right| = \left| \frac{\partial \phi_{ms}}{\partial T} + 2 \frac{\partial \phi_F}{\partial T} + \frac{\gamma}{\sqrt{|V_{SB}| + 2\phi_F + V_o}} \frac{\partial \phi_F}{\partial T} \right|$$

(1.9)

Assuming from (1.3), where  $\frac{E_{G0}}{q} = 1.21V$  is the extrapolated zero-degree band gap, it can be determined that for an n-type doped gate

$$\frac{\partial \phi_{ms}}{\partial T} = \frac{1}{T} \left[ \phi_{ms} + \frac{E_{G0}}{q} + \frac{3kT}{q} \right]. \tag{1.10}$$

From equation (1.5), the temperature coefficient of  $\phi_F$  is given by

$$\frac{\partial \phi_F}{\partial T} = \frac{1}{T} \left[ \phi_F - \left( \frac{E_{G0}}{2q} + \frac{3kT}{2q} \right) \right] \tag{1.11}$$

Therefore, the  $\alpha_{V_{TH}}$  becomes

$$\alpha_{V_{TH}} = \left| \frac{\partial V_{TH}}{\partial T} \right| = \left| \frac{\phi_{ms}}{T} + 2\frac{\phi_F}{T} + \frac{\gamma(N_s, t_{ox}, L, W)}{\sqrt{|V_{SB}| + 2\phi_F + V_o}} \right| \frac{\partial \phi_F}{\partial T}$$

(1.12)

Although the value of  $\alpha_{VTH}$  is assumed to be constant, there are a number of factors which affect its value. As equation (1.12) shows, the transistor length affects the value of  $\alpha_{VTH}$ . For a short channel transistor, the depletion charge associated with channel formation is depleted from source and drain rather than from the gate. Generally this effect leads to a reduction of the substrate body-bias factor  $\gamma$  [3]. As a result according to equation (1.12)  $\alpha_{VTH}$  should decrease with decreasing channel length. Figure 1.3b shows the variation of  $\alpha_{VTH}$  with channel length. It show also be noted that,  $\alpha_{VTH}$  is independent of the width as shown by Figure 1.3b. As seen in the Figure 1.3b,  $\alpha_{VTH}$  can only be considered constant for lengths above  $2\mu m$ .  $|V_{SB}|$  is also affects the value  $\alpha_{VTH}$ , higher body biases leads to a smaller value of  $\alpha_{VTH}$ .

Figure 1.3: a) Temperature Dependence of Threshold Voltage of NMOS (L=2) b) Change of  $\,\alpha_{V_{TH}}$  with the Length of NMOS

## 1.1.3 Carrier Mobility

The electron and hole mobility are dependent on the impurity concentrations of donors and acceptors, on temperature and on whether the carriers are minority or majority carriers [1]. With increasing temperature, the carrier mobility due to lattice scattering decreases

because the increased phonon concentration causes increased scattering. For silicon, the mobility due to lattice scattering varies as  $T^{-2.6}$  for electrons and as  $T^{-2.3}$  for holes [1].

The effect of ionized impurity scattering, however, decreases with increasing temperature because the average thermal speeds of the carriers are increased [1]. Thus, the carriers spend less time near ionized impurity as they pass and the mobility due ionized impurity scattering increases with increasing temperature.

The above two effects operate concurrently on the carriers. Hence, the mobility depends on temperature as in [5]

$$\mu(T) = \mu_0 \left(\frac{T}{T_0}\right)^{\alpha_\mu} \tag{1.13}$$

where  $\mu_0$  is the mobility at temperature  $T_0$ , and  $\alpha_\mu$  is the mobility temperature exponent.

#### 1.2 Current References

Current references are essential part of most integrated circuits, since most fundamental blocks such as amplifiers, phase-locked loops (PLLs) and oscillators are dependent on a current reference. Voltage references in particular are usually derived from and are dependent on current references. It should be noted that a current reference does not have to be temperature-independent; however, its temperature dependence should be well characterized and controlled.

The processing and distribution of current signals are done more easily and faster than voltage signals and, therefore, for a given technology, the circuits designed using current-mode approach operate faster than their voltage-mode counterparts. Additionally, the current controls the transconductance of transistors, which in turns affects the static and

dynamic circuits' characteristics. Ultimately, the current sources influences the power consumption of many circuits.

A current linearly proportional to temperature, usually referred to as a proportional-to-absolute temperature (PTAT) current, is the most commonly used reference current. The popularity of PTAT currents is due to the practical, predictable and linear nature of PTAT relation. The other three commonly used current references are complementary-to-absolute temperature (CTAT), temperature-independent and squared PTAT (PTAT<sup>2</sup>) current references. These currents references are explained in the next few sections.

### 1.2.1 PTAT Current References

A PTAT current reference generates a current which increases as temperature increases. The difference of the base-emitter voltage of two bipolar transistors is proportional to the temperature and are used for the design of PTAT current references. For an pnp bipolar transistor (BJT), the base-emitter voltage [6],  $V_{EB}$ , is given by

$$V_{EB} = V_T \ln \left( \frac{I_C}{I_S A} \right) \tag{1.14}$$

where  $I_C$  is collector current, A is the emitter area and  $J_S$  is the saturation current density.

Using equation (1.14), the difference of the base-emitter voltages of two BJT transistors,  $Q_1$  and  $Q_2$ , can is given by

$$V_{EB2} - V_{EB1} = V_T \ln \left( \frac{I_{C1}}{J_s A_2} \frac{J_s A_1}{I_{C2}} \right) = \frac{kT}{q} \ln \left( \frac{I_{C1}}{A_2} \frac{A_1}{I_{C2}} \right)$$

(1.15)

$I_{C1}$  and  $I_{C2}$  are the collector currents of  $Q_1$  and  $Q_2$ , respectively. As apparent from equation (1.15) the difference of two base-emitter voltages is proportional to the absolute temperature.

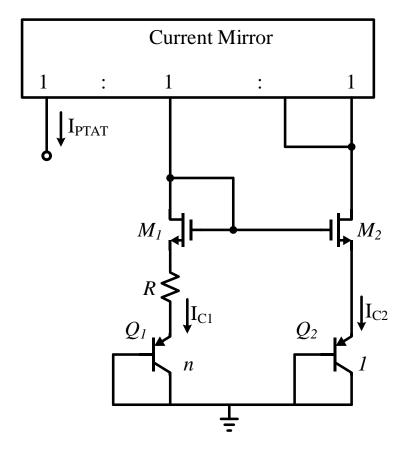

Figure 1.4 shows a PTAT current reference circuit using the difference of two baseemitter voltages [6]. Transistors  $M_1$  and  $M_2$  form a current mirror, developing equal currents for transistors  $Q_1$  and  $Q_2$ , i.e.,  $I_{C1} = I_{C2}$ . From Kirchhoff's voltage law and applying (1.15),

$$I_{C1}R = V_{EB2} - V_{EB1} = \frac{kT}{q} \ln \left( \frac{I_{C1}}{A_2} \frac{A_1}{I_{C2}} \right)$$

(1.16)

The current,  $I_{PTAT}$ , will then be

$$I_{PTAT} = I_{C1} = \frac{kT}{qR} \ln(n) \tag{1.17}$$

$n = \frac{A_1}{A_2}$  is the is the emitter-area ratio of  $Q_1$  to  $Q_2$ .

The transistors  $M_1$  and  $M_2$  are the same size and must be laid out to match well. The channel length of these two transistors must be large enough to minimize channel length modulation errors on the PTAT current. It should be noted that the circuit has two stable points; when  $I_{C1} = I_{C2}$  is the desired operating current and when it is zero current. A start-up circuit [6] is required to eliminate the possible zero current condition by injecting current at a suitable node and force the circuit to move from the zero state to the correct point of operation.

Figure 1.4: PTAT Current Generator

## 1.2.2 CTAT Current References

Another important current reference is a reference that generates a current which is complementary-to-absolute temperature (CTAT), the current decreases linearly with increasing temperature (the complement of PTAT). A CTAT dependence are often used for second-order voltage references as well as for first-order current references [6]. The threshold voltage of a MOSFET and the base-emitter voltage of a BJT both have a negative temperature coefficients and thus used for generating CTAT currents.

In the Figure 1.5, the base-emitter voltage is forced across the resistor (R) using the Op-amp. By mirroring the current flowing through the resistor elsewhere in the circuit a CTAT current is obtained. The CTAT is therefore given by

$$I_{CTAT} = \frac{V_{EB1}}{R} \tag{1.18}$$

From (2.6) as shown in section 2.2, the TC of the base-emitter voltage is assumed as -2.2 mV/°C at room temperature [6]. The temperature coefficient of the resistor is considered negligible, hence current shows a negative temperature dependence.

Figure 1.5: CTAT Current Generator using V<sub>BE</sub>

#### 1.2.3 Temperature-Independent Current References

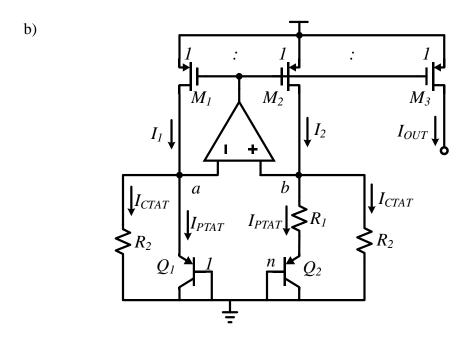

Temperature-independent current generators are usually used in the design of temperature-independent voltage references. They also find applications in the biasing of circuits which require a fixed current across an operating temperature range. The simplest way to obtain a temperature-independent current is summing PTAT and CTAT currents in appropriate proportion [6]. These summation usually leads to first-order temperature-independent (quasi-temperature-independent) current.

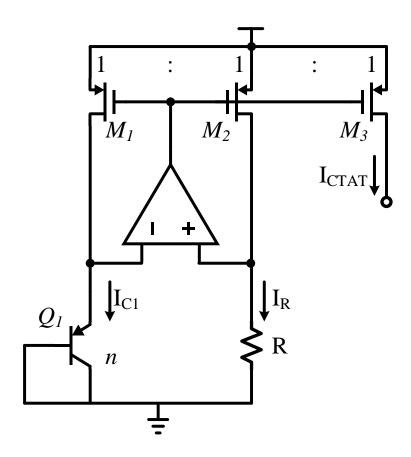

Figure 1.6 illustrates one possible design for summing the PTAT and CTAT currents. In this circuit,  $I_{PTAT}$  is generated by the loop consisting of transistors  $Q_1$  and  $Q_2$  and resistor  $R_1$  and the CTAT current is created by forcing the  $V_{EB}$  of transistor  $Q_1$  across the two  $R_2$  resistors. It is again assumed that the temperature coefficients of the resistors are very low. The Op-amp is so controlled that the voltages at node a and b are equalized [7], hence:

$$I_{PTAT}R_1 = V_{EB1} - V_{EB2} = \frac{kT}{q}\ln(n)$$

(1.19)

$$I_{PTAT} = \frac{kT}{qR_1} \ln(n) \tag{1.20}$$

$$I_{CTAT} = \frac{V_{EB1}}{R_2} \tag{1.21}$$

Since, the gates of  $M_1$ ,  $M_2$ , and  $M_3$  are connected to a common node the current  $I_1$ ,  $I_2$ , and  $I_{OUT}$  becomes the same value due to the current mirror. Henceforth:

$$I_{OUT} = I_2 = I_1 = I_{PTAT} + I_{CTAT} = \frac{kT}{qR_1}\ln(n) + \frac{V_{EB1}}{R_2}$$

(1.22)

Figure 1.6: Temperature-Independent Current Reference a) Concept and b) Implementation

Another simple technique for the generating a temperature-independent current is to force a temperature-independent voltage across a resistor with a very small temperature coefficient. This technique requires a temperature-independent voltage reference, hence is restricted to certain applications.

## 1.2.4 PTAT<sup>2</sup> Current References

A PTAT<sup>2</sup> current is a current which is proportional to the square of temperature. PTAT<sup>2</sup> current references are commonly used in voltage reference for curvature compensation. Most  $V_{GS}$  -based references use some kind of PTAT<sup>2</sup> current for temperature compensation as is shown in section 3.2.1.

A simple method of implementing a PTAT<sup>2</sup> current reference is to force a PTAT voltage through a resistor which shows a PTAT dependence. This method however depends on the technology. Similarly, the Gilbert Multiplier with a positive temperature coefficient resistor can be used in CMOS technologies to generate a PTAT<sup>2</sup> current [6].

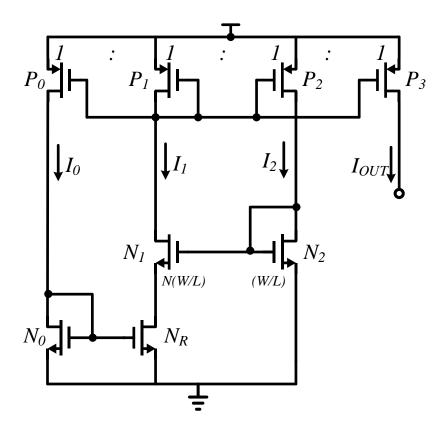

Figure 1.7 illustrates a CMOS implementation for a PTAT2 current generator [7]. In this circuit, transistors  $N_1$  and  $N_2$  operate in sub-threshold region, transistors  $N_0$  in the saturation region and  $N_R$  operates in the linear region [8]. The transistors  $P_0 - P_3$  forms a four-transistor current mirror with a unity mirroring ratio. Using KVL for the voltage loop composed of transistors  $N_1$ ,  $N_2$  and  $N_R$ , the output current can be expressed as

$$I_{1} = \frac{V_{GSN_{1}} - V_{GSN_{2}}}{R_{DSN_{P}}} = \frac{mV_{T}}{R_{DSN_{P}}} \ln\left(\frac{(W/L)_{1}}{(W/L)_{2}}\right)$$

(1.23)

The  $R_{DSN_R}$  is the output resistance of transistor  $N_R$ , and is given by

$$R_{DSN_R} = \frac{1}{K_{N_R} (V_{GSN_R} - V_{TH})}$$

(1.24)

also,

$$V_{GSN_0} = V_{GSN_R} = V_{TH} + \sqrt{\frac{2I_0}{K_{N_0}}}$$

(1.25)

where  $K_i = \mu C_{ox} \left(\frac{W}{L}\right)_i$  and m is gate-to-surface coupling coefficient (sub-threshold slope factor).

Since the current mirror has unity mirroring factor,  $I_0 = I_1 = I_2 = I_{OUT}$ , hence using the equations (1.23), (1.24), and (1.25) the output current can written as

$$I_{OUT} = \frac{2m^2 K_{N_R}^2}{K_{N_0}} V_T^2 \ln^2 \left( \frac{(W/L)_1}{(W/L)_2} \right)$$

(1.26)

Note  $K_i$  depends on mobility. If in a technology the  $\alpha_{\mu}$  (the mobility temperature exponent) small and the mobility could be considered constant over the desired temperature range, the current  $I_{OUT}$  would be proportional to the square of the temperature.

Figure 1.7: CMOS PTAT<sup>2</sup> Current Reference

Precise, integrated current references are usually difficult circuits to design [6]. This inaccuracies are due to the low tolerance (on the order of 10 -20% [6]) of the sheet resistance in digital CMOS processes. As seen from the various current references discussed above, most current references are derived from a voltage across a resistor, hence the tolerance of the resistor translates directly to the overall intolerance of the current reference.

### 1.3 Voltage References

Voltage references (VRs) are essential components in modern SOC applications. In order to ensure compatibility with the rest of the system, VRs are preferentially implemented with a standard digital CMOS process. Due to their higher accuracy and predictability, voltage references are more popular than current references in circuit design [6]. Since current references are usually derived by forcing a voltage across a resistor, the accuracy of the resistor (which is about 10% to 20% for integrated resistors [6]) directly translate into the accuracy of the reference current. Reference voltages on the other hand are usually based on resistor ratio making voltage references more accurate than the current references.

### 1.3.1 Types of Voltage References

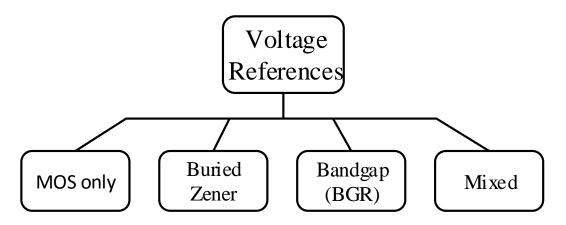

There are various ways of realizing a voltage reference. Current mirrors, diodes and current references are usually the building blocks for voltage references. By the basis of technology in which the reference is constructed or the method of deriving the constant output voltage, voltage references can be grouped into four main categories as shown in Figure 1.8. Threshold voltage is the most obvious way of deriving a reference voltage in a strictly MOS technology. In bipolar processes, the emitter base junction of a BJT can be used to derive the band-gap voltage of silicon for use as a reference voltage. It is also possible to create a BJT, which is adequate to extract the band-gap voltage of silicon in a MOS process.

Figure 1.8: Categories of Voltage References

## **MOS Only Reference**

With the drive for the integration of various mixed signal functional modules into one System on Chip (SOC), there have been numerous attempts to design a good voltage reference using only MOS components.

The most obvious method of producing a MOS Only reference uses the difference between two different threshold voltages to extract the constant reference voltage as implemented in [9]. This design of course is based on the availability of a process in which there are two different threshold voltages for the same type of device (either NMOS or PMOS). Such feature can be obtained by using a selective channel implant, by using different materials for the gate stack, or by doping differently the poly-silicon gates. This cannot be done in the standard CMOS process because of the additional fabrication steps required.

Another type of MOS only voltage references, implemented with a standard CMOS technology, are based on a weighted difference between the gate-source voltages of two

MOS transistors [10]. Other methods take advantage of characteristics of a MOS devices operating in sub-threshold to achieve stable references [11], [12], and [13].

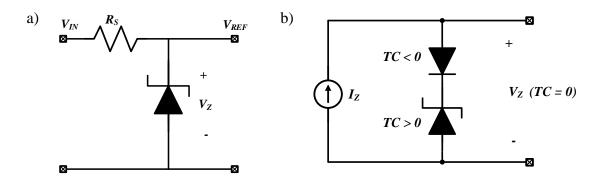

#### **Buried Zener References**

The most basic type of reference that can be constructed uses the reverse breakdown voltage of a zener diode. This is usually implemented as shunt regulator by using a resistor and a Zener diode [14] as shown in figure 1.8a. This reference has very little dependence on the supply but it does have a fairly strong temperature dependence.

A much temperature stable reference can be achieved by thermally compensating the Zener diode as shown in Figure 1.8b. The thermal compensation of the Zener diode is done by connecting in series with the Zener diode a forward-biased diode having an equal but opposite temperature coefficient (TC). Thermal stability can further be enhanced by substrate thermo-stating [14]. This can achieve a reference with a typical TC of 0.3 ppm/°C.

A common problem with references based on breakdown Zener diodes is noise, especially avalanche noise, which affects devices with breakdown above 5V, where avalanche breakdown predominates [14]. Some of this noise can be eliminated if the zener diode is buried in the substrate away from the surface giving rise to buried Zener references.

A Zener reference is typically used in applications where extremely high precision is necessary. The tailor made processes that are required are generally significantly more expensive than a standard digital CMOS process which makes a buried zener reference a poor choice for inexpensive mixed signal ICs. Additionally the best breakdown voltages

range from 6 V to 7 V, hence usually require supply voltages on the order of 10 V to operate [14].

Figure 1.9: Zener Diode References a) Zener Diode as Shunt Regulator b) Thermally Compensated Breakdown Zener Diode

## **Bandgap References (BGR)**

Due to the limitation of the Zener diodes discussed above, for applications with supply voltages below 10 V, bandgap voltage references are used since the output is primarily determined by the bandgap voltage ( $V_{G0} = \frac{E_{G0}}{q} \approx 1.205V$ ). This type of reference uses the base emitter junction of two or more bipolar transistors to extract the 0K bandgap voltage ( $V_{G0}$ ) of silicon.

BGRs relies on the temperature dependence of the base-emitter voltage ( $V_{BE}$ ) BJTs or an equivalent forward-biased diode.

### **Mixed References**

A BiCMOS processes can integrate both BJT and MOS devices on a single chip. Unfortunately, these processes are much more expensive than a standard digital CMOS process and are therefore not a valid for SOC applications. However, it is possible to create two types of bipolar transistors in a digital CMOS process without adding any process steps. These transistors may not be high gain or high speed devices but they function consistently from chip to chip, and therefore, can be used to extract the bandgap voltage for a reference. In modern literature, any reference that is dependent on the bandgap voltage of Si is considered a bandgap reference. Such references are discussed in the next section 2.

# 1.3.2 Curvature-Correction Techniques

A reference voltage temperature dependence can be represented as a polynomial shown below

$$V_{REF}(T) = V_{REF}|_{T_0} \left( 1 + TC_1 \left( \frac{T}{T_0} \right) + TC_2 \left( \frac{T}{T_0} \right)^2 + TC_3 \left( \frac{T}{T_0} \right)^3 + \cdots \right)$$

(1.27)

$T_0$  is the reference temperature,  $TC_1$  represents the first-order (linear) temperature dependence,  $TC_2$  the second-order, and so on. Higher than first-order terms are usually lumped together and described as the "curvature" of the drift.

VRs can be categorized into different performance levels (i.e. zero-order, first-order, or second-order). Zero-order references are the most rudimentary since they are typically not temperature compensated. The first-order references are references in which the

dependence of the polynomial's first-order term on temperature is effectively cancelled. These references typically exhibit TCs ranging from 50 to 100 ppm/°C [6]. Second-order as well as high-order voltages references, compensate for one or more higher-order temperature dependent terms.

## **Zero-Order Compensation**

This is the simplest and most rudimentary way generate a reference voltage. The zero-order is usually achieved by forcing current to flow through a pn junction diode. The circuit shown in Figure 1.8a is one of the most popular zero-order references. The other implementation uses a forward biased diode; this reference typically has a TC of -2.2 mV/ $^{\circ}$ C [6].

## **First-Order Compensation**

The BGRs discussed in section 1.3.1 is the most popular first-order reference. First-order compensation usually successfully compensates for the linear temperature term of BJT base-emitter voltage,  $V_{BE}$ , but usually does not compensate for the nonlinear term [6].

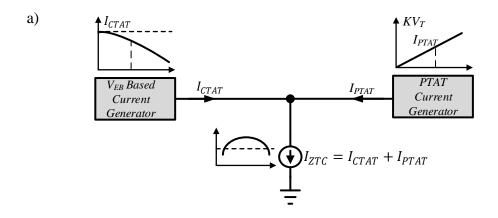

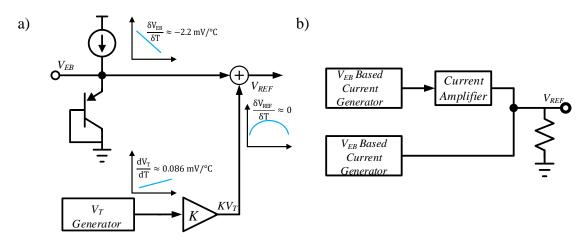

A PTAT term based on thermal voltage ( $V_T$ ) is amplified by a factor and counterbalanced by the linear temperature term of BJT base-emitter voltage, which is a CTAT. The basic concept is clearly illustrated in the classical bandgap reference by WIDLAR (1971).

$V_T = \frac{kT}{q}$  has a positive TC equal to 0.086 mV/°C whilst  $V_{BE}$  has a temperature coefficient of 2.2 mV/°C. Hence, a first-order temperature compensation is obtained by properly combining  $V_{BE}$  and  $V_T$  given by

$$V_{REF} = V_{BE} + KV_T \tag{1.28}$$

where

$$K = -\frac{TC(V_{BE})}{TC(V_T)} = 25.6$$

[15].

There two main ways of implementing a first-order reference. The first method is by properly adding two voltages proportional to  $V_{BE}$  and  $V_{T}$  to obtain a temperature-independent reference. This configuration known as the voltage-mode requires a minimum supply above 1.2 V and output is usually approximately  $V_{G0} = 1.2 V$ .

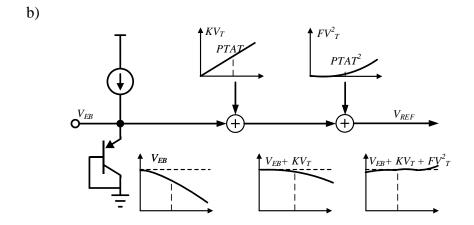

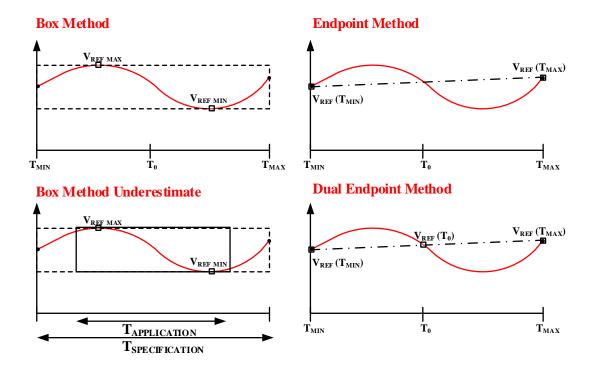

To generate a reference sub- 1 V first-order BGR, a current-mode bandgap is used. In this implementation two currents, one proportional to  $V_{BE}$  and the other proportional to  $V_T$ , are properly scaled and summed up. The summed current, which is temperature-independent, goes through a resistor, generating a temperature-independent voltage. This method allows BGR to be implemented with sub-1 V supplies [7]. Figure 1.9 shows the implementation of first-order BGRs using the two techniques.

Figure 1.10: Conceptual Implementation of a First-Order Reference a) Voltage-Mode b) Current-Mode

# **Second-Order Compensation**

The first-order references discussed above are not adequate for high precision and high performance systems such as data converters and power converters in battery powered ICs. This has resulted in the development of higher-order, curvature compensation techniques as in [12], [14], [16], and [17].

The second-order references do not just cancel the linear temperature term of  $V_{BE}$ . They also attempt to approximately cancel the nonlinear component of equation (2.3). This process can be accomplished by one of two separate techniques (or a combination of the two).

The first method is to make the value of  $(\eta - \theta)$  in equation (2.3) zero. When this is done successfully, there would be no nonlinear temperature-dependent term in (2.3). Typically  $\eta \approx 4$  for most processes, henceforth a perfect cancelation of the nonlinear term could be achieved by using a very strongly temperature-dependent bias current. Unfortunately, building a fourth-order temperature-dependent current is complicated, in fact many design use only PTAT<sup>2</sup> sources. The other technique, used by many of curvature- compensated references, is to simply add a curvature-correcting component which increases with temperature in a nonlinear fashion.

Second-order compensation, essentially tries to cancel the second-order term in the Taylor-series (equation (2.4)) of the diode relationship in equation (2.3). The traditional method of doing such compensation is through the addition of a PTAT<sup>2</sup> term to the output voltage relation of a first-order bandgap reference [6]. In this, the negative temperature dependence of the logarithmic term of  $V_{BE}$  is canceled with a positive quadratic term [6].

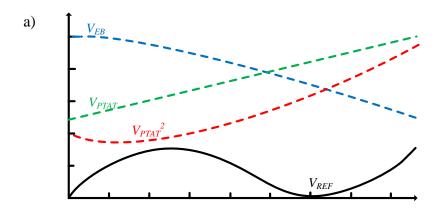

Figure 1.10a shows the temperature characteristics achieved by a typical PTAT<sup>2</sup> curvature-compensated reference.

One implementation of this technique is illustrated in Figure 1.10b [15]. A PTAT correction voltage  $KV_T$  is added to  $V_{EB}$  to cancel out the linear temperature variation of  $V_{EB}$ . After the PTAT correction voltage is added, the reference output  $V_{REF}$  will exhibit mostly the quadratic temperature variation as shown in the Figure 1.10b. Using a PTAT<sup>2</sup> correction voltage  $FV_T^2$ , the quadratic temperature variation of the  $V_{EB}$  is cancelled at the final reference output.

Figure 1.11: Squared PTAT Curvature-Correction a) Typical Temperature Dependence b) Implementation Concept

# **State-of-the-Art Curvature Correction Techniques**

Various design approaches can be adopted to perform curvature correction to yield both the second-order compensation discussed above and higher compensation. One method is piecewise-linear compensation [19], [20]. Other techniques uses temperature-dependent resistor ratios. This method usually involves using resistors of different TCs to achieve a nonlinear or piecewise curvature correction [16] and [18].

The other is to cancel the nonlinearity using an exponential temperature compensation [21]. Figure 1.11 shows the temperature of a piecewise linear curvature-corrected bandgap reference [6].

Figure 1.12: Temperature Dependence of Piecewise-Linear Curvature Corrected Bandgap

# 1.4 Definitions and Metrics

Power management circuits, data converters, oscillators and a variety of other circuits require some kind of reference standard to function at the desired degree of accuracy. Hence the primary requirements of voltage references (VRs) are accuracy and stability [14], [22].

VRs come in many forms and offer different features, but in the end, accuracy and stability, are a voltage reference's most important features [22], [14], as the main purpose of the reference is to provide a known output voltage. Variation from this known value is an error. Voltage reference specifications usually predict the uncertainty of the reference under certain conditions.

The ability of a voltage reference (VR) to maintain a constant output under varying external conditions is characterized in terms of performance parameters such as line sensitivity, and temperature coefficient. The long-term stability is also important metric for voltage references. These performance metrics for voltage reference applications are discussed in the next few sections.

## 1.4.1 Initial Accuracy

The initial accuracy of a VR indicates how close to the stated nominal voltage the reference voltage is guaranteed to be at room temperature under stated bias conditions [23]. While the initial output voltage may vary from unit to unit, if it is constant for a given unit, then it can be easily calibrated [22]. This specification is usually for room temperature only, with a defined input voltage and load current. It provides a starting point

for most of the other specifications. In many applications, initial accuracy is the most important specification. Initial accuracy tolerance can be affected by package stress, so proper control of the solder temperature profile is essential and twisting of the PCB must be kept to a minimum. Typical initial accuracies are in the range of 1% to 0.01%, which translates into 1 LSB (least significant bit) error in 6 to 12 bit converters [24].

## 1.4.2 Temperature Coefficient (TC)

The temperature coefficient is a measure of a VR's ability to maintain the prescribed output voltage under varying temperature. The TC or "drift", has unit of parts-per-million per degree Celsius (ppm/°C). The temperature coefficient can be specified over several different temperature ranges, including the commercial temperature range (0 to 70°C), the industrial temperature range (-40 to 85°C), and the extended temperature range (-40 to 125°C) [23].

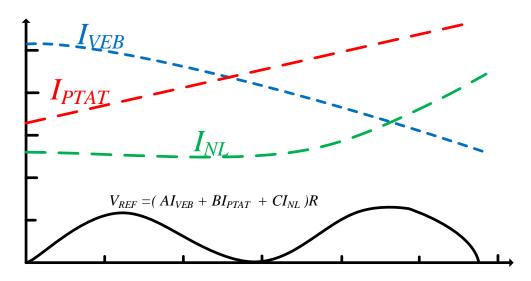

There are several methods of defining TC, with the "box" method being used most often [23]. This method to calculates maximum total error over the specified temperature range, whereas other methods use the values of the  $V_{REF}$  at the endpoints of the temperature range ( $T_{MIN}$ ,  $T_{MAX}$ ). The endpoints method fails to account for curvature (higher-order) in the temperature change, hence are usually not ideal. It should however be noted that the box method may under-estimate the TC if the temperature of the application is smaller than the range over which the TC is specified [23].

Equation (1.29) and (1.30) shows the formula for the box and endpoint measurement respectively.

$$TC_{BOX} = 10^6 \left( \frac{V_{REF \, MAX}|_T - V_{REF \, MIN}|_T}{V_{REF}|_{T_0}} \right) \left( \frac{1}{T_{MAX} - T_{MIN}} \right)$$

(1.29)

$$TC_{ENDPOINTS} = 10^6 \left( \frac{V_{REF}|_{T_{MAX}} - V_{REF}|_{T_{MIN}}}{V_{REF}|_{T_0}} \right) \left( \frac{1}{T_{MAX} - T_{MIN}} \right)$$

(1.30)

The Figure 1.12 shows the different methods for TC calculation [23].

Figure 1.13: Different Methods for TC Calculation

# 1.4.3 Thermal Hysteresis

A change in output voltage as a result of a temperature change. When voltage references experience a temperature change and return to the initial temperature, they do not always have the same initial output voltage. Thermal hysteresis is challenging to correct and is a major source of error in systems that experience temperature changes of

25°C and above [25], [24]. Thermal hysteresis is not tested in production and datasheets only provide a typical shift [23], which is usually about 25 ppm.

## 1.4.4 Long-Term Stability

Long-term stability describes the typical shift in the reference voltage ( $V_{REF}$ ) after 1000 hours (6 weeks) of continuous operation under nominal operating conditions and is it also an important performance metric for VRs, particularly for repeatability within a system. The long-term stability in a voltage reference increases with the square root of the elapsed time, usually expressed in ppm/1000 hours [23]. Longer-term shifts are caused by the aging of the circuit. The buried Zener references typically have a long-term stability of 5-20 ppm/1000 hours which is the best for monolithic references [24] whereas bandgap references generally have a long-term stability of 20-120 ppm/1000 hours.

## 1.4.5 Power Supply Rejection (PSR)

To ensure system robustness, an "ideal" voltage reference circuit must reject fluctuations in supply voltage and generate a clean reference voltage. PSR is often used to evaluate how well a voltage reference circuit rejects supply noise or spurious signals at a given frequency coupled on the supply rails, which can be expressed in dB as

$$PSR = 20\log\left(\frac{V_{REF}}{V_{DD}}\right) \tag{1.31}$$

The PSR over a wide frequency range describes the susceptibility of the voltage reference circuit to power supply noise.

# 1.4.6 Line regulation

An error produced by a change in the input voltage,  $\frac{\Delta V_{REF}}{\Delta V_{DD}}$ . This is a dc specification and does not include the effects of ripple voltage or line transients. The importance of line regulation depends on the tolerance of the input supply. The line regulation (LR) of a VR expressed in ppm [23] is given by

$$LR = 10^{6} \left( \frac{V_{REF}|_{V_{DDMAX}} - V_{REF}|_{V_{DDMIN}}}{V_{REF}|_{V_{DDMIN}}} \right) \left( \frac{1}{V_{DD_{MAX}} - V_{DD_{MIN}}} \right)$$

(1.32)

Due the recent drive for low power mixed-mode SOC applications, power consumption, noise, area and power supply rejection (PSR) has become very important design criteria for voltage references (VR).

#### 2. CMOS BANDGAP VOLTAGE REFERENCES

Since the mid 1970's, bandgap references (BGR) circuits have been widely used in analog IC. Most BGR circuit require some kind of diode but unfortunately, a good diode is usually not available in most standard digital CMOS processes. It is usually possible to create two types of bipolar junction transistor (BJT) devices from the standard structures in a digital CMOS process. One of these structures is similar to a lateral BJT device in a typical bipolar process and other is similar to that of a standard vertical device that can be found in several bipolar processes.

In this section, we briefly describe *pn* diodes temperature characteristics and the implementation of BJTs in CMOS processes. We will also discuss an implementation of low power bandgap voltage reference in CMOS technology.

# 2.1 Bipolar Transistors (BJT) in CMOS

A realistic BJT has certain design and specified characteristics. The device doping has to follow a specific pattern; emitter needs to have the highest doping, followed by the base, with the collector having the lowest doping. The base of ideal BJT is usually very narrow to increase the speed of the device. A narrow base helps reduce the amount of charge that can be stored on the base and hence improves the device's switching speed [1]. The collector must have a much larger area than the emitter to allow as many charge carriers as possible to be collected. This design pattern improves the current gain of the device.

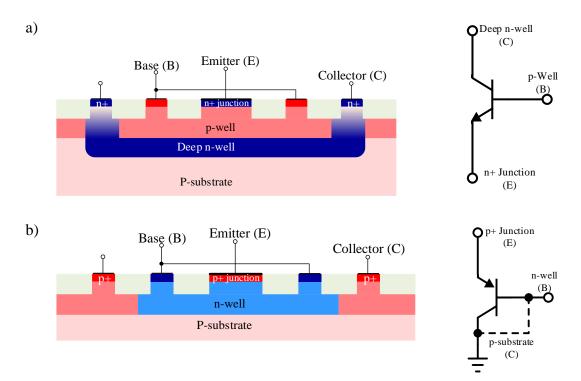

In a standard digital CMOS process it is not possible to control these parameters since only the standard CMOS structures can be used. It is not possible for a designer to change any of these process parameters. In typical single well CMOS processes, either NPN devices (p-well process) or PNP (n-well process) devices are available.

The first transistor type is a lateral transistor that has a cross-section similar to that in Figure 2.1a. These lateral transistors is an arrangement of the standard MOSFET structure into a topology that will function as a bipolar transistor and is usually available twin-well process like the *IBM*180 *CMOS7RF* process. It is modeled as an *npn*, with the n+ cathode as the emitter, the p-well base, and deep n-well as the collector. Unfortunately they do not have ideal BJT characteristics.

The other structure is a vertical *pnp* transistor as shown Figure 2.1b, with the p+junction, n-well, and substrate forming the emitter, base, and collector respectively. The vertical device is much simpler than the lateral device but has one significant drawback. To create the collector it is necessary to use the substrate as an active terminal in the transistor; meaning the collector voltage of all vertical devices on a single chip must be connected to the same potential. Hence, it is usually used as simple two terminal device (diode) in which the N-well and the substrate ring surrounding the device are shorted together.

Figure 2.1: CMOS BJTs a) Lateral NPN b) Vertical PNP

# 2.2 V<sub>EB</sub> Temperature Characteristics

The collector current,  $I_c$ , and forward voltage of the emitter-base diode of a pnp BJT can be express as [14]

$$V_{EB} = V_T \ln \left(\frac{I_c}{I_s}\right) \tag{2.1}$$

The saturation current,  $I_s$ , is given by [6]

$$I_s = CT^{\eta} e^{-\frac{V_{G0}}{V_T}} \tag{2.2}$$

where C is a temperature-independent constant and  $\eta$  is a process dependent constant ranging from 3.6 to 4. The  $I_c$  can be expressed a temperature dependent current given by:

$$I_c = DT^{\theta} \tag{2.3}$$

D is a constant and  $\theta$  is a number defining the temperature dependence of the current forced through the collector.

Using (2.1)-(2.3) and solving for the constants at reference temperature,  $T_0$ , the temperature dependence of  $V_{EB}$  can be expressed as

$$V_{EB} = V_{G0} - \frac{T}{T_0} [V_{G0} - V_{BE}(T_0)] - [\eta - \theta] V_T \ln \left(\frac{T}{T_0}\right)$$

(2.4)

Obtaining the Taylor-series expansion of the logarithmic components of equation (2.4), the temperature dependence,  $V_{EB}$ , can be expressed as [6]

$$V_{EB} = V_{G0} + (\eta - \theta)V_T|_{T_0} - \left[\frac{V_{G0} - V_{EB}(T_0) + (\eta - \theta)V_T|_{T_0}}{T_0}\right]T$$

$$-\left\{\frac{(\eta - \theta)V_T|_{T_0}}{T_0}\left[T\ln\left(\frac{T}{T_0}\right) - T + T_0\right]\right\}$$

(2.5)

where  $V_{EB}(T_0)$  is the base-emitter voltage at  $T_0$  and  $V_T|_{T_0}$  is the thermal evaluated at  $T_0$ .

An understanding of the  $V_{EB}$  relation above is central for the designing of accurate bandgap references.

Based on (2.1) and (2.2), the TC of the  $V_{EB}$  is usually approximated as:

$$TC(V_{EB}) = \frac{\partial V_{EB}}{\partial T} = -\left(\frac{V_{G0} - V_{EB}}{T} + \frac{3k}{q}\right)$$

(2.6)

assuming  $V_{EB}=650~mV$  at room temperature, we get  $TC(V_{EB})=-2.2~mV/^{\circ}C$

# 2.3 Commercial Voltage Reference ICs

Since the 1960s when the discrete Zener diode was introduce, monolithic voltage references have evolved over many generations [24], so that today they are available in various distinct categories. These include the Zener, MOS only, bandgap, the buried-zener, the XFET® from Analog Devices, along with the FGA<sup>TM</sup> from Xicor/Intersil and mixed references. Integrated voltage references are now manufactured using various processes [24] (e.g. Bipolar, JFET, complementary-bipolar, Bi-CMOS, CMOS).

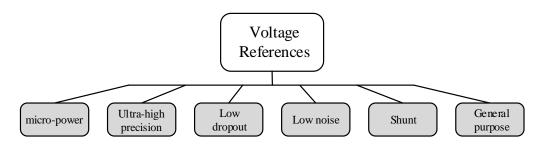

The new design processes has led to high thermal stabilities, improved initial accuracies, lower-power, lower noise, smaller chips and packages. Voltage references today are subdivided into different types which includes micro-power, ultra-high precision, low dropout, low noise, shunt and general purpose references [24]. A lot of these references have added features for high performance applications such as automotive, space, defense, and avionics. Some references even allow for user trimming, filtering and adjustment of the reference voltage.

Figure 2.2: Types of Commercial Monolithic Voltage References

The invention of the bandgap references by Bob Widlar in the late 1960's [24] was probably due the fact that the references that was created by Zener diodes were sensitive to temperature drift, noisy and required more than 5 V to function [24]. Even though Zener references today are much less noisy and offers better temperature stability, they still require high voltages to function, hence are not ideal for low voltage applications. Hence the bandgap reference is the most popular for low voltage designs.

The LM10 of National Semiconductor's (now part of Texas Instruments Inc.) was the earliest device to use the first generation bandgap references. During the inventions of the BGR by Bob Widlar, Analog Devices Inc. also introduced its legendary AD580. The AD580 was the first precision BGR [24] and based on what is referred to today as the *Brokaw cell* (we will discuss the CMOS implementation of it in the next section).

Since its invention, BGRs have been refined and manufactured by various analog product makers [24]. Although the two-terminal (shunt) bandgaps are most common, there are more sophisticated series types. Table 2.1 provides a summary of some of the popular proprietary bandgap based voltage reference products. Table 2.2 performance comparison of selected bandgap references in today's market.

Table 2.1: Popular Proprietary Bandgap Based Voltage Reference Products

| Manufacturers     | Products                                    |  |  |  |  |  |

|-------------------|---------------------------------------------|--|--|--|--|--|

|                   |                                             |  |  |  |  |  |

| Analog Devices    | ADR34xx, ADR280, REF19x                     |  |  |  |  |  |

| Intersil          | ISL21010-xx, ISL21080-xx, ISL21060-xx       |  |  |  |  |  |

| Linear Technology | LTC6655, LT1004, LM185, LT1034, LT1634      |  |  |  |  |  |

| Maxim             | MAX6072, MAX6071, MAX6070, MAX6010, MAX8069 |  |  |  |  |  |

| Microchip         | MCP1525/41                                  |  |  |  |  |  |

| Texas Instruments | LM412x, LM4132, LM4140, REF29xx, REF3012    |  |  |  |  |  |

Table 2.2: Performance Comparison of Selected Bandgap References in Today's Market

| Table 2.2. Terrormance Comparison of Selected Bandgap References in Today's Market |           |           |          |             |            |  |  |  |  |

|------------------------------------------------------------------------------------|-----------|-----------|----------|-------------|------------|--|--|--|--|

| Specification                                                                      | REF3012   | MAX6070   | REF191   | ISL21080-09 | MCP1525/41 |  |  |  |  |

| Technology                                                                         | CMOS      | N/A       | CMOS     | N/A         | CMOS       |  |  |  |  |

| Temperature Range (°C)                                                             | -40 – 125 | -40 – 125 | -40 – 85 | -40 – 85    | -40 – 85   |  |  |  |  |

| Supply Voltage (V)                                                                 | 1.8 – 5.5 | 2.7 – 5.5 | 3–15     | 2-5.5       | 2.7 – 5.5  |  |  |  |  |

| Supply Current (µA)                                                                | 42        | 130       | 45       | 0.35        | 95         |  |  |  |  |

| Vref (V)                                                                           | 1.250     | 1.250     | 2.048    | 0.9         | 2.5        |  |  |  |  |

| Initial Accuracy (± %)                                                             | 0.2       | 0.08      | 0.1      | 0.7         | 1          |  |  |  |  |

| TC (ppm/°C)                                                                        | 35        | 8         | 10       | 50          | 50         |  |  |  |  |

| LR (µV/V)                                                                          | 60        | 100       | 16       | 30          | 107        |  |  |  |  |

| PSR (dB) @120Hz                                                                    | -62       | -100      | -82      | -40         | -75        |  |  |  |  |

| Output Voltage Noise<br>(0.1 to 10Hz, µVp-p)                                       | 14        | 3.6       | 20       | 40          | 145        |  |  |  |  |

# 2.4 The Classical CMOS Bandgap Reference

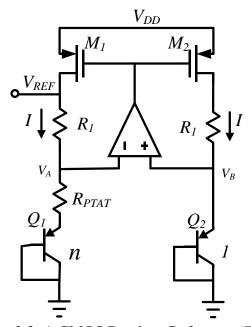

The most common bandgap reference (BGR) is a first order voltage reference. These reference is based on summing the voltage of a forward-biased diode (or base-emitter junction) and a PTAT voltage obtained from the  $\Delta V_{EB}$ . These can either be implemented as a current or voltage mode as shown in Figure 1.10 or a voltage mode whose CMOS implementation is shown in Figure 2.2

From the Figure 2.2 the, we have

$$V_{REF} = V_{EB2} + V_{R_4} (2.7)$$

Also, assuming the op-amp has large gain and that its input terminals ( $V_A$  and  $V_B$ ) are at the same voltage, then

$$V_{R_{PTAT}} = V_{EB2} - V_{EB1} = \Delta V_{EB} \tag{2.8}$$

Considering (1.15),

$$I = \frac{V_{R_{PTAT}}}{R_{PTAT}} = \frac{\Delta V_{EB}}{R_{PTAT}} = \frac{V_T \ln(n)}{R_{PTAT}}$$

(2.9)

This makes,

$$V_{R_1} = IR_1 = \frac{R_1}{R_{PTAT}} V_T \ln(n)$$

(2.10)

Clearly,  $V_{R_1}$  is PTAT voltage and when added the  $V_{EB2}$ , as in (2.7) we will obtain a first order temperature reference given by:

$$V_{REF} = V_{EB2} + \frac{R_1}{R_{PTAT}} V_T \ln(n)$$

(2.11)

A zero TC (ZTC) can be obtained at a particular temperature by differentiating (2.11) and equating to zero.

$$\frac{\partial V_{REF}}{\partial T} = \frac{\partial V_{EB2}}{\partial T} + \frac{R_1}{R_{PTAT}} \left(\frac{k}{T}\right) \ln(n) \tag{2.12}$$

Note that a room temperature  $\frac{k}{T} \approx 0.086 \ mV/^{\circ}C$  and  $\frac{\partial V_{EB2}}{\partial T} \approx -2.2 mV/^{\circ}C$ . Hence for ZTC at room temperature

$$\frac{R_1}{R_{PTAT}}\ln(n) = 25.58\tag{2.13}$$

Figure 2.3: A CMOS Bandgap Reference (The Brokaw Cell)

Using the (1.15) and (2.4) it can be shown that for ZTC at  $T = T_0$ , the output  $V_{REF}$  is:

$$V_{REF}|_{T_0} = V_{G0} + [\eta - 1]V_T|_{T_0}$$

(2.14)

For the case of  $T_0 = 300 K$  and  $\eta = 2.3$  implies,

$$V_{REF}|_{T_0} = 1.24 V (2.15)$$

The name bandgap originates from the fact that output is dependent of the bandgap voltage ( $V_{G0}$ ) of silicon as seen in (2.14). The voltage reference circuit in Figure 2.3 is a CMOS implementation of the voltage reference originally proposed by Brokaw, A.P. in 1974. Due to the 1.24 V voltage output for ZTC this reference requires a supply above 1 V to function, hence other techniques have been proposed over the years for sub-1 V designs. An example of such circuits is described in the next section.

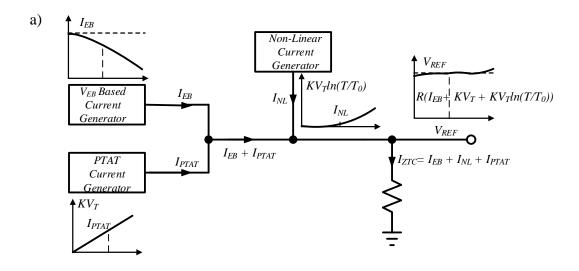

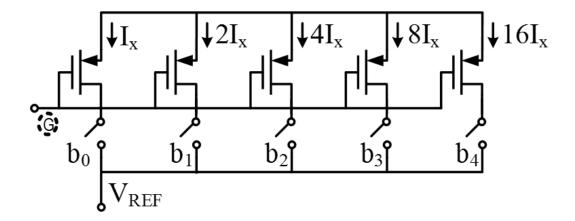

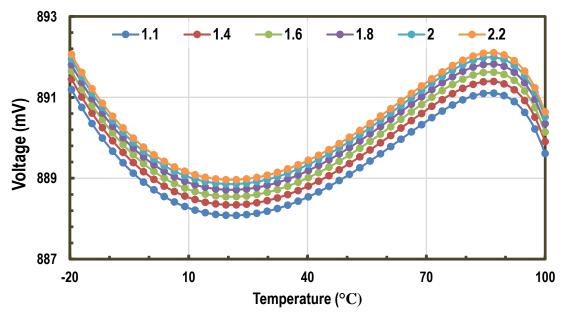

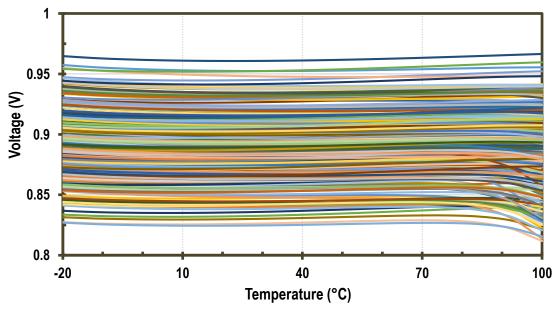

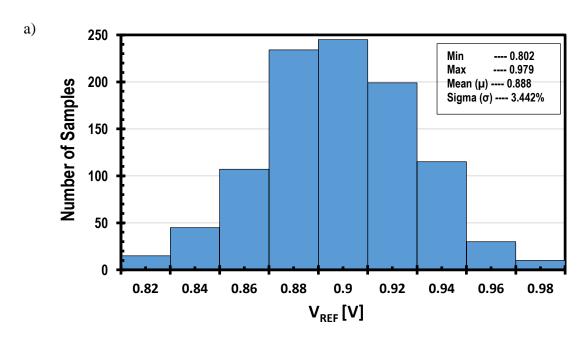

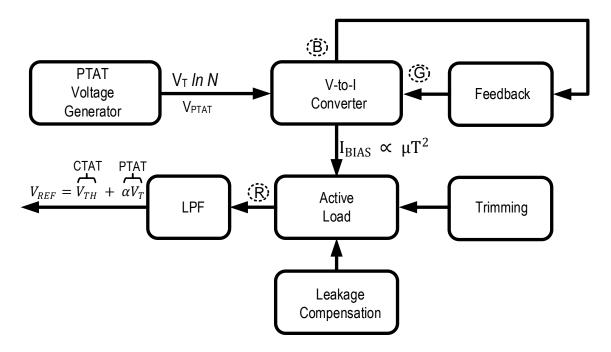

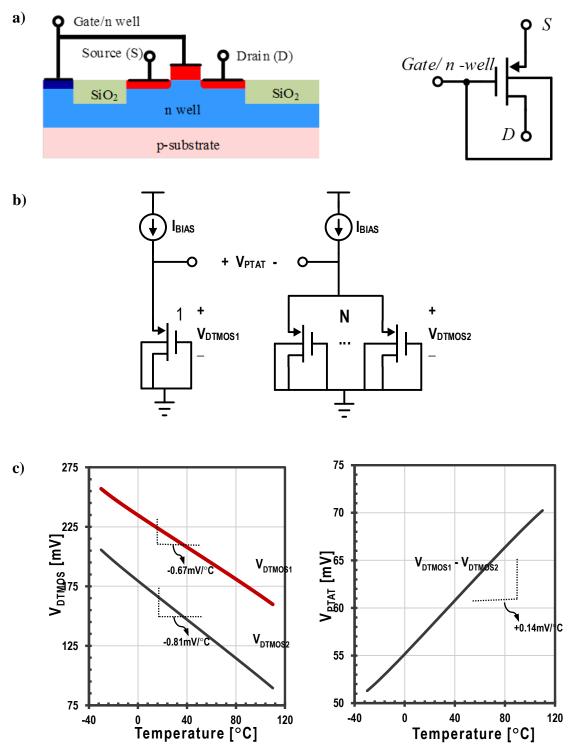

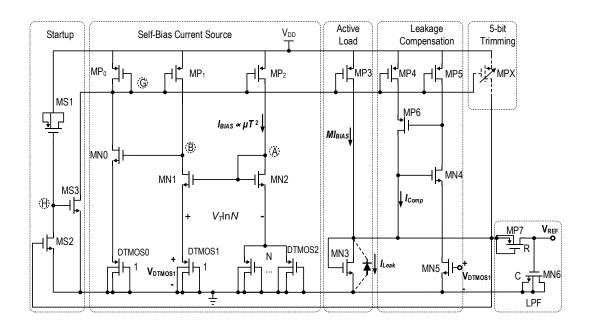

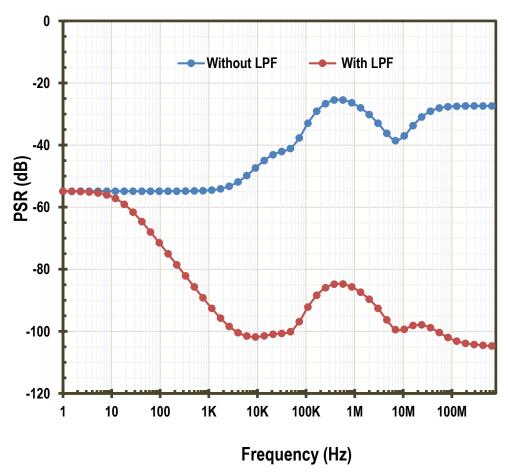

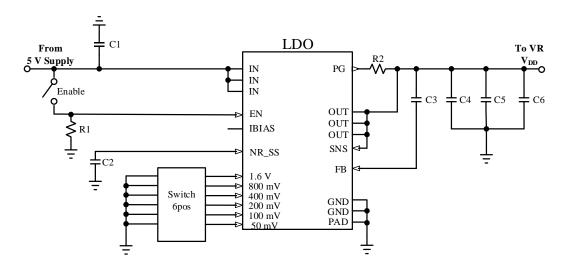

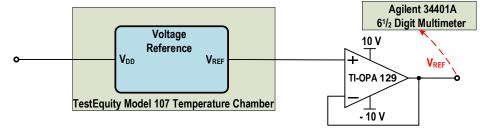

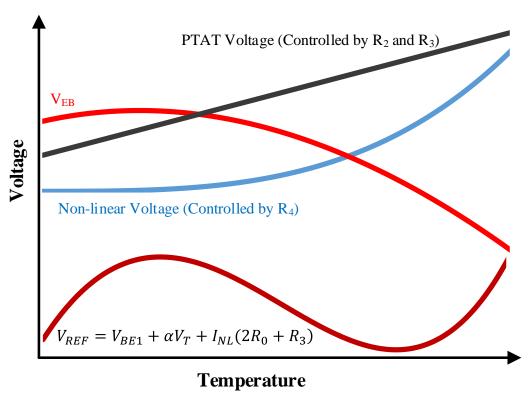

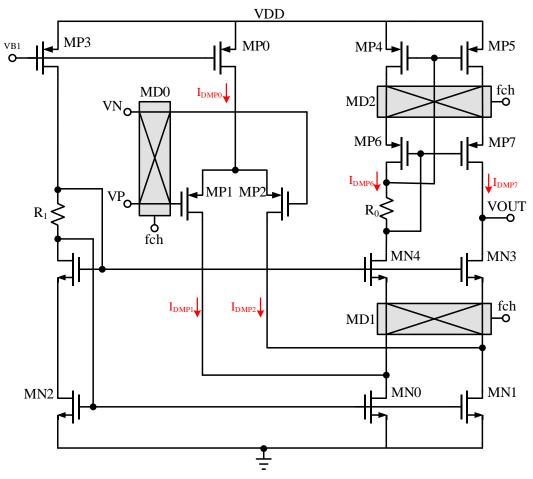

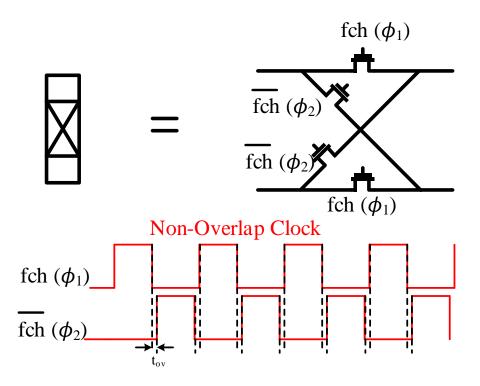

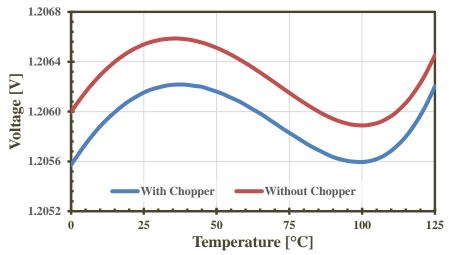

# 2.5 Design of Sub-1 V CMOS Bandgap Reference