# HIGH PERFORMANCE ON-CHIP INTERCONNECTS DESIGN FOR FUTURE MANY-CORE ARCHITECTURES

A Dissertation

by

## HYUNJUN JANG

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Eun Jung Kim     |

|---------------------|------------------|

| Committee Members,  | Paul Gratz       |

|                     | Rabi Mahapatra   |

|                     | Duncan M. Walker |

| Head of Department, | Dilma Da Silva   |

December 2015

Major Subject: Computer Engineering

Copyright 2015 Hyunjun Jang

### ABSTRACT

Switch-based Network-on-Chip (NoC) is a widely accepted inter-core communication infrastructure for Chip Multiprocessors (CMPs). With the continued advance of CMOS technology, the number of cores on a single chip keeps increasing at a rapid pace. It is highly expected that many-core architectures with more than hundreds of processor cores will be commercialized in the near future. In such a large scale CMP system, NoC overheads are more dominant than computation power in determining overall system performance. Also, for modern computational workloads requiring abundant thread level parallelism (TLP), NoC design for highly-parallel, many-core accelerators such as General Purpose Graphics Processing Units (GPGPUs) is of primary importance in harnessing the potential of massive thread- and data-level parallelism. In these contexts, it is critical that NoC provides both low latency and high bandwidth within limited on-chip power and area budgets.

In this dissertation, we explore various design issues inherent in future many-core architectures, CMPs and GPGPUs, to achieve both high performance and power efficiency. First, we deal with issues in using a promising next generation memory technology, Spin-Transfer Torque Magnetic RAM (STT-MRAM), for NoC input buffers in CMPs. Using a high density and low leakage memory offers more buffer capacities with the same die footprint, thus helping increase network throughput in NoC routers. However, its long latency and high power consumption in write operations still need to be addressed. Thus, we propose a hybrid design of input buffers using both SRAM and STT-MRAM to hide the long write latency efficiently. Considering that simple data migration in the hybrid buffer consumes more dynamic power compared to SRAM, we provide a lazy migration scheme that reduces the dynamic power consumption of the hybrid buffer.

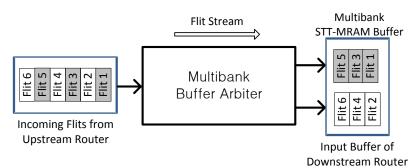

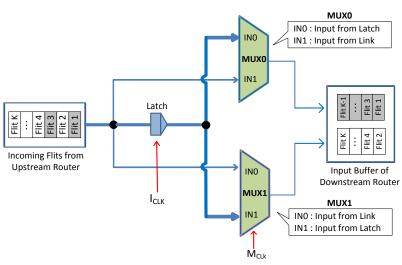

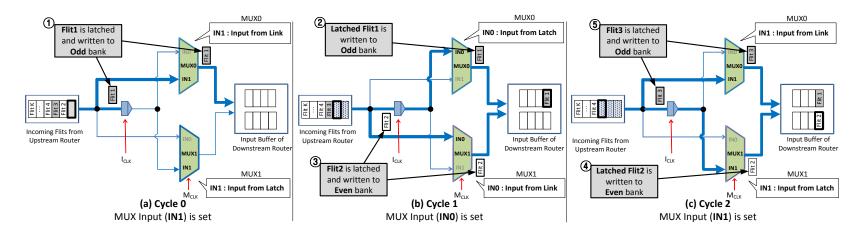

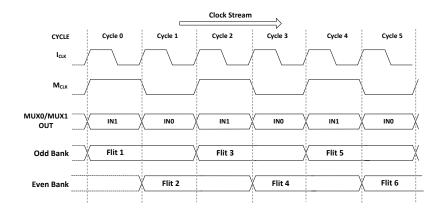

Second, we propose the first NoC router design that uses only STT-MRAM, providing much larger buffer space with less power consumption, while preserving data integrity. To hide the multicycle writes, we employ a multibank STT-MRAM buffer, a virtual channel with multiple banks where every incoming flit is seamlessly pipelined to each bank alternately. Our STT-MRAM design has aggressively reduced the retention time, resulting in a significant reduction in the latency and power overheads of write operations. To ensure data integrity against inadvertent bit flips from the thermal fluctuation during the given retention time, we propose a costefficient dynamic buffer refresh scheme combined with Error Correcting Codes (ECC) to detect and correct data corruption.

Third, we present schemes for bandwidth-efficient on-chip interconnects in GPG-PUs. GPGPUs place a heavy demand on the on-chip interconnect between the many cores and a few memory controllers (MCs). Thus, traffic is highly asymmetric, impacting on-chip resource utilization and system performance. Here, we analyze the communication demands of typical GPGPU applications, and propose efficient NoC designs to meet those demands.

#### ACKNOWLEDGEMENTS

First of all, I would like to thank my adviser, Dr. Eun Jung Kim, for her consistent and careful guidance. Her advice made it possible to complete my PhD study. I am truly grateful for her encouragement and constant motivation throughout this work. Also, I would like to thank my committee members, Dr. Paul Gratz, Dr. Rabi Mahapatra, and Dr. Duncan M. Walker. Many thanks also go to Dr. Ki Hwan Yum for his support throughout my PhD study, especially for his careful feedback on research papers. Second, I would like to thank all of the previous and current members of the High Performance Computing Laboratory, especially Minseon Ahn, Baiksong An, Lei Wang, Rahul Boyapati, Jagadish Chandar Jayabalan, Wen Yuan, Rohan Kansal, Nikhil Kulkarni, Sagar Narayanan, Kyunghoon Kim, and Jiayi Huang for supporting and helping my research. Last but not least, I am especially grateful to my wife, Ara Cho, and parents for their incredible support, patience and trust for me. Without their dedication and belief, I couldn't have completed this study.

# TABLE OF CONTENTS

|     |              | Pa                                                                                               | age                  |

|-----|--------------|--------------------------------------------------------------------------------------------------|----------------------|

| AE  | BSTR         | ACT                                                                                              | ii                   |

| AC  | CKNC         | OWLEDGEMENTS                                                                                     | iv                   |

| ТА  | BLE          | OF CONTENTS                                                                                      | v                    |

| LIS | ST O         | F FIGURES                                                                                        | vii                  |

| LIS | ST O         | F TABLES                                                                                         | xi                   |

| 1.  | INT          | RODUCTION                                                                                        | 1                    |

| 2.  |              | BRID BUFFER DESIGN WITH STT-MRAM FOR ON-CHIP INTER-                                              | 4                    |

|     | $2.1 \\ 2.2$ | Introduction                                                                                     | 4<br>7<br>7<br>8     |

|     | $2.3 \\ 2.4$ | Performance and Power Model of STT-MRAM                                                          | 9<br>11<br>11        |

|     | 2.5          | <ul> <li>2.4.1 Generic Baseline Router Architecture</li></ul>                                    | 11<br>13<br>17<br>17 |

|     | 2.6          | marks                                                                                            | 20<br>23<br>25       |

| 3.  |              | IGN AND ANALYSIS OF STT-MRAM ROUTER: TOWARDS POWER-<br>ICIENT AND RELIABLE ON-CHIP INTERCONNECTS | 26                   |

|     | 3.1<br>3.2   | Introduction                                                                                     | 26<br>30<br>30<br>31 |

|    | 3.3                                                                                      | Motiva                                                                                                                        | ation                                                                                          | 35                                                                |

|----|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|

|    |                                                                                          | 3.3.1                                                                                                                         | STT-MRAM for NoC Routers                                                                       | 35                                                                |

|    |                                                                                          | 3.3.2                                                                                                                         | Determining Proper Retention and Switching Times                                               | 36                                                                |

|    |                                                                                          | 3.3.3                                                                                                                         | Avoiding Flit Losses                                                                           | 37                                                                |

|    |                                                                                          | 3.3.4                                                                                                                         | Performance Impact Analysis                                                                    | 39                                                                |

|    | 3.4                                                                                      | STT-N                                                                                                                         | IRAM Router Architecture                                                                       | 43                                                                |

|    |                                                                                          | 3.4.1                                                                                                                         | Baseline Router Architecture                                                                   | 43                                                                |

|    |                                                                                          | 3.4.2                                                                                                                         | STT-MRAM Router Design                                                                         | 43                                                                |

|    |                                                                                          | 3.4.3                                                                                                                         | Nonvolatility-Relaxed STT-MRAM Buffer                                                          | 54                                                                |

|    | 3.5                                                                                      | Evalua                                                                                                                        | ation                                                                                          | 64                                                                |

|    |                                                                                          | 3.5.1                                                                                                                         | System Configuration                                                                           | 64                                                                |

|    |                                                                                          | 3.5.2                                                                                                                         | Performance and Power Analysis                                                                 | 65                                                                |

|    |                                                                                          | 3.5.3                                                                                                                         | Sensitivity Analysis                                                                           | 69                                                                |

|    | 3.6                                                                                      | Discus                                                                                                                        | sion $\ldots$ | 71                                                                |

|    |                                                                                          | 3.6.1                                                                                                                         | Impact of Write Delays of STT-MRAM                                                             | 71                                                                |

|    |                                                                                          | 3.6.2                                                                                                                         | Comparison with Other NoC Techniques                                                           | 72                                                                |

|    |                                                                                          | 3.6.3                                                                                                                         | Impact of End-to-End and Per-Hop Error Protection                                              | 74                                                                |

|    | 3.7                                                                                      | Relate                                                                                                                        | d Work                                                                                         | 75                                                                |

|    | 3.8                                                                                      | Other                                                                                                                         | Applications and Future Work                                                                   | 76                                                                |

|    | 3.9                                                                                      | Conclu                                                                                                                        | sions                                                                                          | 76                                                                |

|    |                                                                                          |                                                                                                                               |                                                                                                |                                                                   |

| 4. |                                                                                          |                                                                                                                               | TH-EFFICIENT ON-CHIP INTERCONNECT DESIGNS FOR                                                  | 77                                                                |

| 4. | GPC                                                                                      | GPUS                                                                                                                          |                                                                                                |                                                                   |

| 4. | GPC<br>4.1                                                                               | GPUS<br>Introd                                                                                                                | $\dots$ uction $\dots$ | 77                                                                |

| 4. | GPC                                                                                      | GPUS<br>Introd<br>Backg                                                                                                       |                                                                                                | 77<br>79                                                          |

| 4. | GPC<br>4.1                                                                               | GPUS<br>Introd<br>Backg<br>4.2.1                                                                                              | uction                                                                                         | 77<br>79<br>79                                                    |

| 4. | GPC<br>4.1<br>4.2                                                                        | PUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2                                                                                      | uction                                                                                         | 77<br>79<br>79<br>80                                              |

| 4. | GPC<br>4.1                                                                               | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Desigr                                                                           | uction                                                                                         | 77<br>79<br>79<br>80<br>81                                        |

| 4. | GPC<br>4.1<br>4.2                                                                        | PUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2                                                                                      | uction                                                                                         | 77<br>79<br>79<br>80<br>81<br>81                                  |

| 4. | GPC<br>4.1<br>4.2                                                                        | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Design<br>4.3.1<br>4.3.2                                                         | uction                                                                                         | 77<br>79<br>79<br>80<br>81<br>81<br>90                            |

| 4. | GPC<br>4.1<br>4.2<br>4.3                                                                 | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Design<br>4.3.1<br>4.3.2                                                         | uction                                                                                         | 77<br>79<br>79<br>80<br>81<br>81                                  |

| 4. | GPC<br>4.1<br>4.2<br>4.3                                                                 | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Design<br>4.3.1<br>4.3.2<br>Perfor                                               | uction                                                                                         | 77<br>79<br>80<br>81<br>81<br>90<br>99                            |

| 4. | GPC<br>4.1<br>4.2<br>4.3                                                                 | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Design<br>4.3.1<br>4.3.2<br>Perfor<br>4.4.1                                      | uction                                                                                         | 77<br>79<br>79<br>80<br>81<br>81<br>90<br>99                      |

| 4. | GPC<br>4.1<br>4.2<br>4.3                                                                 | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Desigr<br>4.3.1<br>4.3.2<br>Perfor<br>4.4.1<br>4.4.2                             | uction                                                                                         | 77<br>79<br>79<br>80<br>81<br>81<br>90<br>99<br>99<br>99          |

| 4. | GPC<br>4.1<br>4.2<br>4.3                                                                 | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Desigr<br>4.3.1<br>4.3.2<br>Perfor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4           | uction                                                                                         | 77<br>79<br>79<br>80<br>81<br>81<br>90<br>99<br>99<br>99          |

|    | <ul> <li>GPG</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul> | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Design<br>4.3.1<br>4.3.2<br>Perfor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>Relate | uction                                                                                         | 77<br>79<br>80<br>81<br>90<br>99<br>99<br>99<br>108<br>109<br>112 |

| 4. | <ul> <li>GPG</li> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul> | GPUS<br>Introd<br>Backg<br>4.2.1<br>4.2.2<br>Design<br>4.3.1<br>4.3.2<br>Perfor<br>4.4.1<br>4.4.2<br>4.4.3<br>4.4.4<br>Relate | uction                                                                                         | 77<br>79<br>80<br>81<br>90<br>99<br>99<br>99<br>108<br>109        |

## LIST OF FIGURES

# FIGURE

| 2.1  | The Two States of an MTJ Module                                                                    | 7  |

|------|----------------------------------------------------------------------------------------------------|----|

| 2.2  | Maximum Intra-Router Latency of an On-Chip Router $(SRAM \#: SRAM Buffer Size per VC)$             | 10 |

| 2.3  | Generic Router Architecture                                                                        | 11 |

| 2.4  | A Generic SRAM Input Buffer (a) and a Hybrid Input Buffer (b) $\ . \ .$                            | 12 |

| 2.5  | Simple Flit Migration Scheme in Hybrid Buffer Design                                               | 12 |

| 2.6  | CMP Layout                                                                                         | 15 |

| 2.7  | Performance Comparison with Synthetic Workloads                                                    | 18 |

| 2.8  | Performance Comparison with O1TURN Routing Algorithm                                               | 18 |

| 2.9  | Performance Comparison with Different Topologies                                                   | 19 |

| 2.10 | Performance Comparsion with Various STT-MRAM Write Latencies .                                     | 19 |

| 2.11 | Throughput with Different STT-MRAM Write Latencies                                                 | 22 |

| 2.12 | SPLASH-2 Benchmark Results                                                                         | 22 |

| 2.13 | Comparison of Power Efficiency                                                                     | 24 |

| 3.1  | Per-Application Intra-Router Latency Distribution ( <i>canneal</i> in PAR-SEC Benchmarks)          | 29 |

| 3.2  | STT-MRAM Cell Structure                                                                            | 30 |

| 3.3  | The Relationship between Switching Current and Switching Time for<br>Different MTJ Retention Times | 32 |

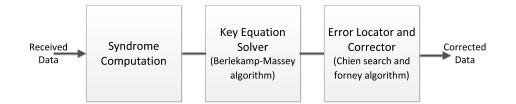

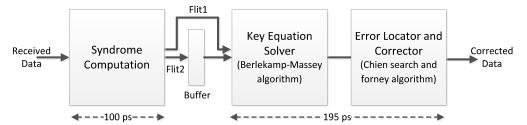

| 3.4  | BCH ECC Decoder Block Diagram                                                                      | 33 |

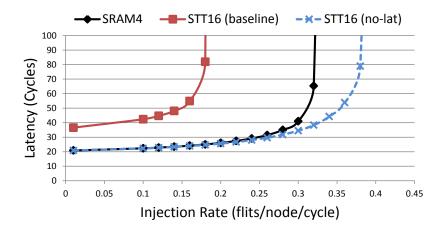

| 3.5  | Performance Comparison between SRAM and STT-MRAM Routers<br>under the Same Area Budget                                                                                                         | 35 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

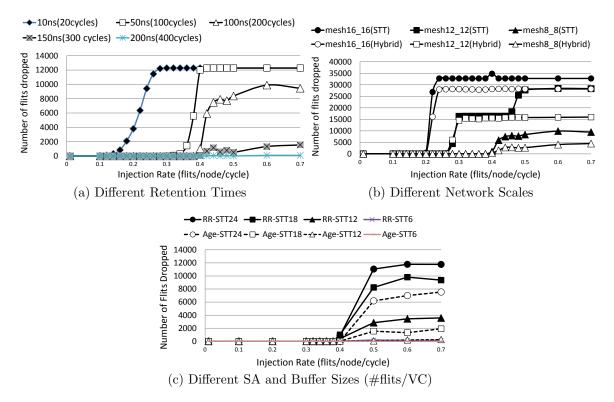

| 3.6  | Various Factors Affecting the Number of Flits Dropped                                                                                                                                          | 38 |

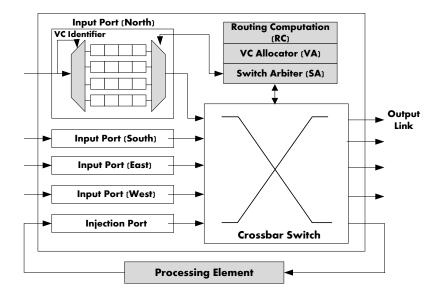

| 3.7  | Baseline Router Architecture                                                                                                                                                                   | 39 |

| 3.8  | Multibank STT-MRAM Buffer                                                                                                                                                                      | 45 |

| 3.9  | Dual-Bank STT-MRAM Buffer Example (Sequence of Operations: $(1)$ ~ $(5)$                                                                                                                       | 46 |

| 3.10 | Timing Diagram Corresponding to Figure 3.9                                                                                                                                                     | 47 |

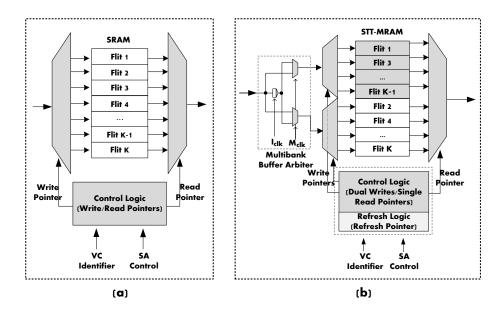

| 3.11 | A Baseline SRAM Input Buffer (a) and a Dual-Bank STT-MRAM Input Buffer (b)                                                                                                                     | 48 |

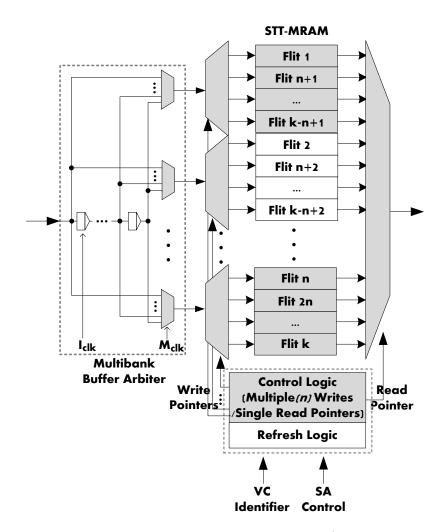

| 3.12 | A General Multibank STT-MRAM Buffer ( $k$ : Total Number of Flits<br>Buffered, To Hide <i>n</i> -cycle Write Latencies, <i>n</i> -1 Latches and <i>n</i> Banks<br>Are Needed.)                 | 51 |

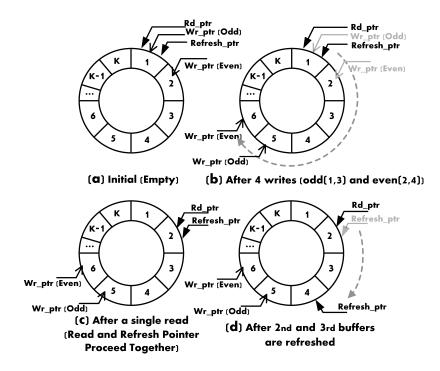

| 3.13 | Circular Queue for Dual-Bank STT-MRAM Buffer (Assuming all errors are correctable / Sequence: $(a) \sim (d)$ )                                                                                 | 52 |

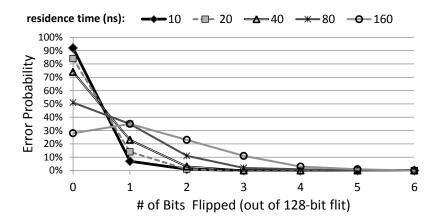

| 3.14 | Probability of the Number of Bits Flipped (Note that the sum of error probabilities under a specific residence time is $100 \%$ )                                                              | 56 |

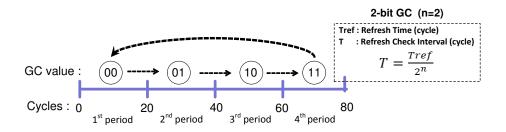

| 3.15 | An Example of a 2-bit Global Counter (GC) Refresh Logic (Assuming refresh time is 80 cycles (40 ns in 2 GHz))                                                                                  | 59 |

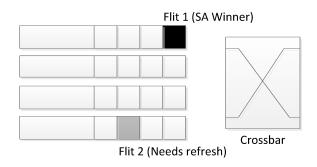

| 3.16 | Concurrent Error Protection Example                                                                                                                                                            | 59 |

| 3.17 | Two-Phase ECC for Concurrent Error Protection                                                                                                                                                  | 60 |

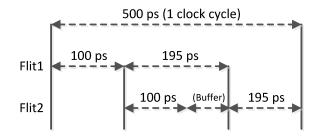

| 3.18 | Timing Diagram of Concurrent Error Protection based on Two-Phase         ECC                                                                                                                   | 60 |

| 3.19 | Performance Comparison with Different Synthetic Workloads                                                                                                                                      | 60 |

| 3.20 | Performance Comparison with Different Topologies                                                                                                                                               | 61 |

| 3.21 | Normalized Power Consumption - SRAM/Hybrid/STT-MRAM with Different Refresh Rates (Low-ECC: Low Refresh Rate (80ns) / Opt-ECC: Optimal Refresh Rate (40ns), See Section 3.4.3.1 for details.) . | 62 |

| 3.22 | PARSEC Benchmark Results (Power and Performance Graphs)                                                                                                                                        | 62 |

| 3.23 | Sensitivity Analysis                                                                                                                                                     | 68  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.24 | Normalized STT-MRAM Density under the Same Per-Router Area<br>Budget                                                                                                     | 71  |

| 3.25 | Comparisons with BLESS [48] and WPF [45] (UR) $\ldots \ldots \ldots$                                                                                                     | 72  |

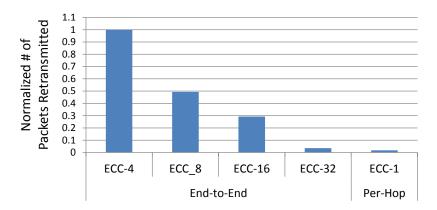

| 3.26 | Comparisons between Different ECC Schemes (End-to-End vs. Per-<br>Hop)                                                                                                   | 73  |

| 3.27 | Normalized Number of Packets Retransmitted under Different ECC<br>Schemes                                                                                                | 74  |

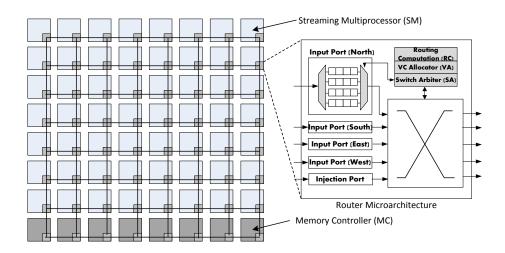

| 4.1  | GPGPU NoC Layout and Router Microarchitecture. (The NoC layout consists of many SMs and a few MCs, each of which contains an NoC router.)                                | 79  |

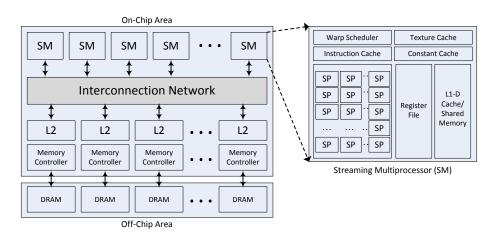

| 4.2  | GPGPU Microarchitecture and Streaming Multiprocessor (SM) $\ . \ .$ .                                                                                                    | 80  |

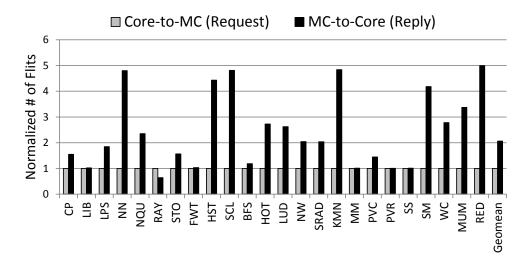

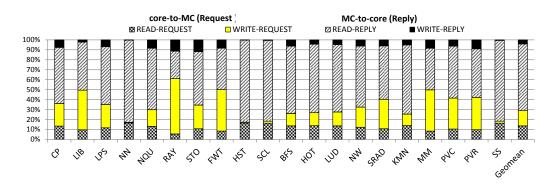

| 4.3  | Normalized Traffic Volumes Between Cores and MCs                                                                                                                         | 82  |

| 4.4  | Packet Type Distribution for GPGPU Benchmarks                                                                                                                            | 82  |

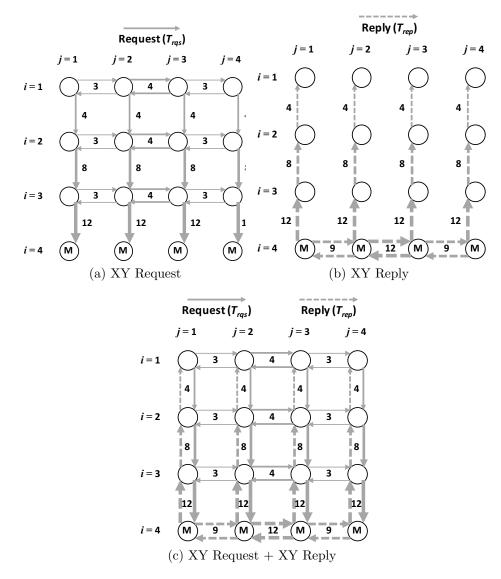

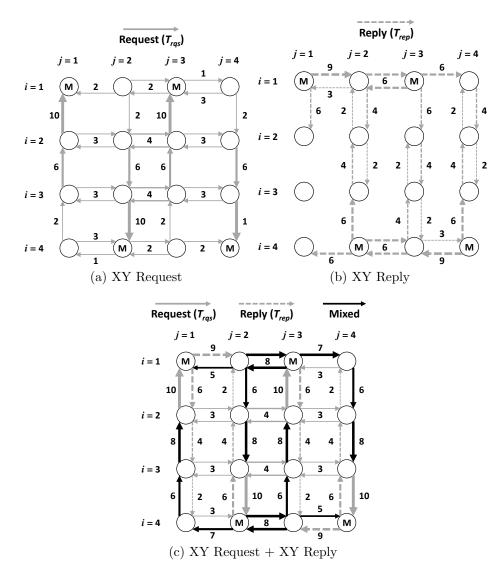

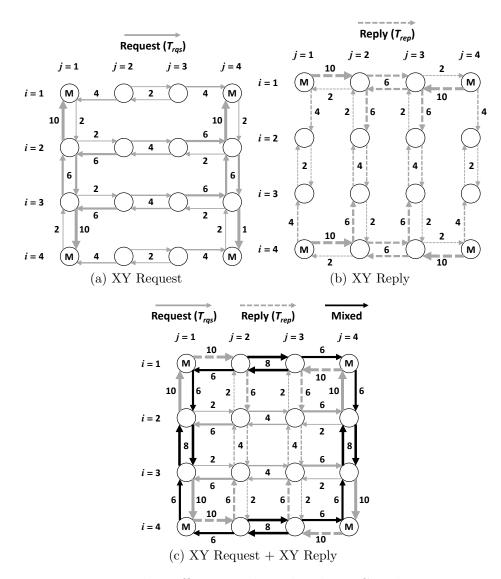

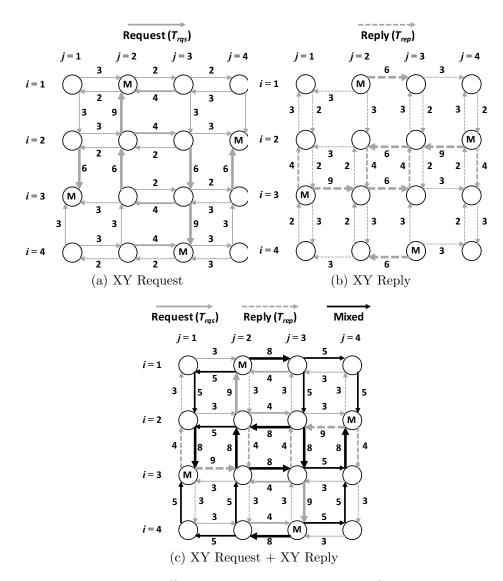

| 4.5  | Network Traffic Example with XY Routing. (Note that request (a) and reply (b) traffic take different paths, thus traffic does not mix on horizontal and vertical links.) | 93  |

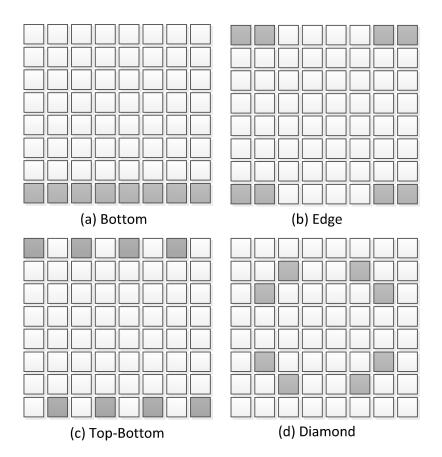

| 4.6  | Different MC Placements. (Shaded tiles represent MCs co-located with GPGPU cores.)                                                                                       | 94  |

| 4.7  | Network Traffic Example with Top-Bottom MC and XY Routing. $\ . \ .$                                                                                                     | 95  |

| 4.8  | Network Traffic Example with Edge MC and XY Routing                                                                                                                      | 96  |

| 4.9  | Network Traffic Example with Diamond MC and XY Routing                                                                                                                   | 97  |

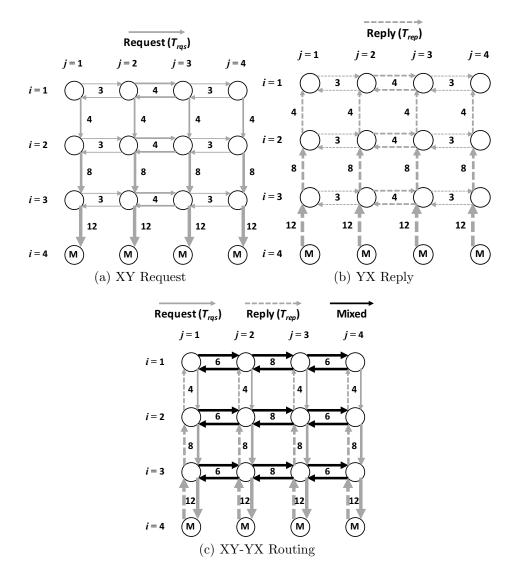

| 4.10 | Network Traffic Example with XY-YX Routing. ( <i>Note, request/reply traffic is mixed on horizontal links.</i> )                                                         | 98  |

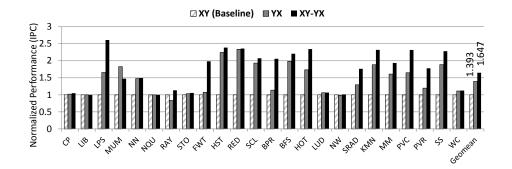

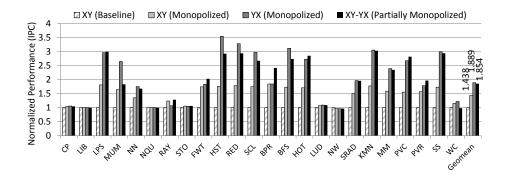

| 4.11 | Speed-up with Routing Algorithms (Normalized to baseline $XY$ )                                                                                                          | 101 |

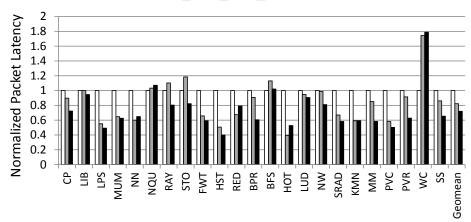

| 4.12 | Normalized Packet Latency under Different Routing Algorithms                                                                                                             | 101 |

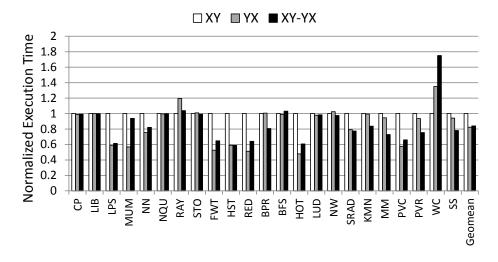

| 4.13 | Normalized Execution Time under Different Routing Algorithms                                                                                                             | 101 |

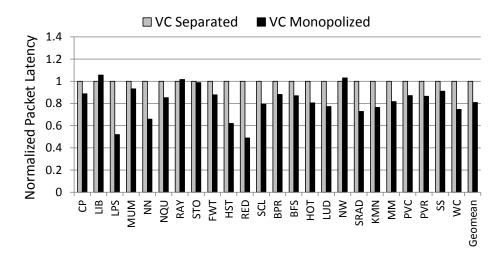

| 4.14 | Normalized Packet Latency under VC Monopolizing Scheme                                                                                                                   | 102 |

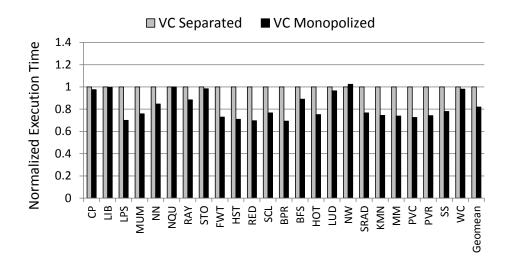

| 4.15 | Normalized Execution Time under VC Monopolizing Scheme                                                                                                                    | 103 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.16 | Speed-up with VC Monopolized Scheme (Normalized to XY routing with VC separated for each traffic)                                                                         | 104 |

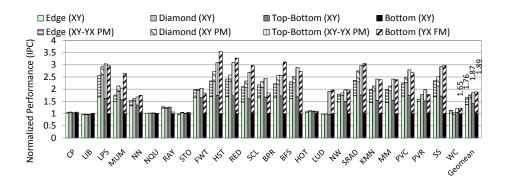

| 4.17 | Speed-up with Different MC Placements with Routing Algorithms ( <i>PM: Partial Monopolizing, FM: Full Monopolizing, Normalized to bottom <math>MC+XY</math> routing</i> ) | 104 |

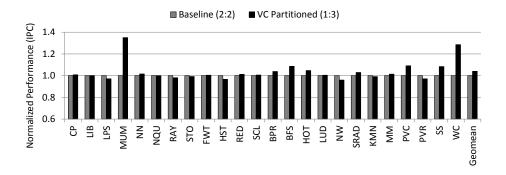

| 4.18 | Speed-up with Asymmetric VC Partitioning $(Request:Reply = 1:3)$ .                                                                                                        | 106 |

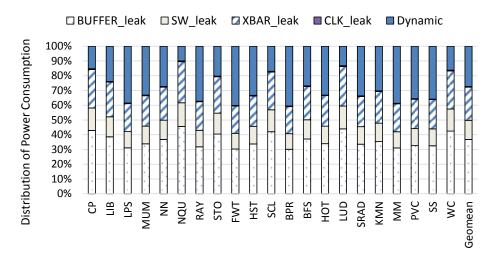

| 4.19 | Distribution of Power Consumption in NoC                                                                                                                                  | 106 |

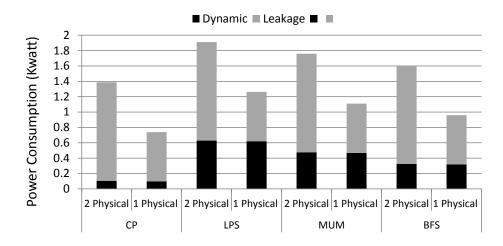

| 4.20 | Network Power Breakdown under 2 Physical vs. 1 Physical Network .                                                                                                         | 107 |

| 4.21 | Detailed Network Power Breakdown (MUM benchmark) under 2 Phys-<br>ical vs. 1 Physical Network                                                                             | 107 |

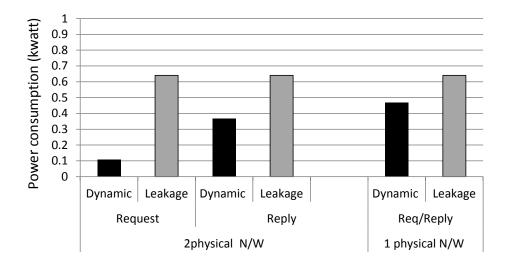

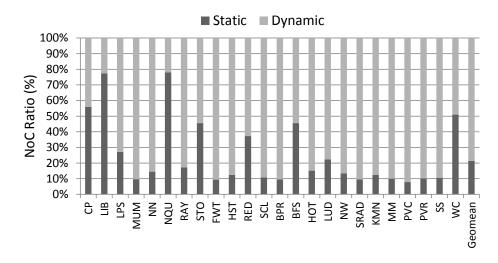

| 4.22 | NoC Static vs. Dynamic Ratio                                                                                                                                              | 108 |

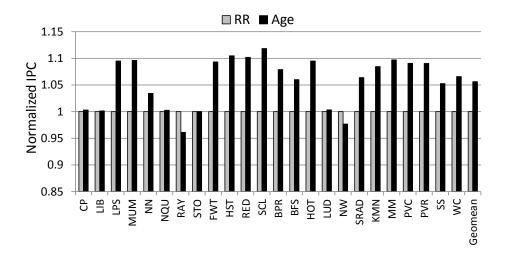

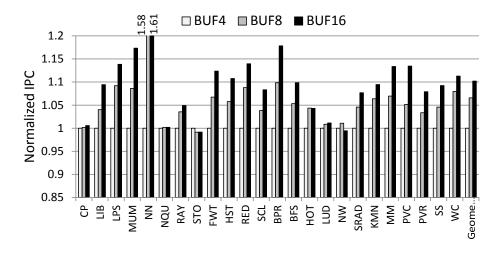

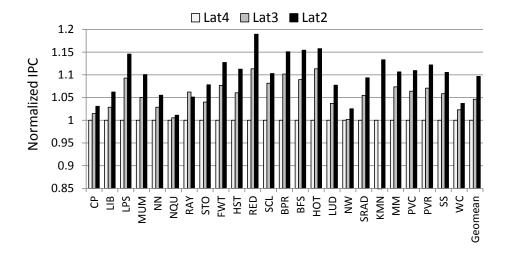

| 4.23 | Normalized IPC under Different Arbitration Policy (RR vs. Age) $~$                                                                                                        | 110 |

| 4.24 | Normalized IPC under Different Buffer Depth                                                                                                                               | 111 |

| 4.25 | Normalized IPC under Different Router Pipeline Latencies                                                                                                                  | 111 |

# LIST OF TABLES

# TABLE

## Page

| 2.1 | CMP System Configuration                                                                                                                                                                                                                   | 17  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2 | SRAM and STT-MRAM Parameters                                                                                                                                                                                                               | 17  |

| 3.1 | CMP System Configuration                                                                                                                                                                                                                   | 65  |

| 3.2 | SRAM and STT-MRAM Parameters with Different Retention Times (The Hybrid Buffer [33] utilizes 10 ms.)                                                                                                                                       | 65  |

| 4.1 | The Average Number of Vertical/Horizontal Hops under Different MC Placements in an $(N \ge N)$ Mesh $\ldots \ldots \ldots$ | 91  |

| 4.2 | System Configuration                                                                                                                                                                                                                       | 100 |

#### 1. INTRODUCTION

The ever-increasing power consumption and diminishing returns in the performance of unicore processor have led to the advent of many-core architectures. This many-core trend may lead to hundreds of cores integrated on a single chip. As the number of core counts increases, a scalable, flexible, and high bandwidth on-chip communication fabric becomes critically important. In this context, switch-based Network-on-Chip (NoC) are fast replacing buses and crossbars as the pervasive communication fabric for many-core chips. In such an NoC, an on-chip router is attached to every node and adjacent nodes are connected via local on-chip wiring. This NoCbased many-core architecture has been prevalent in Chip Multiprocessors (CMPs) domains. Also, especially for modern computational workloads such as graphics and data-intensive scientific applications necessitating abundant thread level parallelism (TLP), NoC designs for highly-parallel, many-core accelerators such as General Purpose Graphics Processing Units (GPGPUs) have emerged as an important field of research. For high performance many-core architectures, it is critical that NoC supplies high bandwidth at ultra-low latencies within a tight power and area budgets.

This dissertation addresses a number of design challenges regarding high performance NoCs for many-core architectures to achieve high performance and power efficiency. First, we present a new design of NoC router based on a next-generation memory technology, Spin-Transfer Torque Magnetic RAM (STT-MRAM) in CMPs. STT-MRAM has high density and near-zero leakage power, thus adopting STT-MRAM in NoC has significant merits in improving throughput with less power consumption. However, its long latency and high power consumption in write operations compared to those of SRAM need to be addressed. Thus, we propose a hybrid design of input buffers combining both SRAM and STT-MRAM to hide the long write latency. Also, considering that simple data migration in the hybrid buffer consumes more dynamic power compared to SRAM, we design a lazy migration scheme allowing the flit migration only when the network load exceeds a certain threshold, which helps to reduce the dynamic power consumption significantly. Simulation results show that the proposed scheme enhances the throughput by 21% on average.

Second, we propose the first NoC router design that uses only STT-MRAM in buffers, while preserving data integrity. By eliminating SRAM, it offers much larger buffer space with less power consumptions. To hide the multicycle write latencies of STT-MRAM, we propose a novel pipelined input buffer design, a multibank STT-MRAM buffer, which is a Virtual Channel (VC) with multiple banks where every incoming flit is delivered to each bank alternately via a simple latch inside a router. Through this, we can avoid performance degradation while consuming less area and power. Our STT-MRAM design also has aggressively reduced the retention time, resulting in a significant reduction in the latency and power overheads of write operations. To ensure data integrity under the limited retention time and random bit flips of STT-MRAM, we employ cost-efficient dynamic buffer refresh schemes combined with Error Correcting Codes (ECC) that are extensively used in memories and storage devices to tolerate both transient and static errors. Simulation results show that the proposed STT-MRAM NoC router improves throughput by 20.7% and achieves 17% savings in the total router power with minimum hardware overheads compared with an SRAM based NoC router.

Third, we present bandwidth-efficient on-chip interconnects designs for GPGPUs. Unlike CMP systems, where traffic tends to be uniform across the cores communicating with distributed on-chip caches, the communication in GPGPUs is highly asymmetric, mainly between many compute cores and a few memory controllers (MCs). Thus the MCs often become hot spots, leading to skewed usage of the NoC resources and network bottlenecks. We quantitatively analyze the impact of network traffic patterns in GPGPUs with different MC placements and dimension order routings. Then, based on this analysis, we suggest VC monopolizing and partitioning schemes which dramatically improve NoC resource utilization without causing protocol deadlocks. We also investigate the impact of XY, YX, and XY-YX routing algorithms under diverse MC placements. Simulation results show the proposed NoC schemes improve overall GPGPU performance by up to 64.7% over baseline. Compared to the top performing prior work, our VC monopolizing and partitioning schemes achieve a performance gain of 25% with a simple MC placement policy.

# 2. HYBRID BUFFER DESIGN WITH STT-MRAM FOR ON-CHIP INTERCONNECTS \*

### 2.1 Introduction

With the continued advance of CMOS technology, the number of cores on a single chip keeps increasing at a rapid pace. And it is highly expected that many-core architectures with more than hundreds of processor cores will be commercialized in the near future. In a large-scale chip multiprocessor (CMP) system, network overheads are more dominant than computation power in determining overall system performance. While shared buses provide networking performance enough for a small number of CMP nodes, they cannot be good solutions for many-core systems due to the limitation on scalability. Accordingly, switch-based networks-on-chip (NoCs) are being adopted as an emerging design trend in many-core CMP environments. Since all components in a chip including processors, caches and interconnects must compete for limited area and power budgets, resources available for NoCs are tightly constrained compared to off-chip interconnects. Moreover, network performance becomes more significant with the increasing scale of CMP systems. Therefore, a new and innovative NoC design that can guarantee better performance with limited resources is necessary for many-core systems.

The advance of memory technology has ushered in new non-volatile memory (NVM) designs that overcome the drawbacks of existing memories such as SRAM or DRAM. Among them, Spin-Torque Transfer Magnetic RAM (STT-MRAM) is being regarded as a promising technology for a number of advantages over the conventional

$<sup>^{*}</sup>$  ©2012 IEEE. Reprinted, with permission, from Hybrid Buffer Design with STT-MRAM for On-Chip Interconnects by Hyunjun Jang, Baik Song An, Nikhil Kulkarni, Ki Hwan Yum and Eun Jung Kim, in Networks on Chip (NoCS), May 2012

RAMs. STT-MRAM is a next-generation memory that uses magnetic materials as the main information carrier. It achieves lower leakage power and higher density compared to the existing SRAM. Also, STT-MRAM shows higher endurance compared to other NVM techniques such as Phase Change Memory (PCM) or Flash, which makes STT-MRAM more attractive for on-chip memories that must tolerate much more frequent write accesses compared to off-chip memories. However, one of the biggest weaknesses of STT-MRAM is long write latency compared to SRAM. Since the fast access time of memories on a chip must be guaranteed and cannot be negotiable, the slow write operations of STT-MRAM limit its popularity, even though it shows competitive read performance. Another serious drawback of STT-MRAM is high power consumption in write operations. This issue of high power consumption in STT-MRAM must be resolved in NoCs due to the limited power budgets.

Despite these weaknesses, using STT-MRAM in the NoC design has significant merits since an on-chip router can incorporate larger input buffers compared to SRAM with the same area budget because of the higher density of STT-MRAM. Larger input buffers contribute to improving the throughput of NoC, which results in the enhancement of overall system performance. However, the aforementioned challenges must be addressed first to exploit the benefit of STT-MRAM in NoC. Since the input buffer of an on-chip router must handle arriving flits on time, it is impossible in reality to use STT-MRAM without additional technique to hide the long write latency. Moreover, addressing the high write power issue of STT-MRAM is mandated in NoC environments.

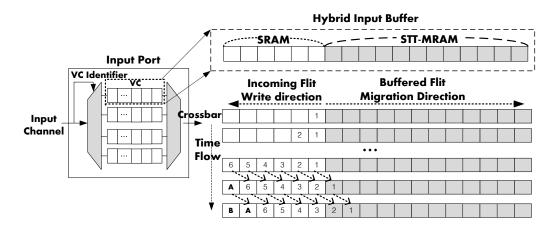

In this study, we explore the design issues of adopting STT-MRAM in on-chip interconnects. First, by relaxing the non-volatility of STT-MRAM, the latency as well as the power consumption in write operations can be reduced at the sacrifice of the retention time [34, 59]. Based on the observation of intra-router latency of flits, we find out that the retention time needed for input buffers in NoC can be significantly shortened. We exploit the write latency reducing technique [34] in the input buffers of on-chip routers, and decrease the latency to less than 2ns that corresponds to 6 cycles in 3GHz clock frequency. Then we propose a hybrid design of input buffers combining both SRAM and STT-MRAM. By allowing each arriving flit to be stored in the SRAM buffer first and then migrated to STT-MRAM, the write latency of STT-MRAM is effectively hidden, thus increasing network throughput.

Simply migrating each flit from SRAM to STT-MRAM buffer causes significant power consumption due to the high write power of STT-MRAM, compared to existing SRAM-based input buffers. So we design a lazy migration scheme that allows the flit migration only when the network load exceeds a certain threshold, which helps to reduce the power consumption significantly. Simulation results show that the hybrid input buffers improve the network throughput by 21% in synthetic workloads and 14% in SPLASH-2 parallel benchmarks on average compared to pure SRAM-based buffers with the same area overheads. Also, the lazy migration scheme contributes to power reduction by 61% on average compared to the simple migration scheme that always migrates flits from SRAM to STT-MRAM.

The remainder of this study is organized as follows. We discuss related work in Section 2.2, followed by the performance and power model of STT-MRAM in Section 3.2.2. In Section 3.4, we explain the hybrid buffer design using STT-MRAM in detail. Section 3.5 presents simulation results and analysis, and finally Section 3.9 summarizes our work and makes conclusions.

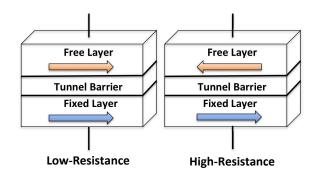

Figure 2.1: The Two States of an MTJ Module

## 2.2 Related Work

Since there has been no prior work using STT-MRAM in NoC design, we only summarize the relevant studies of STT-MRAM technologies as well as the application of NVM to diverse system domains such as processors and memories.

### 2.2.1 STT-MRAM

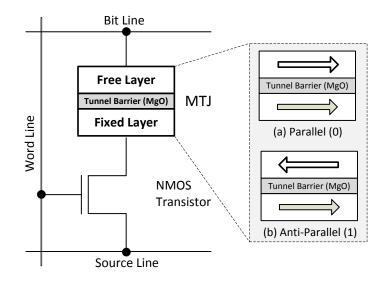

STT-MRAM is a next generation memory technology that takes advantage of magnetoresistance for storing data. It uses a Magnetic Tunnel Junction (MTJ), the fundamental building block, as a binary storage. An MTJ comprises a three-layered stack: two ferromagnetic layers and an MgO tunnel barrier in the middle. Among them, the fixed layer located at the bottom has a static magnetic spin, the spin of the electrons in the free layer at the top is influenced by applying adequate current through the fixed layer to polarize the current, and the current is passed to the free layer. Depending on the current, the spin polarity of the free layer changes either parallel or anti-parallel to that of the fixed layer. The parallel indicates a zero state, and the anti-parallel a one state. Figure 2.1 depicts the two parallel and anti-parallel states of an MTJ module. A single MTJ module is coupled with a transistor to form a basic memory cell of STT-MRAM called a 1T-1MTJ cell.

#### 2.2.2 Utilizing NVMs in Processors and Memories

Several schemes have been proposed to provide architectural support for applying NVMs to system components. Jog *et al.* [34] proposed to achieve better write performance and energy consumption of STT-MRAM-based L2 cache through adjusting data retention time of STT-MRAM. Similarly, Smullen *et al.* [59] reduced the write latencies as well as dynamic energy of STT-MRAM by lowering the retention time for designing on-chip caches. In [47], they integrated STT-MRAM into on-chip caches in a 3D CMP environment and proposed a mechanism of delaying cache accesses to busy STT-MRAM banks to hide long write latency. Prior to that, Sun *et al.* [61] stacked MRAM-based L2 caches on top of CMPs and reduced overheads through read-preemptive write buffer and hybrid cache design using both SRAM and MRAM. Guo *et al.* [26] resolved the design issues of microprocessors using STT-MRAM in detail for more power-efficient CMP systems.

PCM also has been constantly explored to replace existing SRAM or DRAMbased memory systems. Due to its lower endurance compared to SRAM or STT-MRAM, PCM is mainly adopted for off-chip memories rather than on-chip caches. Several designs of PCM-based main memory were discussed in [73, 53, 42]. In [52], adaptive write cancellation and write pausing policies were proposed to reduce energy and improve performance. Zhou *et al.* [72] suggested a new memory scheduling scheme that allows Quality-of-Service (QoS) tuning through request preemption and row buffer utilization.

#### 2.3 Performance and Power Model of STT-MRAM

As an area model of STT-MRAM, we use ITRS 2009 projections [32] as well as the model used in [26], where a 1T-1MTJ cell size is  $30F^2$  in the 32nm technology. When we assume that an SRAM cell size is approximately  $146F^2$  with the same technology, one SRAM cell can be substituted by at least four STT-MRAM cells under the same area budget. Also, about 3.2ns of write latency can be achieved with  $30F^2$  STT-MRAM cell size [26]. It corresponds to 10 cycles in 3GHz clock frequency, which is quite long for on-chip routers compared to SRAM that completes both read and write accesses in a single cycle. Reducing retention time from 10 years to 10ms guarantees the same write latency with one third of original write current needed [34]. Using lower current is beneficial in terms of area overheads because it facilitates to implement STT-MRAM cells with smaller transistors, which reduces actual cell area.

In this study, we slightly increase write current to reduce this write latency of STT-MRAM further. The write latency reduces from 3.2ns to 1.8ns through increasing the write current from  $50\mu$ A to  $75\mu$ A under 125 °C of a temperature. Note that even this increased current is far less than the original current needed for 10 years of retention time, while maintaining the same STT-MRAM cell size,  $30F^2$ . Also, the increased current does not hurt write energy consumption since the MTJ switching time decreases accordingly [26]. As a result, the write latency decreases from 10 to 6 cycles in 3GHz clock frequency. The increased write current may hurt the performance in terms of read latency. However, we verify that the reduction of write latency from 3 to 1.8ns affects the read latency to only a small extent [59]. Therefore, we can assume that the increased read latency can still be covered by a single cycle, considering the original read delay of 122ps [26], which is far shorter than 333ps, a

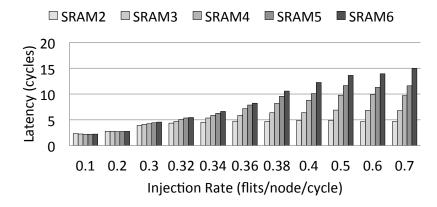

Figure 2.2: Maximum Intra-Router Latency of an On-Chip Router (SRAM#: SRAMBuffer Size per VC)

cycle time in 3GHz clock frequency.

The relaxed retention time of 10ms may hurt the reliability of data stored in an STT-MRAM buffer, if the retention time is shorter than the intra-router delay of a flit, defined by the time difference between arrival time at the buffer and departure time in a router. Figure 2.2 depicts maximum intra-router latency for different injection rates ranging from 0.1 to 0.7 with various SRAM buffer sizes per VC, under uniform random synthetic workloads. We observe that the latency does not go up beyond 16 cycles, and it is almost negligible compared to 10ms, which corresponds to more than 30 million cycles in 3GHz clock frequency <sup>1</sup>. Hence, it is confirmed that even the reduced retention time is completely enough to hold a flit in STT-MRAM buffers safely. For the read and write energy model of STT-MRAM, we conservatively adopt the same parameters from [26], 0.01pJ and 0.31pJ per bit for read and write, respectively. Note that these are based on 3.2ns of write latency, so actual write energy becomes smaller after decreasing the latency to 1.8ns.

<sup>&</sup>lt;sup>1</sup>Note that in deadlock situations, packets can stay in the network forever. In this study, we adopt deadlock-free routing algorithms, thus avoiding such situations.

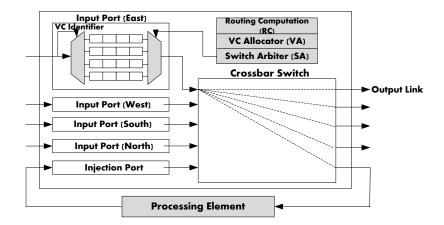

Figure 2.3: Generic Router Architecture

### 2.4 An On-Chip Router Architecture with Hybrid Buffer Design

In this section, we describe a generic router architecture and a buffer structure in NoC and present our hybrid buffer design that maximizes the mutually complementary features of the two different memory technologies, SRAM and STT-MRAM, while minimizing the drawbacks of STT-MRAM, the long latency and high power consumption in write operations.

### 2.4.1 Generic Baseline Router Architecture

The generic NoC router architecture is depicted in Figure 2.3. It is based on the state-of-the-art speculative router architecture [51]. Each arriving flit goes through 2 pipeline stages in the router: routing computation (RC), VC allocation (VA) and switch arbitration (SA) at the first cycle, and switch traversal (ST) at the second cycle. A lookahead routing scheme [23] is adopted, which generates routing information of the downstream router for an incoming flit prior to the buffer write, thus removing the RC stage from the critical path. Each router has multiple VCs per input port and uses flit-based wormhole switching [14]. Credit-based VC flow control [13] is

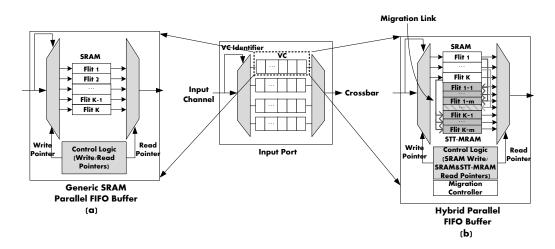

Figure 2.4: A Generic SRAM Input Buffer (a) and a Hybrid Input Buffer (b)

Figure 2.5: Simple Flit Migration Scheme in Hybrid Buffer Design

adopted to provide the back-pressure from downstream to upstream routers, thus controlling flit transmission rate to prevent packet loss due to buffer overflow.

Due to the limited area and power resources and ultra-low latency requirements, on-chip routers rely on very simple buffer structure. VC-based NoC routers consist of a number of FIFO buffers per input port where each FIFO corresponds to a VC as illustrated in Figure 2.4(a). Each input port has v VCs, each of which has a k-flit FIFO buffer. Current on-chip routers have small buffers to minimize area overheads, thus v and k are much smaller than in macro networks. The necessity for ultra-low latency leads to a parallel FIFO buffer design as shown in Figure 2.4. Contrary to a serial FIFO implementation, the parallel structure eliminates unnecessary intermediate processes for a flit to traverse all buffer entries until it leaves the buffer [70]. This fine-grained control requires more complex logic, which manages read and write pointers to keep the FIFO order. The read and write pointers in the parallel FIFO registers control an input demultiplexer and an output multiplexer. The write pointer points to the tail of the queue, and the read pointer points to the head of the queue. For a read operation, the flit pointed by the head is selected and transmitted to a crossbar input port. Similarly, write operation leads the incoming flit to be written to the location pointed by the tail pointer. The pointers are promptly updated after each read or write operation. After a read operation, once the head is overlapped with the tail, the buffer becomes empty. After a write operation, likewise, if the tail moves to the same position pointed by the head, the buffer is full.

## 2.4.2 An On-Chip Router Architecture with Hybrid Buffer Design

In this section, we show an on-chip router architecture with hybrid buffer design that combines SRAM and STT-MRAM. The hybrid design aims to maximize advantages inherent in different memory technologies in a synergistic fashion for performance improvement while consuming power economically. The key idea is inspired by the nature of STT-MRAM that provides 4 times more buffer space than SRAM under the same area constraint due to its higher density characteristics [26, 74]. The increased buffer size contributes to making on-chip routers have spacious rooms for buffering, thus boosting the overall network throughput with no additional area overheads compared to a pure SRAM-based input buffer.

Figure 2.4(b) depicts the proposed hybrid input buffer of a VC. Compared to the pure SRAM buffer shown in Figure 2.4(a), the STT-MRAM is attached to each VC in parallel with the SRAM buffer. Each SRAM buffer entry is connected to *m* dedicated STT-MRAM buffer entries through separate migration links. The hybrid parallel FIFO buffer maintains read/write pointers. An incoming flit is first written to the SRAM buffer, thus the write pointer points to SRAM buffer entries only. But an outgoing flit may leave from either SRAM or STT-MRAM and the read pointer covers the entire buffer, both SRAM and STT-MRAM buffer entries.

A migration controller triggers the flit migration and determines if a certain flit is ready to be migrated to STT-MRAM. VC flow control is performed based on the availability of SRAM in downstream routers, meaning that the availability of STT-MRAM is not considered, because a write operation to STT-MRAM cannot finish in a single cycle.

## 2.4.2.1 Simple Flit Migration Scheme

The key design goal of the hybrid input buffer is to guarantee seamless read and write operations in every cycle to achieve higher throughput with an increased buffer size. To serve this purpose, we devise a flit migration scheme, which seamlessly migrates buffered flits from SRAM to STT-MRAM to secure more SRAM buffer space for incoming flits, while hiding the long write latency of STT-MRAM.

Figure 2.6: CMP Layout

Figure 2.5 depicts an example of the migration scheme, where each VC consists of 6 SRAM and 12 STT-MRAM buffer entries. The STT-MRAM buffer write latency is assumed to be 6 cycles. When an incoming flit arrives, it is written to the SRAM buffer first, and the migration from SRAM to STT-MRAM begins immediately. Supposing that a new flit arrives every cycle, the SRAM buffer becomes full eventually in the 6th cycle. At the same time, the first flit is migrated to STT-MRAM successfully and one SRAM buffer entry becomes available. Then a subsequent incoming flit occupies the released SRAM buffer entry with no additional timing delay. Note that Figure 2.5 illustrates the concept in a logical way, and no physical shift occurs except the migration from SRAM to STT-MRAM. The placement of flits in STT-MRAM is logical and is not the physical placement described in Figure 2.4(b).

### 2.4.2.2 Power-Efficient Lazy Migration

In the simple migration scheme explained in the previous section, the migration begins immediately as soon as an incoming flit arrives at the SRAM buffer. The simple migration wastes lots of power in a low network load because most of the flits initially written to SRAM leave the buffer in the middle of migration to STT-MRAM.

Based on this observation, we propose a **lazy migration scheme**, which selectively triggers the migration of a flit based on the estimated network load per VC in the on-chip router. The network load is indirectly estimated by tracking the number of flits in the SRAM buffer. If the ratio of the number of flits in the SRAM buffer to the total SRAM buffer size exceeds a certain predefined threshold level, the flit migration is performed for every subsequent incoming flit as long as the the ratio exceeds the threshold. In this way, we can save total write power associated with the migration operation.

To implement the lazy migration scheme, the migration controller is augmented to keep track of the flits in the SRAM buffer and triggers the migration adaptively. The write power is reduced by up to 79% in a low network load compared to the simple migration, which will be discussed in detail in Secton 3.5.

| System Parameters  | Details                     |

|--------------------|-----------------------------|

| Clock frequency    | 3GHz                        |

| # of processors    | 32                          |

| L1 I and D caches  | direct-mapped 32KB (L1I)    |

|                    | 4-way 32KB (L1D), 1 cycle   |

| L2 cache           | 16-way $16MB$ , $20$ cycles |

|                    | 32 banks, $512$ KB/bank     |

| Cache block size   | 64B                         |

| Coherence protocol | Directory-based MSI         |

| Memory latency     | 300 cycles                  |

| Flit size          | 16B                         |

|                    | 1 flit (Benchmark-control)  |

| Packet size        | 5 flits (Benchmark-data)    |

|                    | 4 flits (Synthetic)         |

Table 2.1: CMP System Configuration

Table 2.2: SRAM and STT-MRAM Parameters

| Parameter              | SRAM  | STT-MRAM |

|------------------------|-------|----------|

| Read Energy (pJ/flit)  | 5.25  | 3.826    |

| Write Energy (pJ/flit) | 5.25  | 40.0     |

| Leakage Power (mW)     | 0.028 | 0.005    |

#### 2.5 Performance Evaluation

In this section, we evaluate the proposed hybrid on-chip router to examine how much it improves the overall network performance while reducing the power consumption in NoC, using several benchmarks and synthetic workloads.

## 2.5.1 System Configuration

A cycle-accurate NoC simulator is used to conduct the detailed evaluation of the proposed scheme. It implements the pipelined router architecture with VCs, a VC arbiter, a switch arbiter and a crossbar. Under the 32nm process technology, all simulations are performed in an 8x8 network having 32 out-of-order processors and 32 L2 cache banks on a single chip as shown in Figure 2.6. The network is

Figure 2.7: Performance Comparison with Synthetic Workloads

Figure 2.8: Performance Comparison with O1TURN Routing Algorithm

Figure 2.9: Performance Comparison with Different Topologies

Figure 2.10: Performance Comparison with Various STT-MRAM Write Latencies

equipped with 2-stage speculative routers with lookahead routing [23]. The router has a set of v VCs per input port. Each VC contains a k-flit buffer with 16B flit size. In our evaluation, we assume that v is 4, and k may vary with different buffer configurations. A dimension order routing algorithm, XY, and O1TURN [58] are used with wormhole switching flow control.

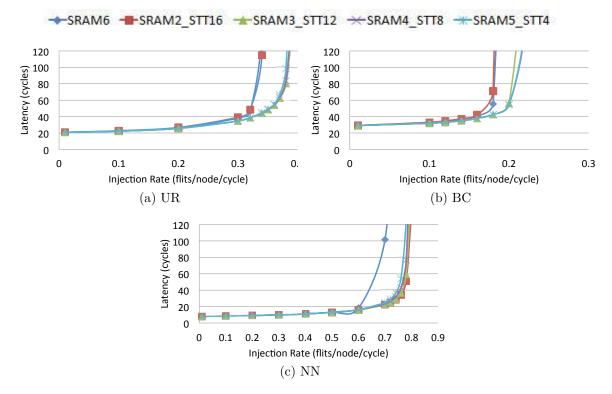

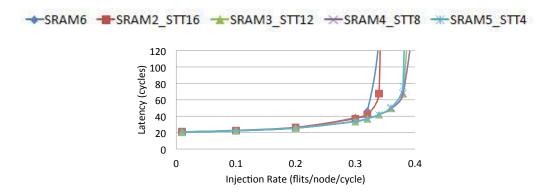

A variety of synthetic workloads are used to measure the effectiveness of the hybrid on-chip router: uniform random (UR), bit complement (BC) and nearest neighbor (NN). To evaluate the proposed schemes under realistic environments, we also use SPLASH-2 [57] parallel benchmark traces. The traces are obtained using Simics [46], a full system simulation platform. Table 3.1 specifies the detailed CMP configuration we use to run benchmarks.

We use Orion 2.0 [35] to estimate router power consumption. In addition, parameters shown in Table 3.2 are cited from [32, 26], for both SRAM and STT-MRAM. The unit of parameter for the leakage power is mW per 1-flit buffer. Throughout this study, the size of SRAM and STT-MRAM buffers are denoted by SRAM# and STT#, respectively. As stated in Section 2.4.2, STT-MRAM provides 4 times more buffer space compared to SRAM under the same area budget, thus SRAM1 is equal to STT4. Unless otherwise stated, the write latency of STT-MRAM is 6 cycles based on the analysis in Section 3.2.2.

### 2.5.2 Performance Analysis with Synthetic Workloads and Benchmarks

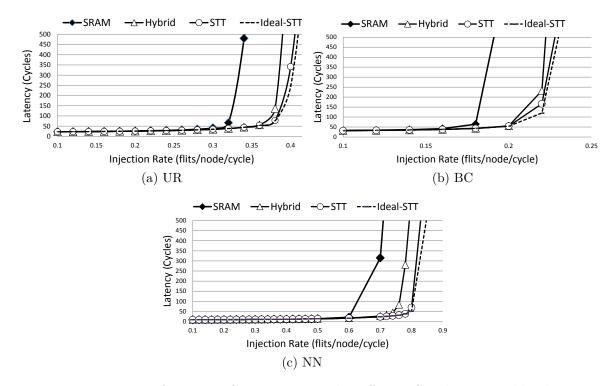

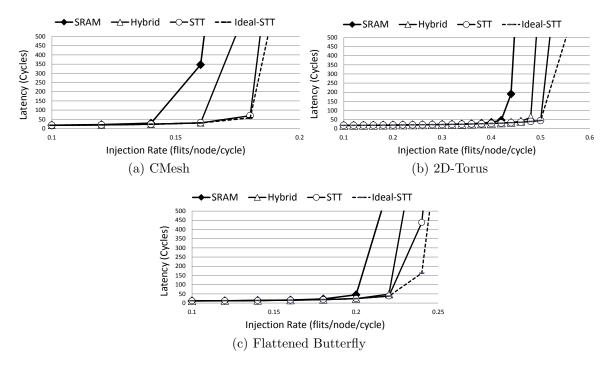

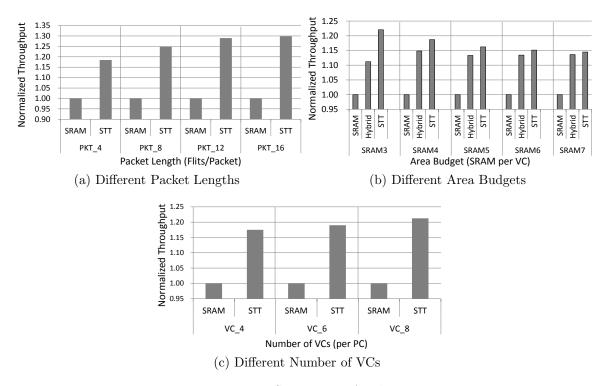

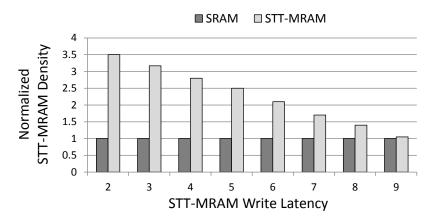

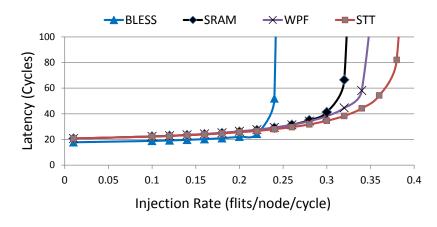

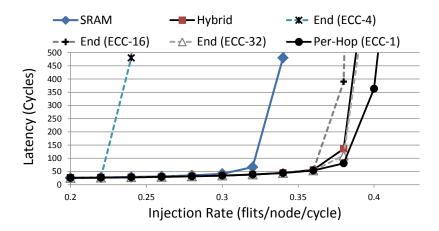

Figure 2.7 shows performance improvement for various hybrid input buffer configurations compared to the pure SRAM buffer, under UR, BC and NN traffic patterns. All results are measured under the same area budget, *SRAM6* per VC, for input buffers. In all cases, the hybrid design shows throughput improvement by 18% for UR, 28% for BC, and 17% for NN on average. These results indicate that although the STT-MRAM write latency is longer than that of SRAM, the performance loss is offset by the increased buffer size due to the high density of STT-MRAM, thus resulting in performance improvement.

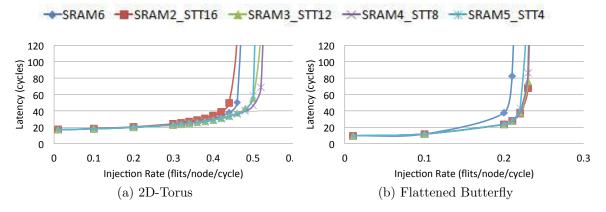

We also evaluate the hybrid design using O1TURN [58] routing algorithm as well as various topologies: 2D-torus and flattened butterfly [38]. Figure 2.8 shows the performance with O1TURN in the 8x8 2D-mesh topology, where the overall throughput increases by 15% on average, while Figure 2.9 shows that the throughput is increased in 2D-torus and flattened butterfly by 13% and 15%, respectively.

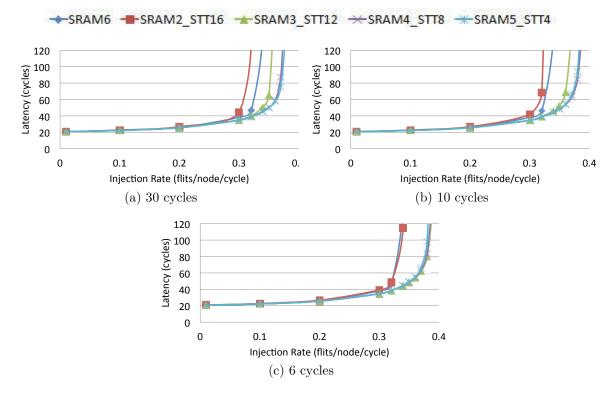

To examine the impact of different write latencies of STT-MRAM on network performance, we conduct experiments under 2D-mesh and XY routing algorithm. Figure 2.10 shows the performance in terms of packet latency with 3 different write latencies of STT-MRAM: 30, 10, and 6 cycles. It clearly indicates that the overall network performance is affected by the duration of STT-MRAM write operation. Among the different hybrid configurations, *SRAM2\_STT16* shows the worst performance. This is because the SRAM buffer space is too small to retain the incoming flits for sufficient period of time for migration, 6 cycles, which makes the simple flit migration scheme less efficient. Thus, the long write latency of STT-MRAM is not effectively hidden, resulting in the early saturation of the network. As shown in Figure 2.2, every flit stays in the buffer for at least 3 cycles. So the SRAM buffer size should be greater than or equal to 3 to run the migration scheme seamlessly.

If the write latency is long, 30 cycles, the performance is mostly determined by the SRAM size. This is because the long write latency lowers the possibility for flits to be migrated to the STT-MRAM buffer before network saturation. Therefore, *SRAM5\_STT4* shows the best throughput improvement. On the contrary, if the write latency is sufficiently short, 6 cycles, the performance is greatly impacted by the total buffer size including both SRAM and STT-MRAM except the *SRAM2\_STT16* case.

Figure 2.11: Throughput with Different STT-MRAM Write Latencies

Figure 2.12: SPLASH-2 Benchmark Results

Thus, *SRAM3\_STT12* shows the highest throughput compared to other configurations.

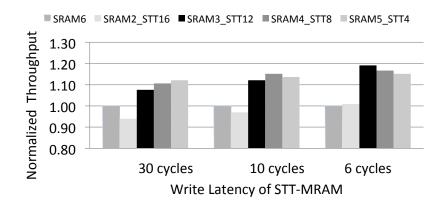

To make a clear quantitative comparison of relative performance of the 3 different write latencies, we show network throughput normalized to the SRAM6 in Figure 2.11, based on the results in Figure 2.10. Figure 2.11 confirms the aforementioned analysis. In case of a relatively long write latency, 30 cycles, the hybrid input buffer having the largest SRAM buffer outperforms the others by up to 11% compared to the pure SRAM6 buffer. Likewise, in case of a low write latency, 6 cycles, except the  $SRAM2\_STT16$  case, the one having the largest total buffer size,  $SRAM3\_STT12$  beats the other configurations by up to 18% in terms of network throughput.

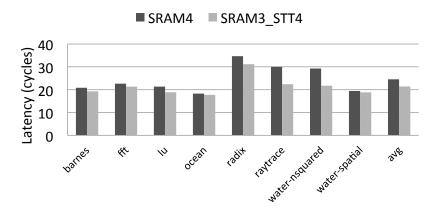

Figure 2.12 shows the average network latency with SPLASH-2 benchmark traces. We assume *SRAM4* per VC as an area budget, the same as a cache block size. In general, the hybrid input buffer outperforms the pure SRAM-based one, by approximately 14% on average. Specifically, *water-nsquared* shows the best improvement by 34.5% while *ocean* shows the least improvement by 3.2%. The amount of improvement varies depending on the traffic patterns. We observe that in the benchmarks showing higher improvement, hot spots exist in their communication, whereas in the benchmarks with slight performance improvement, communication is evenly spread across the whole network.

Finally, we make a sensitivity analysis of the number of buffer entries in NoC routers. Under two different area budgets, *SRAM4* and *SRAM6*, we compare the throughput of the pure SRAM-based buffer and the hybrid buffer that shows the best performance. As the budget decreases from *SRAM6* to *SRAM4*, the amount of improvement coming from the hybrid buffer increases by approximately 5.5%. This trend indicates that the hybrid buffer is more beneficial as the area budget in CMP environments becomes tighter.

### 2.5.3 Power Analysis

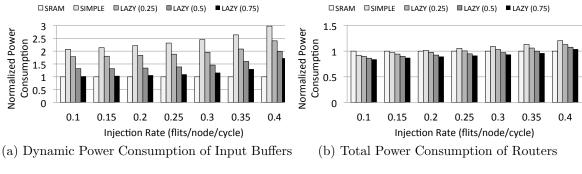

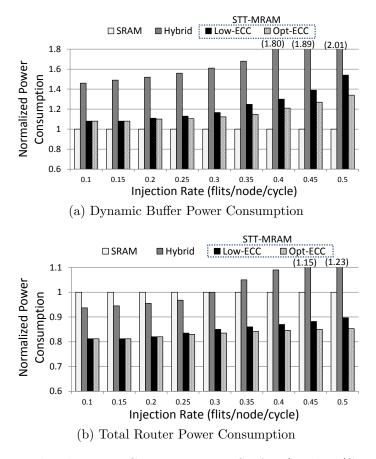

Since power is one of the main issues in the NoC router design, we evaluate power consumption of the hybrid input buffer and compare the effect of the two migration schemes explained in Section 3.4. Figure 2.13a compares the dynamic buffer power consumption of 4 different migration schemes in  $SRAM3\_STT12$ : simple and lazy with 3 different thresholds (0.25/0.5/0.75). All results are normalized to that of the

Figure 2.13: Comparison of Power Efficiency

pure SRAM-based buffer, *SRAM6*. The lazy migration scheme with the threshold 0.75 consumes significantly less amount of power, by 53% on average, compared to the simple migration scheme. In a low network load (0.1), the power consumption of the lazy migration scheme with the threshold 0.75 is almost equivalent to that of the baseline SRAM. In a high network load (0.4), however, the flit migration occurs more frequently in the hybrid buffer due to the highly congested network. Accordingly, the migration lowers the possibility of reducing the dynamic power, thus increasing the power consumption of the lazy migration by up to 1.7x more than the baseline SRAM.

Figure 2.13b compares the total router power consumption of the 4 migration schemes that includes both leakage and dynamic power consumption of all routers across the network. In a low network load (0.1), the total power consumption of routers with the hybrid buffer is less than that of routers with the pure SRAM buffer by 16%. This is due to much less leakage power consumption of STT-MRAM compared to SRAM as shown in Table 3.2. As the network gets more congested, however, the hybrid buffer consumes more power compared to the baseline SRAM buffer. In a high network load (0.4), for instance, the lazy migration scheme with the threshold 0.75 consumes more power by up to 4% compared to the baseline SRAM.

#### 2.6 Conclusions

In the deep sub-micron era, NoC has surfaced as a promising solution to reduce wiring delays and provide significant scalability in future many-core architecture. The NoC performance is heavily affected by the routers' buffer size and their efficient utilization. In this study, we have proposed a hybrid input buffer design using STT-MRAM with SRAM to achieve better network throughput with marginal power overheads in on-chip interconnection networks. The high density of STT-MRAM facilitates to accommodate larger buffer compared to the conventional SRAM under the same area budgets. Through the flit migration schemes, the long write latency of STT-MRAM is effectively hidden while minimizing the power overheads.

Simulation results indicate performance improvement of around 21% and 14% on average under the synthetic workloads and benchmarks, respectively, compared to the conventional on-chip router with the SRAM input buffer.

For future work, we intend to devise an STT-MRAM-aware routing algorithm and provide an architectural support to reduce the overall power consumption and latency further.

# 3. DESIGN AND ANALYSIS OF STT-MRAM ROUTER: TOWARDS POWER-EFFICIENT AND RELIABLE ON-CHIP INTERCONNECTS

#### 3.1 Introduction

Switch-based Network-on-Chip (NoC) has become a popular architecture orchestrating chip-wide communication in Chip Multiprocessors (CMPs). NoC should be carefully designed due to its inherent constraints of the restricted power and area budgets in a chip. NoC consumes up to 28% of the chip power, and among the different components comprising on-chip interconnects, buffers are the largest leakage power consumers in NoC routers, consuming about 68% of the total router leakage power [18]. Buffers also consume significant dynamic power [65], and this consumption increases rapidly as data flow rates increase. Consequently, designing an innovative buffer structure plays a crucial role in architecting high performance and low power on-chip interconnects.

Spin-Transfer Torque Magnetic RAM (STT-MRAM) [59, 62] is a promising next generation memory technology that can replace conventional RAMs due to its nearzero leakage power and high density. Adopting STT-MRAM in NoC has significant merits since an on-chip router can provide larger input buffers under the same area budget compared with conventional SRAM routers. Thus, STT-MRAM input buffers contribute to improving throughput, which results in enhanced system performance with less power consumption. STT-MRAM is CMOS-compatible, and provides virtually infinite write endurance [26] compared with other memory technologies such as Phase Change Memory (PCM), Flash, and Memristor. This makes STT-MRAM a more viable solution as an on-chip memory that should tolerate frequent write accesses. Besides, STT-MRAM is immune to the radiation induced soft errors, thus providing robust cell storages, and can scale beyond 10 *nm* technology [21]. However, the weaknesses of STT-MRAM, long latency and high power consumption in write operations and thermal fluctuation-induced random bit flips, should be properly addressed because fast accesses to on-chip memories that guarantee data integrity must be assured for high performance and reliable NoCs.

For addressing the write speed and energy limitations of STT-MRAM, several studies have been performed in designing caches and NoC routers. An adaptive block placement and migration policy for hybrid STT-RAM and SRAM last level caches has been proposed in [66]. A region-based hybrid cache [69] with small fast SRAM and large slow MRAM mitigates performance degradation and energy overheads. For NoC routers, an SRAM/STT-MRAM hybrid buffer [33] shows substantial throughput improvements across various workloads. However, the inevitable use of SRAM to hide the multicycle writes of STT-MRAM sacrifices area, and wastes significant dynamic power in migrating data between the disparate memories. The leakage power overhead due to SRAM also increases as network scale grows and technology scales down.

Thermal stability is another key issue of STT-MRAM, determining how much stability STT-MRAM can provide against thermal fluctuation, thus directly impacting data integrity [16]. Even under a high thermal stability, however, we cannot totally avoid the occurrence of bit flips because of the stochastic nature of STT-MRAM [49]. Therefore to ensure data integrity we need to provide proper measures for detecting and correcting such transient errors in STT-MRAM. Prior approaches have evaluated the impacts of thermal fluctuation on STT-MRAM reliability, and proposed schemes ensuring data integrity for caches and off-chip storages [16, 12]. Their schemes, however, cannot be directly applicable to NoCs since they are designed for memories having longer data residence time and larger capacities compared to those of latency-sensitive, area- and power-limited buffers in NoCs.

In this study, we propose the first NoC router design that uses only STT-MRAM in buffers, while preserving data integrity. By eliminating SRAM, it offers much larger buffer space with less power consumptions. To hide the multicycle write latencies of STT-MRAM, we propose a novel pipelined input buffer design, a multibank STT-MRAM buffer, which is a virtual channel (VC) with multiple banks where every incoming flit is delivered to each bank alternately via a simple latch inside a router. Through this, we can avoid performance degradation while consuming less area and power.

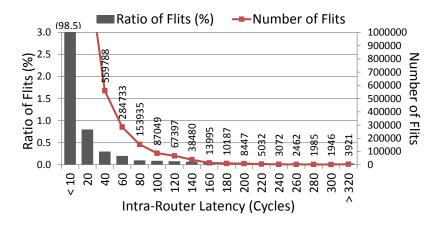

We use the write latency reduction technique [62], which sacrifices the data retention time of an Magnetic Tunnel Junction (MTJ), a bit storage of STT-MRAM. This can be possible due to the short intra-router latency<sup>1</sup> of a flit in on-chip routers. In our simulation, the average intra-router latency in PARSEC benchmarks in an (8x8) mesh network is less than 3 cycles<sup>2</sup>. However, for applications that exhibit bursty communication and heavy loads, we observe that flits are staying in STT-MRAM buffers longer than a given retention time, increasing the possibilities of flit losses due to the expired retention period. This is because some flits have fairly high intra-router latencies while most of the flits are clustered around low intra-router latencies less than 10 cycles as shown in Figure 3.1. These lost flits incur noticeable performance losses especially when the flits are parts of control packets carrying critical cache coherence information. On average, 78.7% of traffic is such single-flit control packets in PARSEC benchmarks [45]. Therefore, to ensure data integrity under the limited retention time and random bit flips of STT-MRAM, we propose cost-efficient dynamic buffer refresh schemes, the processes in which cells' values are

<sup>&</sup>lt;sup>1</sup>An intra-router latency is the time interval between the arrival of a flit at an input buffer and the departure from a router through a crossbar.

<sup>&</sup>lt;sup>2</sup>See Section 3.5 for detailed system configuration.

Figure 3.1: Per-Application Intra-Router Latency Distribution (*canneal* in PARSEC Benchmarks)

kept valid by triggering refreshes in a timely manner. Note that refreshes are performed in tandem with Error Correcting Codes (ECC) that are extensively used in memories and storage devices to tolerate both transient and static errors [60]. ECCs detect and correct data corruption, thus mitigating the impacts of random bit flips on NoCs.

The main contributions of this study are as follows:

- We present a detailed analysis on design tradeoffs of an MTJ especially in terms of write performance, write power, and retention time, which are suitable for performance- and power-efficient NoCs.

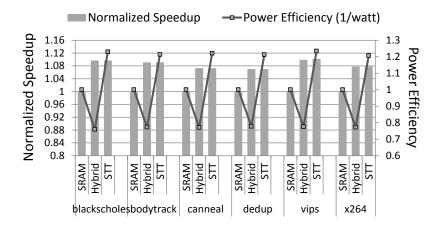

- We propose a novel multibank input buffer design, which is implemented entirely with STT-MRAM and delivers optimal power saving (17%) and performance improvement (20.7%) compared to a conventional SRAM router.

- We suggest a cost-efficient buffer refresh scheme combined with ECC: a global counter refresh scheme, which periodically checks and restores data integrity in buffers, maintaining the validity of flits.

Figure 3.2: STT-MRAM Cell Structure

### 3.2 Background

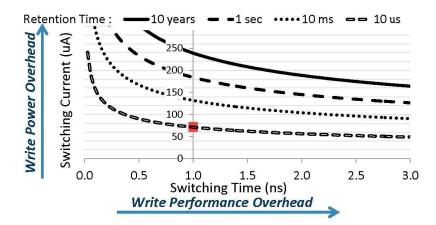

In this section, we review key features of STT-MRAM and analyze design tradeoffs of an MTJ cell in terms of switching time (the time taken for completing a write operation in an MTJ cell, namely write latency), switching current (the power required to change an MTJ cell value, namely write power), and data retention time.

### 3.2.1 STT-MRAM

STT-MRAM is a next generation memory technology that exploits magnetoresistance for storing data. In STT-MRAM, each data bit is stored in an MTJ, a fundamental building block. An MTJ consists of three layers: two ferromagnetic layers and a Magnesium Oxide (MgO) tunnel barrier layer in the middle as shown in Figure 3.2. Depending on the current that propagates through the fixed layer, the spin polarity of the free layer changes to either parallel (*zero*) or anti-parallel (*one*) to that of the fixed layer. A single MTJ module is coupled with an NMOS transistor to form a basic memory cell of STT-MRAM, called a 1T-1MTJ.

# 3.2.2 STT-MRAM Design Considerations

#### 3.2.2.1 Retention Time