## MILLIMETER-WAVE CONCURRENT DUAL-BAND BICMOS RFICS

## FOR RADAR AND COMMUNICATION RF FRONT-END

A Dissertation

by

## DONGHYUN LEE

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Cam Committee Members, Chin Greg Reza

Head of Department,

Cam Nguyen Chin B. Su Gregory H. Huff Reza Langari Miroslav Begovic

December 2015

Major Subject: Electrical Engineering

Copyright2015 Donghyun Lee

### ABSTRACT

The recent advancement in silicon-based technologies has offered the opportunity for the development of highly-integrated circuits and systems in the millimeter-wave frequency regime. In particular, the demand for high performance multi-band multi-mode radar and communication systems built on silicon-based technologies has been increased dramatically for both military and commercial applications.

This dissertation presents the design and implementation of advanced millimeterwave front-end circuits in SiGe BiCMOS process including a transmit/receive switch module with integrated calibration function, low noise amplifier, and power amplifier for millimeter-wave concurrent dual-band dual-polarization radars and communication systems. The proposed circuits designed for the concurrent dual-band dual-polarization radars and communication systems were fabricated using 0.18-µm BiCMOS process resulting in novel circuit architectures for concurrent multi-band operation.

The developed concurrent dual-band circuits fabricated on 0.18-µm BiCMOS process include the T/R/Calibration switch module for digital beam forming array system at 24.5/35 GHz, concurrent dual-band low noise amplifiers at 44/60 GHz, and concurrent dual-band power amplifier at 44/60 GHz. With having all the design frequencies closely spaced to each other showing the frequency ratio below 1.43, the designed circuits provided the integrated dual-band filtering function with Q-enhanced frequency responses. Inspired by the composite right/left- handed metamaterial

transmission line approaches, the integrated Q-enhanced filtering sub-circuits provided unprecedented dual-band filtering capability.

The new concurrent dual-band dual-mode circuits and system architecture can provide enhanced radar and communication system performance with extended coverage, better image synthesis and target locating by the enhanced diversity. The circuit level hardware research conducted in this dissertation is expected to contribute to enhance the performance of multi-band multi-mode imaging, sensing, and communication array systems.

# DEDICATION

To my family for all their endless love and support

## ACKNOWLEDGEMENTS

This dissertation would not have been possible without the help of many people. I would like to express my gratitude to all my committee members, Prof. Cam Nguyen, Prof. Chin B. Su, Prof. Gregory Huff, and Prof. Reza Langari for their valuable input and support throughout the course of this research. Thanks also go to my friends and colleagues who were willing to provide help and support during my time at Texas A&M University. Their encouragement and support have also become great motivation for me to accomplish this degree.

Lastly, my deepest gratitude goes to my parents who have supported me with their unconditional love all the time. I would have not reached this far without their support. I am deeply indebted to my family for all their sacrifice and support along the way as I finished my research.

## NOMENCLATURE

| BiCMOS | Bipolar Complementary Metal Oxide Semiconductor |  |

|--------|-------------------------------------------------|--|

| BJT    | Bipolar Junction Transistor                     |  |

| CMOS   | Complementary Metal Oxide Semiconductor         |  |

| CRLH   | Composite Right/Left- Handed                    |  |

| GaAs   | Gallium Arsenide                                |  |

| HBT    | Heterojunction Bipolar Technology               |  |

| LNA    | Low Noise Amplifier                             |  |

| MAG    | Maximum Available Gain                          |  |

| MTM    | Metamaterial                                    |  |

| NF     | NF                                              |  |

| PA     | Power Amplifier                                 |  |

| PDK    | Process Design Kit                              |  |

| RF     | Radio Frequency                                 |  |

| SiGe   | Silicon Germanium                               |  |

| SPST   | Single-Pole Single-Throw                        |  |

# **TABLE OF CONTENTS**

|                                                                                                                                                                                                                                                                                                                                                     | Page                                               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| ABSTRACT                                                                                                                                                                                                                                                                                                                                            | ii                                                 |

| DEDICATION                                                                                                                                                                                                                                                                                                                                          | iv                                                 |

| ACKNOWLEDGEMENTS                                                                                                                                                                                                                                                                                                                                    | v                                                  |

| NOMENCLATURE                                                                                                                                                                                                                                                                                                                                        | vi                                                 |

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                                                   | vii                                                |

| LIST OF FIGURES                                                                                                                                                                                                                                                                                                                                     | x                                                  |

| LIST OF TABLES                                                                                                                                                                                                                                                                                                                                      | xiv                                                |

| CHAPTER I INTRODUCTION                                                                                                                                                                                                                                                                                                                              | 1                                                  |

| <ul> <li>1.1 Technical Background of the Proposed Dual-band Circuits and Modules</li> <li>1.1.1 Objectives and Motivation of the Research</li> <li>1.1.2 Radar System Overview</li> <li>1.1.3 Radar System Equations</li> <li>1.1.4 Millimeter-wave Radar and Communication System Applications</li> <li>1.1.5 Dissertation Organization</li> </ul> | 1<br>2<br>3<br>5<br>7<br>11                        |

| CHAPTER II CONCURRENT DUAL-BAND T/R/CALIBRATION SWITCH                                                                                                                                                                                                                                                                                              | 13                                                 |

| <ul> <li>2.1 RF CMOS Switch Architecture and Consideration</li></ul>                                                                                                                                                                                                                                                                                | 13<br>13<br>15<br>16<br>16<br>22<br>23<br>23<br>23 |

| Negative Resistance Generation Circuit<br>2.2.4 T/R/Calibration Switch Module Architecture, Analysis, and Design<br>2.2.4.1 Deep n-well NMOS Transistors<br>2.2.4.2 Proposed T/R/Calibration Switch Module                                                                                                                                          | 27<br>32<br>33<br>35                               |

| 5.1 Contribution                                                   | 122 |

|--------------------------------------------------------------------|-----|

| CHAPTER V SUMMARY AND CONCLUSION                                   |     |

| 4.2.3 Conclusion                                                   |     |

| 4.2.2.2 Concurrent Dual-band Power Amplifier: Performance          |     |

| 4.2.2.1 Two Stage Concurrent Dual-band Power Amplifier             |     |

| 4.2.2 Concurrent Dual $Q/V$ -band Power Amplifier Design           |     |

| 4.2.1 Introduction and Motivation.                                 |     |

| 4.2 Concurrent Dual <i>Q</i> / <i>V</i> -band Power Amplifier      |     |

| 4.1.4 Class of Power Amplifiers                                    |     |

| 4.1.3 Power Amplifier Linearity                                    | 96  |

| 4.1.2 Power Amplifier Efficiency                                   |     |

| 4.1.1 Power Capability                                             |     |

| 4.1 Power Amplifier Principles                                     |     |

| 4.1 Demon Amulifian Dringin 1                                      | 0.2 |

| CHAPTER IV CONCURRENT DUAL-BAND POWER AMPLIFIER                    | 93  |

| 3.2.4 Conclusion                                                   | 91  |

| 3.2.3.4 Comparison with Other Works                                |     |

| Low Noise Amplifiers                                               |     |

| 3.2.3.3 Dual-mode Operation Linearity Performance of Proposed      | 0.0 |

| 3.2.3.2 Concurrent Dual-band LNA with Q-enhanced E-CRLH            | 86  |

| 3.2.3.1 Concurrent Dual-band LNA with Q-enhanced CRLH.             |     |

| 3.2.3 Concurrent Dual-band Low Noise Amplifiers: Performance       |     |

| 3.2.2.3 Two Stage Concurrent Dual-band Low Noise Amplifiers        |     |

| 3.2.2.2 Wideband Input Matching                                    |     |

| 3.2.2.1 Q-enhanced Synthesized CRLH and E-CRLH                     |     |

| 3.2.2 Concurrent Dual-band Low Noise Amplifier Design              |     |

| 3.2.1 Introduction and Motivation                                  |     |

| 3.2 Concurrent Dual-band Low Noise Amplifiers                      | 62  |

| 3.1.1 RF/Millimeter-wave Low Noise Amplifier Design Considerations | 61  |

| 3.1 RF/Millimeter-wave Low Noise Amplifiers                        |     |

|                                                                    |     |

| CHAPTER III CONCURENT DUAL-BAND LOW NOISE AMPLIFIERS               | 61  |

| 2.2.6 Conclusion                                                   | 60  |

| 2.2.5.5 Performance Discussion and Comparison                      |     |

| 2.2.5.4 Power Handling and Linearity                               |     |

| 2.2.5.3 Dual-bandpass T/R/Calibration Switch Module                |     |

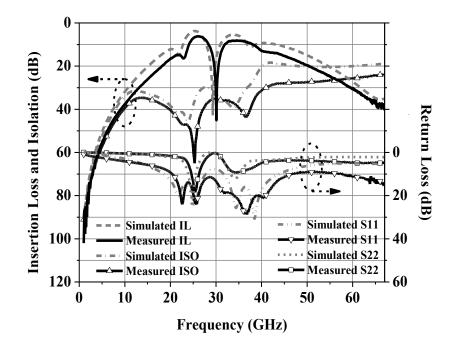

| 2.2.5.2 Dual-band Single-pole Single-throw Switch                  |     |

| 2.2.5.1 Dual-band Metamaterial CRLH Network                        |     |

| 2.2.5 T/R/Calibration Switch Module: Performance and Discussion    |     |

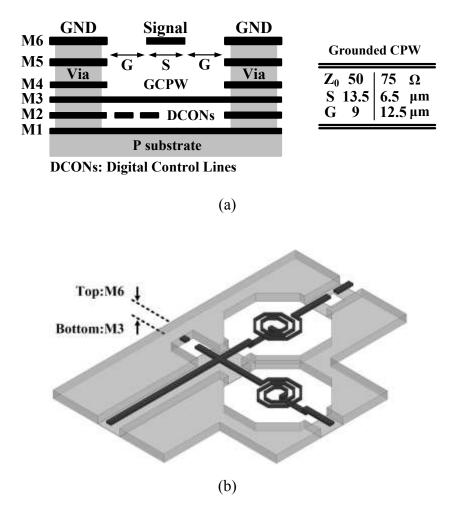

| 2.2.4.3 GCPW and Comprehensive Electromagnetic Simulation          |     |

|                                                                    | 40  |

| REFERENCES 1 | 125 |

|--------------|-----|

|--------------|-----|

## **LIST OF FIGURES**

|             |                                                                                                                                                                                                                                                                                                                                                                            | Page |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

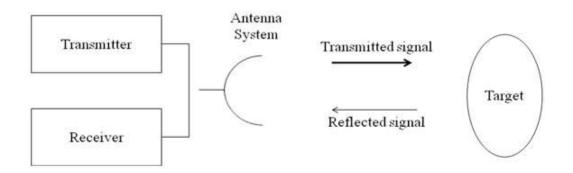

| Figure 1.1  | Illustration of basic radar systems                                                                                                                                                                                                                                                                                                                                        | 3    |

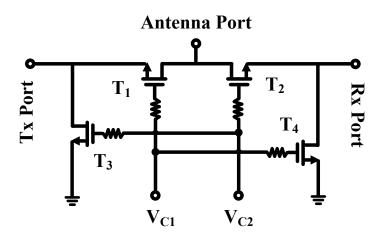

| Figure 2.1  | Conventional series-shunt switch architecture                                                                                                                                                                                                                                                                                                                              | 15   |

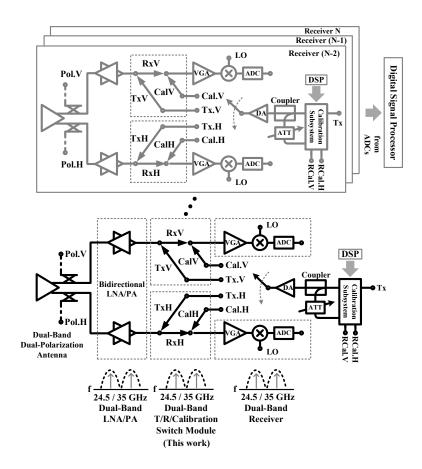

| Figure 2.2  | Digital beam forming array architecture                                                                                                                                                                                                                                                                                                                                    | 17   |

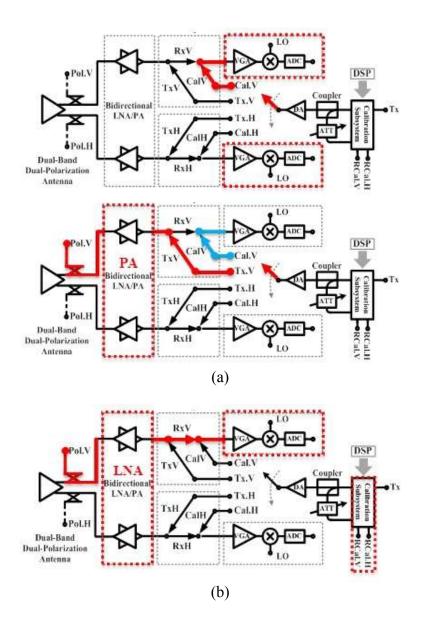

| Figure 2.3  | Calibration scheme (a) Transmit reference calibration and (b) Receive calibration                                                                                                                                                                                                                                                                                          | 18   |

| Figure 2.4  | Cascaded quasi-elliptic dual-bandpass network                                                                                                                                                                                                                                                                                                                              | 24   |

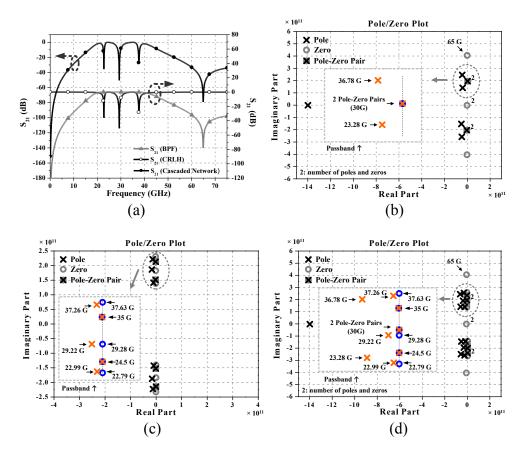

| Figure 2.5  | (a) S21 plot, (b) Pole/Zero plot: BPF, (c) Pole/Zero plot: CRLH TL, and (d) Pole/Zero plot: Cascaded BPF and CRLH TL                                                                                                                                                                                                                                                       | 25   |

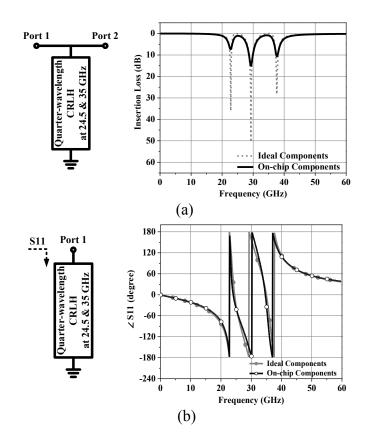

| Figure 2.6  | Simulated (a) S21of two-port CRLH and (b) phase of S11 of one-port CRLH                                                                                                                                                                                                                                                                                                    | 26   |

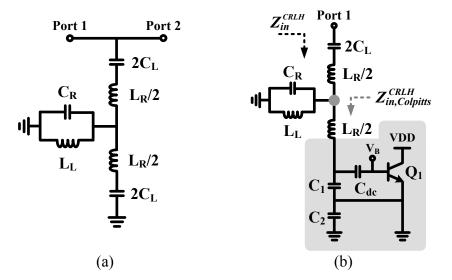

| Figure 2.7  | (a) Original passive CRLH network and (b) CRLH network coupled with a Colpitts style negative resistance generation circuit                                                                                                                                                                                                                                                | 28   |

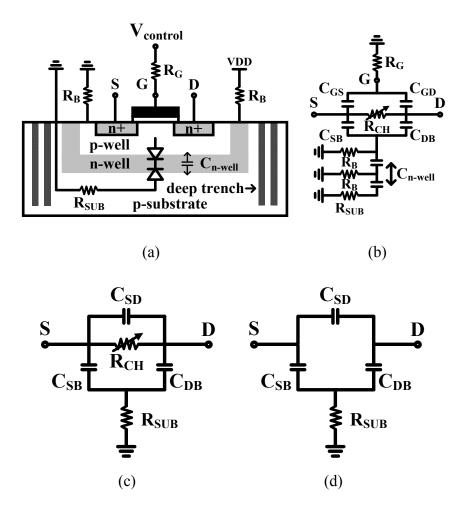

| Figure 2.8  | (a) Cross sectional view of nMOS transistor, (b) its equivalent circuit, and simplified on-state, (c) and (d) off-state equivalent circuits. $C_{SD}$ , $C_{SB}$ , $C_{DB}$ , $R_{CH}$ , and $R_{SUB}$ represent the parasitic capacitance between the source and drain, source and body, drain and body, on-state resistance, and equivalent resistance of the substrate, |      |

|             | respectively                                                                                                                                                                                                                                                                                                                                                               | 33   |

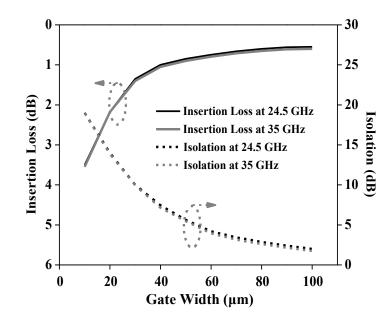

| Figure 2.9  | Insertion loss and isolation for different nMOS gate widths                                                                                                                                                                                                                                                                                                                | 34   |

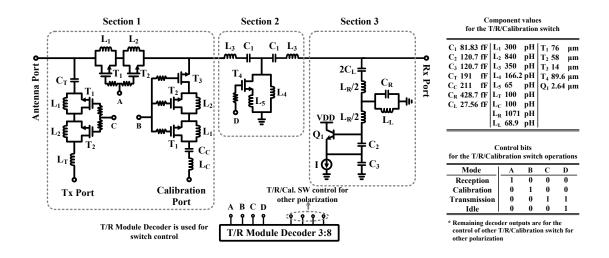

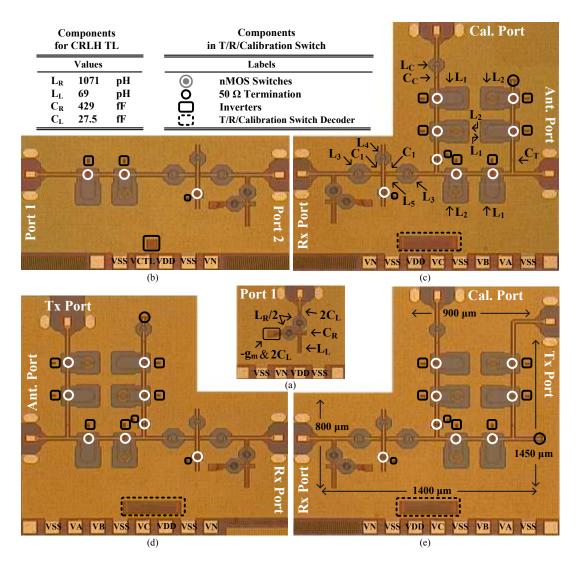

| Figure 2.10 | Proposed concurrent dual-bandpass T/R/Calibration switch module                                                                                                                                                                                                                                                                                                            | 36   |

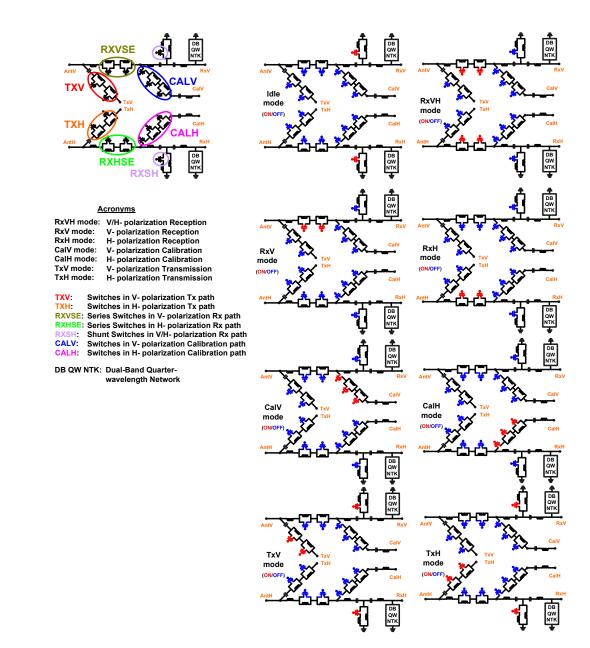

| Figure 2.11 | Digital control scheme for a pair of T/R/Calibration switch module for both V- and H- polarization transceiver                                                                                                                                                                                                                                                             | 39   |

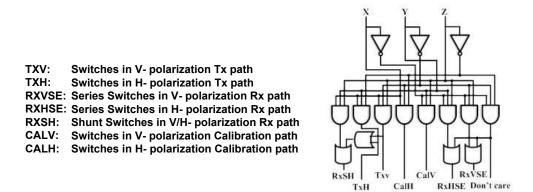

| Figure 2.12 | 2 Digital control circuit for T/R/Calibration Switch Module                                                                                                                                                                                                                                                                                                                | 40   |

| Figure 2.13 | (a) GCPW structure and (b) EM simulation model                                                                                                                                                                                                                                                                                                                             | 41   |

| Figure 2.14 | <ul> <li>4 Microphotographs of T/R/Calibration switches: (a) one-port CRLH,</li> <li>(b) dual-bandpass SPST switch, (c) T/R/Calibration switch with Tx port termination, (d) T/R/Calibration switch with Calibration port termination, and (e) T/R/Calibration switch with Antenna port termination</li> </ul> |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

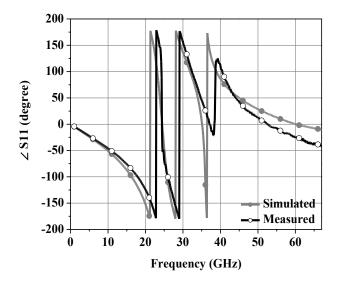

| Figure 2.1: | 5 One-port CRLH $\angle$ S11                                                                                                                                                                                                                                                                                   |

| Figure 2.1  | 6 Dual-band SPST switch S parameters                                                                                                                                                                                                                                                                           |

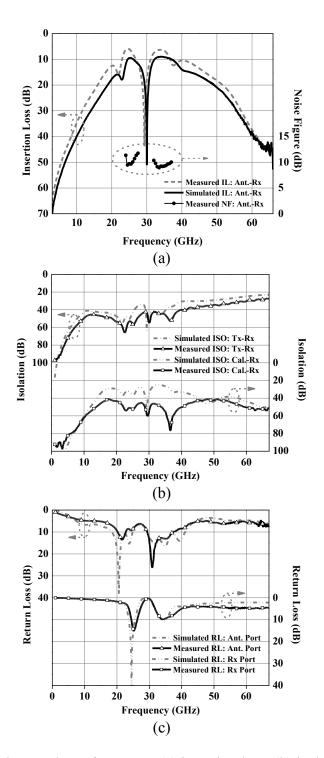

| Figure 2.1  | 7 Reception mode performance: (a) insertion loss, (b) isolation, and (c) return loss                                                                                                                                                                                                                           |

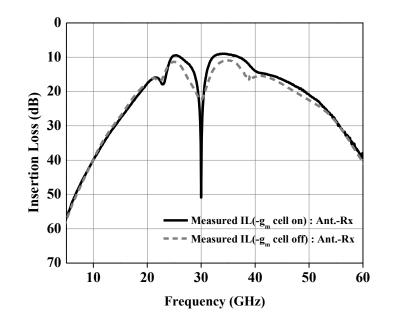

| Figure 2.1  | 8 Reception-mode insertion loss with $-g_m$ cell on and off                                                                                                                                                                                                                                                    |

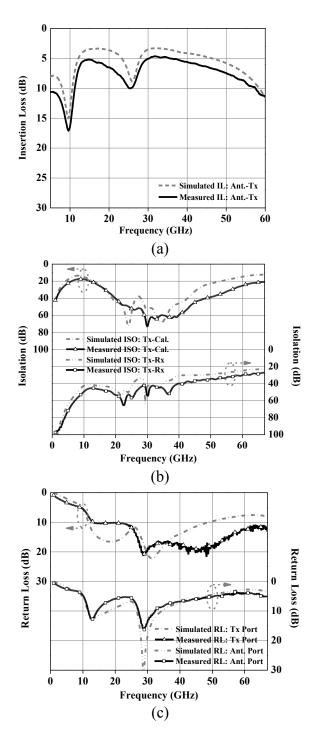

| Figure 2.1  | 9 Transmission mode performance: (a) insertion loss, (b) isolation,<br>and (c) return loss                                                                                                                                                                                                                     |

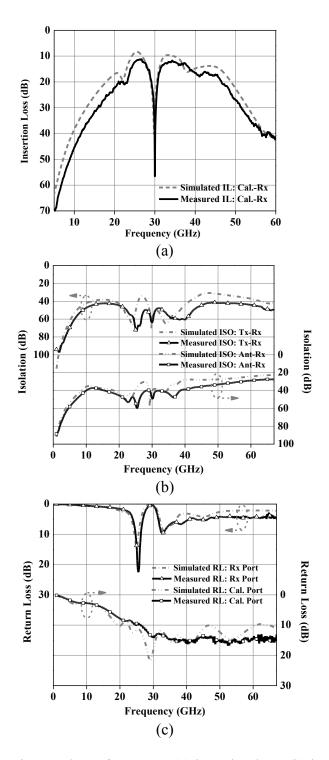

| Figure 2.2  | 0 Calibration mode performance: (a) insertion loss, (b) isolation, and (c) return loss.                                                                                                                                                                                                                        |

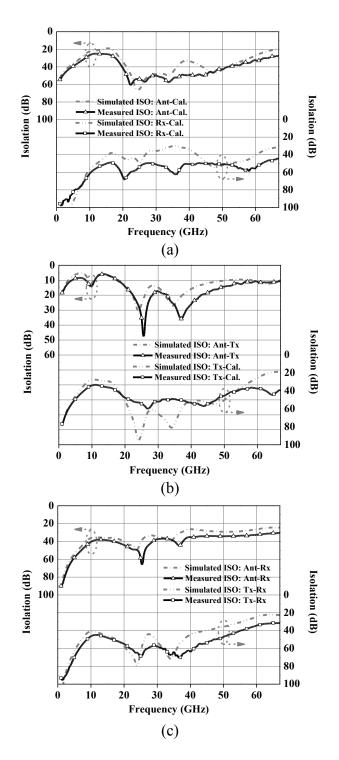

| Figure 2.2  | 1 Idle mode performance: isolation between (a) Antenna-Calibration<br>and Rx-Calibration ports, (b) Tx-Calibration and Antenna-Tx ports,<br>and (c) Antenna-Rx and Tx-Rx ports                                                                                                                                 |

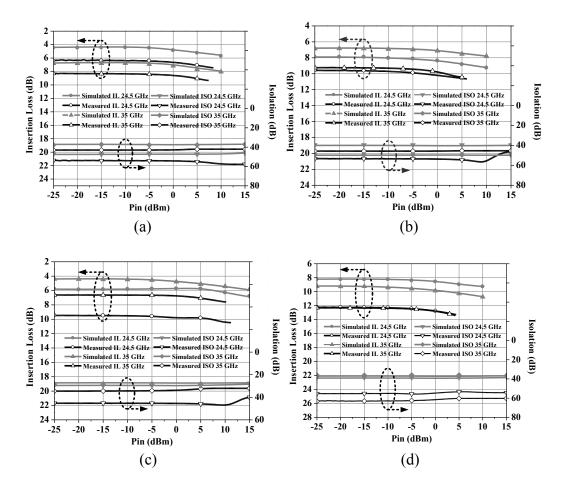

| Figure 2.22 | <ul> <li>P1dB Linearity performance of the T/R/Calibration switch:</li> <li>(a) dual-band SPST, (b) reception path, (c) transmission path, and (d) calibration path.</li> </ul>                                                                                                                                |

| Figure 2.2. | <ul> <li>3 IP3 Linearity performance of the T/R/Calibration switch:</li> <li>(a) dual-band SPST, (b) reception path, (c) transmission path, and (d) calibration path.</li> </ul>                                                                                                                               |

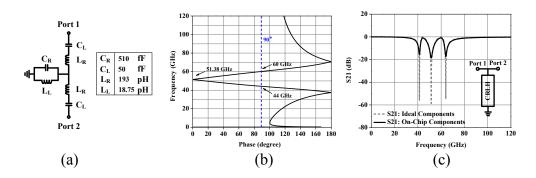

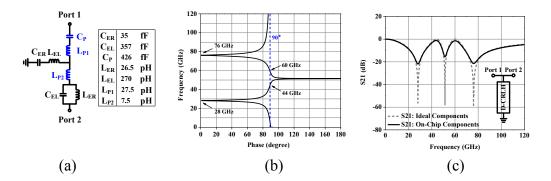

| Figure 3.1  | (a) CRLH network (b) dispersion diagram of CRLH and (c) insertion loss with ideal and on-chip components                                                                                                                                                                                                       |

| Figure 3.2  | <ul><li>(a) E-CRLH network (b) dispersion diagram of E-CRLH and</li><li>(c) insertion loss with ideal and on-chip components</li></ul>                                                                                                                                                                         |

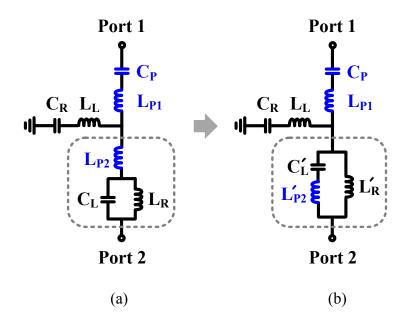

| Figure 3.3  | Network transformation: (a) E-CRLH with parasitic components for additional transmission zeroes and (b) E-CRLH with transformed network                                                                                                                                                                        |

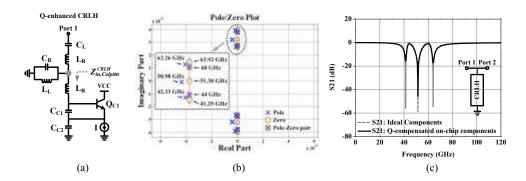

| Figure 3.4  | (a) active CRLH network (b) dispersion diagram of active CRLH                                                                                                                                                                                                                                                  |

|             | and (c) insertion loss with ideal and on-chip components                                                                                                                                                                                         | 69 |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

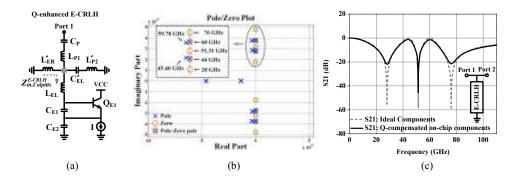

|             | are 3.5 (a) active E-CRLH network (b) dispersion diagram of active E-CRLH and (c) insertion loss with ideal and on-chip components                                                                                                               |    |

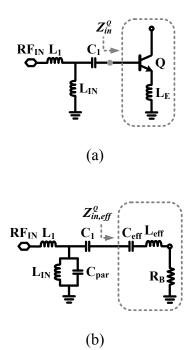

| Figure 3.6  | .6 Wideband input matching for concurrent dual-band LNAs: (a) original circuit configuration and (b) its equivalent circuit model                                                                                                                |    |

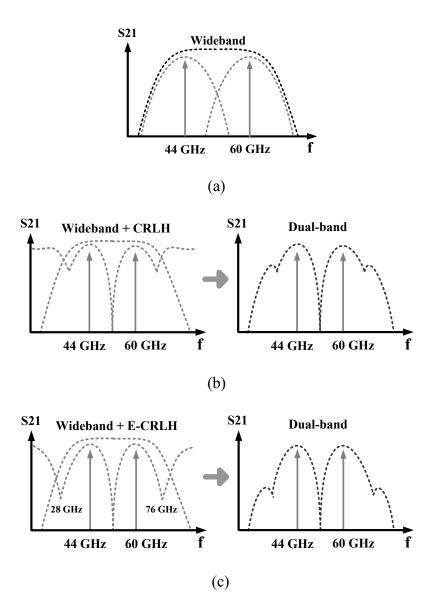

|             | Concurrent dual-band LNAs realization: (a) Wideband S21 response<br>with two stages, (b) Wideband and CRLH superposition, and<br>(c) Wideband and E-CRLH superposition                                                                           | 75 |

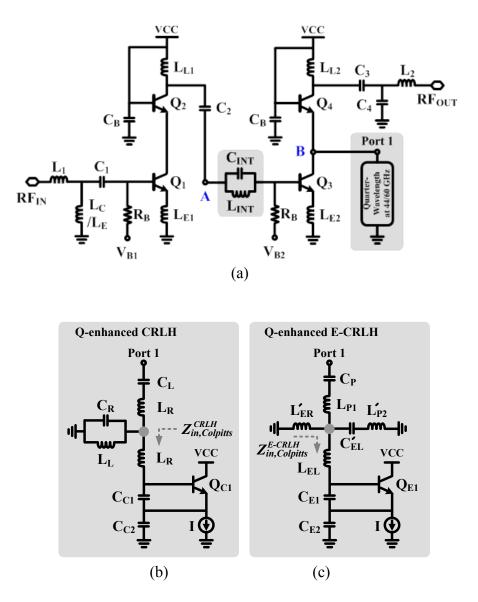

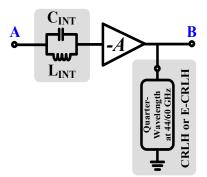

| Figure 3.8  | (a) Concurrent dual-band two-stage LNA schematic, (b) Q-enhanced CRLH, and (c) Q-enhanced E-CRLH                                                                                                                                                 | 76 |

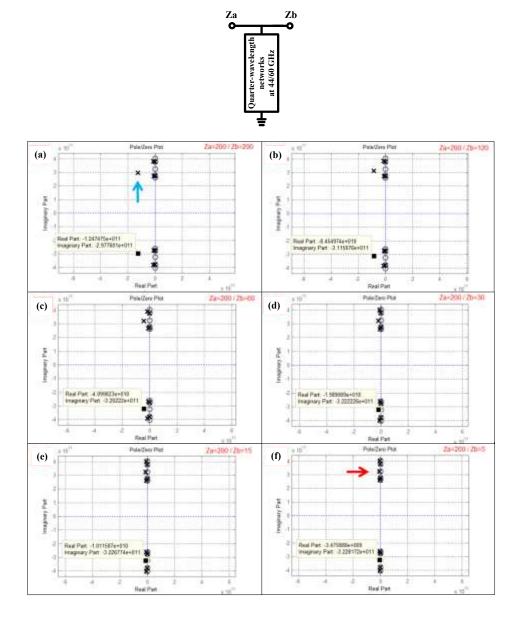

| Figure 3.9  | Pole migration with different impedance condition                                                                                                                                                                                                | 78 |

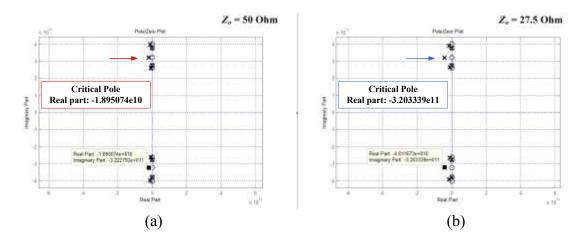

| Figure 3.10 | Pole migration with fixed outside impedance (a) Quarter-wavelength<br>network with characteristic impedance of 50 Ohm and (b) Quarter-<br>wavelength network with characteristic impedance of 27.5 Ohm                                           | 79 |

| Figure 3.11 | <ul><li>(a) Equivalent circuit model for a network from node A to B in the concurrent dual-band LNA schematic for pole/zero analysis,</li><li>(b) Q-enhanced CRLH, and (c) Q-enhanced E-CRLH</li></ul>                                           | 81 |

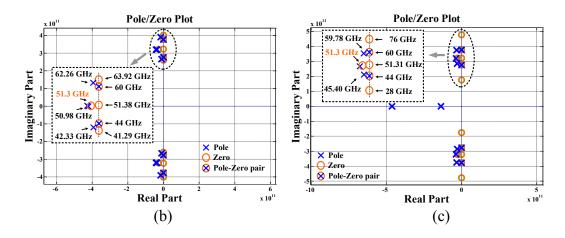

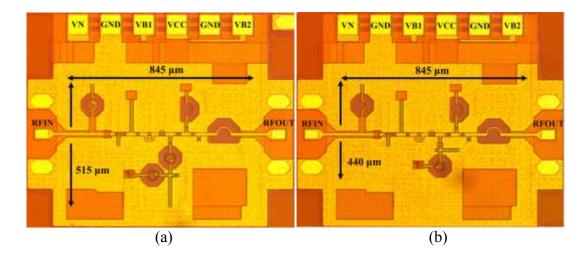

| Figure 3.12 | Die photos (a) Concurrent dual-band LNA with Q-enhanced CRLH (b) Concurrent dual-band LNA with Q-enhanced E-CRLH                                                                                                                                 | 83 |

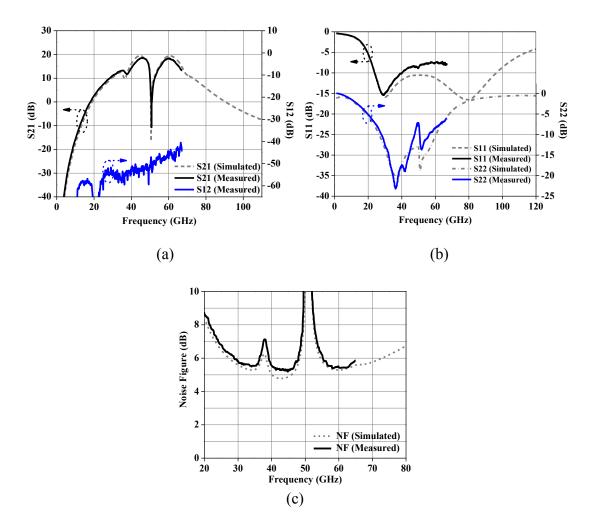

| Figure 3.13 | Concurrent dual-band LNA with the Q-enhanced CRLH (a) S21 and S12, (b) S11 and S22, and (c) noise figure                                                                                                                                         | 84 |

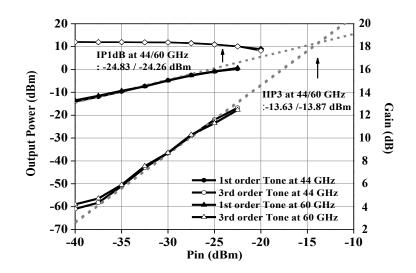

| Figure 3.14 | Linearity performance: Concurrent dual-band LNA with the Q-enhanced CRLH                                                                                                                                                                         | 85 |

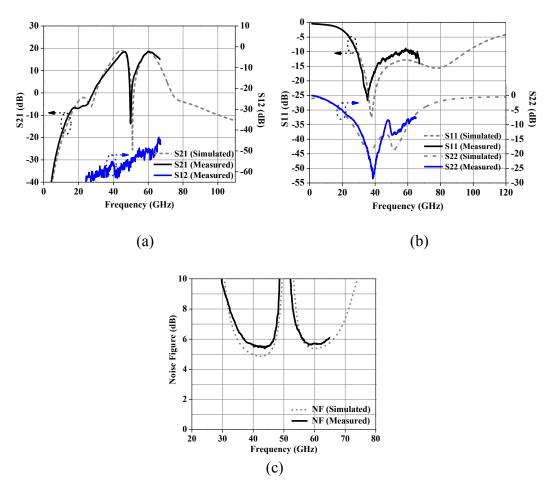

| Figure 3.15 | Concurrent dual-band LNA with the Q-enhanced E-CRLH (a) S21 and S12, (b) S11 and S22, and (c) noise figure                                                                                                                                       | 87 |

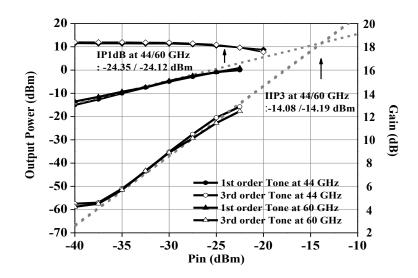

| Figure 3.16 | Linearity performance: Concurrent dual-band LNA with the Q-enhanced E-CRLH                                                                                                                                                                       | 88 |

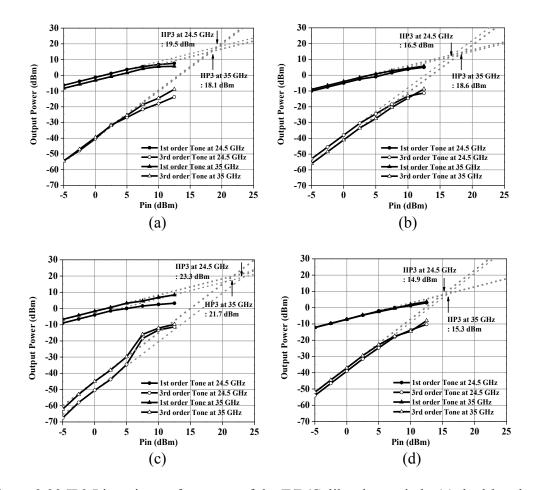

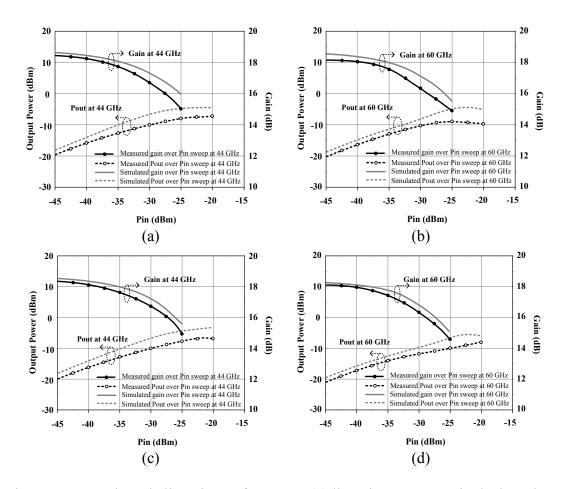

| Figure 3.17 | Dual-mode linearity performance: (a) linearity at 44 GHz in<br>dual-mode LNA with Q-enhanced CRLH network, (b) linearity<br>at 60 GHz in dual-mode LNA with Q-enhanced CRLH network,<br>(c) linearity at 44 GHz in dual-mode LNA with Q-enhanced |    |

|             | E-CRLH network, and (d) linearity at 60 GHz in dual-mode LNA with Q-enhanced E-CRLH network                                                                                                                    | 89  |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

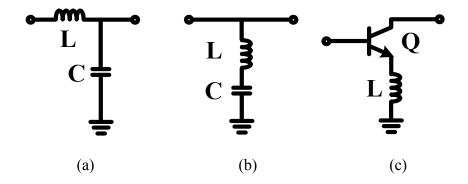

| Figure 4.1  | (a) Low pass matching network, (b) notch filter for harmonic termination, and (c) degeneration                                                                                                                 | 97  |

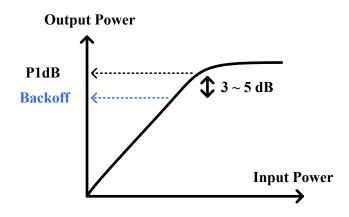

| Figure 4.2  | Backoff operation of power amplifier for linearity                                                                                                                                                             | 98  |

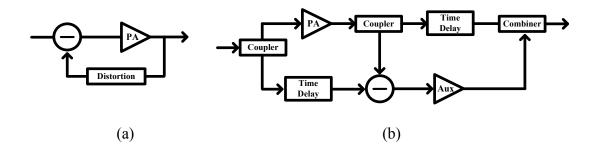

| Figure 4.3  | (a) Feedback and (b) feedforward technique                                                                                                                                                                     | 99  |

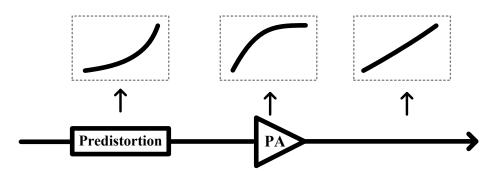

| Figure 4.4  | Predistortion technique                                                                                                                                                                                        | 99  |

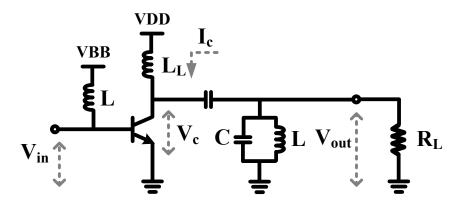

| Figure 4.5  | Power amplifier with tuned load                                                                                                                                                                                | 100 |

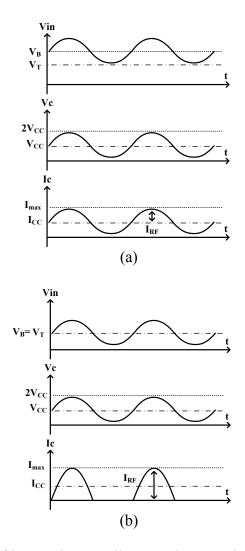

| Figure 4.6  | Waveforms of base voltage, collector voltage, and collector current<br>of (a) Class A amplifier (b) Class B amplifier and (c) class C<br>amplifer                                                              | 101 |

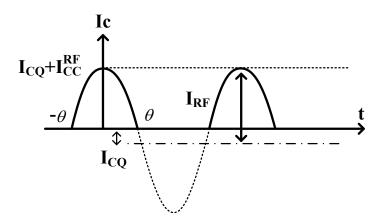

| Figure 4.7  | Class A, B, and C waveform analysis                                                                                                                                                                            | 103 |

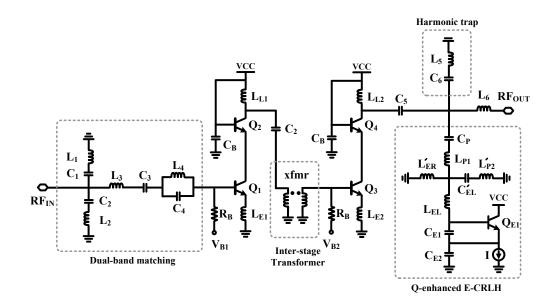

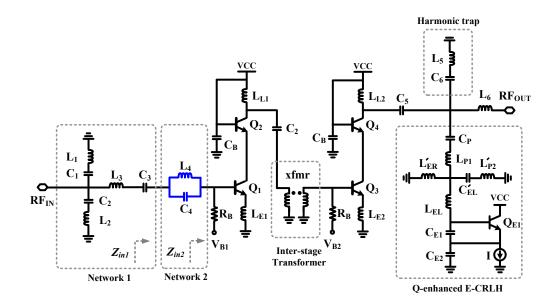

| Figure 4.8  | Schematic of dual-band power amplifier                                                                                                                                                                         | 107 |

| Figure 4.9  | Input impedance matching for dual-band power amplifier                                                                                                                                                         | 108 |

| Figure 4.10 | Input impedance matching                                                                                                                                                                                       | 109 |

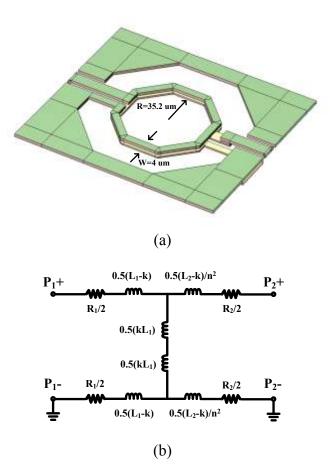

| Figure 4.11 | On-chip transformer for inter-stage impedance matching (a) stacked transformer and (b) simplified equivalent circuit of the transformer                                                                        | 112 |

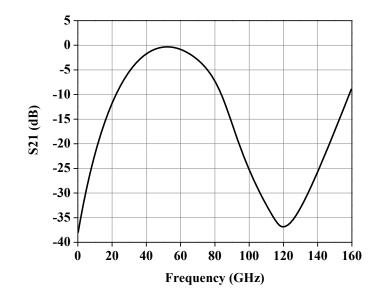

| Figure 4.12 | S-parameter of the designed on-chip transformer                                                                                                                                                                | 113 |

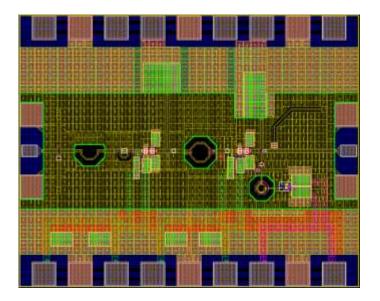

| Figure 4.13 | Complete concurrent dual $Q/V$ - band power amplifier layout                                                                                                                                                   | 114 |

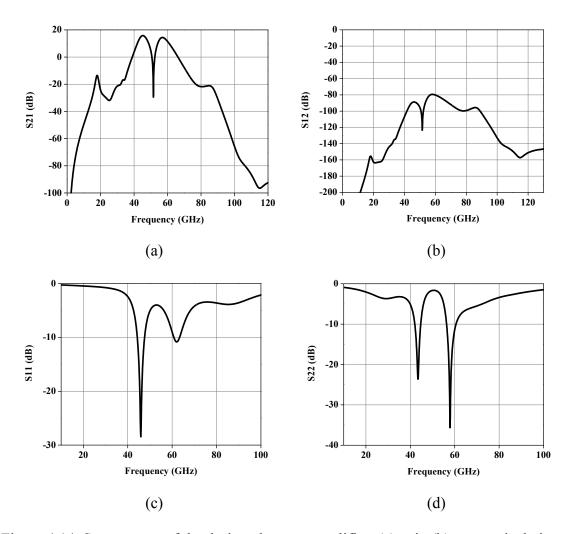

| Figure 4.14 | S-parameter of the designed power amplifier: (a) gain<br>(b) reverse isolation (c) S11 and (d) S22                                                                                                             | 116 |

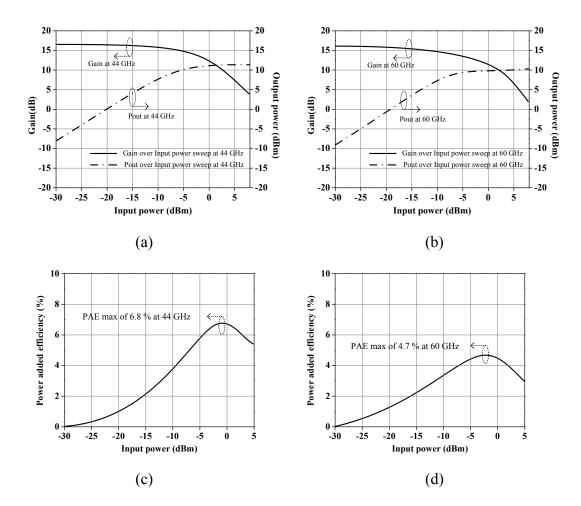

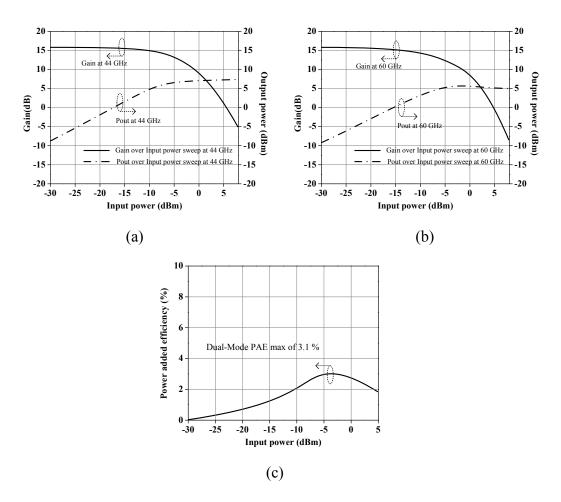

| Figure 4.15 | Single-band mode: gain, output power and PAE (a) gain<br>and output power at 44 GHz, (b) gain and output power at 60 GHz,<br>(c) power added efficiency at 44 GHz, and (d) power added<br>efficiency at 60 GHz | 118 |

| Figure 4.16 | Dual-band mode: gain, output power and PAE (a) gain and output<br>power at 44 GHz, (b) gain and output power at 60 GHz, (c) power<br>added efficiency in dual-mode                                             | 119 |

# LIST OF TABLES

# Page

| Table 1.1 Radar sensor architectures: benefits and disadvantages                | 10  |

|---------------------------------------------------------------------------------|-----|

| Table 2.1 Digital control scheme with modified 3:8 decoder                      | 40  |

| Table 2.2 Measured performance summary of the K/Ka-band T/R/Calibration switch  | 59  |

| Table 3.1 Performance comparison for dual-band low noise amplifiers             | 90  |

| Table 4.1 Conduction angle and efficiency of power amplifers                    | 102 |

| Table 4.2 Component values for concurrent dual-band power amplifer              | 107 |

| Table 4.3 Cocurrent dual $Q/V$ - band power amplifer performance and comparison | 120 |

#### **CHAPTER I**

### **INTRODUCTION**

### 1.1 Technical Background of the Proposed Dual-band Circuits and Modules

There has been increasing demand in multi-band multi-mode radar and communication systems in millimeter-wave frequency bands between 30 and 300 GHz. The millimeter-wave spectrum has been mostly used for military radar application using expensive compound semiconductor process such as Gallium Arsenide (GaAs), Indium Phosphide (InP) and so on. However, cost effective silicon based technologies such as CMOS and BiCMOS enable cost-effective integrated circuits and systems with comparable performance to expensive compound processes such as GaAs and InP. Also, the demand in high-data rate wireless communication exploiting millimeter-wave spectrum led the research and development of highly-integrated multi-functional millimeter-wave circuits and systems.

In this research, the RF front-end circuits including transmit/receive switch module, low noise amplifiers, and power amplifier development was conducted for novel, compact, multi-band, and multi-polarization millimeter-wave system, which are proposed for an innovative and intelligent dual-band and dual-polarization radar and wireless communication systems. The main focus of this research is to develop some multi-band and multi-mode components in K/Ka (24.5/35 GHz) - and Q/V (44/60 GHz) - band frequency spectrum. The developed front-end circuits includes concurrent dual

K/Ka- band T/R/Calibration switch module to support dual-polarization operation, concurrent dual Q/V- band low noise amplifiers, and a concurrent dual Q/V- band power amplifier. All the proposed circuits and modules aims to achieve electrical integration of two modalities in K/Ka- and Q/V- band. The concurrent operation, which enables the circuits function together over multi-bands radically reduces the circuit size making a large concurrent dual-band millimeter-wave antenna array system feasible. This is not only cost effective but also innovative in that design complexity in realizing multi-band system is greatly reduced.

## **1.1.1 Objectives and Motivation of the Research**

The objective of this research is to propose and develop integrated circuits, modules, and systems, which electrically combine multi modalities in K/Ka- and Q/V-bands. Rather than combining circuits optimized at single frequency in parallel, designing a single unit circuit operating over multi-band simultaneously can improve system performance while reducing the cost and complexity in realizing multi-band systems. Such multi-band components employed in multi-band radar and wireless communication systems can provide advantages over single-band components for better detection, identification, target tracking, locating, and high-data rate wireless communication by the frequency and polarization diversity. This enhanced detection coverage, precise target location, increased resolution, improved reliability, and high-data rate for both radar and wireless communication systems can be attractive in that all

Fig. 1.1. Illustration of basic radar systems

the aforementioned improvement can be realized within a single circuit designed based on concurrent multi-band principle. The following sections will introduce some radar and commercial wireless communication applications which would benefit from the multi-band multi-modal circuits and modules proposed in this research by extended frequency and polarization diversity.

## 1.1.2 Radar System Overview

Radar system refers to hardware and software combined system which utilizes radio frequency for detecting and ranging targets [1]. Radar systems illuminate a target with a certain frequency signal to process the backscattered signals for, to mention a few, precise distance measurement, velocity measurement, surveillance, scatterometry, cloud radar monitoring for weather forecast, subsurface sensing, industrial applications such as presence sensing of objects and distance control, automotive applications including safety distance measurement, blind spot detection and traffic monitoring. Other applications of radar systems include utilizing a scanning beam of a transmitter of radar for generating image of certain targets or areas.

Figure. 1.1 presents the basic principle of radar systems. The transmitter in the radar system sends out a electromagnetic signal at a certain spectrum of frequency in the form of a pulse or continuous wave to an intended target through an antenna system. Once the target is illuminated by the transmit signal, a certain amount of signal is reflected back to the radar system so the receiver can capture the backscattered signal from the target. In conjunction with the signal processing unit, the backscattered signal is processed to detect the target presence, location, image, or velocity. The target distance can be calculated by measuring the round-trip time of the radar signal from the target.

The calculation of target's location can be performed using narrow electromagnetic beam transmitted from the radar system. The precise location can be calculated by measuring the maximum received power from the echo signal. Also, if the target is a moving platform, the reflected signal will undergo the Doppler shift effect. The measured frequency shift is proportional to the velocity of the moving platform, which provides the information regarding the relative velocity to the radar system.

#### **1.1.3 Radar System Equations**

It is important to go over a number of radar system equations because they not only provide the relationship between the transmitter and receiver of a radar system but also characterize the relationship between the radar system and potential targets. The measures would also serve as a fundamental tool to radar systems since the radar system equation represents the physical relationship of the transmit power to the receiving of the reflected signals, or echo signals, from a target. With a certain sensitivity of the radar receiver, the radar equation helps to determine a maximum range for detection [2]. Supposing the radar system employs isotropic antenna to transmit radar signal, the power density at the distance R from the radar system can be expressed as

$$P_d = \frac{P_t}{4\pi R^2} \tag{1.1}$$

where  $P_d$  and  $P_t$  are the power density and the transmitted power from a radar system, respectively. The measure of power density is based on the watts per square meter. However, in many cases, radar systems employ directional antenna system to increase the gain of the radiated power. The gain of antenna is proportional to the directivity which means how much radiated energy is concentrated into a certain direction. With the antenna gain designated as G, the power density expression in (1.1) can be rewritten as

$$P_d = \frac{P_t G}{4\pi R^2} \tag{1.2}$$

where  $P_d$  and G are the power density and the antenna gain of directional antenna system, respectively. The power of the received signal from a target requires more terms to reflect the radar cross section and the effective area of the antenna system. The received power of the backscattered signal is expressed as

$$P_r = \frac{P_t G}{4\pi R^2} \times A_e \times \frac{\sigma}{4\pi R^2}$$

(1.3)

where Ae is the effective area of the antenna system and  $\sigma$  is the radar cross section of a target respectively.

The maximum detectable range of a radar system can be derived based on (1.3). Designating the lowest detectable signal power from a target as  $P_{rmin}$  and substituting it with the received power term in (1.3), the maximum range of a radar system can be expressed as

$$R_{\max} = \left[\frac{P_t G A_e \sigma}{\left(4\pi\right)^2 P_{r\min}}\right]^{1/4}$$

(1.4)

Any target beyond this maximum range shown in (1.4) cannot be detected.

### 1.1.4 Millimeter-wave Radar and Communication System Applications

There has been a great demand in utilizing higher frequency spectrum above 30 GHz since the microwave frequency spectrum was fully occupied with numerous commercial and military applications [3-10]. The possible benefit in utilizing the millimeter-wave spectrum is high data rate on a wide frequency spectrum. Also, a relatively shorter wavelength in millimeter-wave spectrum enables smaller circuit sizes resulting in compact electronic systems. A number of millimeter-wave radar and wireless communication applications which benefit from the characteristic of millimeter-wave spectrum are overviewed.

The millimeter-wave spectrum can be utilized for both long- and short- range radar and wireless communication systems. For long range application, the millimeter-wave frequency band such as Ka (26.5 to 40 GHz) - and Q (33 to 50 GHz) - band are utilized for satellite communications, terrestrial fixed point-to-point data link, radio astronomy radar application and high resolution radar systems [11]. The aforementioned Ka/Q- band frequency spectrum suffers relatively less atmospheric attenuation compared to other bands up to 300 GHz and hence can be utilized for long range radar and communication.

The frequency spectrum such as *V*-band (57-64 GHz) and *E*-band (71-86 GHz) are used for high-data rate wireless communication systems, however, the applications are mostly confined to relatively shorter distance in the range of several kilometers, typically 2 or 3 kilometers or less due to atmospheric attenuation [12-14]. For the 60

GHz band, it is recently exploited for short-range wireless communication below 100 meters for applications such as 802.11ad and 802.11ac [15-16]. The increased demand in high-date rate and high-definition multimedia mobile devices are driving the need of 60 GHz wireless connectivity application. While the application is mostly confined for close proximity wireless communication for line-of-sight data transfer due to the atmospheric attenuation, this line-of-sight link enables high data-rate communication between multiple devices which present within close proximity without interference. While it has become possible to use cost effective CMOS process for millimeter-wave system design recently, the standard established for the 60 GHz ISM band for PAN and LAN is predicted to gain strong momentum later on [17].

Other noticeable application includes the active radar sensor system for car collision avoidance. The original plan to use both 24 and 77 GHz spectrum is nullified due to possible interference in 24 GHz ISM band and therefore only 77 GHz is used for the automotive radar system [18-20]. The automotive radar application will leverage the safety of drivers by the collision avoidance, enhanced automatic cruise control, and blind spot monitoring. This application is also expected to grow exponentially once the regulation for the car safety is established.

The millimeter-wave systems operating in W(75 - 110 GHz) -band has been also used for passive imaging radar and wireless system for remote sensing. Compared to the active radar systems, passive radar sensors are only composed of receivers which measure the weak black-body radiation, or thermal radiation, emitted from an intended target. The actual power received by the receiver from the an intended target can be represented as follows.

$$P = k\Delta fT \tag{1.5}$$

where k and T are the Boltzmann's constant and surface temperature of the intended target, respectively. And  $\Delta f$  specifies the receiver bandwidth over which the black-body is integrated [21]. The received power level is used to construct the image of an intended target. Since those systems process very weak black-body radiation, it is required for the receiver in passive radar systems to have excellent sensitivity. Passive millimeter-wave imaging systems are mostly utilized for assistant landing system for aerial vehicles, concealed weapon and explosive detection, car crash avoidance in harsh weather, and etc. The application field is expanding to medical and biomedical imaging systems for breast cancer and other cancer detections. The following table summarizes the advantages and disadvantages of radar sensors in various frequency spectrums.

It can be seen from Table 1.1, the millimeter-wave radar systems offer many advantages over the infrared imager radar sensor [22]. They provide signal penetration for concealed target recognition, high spatial and frequency resolution for image generation and velocity measurement. Including other applications aforementioned, there is growing demand in the areas such as medical and biomedical imaging and detection, cosmic ray observation, next generation wireless communication systems referred to 5G.

# Table 1.1

## Radar sensor architectures: benefits and disadvantages

| Radar Sensor                                   | Advantages                                                                                                                                                 | Disadvantages                                                      |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|

| RF/millimeter-<br>wave radar<br>(Active)       | <ol> <li>Distance and image acquisitions</li> <li>Wide scanning range</li> <li>Independent from weather condition</li> <li>Velocity measurement</li> </ol> | <ol> <li>Low resolution</li> <li>Weak to interference</li> </ol>   |

| RF/millimeter-<br>wave radiometer<br>(Passive) | <ol> <li>Concealed operation</li> <li>Wide scanning range</li> <li>Independent from weather condition</li> <li>Velocity measurement</li> </ol>             | <ol> <li>Low radiated power</li> <li>Low resolution</li> </ol>     |

| Infrared imager                                | <ol> <li>Spatial and frequency resolution</li> <li>Concealed operation</li> </ol>                                                                          | <ol> <li>Weather condition</li> <li>No distance measure</li> </ol> |

And therefore the millimeter-wave circuits and systems are expected to contribute for both radars and wireless communication systems later on with a strong momentum boosted by commercial wireless applications [23-25]. Along with the

technical maturity in developing cost effective process and foundry for millimeter-wave application, emerging demand in new millimeter-wave radar sensors and wireless communication systems are expected to be fulfilled with highly integrated and multifunctional circuits and systems.

#### 1.1.5 Dissertation Organization

In this dissertation, various novel multi-band circuits and circuit architectures for the use of millimeter-wave radar and wireless communication systems are proposed. The dual-band circuits presented in this thesis are fabricated on Jazz 0.18- $\mu$ m BiCMOS process working at *K*/*Ka*/*Q*/*V* (24.5/35/44/60 GHz) -band frequency spectrum.

Chapter II starts with a concurrent dual-band T/R switch module with integrated filtering and calibration function (hereafter, T/R/Calibration switch module) for dual-polarization digital beam forming array architecture. In the newly proposed concurrent dual-band dual-polarization digital beam former architecture, the T/R/Calibration switch module provided dual-bandpass filtering function to avoid any blocker signals to saturate the receiver. Also the integrated calibration function enabled self-calibration both the transmit reference and receive calibration therefore enhancing accurate image synthesis of the full polarimetric digital beam former array system. Chapter III introduces novel concurrent dual-band low noise amplifiers with integrated dual-bandpass filtering function. The Q-enhanced dual-band quarter-wavelength network inspired by the composite right/left- handed metamaterial transmission line and its electrical dual

structure were utilized in realizing the dual-bandpass frequency response. The possible stability issue arose from the critical poles reside in the proposed Q-enhanced dual-band networks are resolved by employing an additional inter-stage matching network which provides pole/zero cancellation. The additional transmission zero added by the inter-stage matching network effectively suppressed the critical poles from over-compensation by the added negative resistance ensuring stable operation of the amplifiers with concurrent dual bandpass frequency response. Chapter IV proposes a new concurrent dual-band power amplifier design with dual-band impedance matching networks and harmonic termination provided by the metamaterial inspired networks. The techniques employed in this design provided filtering function to effectively suppress the intermodulation and harmonic frequency terms. Chapter V summarizes the contribution of the proposed development.

### **CHAPTER II**

### **CONCURRENT DUAL-BAND T/R/CALIBRATION SWITCH**

#### 2.1 RF CMOS Switch Architecture and Consideration

RF switches have played an important role in radar and communication systems. In the past, compound semiconductors such as GaAs were widely used for performance switching function in RF/millimeter-wave radar and communication systems. However, emerging demand for cost effective solutions in realizing RF/millimeter-wave systems lead the technical maturity of CMOS process, which has become a favorable solution even for millimeter-wave IC design. However, it is still challenging to design highperformance RF/millimeter-wave switches due to the inherent low resistivity substrate, low mobility, and various parasitic parameters of CMOS process. Hence, the fundamental T/R switch performance metrics and previous T/R switch works are overviewed.

## 2.1.1 T/R Switch Performance Metrics

A number of T/R switch performance metrics are introduced in this section. The basic performance parameters of the T/R switch design are: Insertion loss, Isolation, Linearity, and Impedance matching.

The insertion loss (IL) refers the power loss due to the switch which is characterized by the difference in output power and input power of the switch. Since the T/R switch is usually located at the front-end before antenna or array antenna systems, the insertion loss directly affects the noise figure (NF) of the system. Therefore, it is critical to keep the insertion loss as low as possible for any RF/millimeter-wave radar and communication systems.

The isolation (ISO) characterizes how much power is attenuated at the output compared to the input of the switch. For example, if the reception path in a Single-Pole Double-Throw (SPDT) T/R switch, the isolation is characterized over the transmission path. The difference in the input and output power level in the transmission path is designated is the isolation performance. The isolation of more than 30 dB is usually considered to be the minimum requirement.

The impedance matching condition is also an important measure of T/R switches. It is a measure of return loss at the input and the output ports of the turned-on path. The minimum return loss more than 10 dB is considered as reasonable.

The linearity performance indicates how much power the switch can handle without distortion or saturation. The 1-dB compression point (P1dB) and third-order intercept point (IP3) are the measure of linearity performances. The required P1dB and IP3 performance are in accordance with desired system performance.

Other consideration for switch design is switching speed, which is expected to be in the sub-nano second range in many millimeter-wave radar or communication system,

Figure 2.1. Conventional series-shunt switch architecture

low power consumption if it employs power consuming active devices, and easy integration with other circuits.

## 2.1.2 Conventional T/R Switch

A conventional T/R switch architecture is shown in Fig. 2.1. In the turned-on path, the series and shunt nMOS devices are turned on and off, respectively, and in the turned-off path, the series and shunt nMOS devices are turned off and on, respectively. With higher operating frequency, performance degradation in terms of insertion loss and isolation is easily observed due to parasitic capacitance between source and drain, low-resistivity bulk substrates [26-28]. As mentioned briefly, other compound semiconductors such as GaAs or GaN provides higher substrate resistance, which

minimizes leakage loss to the substrate [29-30]. There have been attempts to reduce the high-frequency leakage to the bulk substrate which resulted in bulk-floating switch architecture [31-32]. In this switch device, additional n-well layer isolates p-well of the nMOS switch device from the bulk substrate. Also, a biasing technique to keep the junction created by the n-p-n layer reverse biased to minimize the leakage is proposed as well. Other switch architecture which is commonly used for broadband operation is also proposed based on the synthetic transmission line formation and the architecture utilizes the off-state capacitance of shunt transistors to mimic that of a transmission line structure [33-34].

### 2.2 Concurrent Dual-band T/R/Calibration Switch Module

The proposed T/R/Calibration switch is presented in this section. The motivation of the multi-path T/R/Calibration switch work is introduced and then the new approach in realizing the concurrent dual bandpass filtering response and switch architecture will be presented. Finally, the complete four-port circuit design and the discussion on the measured performance will follow.

## 2.2.1 Introduction and Motivation

Multi-band systems offer a great deal of benefit in modern communication and radar systems. In particular, multi-band antenna-array radar systems with their extended

Figure 2.2.Digital beam forming array architecture

frequency diversity provide numerous advantages in detection, identification, locating and tracking a wide range of targets, including enhanced detection coverage, accurate target location, reduced survey time and cost, increased resolution, improved reliability and target information.

One of the challenging issues in an antenna-array system design is the calibration. Calibration is a critical issue, especially for millimeter-wave systems, due to various uncertainties such as imbalance and incoherence among receiver channels,

Figure 2.3.Calibration scheme (a) Transmit reference calibration and (b) Receive calibration

imbalances in amplitude and phase from components, unavoidable differences between LO signals, and power-distribution reconstruction errors in signal processing resulting from non-ideal situations. Especially for single-chip array systems, the inevitable

changes of signal parameters with process, voltage and temperature variations result in amplitude and phase errors in various constituent on-chip subsystems including the array transceiver.

In particular, an accurate calibration is a matter of significant importance for some array systems such as that proposed in Fig. 2.2 having bidirectional amplifiers for the digital beam forming (DBF) architecture in [35] or a location sensor in [36]. Moreover, in a fully polarimetric sensing system, the need of accurate calibration is critical since the ratios of amplitude and the deviations in phase between the four polarimetric (HH, VV, HV, and VH) signals contain important information for the image synthesis. A failure in accurate calibration may degrade the benefit of utilizing full polarimetry and result in misinterpretation of scattered signals. The accurate calibration can be achieved by system design in conjunction with digital signal processing. Achieving this very strict requirement of calibration is extremely difficult, particularly for systems-on-chip. A periodic calibration operation can help maintain the original performance of an array system by establishing the correction on the magnitude and phase in all the array channels.

The internal calibration for the proposed array system in Fig. 2.2 is composed of two operations, namely, transmit reference calibration and receive calibration.

In the transmit reference calibration, the dual-band receivers (VGA, Mixer and ADC chain) in Fig. 2.3(a). are calibrated first. A weak signal from the driver amplifier (DA) will be sent to Cal.H and Cal.V port and go through CalH and CalV path in the T/R/Calibration switch module and the corresponding dual-band receiver to compare the

output signals. The differences in amplitude and phase are recorded and designated as the receiver errors. Second, the weak signal from the DA will be directed to Tx.H and Tx.V port to go through TxH and TxV path in the T/R/Calibration switch module and the PA path of the bidirectional amplifier in each polarization channel. Third, the coupled signals from Pol.H and pol.V port will be sent to Cal.H and Cal.V port, respectively, and go through the corresponding H- and V- channel receiver. From the received signals, the designated receiver errors are subtracted to identify the deviations in magnitude and phase between each H- and V- channel, which are essentially the transmit errors. In the transmit mode of system, this transmit error will be adjusted by the calibration subsystem so the transmit signal for each H- and V- polarization can be maintained identical.

In the receive calibration, attenuated signals from RCal.H and RCal.V port in Fig. 2.3(b) will be distributed to Pol.H and Pol.V port, respectively. The injected signal will go through the LNA path in the bidirectional amplifier, RxH and RxV path in the T/R/Calibration switch module and the dual-band receiver. The discrepancies of the amplitude and phase in the received signal between H- and V- channels will be recorded in a digital signal processor (DSP) block and classified as the gain and phase errors of the entire receiver including the LNA in the bidirectional amplifier, T/R/Calibration switch module and receiver. In the received signal between the gain and phase errors of the entire receiver including the LNA in the bidirectional amplifier, T/R/Calibration switch module and dual-band receiver. In the reception mode of system, this receiver error will be subtracted from the signals reflected by intended targets.

In operation, a potential target is illuminated in the transmission mode with calibrated transmitting signals and the backscattered signal from the target is received through the antennas of all receivers in the reception mode. The digitalized output signals in this mode are essentially the backscattered signals from the target with the inherent gain and phase errors of the receiver channels embedded. The DSP then subtracts the errors recorded in the receive calibration mode from the received signals to extract useful information. This calibration procedure can also be used as a built-in diagnosis tools to self-check the system's function [36].

Compare to the RF domain phase shifting array architectures, which possess a spatial beam steering function [37], the digital beam former performs multiple beam generation at the DSP. Such array architecture without a spatial filtering operation is vulnerable to unfiltered strong interference signals, which may saturate receiver channels and burden baseband circuits including ADC with linearity and power consumption issues [35]. Therefore, it would be of a great benefit to reject out-of-band signals to alleviate the burden of both RF and baseband blocks in the DBF array system.

This section presents a novel fully integrated concurrent dual-band 0.18-µm BiCMOS T/R/Calibration switch module in *K*- and *Ka*-band centered at 24.5 and 35 GHz, combining the transmit/receive (T/R) function with the integrated calibration and filter function, for dual-band array systems such as the DBF array shown in Fig. 2.2 using Jazz 0.18-µm BiCMOS process [38]. Possible application of the T/R/Calibration switch module is in a communication or sensing dual-band system, which works in two different bands centered at 24.5 and 35 GHz simultaneously, such as that described in Fig. 2.2.

#### 2.2.2 Background Theories

There has been a significant interest in the use of metamaterial composite right/left-handed (CRLH) transmission lines (TLs). The artificial combination of right-handed (RH) and left-handed (LH) networks enables the phase delay control of CRLH TLs [39-43]. The CRLH TL is characterized by its phase constant  $\beta_{CRLH}$  and characteristic impedance  $Z_{CRLH}$ , which provide conditions to determine the transmission line's dispersion, as

$$\beta_{CRLH} = \omega \sqrt{L_R C_R} - \frac{1}{\omega \sqrt{L_L C_L}}$$

(2.1)

$$Z_{CRLH} = \sqrt{\frac{L_R}{C_R}} = \sqrt{\frac{L_L}{C_L}}$$

(2.2)

where  $L_R$ ,  $C_R$  and  $L_L$ ,  $C_L$  are the inductance, capacitance for the right handedness and left handedness per unit cell of the CRLH TL, respectively. Equations (2.1)-(2.2) offer an extra degree of freedom to control the phase delay of a CRLH TL. This property can be utilized to realize quarter-wavelength TLs at two arbitrary design frequencies. In other words, the general dispersive phase delay relationship of a CRLH TL as shown in Eq. (2.1) enables the quarter-wavelength characteristic at two arbitrary frequencies upon enforcing the characteristic impedance condition in Eq. (2.2).

#### 2.2.3 T/R/Calibration Switch Module Design

In this section, the proposed concurrent dual *K/Ka*-band T/R/Calibration switch module design is introduced in detail. First, the fundamental ideas in realizing dual bandpass filtering frequency response will be presented, which will be followed by circuit level details with complete module's performance evaluation.

#### 2.2.3.1 Cascaded Quasi-elliptic Dual-bandpass Network

One of the major concerns in developing the T/R/Calibration switch module presented in this paper is to create a dual-band filtering function in the receiver path. As briefly explained earlier, the DBF array transceiver shown in Fig. 2.2 operates without a spatial beam steering function and therefore a rejection of out-of-band signals is essential. By employing bandpass filtering function in the proposed T/R/Calibration switch module, it was intended to achieve an out-of-band rejection of more than 30 dB below 10.5 GHz and above 59 GHz (2nd order IMDs).

Fig. 2.4 shows the cascaded quasi-elliptic dual-bandpass network, which is the main body of the complete T/R/Calibration switch module, assuming (non-resistive) ideal elements. It can be divided into two separate parts, namely, a bandpass filter (BPF) and a CRLH section, which are separately synthesized to meet certain magnitude and phase delay specifications, respectively.

|     | CRLH                        | Component values<br>for cascaded dual-bandpass network<br>with quasi-elliptic response                                            |  |  |  |

|-----|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|     | $L_{R/2} $                  | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                            |  |  |  |

| BPF | <sup>2C<sub>L</sub></sup> ‡ | $\begin{array}{c} \mathbf{C}_{\mathrm{L}} 2 7 3 5 0 \mathbf{H} \\ \mathbf{L}_{\mathrm{L}} 68.9 \mathbf{p} \mathbf{H} \end{array}$ |  |  |  |

Figure 2.4.Cascaded quasi-elliptic dual-bandpass network

The BPF is the third-order type-I Chebyshev filter with an additional inductor (L<sub>2</sub>) inserted in the shunt resonator tank to realize an additional rejection-zero at 65 GHz. The rejection-zero was added to make the high-frequency skirt characteristic sharper. The insertion loss (S21) and pole/zero plots associated with the BPF are presented in Figs. 2.5(a) and (b), respectively. As shown in Fig. 2.5(a), the BPF is wideband with a bandwidth of 13.5 GHz centered at 30 GHz. The associated pole/zero plot in Fig. 2.5(b) shows two zeros at the origin and a complex conjugate pair of zeros at 65 GHz. This BPF network has two poles at 23.28 GHz and 36.78 GHz which determines its bandwidth.

The S21 and pole/zero plot of the CRLH are displayed in Figs. 2.5(a) and (c), respectively. As explained in the previous section, this CRLH network creates quarter-wavelength consecutively to make open at two design frequencies, herein, 24.5 and 35 GHz. It can be seen from Fig. 2.5(a) that the insertion losses at the design frequencies are 0 dB due to this extra ordinary phase delay of this network. Also observed in the plot is a rejection occurring at the transition frequency of 29.28 GHz. In the pole/zero plot for

Figure 2.5.(a) S21 plot, (b) Pole/Zero plot: BPF, (c) Pole/Zero plot: CRLH TL, and (d) Pole/Zero plot: Cascaded BPF and CRLH TL

the CRLH network, the overlapped pole/zero pairs on the  $j\omega$  axis at 24.5 and 35 GHz suggest that this network has no loss at those design frequencies. The transmission zeros in the S21 plot also appears in the pole/zero plot.

Along with the poles and zeros on the  $j\omega$  axis, what should be examined closely are the critical poles of the CRLH network. The critical pole which appears at 29.22 GHz should be of a great concern since its frequency is very close to the zero appearing at 29.28 GHz. Thus if a certain margin of stability is not guaranteed, the critical pole at

Figure 2.6.Simulated (a) S21 of two-port CRLH and (b) phase of S11 of one-port CRLH

29.22 GHz would start to move toward the  $j\omega$  axis of the pole/zero plot, and eventually reaching the threshold of an oscillation. The calculated component values for +90° and -90° at the two design frequencies in the paper, 24.5 and 35 GHz, using a single unit cell of the CRLH are listed in Table I. The characteristic impedance for this network is 50 Ohm. This CRLH section will be coupled with a negative-resistance generation circuit to be presented later to improve the quality factor at 29.28 GHz.

The dual-bandpass filtering function of the entire network in Fig. 2.4 is realized by cascading the BPF and CRLH sections discussed above. As shown in Fig. 2.5(a), the BPF section creates a wide pass-band including the design frequencies of 24.5 and 35 GHz while the CRLH section creates open only at these two design frequencies. The S21 plot of the entire cascaded network is also presented in Fig. 2.5(a), showing a dual-bandpass filtering characteristic. It can be seen from the pole/zero plot of this entire network in Fig. 2.5(d) that all the poles and zeros observed in the separate BPF and CRLH networks appear together. By examining the pole/zero locations shown in Fig. 2.5(d), it can be seen that this network provides quasi-elliptic frequency response. Although the entire network in Fig. 2.4 may be considered as a dual-bandpass filter, categorizing it as a network with a quasi-elliptic dual-bandpass response, rather than as a dual-bandpass filter, is more reasonable since the dual-band frequency response of the CRLH section is the result of a specific phase delay, not a dual-band filter synthesis based on magnitude specifications per se.

# 2.2.3.2 Dual-band Quarter-wavelength Network Coupled with a Negative Resistance Generation Circuit

A difficulty in utilizing the CRLH TL for a dual-bandpass filtering function presented in the previous section is the low quality factors (Q) of on-chip components, especially those of inductors. They significantly deteriorate the frequency response and limit the signal rejection at the transition frequency to around 15 dB. Figs. 2.6(a) and (b) show the simulated insertion loss and the phase of the reflection coefficient of two-port

Figure 2.7.(a) Original passive CRLH network and (b) CRLH network coupled with a Colpitts style negative resistance generation circuit

and one-port single-cell CRLH networks, respectively, using the ideal and actual on-chip components.

For the simulation results with on-chip components, the real PDK (process design kit) capacitors from Jazz 0.18-µm BiCMOS process [38] and actual EM-simulated spiral inductors are used. As shown in Fig. 2.6.(a), the frequency response with the actual on-chip components loses its sharp frequency response due to the components' low Q, while still maintaining the intended phase delay at the design frequencies as seen in Fig. 2.6(b). As displayed in Fig. 2.6(b), the phase of S11 of the one-port CRLH structure crosses zero consecutively at the two design frequencies, thereby providing a sufficient condition to prove that this network creates an open in virtue of the quarter-wavelength at the design frequencies. A difficulty in utilizing the

CRLH TL for a dual-bandpass filtering function presented in the previous section is the low quality factors (Q) of on-chip components, especially those of inductors. They significantly deteriorate the frequency response and limit the signal rejection at the transition frequency to around 15 dB. Figs. 2.6(a) and (b) show the simulated insertion loss and the phase of the reflection coefficient of two-port and one-port single-cell CRLH networks, respectively, using the ideal and actual on-chip components.

To overcome the low Q issue, a Colpitts style negative-resistance generation circuit is coupled with the CRLH network as shown in Fig. 2.7. The original passive CRLH network is shown in Fig. 2.7(a) and the CRLH network with improved Q is described in Fig. 2.7(b). It should be noted that the transition frequency appears at [41]

$$\omega_0 = \frac{1}{\sqrt[4]{L_R C_R L_L C_L}}$$

(2.3)

The resonant frequencies of series  $L_R$  and  $C_L$  and shunt  $L_L$  and  $C_R$  are

$$\omega_{SE} = \frac{1}{\sqrt{L_R C_L}}, \quad \omega_{SH} = \frac{1}{\sqrt{L_L C_R}}$$

(2.4)

respectively. These resonant frequencies are equal upon enforcing the condition (2.2) which leads  $\omega_0 = \omega_{SE} = \omega_{SH}$ . A Colpitts style negative resistance generation circuit is coupled with the original CRLH network as shown in Fig. 2.7(b) at  $L_R/2$  and  $2C_L$  section

of which resonant frequency is  $\omega_{SE}$ . The input impedances designated in Fig. 2.7(b) can be expressed as

$$Z_{IN}^{CRLH} = (j\omega L_R / 2 + \frac{1}{j\omega 2C_L}) + (j\omega L_L \| \frac{1}{j\omega C_R}) \| Z_{IN,Colpitts}^{CRLH}$$

(2.5)

$$Z_{IN,Colpitts}^{CRLH} = R_{L_R/2} + j\omega L_R/2 + \frac{1}{j\omega} \left(\frac{1}{C_1} + \frac{1}{C_2}\right) - \frac{g_m}{\omega^2 C_1 C_2}$$

(2.6)

where  $R_{Lg/2}$  and  $g_m$  are the resistance of the inductor  $L_R/2$  and the transconductance of the BJT Q<sub>1</sub>, respectively. The resistance is inserted only in (2.6) to facilitate manifesting a condition for Q enhancement. For the circuit in Fig. 2.7(b) to operate properly, it is necessary for it to maintain the same phase delay as in the original network shown in Fig. 2.7(a). To that end, the capacitor values of C<sub>1</sub> and C<sub>2</sub> must comply with the condition below, excluding parasitic capacitances to accommodate the desired phase delay and hence the unique dual-band characteristic offered by the CRLH TL:

$$2C_L = \frac{C_1 C_2}{C_1 + C_2} \tag{2.7}$$

Also, the current level which determines the transconductance of Q1 should be chosen carefully to prevent a possible instability which could arise from the existence of a negative resistance. As is seen in (2.6), the negative  $g_m$  can effectively cancel out the resistance in the network, thereby enhancing the Q at the transition frequency. However, an excessive negative resistance at the transition frequency (29.28 GHz) can cause the adjacent critical pole at 29.22 GHz driven to the  $j\omega$  axis on the pole/zero map, leading the network to an oscillation state or a marginally stable state. The critical pole at 29.22 GHz was already verified with the pole/zero analysis of the CRLH network.

The marginal stability condition when the oscillation could possibly occur due to the excessive negative  $g_m$  can be derived from (2.6). Besides the resistance  $R_{Lg/2}$  in the Colpitts negative-resistance generation section of the CRLH network, there is also some resistance introduced by external circuits connected to this network. The quantitative expression for a marginal stability can then be written as

$$\frac{g_m^{osc}}{\omega^2 C_1 C_2} = R_{L_R/2} + R_{ext}$$

(2.8)

where  $g_m^{osc}$  and  $R_{ext}$  mean the transconductance for an oscillation and resistance introduced by external circuits, respectively. The optimum transconductance  $g_m^{opt}$  for Q enhancement without an oscillation can be derived as

$$g_m^{opt} = \omega^2 C_1 C_2 R_{L_g/2} \tag{2.9}$$

By taking the ratio of (2.8) for the possible oscillation and (2.9) for the optimum resistance cancellation, the safety margin can be obtained as

$$I_{osc} = I_{opt} \left( 1 + \frac{R_{ext}}{R_{L_R/2}} \right)$$

(2.10)

where  $I_{osc}$  and  $I_{opt}$  are the current for oscillation and optimum resistance cancellation, respectively. From (2.10), it can be observed that the current for an oscillation is always larger than the current for the optimum resistance cancellation for Q enhancement. The additional resistance introduced with external circuits hence prevents oscillation from an excessive negative transconductance by adding more loss which preserves a stable operation.

# 2.2.4 T/R/Calibration Switch Module Architecture, Analysis, and Design

In this section, the developed concurrent dual *K/Ka*- band T/R/Calibration switch module with quasi-elliptic dual-bandpass frequency response is presented with its entire architecture.

Since the switch function of the proposed module is dependent on the nMOS transistors, the physical structure of deep n-well nMOS transistor will be overviewed first. A biasing technique to overcome the inherent high-frequency leakage path is presented for the use of the deep n-well nMOS transistors as switch. The entire integrated switch module architecture which supports dual bandpass filtering function in multi paths are presented in detail with the complete integrated digital control circuitry for a pair of T/R/Calibration switch module for both V- and H- polarization transceiver.

## 2.2.4.1 Deep n-well NMOS Transistors

Figure 2.8.(a) Cross sectional view of nMOS transistor, (b) its equivalent circuit, and simplified (c) on-state, and (d) off-state equivalent circuits.  $C_{SD}$ ,  $C_{SB}$ ,  $C_{DB}$ ,  $R_{CH}$ , and  $R_{SUB}$  represent the parasitic capacitance between the source and drain, source and body, drain and body, on-state resistance, and equivalent resistance of the substrate, respectively.

Fig. 2.8 presents a simplified cross-sectional geometry of a deep n-well CMOS transistor and its equivalent-circuit model. Deep n-well transistors have been used in the design of switches [45-48]. The deep n-well provides isolated p-well for nMOS devices,

Figure 2.9.Insertion loss and isolation for different nMOS gate widths

thus floating them on a bulk substrate. To prevent the signal loss due to the junction capacitance caused by the deep n-well, it can be biased at 1.8 V while the isolated p-well/p-substrate is biased at 0 V, thus keeping the junction diodes reverse-biased all the time [44-47]. Along with the deep n-well process, a double deep trench, as seen in Fig. 2.8(a), is also used in the actual layout to prevent the coupling of noise and unwanted signals from adjacent devices.