# REDUCING WASTE IN MEMORY HIERARCHIES

A Dissertation

by

# YINGYING TIAN

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Daniel A. Jiménez |

|---------------------|-------------------|

| Committee Members,  | Nancy M. Amato    |

|                     | Eun Jung Kim      |

|                     | Paul V. Gratz     |

| Head of Department, | Dilma Da Silva    |

May 2015

Major Subject: Computer Science

Copyright 2015 Yingying Tian

#### ABSTRACT

Memory hierarchies play an important role in microarchitectural design to bridge the performance gap between modern microprocessors and main memory. However, memory hierarchies are inefficient due to storing waste. This dissertation quantifies two types of waste, dead blocks and data redundancy. This dissertation studies waste in diverse memory hierarchies and proposes techniques to reduce waste to improve performance with limited overhead.

This dissertation observes that waste of dead blocks in an inclusive last level cache consists of two kinds of blocks: blocks that are highly accessed in core caches and blocks that have low temporal locality in both core caches and the last-level cache. Blindly replacing all dead blocks in an inclusive last level cache may degrade performance. This dissertation proposes temporal-based multilevel correlating cache replacement to improve performance of inclusive cache hierarchies.

This dissertation observes that waste exists in private caches of graphics processing units (GPUs) as *zero-reuse blocks*. This dissertation defines zero-reuse blocks as blocks that are dead after being inserted into caches. This dissertation proposes adaptive GPU cache bypassing techinque to improve performance as well as reducing power consumption by dynamically bypassing zero-reuse blocks.

This dissertation exploits waste of data redundancy at the block-level granularity and finds that conventional cache design wastes capacity because it stores duplicate data. This dissertation quantifies the percentage of data duplication and analyze causes. This dissertation proposes a practical cache deduplication technique to increase the effectiveness of the cache with limited area and power consumption.

# TABLE OF CONTENTS

|     |                          | Р                                                                                                                                                                      | age                                                                                                     |

|-----|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| AF  | BSTR                     | ACT                                                                                                                                                                    | ii                                                                                                      |

| TA  | BLE                      | OF CONTENTS                                                                                                                                                            | iii                                                                                                     |

| LIS | ST O                     | F FIGURES                                                                                                                                                              | vi                                                                                                      |

| LIS | ST O                     | F TABLES                                                                                                                                                               | viii                                                                                                    |

| 1.  | INT                      | RODUCTION                                                                                                                                                              | 1                                                                                                       |

|     | 1.1<br>1.2<br>1.3<br>1.4 | The Problem: Cache Waste                                                                                                                                               | $     \begin{array}{c}       1 \\       2 \\       3 \\       5 \\       5 \\       5     \end{array} $ |

| 2.  | BAC                      | CKGROUND AND RELATED WORK                                                                                                                                              | 7                                                                                                       |

|     | 2.1<br>2.2<br>2.3<br>2.4 | Dead Block Prediction                                                                                                                                                  | 7<br>8<br>9<br>11                                                                                       |

| 3.  | PRE                      | ELIMINARY WORK                                                                                                                                                         | 13                                                                                                      |

|     | $3.1 \\ 3.2 \\ 3.3$      | Sampling Dead Block Predictor                                                                                                                                          | 13<br>14<br>15                                                                                          |

| 4.  |                          | DUCING WASTE OF DEAD BLOCKS IN INCLUSIVE CACHE HI-                                                                                                                     | 16                                                                                                      |

|     | 4.1<br>4.2               | MotivationTemporal-based Multi-level Correlating Cache Replacement4.2.1Correlating Temporal Locality Detector4.2.2How Does TMC Work?4.2.3Comparison with Previous Work | 16<br>19<br>20<br>24<br>27                                                                              |

|    | 4.3 | Experimental Methodology                                           | 29 |

|----|-----|--------------------------------------------------------------------|----|

|    |     | 4.3.1 Simulation Environment                                       | 29 |

|    |     | 4.3.2 Benchmarks                                                   | 31 |

|    | 4.4 | Evaluation                                                         | 31 |

|    |     | 4.4.1 Performance Improvement with Inclusion-Sensitive Workloads   | 33 |

|    |     | 4.4.2 Performance Improvement with Inclusion-Insensitive Workloads | 35 |

|    |     | 4.4.3 Compared to an Enhanced Non-inclusive Cache                  | 37 |

|    |     | 4.4.4 Scalability Analysis                                         | 38 |

|    |     | 4.4.5 Detection Accuracy and Coverage                              | 42 |

|    |     | 4.4.6 Overhead Analysis                                            | 42 |

|    | 4.5 | Summary                                                            | 45 |

| 5. | REI | DUCING WASTE OF DEAD BLOCKS IN GPU PRIVATE CACHES .                | 47 |

|    | 5.1 | Motivation                                                         | 48 |

|    |     | 5.1.1 Memory Characteristics of GPGPU Programs                     | 48 |

|    |     | 5.1.2 Improving GPU Caches                                         | 50 |

|    | 5.2 | Adaptive GPU Cache Bypassing                                       | 51 |

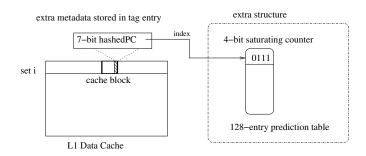

|    |     | 5.2.1 Structure of PC-based Bypass Predictor                       | 54 |

|    |     | 5.2.2 Prediction Algorithm Details                                 | 56 |

|    |     | 5.2.3 Comparison with Counter-based Bypass Prediction              | 59 |

|    | 5.3 | Experimental Methodology                                           | 60 |

|    |     | 5.3.1 Simulation Environment                                       | 60 |

|    |     | 5.3.2 Benchmarks                                                   | 60 |

|    | 5.4 | Evaluation                                                         | 62 |

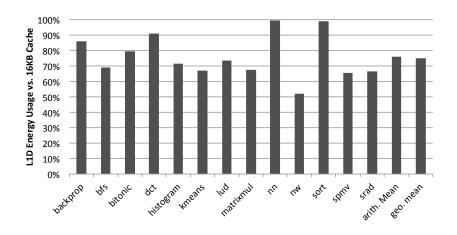

|    |     | 5.4.1 Energy Saving                                                | 62 |

|    |     | 5.4.2 Performance                                                  | 63 |

|    |     | 5.4.3 Prediction Accuracy and Coverage                             | 66 |

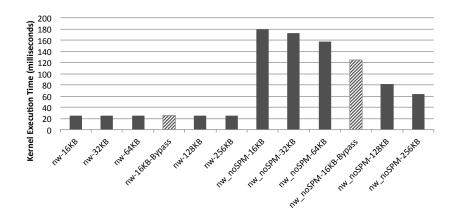

|    |     | 5.4.4 A Case Study of Benchmark <i>Needleman-Wunsch</i>            | 69 |

|    | 5.5 | Summary                                                            | 70 |

| 6. | REI | DUCING DATA REDUNDANCY IN THE LAST LEVEL CACHES                    | 72 |

|    | 6.1 | Reasons of Cache Deduplication                                     | 72 |

|    | 6.2 | Challenges of Reducing Data Redundancy                             | 75 |

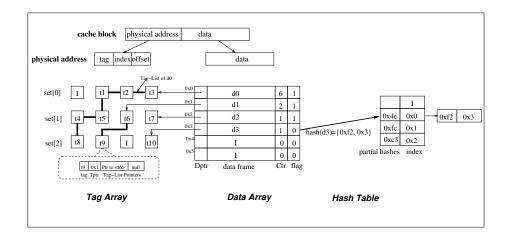

|    | 6.3 | Deduplicated Last-Level Cache                                      | 77 |

|    |     | 6.3.1 Structure                                                    | 77 |

|    |     | 6.3.2 Operations                                                   | 81 |

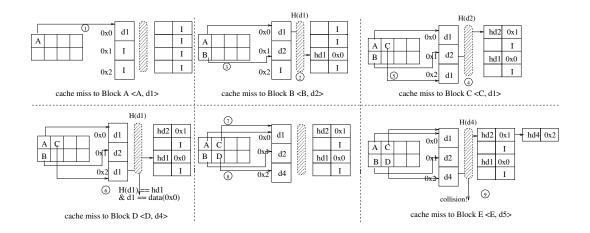

|    |     | 6.3.3 An Example of Hash-based Post-Process Deduplication          | 83 |

|    |     | 6.3.4 Hash Collision Resolution                                    | 85 |

|    | 6.4 | Experimental Methodology                                           | 86 |

|    |     | 6.4.1 Simulation Environment                                       | 86 |

|    |     | 6.4.2 Benchmarks                                                   | 88 |

|    | 6.5  | Evalua | ation                                                        | 89  |

|----|------|--------|--------------------------------------------------------------|-----|

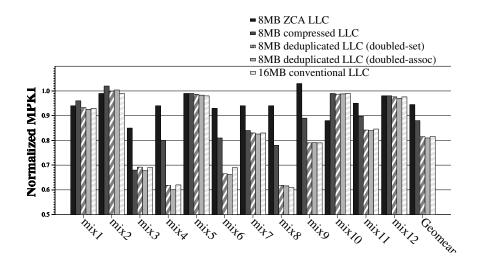

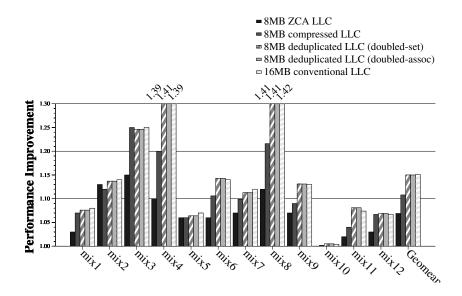

|    |      | 6.5.1  | Performance Improvement                                      | 89  |

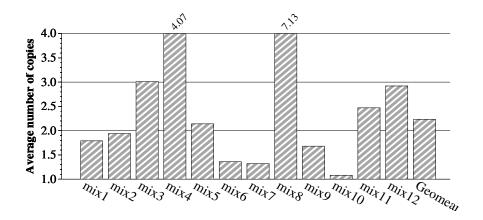

|    |      | 6.5.2  | Effective Cache Capacity                                     | 91  |

|    |      | 6.5.3  | Storage Analysis                                             | 93  |

|    |      | 6.5.4  | Power and Energy                                             | 94  |

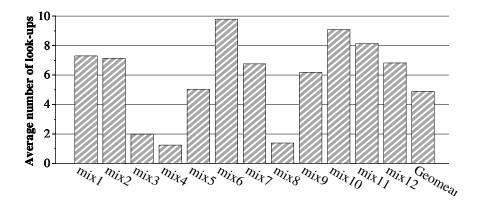

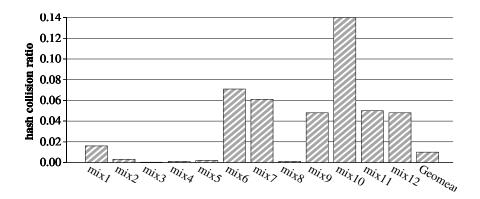

|    |      | 6.5.5  | Hashing Analysis                                             | 94  |

|    |      | 6.5.6  | Process Latency                                              | 97  |

| 7. | CON  | ICLUS  | ION                                                          | 98  |

|    | 7.1  | Reduc  | ing Waste Caused By Dead Blocks in Inclusive Cache Hierarchy | 98  |

|    | 7.2  | Reduc  | ing Waste Caused By Dead Blocks in GPU Private Caches        | 99  |

|    | 7.3  | Reduc  | ing Wasted Caused By Data Redundancy in Last-Level Caches    | 99  |

| Rł | EFER | ENCES  | 5                                                            | 100 |

# LIST OF FIGURES

| FIGURE |                                                                                                       |    |

|--------|-------------------------------------------------------------------------------------------------------|----|

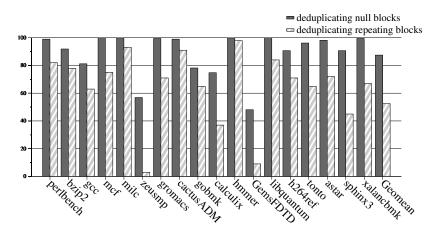

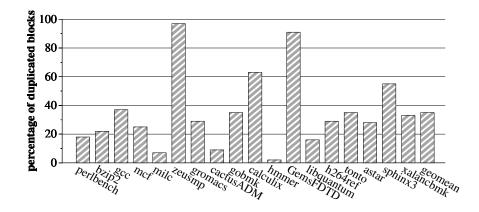

| 1.1    | Percentage of distinct blocks for null block deduplication and all re-<br>peating block deduplication | 4  |

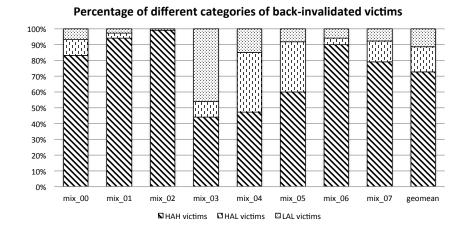

| 4.1    | Percentage of different categories of back-invalidated blocks due to LLC LRU replacement              | 18 |

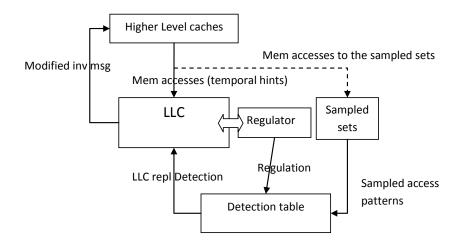

| 4.2    | Block diagram of CTL detector                                                                         | 21 |

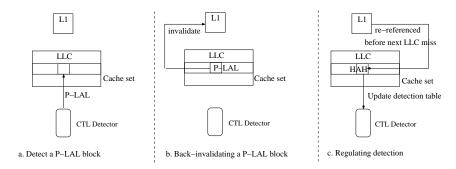

| 4.3    | Detect HAH blocks from P-LAL blocks                                                                   | 26 |

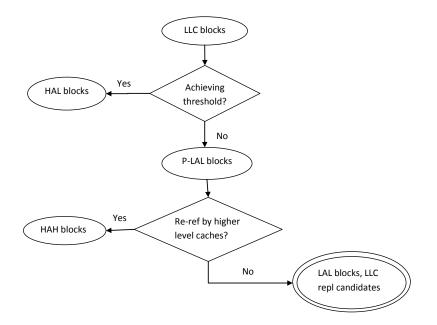

| 4.4    | Two-level detection of LLC block categorization                                                       | 27 |

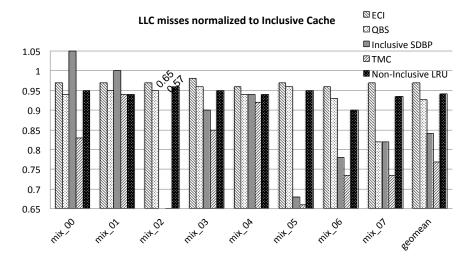

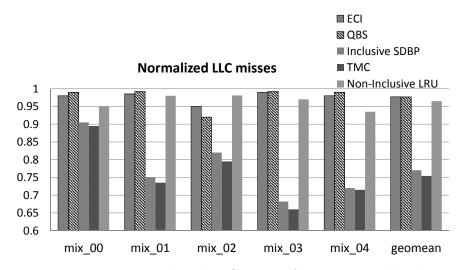

| 4.5    | LLC misses for inclusion-sensitive workloads                                                          | 33 |

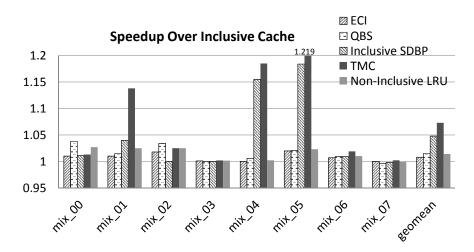

| 4.6    | Performance improvement of inclusion-sensitive workloads $\ldots \ldots$                              | 34 |

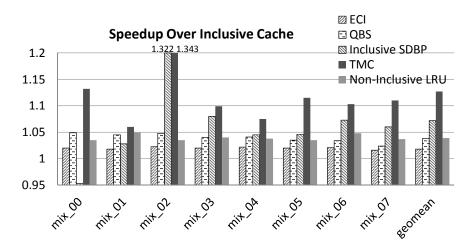

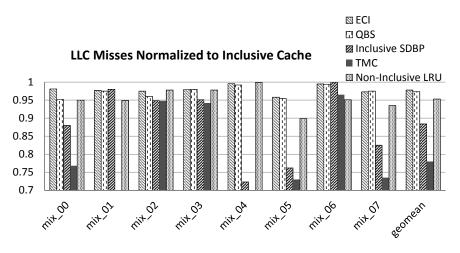

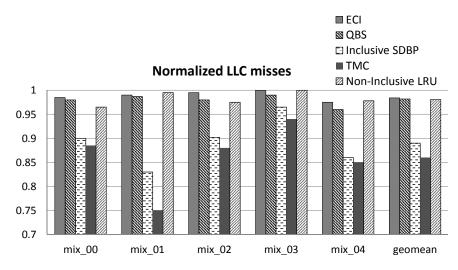

| 4.7    | LLC misses for inclusion-insensitive workloads                                                        | 35 |

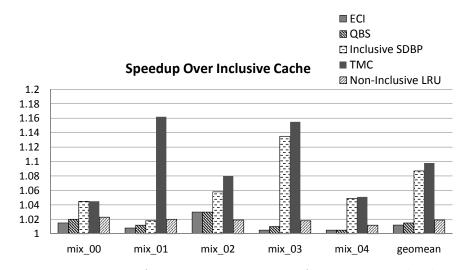

| 4.8    | Performance improvement of inclusion-insensitive workloads                                            | 36 |

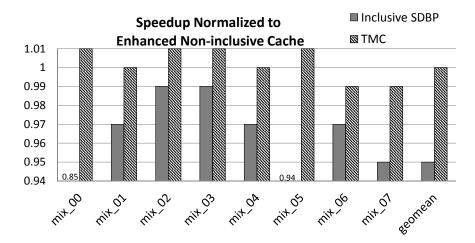

| 4.9    | Speedup normalized to enhanced non-inclusive cache                                                    | 37 |

| 4.10   | Normalized LLC misses for 4-core workloads                                                            | 38 |

| 4.11   | Normalized LLC misses for 8-Core workloads                                                            | 39 |

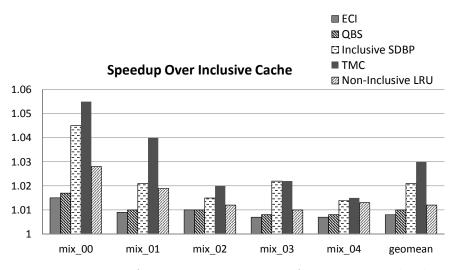

| 4.12   | Performance improvement for 4-core workloads                                                          | 40 |

| 4.13   | Performance improvement for 8-core workloads                                                          | 40 |

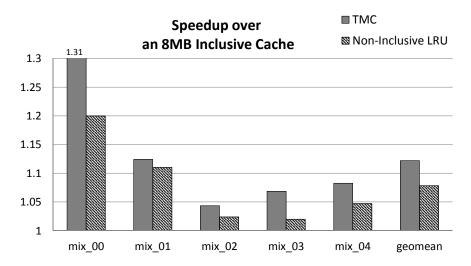

| 4.14   | Performance improvement for 8-core workloads on 8MB LLC                                               | 42 |

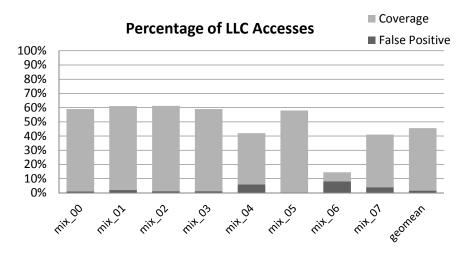

| 4.15   | Coverage and false positive rate of CTL detector                                                      | 43 |

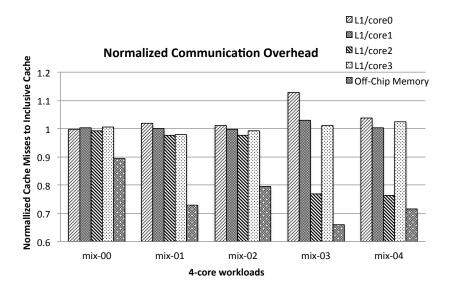

| 4.16   | Normalized communication overhead for 4-core workloads                                                | 45 |

| 5.1    | Zero-reuse blocks in the L1 data cache                                                                | 49 |

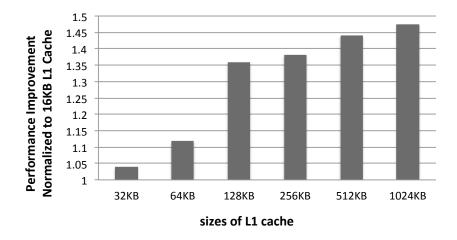

| 5.2  | Performance improvement normalized to a 16KB L1 cache with different cache sizes                                                                                                                                                                                           | 50 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

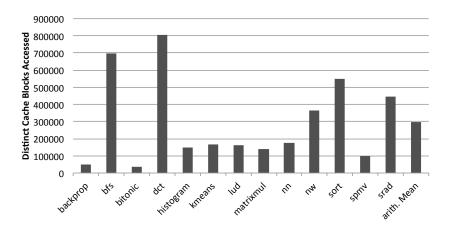

| 5.3  | Number of distinct blocks accessed in execution of each benchmark .                                                                                                                                                                                                        | 53 |

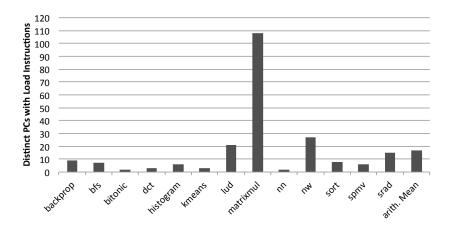

| 5.4  | Number of distinct load instruction PCs executed in each benchmark                                                                                                                                                                                                         | 53 |

| 5.5  | Structure of PC-based bypass predictor in GPU L1 cache                                                                                                                                                                                                                     | 55 |

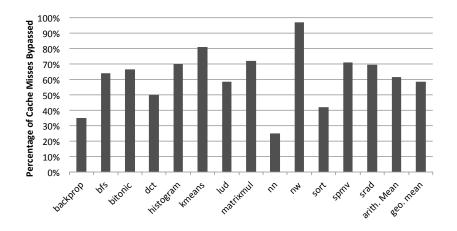

| 5.6  | Ratio of bypasses to cache misses                                                                                                                                                                                                                                          | 63 |

| 5.7  | Energy usage of 16KB cache with by<br>passing (relative to baseline) $$ .                                                                                                                                                                                                  | 64 |

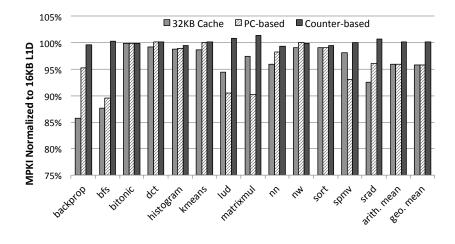

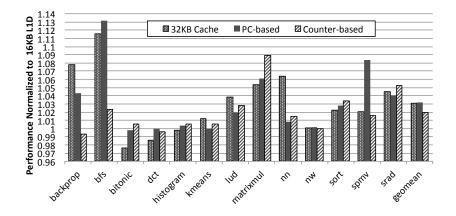

| 5.8  | Reduction in L1 misses for different techniques                                                                                                                                                                                                                            | 67 |

| 5.9  | Speedup over the baseline for different techniques                                                                                                                                                                                                                         | 67 |

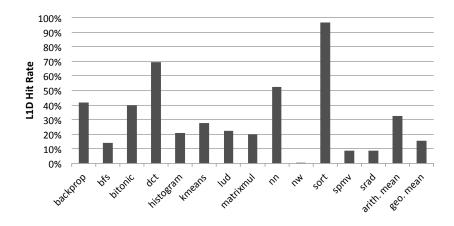

| 5.10 | L1 cache hit rate of each benchmark in the baseline $\ldots \ldots \ldots \ldots$                                                                                                                                                                                          | 68 |

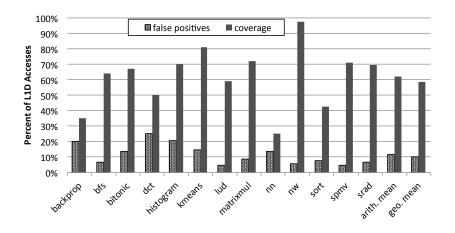

| 5.11 | False positive and coverage of bypassing predictor                                                                                                                                                                                                                         | 68 |

| 5.12 | Execution time of nw with different configurations                                                                                                                                                                                                                         | 70 |

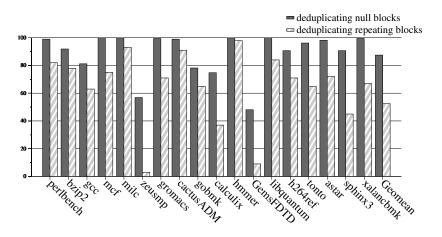

| 6.1  | Average percentage of duplicated blocks in LLC                                                                                                                                                                                                                             | 73 |

| 6.2  | Percentage of distinct blocks for null-block deduplication and full-<br>block deduplication                                                                                                                                                                                | 74 |

| 6.3  | Structure of a deduplicated LLC. Blocks t1, t2, t3, t4, t5 and t8 are duplicated blocks, sharing identical data d0; t6 and t9 share data d1; t7 is a distinct block with data d2; and, t10 is inserted as a distinct block and has not been analyzed for deduplication yet | 78 |

| 6.4  | An example of hash-based post-process last-level cache deduplication                                                                                                                                                                                                       | 84 |

| 6.5  | Reduction in LLC misses normalized to 8MB conventional LLC $~$                                                                                                                                                                                                             | 91 |

| 6.6  | Performance Improvement normalized to 8MB conventional LLC                                                                                                                                                                                                                 | 92 |

| 6.7  | Average amount of duplication                                                                                                                                                                                                                                              | 92 |

| 6.8  | Average number of look-ups for data comparison                                                                                                                                                                                                                             | 96 |

| 6.9  | Hash collision                                                                                                                                                                                                                                                             | 96 |

# LIST OF TABLES

| TABLE |                                                                                                                                                                                                                                                             |    |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.1   | Inclusion-sensitive dual-core workloads                                                                                                                                                                                                                     | 32 |

| 4.2   | Inclusion-insensitive dual-core workloads                                                                                                                                                                                                                   | 32 |

| 4.3   | 4-core workloads                                                                                                                                                                                                                                            | 32 |

| 4.4   | 8-core workloads                                                                                                                                                                                                                                            | 32 |

| 4.5   | Legend for the baseline and various cache optimization techniques                                                                                                                                                                                           | 33 |

| 4.6   | Dynamic and leakage power of TMC (Watts)                                                                                                                                                                                                                    | 44 |

| 5.1   | System configuration                                                                                                                                                                                                                                        | 61 |

| 5.2   | Workloads and inputs                                                                                                                                                                                                                                        | 61 |

| 5.3   | Power cost                                                                                                                                                                                                                                                  | 62 |

| 6.1   | The 18 SPEC CPU2006 benchmarks with LLC cache misses per 1,000 instructions for LRU, instructions per cycle for LRU in a 2MB cache, and number of instructions fast-forwarded to reach the simpoint (B = billions). Memory-intensive benchmarks in boldface | 89 |

| 6.2   | 12 mixes of quad-core workload ('F' stands for deduplication-friendly, 'S' for deduplication-sensitive and 'I' for deduplication-insensitive)                                                                                                               | 90 |

| 6.3   | Storage cost analysis                                                                                                                                                                                                                                       | 93 |

| 6.4   | Dynamic and leakage power of each LLC design                                                                                                                                                                                                                | 95 |

| 6.5   | Dynamic energy cost of each LLC and main memory                                                                                                                                                                                                             | 95 |

#### 1. INTRODUCTION

Memory is essential to a computer system to store code and data. Modern computer systems use a hierarchical memory design to bridge the performance gap between microprocessors and main memory with reasonable cost. Memory hierarchies work by exploiting *locality of reference* [11, 28], *i.e.* the observation that memory references tend to be localized in terms of time and space, referred to as *temporal locality* and *spatial locality*, respectively.

Caches [106] store instructions and data that exhibit locality with low access latencies. Caches are usually small and fast compared to the main memory. References to memory locations that are stored in caches can be satisfied in just a few clock cycles, while a miss in the last-level cache will go all the way down to significantly slower DRAM main memory, incurring hundreds of cycles of delay. The cache plays an important role in modern processors as a performance-critical structure to reduce the average memory access latency and provide high bandwidth. Compared to main memory, cache technology typically costs more per-bit, but an efficient cache can be large enough to hold only the working set of an application, and thus have most of the accesses hit in the cache, leading to far faster accesses and often less energy consumption than main memory. However, in practices caches are often inefficient because they store useless or redundant data, leading to a significant waste of storage.

# 1.1 The Problem: Cache Waste

This dissertation quantifies two types of waste: dead blocks [64] and data redundancy [73].

#### 1.1.1 Waste of Dead Blocks

Caches organize data and instructions into fixed-sized blocks of *e.g.* 64 bytes. A cache block is *dead* from the last reference to that block until the block is evicted from the cache [64]. Dead blocks lead to cache inefficiency [14] and should be replaced by useful blocks as early as possible to improve cache efficiency. Previous work [64, 58, 56] introduced several dead block prediction techniques to reduce dead blocks in last-level caches (LLCs) for chip-multiprocessors (CMPs). However, these techniques cannot be directly applied to other cache types due to different cache characteristics.

## 1.1.1.1 Dead Blocks in Inclusive Caches

Inclusive caches have been widely used in chip-multiprocessors to simplify cache coherence. They suffer from poor performance compared to non-inclusive or exclusive caches because of the limited capacity of the inclusive cache hierarchy, and ignorance of temporal locality in the last-level cache. Blocks that are highly referenced (referred to as *hot blocks*) are always found in higher level caches (a.k.a. core caches) and are rarely referenced in the LLC. Thus, they tend to become dead blocks in the LLC despite the fact that they have high locality. Due to the inclusion property, blocks replaced from the LLC must be invalidated from core caches. Evicting these dead blocks from the entire cache hierarchy harms performance by introducing costly offchip misses for hot blocks that makes the inclusive cache perform even more poorly.

## 1.1.1.2 Dead Blocks in GPU caches

Modern graphics processing units (GPUs) include hardware-controlled caches to reduce bandwidth requirements and energy usage [7, 41]. Current GPU cache hierarchies are inefficient for general purpose GPU computing (GPGPU). GPGPU workloads tend to include data structures that would not fit in any reasonably sized caches, leading to low cache hit rates. This problem is exacerbated by the design of GPUs, which share small caches between many threads. Caching these data structures wastes cache capacity and power while evicting useful data that may otherwise fit into the cache. These blocks are *dead-on-arrival* [56] and should not be inserted into GPU caches. Previous CPU LLC-based dead block prediction techniques cannot be directly applied on GPU caches due to their sophisticated mechanisms as well as significant power and storage overhead.

# 1.1.2 Waste of Data Redundancy

Data redundancy is another source of cache waste. In a conventional cache, each block is associated with a requested memory block address and a copy of the data. Cache blocks with different addresses can contain copies of identical data. These *duplicated* blocks waste cache capacity and power because of the storage of redundancy. Previous work exploited specific data redundancy such as zero with compression techniques [31, 2]. This dissertation shows that many blocks in the working set of typical benchmark programs have the same values, far beyond the zerocontent blocks one would expect in any program. As shown in Figure 1.1, eliminating zero-content (null) blocks can save 13% of the cache capacity while eliminating all possible duplication leads to 47.5% of cache blocks removed or invalidated in a 2MB LLC.

#### 1.2 The Solutions

In an inclusive LLC, there are two kinds of dead blocks: blocks that are highly accessed in core caches and blocks that have low temporal locality in both core caches and the LLC. Replacing hot core-cache blocks will hurt performance. The optimized replacement candidates should only be blocks that have low temporal locality in the whole cache hierarchy, whose replacement and back-invalidation will not cause extra

Figure 1.1: Percentage of distinct blocks for null block deduplication and all repeating block deduplication

cache misses; instead, replacing them with other useful blocks as early as possible will increase the cache efficiency and performance. This dissertation proposes Temporalbased Multi-level Correlating (TMC) cache replacement to choose LLC blocks that have low temporal locality in the whole inclusive cache hierarchy as LLC replacement candidates with high accuracy and minimal overhead.

To reduce waste in GPU caches, this dissertation develops a simple dynamic bypass predictor designed for small GPU caches with only hundreds of of bytes of storage overhead. The bypass predictor dynamically predicts if cache blocks are likely to be dead after their first references and bypasses these dead blocks to avoid polluting caches. That is, some blocks are not placed in the GPU cache, but rather bypass the cache and go directly to the consuming functional unit. Instead of increasing power overhead, the proposed GPU cache bypass technique reduces the power consumption of the baseline. Beside reducing the energy cost, the proposed bypass predictor improves GPU performance.

Data deduplication is a specific compression technique that has been widely used

in disk-based storage systems [27, 111]. With data deduplication, only a single instance of identical data is physically stored. The redundant data is stored as references to the corresponding data in a deduplicated data storage to improve storage utilization. Although commonly used in disk storage and proposed for main memory compression, data deduplication is a challenge in on-chip caches with limited overhead due to several design concerns. This dissertation proposes a practical cache deduplication technique to exploit block-level data redundancy dynamically to increase the effectiveness of the cache with limited area and power consumption.

#### 1.3 Thesis Statement

The performance and efficiency of modern processors can be improved by reducing waste in memory hierarchies.

## 1.4 Contributions

This dissertation makes the following original contributions:

- This dissertation introduces Temporal-based Multi-level Correlating (TMC) cache management for inclusive caches to reduce waste of dead blocks. TMC chooses blocks that will not be re-referenced in all cache levels as LLC replacement candidates. TMC samples LLC cache access patterns and correlates them with temporal locality knowledge passively acquired from higher level caches to choose temporal-aware LLC replacement candidates, providing performance improvement while consuming minimal overhead.

- This dissertation proposes a simple and effective GPU cache bypass predictor prevents streaming one-time-use values from being needlessly inserted into the cache. The predictor has high accuracy and minimal area overhead. It demonstrates performance gains and energy savings when using the proposed bypass

techinque for a GPU L1 data cache. This dissertation studies limitations of current GPU cache design and the effects of a bypass predictor as they relate to using scratchpad memories.

• This dissertation quantifies the waste causes by data duplication and finds that widespread duplication exists in caches. It proposes a unified cache deduplication technique to increase effective cache capacity with limited area and power consumption. The deduplicated last-level cache improves performance without increasing physical area consumption.

#### 2. BACKGROUND AND RELATED WORK

This dissertation proposes techniques to reduce waste of dead blocks and data redundancy in diverse types of memory hierarchies to improve efficiency and performance. To provide context for our research, we first give background and brief description of related work.

## 2.1 Dead Block Prediction

Cache blocks are *dead* from the last reference until they are evicted [64]. Storing dead block in caches waste capacity without improving performance. Replacing dead blocks as soon as possible with live blocks improves cache efficiency. Dead Block Prediction [64] is a technique that predicts whether cache blocks are likely to be dead after certain references and drives optimization techniques to improve performance.

Previous work introduces several dead block prediction techniques [64, 74, 55, 44, 1]. Lai *et al.* proposed a trace-based dead block predictor to drive prefetching. This predictor collects sequences (*i.e.* traces) of memory instructions that access the same block. The intuition is that if a trace leads to the last access for one block, then the same trace will lead to the last access for other blocks. Trace-based dead block predictor is also used to drive a cache coherence protocol optimization [25, 101] and dynamic self-invalidation [65]. Khan *et al.* proposed a skewed trace-based dead block predictor and utilized dead blocks as a "virtual victim cache" to store LRU victims from hot sets for future reuse [55].

Counter-based dead block predictor uses both memory addresses and memory instructions to record counters of cache access events and make dead block predictions [58]. The Live-time Predictor (LvP) tracks the number of accesses to each cache block. The Access Interval Predictor (AIP) tracks the access interval of each cache block. The counter-based dead block predictor uses dead blocks as replacement candidates, to replace dead blocks as early as possible for useful blocks.

A time-based predictor [44] was proposed to record the number of cycles a block is alive and predict a block to be dead if it is not accessed for twice of the number of cycles. This predictor is used for L1 cache prefetching and filtering a victim cache.

The cache burst predictor [74] proposes to make dead block prediction and update the prediction table on cache bursts rather than on all cache accesses. A cache burst consists of all the contiguous accesses to a block in the MRU position. The work yields little advantage for lower level caches since most bursts are filtered out by the core cache.

#### 2.2 Improving Inclusive Cache Hierarchies

Inclusive caches have been widely used in chip multiprocessors (CMPs) to simplify cache coherence. However, they have poor performance compared with non-inclusive caches and exclusive caches. Previous work introduced several techniques to improve the performance of inclusive cache hierarchies.

Global Replacement Policy [113] was designed to use one unified replacement policy to control the replacement of cache blocks in all caches of an inclusive cache hierarchy. This proposal was only evaluated with single-threaded workloads and the results showed the global replacement policy sometimes performed worse than the corresponding local replacement policy. Grade *et al.* [35] analyzed the performance of Global Replacement Policy by deconstructing the policy with reuse-distance analysis and evaluated it in a multi-core inclusive cache hierarchy to show that the performance with global replacement policy was actually limited. Zahran *et al.* [114] proposed to make global cache placement decision based on access patterns of dierent blocks. This technique is not designed for inclusive caches because it violates the inclusion property by placing some blocks only into higher level caches but not the LLC. It can be treated as a non-inclusive cache managed by a global placement policy to achieve the capacity of an exclusive cache.

Temporal Locality Aware (TLA) [47] inclusive cache management policy suite was designed to improve the performance of inclusive caches by reducing the frequency of invalidation of inclusion victims that have high temporal locality in core caches. Successful TLA policies can identify cache blocks that have high temporal locality in core caches and avoid evicting these blocks from the LLC. It consists of three policies: Temporal Locality Hints (TLH), Early Core Invalidation (ECI), and Query Based Selection (QBS). TLA policies can only identify a limited number of highly reference blocks in core caches. Moreover, even the replace candidates in the LLC do not have high temporal locality in core caches, they may still be live blocks in the LLC whose invalidation will also hurt the cache performance by incurring hundreds of cycles of memory access penalty.

Gaur *et al.* [36] proposed a bypass and insertion algorithms for exclusive last-level caches in the LLC to improve the cache performance, but it was only designed for exclusive caches.

# 2.3 Improving GPU Private Caches

Graphics Processing Units (GPUs) provide tremendous throughput and high performance computing. Recently, GPUs have been used for general purpose computing. To support this effort, programming models such as CUDA [84] and OpenCL [39] have been developed for easier programming; hardware support such as memory hierarchies has been implemented in GPU cores. Recent work introduced several techniques to improve GPU memory hierarchy. Compiler-controlled scratchpad memories [61, 54, 9] were proposed to improve the efficiency of scratchpad memories. Knight *et al.* proposed an optimizing compiler for architectures with software-managed memory hierarchies [61] to explicitly manage scratchpad memories. Kandemir *et al.* proposed a compiler-controlled dynamic on-chip scratchpad memory management technique for real-time embedded systems.

Jia *et al.* proposed a Memory Request Prioritization Buffer (MRPB) to improve GPU performance [50]. MRPB also employs cache bypassing to mitigate intra-warp contention. Instead of distinguishing reused blocks from significant amount of zeroreuse blocks, MRPB blindly and aggressively bypasses memory requests when there are resource limits, which can cause performance degradation, as stated in [50]. To evaluate MRPB in terms of programmability, Jia *et al.* created an "unshared" version of some Rodinia benchmarks that used scratchpad memory by simply using global memory instead. Simply replacing *\_local\_* functions with *\_global\_* ones will cause significant degradation of performance and lead to biased comparison.

Rogers *et al.* proposed Cache-Conscious Wavefront Scheduling (CCWS) to improve GPU cache efficiency by avoiding data thrashing that causes cache pollution [92]. CCWS restricts the number of wavefronts that are able to access the caches by changing the scheduler to schedule a limited number of wavefronts, which adversely affects the ability of hiding high memory access latency of GPUs.

Lee and Kim proposed a thread-level-parallelism-aware cache management policy to improve performance of the shared last level cache (LLC) in heterogeneous multicore architecture [67]. They focus on shared LLCs that are dynamically partitioned between CPUs and GPUs. Mekkat *et al.* proposed a similar idea for heterogeneous LLC management [75], to better partition LLC for GPUs and CPUs in a heterogeneous system.

## 2.4 Eliminating Data Redundancy

Data redundancy widely exists in storage structures. Data deduplication is used in disk-based storage systems to reduce storage consumption [27, 111, 43].

Address Correlation [96] analyzes the phenomenon of data duplication in the L1 cache without giving a feasible implementation. Non Redundant Data Cache [77] proposes a sub-block level cache deduplication technique, which requires value-based data storage overhead and an extra value search on the critical path. Content-Based Block Caching [78] was an inline deduplication technique designed to improve diskbased storage systems. The binary tree structure and the significant storage overhead of the block cache (the storage of all possible LUN/offset pairs per data entry) make it impractical in a cache level. The mergeable cache architecture [13] was proposed to use deduplication in caches by merging cache blocks with similar data. Dusser etal. [30] investigated zero-content data contained in cache blocks and proposed to use an augmented cache to store null blocks to increase effective cache capacity. Since the percentage of zero-content blocks is small on average, the overall performance improvement is small. The HICAMP architecture [21] utilizes memory deduplication to reduce the overhead of copying shared data. Main memory in this architecture is designed as an associative hash table, suffering from underutilization. Moreover, the lookup in overflow area designed for hash collisions is expensive. CATCH [60] was proposed to use cache-content-deduplication in instruction caches. It only works for instruction caches since it does not support modifications in cached data.

Data compression is another technology to eliminate redundant data [118, 103, 15, 107, 59, 95, 102, 93]. We focus on cache compression techniques in particular. Yang *et al.* [110] proposed Frequent Value Compression in first-level caches. By encoding frequent values during the memory accesses into a small number of bits, the capacity of a cache block is potentially increased. Zhang et al. [115] proposed the frequent value cache (FVC) based on the observation of frequent value locality. FVC employs a value-centric approach to hold only frequently accessed values in a compressed form. Instead of using value-based encoding scheme, Alameldeen etal. [3] proposed Frequent Pattern Compression (FPC), a pattern-based compression scheme for L2 caches. By storing common word patterns in a compressed form with certain prefixes, FPC provides comparable compression ratio to more complex schemes. To reduce useless decompression overhead, Alameldeen et al. [2] proposed an adaptive policy to dynamically trade off between the benefit of compression with the cost overhead. Hallnor et al. [40] proposed to use a unified compression scheme to compress and decompress data in the LLC, main memory and memory channels. Although the unified compression scheme eliminates the additional compression and decompression expense required in data transferring between the LLC and the main memory, it cannot avoid compression/decompression overhead incurred with data transferring between different cache levels. Base-Delta-Immediate Compression [87] is another data compression algorithms representing data using a base value and an array of differences. For value or pattern based compression, besides the complex compression and decompression logic and unavoidable decompress latency, another drawback is that most of cache management policies cannot be used efficiently in a compressed cache because of the variation of block sizes.

The V-Way cache [89] proposes to vary the associativity of a cache on a perset basis to increase the effective cache capacity. Zcache [94] proposes to provide higher associativity than the number of physical ways by increasing the number of replacement candidates.

#### 3. PRELIMINARY WORK\*

A last-level cache (LLC) occupies large chip area with significant power requirements. However, LLCs are inefficient because they store dead blocks. On average, 86% of blocks in a 2MB LLC are dead [56], causing low cache efficiency.

Previous work proposes different dead block prediction techniques [26, 74, 55, 44, 1]. These techniques consume significant storage and power overhead due to a large amount of metadata. Moreover, previous dead block prediction techniques cannot be applied to last-level caches effectively due to the fact that the access pattern associated with traces of memory instruction are filtered out by the L1 caches, leaving precious little contextual information.

As preliminary work to the research in this dissertation, we investigated *sampling dead block prediction* technique that uses sampled program counters (PCs) to predict if a LLC block is likely to be dead.\*A sampling dead block predictor keeps track of only metadata of a small number of cache sets and updates the prediction table only on sampler accesses rather than every single cache access.

#### 3.1 Sampling Dead Block Predictor

A sampling dead block predictor keeps a small partial tag array, referred to as a *sampler*. The sampler samples a fews sets from the whole LLC, i.e., a sampler of 32 sampled sets from a LLC of 2,048 sets. Each sampler entry contains only a 15-bit partial tag to conserve area and energy with high enough accuracy. Each access to the LLC incurs an inquiry to the predictor for prediction; while the predictor is only

<sup>\*</sup>Part of this chapter is reprinted with permission from "Sampling Dead Block Prediction for Last-Level Caches" by Samira M. Khan, Yingying Tian, and Daniel A. Jiménez, 2010. Proceedings of the 2010 43rd Annual IEEE/ACM International Symposium on Microarchitecture, IEEE Computer Society Washington, DC, USA. Copyright [2010] by IEEE Computer Society.

updated on accesses to the sampler sets. The intuition behind a sampler is that the learning acquired through sampling generalizes to the entire cache. Furthermore, with the help of sampler, the replacement policy used in the LLC can be different from the one used in the sampler, i.e., less expensive replacement policies such as random and not-recently-used (NRU).

A sampling dead block predictor uses only the PC to index its prediction table, instead of a trace of PCs (a.k.a. refTrace). The PC-based dead block predictor works better than the refTrace predictor for LLCs due to the fact that temporal locality has been filtered by core caches. Thus a reference trace brings more noise rather than useful information compared to simply using the PC of the last memory instruction that accesses to the corresponding block.

Beside the structure of a sampler and PC-based prediction, the third feature of our sampling dead block predictor is the skewed organization [98] of the prediction table to reduce hash collision. The predictor keeps three hash tables, each indexed by a different hash of a 15-bit signature. Each access to the predictor yields three counter values whose sum is used as a confidence compared with a threshold; if the threshold is met, then the corresponding block is predicted dead. With the help of the skewed organization, the effect of destructive conflicts is reduced.

# 3.2 Evaluation

Based on our experiments, a sampling predictor can reduce the number of LLC misses over LRU by 11.7% for memory-intensive single-thread benchmarks and 23% for multi-core workloads. The reduction in misses yields a geometric mean speedup of 5.9% for single-thread benchmarks and a geometric mean normalized weighted speedup of 12.5% for multi-core workloads. Due to the reduced state and number of accesses, the sampling predictor consumes only 3.1% of the of the dynamic power

and 1.2% of the leakage power of a baseline 2MB LLC, comparing favorably with more costly techniques.

# 3.3 Summary

Sampling dead block prediction can improve performance for last-level caches while reducing the power and storage requirements over previous techniques. However, all the proposed dead block prediction techniques, including sampling dead block prediction, are designed for monolithic caches and cannot be applied to specific cache hierarchies, i.e. inclusive cache hierarchies. This dissertation explores characteristics of dead blocks in inclusive cache hierarchies and proposes temporalbased multilevel correlating cache management technique for inclusive LLC in the next chapter.

# 4. REDUCING WASTE OF DEAD BLOCKS IN INCLUSIVE CACHE HIERARCHIES\*

Inclusive cache hierarchies have been widely used in Chip Multiprocessors (CMPs) because of the simplicity in maintaining cache coherence [10, 20]. However, compared to exclusive [53] or non-inclusive [112, 117] cache hierarchies, inclusive cache hierarchies have limited performance due to the inclusion property that all the cache blocks in higher level caches (a.k.a. core caches) must be a subset of the shared last-level cache (LLC). When the sum of the sizes of all core caches is comparable to the size of the LLC, overall capacity of the inclusive cache hierarchy becomes limited compared to exclusive and non-inclusive caches and the performance becomes poor. Moreover, when cache blocks in the inclusive LLC are replaced, they must also be invalidated from all higher level caches to maintain inclusion. Due to the fact that temporal locality is hidden by higher level caches, hot blocks that are highly referenced in higher level caches are rarely accessed in the LLC and therefore become LLC replacement victims and are invalidated from the entire cache hierarchy, eventually causing cache misses and incurring hundreds of cycles of memory access penalties.\*

## 4.1 Motivation

To bridge the performance gap between non-inclusive and inclusive caches, one naive solution would be increase the size of the inclusive LLC. However, the chip area occupied by caches is already more than half of the overall chip area [105, 63, 94], which contributes to significant power consumption. Simply increasing cache sizes

<sup>\*</sup>Part of this chapter is reprinted with permission from "Temporal-based Multilevel Correlating Inclusive Cache Replacement" by Yingying Tian, Samira M. Khan, and Daniel A. Jiménez, 2013. ACM Transactions on Architecture and Code Optimization (TACO), ACM, New York, NY, USA. Copyright [2013] by ACM.

will not help performance improvement.

Another way to improve inclusive caches is to intelligently choose LLC replacement candidates that have low temporal locality in higher level caches. Backinvalidation of these blocks will not cause performance loss. Previous work [47] identified blocks that have high temporal locality in higher level caches and reduced the frequency of back-invalidating them, making performance of inclusive cache hierarchies similar to that of non-inclusive caches. However, blocks that have poor temporal locality in higher level caches may still have temporal locality in the LLC and the replacement of these blocks will still hurt the overall performance. If a block will not be referenced in either higher level caches or the LLC<sup>1</sup>, replacement and consequent back-invalidation of this block will not hurt performance. In fact, cache performance can be improved by replacing these known replaceable blocks with others deemed more useful. Thus, inclusive caches are capable to outperform non-inclusive caches.

This dissertation categorizes LLC blocks into three exclusive groups based on their temporal characteristics in both higher level caches and the LLC:

- *HAH blocks*: blocks that are highly referenced in higher level caches;

- *HAL blocks*: blocks that are highly referenced in the LLC;

- *LAL blocks*: blocks that have low temporal locality in both higher level caches and the LLC, which should be the group of LLC replacement candidates.

The LLC replacement candidates chosen from LAL blocks will not hurt inclusive cache performance. By contrast, replacing these blocks with useful ones as early as possible helps improve cache efficiency.

<sup>&</sup>lt;sup>1</sup>At the time an invalidated block is requested again, if it is still kept in a corresponding cache of a non-inclusive cache hierarchy with the same replacement policy, it is treated as being re-referenced before its eviction; otherwise, it will not be referenced until its eviction.

Figure 4.1 shows the average percentages of different categories of blocks that are back-invalidated due to LRU replacement in the LLC. On average, 72.51% of the back-invalidated blocks are referenced again before their eviction in corresponding sets of a non-inclusive L1 cache. These blocks are HAH blocks and should not be invalidated from the cache hierarchy. There are 15.82% of blocks not hit in the L1 cache but re-referenced in the LLC before being replaced from the LLC. These blocks are HAL blocks that have temporal locality in the LLC and should not be invalidated from whole cache hierarchy, either. The remaining 11.67% of back-invalidated blocks are not re-referenced until they are evicted from the LLC in a corresponding noninclusive cache hierarchy. These blocks are LAL blocks and replacement of these blocks is harmless to the performance of inclusive caches, so they should be chosen as LLC replacement victims whenever possible.

Figure 4.1: Percentage of different categories of back-invalidated blocks due to LLC LRU replacement

#### 4.2 Temporal-based Multi-level Correlating Cache Replacement

This dissertation proposes Temporal-based Multi-level Correlating (TMC) cache replacement to choose LLC blocks that have low temporal locality in all caches as inclusive LLC replacement candidates. The technique intelligently categorizes LLC blocks into three exclusive groups using two-level categorization. It first categorizes LLC blocks based on their local temporal locality in the LLC into two groups: HAL and P-LAL (potential LAL blocks). Then it identifies HAH blocks from P-LAL blocks, and replaces the other LAL blocks when needed. It uses a *correlating tempo*ral locality detector (CTL detector) to detect LAL blocks with high accuracy. To first categorize HAL and P-LAL blocks, a CTL detector uses sampled program counters (PCs) to determine when a LLC block is likely to be a P-LAL block. The key intuition behind TMC is that if a memory access instruction PC leads to a P-LAL block, then there is a high probability that the same PC will lead to another P-LAL block. Previous work has found correlations between observed patterns of memory access instructions and cache accesses [25, 24, 101, 66, 55, 56, 108]. As stated in [25], it is because "program behavior is repetitive, e.g., a critical section used a fixed set of instructions to read and modify data". If an instruction is "repeatable and always leads to (and can be associated with) the same event, a predictor can dynamically learn the behavior and accurately predict the event". "Much as path-based predictors [80] predict conditional branches dynamically based on correlating a sequence of basic-block *addresses*", a PC-based predictor predicts an event dynamically based on correlating PCs of memory access intructions. In the LLC, temporal locality is filtered by higher level caches and memory access patterns are roughly consistent across groups of sets. Thus, the learning acquired through sampling a few sets generalizes to the entire LLC [90, 56]. Using sampled PC information to detect P-LAL blocks are accurate

and consumes little. After the first level categorization, the CTL detector detects HAH blocks from the P-LAL group, using temporal information passively acquired from higher level caches. To get temporal information filtered by higher level caches, the naive way is to send this information to the LLC actively on every cache hit in higher level caches. However, the number of cache hit in higher level caches is extremely large and sending that number of requests to the LLC will consume a lot of bandwidth and energy. Therefore, in TMC the temporal locality of higher level caches is passively acquired by the LLC on each LLC miss, which is far less than the number of cache hit in higher level caches.

Compared to previous work, this technique has the following advantages: 1) detecting temporal-aware LLC replacement candidates with high accuracy and minimal storage overhead; 2) correlating multi-level temporal information with minimal communication overhead; 3) self-training at runtime for accurate detection. The design of correlating temporal locality detector and how it works in detail will be discussed in the following sections.

## 4.2.1 Correlating Temporal Locality Detector

A CTL detector consists of a detection table, a decoupled structure storing sampled LLC sets, a detection regulator and a modified invalidation message format. Figure 4.2 gives a block diagram of a CTL detector, showing the structure and related communication.

#### 4.2.1.1 Detection Table

The detection table is a hash table of saturating counters, indexing by a hashed PC. It is accessed on sampled LLC cache accesses, which is descirbed in detail in the following subsection. Each access to the detection table yields a confidence compared with a threshold; as long as the threshold is not reached, blocks accessed by that PC

Figure 4.2: Block diagram of CTL detector

are likely to be HAL blocks, otherwise, blocks are grouped as P-LAL blocks. When an LLC block is referenced, the corresponding PC that accesses this block is hashed to index a detection table to determine its group.

To reduce the impact of conflicts in the table, The detection table uses the skewed organization [99, 76] of three tables. Each access to the detection table yields three values of counters that are summed up to compare with an threshold. In our experiments, the detection table has three 4,096-entry tables of 2-bit saturating counters, each indexed by a different hash function of a 15-bit partial PC. The skewed prediction table consumes a total of 3KB in storage.

# 4.2.1.2 Sampled Access Patterns

To reduce the storage and power overhead, the detection table is only updated on a small fraction of cache accesses referred to as sampled access patterns. The intuition is that memory access patterns are roughly consistent across sets. Thus, the CTL detector keeps track of program behavior by sampling a small number of LLC sets using a decoupled structure containing only partial tags and kept outside the LLC [91]. This structure can be configured differently than the configuration of the LLC to provide improved detection accuracy [56]. For instance, This dissertation finds that for a 16-way set-associative LLC, a reduced associativity of 12 ways provides accurate detection with less state. The LLC is decoupled from the sampled sets and does not require keeping extra PC information to update the detection table. Thus, each cache block in the LLC only holds two extra bits of metadata to store the categorization information, which consumes less than 0.5% of a 2MB LLC, further reducing the storage overhead. The sampled sets are accessed in parallel with the LLC. When an LLC access occurs in a sampled set, the CTL detector hashes the PC that accessed this block to index the detection table and update the corresponding saturating counter. Accesses to blocks whose sets are not in the sampled sets will not update the detection table. In on our experiments, the sampled sets contain only 64 sets of tags, randomly selected from the LLC. Each sampled set has 12 entries consisting of 15-bit partial tags, 15-bit partial PCs, and other metadata used for CTL detection, consuming 3.375KB of total storage overhead. Compared to accessing the detection table on each LLC access, the number of accesses to the detection table is reduced by more than 95%. Note that more sampled sets slightly slightly improves the detection accuracy while too many sets can increase destructive interference in the detection tables. Since power overhead is a serious issue in cache design, this dissertation chooses to slightly sacrifice the performance improvement for far less power consumption.

## 4.2.1.3 Modified Invalidation Message Format

The P-LAL group consists of HAH blocks and LAL blocks. In the second level categorization, a CTL detector randomly back-invalidates P-LAL blocks before replacing them from the LLC. The intuition is this: if the block is a HAH block, it will be requested soon by higher level caches; otherwise, it is a LAL block and can be replaced. To invalidate blocks from higher level caches, this dissertation simply modifies the format of invalidation message instead of changing default inclusion protocol.

In a conventional inclusive cache hierarchy, on each LLC miss, the LLC sends an invalidation message to all higher level caches with the physical address of the replacement victim. If the block is present in any caches, it is invalidated from those caches. Instead of generating extra messages, this work modifies the format of the invalidation message with extra physical address fields. On each LLC miss, the CTL detector sends one invalidation message encapsulating the physical address of a replacement victim together with N physical addresses of P-LAL blocks. There is no extra control message involved. The value of N is related to traffic overhead. Although the inclusion protocol is unchanged, the throughput of on-chip network is increased by N. A large N will also invalidate more higher level cache blocks and may cause unnecessary cache misses. Based on our experiments, N = 1 is sufficient for accurate detection as well as minimal communication overhead. Higher level caches de-encapsulate the invalidation message and invalidate blocks with addresses stored in the message. Higher level caches do not send any acknowledgment or temporal information to the LLC. Temporal locality information is passively acquired by the LLC with subsequent LLC accesses.

# 4.2.1.4 Detection Regulator

A detection regulator is used to regulate previous P-LAL detection. If the block is a HAH block, it will be requested soon by higher level caches and a LLC hit will occur. The detection regulator therefore gets the hint that the block should be kept in the higher level cache(s). Thus, the previous P-LAL is remarked as a HAH block, and its replacement state is updated. If the tag of block is located in the sampled sets, the corresponding counters in the detection table are also updated. If the block is not requested after certain cycles, it is treated as harmless for replacement. The detection regulator then marks the block as a LAL block and reinforces previous detection if the block is in the sampled set. The number of cycles the regulator waits before tagging LAL blocks is related to the accuracy of detection. If it waits longer, there is a higher probability of making a more accurate detection. However, it also delays the procedure of grouping blocks. Based on our experiments, waiting until another LLC miss occurs is sufficient to make accurate and timely decisions.

# 4.2.2 How Does TMC Work?

This section describes the TMC algorithm in detail.

On each LLC cache access, the technique first checks whether the set of the requested block is in the sampled sets. If so, the sampled tag array is accessed in parallel with the LLC; otherwise, only the LLC is accessed. On an access to a sampled set, if the tag is in the set, it is a sampled hit, the partial PC stored in the corresponding tag entry is used to index to the detection table, and the counter of the detection table entry is decremented by one, indicating the stored PC is likely to lead to a HAL block. The stored partial PC is updated to the PC that currently requests the block. The corresponding replacement status is updated, e.g., the accessed block is move to MRU according to LRU replacement policy. The categorization of the current block is decided by the detection table with the stored PC and comparing the corresponding counter with the threshold; if the threshold is not reached, the current block is marked as a HAL block; or it is marked as a P-LAL block. If the accessed block is not in the sampled set, it is a sampled miss, a replacement candidate is needed. If there is a LAL block marked in the sampled set, it is the

replacement victim; if there is no LAL block in current set, a P-LAL block is chosen; if there is neither LAL nor P-LAL block, a normal LRU block is replaced. The partial PC stored in the replacement victim entry is indexed into the detection table, the corresponding counter in the detection table entry is incremented by one, indicating that the stored PC is likely to lead to a P-LAL block. Then the partial tag, partial PC, and replacement status are updated. Finally, the group of the block is updated by hashing the partial PC into the detection table and comparing the corresponding counter with the threshold.

The LLC is accessed in parallel with the sampled sets. On LLC hit, the PC of the memory instruction that accesses this block is indexed into the detection table to determine the categorization of the accessed block. Replacement status and other metadata are also updated. On LLC miss, a LAL block is chosen for replacement. If there is no LAL block, a P-LAL is chosen; if there is no P-LAL block, the LRU block is replaced. The corresponding metadata of the incoming block is updated and the categorization of the coming block is made by indexing the PC that caused the LLC miss into the detection table and comparing the counter with the threshold. Note that with TMC, the LLC may use a less costly replacement policies (e.g., notrecently-used replacement, random replacement, etc.) to further reduced storage overhead because the sampled sets are decoupled from the LLC and the detection table is updated only with sampled information. To fairly evaluate our technique, this work conservatively uses the LRU replacement policy in our experiments to maintain consistency with other techniques.

To maintain inclusion, the address of the replacement victim is sent back to all higher level caches for invalidation. Besides the address of the replaced block, the address of a P-LAL block (if there are P-LAL blocks marked, as shown in Figure 4.3(a)) is encapsulated into the back-invalidation message packet too for temporal hints from higher level caches. Both the replaced block and the selected P-LAL block is invalidated from all higher level caches if presented (Figure 4.3(b)). It is to detect HAH blocks from consequent behaviors of higher level caches according to the intuition: if the block is a HAH block, it will be requested soon by higher level caches (Figure 4.3(c)); otherwise, it will not be requested until being evicted. If the block is re-referenced before next LLC miss occurs, it is a LLC hit to a P-LAL block. Replacement status of this block is updated, indicating it keeps temporal locality, and this block is marked as HAH instead of P-LAL. If the set where this block locates is sampled, the corresponding counter in the detection table is also updated. If the back-invalidated P-LAL block is not referenced until another LLC miss occurs, it is marked as a LAL block and can be replaced.

Figure 4.4 shows the two level detection of the categories of LLC blocks. HAL blocks should be kept in the LLC and HAH blocks should be kept in the corresponding higher level caches; LAL blocks can be replaced from the LLC and invalidated from the whole inclusive cache hierarchy without causing performance loss.

Figure 4.3: Detect HAH blocks from P-LAL blocks

Figure 4.4: Two-level detection of LLC block categorization

# 4.2.3 Comparison with Previous Work

This section compares TMC with previous inclusive cache management techniques.

# 4.2.3.1 Temporal Locality Aware (TLA) Policy Suite

The Temporal Locality Aware (TLA) policy suite [47] was proposed to improve inclusive cache performance. It consists of three policies: Temporal Locality Hints (TLH), Early Core Invalidation (ECI) and Query Based Selection (QBS). As claimed in [47], TLH is only a limit study; ECI is a lower traffic solution with limited performance; QBS performs best among three TLA policies, achieving similar performance to a non-inclusive cache. The goal of TLA is to identify hot blocks in higher level caches (a.k.a. HAH blocks according to our definition) and avoid replacing these blocks from the LLC. Although the replacement victims chosen by TLA are not highly accessed in higher level caches, there is a chance that they will be re-referenced in the LLC (a.k.a. HAL blocks in our definition). Compared to TLA, TMC identifies hot blocks in higher level caches and also hot blocks in the LLC, and avoids replacing these blocks from the LLC. Cache efficiency is further improved by bringing useful blocks into the cache as early as possible. Therefore, instead of achieving similar performance, TMC actually outperforms non-inclusive caches significantly with low overhead.

Compared to QBS, the best management policy of TLA suite, TMC has not only better performance improvement, but also lower communication overhead. On each LLC replacement, QBS chooses a block and queries to see if it is present in any core caches. If the block is located in some core caches, QBS has to find another block in the LLC and repeats the query procedure again until it finds a block absent in all core caches to replace. If the number of queries is unlimited, up to 1.5KB of data is transferred on-chip on each LLC miss in a dual-core CMP, compared to 32 bytes per LLC miss with TMC. The query number of QBS is limited, as stated in [47], as at least two queries per LLC miss is required to achieve acceptable performance, the on-chip communication overhead is still six times more than that of TMC.

Compared to TLA suite, TMC requires extra PC information sent to the LLC. Sending this extra information to the LLC has been proposed by much previous work [25, 24, 101, 66, 55, 56, 108]. TMC has higher storage overhead, but it is as low as less than 1% of the capacity of the LLC in a dual-core CMP. TMC has lower communication overhead compared to QBS. TMC outperforms ECI and QBS by 10.7% and 8.6% respectively.

#### 4.2.3.2 Sampling Dead Block Prediction

We also compare this work with our preliminary work: Sampling Dead Block Prediction (SDBP) [56]. SDBP is designed to identify dead blocks in the LLC and replace them with live blocks as early as possible to improve cache efficiency. Compared to other dead block prediction techniques, SDBP uses far less overhead to make predictions with much higher accuracy. However, since SDBP has no awareness of temporal locality in core caches, predictions are made based on local information of LLC accesses. Therefore the predicted dead block in the LLC can be highly referenced blocks in core caches and the replacement of these blocks will cause costly off-chip cache misses that hurt the inclusive cache performance.

We compare our work with SDBP from performance to overhead. Based on our experiments, TMC achieves an average performance improvement of 5.2% over SDBP in an inclusive cache hierarchy. Moreover, TMC performs comparable to an enhanced non-inclusive cache with SDBP, which utilizes SDBP in a non-inclusive cache. The storage overhead of TMC is 4KB compared to SDBP and the on-chip communication overhead is 32 bytes on each LLC miss.

The performance comparison will be shown in detail in Section 4.4.

#### 4.3 Experimental Methodology

This section outlines the experimental methodology used in this study.

#### 4.3.1 Simulation Environment

We use the MARSSx86 cycle-accurate simulator, a full system simulation of the x86-64 architecture. We use the multi-core implementations [86] with extensive enhancements for improved simulation accuracy and performance. It detailed models an out-of-order 4-wide 5-stage pipeline with a 128-entry reorder buffer, coherent

caches with MESI protocol as well as on-chip interconnections. We modified the simulator to collect instructions-per-cycle (IPC) figures as well as cache misses.

The micro-architectural parameters closely model Intel Core i7 [16] with the following parameters (the same as in [47]): Three level cache hierarchy, L1, L2 and a shared LLC. The L1 and L2 caches are private in each core. The L1 I-cache and D-cache are 4-way 32KB each and the L2 cache is unified 8-way 256KB. As in the Intel Core i7, inclusion is not enforced between private L1 and L2 caches. The shared LLC is a unified 2MB cache for dual-core CMP and 2MB per core for 4-core CMP and 8-core CMP. We simulate a dual-core CMP with 2MB LLC to compare with previous work [47] that ran experiments under this configuration. However, the configuration of 2MB per core LLC is more realistic in current industrial design. The block size of all caches in the hierarchy is 64 bytes. The access latencies for the L1, L2, LLC, and main memory are 1, 10, 24, and 250 cycles, respectively. The default replacement policy of each cache is the LRU replacement policy.

In TMC, there are 64 sampled sets of tags, evenly chosen from among the sets of the LLC. Note that, for 2MB, 4MB, 8MB and 16MB caches, the number of sampled sets is constant, i.e., the storage overhead of sampled sets does *not* increase with core count. Each sampled set contains 12 entries consisting of a 15-bit partial tag, a 15-bit partial PC, and 2 bits of categorization. The detection table consists of three 4,096-entry tables of 2-bit saturating counters, also regardless of core count. For each LLC block, we store an additional 2 bits of categorization for TMC. Note that TMC does not make any prediction for prefetched blocks. Prefetched blocks are inserted and replaced using default LRU replacement policy. For QBS, it requires a control mechanism to maintain information about the presence of a queried block in all higher level caches.

### 4.3.2 Benchmarks

We use the SPEC CPU 2006 benchmark suite [42]. Each benchmark is compiled for the x86-64 instruction set. Note that not all the workloads will hurt inclusive cache performance. Based on our experiments, some workloads running with an inclusive LLC perform similar to a non-inclusive LLC. We classify workloads into two categories: inclusion-sensitive and inclusion-insensitive workloads. To evaluate whether a certain technique can help improve the performance of both categories of workloads, we run sixteen dual-core workloads, eight of them are inclusionsensitive (The selection criteria is that the performance gap between the inclusive cache and the non-inclusive cache is larger than 3%.) and the other eight workloads are inclusion-insensitive (The performance gap is smaller than 3%). We also randomly selected five 4-core workloads whose average performance gap is 1.7%, and five 8-core workloads with an average performance gap of 1.2%, to evaluate the scalability of all techniques. In each workload, benchmarks run simultaneously, restarting after one billion instructions until another two billion instructions (four billion instructions for 8-core workloads) are totally executed. Table 4.1, 4.2, 4.3 and 4.4 show the workload mixes we use in the experiments respectively. We also simulated ECI, QBS and SDBP in both the inclusive hierarchy and the non-inclusive hierarchy for comparison.

### 4.4 Evaluation

This section discusses the results of our experiments. In the graphs below, several techniques are referred as abbreviation. Table 4.5 gives a legend for them. The *Inclusive Cache* stands for the baseline.

| Name   | Benchmarks      |

|--------|-----------------|

| mix-00 | perlbench, mcf  |

| mix-01 | mcf, calculix   |

| mix-02 | hmmer, mcf      |

| mix-03 | gromacs, mcf    |

| mix-04 | gobmk, mcf      |

| mix-05 | gobmk, GemsFDTD |

| mix-06 | gamess, sphinx3 |

| mix-07 | namd, xalancbmk |

Table 4.1: Inclusion-sensitive dual-core workloads

| Name   | Benchmarks            |

|--------|-----------------------|

| mix-00 | calculix, GemsTDTD    |

| mix-01 | astar, tonto          |

| mix-02 | gcc, mcf              |

| mix-03 | gobmk, soplex         |

| mix-04 | sphinx3, milc         |

| mix-05 | perlbench, libquantum |

| mix-06 | bzip2, hmmer          |

| mix-07 | gromacs, h264ref      |

Table 4.2: Inclusion-insensitive dual-core workloads

| Name   | Benchmarks                         |

|--------|------------------------------------|

| mix-00 | GemsFDTD, h264ref, tonto, lbm      |

| mix-01 | gobmk, sphinx3, xalancbmk, mcf     |

| mix-02 | namd, bzip2, gcc, mcf              |

| mix-03 | perlbench, gcc, namd, zeusmp       |

| mix-04 | sphinx3, gamess, zeusmp, perlbench |

Table 4.3: 4-core workloads

| Name   | Benchmarks                                                               |

|--------|--------------------------------------------------------------------------|

| mix-00 | xalancbmk, tonto, mcf, sphinx3, libquantum, namd, gobmk, soplex          |

| mix-01 | perlbench, h264ref, gcc, hmmer, libquantum, soplex, calculix, GemsFDTD   |

| mix-02 | zeusmp, calculix, namd, gromacs, xalancbmk, bwaves, gamess, sphinx3      |

| mix-03 | omnetpp, h264ref, libquantum, gcc, hmmer, GemsFDTD, calculix, soplex     |

| mix-04 | astar, soplex, xalancbmk, GemsFDTD, h264ref, calculix, libquantum, hmmer |

Table 4.4: 8-core workloads

| Name               | Technique                                                                    |

|--------------------|------------------------------------------------------------------------------|

| Inclusive Cache    | Inclusive Baseline with default LRU policy in each cache                     |

| ECI                | Early Core Invalidation cache management policy in an inclusive LLC          |

| QBS                | Query Based Selection cache management policy in an inclusive LLC            |

| Inclusive SDBP     | Dead block replacement with SDBP in an inclusive LLC                         |

| TMC                | Temporal-based Multi-level Correlating cache replacement in an inclusive LLC |