# LOW POWER HIGH EFFICIENCY INTEGRATED CLASS-D AMPLIFIER CIRCUITS FOR MOBILE DEVICES

## A Dissertation

by

## ADRIAN ISRAEL COLLI-MENCHI

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

Chair of Committee, Edgar Sánchez-Sinencio

Committee Members, Samuel Palermo

Hamid Toliyat

Zenón Medina-Cetina

Head of Department, Chanan Singh

May 2015

Major Subject: Electrical Engineering

Copyright 2015 Adrian Israel Colli-Menchi

#### ABSTRACT

The consumer's demand for state-of-the-art multimedia devices such as smart phones and tablet computers has forced manufacturers to provide more system features to compete for a larger portion of the market share. The added features increase the power consumption and heat dissipation of integrated circuits, depleting the battery charge faster. Therefore, low-power high-efficiency circuits, such as the class-D audio amplifier, are needed to reduce heat dissipation and extend battery life in mobile devices. This dissertation focuses on new design techniques to create high performance class-D audio amplifiers that have low power consumption and occupy less space.

The first part of this dissertation introduces the research motivation and fundamentals of audio amplification. The loudspeaker's operation and main audio performance metrics are examined to explain the limitations in the amplification process. Moreover, the operating principle and design procedure of the main class-D amplifier architectures are reviewed to provide the performance tradeoffs involved.

The second part of this dissertation presents two new circuit designs to improve the audio performance, power consumption, and efficiency of standard class-D audio amplifiers. The first work proposes a feed-forward power-supply noise cancellation technique for single-ended class-D amplifier architectures to improve the power-supply rejection ratio across the entire audio frequency range. The design methodology, implementation, and tradeoffs of the proposed technique are clearly delineated to demonstrate its simplicity and effectiveness. The second work introduces a new class-D output stage design for piezoelectric speakers. The proposed design uses stacked-cascode thick-oxide CMOS transistors at the output stage that makes possible to handle high voltages in a low voltage standard CMOS technology. The design tradeoffs in efficiency, linearity, and electromag-

netic interference are discussed.

Finally, the open problems in audio amplification for mobile devices are discussed to delineate the possible future work to improve the performance of class-D amplifiers. For all the presented works, proof-of-concept prototypes are fabricated, and the measured results are used to verify the correct operation of the proposed solutions.

# DEDICATION

To God and to my family.

#### **ACKNOWLEDGEMENTS**

First and foremost, I would like to thank God for all the blessings that He has bestowed upon me. Without His grace, I would have been lost.

"The Lord is my rock, my fortress, and my deliverer, my God, my rock in whom I take refuge, my shield, and the horn of my salvation, my stronghold." (Psalm 18:2)

I would like to thank my advisor, Dr. Edgar Sánchez-Sinencio, for his invaluable support and motivation throughout the development of this research. I am grateful for his academic guidance, professional advisement, and friendship.

I would like to thank my committee members, Dr. Samuel Palermo, Dr. Hamid Toliyat, and Dr. Zenón Medina-Cetina for all their comments and suggestions to improve the quality of the research presented in this dissertation.

I would like to express my sincere gratitude to my wife, Liliana, for her unconditional love, support, encouragement, and patience. Many thanks to my parents, Jose and Ana, for their constant support and motivation. I am also grateful to my little sister Monica, for her love and comprehension.

I would like present my deep appreciation to Miguel Rojas-Gonzalez and Joselyn Torres for the numerous technical discussions that helped to develop this research work. Thanks also to my research colleagues Jorge Zarate, Salvador Carreon, Efrain Gaxiola, Jiayi Jin, Xiaosen Liu, Fernando Lavalle, and Carlos Briseno.

Finally, thanks to the National Council of Science and Technology (CONACYT) of Mexico for the economic support throughout most of my doctoral studies.

#### **NOMENCLATURE**

BTL Bridge Tied Load

CDA Class-D Amplifier

CMOS Complementary Metal Oxide Semiconductor

DMOS Double-Diffused Metal Oxide Semiconductor

DEMOS Drain Extended Metal Oxide Semiconductor

EM Electromagnetic

EMI Electromagnetic Interference

GBW Gain Bandwidth Product

IMD Intermodulation Distortion

LDMOS Laterally Diffused Metal Oxide Semiconductor

NMOS Negative Channel Metal Oxide Semiconductor

PCB Printed Circuit Board

PFM Pulse Frequency Modulation

PMOS Positive Channel Metal Oxide Semiconductor

PSRR Power Supply Rejection Ratio

PWM Pulse Width Modulation

PZ Piezoelectric

RMS Root Mean Square

SNR Signal to Noise Ratio

SMC Sliding Mode Control

SPL Sound Pressure Level

THD Total Harmonic Distortion

THN+N Total Harmonic Distortion plus Noise

# TABLE OF CONTENTS

| P                                                                                  | age            |

|------------------------------------------------------------------------------------|----------------|

| BSTRACT                                                                            | ii             |

| EDICATION                                                                          | iv             |

| CKNOWLEDGEMENTS                                                                    | V              |

| OMENCLATURE                                                                        | vi             |

| ABLE OF CONTENTS                                                                   | vii            |

| IST OF FIGURES                                                                     | X              |

| IST OF TABLES                                                                      | viii           |

| INTRODUCTION                                                                       | 1              |

|                                                                                    |                |

| 1.1 Motivation          1.2 Research impact          1.3 Dissertation organization | 1<br>2<br>3    |

| FUNDAMENTALS AND METRICS OF AUDIO AMPLIFICATION                                    | 6              |

|                                                                                    |                |

| 2.1 Principles of sound and audio                                                  | 6<br>6<br>8    |

| 2.2 Loudspeaker transducers in mobile devices                                      | 9<br>10        |

| 2.2.2 Piezoelectric speaker                                                        | 12<br>14       |

| 2.3.1 Total harmonic distortion plus noise                                         | 15<br>17       |

| 2.3.3 Power supply rejection ratio                                                 | 18<br>20<br>21 |

| 2.4 Audio amplifier classification                                                 | 25             |

| PRINCIPLES OF CLASS-D AUDIO AMPLIFIERS                                             | 30             |

|    |      |                                                                    | Page |

|----|------|--------------------------------------------------------------------|------|

|    | 3.1  | Class-D amplification                                              | 30   |

|    |      | 3.1.1 Advantages and disadvantages of class-D amplifiers           |      |

|    |      | 3.1.2 Class-D amplifier power losses                               |      |

|    |      | 3.1.2 Class-D amplified power losses                               |      |

|    |      | 3.1.4 Commercial class-D audio amplifiers typical specifications   |      |

|    | 3.2  | Close loop class-D architectures                                   | 40   |

|    | 3.2  | 3.2.1 Pulse width modulation                                       | 44   |

|    |      | 3.2.2 Sigma-delta modulation                                       | 53   |

|    |      | 3.2.3 Self-oscillating modulation                                  |      |

|    |      | 3.2.4 Modulation architecture comparison                           |      |

|    | 3.3  | Class-D design implementation tradeoffs                            |      |

|    | 3.3  | 3.3.1 Compensator amplifier                                        |      |

|    |      | 3.3.2 Pulse-width modulator                                        |      |

|    |      | 3.3.3 Class-D output stage                                         |      |

|    |      | 3.3.4 Output filter                                                | 97   |

|    |      | 3.3.5 Current and voltage sensor techniques                        | 99   |

|    |      | 3.3.5 Current and voltage sensor techniques                        | 25   |

| 4. | A FI | EED FORWARD POWER SUPPLY NOISE CANCELLATION                        |      |

|    | TEC  | CHNIQUE FOR CLASS-D AMPLIFIERS                                     | 106  |

|    | 4.1  | Power-supply noise problem in class-D audio amplifiers             | 106  |

|    | 4.2  | Power-supply noise modeling in class-D audio amplifiers            |      |

|    | 1.2  | 4.2.1 Single-ended load                                            |      |

|    |      | 4.2.2 Bridge-tied load                                             |      |

|    | 4.3  | Proposed feed-forward power-supply noise cancellation technique    |      |

|    | 1.5  | 4.3.1 Proposed FFPSNC technique description                        |      |

|    |      | 4.3.2 Class-D with FFPSNC technique circuit implementation         |      |

|    | 4.4  | Proposed technique tradeoffs and methodology                       |      |

|    | 1. 1 | 4.4.1 FFPSNC technique implementation tradeoffs                    |      |

|    |      | 4.4.2 FFPSNC technique design procedure                            |      |

|    | 4.5  | Simulation results of proposed FFPSNC technique                    |      |

|    | 4.6  | Experimental results of CDA with FFPSNC technique                  |      |

|    | 4.7  | Conclusion                                                         |      |

|    | 4.7  | Conclusion                                                         | 140  |

| 5. | A H  | IGH-EFFICIENCY SELF-OSCILLATING CLASS-D                            |      |

|    | AMI  | PLIFIER FOR PIEZOELECTRIC SPEAKERS                                 | 147  |

|    | 5.1  | Background in audio amplifiers for PZ speakers                     | 147  |

|    | 5.2  | Class-D amplifier design considerations for piezoelectric speakers |      |

|    | 5.3  | Proposed class-D architecture for piezoelectric speakers           |      |

|    | 0.0  | 110p0000 01m00 D midilicotate for production openitors             | 101  |

|    |            |                                                           | Page |

|----|------------|-----------------------------------------------------------|------|

|    |            | 5.3.1 Architecture description                            | 152  |

|    |            | 1                                                         | 153  |

|    |            |                                                           | 153  |

|    |            | <ul><li>5.3.3 Self-oscillating modulator design</li></ul> | 154  |

|    | 5.4        | Proposed stacked-cascode H-bridge output stage            | 160  |

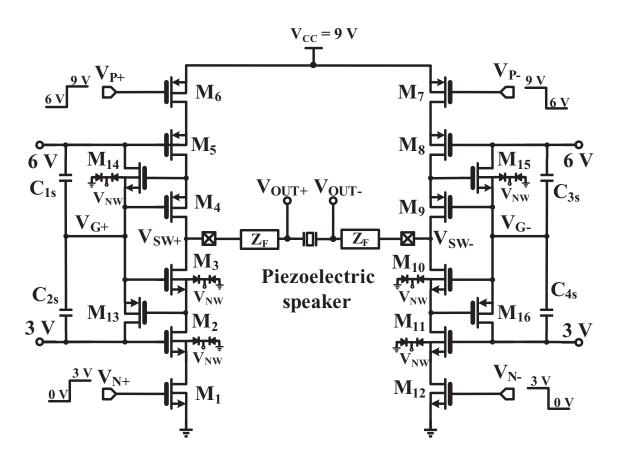

|    | 5.4        | 5.4.1 Stacked-cascode output stage description            | 161  |

|    |            | 5.4.2 Stacked-cascode output stage description            | 163  |

|    |            | 5.4.2 Stacked-cascode output stage operation              | 166  |

|    | 5.5        | Experimental results of CDA for PZ speakers               | 170  |

|    | 5.6        | Conclusion                                                | 177  |

|    | 5.0        | Conclusion                                                | 1//  |

| 6. | OPE        | EN PROBLEMS IN CLASS-D AMPLIFIERS                         | 179  |

|    | 6.1        | Class-D amplifier current trends                          | 179  |

|    | 6.2        | Audio CODEC integration                                   | 181  |

|    |            |                                                           |      |

| 7. | SUM        | MMARY                                                     | 184  |

| RE | EFERI      | ENCES                                                     | 186  |

| AF | PPEN       | DIX A. CLASS-G AMPLIFIER CASE STUDY                       | 202  |

|    | A.1        | Class-G amplification background                          | 202  |

|    | A.1<br>A.2 | Proposed class-G implementation                           | 204  |

|    | A.3        |                                                           | 208  |

|    | A.4        | Experimental results of proposed class-G amplifier        | 215  |

|    | A.5        | Conclusion                                                | 219  |

|    | 11.5       | Conclusion                                                | 21)  |

| AF | PPEN]      | DIX B. CLASS-D AMPLIFIER WITH SLIDING MODE                | 220  |

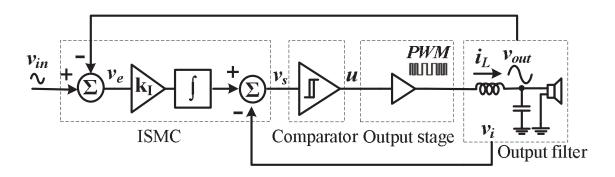

|    | B.1        | Design of the proposed class-D architecture with ISMC     | 220  |

|    | B.2        | Integral sliding mode controller                          |      |

|    | B.3        | Experimental results of CDA with ISMC                     | 227  |

|    | B.4        | Conclusion                                                | 233  |

| ΑF |            | DIX C. PAPER CONTRIBUTIONS                                |      |

# LIST OF FIGURES

| FIGURE |                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------|------|

| 1.1    | Proposed solution to cancel supply noise (Section 4)                              | 3    |

| 1.2    | Proposed solution to drive piezoelectric speakers (Section 5)                     | 4    |

| 2.1    | Audio amplifier operation.                                                        | 7    |

| 2.2    | Audio waveform across distance                                                    | 7    |

| 2.3    | EM speaker physical structure side view                                           | 10   |

| 2.4    | EM electrical impedance versus frequency                                          | 11   |

| 2.5    | PZ speaker physical structure side view                                           | 12   |

| 2.6    | PZ and EM speakers impedance versus frequency comparison                          | 13   |

| 2.7    | THD+N typical plot against output power for audio amplifiers                      | 16   |

| 2.8    | Typical output frequency spectrum for audio amplifiers                            | 18   |

| 2.9    | PSRR measurement example for a noise signal at 217 Hz with -20 dB amplitude       | 19   |

| 2.10   | PS-IMD measurement example for a noise signal at 217 Hz and audio signal at 1 kHz | 21   |

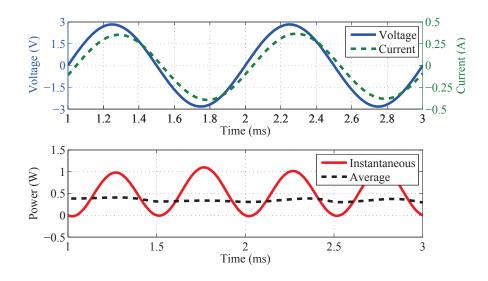

| 2.11   | Instantaneous and average power for a EM speaker with $\phi < 15^{\circ}.$        | 22   |

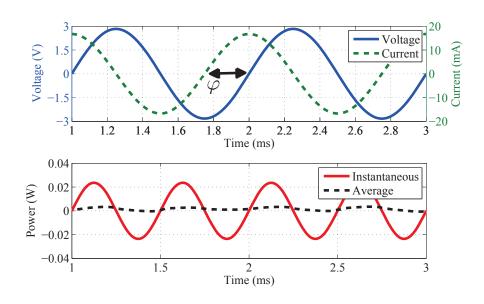

| 2.12   | Instantaneous and average power for a PZ speaker with $\phi\cong 90^\circ.$       | 23   |

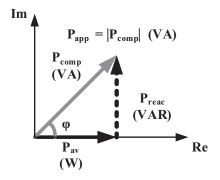

| 2.13   | Complex power definition                                                          | 24   |

| 2.14   | Main linear amplification classes                                                 | 25   |

| 2.15   | Class-G amplifier operation                                                       | 26   |

| 2.16   | Class-H amplifier operation                                                       | 27   |

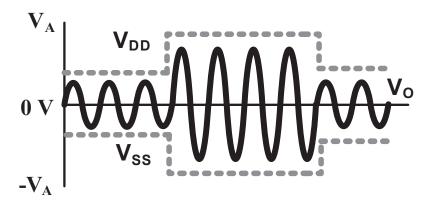

| 2.17   | Class-D amplifier operation, time domain                                          | 28   |

| FIGURE |                                                                                                       | Page |

|--------|-------------------------------------------------------------------------------------------------------|------|

| 2.18   | Class-D amplifier operation, frequency domain                                                         | 29   |

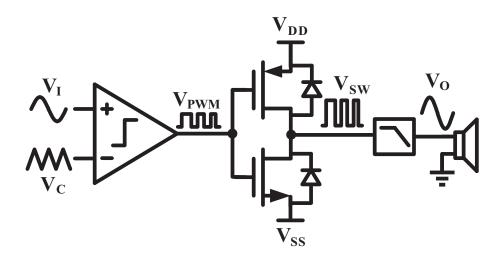

| 3.1    | Analog class-D amplifier in single-ended open-loop architecture                                       | 31   |

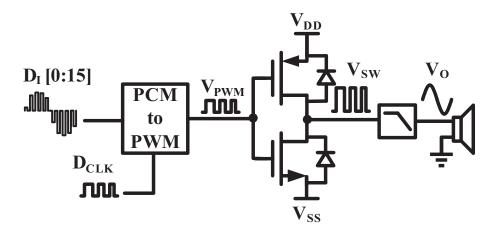

| 3.2    | Digital class-D amplifier in single-ended open-loop architecture                                      | 31   |

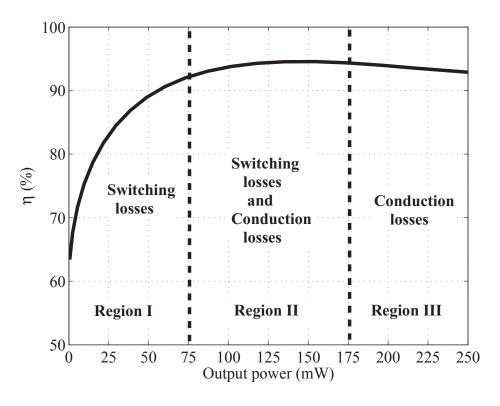

| 3.3    | PCM and PWM comparison                                                                                | 32   |

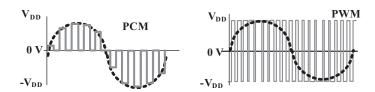

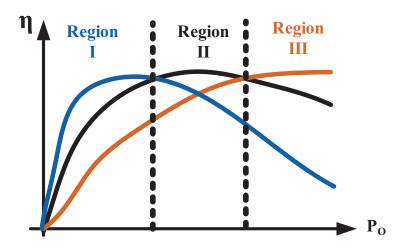

| 3.4    | Efficiency versus output power example for a class-D amplifier, showing power losses dominated region | 35   |

| 3.5    | Efficiency curves for different output stage optimizations                                            | 36   |

| 3.6    | Class-D output stage driving an EM speaker load                                                       | 37   |

| 3.7    | Class-D output stage driving a PZ speaker load                                                        | 37   |

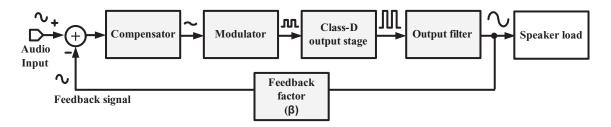

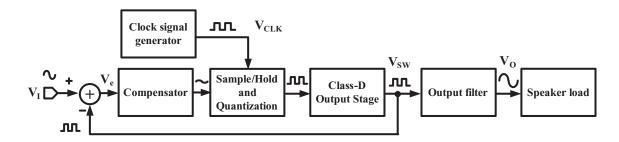

| 3.8    | General close loop CDA architecture                                                                   | 41   |

| 3.9    | Close loop CDA architecture with alternative feedback, including output filter                        | 42   |

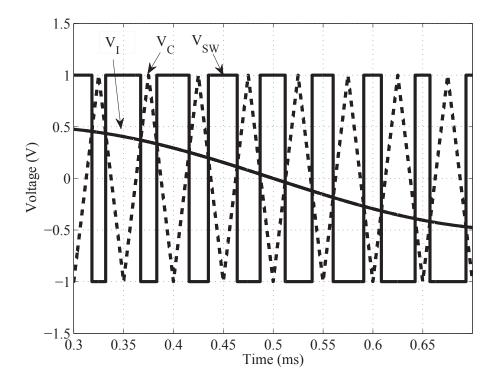

| 3.10   | Open loop PWM waveforms                                                                               | 44   |

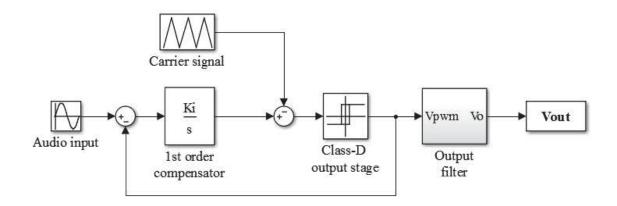

| 3.11   | Close loop PWM CDA architecture                                                                       | 45   |

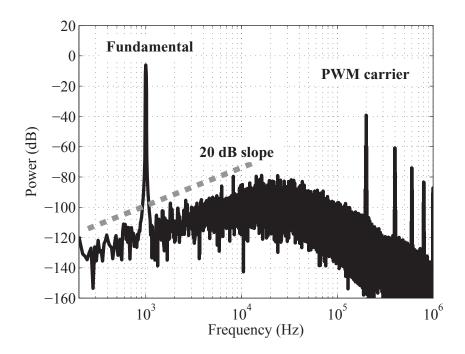

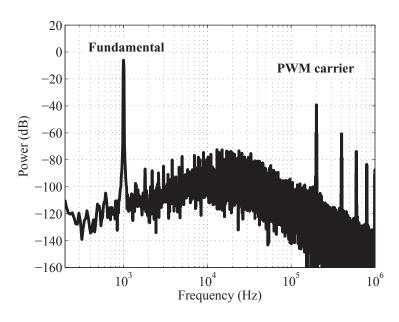

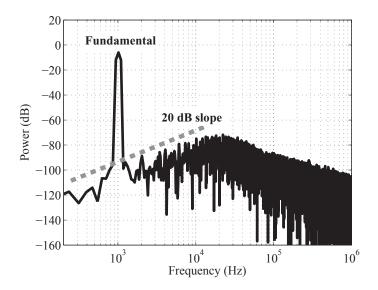

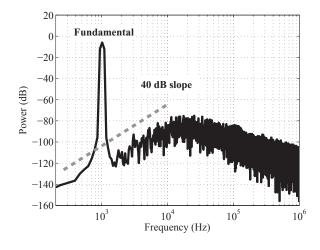

| 3.12   | Output spectrum for 1st order PWM CDA with UGF=50 kHz                                                 | 46   |

| 3.13   | Simulink model for 1st order PWM CDA architecture                                                     | 47   |

| 3.14   | Output spectrum for 1st order PWM CDA with UGF=25 kHz                                                 | 48   |

| 3.15   | Output spectrum for 1st order PWM CDA with UGF=100 kHz                                                | 49   |

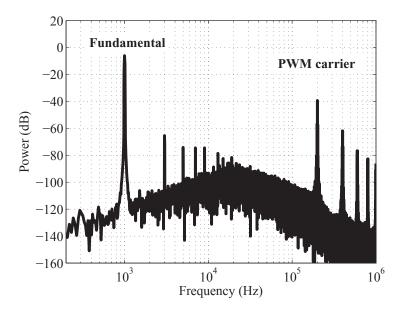

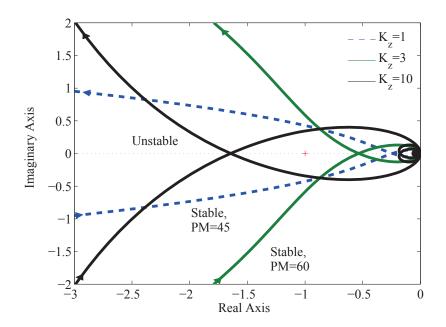

| 3.16   | Bode plot for second order PWM CDA for different $K_z$ values                                         | 50   |

| 3.17   | Nyquist plot for second order PWM CDA for different $K_z$ values                                      | 51   |

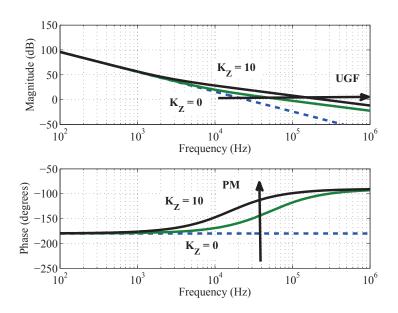

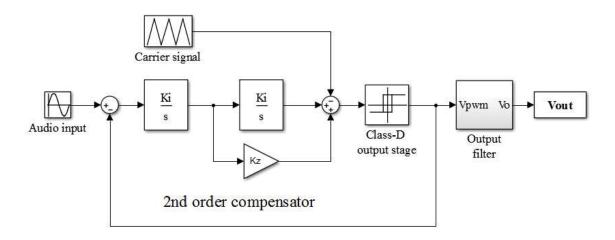

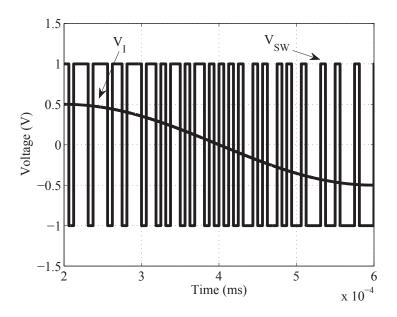

| 3.18   | Simulink model for 2nd order PWM CDA architecture                                                     | 52   |

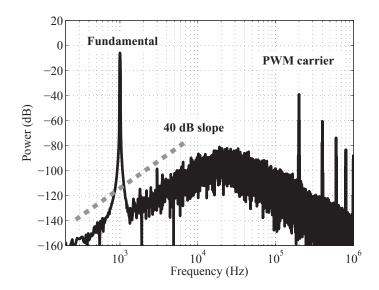

| 3.19   | Output spectrum for 2nd order PWM CDA with UGF=50 kHz                                                 | 52   |

| 3.20   | Close loop SDM waveforms                                                                              | 54   |

| FIGURE |                                                                                 | Page |

|--------|---------------------------------------------------------------------------------|------|

| 3.21   | Close loop SDM CDA architecture                                                 | 54   |

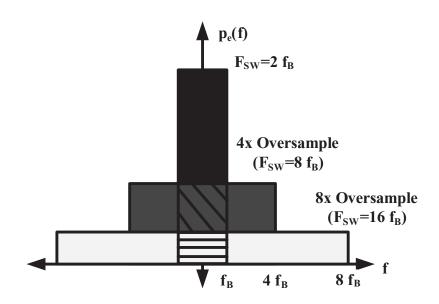

| 3.22   | Oversampling effect on the error power density                                  | 56   |

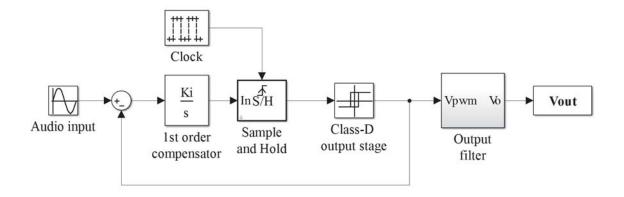

| 3.23   | Simulink model for 1st order SDM CDA architecture                               | 58   |

| 3.24   | Output spectrum for 1st order SDM CDA with OSR=128                              | 59   |

| 3.25   | Output spectrum for 2nd order SDM CDA with OSR=128                              | 60   |

| 3.26   | Output spectrum for 2nd order SDM CDA with OSR=256                              | 61   |

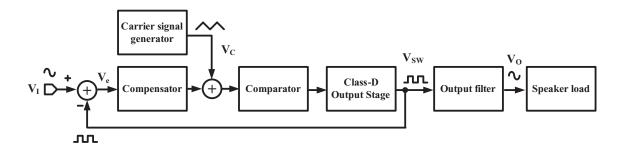

| 3.27   | Close loop general SOM CDA architecture                                         | 62   |

| 3.28   | Bang-bang SOM CDA architecture                                                  | 63   |

| 3.29   | Simulink model for bang-bang CDA architecture                                   | 64   |

| 3.30   | Output spectrum for bang-bang CDA architecture                                  | 65   |

| 3.31   | Simulink model for a 2nd order SOM CDA architecture                             | 66   |

| 3.32   | Output spectrum for 2nd order general SOM CDA architecture                      | 66   |

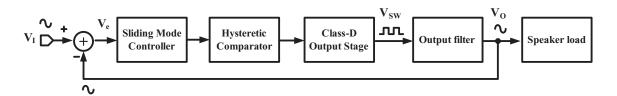

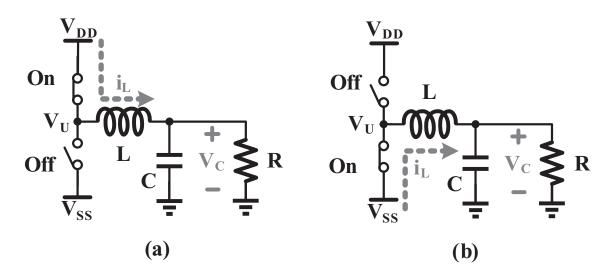

| 3.33   | Close loop SMC CDA architecture                                                 | 67   |

| 3.34   | Switching structure in the CDA when connected to (a) $V_{DD}$ or (b) $V_{SS}$ . | 67   |

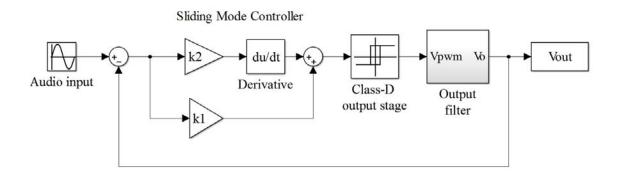

| 3.35   | Simulink model for SMC CDA architecture                                         | 69   |

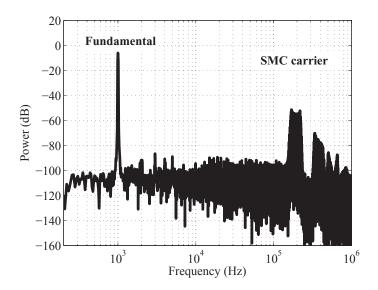

| 3.36   | Output spectrum for SMC CDA architecture                                        | 69   |

| 3.37   | Close loop ISMC CDA architecture                                                | 70   |

| 3.38   | Simulink model for ISMC CDA architecture                                        | 71   |

| 3.39   | Output spectrum for ISMC CDA architecture                                       | 71   |

| 3.40   | First-order single-ended PWM class-D audio amplifier circuit                    | 73   |

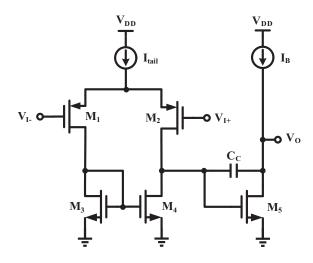

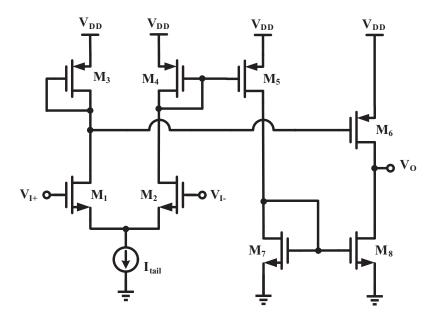

| 3.41   | Miller compensated two-stage amplifier                                          | 77   |

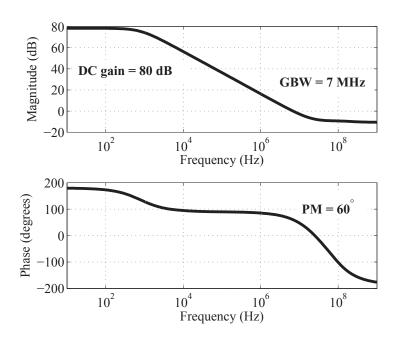

| 3.42   | Bode plot of two-stage example amplifier                                        | 81   |

| FIGURE |                                                                                                | Page |

|--------|------------------------------------------------------------------------------------------------|------|

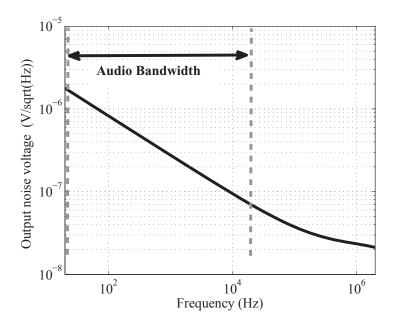

| 3.43   | Equivalent output noise voltage for the example amplifier                                      | 82   |

| 3.44   | Comparator schematic diagram with push-pull output stage                                       | 83   |

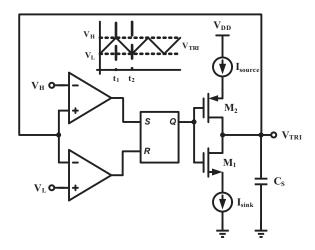

| 3.45   | Triangle wave generator circuit                                                                | 86   |

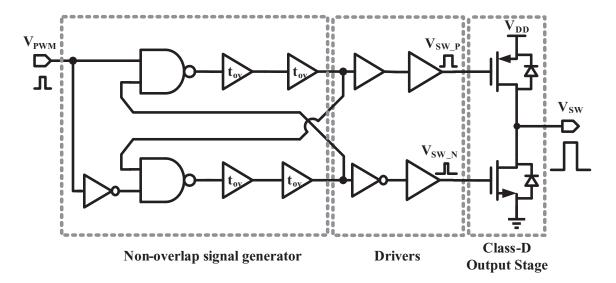

| 3.46   | Class-D output stage with auxiliary circuits                                                   | 88   |

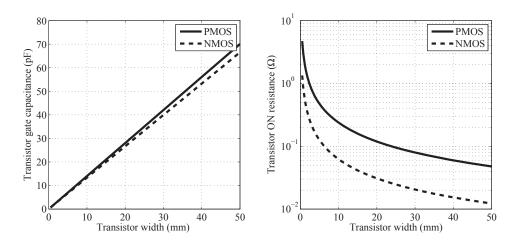

| 3.47   | Transistor gate capacitance and $R_{dsON}$ versus transistor width                             | 89   |

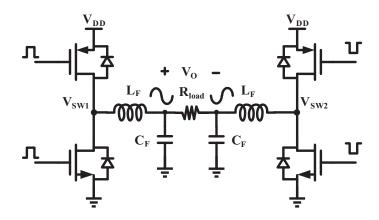

| 3.48   | Full-bridge class-D output stage                                                               | 91   |

| 3.49   | First-order differential PWM CDA architecture                                                  | 93   |

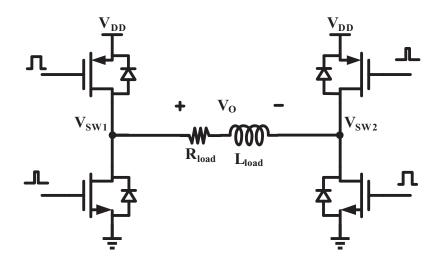

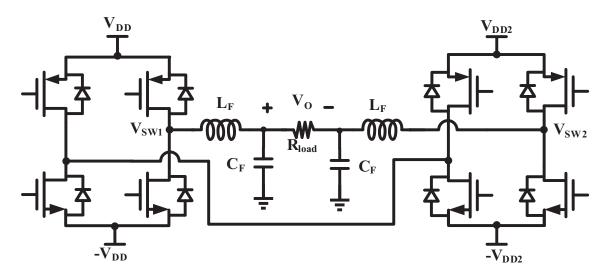

| 3.50   | Filterless class-D output stage                                                                | 94   |

| 3.51   | Filterless and conventional H-bridge switching comparison                                      | 94   |

| 3.52   | Multilevel class-D output stage                                                                | 95   |

| 3.53   | Switching output waveform with 5 quantization levels                                           | 96   |

| 3.54   | Multiphase interleaved class-D output stage                                                    | 96   |

| 3.55   | Single-ended output filter configurations                                                      | 98   |

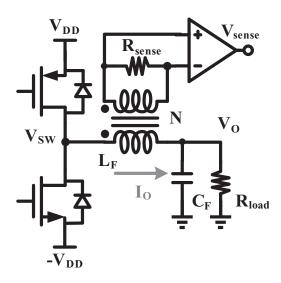

| 3.56   | Current sensing method using inductor series resistor                                          | 99   |

| 3.57   | Current sensing method using current transformer                                               | 100  |

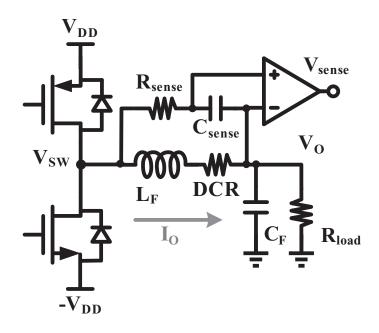

| 3.58   | Current sensing method using DCR sensing                                                       | 101  |

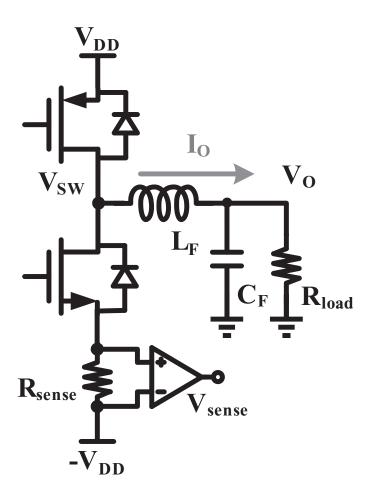

| 3.59   | Current sensing method using source sensing resistor                                           | 102  |

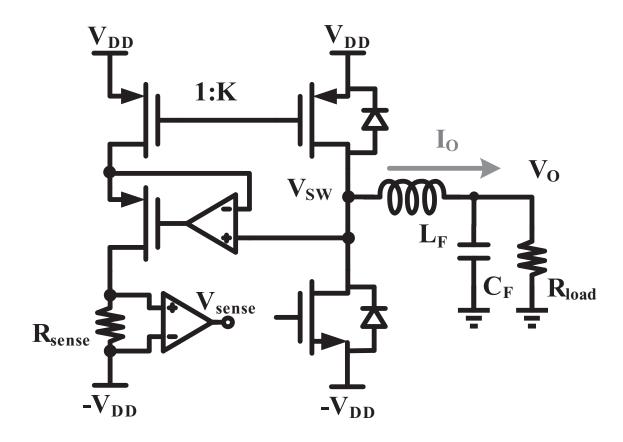

| 3.60   | Current sensing method using a current mirror MOSFET                                           | 104  |

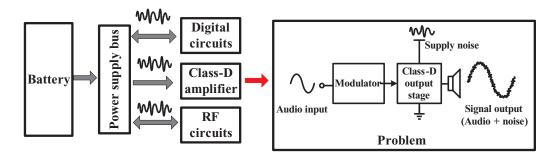

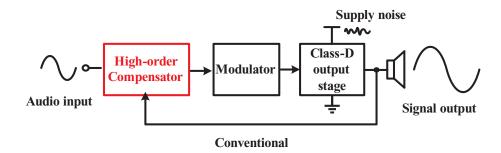

| 4.1    | Power supply noise problem in class-D amplifiers                                               | 107  |

| 4.2    | Conceptual diagram of conventional solution to reduce power supply noise in class-D amplifiers | 107  |

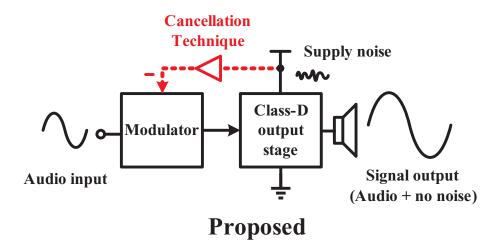

| 4.3    | Conceptual diagram of proposed solution to reduce power supply noise in class-D amplifiers     | 108  |

| FIGURE |                                                                                                                                                                                                                           | Page |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

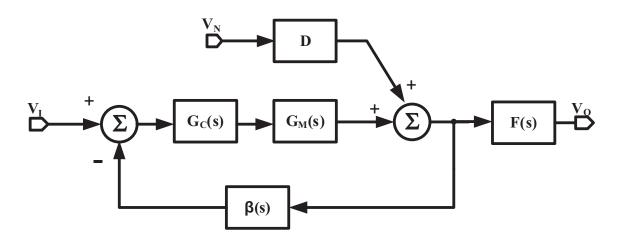

| 4.4    | Single-ended class-D audio amplifier linear model                                                                                                                                                                         | 110  |

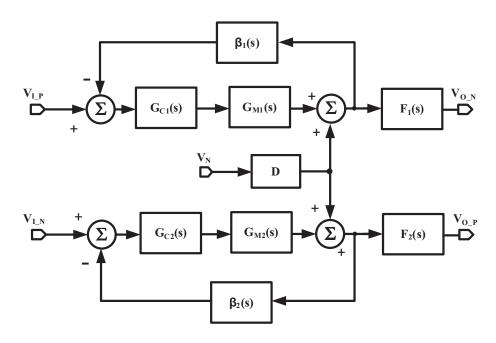

| 4.5    | Bridge-Tied Load differential CDA linear model                                                                                                                                                                            | 112  |

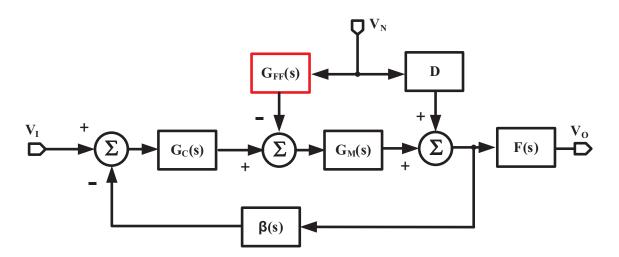

| 4.6    | Class-D amplifier linear model with proposed FFPSNC technique                                                                                                                                                             | 114  |

| 4.7    | Magnitude and phase frequency response of zero-order hold                                                                                                                                                                 | 118  |

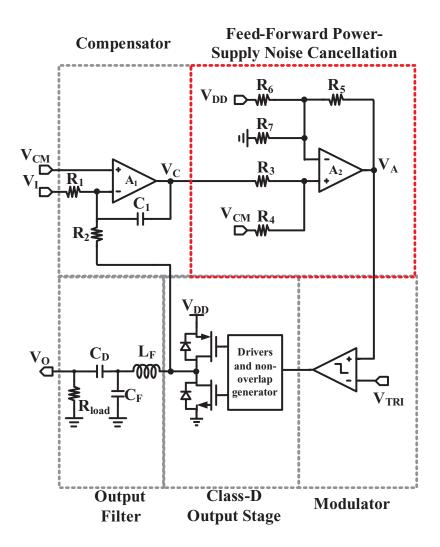

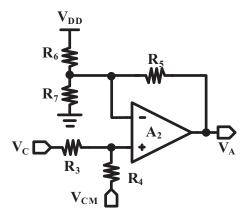

| 4.8    | Proposed CDA implementation with FFPSNC technique                                                                                                                                                                         | 120  |

| 4.9    | PWM comparator schematic diagram                                                                                                                                                                                          | 123  |

| 4.10   | Single-ended class-D output stage                                                                                                                                                                                         | 124  |

| 4.11   | Transistor total gate capacitance and $R_{dsON}$ versus transistor width for output stage sizing                                                                                                                          | 125  |

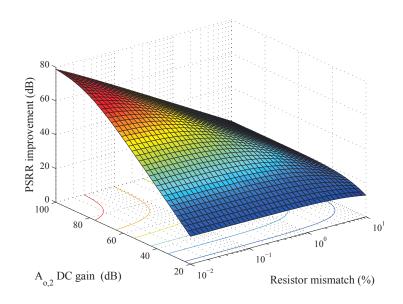

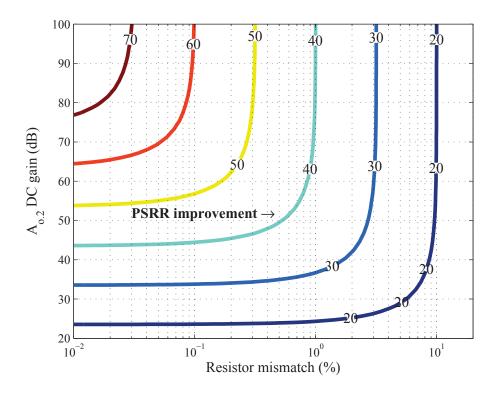

| 4.12   | 3D-surface plot of design tradeoffs for $G_{FF}$ implementation                                                                                                                                                           | 129  |

| 4.13   | Contour plot of design tradeoffs for $G_{FF}$ implementation                                                                                                                                                              | 130  |

| 4.14   | Proposed FFPSNC technique implementation                                                                                                                                                                                  | 131  |

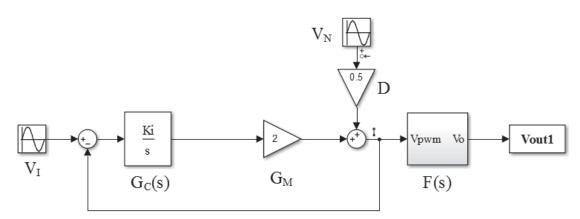

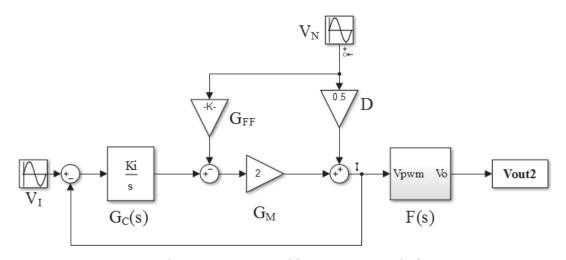

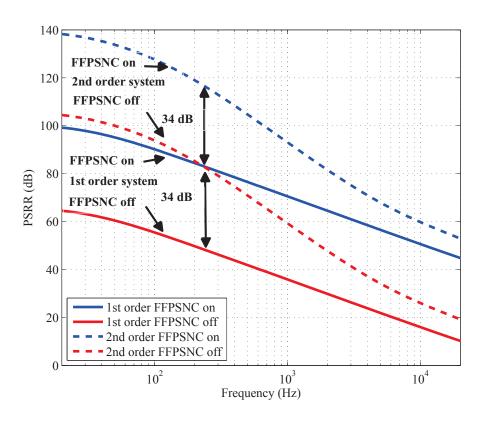

| 4.15   | Simulink models for 1st order PWM CDA for supply noise                                                                                                                                                                    | 133  |

| 4.16   | Simulink models for 2nd order PWM CDA for supply noise                                                                                                                                                                    | 134  |

| 4.17   | PSRR simulation results comparison for transistor level designs                                                                                                                                                           | 135  |

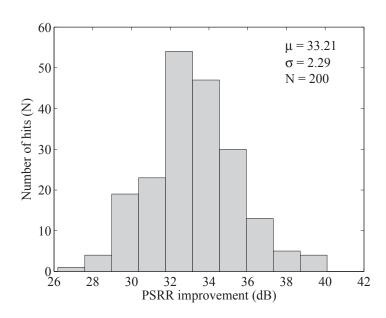

| 4.18   | PSRR improvement Montecarlo simulation results                                                                                                                                                                            | 136  |

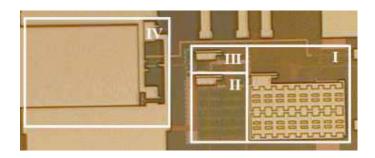

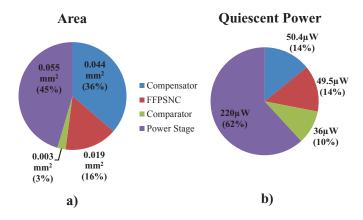

| 4.19   | Class-D audio amplifier die micrograph, I compensator (0.044 mm <sup>2</sup> ), II FFPSNC technique (0.019 mm <sup>2</sup> ), III comparator (0.003 mm <sup>2</sup> ), and IV output power-stage (0.055 mm <sup>2</sup> ) | 137  |

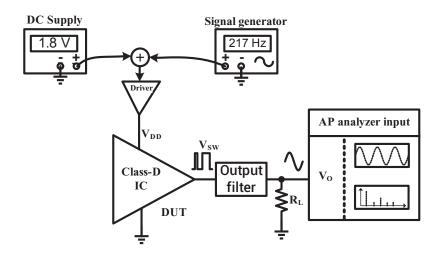

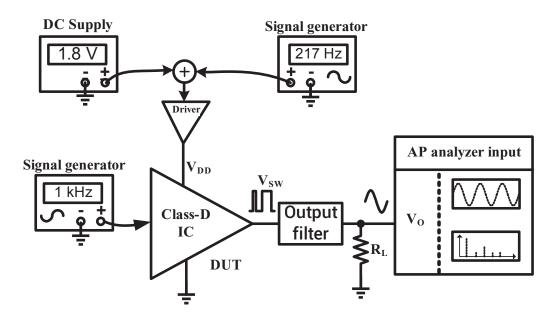

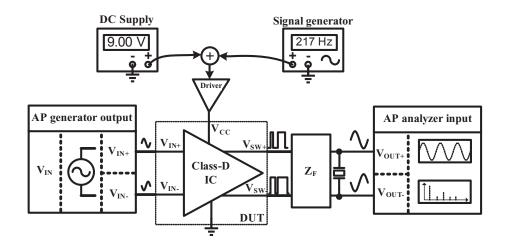

| 4.20   | Test setup for PSRR measurement of single-ended CDA                                                                                                                                                                       | 138  |

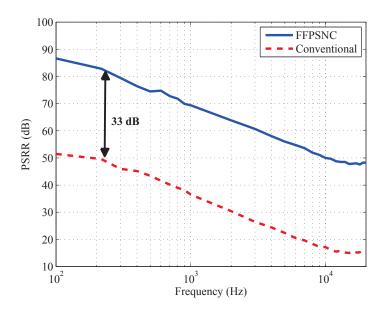

| 4.21   | Class-D audio amplifier PSRR measurement results with FFPSNC technique                                                                                                                                                    | 139  |

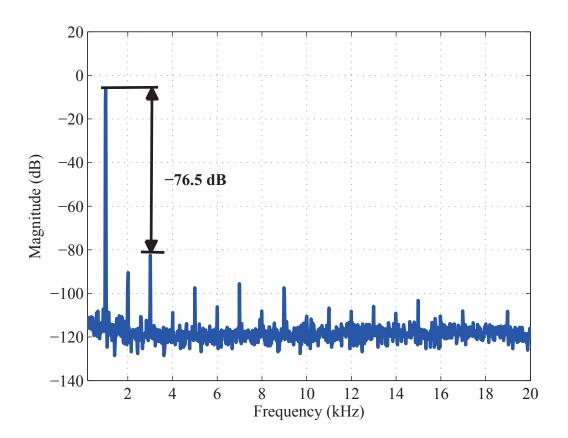

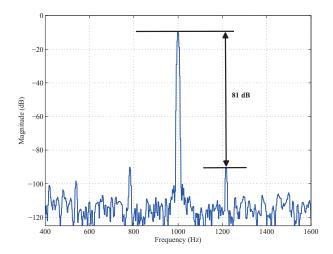

| 4.22   | Measured output spectrum for CDA with FFPSNC technique with Vin= 0.5 Vrms at 1 KHz                                                                                                                                        | 140  |

| FIGURE | Page |

|--------|------|

|--------|------|

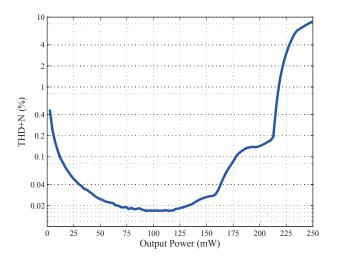

| 4.23 | Measured THD+N versus output power for CDA with FFPSNC technique.                                                                                      | 141 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

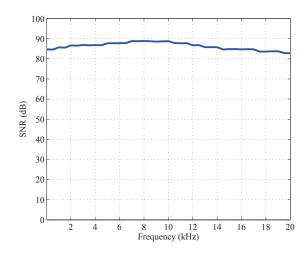

| 4.24 | Measured SNR for proposed CDA with FFPSNC technique                                                                                                    | 141 |

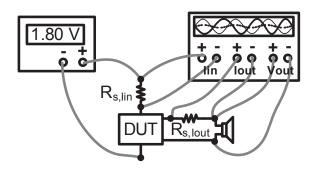

| 4.25 | Test setup for efficiency measurement in single-ended CDA                                                                                              | 142 |

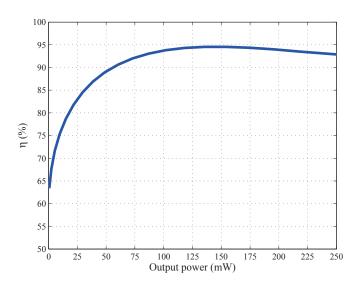

| 4.26 | Measured efficiency versus output power for CDA with FFPSNC technique                                                                                  | 142 |

| 4.27 | Test setup for PS-IMD measurement for single-ended CDA                                                                                                 | 143 |

| 4.28 | Power-supply intermodulation distortion measurement for CDA with FF-PSNC technique                                                                     | 144 |

| 4.29 | CDA with FFPSNC, a) area and b) quiescent power with $V_{in}=0V$                                                                                       | 144 |

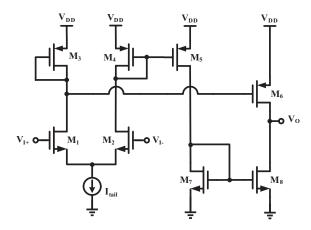

| 5.1  | Proposed CDA architecture for PZ speakers                                                                                                              | 152 |

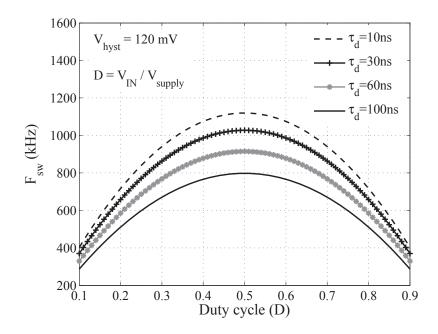

| 5.2  | Calculated switching frequency $(F_{SW})$ versus duty cycle (D) of the CDA for several propagation delay $(\tau_d)$ cases with a fix hysteresis window | 156 |

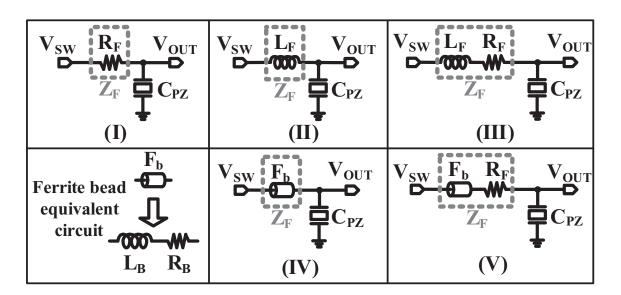

| 5.3  | Different output filter configurations for impedance $Z_F$ together with PZ speaker equivalent impedance $C_{PZ}$                                      | 157 |

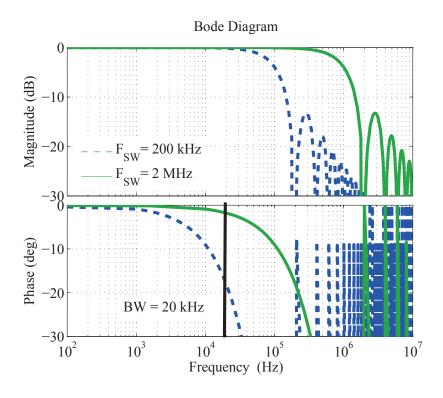

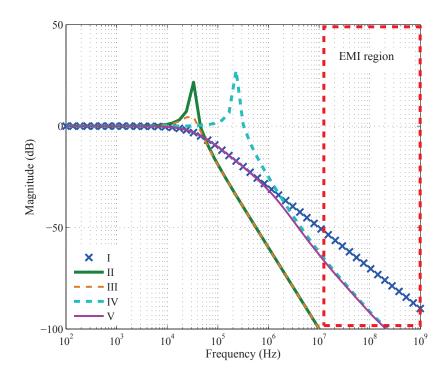

| 5.4  | Bode plot for output filter configurations with PZ speaker                                                                                             | 159 |

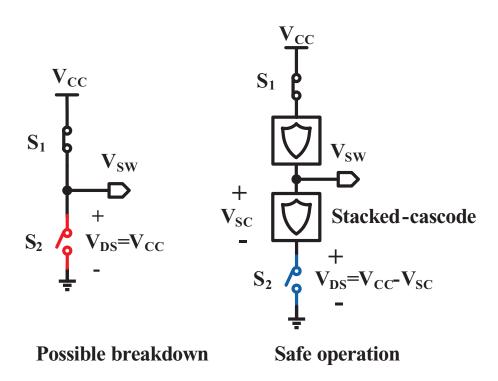

| 5.5  | Stacked-cascode over-voltage protection conceptual operation                                                                                           | 161 |

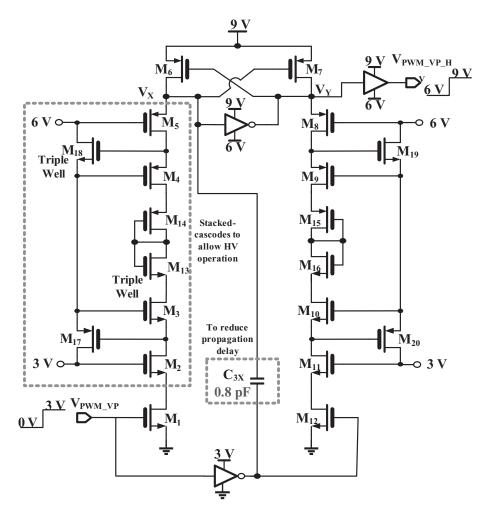

| 5.6  | Proposed output stage schematic for driving PZ speakers                                                                                                | 162 |

| 5.7  | Proposed stacked-cascode output stage simplified operation                                                                                             | 164 |

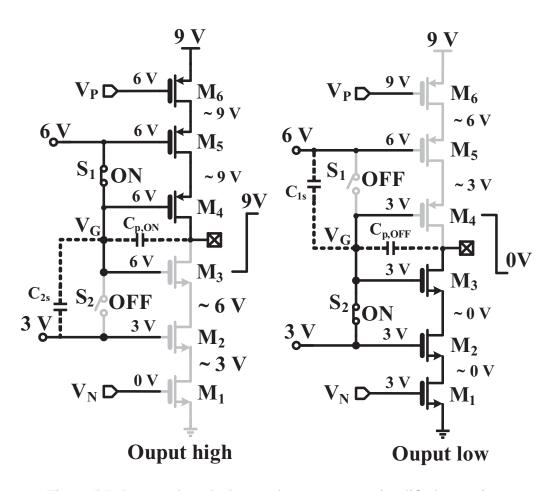

| 5.8  | Transient simulation of $V_G$ across PVT                                                                                                               | 165 |

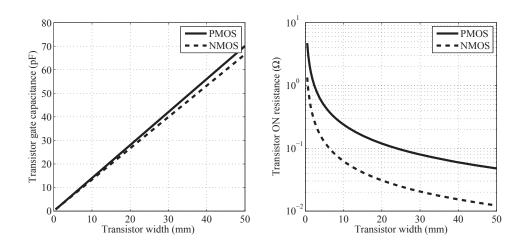

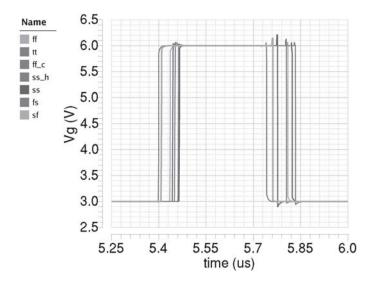

| 5.9  | Gate driver block diagram stacked-cascode output stage                                                                                                 | 166 |

| 5.10 | Level shifter from 1.8 V to 3 V schematic                                                                                                              | 166 |

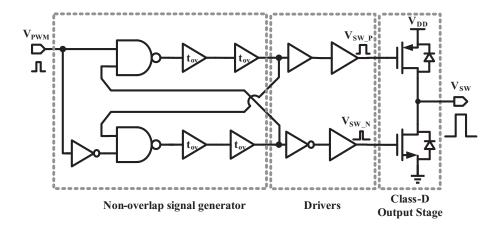

| 5.11 | Implemented non-overlap generator for gate drivers                                                                                                     | 167 |

| 5.12 | Non-overlapping gate drive typical waveforms                                                                                                           | 168 |

| 5.13 | Gate drivers implementation for PMOS and NMOS path                                                                                                     | 169 |

| FIGURE |                                                                                                                                                                                                                                   | Page |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.14   | Level shifter from 3 V to 9 V schematic with floating ground                                                                                                                                                                      | 169  |

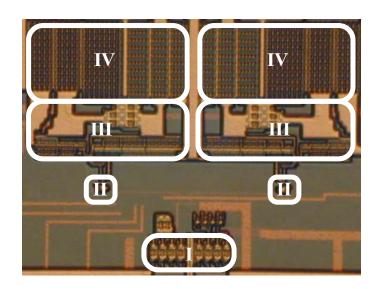

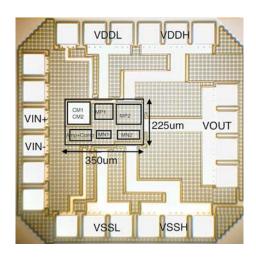

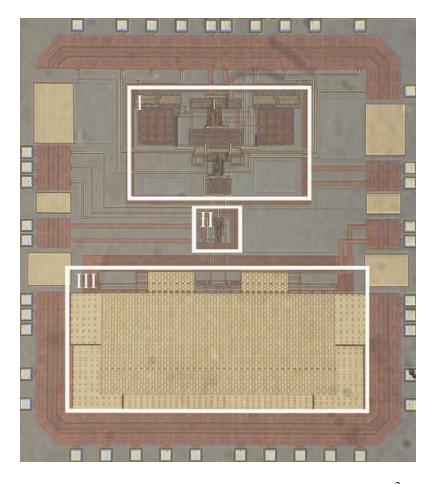

| 5.15   | Die micrograph of CDA for PZ speakers, I integrator (0.0715 mm <sup>2</sup> ), II comparator (0.0026 mm <sup>2</sup> ), III Pre-drivers (0.0852 mm <sup>2</sup> ), and IV stacked-cascode output stage (0.2571 mm <sup>2</sup> ). | 170  |

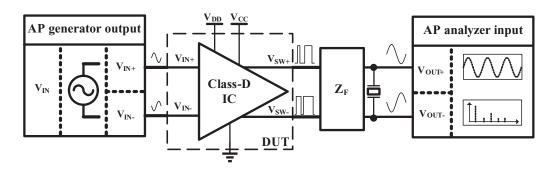

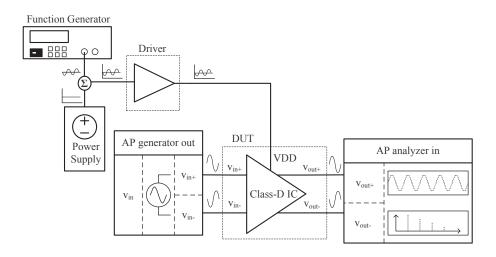

| 5.16   | Measurement test configuration of CDA for PZ speakers                                                                                                                                                                             | 171  |

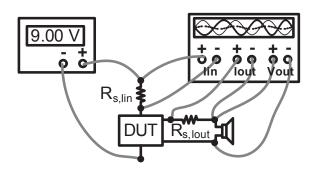

| 5.17   | Measurement test configuration for supply and output currents                                                                                                                                                                     | 171  |

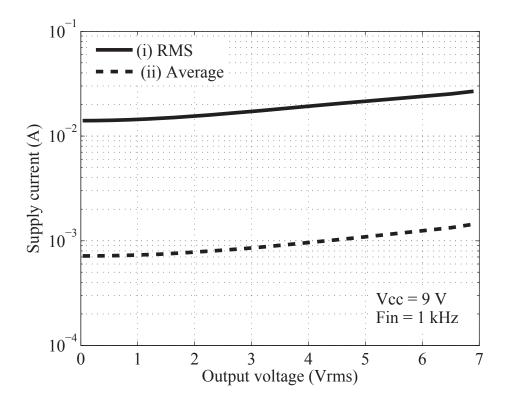

| 5.18   | Measured supply current for CDA driving a PZ speaker                                                                                                                                                                              | 172  |

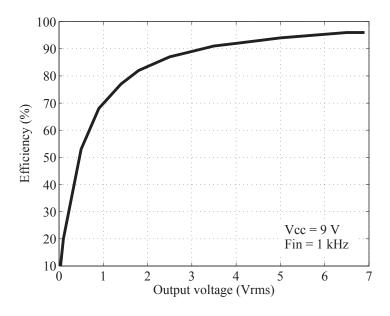

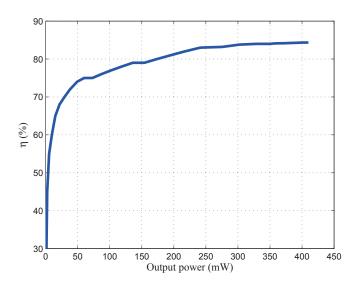

| 5.19   | Measured power-efficiency for CDA driving a PZ speaker                                                                                                                                                                            | 173  |

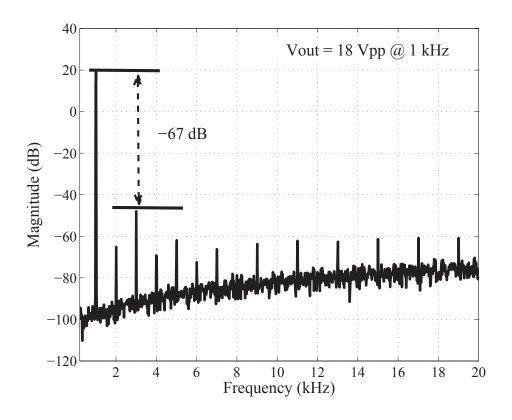

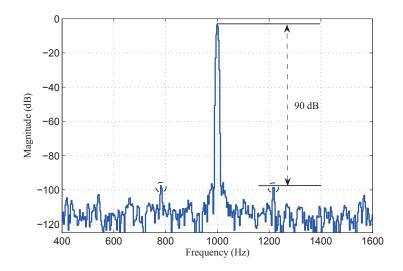

| 5.20   | Measured frequency spectrum for 18 $V_{PP}$ output signal at 1 kHz                                                                                                                                                                | 174  |

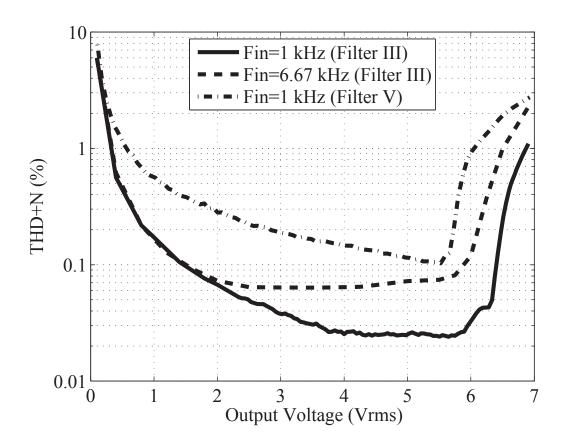

| 5.21   | Comparison of the measured THD+N versus output voltage                                                                                                                                                                            | 175  |

| 5.22   | PS-IMD test bench of CDA for PZ speakers                                                                                                                                                                                          | 176  |

| 5.23   | Measured PS-IMD frequency spectrum of CDA for PZ speakers                                                                                                                                                                         | 176  |

| 6.1    | Typical audio CODEC block diagram                                                                                                                                                                                                 | 181  |

| 6.2    | Comparison between voltage/current ADC and time-domain TDC                                                                                                                                                                        | 183  |

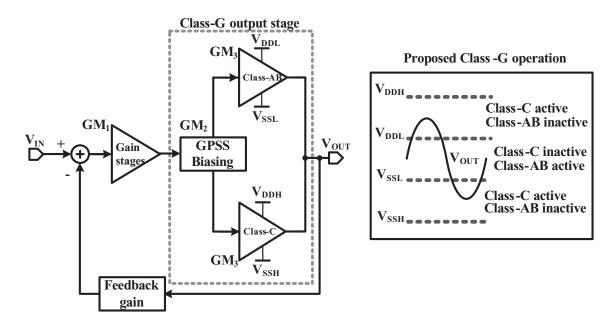

| A.1    | Proposed class-G amplifier diagram and operation                                                                                                                                                                                  | 204  |

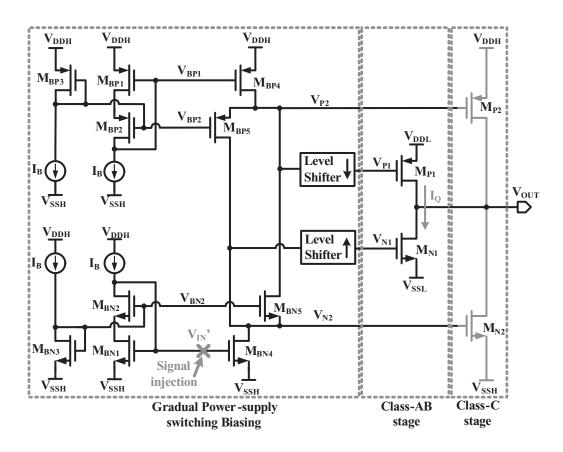

| A.2    | GPSS biasing circuit at quiescent condition                                                                                                                                                                                       | 205  |

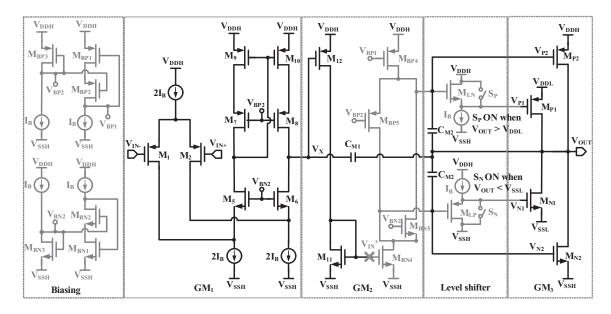

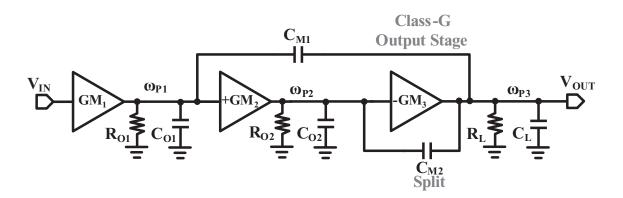

| A.3    | Proposed class-G audio amplifier schematic with GPSS biasing                                                                                                                                                                      | 206  |

| A.4    | Class-G output stage operation across the output voltage swing                                                                                                                                                                    | 207  |

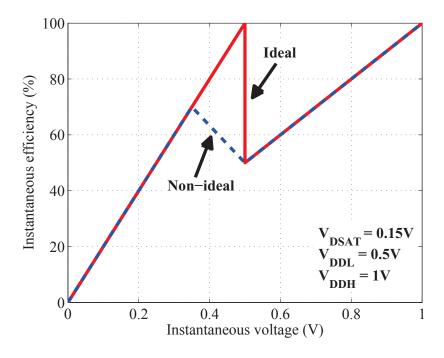

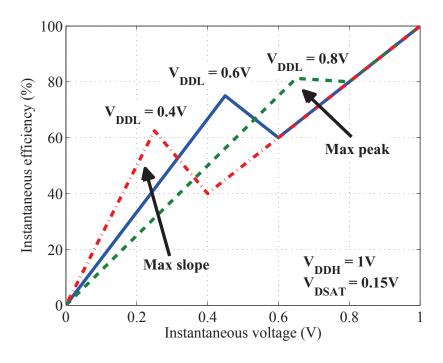

| A.5    | Effect of $V_{DSAT}$ of class-AB transistors on the class-G efficiency                                                                                                                                                            | 209  |

| A.6    | Effect of smaller supply $(V_{DDL})$ choice on the class-G efficiency                                                                                                                                                             | 210  |

| A.7    | Proposed class-G audio amplifier small-signal block diagram                                                                                                                                                                       | 211  |

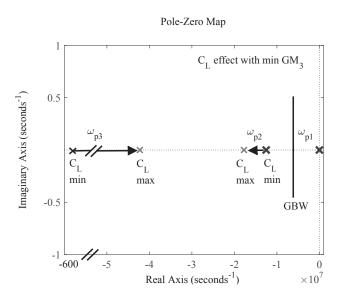

| A.8    | Pole-zero map when load capacitance changes from 10 pF ( $C_L$ min) to 1 nF ( $C_L$ max)                                                                                                                                          | 213  |

FIGURE

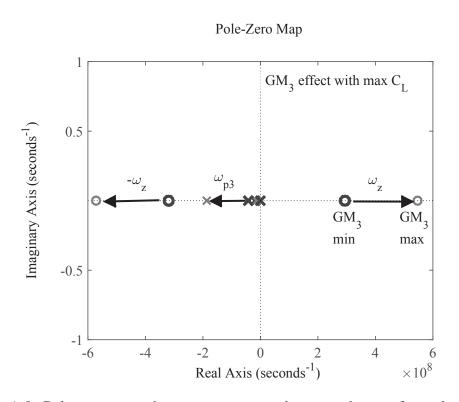

| A.9  | Pole-zero map when output transconductance changes from class-AB ( $GM_3$ min) to class-C ( $GM_3$ max) operation                                           | 214 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| A.10 | Stability and pole location for different output load conditions                                                                                            | 215 |

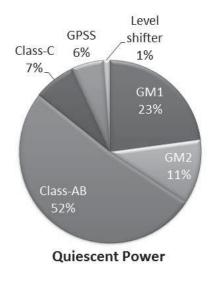

| A.11 | Proposed class-G amplifier die micrograph                                                                                                                   | 216 |

| A.12 | Proposed class-G amplifier quiescent power distribution                                                                                                     | 216 |

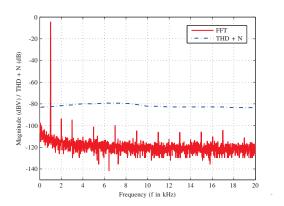

| A.13 | Measured THD+N and output FFT versus frequency                                                                                                              | 217 |

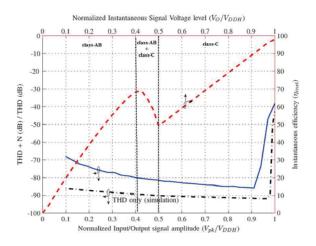

| A.14 | Measured THD+N and efficiency versus amplitude                                                                                                              | 217 |

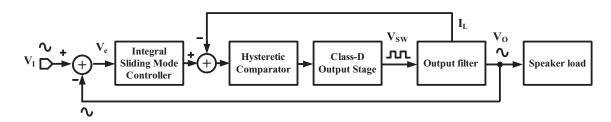

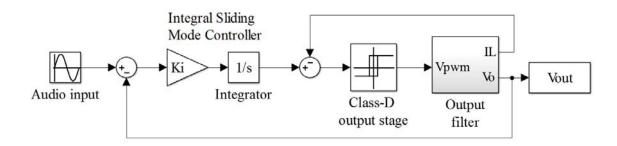

| B.1  | Block diagram of the proposed class-D amplifier                                                                                                             | 221 |

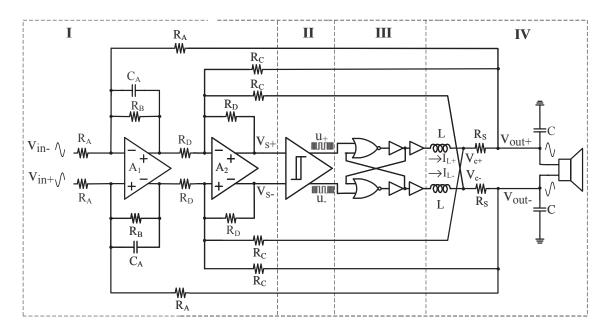

| B.2  | Proposed ISMC implementation, I ISMC implementation, II comparator, III output power stage, IV LPF                                                          | 223 |

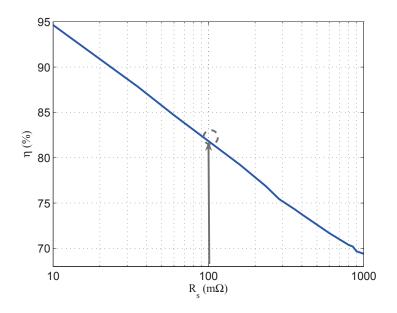

| B.3  | Efficiency versus $R_s$ for $V_{in}=2$ $V_{pp}$                                                                                                             | 224 |

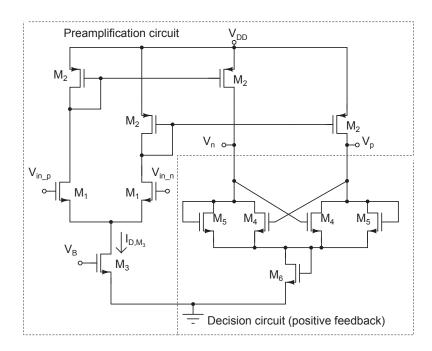

| B.4  | Hysteretic comparator implementation                                                                                                                        | 225 |

| B.5  | Class-D with ISMC die micrograph, I controller (0.430mm <sup>2</sup> ), II comparator (0.033mm <sup>2</sup> ), and III output stage (1.190mm <sup>2</sup> ) | 227 |

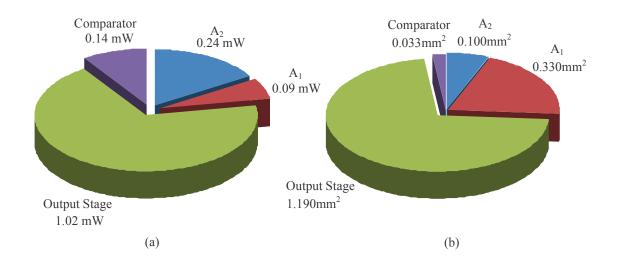

| B.6  | (a) Power and (b) area distribution of the proposed audio amplifier                                                                                         | 228 |

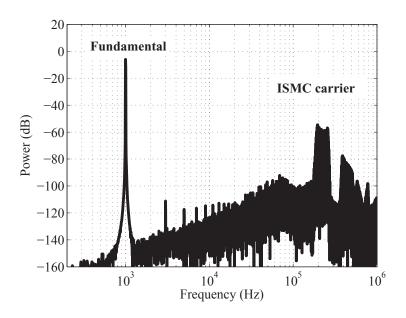

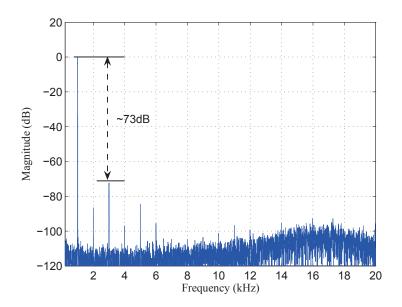

| B.7  | Class-D audio amplifier output FFT when $V_{in}$ = 2.82 $V_{pp}$ at 1 kHz                                                                                   | 229 |

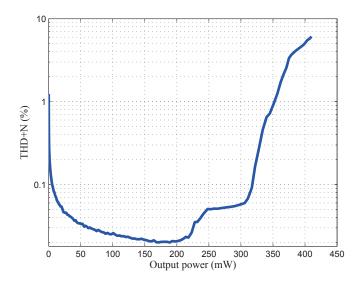

| B.8  | Class-D amplifier with ISMC THD+N versus output power                                                                                                       | 229 |

| B.9  | Class-D amplifier with ISMC efficiency versus output power                                                                                                  | 230 |

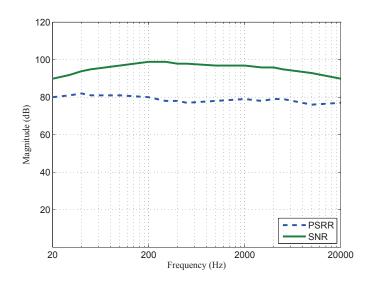

| B.10 | Class-D audio amplifier PSRR and SNR versus frequency                                                                                                       | 230 |

| B.11 | Measurement setup for PS-IMD measurement                                                                                                                    | 231 |

| B.12 | Power supply induced intermodulation distortion measurement                                                                                                 | 231 |

# LIST OF TABLES

| TABLE | I                                                                    | Page |

|-------|----------------------------------------------------------------------|------|

| 2.1   | SPL example levels                                                   | 9    |

| 2.2   | THD+N measurement units                                              | 16   |

| 3.1   | Typical specifications for commercial class-D audio amplifiers       | 39   |

| 3.2   | Summary for the close loop PWM CDA architecture simulations          | 53   |

| 3.3   | Ideal SNR for some SDM examples                                      | 57   |

| 3.4   | Close loop CDA architecture audio performance comparison             | 72   |

| 3.5   | Design procedure for active integrator                               | 80   |

| 3.6   | Design procedure for PWM comparator                                  | 85   |

| 3.7   | Design procedure for half-bridge output stage                        | 90   |

| 3.8   | Design procedure for full-bridge output stage                        | 92   |

| 3.9   | Current sensing techniques comparison for CDA applications           | 105  |

| 4.1   | Proposed FFPSNC technique design procedure for SE PWM architectures. | .132 |

| 4.2   | Comparison between conventional and FFPSNC technique                 | 139  |

| 4.3   | Comparison of FFPSNC technique with state-of-the-art                 | 145  |

| 5.1   | Stacked-cascode biasing design procedure                             | 163  |

| 5.2   | Performance comparison with audio amplifiers for PZ speakers         | 177  |

| A.1   | Comparison with state-of-the-art headphone amplifiers                | 218  |

| B.1   | Performance Summary for CDA with ISMC                                | 232  |

#### INTRODUCTION

#### 1.1 Motivation

The consumer's demand for state-of-the-art multimedia devices such as smart phones and tablet computers has forced manufacturers to provide more system features to compete for a larger portion of the market share. All these extra features expand the number of applications for these devices, but at the expense of increased power consumption and less battery life. Therefore, high-efficiency integrated circuits are needed to extend the battery life of the device.

The audio reproduction feature has become a standard in mobile devices where its high demand has increased the market size for audio integrated circuits at a tremendous rate from around \$2.28 billion in 2013 to an estimated \$2.51 billion in 2014 [1]. Thus, audio amplifiers with low power consumption, high efficiency, and high audio quality are in high demand.

The class-D amplifier (CDA) can operate with high efficiency while providing high audio quality [2, 3, 4, 5, 6, 7]. However, conventional loudspeakers used in mobile devices require large amounts of power to operate, thereby limiting the battery life despite the amplifier's high efficiency. The piezoelectric (PZ) speaker is an alternative that provides high audio quality with low power consumption, but there are few audio amplifiers capable to drive these speakers. Available amplifiers have large power consumption and poor audio quality, lessening the impact and benefit of PZ speakers in mobile devices. Thus, a high-efficiency, low-power audio amplifier for PZ speakers that provides high audio quality is needed.

Another important requirement is that the CDA in mobile devices has to be connected directly to the battery, providing the maximum amount of available power to the load [8, 9]. To reduce the space occupied by integrated circuits, system-on-chip (SOC) applications connect the digital circuits to the same supply as the analog circuits [3, 10]. Consequently, any noise on the battery power-supply plane is mixed together with the audio signal, degrading the audio amplifier performance. Hence, a good power-supply rejection ratio (PSRR) performance is highly desirable in the CDA. Conventional amplifiers increase the power consumption and/or complexity to achieve high PSRR. Thus, a simple and low power solution to increase the PSRR is essential in portable devices.

## 1.2 Research impact

This dissertation focuses on the design of integrated CDA circuits for mobile devices, addressing the issues of driving a low power PZ speaker, and improving the PSRR in the CDA with minimal added power dissipation. New architectures and design techniques for high performance audio amplifiers are introduced to extend battery life and occupy less space.

Nowadays, modern society is taking advantage of the multi-functionality of portable multimedia devices for productivity, education, and entertainment. Loudspeakers and headphones have become a standard in these devices, and having a portable device that provides accessibility and convenience for long periods of time is highly desirable. Therefore, enabling low-power high-efficiency audio amplifiers would provide longer battery life for extended phone calls, remote conferencing, video streaming, games, and music.

The potential of the presented dissertation research would benefit any individual that takes advantage of the multi-functionality of mobile devices. The global leaders in CMOS integrated circuits could leverage the research developments presented in this dissertation to provide mobile devices with extended battery life.

#### 1.3 Dissertation organization

This dissertation is organized as follows. Section 2 reviews the fundamentals of audio amplification. The principles of sound and audio, the loudspeaker's operation, and the main audio performance metrics are described to explain the limitations involved in the audio amplification process. A brief review on audio amplifier classification and operation is discussed to show the efficiency advantage of the CDA over other configurations. Typical specifications of commercial class-D amplifiers are provided to understand the performance requirements in mobile devices.

In Section 3, the operating principle and design procedure of the CDA are examined to provide a broad view of the design tradeoffs involved. The design requirements of the main building blocks in close loop architectures with different modulation techniques are discussed. The main CDA output stage configurations are examined as well as their performance tradeoffs.

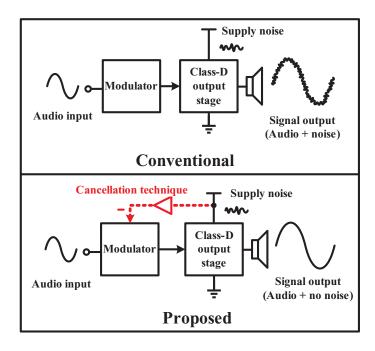

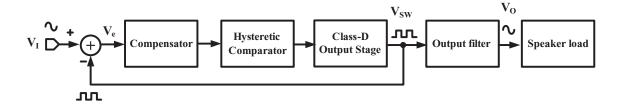

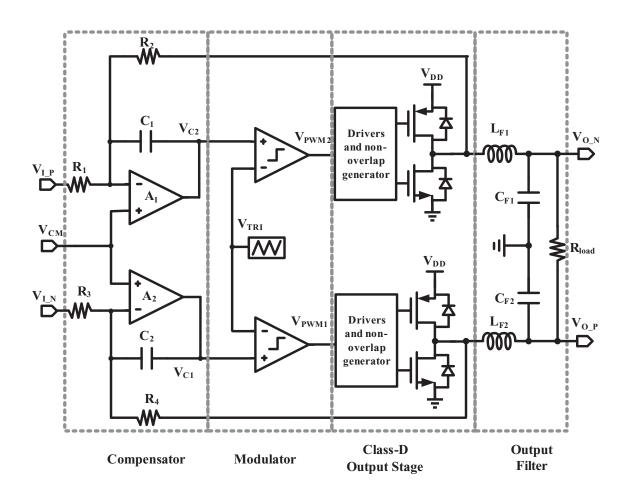

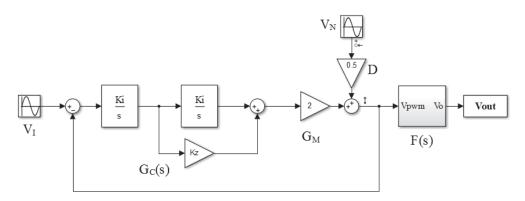

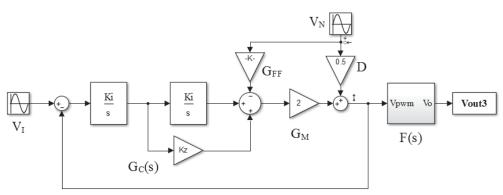

Figure 1.1: Proposed solution to cancel supply noise (Section 4).

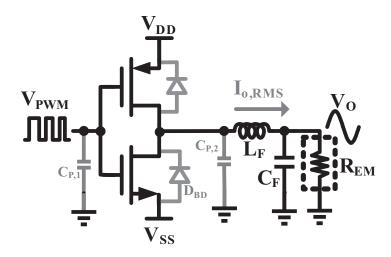

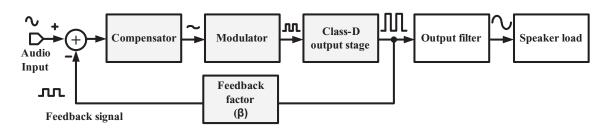

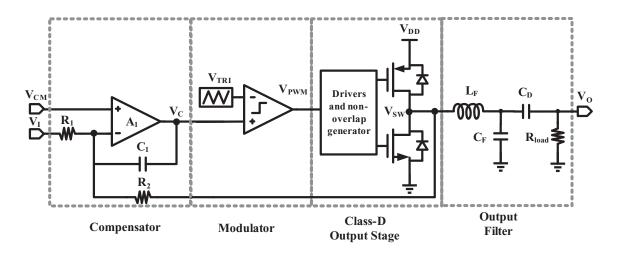

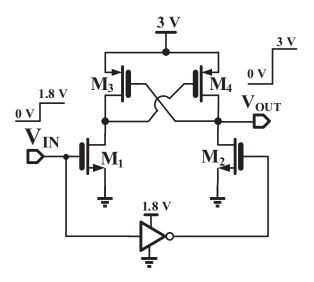

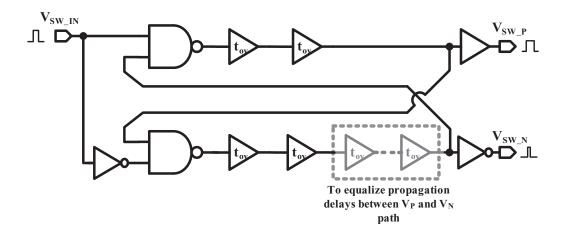

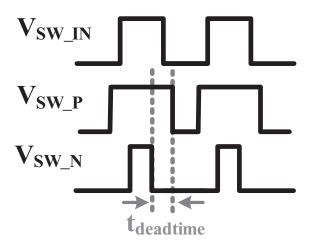

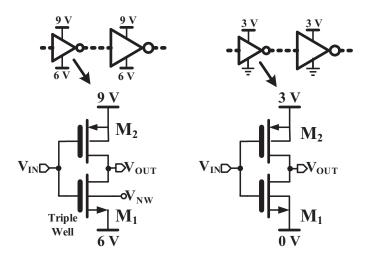

Section 4 presents a feed-forward cancellation technique for single-ended class-D audio amplifier architectures to improve the PSRR performance with low power consumption, as illustrated in Fig. 1.1. The design methodology, implementation, and tradeoffs of the proposed technique are clearly delineated to demonstrate its simplicity and effectiveness. Simulation and experimental results are provided to verify the correct operation of the proposed technique.

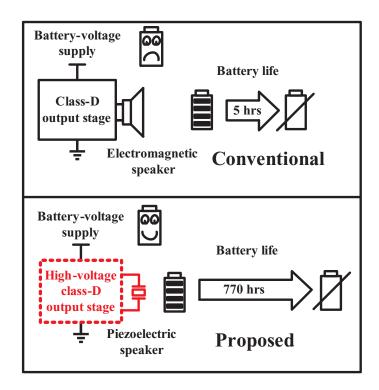

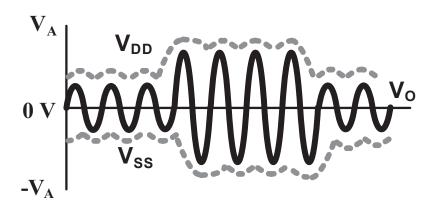

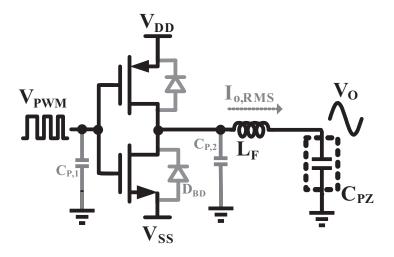

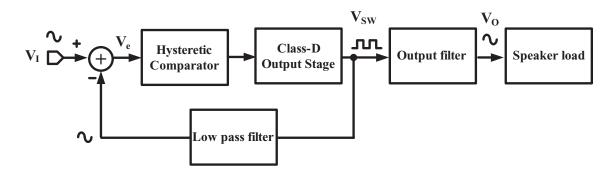

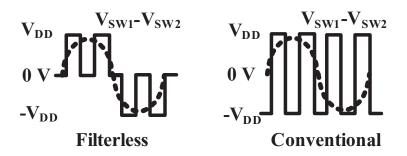

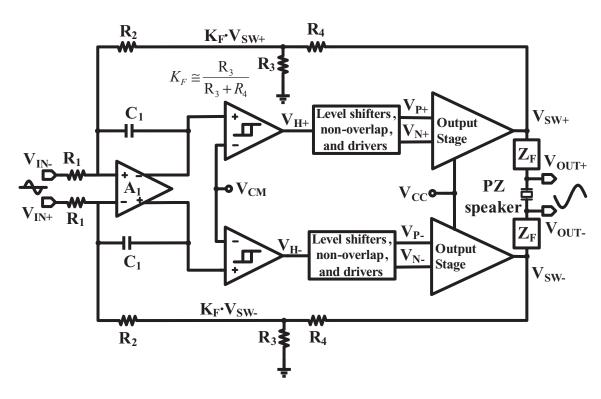

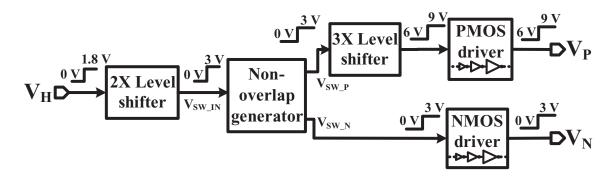

Figure 1.2: Proposed solution to drive piezoelectric speakers (Section 5).

Section 5 introduces a new CDA for driving PZ speakers to extend battery life, as depicted in Fig. 1.2. The PZ speaker's small form factor and low power consumption provide an attractive alternative for conventional loudspeakers. The design tradeoffs of the CDA for driving PZ speakers are examined. A new monolithic implementation is

proposed that uses stacked-cascode thick-oxide CMOS transistors at the class-D output stage, avoiding expensive high-voltage semiconductor devices to handle high voltages in a low voltage standard CMOS technology. The design methodology, implementation, and tradeoffs are provided as well as the experimental results.

The open problems in audio amplification for mobile devices are explained in Section 6 to describe the CDA trends to reduce the cost and EMI of the amplifier; audio CODEC processors are briefly explained to leverage the understanding of the CDA to apply it for low power low voltage analog-to-digital converters. Section 7 summarizes this dissertation. Appendix A is included to briefly detail the operation of a class-G amplifier with a proposed solution to increase the linearity of the amplifier during supply transitions with low power consumption. Appendix B presents more details for a non-linear controller in the class-D amplifier to achieve high PSRR using integral sliding mode control.

#### 2. FUNDAMENTALS AND METRICS OF AUDIO AMPLIFICATION

#### 2.1 Principles of sound and audio

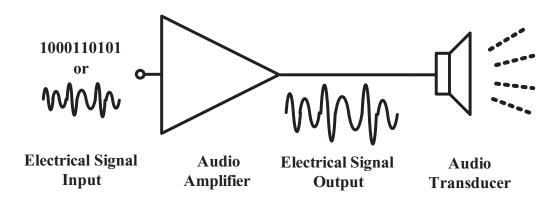

An audio amplifier is a device that takes an input electrical signal representing the desired audio information, amplifies it, and delivers it to a transducer that converts the electrical signal back to audio as described in Fig. 2.1. The input signal can be either digital or analog, but the output signal has to be analog since the audio transducer only operates with continuous time signals.

The main objective of the audio amplifier is to accurately drive the audio transducer with the amplified output signal. To understand the tradeoffs involved in the design of audio amplifiers, it is useful to review the basics on sound and audio signals.

#### 2.1.1 Sound and audio definition

Sound is typically defined as a mechanical pressure wave that propagates through a medium such as air or water. It originates from a vibration source that displaces the medium particles in a backward and forward motion. This pattern is characterized with some generic properties such as wavelength, period, amplitude, and direction.

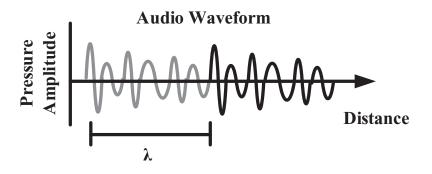

The wavelength of the audio waveform  $(\lambda)$  is the distance that the sound travels in a single direction along a medium in a repeating pattern between consecutive points of the same phase as observed in Fig. 2.2. The typical audio signal contains many different wavelengths with distinct amplitudes, but is typically simplified as a collection of sinusoidal waves. The frequency of the signal, expressed in cycles per second, is expressed as,

$$f = \frac{c}{\lambda} \tag{2.1}$$

where c is the velocity of sound that in air takes the value of 331.45 m/s.

The fundamental frequency of the audio waveform is the greatest common divisor of the frequency of all the different frequency components of the signal. The typical audio frequency spectrum that is perceptible by humans ranges from 20 Hz to 20 kHz, or wavelengths from 16.5 mm to 16.5 m. However, most of the applications in mobile devices do not require the full range; voice communication only contain signals in the 300 Hz to 3 kHz range, and music reproduction could contain signals from 20 Hz up to 5 kHz for different music styles.

Figure 2.1: Audio amplifier operation.

Figure 2.2: Audio waveform across distance.

The high end of the audio frequency spectrum (5 kHz up to 20 kHz) is rarely processed in mobile devices since it is only used in highly specialized professional audio applications like orchestra music reproduction.

## 2.1.2 Sound pressure level

The loudness of the sound wave has been difficult to characterize since each individual perceives the sound pressure differently, depending on age, lifestyle, health, among other circumstances. Therefore, a more formal metric is used to define how strong a sound wave is by measuring the difference, in a given medium, between a reference pressure ( $P_{ref}$ ) and the pressure in the sound wave ( $P_{wave}$ ).

The unit to measure pressure is defined as a pascal ( $P_a = 1 N/m^2$ ). As the human ear can detect sounds with a wide range of amplitudes, the sound pressure is often measured using a logarithmic scale such as the decibel. Therefore, the sound pressure level (SPL) can be defined as,

$$SPL = 20\log 10 \frac{P_{wave}}{P_{ref}} \tag{2.2}$$

where  $P_{ref} = 20\mu Pa$  is typically used since it is considered the threshold of human hearing for the sound propagating through air. The SPL can be measured using an instrument called a sound level meter [11] that senses the changes in pressure using a calibrated microphone and interprets the pressure difference to give a readout in the selected range. High SPL extended exposure can deteriorate a person's hearing by damaging sensitive inner-ear organs.

The typical SPL for conversational speech at 1m is 60 dB, while for a rock concert at 1m of the speaker is 100 dB; in mobile devices, the SPL performance can range from 60 dB up to 120 dB at short distances [12, 13, 14]. Other SPL examples are tabulated in table 2.1 for different scenarios.

The importance of the SPL is that it gives a metric to compare different audio transducers for different scenarios. The overall audio system loudness will depend on how much SPL the system can produce at a given distance.

Table 2.1: SPL example levels

| Example                | SPL (dB) at 1 m |

|------------------------|-----------------|

| Rustling of leaves     | 20              |

| Quiet room             | 40              |

| Conversation           | 60              |

| Road with busy traffic | 80              |

| Noisy factory          | 90              |

| Construction truck     | 100             |

| Jet engine             | 120             |

| Threshold of pain      | 140             |

# 2.2 Loudspeaker transducers in mobile devices

The audio reproduction function in mobile devices can be classified in two applications. First, small audio transducers are used in headphone applications where the sound wave only travels a few centimeters into the ear canal; these are used commonly for handsfree conversations and music listening. Second, moderate audio transducers are used as loudspeakers for video conferences, video games, and other applications where the sound wave has to travel a few meters.

The electric impedance of the speakers used in these applications greatly influences the design of the audio amplifier. Thus, an understanding of their physical construction and operation is needed to analyze their limitations and tradeoffs.

## 2.2.1 Electromagnetic speaker

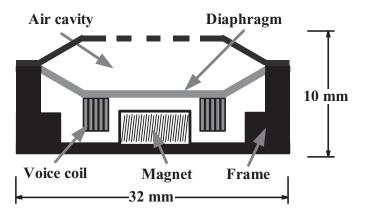

The preferred speaker is the electromagnetic (EM) speaker, consisting of a magnet, a voice coil, and an acoustic cavity, as shown in Fig. 2.3. However, a large form factor is required in the EM speaker to deliver high SPL [15]. The typical materials used for the EM speaker construction are copper for the voice coil, plastic for the diaphragm, acrylonitrile butadiene styrene (ABS) for the frame, and Neodymium for the magnet. It operates by applying an electrical current through the voice coil to induce an electromagnetic field which in turn will generate a displacement of the acoustic diaphragm. Since the electromagnetic coupling factor is very small between the amount of electric current consumed to the amount of magnetic field produced, a large magnet and wide air cavity are needed to produce sound [11, 16].

Figure 2.3: EM speaker physical structure side view.

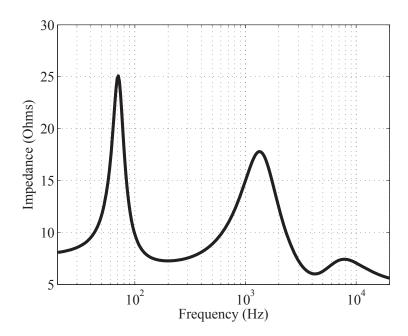

The electrical impedance of a typical EM speaker across the audio frequency bandwidth is shown in Fig. 2.4. It can be observed that, on average, it behaves as a low value impedance between 4 to 32  $\Omega$ . A typical impedance value for most EM loudspeakers is 8  $\Omega$  while for EM headphones it is 32  $\Omega$ .

This means, that the amplifier has to output large electrical current through the voice coil to generate high SPL.

Figure 2.4: EM electrical impedance versus frequency.

An interesting point to note is that the EM speaker's low impedance requires large output power to operate, quickly consuming the battery life of mobile devices. For example, to produce 90 dB of SPL from an 8  $\Omega$  EM speaker, the battery has to provide around 1 W of average power or 353 mA of load current [15, 17, 18]. The battery life can be calculated as,

$$Battery \ life \ (hours) = \frac{Battery \ capacity \ (mAh)}{Load \ current \ (mA)}. \tag{2.3}$$

If a typical lithium-ion battery with 2000 mAh capacity is used with an ideal 100% efficient audio amplifier, the battery life only considering the EM speaker current consumption would be 5.67 hours.

In real applications, the audio amplifier current consumption would also be included in the calculation, decreasing even more the battery life; typical current consumption for audio amplifiers in mobile applications range from 1 mA to 10 mA. Thus, EM loudspeakers limit the battery life despite the audio amplifier's high efficiency and low current consumption.

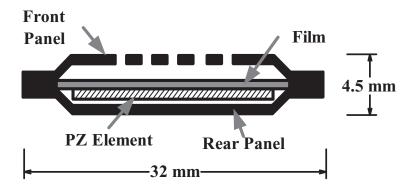

#### 2.2.2 Piezoelectric speaker

The physical structure of a typical PZ speaker is shown in Fig. 2.5 where a PZ element is attached to a film encased between a front panel and rear panel. Typical materials used for its construction are polycarbonate for the front and real panel, plastic resin or metal for the film, and lead zirconate titanate for the PZ element. The PZ element deflects with voltage applied across its terminals, causing the film to warp and bend up and down according to the voltage applied across the PZ element. The deflecting/bending action creates pressure waves pushing air through one or more openings that are arranged on the front panel that resonate and amplify the response of the speaker.

Figure 2.5: PZ speaker physical structure side view.

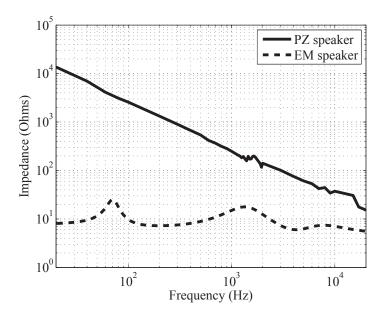

The PZ element in the speaker is typically a multilayer ceramic component that behaves electrically as a capacitor across the audio frequency bandwidth [19]. Fig. 2.6 shows the measured impedance versus frequency of a typical PZ speaker in comparison to the EM speaker impedance. It can be observed that for most of the audio frequency spectrum, the PZ speaker has an impedance orders of magnitude larger than the EM speaker impedance. This allows the audio amplifier to use very low power to operate the speaker, improving the battery life of mobile devices.

The capacitive behavior of the PZ speaker is highly reactive, meaning that the energy applied to the transducer is stored and most of it is returned to the supply each signal cycle. Ideally, this will allow almost no average power consumption from the battery, but the PZ speaker has some dielectric losses in the ceramic material that will dissipate some power as heat. Typical dissipation factors range from 0.4% up to 1% with quality factors > 50 for most PZ speakers available.

Figure 2.6: PZ and EM speakers impedance versus frequency comparison.

The following example will illustrate the PZ speaker's low power consumption. To produce the same 90 dB of SPL from the PZ speaker with a 338  $\Omega$  equivalent impedance at 1 kHz and dissipation factor of 1%, the battery only needs to provide 1.2 mW of average power or 133  $\mu$ A of load current, as will be detailed in Section 5. If the same lithium-ion battery with 2000 mA/h capacity is used solely for the audio amplifier driving the PZ speaker, the battery life calculated using (2.3) would be 15,000 hours. That is a battery life extension of 2645x times compared to the EM speaker. However, in real applications, the audio amplifier current consumption would be dominant, limiting the battery life. If the amplifier has a current consumption of 2.46 mA, the real battery life would be 770 hrs. The PZ speaker provides low power consumption and high SPL, making it an attractive alternative for mobile devices, especially when used with low power high efficiency audio amplifiers.

Typical voltage levels across the PZ speaker terminals should be in the range of 10-20  $V_{pp}$  to achieve the maximum SPL, and could be generated from the battery using high-efficiency step-up voltage circuits [20, 21, 22]. Commercial audio amplifiers for PZ speakers provide high-voltage outputs using these circuits, but their distortion and power consumption is still large [23, 24, 25, 26]. Thus, new circuits for PZ speakers that dissipate less power and produce less distortion are desirable. Section 5 introduces a new audio amplifier for PZ speakers that addresses these issues.

#### 2.3 Performance metrics of audio amplifiers

To determine the quality of an amplifier, it is necessary to understand the main performance metrics in the audio amplification process. The metrics will be used in each proposed work throughout this dissertation to compare the obtained results with the state-of-the-art. The most used signal to measure these metrics is a sinusoidal waveform, typically at 1 kHz.

This is because a sinewave behaves as a single tone in the frequency domain, and its frequency harmonics up to the 20th harmonic are within the audio frequency band. Thus, they are easy to identify and use for various performance metrics.

#### 2.3.1 Total harmonic distortion plus noise

The total harmonic distortion plus noise (THD+N) metric measures the amount of distortion that is generated by the amplification process compared with the fundamental input frequency, including the total noise produced by the amplifier. The THD+N is defined as the ratio of the fundamental frequency power to the sum of the harmonics power plus noise power as,

$$THD + N = \sqrt{\sum_{i=2}^{N} \frac{V_i^2}{V_1} + \frac{V_n^2}{V_1}}$$

(2.4)

where  $V_i$  is the RMS voltage of the *n*th harmonic,  $V_n$  is the integrated noise RMS voltage in the bandwidth of interest, and  $V_1$  is the fundamental frequency RMS voltage. If the noise is not accounted and only the linearity is of interest, then a total harmonic distortion (THD) calculation can be used as,

$$THD = \sqrt{\sum_{i=2}^{N} \frac{V_i^2}{V_1}}.$$

(2.5)

The THD+N metric is the most accepted definition for audio quality of the system since real amplifiers will have noise that is not accounted in the THD metric. For example, for different amplifiers that have the same THD but they operate at different power levels, a large  $V_1$  would reduce the effect of  $V_n$  in the THD+N; but for a small  $V_1$ , the contribution of  $V_n$  is larger, increasing the THD+N, as observed in (2.4). Thus, using the THD metric to compare amplifiers with different output power levels would be unfair.

The THD+N is typically measured against a sweep of output amplitudes for a single signal frequency, or for a sweep of frequencies from 20 Hz to 20 kHz for a single output amplitude. Since the THD+N varies several orders of magnitudes, the measured value can be expressed in logarithmic scale or percentage as expressed in table 2.2.

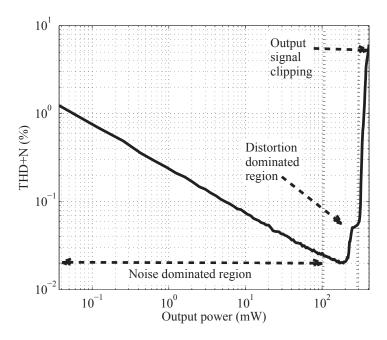

Figure 2.7: THD+N typical plot against output power for audio amplifiers.

Table 2.2: THD+N measurement units

| Decibel (dB) | Percentage (%) |

|--------------|----------------|

| 0            | 100 %          |

| -20          | 10 %           |

| -40          | 1 %            |

| -60          | 0.1 %          |

| -80          | 0.01 %         |

| -100         | 0.001 %        |

A typical THD+N plot against the output power for a 1 kHz signal is illustrated in Fig. 2.7, where 3 regions can be identified. The first region is at low output powers where the THD+N value is dominated by the noise of the circuit. The second region is at medium to high output power where the THD+N value is dominated by the distortion of the output signal. The third region is when the output signal amplitude reaches the supply voltage value and it starts to clip, increasing the distortion drastically as observed in Fig. 2.7.

Other frequency tones can be used to compare the THD+N of an audio amplifier for a fixed output amplitude. A special case is for a 6.6 kHz input signal since the output THD+N would be dominated by the third harmonic ( $V_3$ =19.8 kHz) that is at the high limit of the audio frequency spectrum. This test signal gives the worst case scenario THD+N number of the amplifier. Typical THD+N values for commercial audio amplifiers in mobile devices range from -65 dB to -110 dB.

## 2.3.2 Signal to noise ratio

The signal to noise ratio (SNR) is a metric that defines the ratio of the signal power to the noise power of the amplifier. Noise sources come from the power supply hum (60 Hz), switching noise, thermal noise from the circuit components in the amplifier, and radio frequency interference. The audio amplifier noise floor integrated over the audio frequency spectrum is typically used for the measurement. The SNR can be expressed as,

$$SNR = 10\log\frac{P_o}{P_n} \cong 20\log\frac{V_o}{V_n}$$

(2.6)

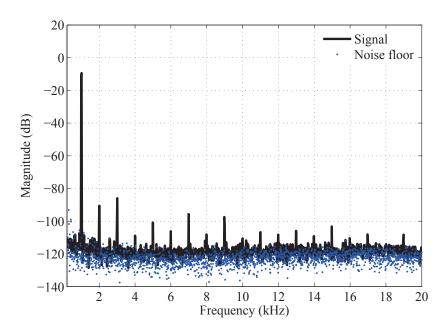

where  $V_o$  is the output voltage amplitude of the fundamental frequency of the audio signal, and  $V_n$  is the integrated output noise of the amplifier. Fig. 2.8 shows a typical frequency spectrum for an audio amplifier where the noise floor and the signal harmonics can be observed. The noise floor is obtained by measuring the output of the audio amplifier with no audio signal.

## 2.3.3 Power supply rejection ratio

The power supply rejection ratio (PSRR) is a metric that defines the ratio between the output signal to the noise signal introduced by the supply of the amplifier. This metric is important since battery-powered devices share the audio amplifier's power supply plane with the same noisy power supply plane of digital circuits. The supply noise mixes with the audio and carrier signals, degrading the overall THD+N performance. Moreover, the supply noise rejection needs to be high over the whole audio frequency spectrum, to avoid a degradation of the THD+N. Since the supply noise could be orders of magnitude smaller than the output signal, the PSRR is typically expressed in decibels as,

$$PSRR = 20\log \frac{V_n}{V_o} = 20\log V_n - 20\log V_o.$$

(2.7)

Figure 2.8: Typical output frequency spectrum for audio amplifiers.

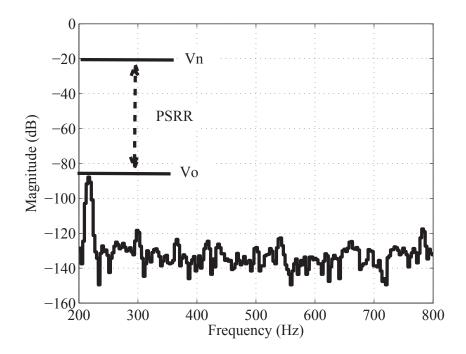

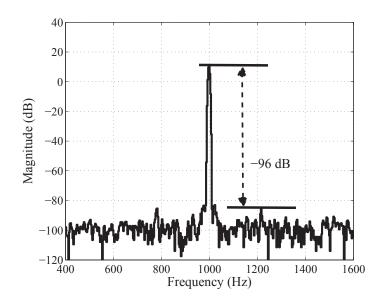

This metric is measured when there is no audio signal present (idle condition) and the noise signal is swept across the audio frequency spectrum. A special case is for the noise signal at 217 Hz; this tone is especially important for audio amplifiers in cell phone devices since it represents the GSM burst used for the device communication. Therefore, if the audio amplifier is intended for a cell phone application, it must have a high PSRR performance also at low frequencies.

Figure 2.9: PSRR measurement example for a noise signal at 217 Hz with -20 dB amplitude.

Fig. 2.9 illustrates a sample PSRR measurement where an input -20 dB tone signal at 217 Hz is applied to the amplifier, and the output signal frequency spectrum is used to extract the signal output, supply noise, and PSRR values.

Since the plot shows the value in logarithmic scale, the PSRR is the difference between the Vo and Vn in decibels that for this example is around 65 dB. The PSRR performance of the audio amplifier is highly dependent on the topology of the amplifier and the output stage connecting the battery supply to the output.

## 2.3.4 Power supply intermodulation distortion

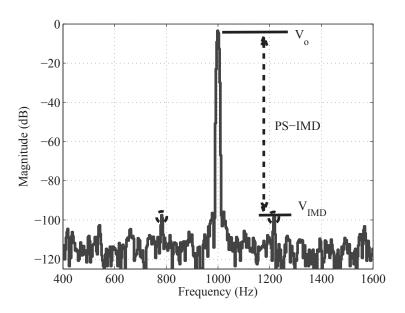

The PSRR metric characterizes the supply noise rejection at the idle condition when no audio signal is present. However, during normal operation, the supply noise and the audio signal are present in the amplifier. The power supply intermodulation distortion (PS-IMD) measures the interaction between the noise and audio signals. The PS-IMD is the amplitude modulation between noise and audio signals at different frequencies. The intermodulation products occur since all amplifiers are non-linear circuits that generate harmonics, and they are located at multiples of the sum and difference frequencies of the audio and noise signal frequencies.

The PS-IMD can be measured from the frequency spectrum of the output signal, as show in Fig. 2.10, where an audio signal at 1 kHz and a noise signal at 217 Hz generate two dominant intermodulation products at 783 Hz and 1217 Hz. The PS-IMD can be expressed as the magnitude ratio between the intermodulation products to the fundamental as,

$$PS - IMD = 20\log \frac{V_o}{V_{IMD}} = 20\log V_o - 20\log V_{IMD}$$

(2.8)

where  $V_{IMD}$  is the intermodulation product amplitude, and  $V_o$  is the fundamental audio signal amplitude. The PS-IMD metric is highly correlated with the linearity of the system and its PSRR performance. If the amplifier has poor PSRR and high distortion, then the PS-IMD will be poor.

## 2.3.5 Power efficiency

One of the most important metrics for audio amplifiers in mobile devices is the power efficiency  $(\eta)$ . This metric represents how much of the energy provided by the battery is effectively used for the intended purpose of audio amplification. In other words, if the audio amplifier consumes/dissipates power due to its biasing or power loss, then the efficiency will be less than 100 %.

The power efficiency is typically estimated as the output power divided by the input (supply) power, using the average power definition over a sinewave signal period ( $T = 2\pi/\omega$ ) as,

$$P_{avg} = \frac{1}{T} \int_0^T v(t) \cdot i(t) \cdot dt = V_{RMS} \cdot I_{RMS} \cdot \cos(\varphi)$$

(2.9)

where the phase angle between the current relative to the voltage is represented by  $\varphi$ .

Figure 2.10: PS-IMD measurement example for a noise signal at 217 Hz and audio signal at 1 kHz.

For an EM speaker, the load appears as almost resistive, and the term  $\cos(\varphi)$  in the output power is close to one, meaning that the voltage and current are in phase, and the power is being dissipated in the load, as observed in the average power in Fig. 2.11. Therefore, the power efficiency for EM speakers could be defined as [27],

$$\eta = \frac{P_{o,avg}}{P_{i,avg}} = \frac{P_{o,avg}}{P_{o,avg} + P_{loss,avg}} = 1 - \frac{P_{loss,avg}}{P_{i,avg}}$$

(2.10)

where the  $P_{o,avg}$  is the average output power delivered to the load,  $P_{i,avg}$  is the average input power consumed from the battery, and  $P_{loss,avg}$  is the average power loss in the audio amplifier. In general, most of the audio amplifier applications are targeted for EM speakers; thus, this efficiency definition is typically used.

Figure 2.11: Instantaneous and average power for a EM speaker with  $\varphi < 15^{\circ}$ .

The PZ speaker is a highly reactive speaker alternative that offers very low power consumption, as discussed in Section 2.2.2.

Its capacitive nature needs a different definition of power efficiency since the current leads the voltage by almost 90 degrees, causing the term  $\cos(\varphi)$  to be close to zero, and appearing as if very little power is being dissipated by the load, as observed in the average power in Fig. 2.12. This happens because the energy supplied by the battery is stored in the reactive load and returned to the battery each cycle. If the average output power is used for the efficiency definition in (2.10), the efficiency will appear very low [28].

Another alternative is to define the efficiency in terms of energy transfer between the supply and load [29, 30]. However, the energy analysis requires an estimation of the energy for each switching cycle, making it a complex procedure. A more suitable definition of the amplifier's power efficiency for capacitive transducers has been proposed in [31, 32, 33], where the apparent power is used for the efficiency calculation.

The apparent power, measured as  $P_{app} = V_{RMS} \cdot I_{RMS}$ , is the magnitude of the complex power vector which contains the information of the reactive power and the average or real power, as observed in Fig. 2.13. The complex power is the general representation for the

Figure 2.12: Instantaneous and average power for a PZ speaker with  $\varphi \cong 90^{\circ}$ .

voltage and current product, and it can be expressed as,

$$\vec{P}_{comp} = \vec{P}_{av} + \vec{P}_{reac} = \vec{P}_{comp} \cos \varphi + \vec{P}_{comp} \sin \varphi. \tag{2.11}$$

Thus, the amplifier's power efficiency for capacitive loads is defined as [32, 33, 31],

$$\eta_{PZ} = \frac{P_{o,app}}{P_{i,app}} = \frac{P_{o,app}}{P_{o,app} + P_{loss,app}} = \frac{1}{1 - \frac{P_{loss,app}}{P_{o,app}}}$$

(2.12)

$$P_{o,app} = V_{o,RMS} \cdot I_{o,RMS} \cong \frac{V_{o,RMS}^2}{|Z_L(j\omega)|}$$

(2.13)

where  $Z_L(j\omega)$  is the equivalent impedance of the PZ speaker at the operating frequency. This efficiency definition states that the amplifier has to process the apparent power required by the PZ speaker with the minimum power dissipation. In other words, the average input power reflects the power dissipation of the system. This is important since the audio amplifier has to be designed for a large capacitive load with low power dissipation. More details about the amplifier design for PZ speakers and its efficiency is addressed on Section 5.

Figure 2.13: Complex power definition.

# 2.4 Audio amplifier classification

The audio amplifier can process the audio signal as a linear operation continuously in time and amplitude, or as a non-linear operation continuously in time but discretely in amplitude. The linear audio amplifiers process the signal with an output stage configured as a current source, while the non-linear audio amplifiers have a switching output stage that process the signal with a modulation scheme.

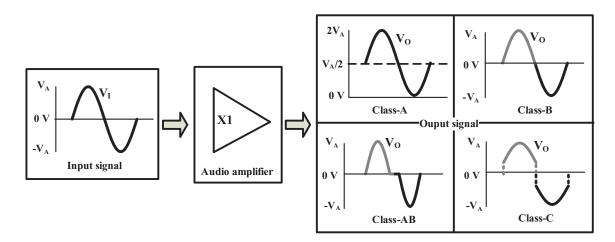

Figure 2.14: Main linear amplification classes.

The main linear amplification classes are summarized in Fig. 2.14. The audio amplifier is typically configured as a voltage follower with enough output current to drive the impedance of the speaker. The main amplifier linear classes are the class-A, class-B, class-AB, and class-C. The linear amplifiers' biasing point defines the range of the input signal that they can amplify at the output with a tradeoff between linearity and power dissipation.

The class-A amplifier outputs 100% of the signal swing, providing minimum distortion; but, its output stage biasing point is placed at half the maximum amplitude of the signal, dissipating large power.

The class-B amplifier's biasing point is chosen to output only 50% of the signal swing; the small biasing point decreases the power consumption, but at the expense of large distortion. The class-AB operation combines the reduced power dissipation and low distortion of the class-B and class-A, respectively; but, it requires a complex biasing scheme to operate [34, 35]. The class-C amplifier's biasing point is chosen to output less than 50% of the output swing to lower the power dissipation drastically; however, its high distortion prohibits its use for audio applications.

Other more advanced amplifier classes have been proposed to increase the power efficiency of linear amplifiers such as the class-G and class-H. The class-G amplifier provides better power efficiency compared with the class-AB operation [36, 37, 38]. The efficiency improvement is achieved by reducing the supply voltage for smaller output signals, and thus, reducing the power dissipation. The power-supply transition is achieved without affecting the dynamic range of the output signal, as observed in Fig. 2.15. However, the distortion during the supply transition can be detrimental in the performance of the amplifier. The detailed class-G operation and a case study to minimize the supply-transition distortion are presented in Appendix A.

Figure 2.15: Class-G amplifier operation.

The class-H amplifier operates in a similar way as the class-G amplifier by continuously changing the supply voltages as observed in Fig. 2.16. The smooth supply transitions allow very low distortion and improved efficiency in the amplification process since the supply is high only when needed by the signal. However, a dedicated power management circuit is required to adapt the supply voltages according to the input signal, degrading the overall efficiency benefits, and increasing the cost and power consumption of the audio amplifier.

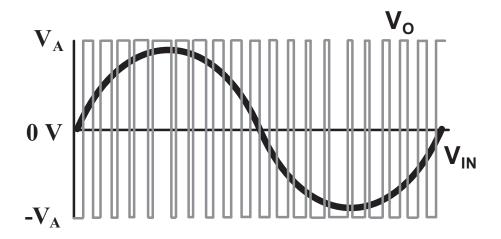

Figure 2.16: Class-H amplifier operation.

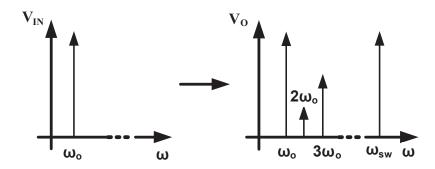

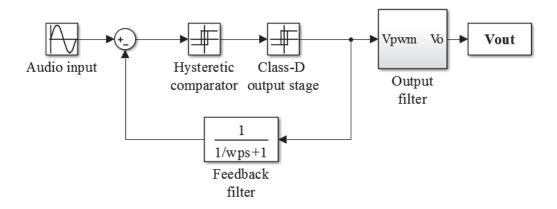

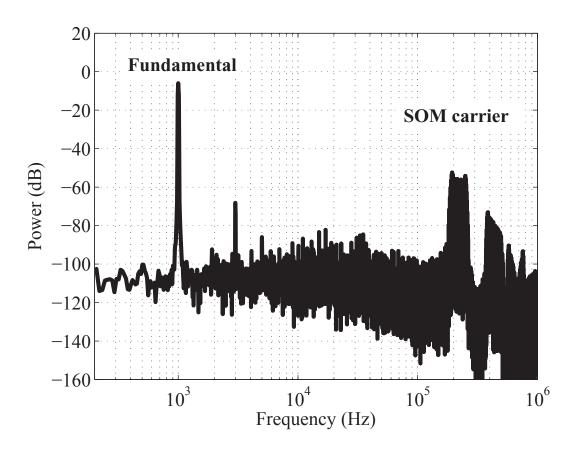

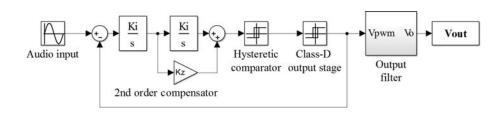

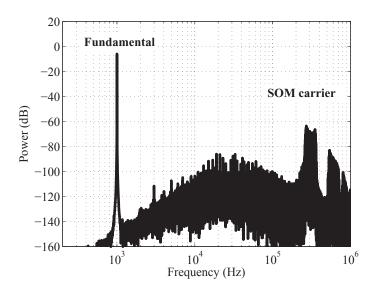

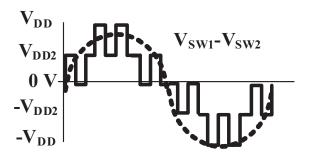

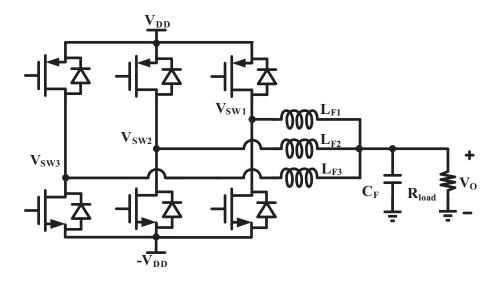

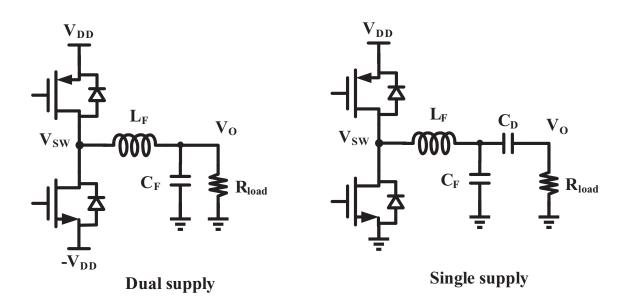

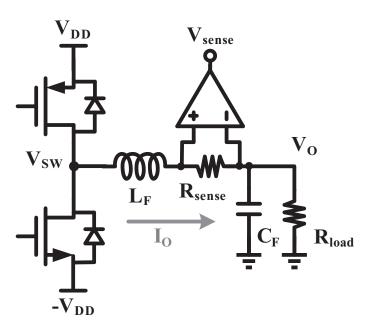

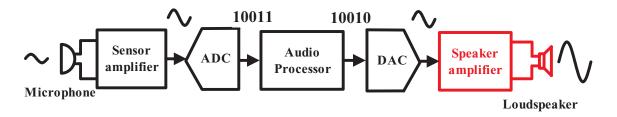

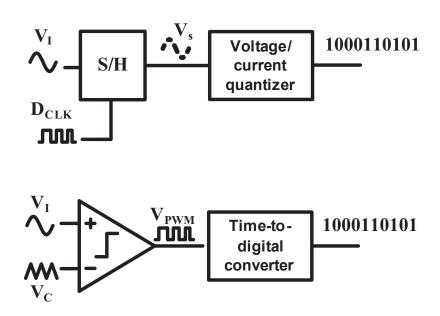

The class-G and class-H amplifiers improve the power efficiency of the amplifier by switching the supply voltage for different levels of output signal. However, the biasing's power dissipation still exist during the amplification process. Another alternative is to keep a fixed supply voltage but switch the output signal between the supply voltages to operate the output stage as a digital switch. This operation is known as a class-D operation, where the continuous input signal is modulated by a high frequency carrier that generates a stream of pulses that are applied to the load, as observed in Fig. 2.17.