# CIRCUIT AND SYSTEM LEVEL DESIGN OPTIMIZATION FOR POWER DELIVERY AND MANAGEMENT

A Dissertation

by

### TONG XU

# Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

| Chair of Committee, | Peng Li           |

|---------------------|-------------------|

| Committee Members,  | Paul V. Gratz     |

|                     | Rabi N. Mahapatra |

|                     | Aniruddha Datta   |

| Head of Department, | Chanan Singh      |

December 2014

Major Subject: Computer Engineering

Copyright 2014 Tong Xu

### ABSTRACT

As the VLSI technology scales to the nanometer scale, power consumption has become a critical design concern of VLSI circuits. Power gating and dynamic voltage and frequency scaling (DVFS) are two effective power management techniques that are widely utilized in modern chip designs. Various design challenges merge with these power management techniques in nanometer VLSI circuits. For example, power gating introduces unique power integrity issues and trade-offs between switching noise and rush current noise. Assuring power integrity and achieving power efficiency are two highly intertwined design challenges. In addition, these trade-offs significantly vary with the supply voltage. It is difficult to use conventional power-gated power delivery networks (PDNs) to fully meet the involved conflicting design constraints while maximizing power saving and minimizing supply noise. The DVFS controller and the DC-DC power converter are two highly intertwining enablers for DVFS-based systems. However, traditional DVFS techniques treat the design optimizations of the two as separate tasks, giving rise to sub-optimal designs.

To address the above research challenges, we propose several circuit and system level design optimization techniques in this dissertation. For power-gated PDN designs, we propose systemic decoupling capacitor (decap) optimization strategies that optimally trade-off between power integrity and leakage saving. First, new global decap and re-routable decap design concepts are proposed to relax the tight interaction between power integrity and leakage power saving of power-gated PDN at a single supply voltage level. Furthermore, we propose to leverage re-routable decaps to provide flexible decap allocation structures to better suit multiple supply voltage levels. The proposed strategies are implemented in an automatic design flow for choosing optimal amount of local decaps, global decaps and re-routable decaps. The proposed techniques significantly increase leakage saving without jeopardizing power integrity. The flexible decap allocations enabled by re-routable decaps lead to optimal design trade-offs for PDNs operating with two supply voltage levels.

To improve the effectiveness of DVFS, we analyze the drawbacks of circuit-level only and policy-level only optimizations and the promising opportunities resulted from the cross-layer co-optimization of the DC-DC converter and online learning based DVFS polices. We present a cross-layer approach that optimizes transition time, area, energy overhead of the DC-DC converter along with key parameters of an online learning DVFS controller. We systematically evaluate the benefits of the proposed co-optimization strategy based on several processor architectures, namely single and dual-core processors and processors with DVFS and power gating. Our results indicate that the co-optimization can introduce noticeable additional energy saving without significant performance degradation.

# DEDICATION

To my wife, Fangfang, and my parents.

#### ACKNOWLEDGEMENTS

This material is based upon work supported by the National Science Foundation under Grants No. 0903485 and No. 0747423 and SRC under Contract 2009-TJ-1987.

Looking back the five years of my PhD life, I have my greatest gratitude to the professors who guided me in the academic work and the friends who cheered me up.

My adviser, Dr. Peng Li, has been a great inspiration. My first thanks goes to him. I have been very fortunate to be able to work for him. He guided me to dive in the research area. With his endless support and invaluable advice, I learned the ways of how to analyze the problems and how to build concrete steps towards solving them. All of those experience added greatly to this thesis. I would also like to thank Dr. Li for always being patient and stimulating my potentials. His support is instrumental for me throughout my course of study.

Thanks also to Dr. Paul V. Gratz, Dr. Rabi N. Mahapatra, Dr. Aniruddha Datta, and Dr. Rabi N. Mahapatra who gave me suggestions and ideas of improvements of my work. The interesting discussion and helpful feedback encouraged me to pursue perfection. Their astute and challenging comments make this dissertation stronger.

Thanks for all my colleague and friends who helped me along the road, especially Boyuan Yan, Suming Lai, Zhiyu Zeng and Leyi Yin. I consider myself lucky to be able to work with them. Their dedication and enthusiasm to the work are the two most important things I have learned. I would also like to thank Dr. Li's research group. It always been enjoyable and rewarding to collaborate with them.

I would also like to thank Hai Lan, Ralf Schmitt, Savithri Sundareswaran, and Brian Mulvaney for showing me the connection between the academia and industry experience. It was a great experience of working in Rambus Inc. and Freescale Semiconductor under the interning programs.

Finally, thanks for my wife, my parents, and my uncle's love and support. Their unconditional love and help gave me the foundation of confidence that I could insist in pursuing doctoral degree and any other challenges in my life. It is to them this work is dedicated.

# TABLE OF CONTENTS

|     |       |                                                              |                                                                                                                                                                                                   | Ρε | age                                                                                |

|-----|-------|--------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------------------------------------------------------------------------------------|

| AB  | STR.  | ACT .                                                        |                                                                                                                                                                                                   |    | ii                                                                                 |

| AC  | KNO   | WLED                                                         | GEMENTS                                                                                                                                                                                           |    | v                                                                                  |

| ТА  | BLE   | OF CC                                                        | ONTENTS                                                                                                                                                                                           |    | vii                                                                                |

| LIS | ST OI | F FIGU                                                       | RES                                                                                                                                                                                               |    | ix                                                                                 |

| LIS | ST OI | F TABI                                                       | LES                                                                                                                                                                                               | X  | viii                                                                               |

| 1.  | INTI  | RODUC                                                        | CTION                                                                                                                                                                                             |    | 1                                                                                  |

|     | 1.1   | Power<br>1.1.1<br>1.1.2                                      | Management Techniques                                                                                                                                                                             |    | $\begin{array}{c} 1 \\ 2 \\ 6 \end{array}$                                         |

|     | 1.2   |                                                              | Dynamic voltage and Frequency Scaling (DVFS)         us Works         Previous Works of Power Gating         Previous Works of DVFS                                                               |    | 0<br>9<br>9<br>10                                                                  |

|     | 1.3   |                                                              | Proposed Solutions on DVFS                                                                                                                                                                        |    | 10<br>11<br>11<br>15                                                               |

| 2.  | DEC   | OUPLI                                                        | ING STRATEGIES FOR POWER GATING                                                                                                                                                                   |    | 16                                                                                 |

|     | 2.1   | Design<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>2.1.5<br>2.1.6 | of Power-Gated PDNs with Single Supply Voltage Background                                                                                                                                         |    | 16<br>17<br>20<br>24<br>34<br>45<br>47                                             |

|     | 2.2   | 2.1.7                                                        | Summary          Power-Gated PDNs with Multiple Supply Voltages          Background          Design Concerns and Trade-Offs          Proposed Diversity Decap Strategy          Optimization Flow |    | <ol> <li>54</li> <li>55</li> <li>55</li> <li>57</li> <li>59</li> <li>62</li> </ol> |

|    |      | $2.2.5 \\ 2.2.6$ | Experimental Results64Summary68                     |

|----|------|------------------|-----------------------------------------------------|

| 3. | SYS  | TEM/C            | CIRCUIT CO-OPTIMIZATION STRATEGIES FOR DVFS 70      |

|    | 3.1  | Design           | n of DVFS for Single-Core Processors                |

|    |      | 3.1.1            | Background                                          |

|    |      | 3.1.2            | Circuit-Level Design                                |

|    |      | 3.1.3            | System-Level Design                                 |

|    |      | 3.1.4            | Opportunities of Circuit/System Co-optimization 79  |

|    |      | 3.1.5            | General Hierarchical Co-optimization                |

|    |      | 3.1.6            | Experimental Results                                |

|    |      | 3.1.7            | Summary                                             |

|    | 3.2  | Design           | n of DVFS for Multi-Core Processors                 |

|    |      | 3.2.1            | Background                                          |

|    |      | 3.2.2            | Opportunities of Circuit/System Co-optimization 110 |

|    |      | 3.2.3            | Experimental Results                                |

|    |      | 3.2.4            | Summary                                             |

|    | 3.3  | Design           | n of DVFS for Power-Gated Processors                |

|    |      | 3.3.1            | Background                                          |

|    |      | 3.3.2            | Circuit-Level Design                                |

|    |      | 3.3.3            | System-Level Design                                 |

|    |      | 3.3.4            | Opportunities of Circuit/System Co-optimization     |

|    |      | 3.3.5            | Experimental Results                                |

|    |      | 3.3.6            | Summary                                             |

| 4. | COL  | NCT US.          | IONS AND FUTURE WORK                                |

| 4. | 001  | ICLUS.           | IONS AND FOTORE WORK                                |

|    | 4.1  | Conclu           | usions                                              |

|    | 4.2  | Future           | e Work                                              |

| RI | EFER | ENCES            | 5                                                   |

# LIST OF FIGURES

Page

# FIGURE

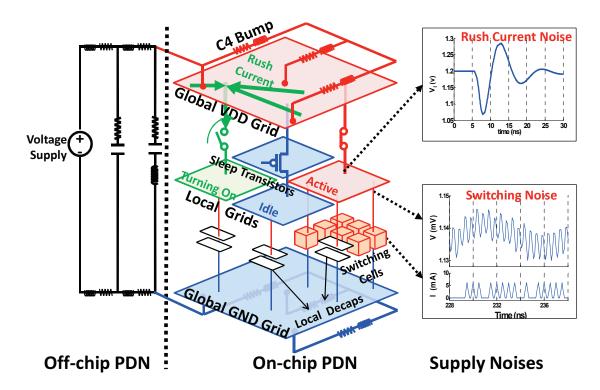

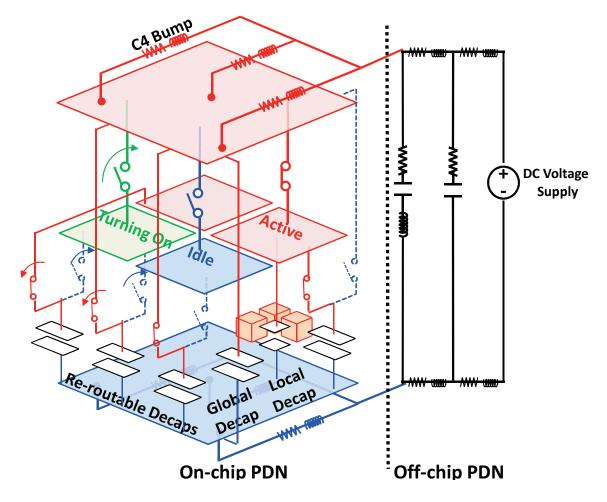

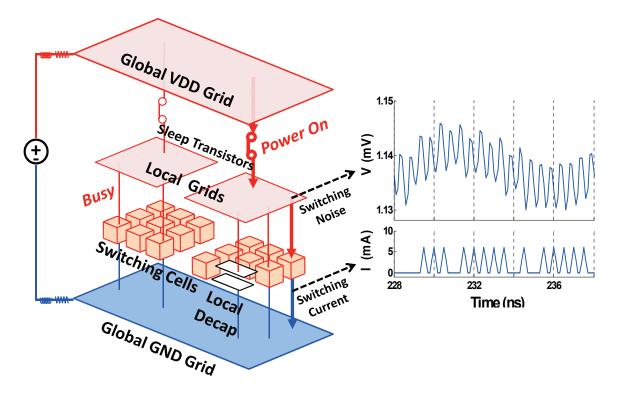

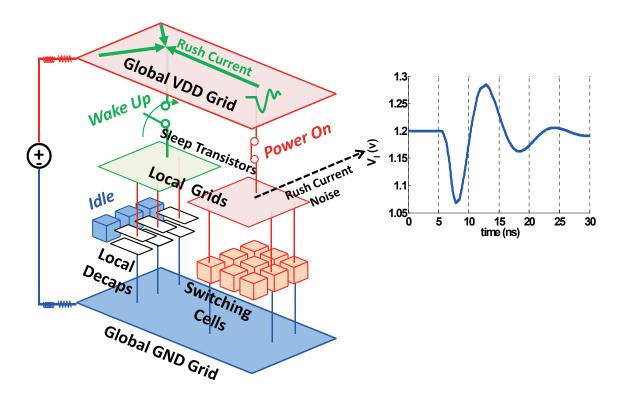

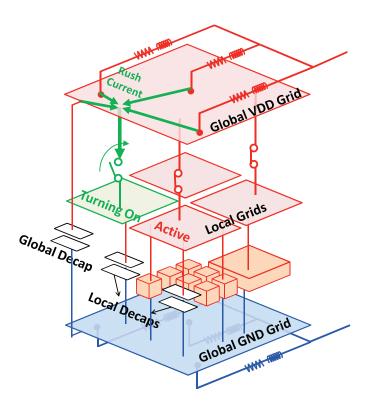

| 1.1 | Typical structure and supply noises of power-gated PDNs. The switch-<br>ing noise is due to switching currents of logic devices. The rush current<br>noise is due to rush currents created to charge up the decaps of a local<br>grid that is woken up.                                                                        | 2   |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

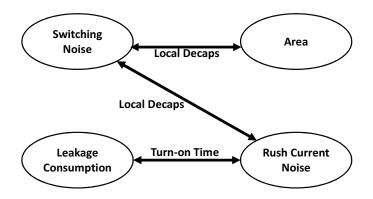

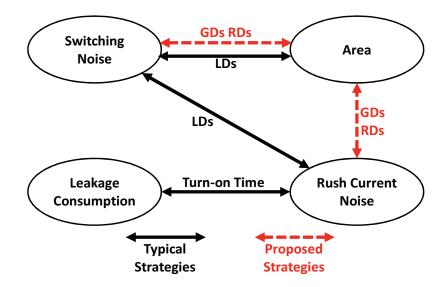

| 1.2 | Design trade-offs and typical strategies of power-gated PDNs with a single supply voltage. The oval-shapes indicate the concerns of a PDN design. The edges indicate the typical strategies to balance design concerns.                                                                                                        | 4   |

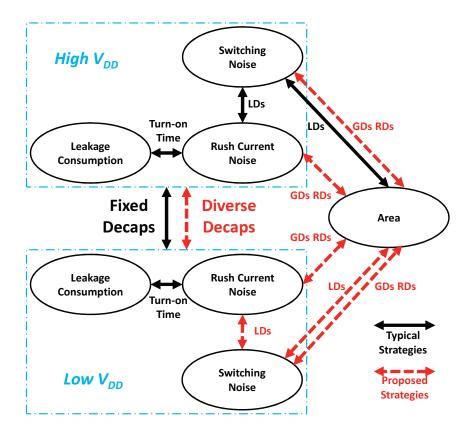

| 1.3 | Design trade-offs and typical strategies of a power-gated PDN with<br>two supply voltages. The oval-shapes indicate the concerns of a PDN<br>design. The edges indicate the typical strategies to balance the design<br>concerns.                                                                                              | 5   |

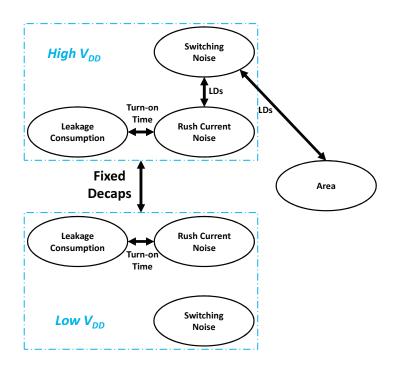

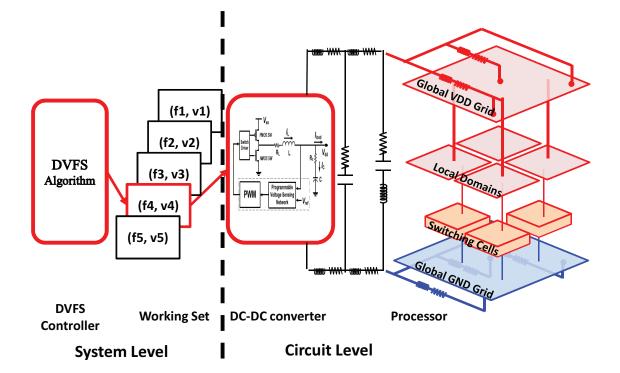

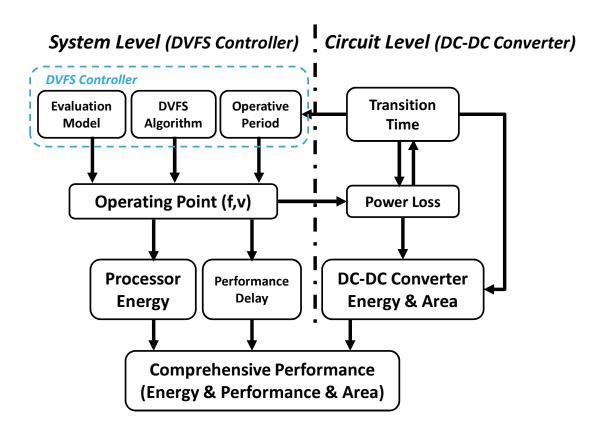

| 1.4 | Typical structure of DVFS system that is composed of a circuit-level DC-DC converter and a system-level DVFS controller.                                                                                                                                                                                                       | 6   |

| 1.5 | Design trade-offs of DVFS at the system level and the circuit level                                                                                                                                                                                                                                                            | 7   |

| 1.6 | Proposed structure of power-gated PDNs. Global decaps and re-<br>routable decaps are utilized in the proposed PDN structure                                                                                                                                                                                                    | 12  |

| 1.7 | Proposed design strategies for power-gated PDN designs with a sin-<br>gle supply voltage. The oval-shapes indicate the concerns of a PDN<br>design. The edges indicate the strategies to balance design concerns.<br>Black solid edges are the typical strategies. Red dash edges are the<br>strategies proposed in this paper | 13  |

| 1.8 | Proposed design strategies for power-gated PDN designs with multi-<br>ple supply voltages. The oval-shapes indicate the concerns of a PDN<br>design. The edges indicate the strategies to balance the design con-<br>cerns. Black solid edges are the typical strategies. Red dash edges are                                   | 1 4 |

|     | the strategies proposed in this paper                                                                                                                                                                                                                                                                                          | 14  |

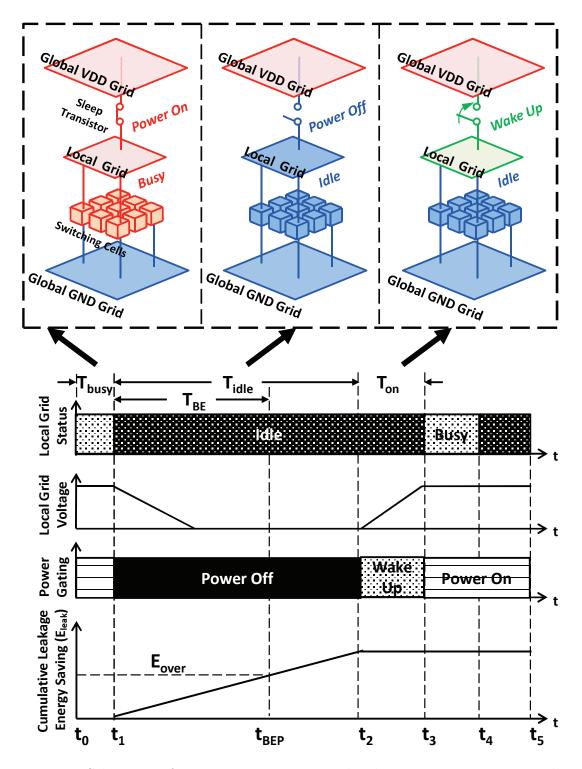

| 2.1 | Schematic of power gating process. The sleep transistor is supposed to be turned off as soon as the idle cycles arrive. $t_{BEP}$ is the break even point at which the energy saving compensates the energy overhead $(E_{leak} = E_{over})$ .                                                                             | 18 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Switching noise of power-gated PDN. The switching noise appears<br>when the local grids are powered on. The switching noise is created<br>by the switching current of logic devices                                                                                                                                        | 21 |

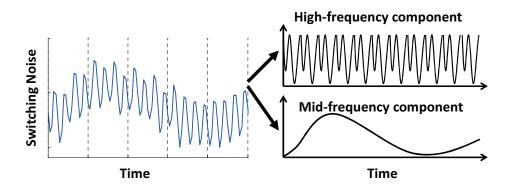

| 2.3 | Components of switching noise. The high-frequency component is due<br>to the IR drop on resistive power grids. The mid-frequency component<br>is due to the resonance from the on-chip capacitance and the package<br>inductance.                                                                                          | 22 |

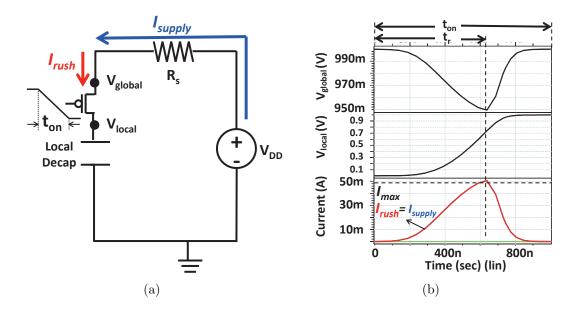

| 2.4 | Rush current noise of power-gated PDN. Rush current noise appears<br>during the wake up process. Rush current noise is due to the rush<br>current created to charge the local decaps                                                                                                                                       | 23 |

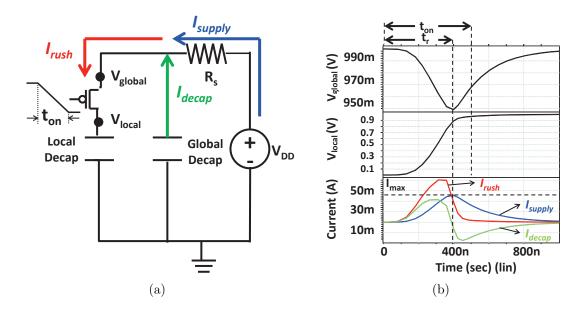

| 2.5 | Structure of global decaps. Global decaps are allocated between the global VDD grid and the global GND grid. The main utilization of global decaps is to suppress rush current noise through providing parts of charging current during the wake up of local grid.                                                         | 25 |

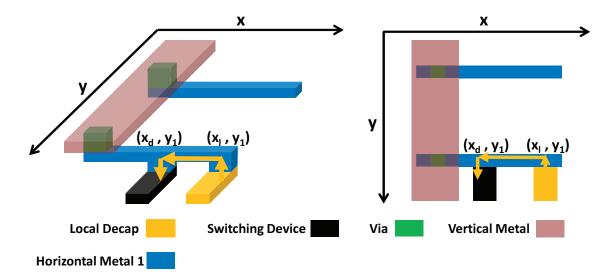

| 2.6 | The schematic layout and the top view of a typical PDN with a local decap. Only the global VDD grid and the local grid are shown in the figure. The global GND grid is not depicted in the figure                                                                                                                          | 26 |

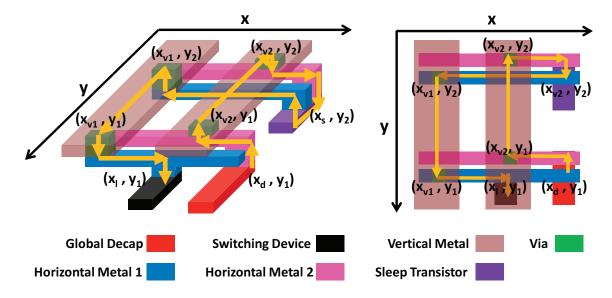

| 2.7 | The schematic layout and the top view of a PDN with a sleep transistor<br>and a global decap. Only the global VDD grid and the local grid are<br>shown in the figure. The global GND grid is not depicted in the layout.<br>Horizontal metal layer 1 and 2 are connected by a sleep transistor                             | 27 |

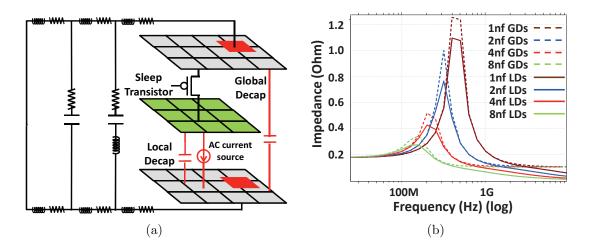

| 2.8 | On-chip decaps' influence on circuit resonance at 45nm technology<br>node. (a) The circuit model for analysis. (b) Impedances of the chip<br>with different amount of local decaps and global decaps                                                                                                                       | 27 |

| 2.9 | Rush current noise suppression through extending turn-on time $t_{on}$ at 45nm technology node. (a) Simple circuit model with no global decap. $R_s$ indicates the equivalent resistance between the supply voltage and the sleep transistor. (b) Voltage drop observed of global grid and the corresponding rush current. | 29 |

|     |                                                                                                                                                                                                                                                                                                                            |    |

| 2.10 | Rush current noise suppression of global decaps. The technology node<br>is 45nm. (a) Simple circuit model with a global decap. $R_s$ indicates<br>the equivalent resistance between the supply voltage and the sleep<br>transistor. (b) Voltage drop observed of global grid and the corre-<br>sponding rush current                                                                                                                                                                                                                                                                          | 30 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

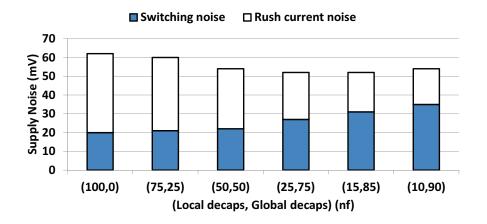

| 2.11 | Trade-off between switching noise and rush current noise. The power-<br>gated PDN utilized for simulation is shown in Fig. 1.6. Total decap<br>budget (100nf) is divided into local decaps and global decaps. Local<br>decaps and global decaps are uniformly distributed on local grids or<br>global grids. The switching devices are modeled as triangular current<br>sources [1]. Turn-on time is 1000ns. The technology node is 45nm.                                                                                                                                                     | 32 |

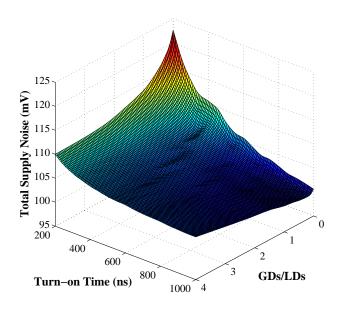

| 2.12 | Total supply noise is controlled though the LD&GD design strategy.<br>Total decap budget (100nf) is divided into local decaps and global<br>decaps. Local decaps and global decaps are uniformly distributed<br>on local grids or global grids. The switching devices are modeled as<br>triangular current sources [1]. The technology node is 45nm                                                                                                                                                                                                                                           | 33 |

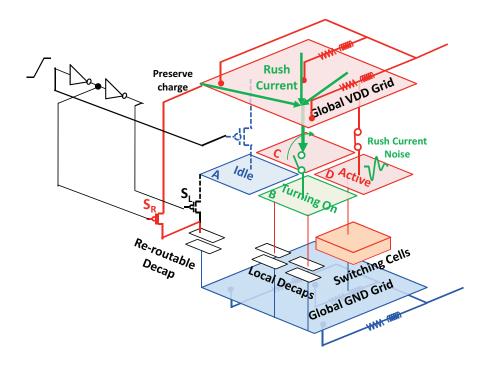

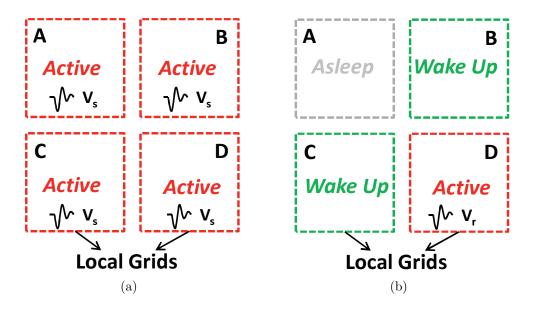

| 2.13 | Re-routable decap Function 1: when the local grid is active, the re-<br>routable decap acts as a local decap to suppress the switching noise<br>of its own power domain.                                                                                                                                                                                                                                                                                                                                                                                                                      | 35 |

| 2.14 | Re-routable decap Function 2: when the local grid is turned off, the re-routable decap is routed to the global VDD grid. It acts as a global decap to suppress the supply noises of other local domains. In addition, the significant charge on re-routable decap is preserved by the global grid.                                                                                                                                                                                                                                                                                            | 36 |

| 2.15 | Re-routable decap Function 3: when the local grid is turned off, the<br>re-routable decap is routed to the other active local grids. It acts as<br>a local decap to suppress the switching noises of other local domains.                                                                                                                                                                                                                                                                                                                                                                     | 37 |

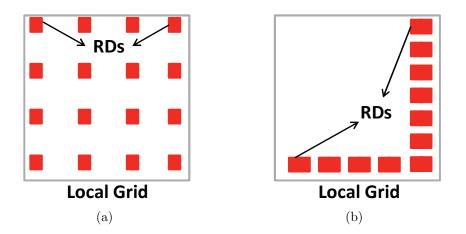

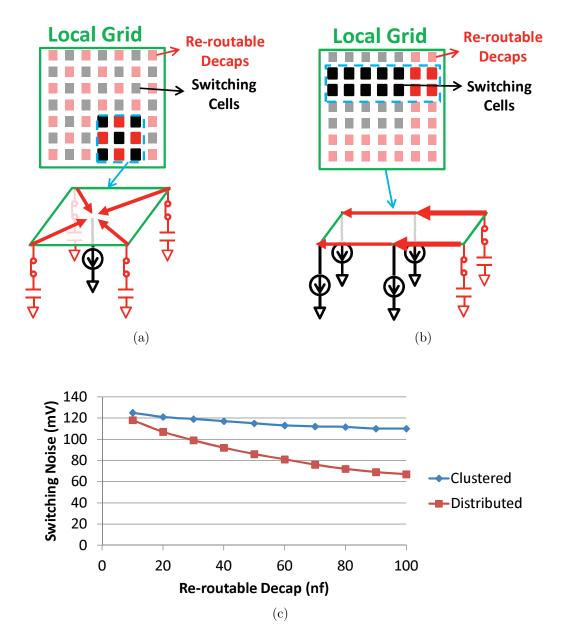

| 2.16 | Two different allocations of re-routable decaps: (a) distributed allo-<br>cation; (b) clustered allocation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 39 |

| 2.17 | Switching noise suppression of re-routable decaps with different allo-<br>cations. The simulations are based on the PDN model shown in Fig.<br>1.6. Only re-routable decaps are utilized in the circuit (no local decap<br>or global decap). The amount of RDs is taken as a tuning parameter.<br>The switching noises of the circuit with different amounts of RDs are<br>monitored. The technology node is 45nm. (a) Distributed allocation<br>of re-routable decaps. (b) Clustered allocation of re-routable decaps.<br>(c) Switching noises with different re-routable decaps allocation. | 40 |

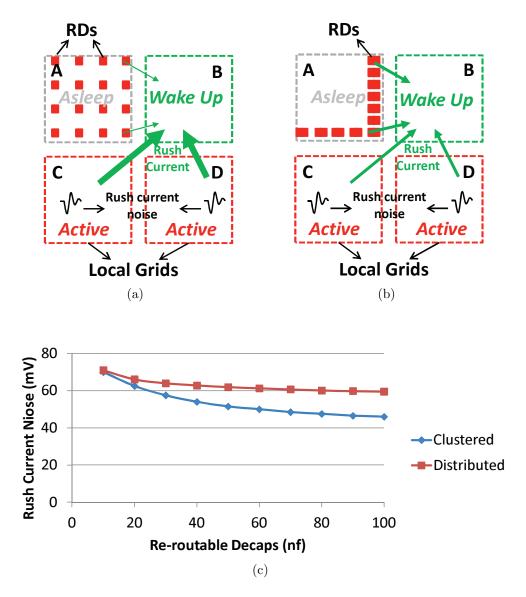

| 2.18 | Rush noise suppression of re-routable decaps with different allocations. The PDN model is shown in Fig. 1.6. Only local decaps and re-<br>routable decaps are utilized in the circuit (no global decap). The<br>amount of local decaps allocated in each local domain is 25nf. Re-<br>routable decaps are only allocated in local grid $A$ . The technology<br>node is 45nm. (a) Distributed allocation of re-routable decaps on<br>local grid $A$ . (b) Clustered allocation of re-routable decaps on local<br>grid $A$ . (c) Rush current noises with different allocations | 42         |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

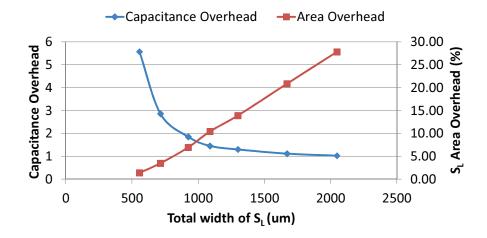

| 2.19 | Capacitance overhead and switch area overhead of the re-routable de-<br>caps required to reduce switching noise to tolerable value. The max-<br>imum tolerable switching noise is 10% of $V_{DD}$ . The circuit model is<br>shown in Fig. 1.1. Only re-routable decaps are utilized in the circuit<br>(no local decaps or global decaps). The re-routable decaps are allo-<br>cated through distributed allocation. The technology node is 45nm.                                                                                                                              | 44         |

| 2.20 | Simulation based optimization flow for PDN design with single supply voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 45         |

| 2.21 | Simulation models for optimization flow. (a) Model for switching noise simulation. (b) Model for rush current noise simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                | 48         |

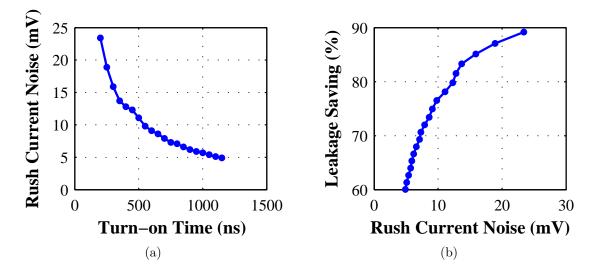

| 2.22 | Rush current noise and leakage saving through the LD only strategy.<br>Switching noise is reduced to 9.5% of $V_{DD}$ . (a) Rush current sup-<br>pression fully depends on extending turn-on time. (b) The interaction<br>between leakage saving and rush current noise. Leakage saving is re-<br>stricted by rush current noise. The leakage saving is normalized to<br>the leakage power consumed without power gating                                                                                                                                                      | 49         |

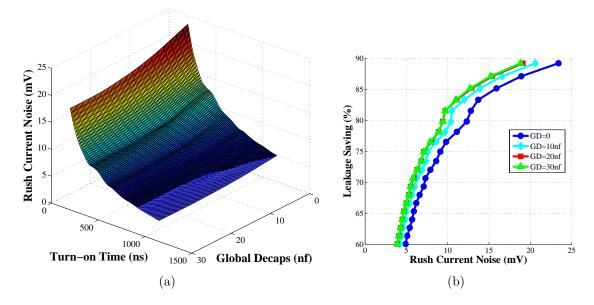

| 2.23 | Rush current noise and leakage saving through the LD&GD strategy.<br>Switching noise is reduced to 9.5% of $V_{DD}$ . (a) Rush current noise is<br>suppressed by both turn-on time and global decaps. The gray zone in<br>Fig. 2.23(a) covers the designs with rush current noise under 0.5% of<br>$V_{DD}$ . (b) Global decaps relax the interaction between leakage saving<br>and rush current noise.                                                                                                                                                                       | 50         |

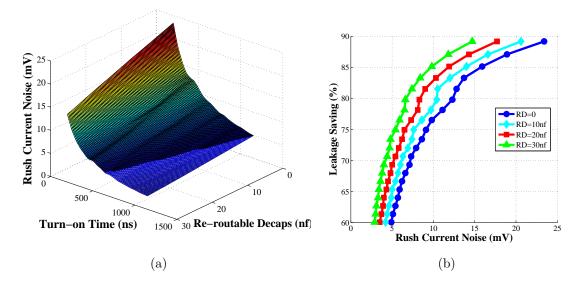

| 2.24 | Rush current noise and leakage saving through the LD&GD&RD strat-<br>egy. No GD is used in order to evaluate the influence of re-routable<br>decaps. Switching noise is reduced to 9.5% of $V_{DD}$ . (a) Rush current<br>noise is suppressed by both turn-on and re-routable decaps. The gray<br>zone covers the designs whose rush current noises are under 0.5% of<br>$V_{DD}$ . (b) Re-routable decaps obviously relax the interaction between                                                                                                                            | <b>F</b> 1 |

|      | leakage saving and rush current noise.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51         |

| 2.25 | Comparison of optimization results obtained from the LD only strat-<br>egy, the LD&GD strategy and the LD&GD&RD strategy. (a) Com-<br>parison of supply noises. (b) Comparison of normalized leakage sav-<br>ings. The leakage savings through different design strategies are nor-<br>malized to the leakage consumption without power gating. (c) Com-<br>parison of normalized performance delays. The performance delays<br>through different design strategies are normalized to the execution<br>time without power gating | 52 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

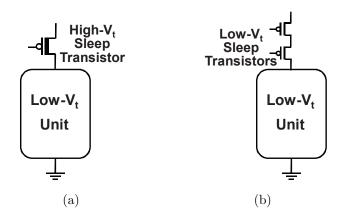

| 2.26 | Structures of sleep transistors. (a) High-threshold sleep transistor. (b) Stacked low threshold voltage sleep transistor                                                                                                                                                                                                                                                                                                                                                                                                         | 56 |

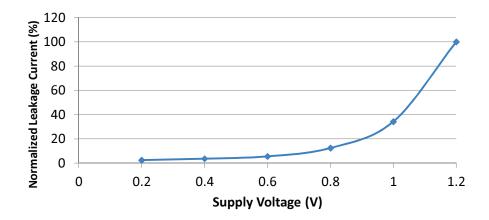

| 2.27 | Normalized leakage current of an inverter increases with the sup-<br>ply voltage $(V_{DD})$ . Leakage current is normalized to the value when<br>$V_{DD}=1.2$ V. The technology node is 45nm                                                                                                                                                                                                                                                                                                                                     | 57 |

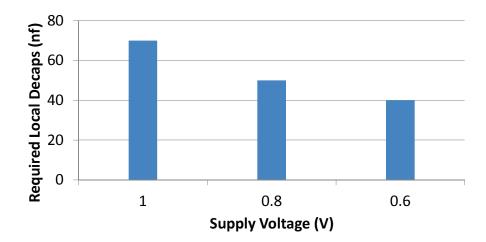

| 2.28 | The decaps required at different supply voltages for the LD Only Strat-<br>egy. The maximum tolerable supply noise is $10\%$ of $V_{DD}$ . The tech-<br>nology node is 45nm.                                                                                                                                                                                                                                                                                                                                                     | 60 |

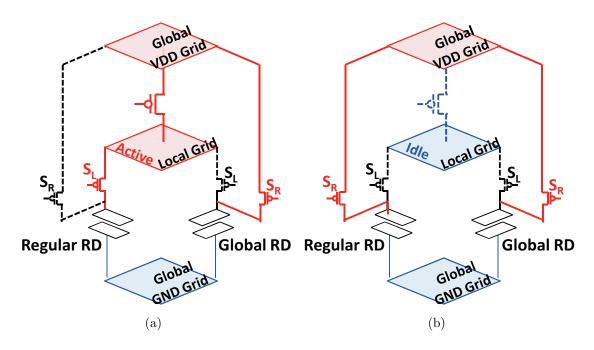

| 2.29 | Usages of regular RD and global RD. (a) When the local grid is active, regular RD is connected to the local grid and global RD is connected to the global VDD grid. (b) When the local grid is idle, both regular RD and global RD are connected to the global VDD grid                                                                                                                                                                                                                                                          | 61 |

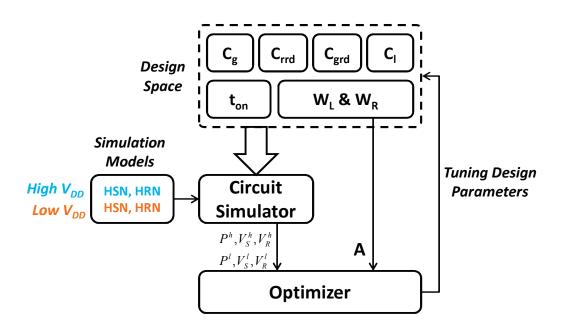

| 2.30 | Simulation based optimization flow with two supply voltages                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 62 |

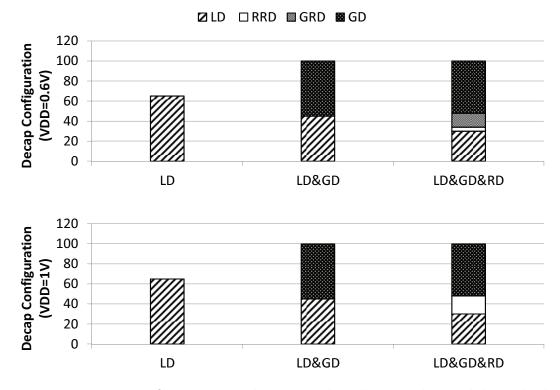

| 2.31 | Decap configurations with two supply voltages. The total decap budget is 100 nf                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 65 |

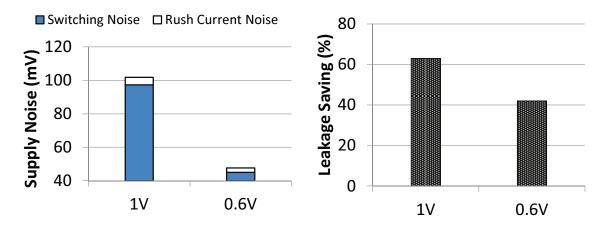

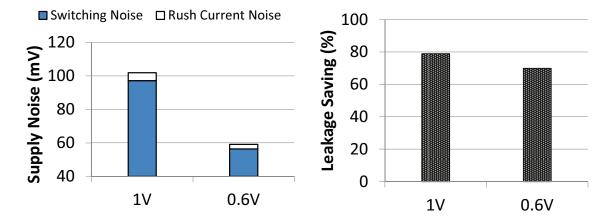

| 2.32 | Supply noises and leakage saving of the LD only strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66 |

| 2.33 | Supply noises and leakage saving of the LD&GD strategy                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 67 |

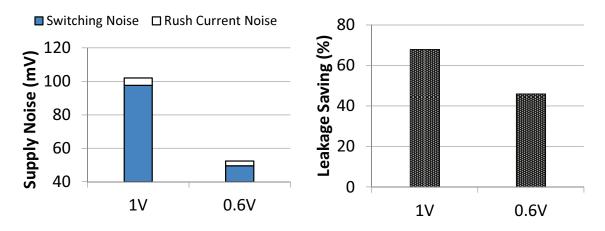

| 2.34 | Supply noises and the leakage saving of the LD&GD&RD strategy. $% \mathcal{A} = \mathcal{A} = \mathcal{A} = \mathcal{A}$ .                                                                                                                                                                                                                                                                                                                                                                                                       | 67 |

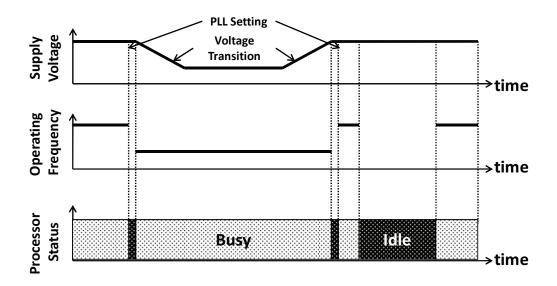

| 3.1  | Supply voltage and operating frequency scaling procedure of single-<br>core processor                                                                                                                                                                                                                                                                                                                                                                                                                                            | 72 |

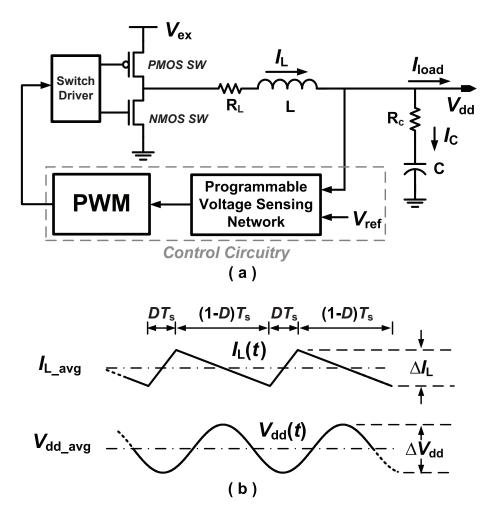

| 3.2  | Illustration of the DC-DC converter we employed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 73 |

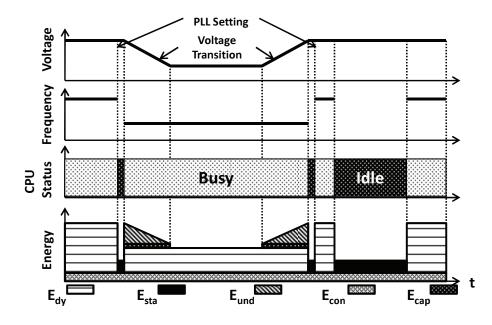

| 3.3 | The supply voltage, frequency and energy consumption during a DVFS                                   |

|-----|------------------------------------------------------------------------------------------------------|

|     | procedure. ( $E_{dy}$ , $E_{sta}$ , $E_{und}$ , $E_{con}$ , and $E_{cap}$ respectively represent the |

|     | dynamic energy of the processor, the static energy of the processor,                                 |

|     | the under driving energy overhead during DVFS transition, the en-                                    |

|     | ergy consumption of the DC-DC converter and the energy consumed                                      |

|     | by charging/discharging capacitors during voltage scaling.)                                          |

80

82

85

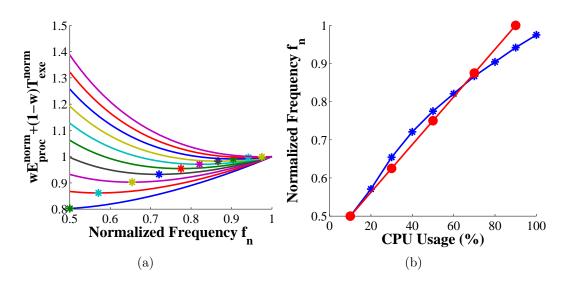

- 3.4 (a) The optimal frequencies to balance  $E_{proc}$  and  $T_{exe}$  with different  $\mu$ .  $\mu$  is the CPU usage when the workload is processed with the maximum frequency. The objective function is  $wE_{proc}^{norm} + (1 - w)T_{exe}^{norm}$ . The technology node is 90nm. (b)  $\mu$ -map from the CPU usage to the optimal frequency.

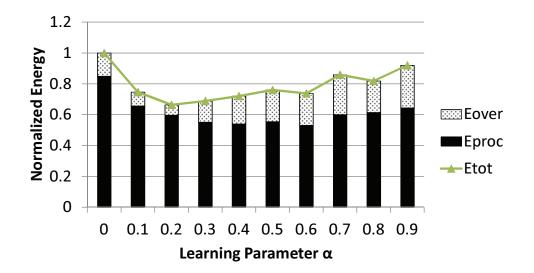

- 3.5  $E_{proc}$  (the processor energy) and  $E_{over}$  (the DVFS energy overhead) may be tuned towards opposite direction through adjusting the DVFS policy. The DC-DC converter design and the DVFS operative period are fixed at different  $\alpha$  values. The energy consumption is normalized to the total energy when the processor constantly operates at highest voltage/frequency ( $\alpha = 0$ ). The simulation is based on benchmark blackscholes [2] with a single thread running on a single-core processor. 83

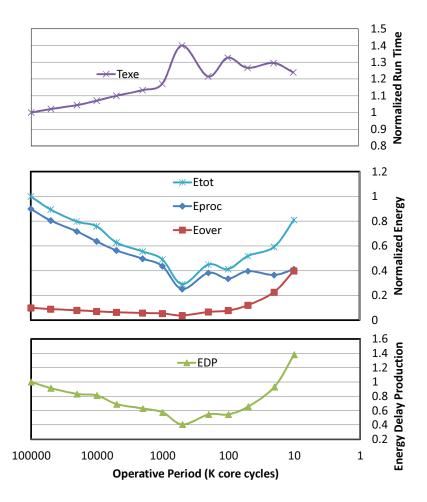

- 3.6 The influence of the DVFS operative period on the run time and the energy consumption. The learning parameter  $\alpha$  is set to 0.5. The longest voltage transition time of the DC-DC converter is 9  $\mu$ s (9K CPU cycles at the highest frequency). The energy consumption and the run time are respectively normalized to the total energy and the execution time when the processor constantly operates at the highest voltage/frequency. The simulation is based on benchmark *blackscholes* [2] with a single thread running on a single-core processor. The technology node is 90nm.

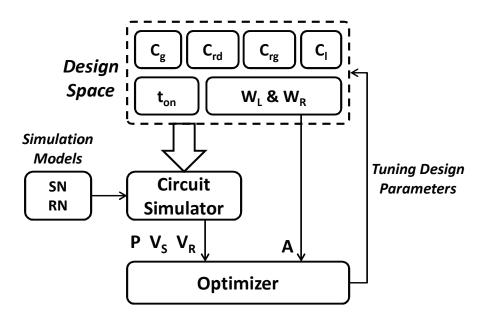

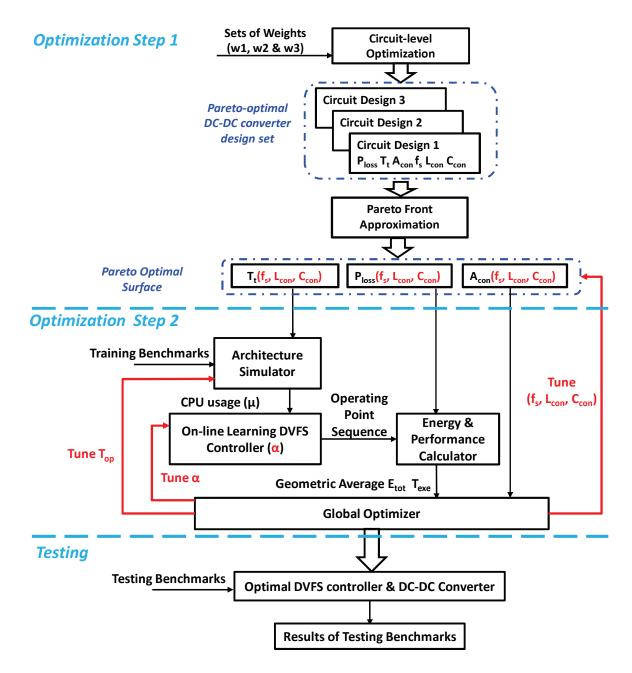

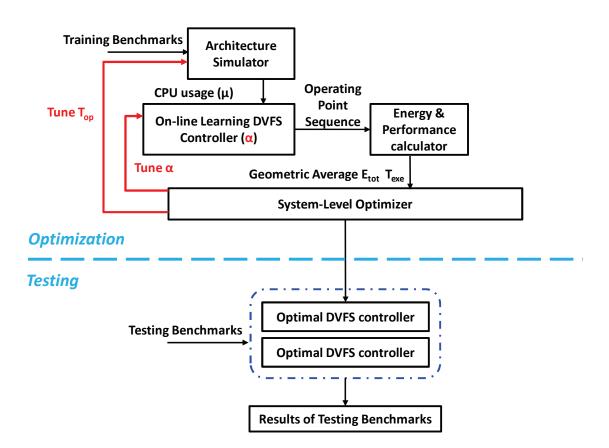

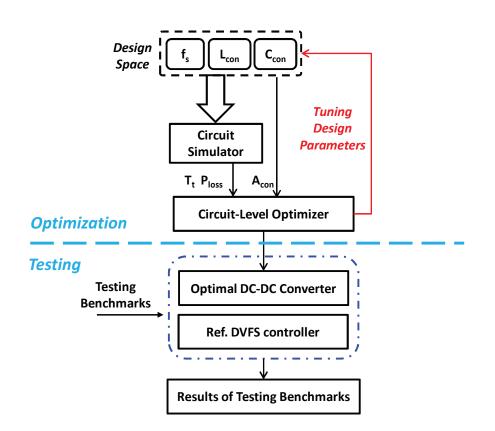

- 3.8 Hierarchical circuit-level and system-level co-optimization and testing flow.

3.9 System-only optimization and testing flow.

94

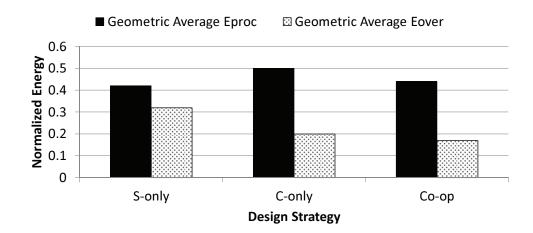

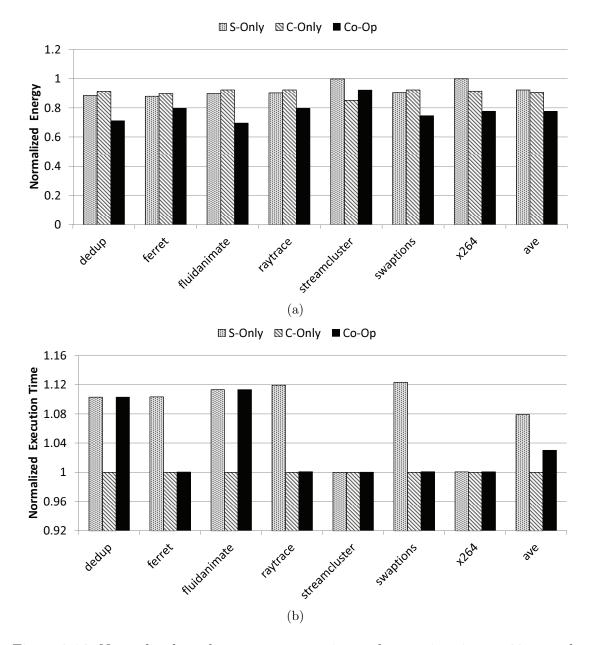

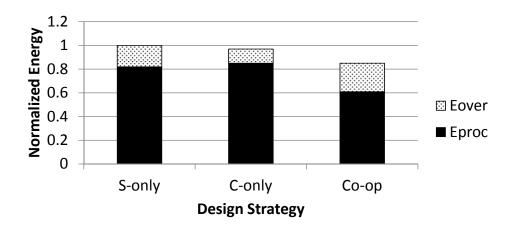

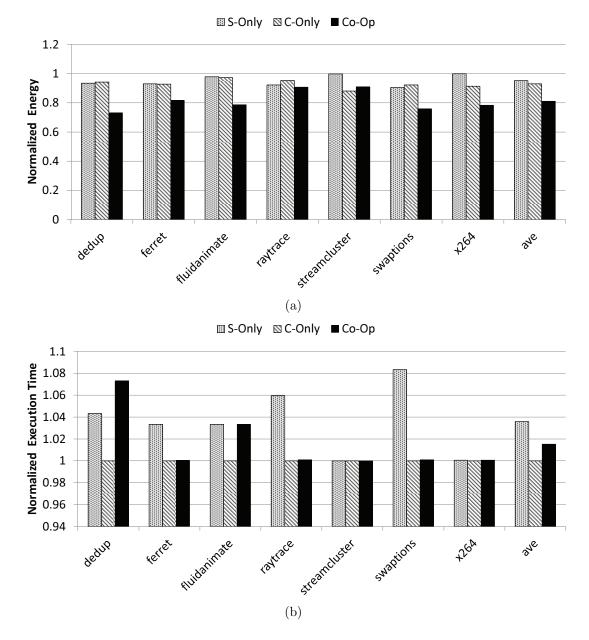

| 3.11 | Normalized geometric average energy consumptions of the testing set.<br>For each strategy, the geometric average processor energy and the<br>geometric average DVFS energy overhead are normalized to the geo-<br>metric average total energy of the reference design. The circuit-level<br>and system-level designs are obtained based on the training set with<br>S-Only, C-Only, and Co-Op strategies respectively. For each bench-<br>mark, the simulation is carried out with a single thread processed on<br>a single-core processor.   | 100 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

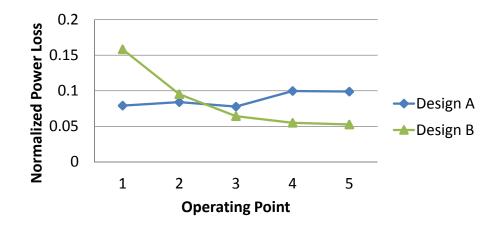

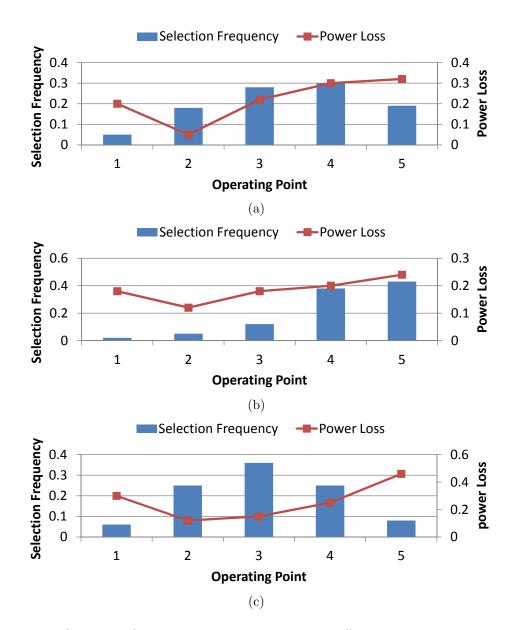

| 3.12 | Selection frequency and power loss at different operating points. The results are based on benchmarks of the testing set with single thread processed on a single-core processor. The circuit-level and system-level designs are obtained based on the training set with S-Only, C-Only, and Co-Op strategies respectively. (a) System Only Optimization; (b) Circuit Only Optimization; (c) Cross-layer Co-optimization                                                                                                                      | 101 |

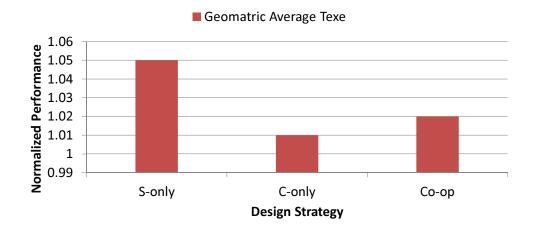

| 3.13 | Normalized geometric average execution time of benchmarks of the testing benchmarks. For each strategy, the geometric average execution time is normalized to the geometric average execution time of the reference design. The circuit-level and system-level designs are obtained based on the training set with S-Only, C-Only, and Co-Op strategies respectively. For each benchmark, the simulation is carried out with a single thread processed on a single-core processor.                                                            | 102 |

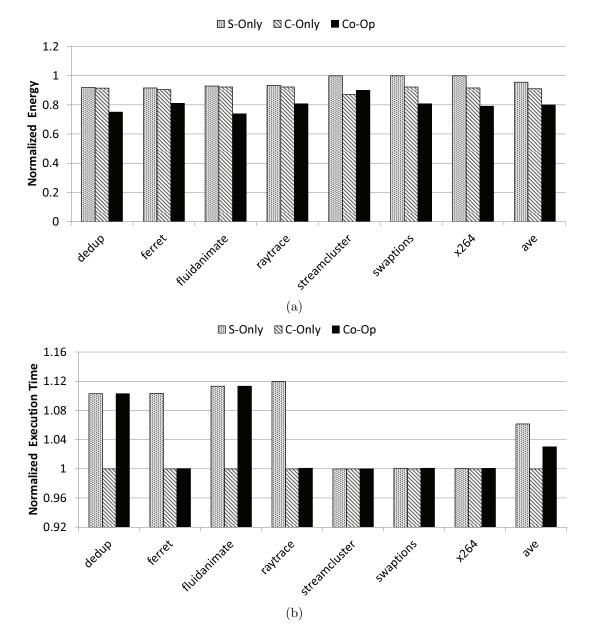

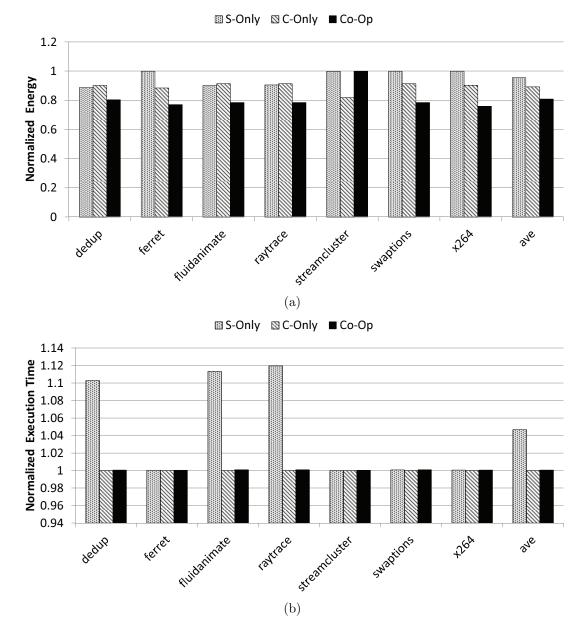

| 3.14 | Normalized total energy consumption and execution time at 90nm technology node. The results are based on the benchmarks in the testing set. The circuit-level and system-level designs are obtained based on the training set with S-Only, C-Only, and Co-Op strategies respectively. The energy consumption and execution time of the three designs are normalized to the reference design. The last column shows the geometric energy/performance of the benchmarks. (a) Normalized total energy consumption. (b) Normalized execution time | 104 |

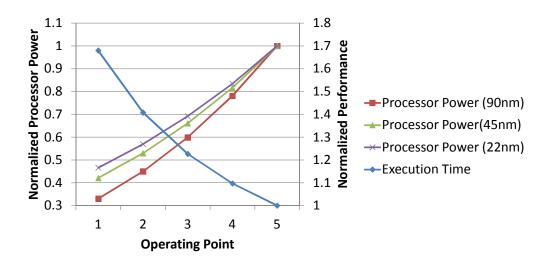

| 3.15 | Execution time and processor energy consumptions at different oper-<br>ating points. The execution time at each operating point is normalized<br>to the execution time at OP 5 (the highest voltage/frequency). At each<br>technology node, the processor energy consumption at each operating<br>point is normalized to the processor energy at OP 5 (the highest volt-<br>age/frequency). The results are based on benchmark <i>bodytrack</i> with<br>one thread on a single-core processor.                                                | 105 |

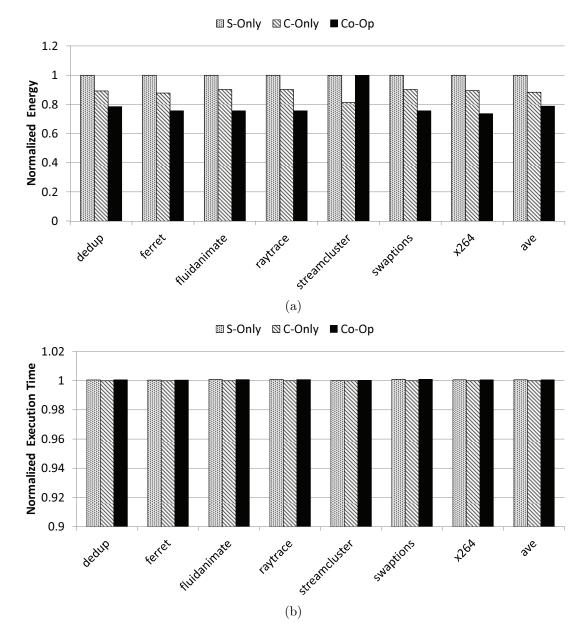

| 3.16 | Normalized total energy consumption and execution time at 45nm          |

|------|-------------------------------------------------------------------------|

|      | technology node. The results are based on the benchmarks in the         |

|      | testing set. The circuit-level and system-level designs are obtained    |

|      | based on the training set with S-only, C-only, and Co-Op strategies     |

|      | respectively. The energy consumption and execution time of the three    |

|      | designs are normalized to the reference design. The last column shows   |

|      | the geometric average energy/performance of the benchmarks. (a)         |

|      | Normalized total energy consumption. (b) Normalized execution time. 107 |

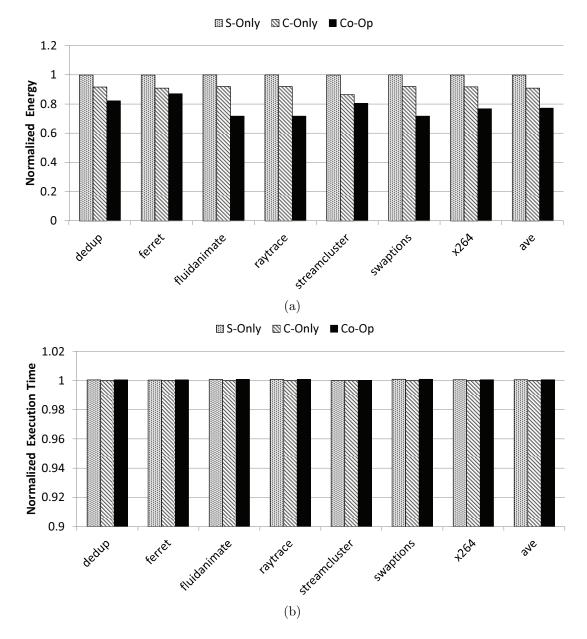

3.17 Normalized total energy consumption and execution time at 22nm technology node. The results are based on the benchmarks in the testing set. The circuit-level and system-level designs are obtained based on the training set with S-only, C-only, and Co-Op strategies respectively. The energy consumption and execution time of the three designs are normalized to the reference design. The last column shows the geometric average energy/performance of the benchmarks. (a) Normalized total energy consumption. (b) Normalized execution time. 108

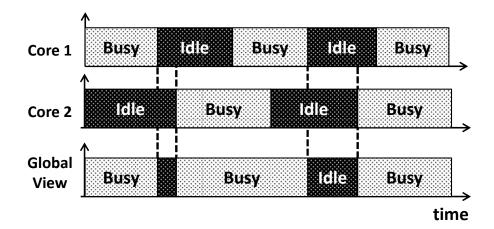

| 3.18 | The working status of a dual-core processor.                             | 110 |

|------|--------------------------------------------------------------------------|-----|

| 3.19 | Normalized energy consumption of benchmark <i>blackscholes</i> . The re- |     |

|      | sults are based on the simulation with two threads processed on two      |     |

|      | cores respectively. The technology node is 90nm.                         | 112 |

. .

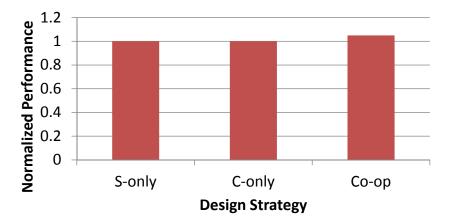

| 3.20 | Normalized performance of benchmark <i>blackscholes</i> . The results are |     |

|------|---------------------------------------------------------------------------|-----|

|      | based on the simulation with two threads processed on two cores re-       |     |

|      | spectively. The technology node is 90nm                                   | 113 |

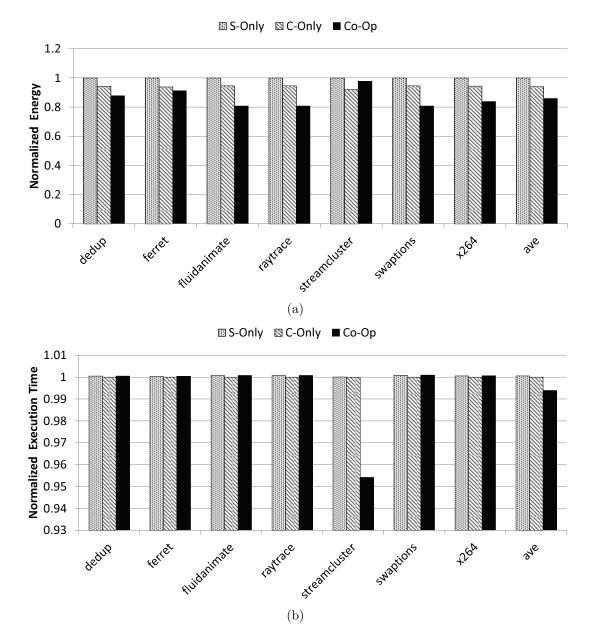

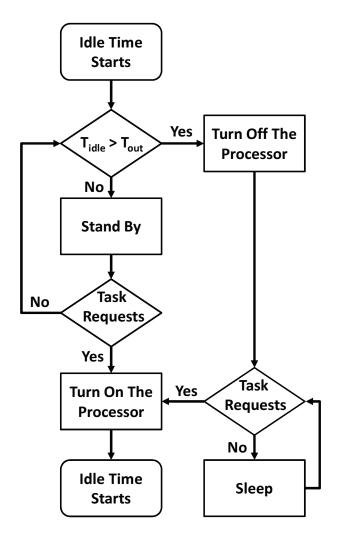

3.21 Normalized total energy consumption and execution time of the dualcore processor at 90nm technology node. The results are based on the benchmarks in the testing set. The circuit-level and system-level designs are obtained based on the training set with S-only, C-only, and Co-Op strategies respectively. The energy consumption and execution time of the three designs are normalized to the reference design. The last column shows the geometric average energy/performance of the benchmarks. (a) Normalized total energy consumption. (b) Normalized execution time. 1153.22 Flowchart of static timeout power gating policy.  $T_{idle}$  is the idle time.

|                  |         | -          | ~    | ~   | - | ~ |   |  |  |   |   |  |         |

|------------------|---------|------------|------|-----|---|---|---|--|--|---|---|--|---------|

| $T_{out}$ is the | timeout | parameter. | <br> | ••• |   |   | • |  |  | • | • |  | <br>118 |

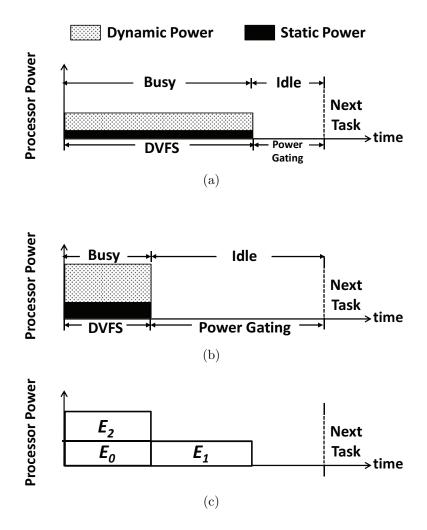

| 3.23 Interplay between DVFS and power gating. (a) The processor operates at low-frequency operating points and the idle time for power gating is shortened. (b) The processor operates at high-frequency operating points and the idle time for power gating is extended. (c) Energy consumption comparison between (a) and (b).                                                                                                                                                                                                                                                                                | 120 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.24 Normalized total energy consumption and execution time of power-<br>gated processor at 90nm technology node. The results are based on<br>the benchmarks in the testing set. The circuit-level and system-level<br>designs are obtained based on the training set with S-only, C-only, and<br>Co-Op strategies respectively. The energy consumption and execution<br>time of the three designs are normalized to the reference design. The<br>last column shows the geometric average energy/performance of the<br>benchmarks. (a) Normalized total energy consumption. (b) Normal-<br>ized execution time  | 124 |

| 3.25 Normalized total energy consumption and execution time of power-<br>gated processor at 45nm technology node. The results are based on<br>the benchmarks in the testing set. The circuit-level and system-level<br>designs are obtained based on the training set with S-only, C-only, and<br>Co-Op strategies respectively. The energy consumption and execution<br>time of the three designs are normalized to the reference design. The<br>last column shows the geometric average energy/performance of the<br>benchmarks. (a) Normalized total energy consumption. (b) Normal-<br>ized execution time. | 125 |

| 3.26 Normalized total energy consumption and execution time of power-<br>gated processor at 45nm technology node. The results are based on<br>the benchmarks in the testing set. The circuit-level and system-level<br>designs are obtained based on the training set with S-only, C-only, and<br>Co-Op strategies respectively. The energy consumption and execution<br>time of the three designs are normalized to the reference design. The<br>last column shows the geometric average energy/performance of the<br>benchmarks. (a) Normalized total energy consumption. (b) Normal-<br>ized execution time  | 127 |

## LIST OF TABLES

# TABLE

# Page

| 2.1 | Impacts of On-Chip Decaps and Turn-on Time on Design Concerns $% \mathcal{A}$ .              | 31  |

|-----|----------------------------------------------------------------------------------------------|-----|

| 2.2 | Comparison among Three Types of On-Chip Decaps                                               | 38  |

| 2.3 | Design Parameters of Power-Gated PDN with Single Supply Voltage .                            | 46  |

| 2.4 | Experimental Setting of Power-Gated PDN with Single Supply Voltage                           | 47  |

| 2.5 | Comparison among Three Design Strategies of Power-Gated PDN with Single Supply Voltage       | 54  |

| 2.6 | Design Trade-Off Variations with Supply Voltage                                              | 59  |

| 2.7 | Design Parameters of Power-Gated PDN with Two Supply Voltages $% \mathcal{A}$ .              | 63  |

| 2.8 | Experimental Setting of Power-Gated PDN with Two Supply Voltages                             | 64  |

| 2.9 | Comparison Among Three Design Strategies of Power-Gated PDN with Two Supply Voltages         | 68  |

| 3.1 | The Working Set of Operating Points and Mapping from CPU usages to Expected Operating Points | 77  |

| 3.2 | Experimental Setting of DVFS design for Single-Core Processor $\ldots$                       | 93  |

| 3.3 | Obtained Pareto-Optimal DC-DC Converter Design Set                                           | 99  |

| 3.4 | Experimental Setting of DVFS design for Dual-Core Processor                                  | 112 |

| 3.5 | Experimental Setting of DVFS design for Power-Gated Processor                                | 122 |

#### 1. INTRODUCTION

As the VLSI technology scales down, power management has become a first-order design consideration for modern chip designs including high-performance processors, embedded processors, and system-on-a-chips (SoCs). Various design issues appear with power management techniques in modern VLSI designs.

CMOS technology scaling doubles the number of transistors in a chip every eighteen months. As a cost, the power consumption of integrated circuits has dramatically grown in the past decades. The power issue of VLSI circuits becomes more critical as the technology scales down to nanometer scale. The power consumption generates a large amount of heat that may increase the temperature of circuits. Working under high temperature affects the reliability and performance of circuits. Extra cooling system and cost are required in order to dissipate the heat. In addition, battery life becomes one main concern of customers with the popularity of mobile devices. The batteries of mobile devices would be exhausted quickly by high power consumption. In order to control the power consumption, different power management techniques are proposed. During these techniques, power gating and dynamic voltage and frequency scaling (DVFS) are widely used in modern VLSI designs.

### 1.1 Power Management Techniques

The power consumption of an integrated circuit can be categorized into static power and dynamic power. Power gating is used to reduce the static power while DVFS is mainly used to control the dynamic power.

### 1.1.1 Power Gating

The static power (standby power) refers to the power consumed due to leakage current when a CMOS circuit is in standby. The percentage of chips that is idle or significantly underclocked (dark silicon) increases as the VLSI process technology scales down [3, 4]. Dark silicon is estimated to take up 20% of the chip area at the 22nm technology node and it will take up 50% at the 8nm node [5]. To this end, leakage power management becomes increasingly important for modern IC designs. Power gating is an effective solution to reduce the leakage consumption [6, 7, 8, 9, 10].

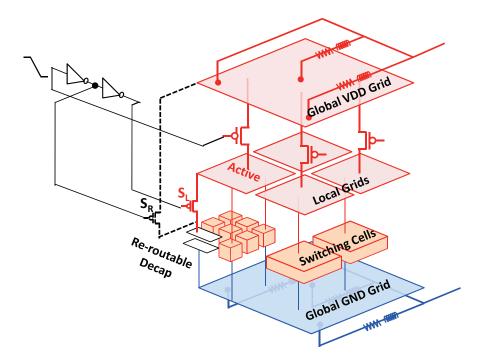

Figure 1.1: Typical structure and supply noises of power-gated PDNs. The switching noise is due to switching currents of logic devices. The rush current noise is due to rush currents created to charge up the decaps of a local grid that is woken up.

A typical power-gated power delivery network (PDN) is shown in Fig. 1.1. The

PDN is composed of an off-chip part and an on-chip part. The off-chip part includes the model of the motherboard, package, and off-chip decoupling capacitors and parasitic inductances [11]. The on-chip part includes a global VDD grid, a global GND grid and multiple local power-gated grids (power domains). Each local power grid is connected to the global  $V_{DD}$  grid through switchable sleep transistors. Hence, the leakage power can be saved by turning off the sleep transistors. Such power delivery networks have been widely adopted in multi-core chips and system-on-a-chips (SoCs) to support the power gating of multiple power domains [7, 10].

Power integrity is a significant concern in power-gated PDN designs. Two types of supply noises exist in the power-gated PDNs: switching noise and rush current (wake-up) noise as shown in Fig. 1.1. The switching noise is caused by switching activities of logic cells. When time variant switching currents flow through off-chip inductors and on-chip resistive grids, a voltage fluctuation is introduced to the logic cells. The rush current noise is a unique source of supply noise for power-gated PDNs. It is due to the rush currents that are created to charge up the decoupling capacitors in a local grid when it is woken up. The other active local grids suffer the voltage fluctuation brought by the rush currents.

The primary design challenge of a power-gated PDN stems from the conflicting objectives of power integrity and power efficiency. We summarize the key design trade-offs and typical design strategies in Fig. 1.2. The oval-shapes of the diagram indicate the design concerns and the edges indicate the typical strategies. Switching noise is typically suppressed by local decaps (LDs) that are connected between the local grids and the global GND grid [12, 13, 14]. In this case, the suppressions of switching noise and rush current noise contradict each other since local decaps are the sources of rush current noise. Hence, it is hard to achieve the power integrity by only using local decaps. Extending the turn-on time of the sleep local grid is a

Figure 1.2: Design trade-offs and typical strategies of power-gated PDNs with a single supply voltage. The oval-shapes indicate the concerns of a PDN design. The edges indicate the typical strategies to balance design concerns.

common strategy to suppress the rush current noise [15, 16, 17]. However, longer turn-on time inevitably reduces energy saving, for there are fewer opportunities to launch power gating. As a result, the leakage saving of power gating is limited by the power integrity requirements.

Another critical problem of power-gated PDN design is the design trade-off variations under different supply voltages. Dynamic Voltage Scaling (DVS) and Dynamic Voltage and Frequency Scaling (DVFS) are widely applied to modern processors to save the dynamic power consumption. These techniques provide different supply voltages for a processor to operate at different operating points. The power-gated PDN design trade-offs between leakage saving and supply noises highly depend on the supply voltages. On one hand, the leakage current of a VLSI circuit exponentially decreases with the supply voltage  $(V_{DD})$ . Hence, power gating at lower  $V_{DD}$  requires longer break even time to compensate its energy overhead. It means that there are fewer opportunities to launch power gating at lower supply voltage. On the other hand, both switching noise and rush current noise, when normalized with respect to the nominal supply voltage, have a tendency to decrease with supply voltage. In summary, leakage saving is the dominant design concern at lower  $V_{DD}$ , while power integrity is the dominant design concern at higher  $V_{DD}$ . Fixed decap configuration is a typical strategy of power-gated PDN designs [18]. As shown in Fig. 1.3, the amount of local decaps are determined based on the switching noise at high  $V_{DD}$ , for it is the worst case of power integrity. However, this amount of local decaps is overdesigned for the power integrity at low  $V_{DD}$  since the switching noise decreases with supply voltage [19]. Obviously, the decap configuration cannot be changed once circuit design is completed. Hence, extending turn-on time becomes the only method to suppress the rush current noise at low  $V_{DD}$ . As a result, the leakage saving at low  $V_{DD}$  is restricted by the overdesigned decaps

Figure 1.3: Design trade-offs and typical strategies of a power-gated PDN with two supply voltages. The oval-shapes indicate the concerns of a PDN design. The edges indicate the typical strategies to balance the design concerns.

### 1.1.2 Dynamic Voltage and Frequency Scaling (DVFS)

As an effective means of controlling power consumption, Dynamic Voltage and Frequency Scaling (DVFS) has been widely adopted to reduce dynamic and static power consumption [20, 7]. Supporting DVFS at the circuit level has been the subject of many circuit design works [21, 22, 19]. At the system-level, many DVFS policies have also been proposed to control power consumption by managing different operating points (voltage and frequency pairs) [23, 24]. Among these, online learning based DVFS policies have been shown to be effective for reducing chip power consumption [24].

Figure 1.4: Typical structure of DVFS system that is composed of a circuit-level DC-DC converter and a system-level DVFS controller.

As shown in Fig. 1.4, a typical structure of DVFS is composed of a system-level part and a circuit-level part. At the system level, a DVFS controller is designed to balance energy consumption and performance delay by adapting to the temporal variation of workloads. The DVFS controller evaluates the energy consumption and the performance delay according to an evaluation model at the end of each operative period. Based on the evaluation, the controller selects an operating point from the working set through a control algorithm. At the circuit level, a DC-DC converter is commonly used to provide the supply voltage of the selected operating point in the following operative period.

Figure 1.5: Design trade-offs of DVFS at the system level and the circuit level.

The design trade-offs of DVFS at the system level and circuit level are illustrated in Fig. 1.5. A DVFS controller can be optimized from three perspectives: operative period, evaluation model and DVFS algorithm as shown in Fig. 1.5. The operative period determines the grain of DVFS. Generally, shortening the operative period allows the DVFS controller to better track workload variations and select more suitable operating points [25, 26]. The evaluation model is used to evaluate the energy consumption and the performance delay of each operating point. Most of DVFS evaluation models are based on CPU performance counters such as cache misses, CPU usages or stall cycles [27, 28]. The accuracy of an evaluation model directly influences the performance of DVFS. A DVFS algorithm is the strategy of operating point selection. Different DVFS algorithms are proposed in the previous works [25, 29, 30, 31]. Compared with other algorithms, online learning based algorithm is more flexible to track the workload variations. In this paper, our DVFS controller adopts the online learning algorithm proposed in [24] to manage the operating points.

Nevertheless, optimizing the DVFS controller only may not necessarily lead to the minimization of the total energy consumption. First, the system-level optimization may increase the DC-DC converter's energy overhead. The fine-grained DVFS requires that the DC-DC converter supports fast transition of output voltage as shown in Fig. 1.5. However, shortening transition time may increase the DC-DC converter's energy overhead at the circuit level. In addition, the operating points selected by the DVFS policy may increase the power loss of the DC-DC converter. The DC-DC converter's energy consumption varies with its output voltage, which is well demonstrated by the power efficiency measurements in [22]. Hence, the total energy consumption may increase even if the operating points reduce the energy consumed by the CPU. Second, evaluation models that are commonly based on CPU performance counters cannot reflect the circuit-level energy consumption. As a result, a system-level optimization balances the CPU energy consumption and the performance delay, but it may not optimize the total energy consumption. Therefore, the optimizations of the DVFS controller and the DC-DC converter shall be synergistically considered as two aspects of the same power problem.

### 1.2 Previous Works

As mentioned in the last section, different design issues appear with power gating and DVFS. Some existing works are proposed to address these problems.

### 1.2.1 Previous Works of Power Gating

For power-gated PDN designs with single supply voltage, some existing works propose solutions to deal with the conflicting objectives of power integrity and power efficiency. Some works suppress the rush current noise through controlling the wakeup process [15, 32, 33, 34, 16, 35]. Stepwise turning on of sleep transistors is used in [15, 32] to suppress the rush current noise. The amount of rush current is controlled through slowing down the charging process. In [33], the authors divided logic cells into small power domains and skew the delay of sleep transistor drivers to avoid simultaneously turning on the domains. Multiple wake-up phases are proposed in [34]. The entire turning on process is partitioned into three stages. The turn-on scheme reduces the rush current during its metastable period of operation, while boosting the power supply rail when no short circuit current paths exist in the logic. However, the entire turn-on time is extended and thereby the leakage saving is reduced. Multiple sleep modes with different sleep depths are proposed in [16, 35]. Each sleep mode represents a trade-off between wake-up penalty and leakage saving through controlling the steady state potential in the sleep mode. Although the turnon time of light sleep modes is shortened, the leakage saving of these modes is reduced correspondingly. Generally, these methods sacrifice parts of leakage saving to reduce the rush current noise. Some other works take use of extra hardware to suppress the rush current noise. The bypass power line and multi-size sleep transistors are used in [17]. But it is not economic for core-level power gating since additional global power networks is required to implement the bypass power line.

For power-gated PDN designs with multiple supply voltages, some works have been devoted on power-gated PDN design and optimization with  $V_{dd}$  higher than 1V[17, 36]. A little has been done for power gating at ultra low supply voltage. In [37], extra control circuits are proposed to suppress rush current noise in the sub-1V region. However, the different design trade-offs at higher supply voltages are not considered. In [18, 24], DVFS and power gating are combined to reduce power consumption. However, the power gating trade-offs varying between operating points are not considered.

### 1.2.2 Previous Works of DVFS

For most of DVFS designs, the circuit-level DC-DC converter and the systemlevel DVFS policy are designed separately. Various DVFS policy are proposed in [38, 39, 24, 40]. The objective of these works is to improve the DVFS controller to better track the work loads and balance the processor energy consumption and the performance delay. Different DC-DC converter designs are proposed in [41, 42, 43, 44, 45, 46, 22]. The objective of these works is to increase the energy efficiency and transition speed. However, separate designs lack the comprehensive consideration of the entire system. In this case, even if the objectives are achieved for each level, the entire DVFS system may still not reach the overall optimality.

Some existing works discuss the influence of the DC-DC converters on DVFS performance. A joint optimization of the DC-DC converter and computational core is proposed in [47] to minimize the system energy. The core architecture is improved

to reduce the influence of the DC-DC converter's power loss. However, the benefit is limited in the subthreshold region (low output voltage) and the influence of the system-level management policy is not considered. The authors of [48] propose a DC-DC converter aware DVS approach, where a standard DVS algorithm is first used to determine the execution order of a set of tasks and the supply voltage for each task. Given the schedule produced by the fixed DVS algorithm, the authors optimize the DC-DC converter to minimize the system energy based on an operating-point dependent energy model of the DC-DC converter. The outcome of this circuit-level optimization leads to revision of the supply voltages while the execution order and the start time of each task are kept the same. In this approach, the system-level DVS controller is fixed and not jointly optimized with the supporting circuit. In addition, this work does not specifically target online learning based DVFS schemes which may exhibit a stronger dependency on the underlying electrical characteristics of the DC-DC converter.

As such, an interesting and practically relevant question to ask is that to what extent power management controller and DC-DC converter shall be jointly co-optimized and what benefit may be resulted from this cross-layer co-optimization. We attempt to answer this question by investigating how the performances of online-learning based the DVFS controller depend on the underlying DC-DC converter design.

### 1.3 Proposed Solutions

#### 1.3.1 Proposed Solutions on Power Gating

In this dissertation, we employ both global decaps (GDs) and re-routable decaps (RDs) to deal with the design problems associated with power-gated PDNs. Fig. 1.6 shows the PDN structure proposed in this work. Global decaps are allocated between global VDD and GND grids. They are mainly used to suppress the rush

current noise by providing parts of charge required by local decaps. A re-routable decap is connected to the local grid and the global VDD grid via two switches. Reroutable decaps can work as local decaps or global decaps through controlling the switches.

Figure 1.6: Proposed structure of power-gated PDNs. Global decaps and re-routable decaps are utilized in the proposed PDN structure.

For power-gated PDNs with single supply voltage, global decaps and re-routable decaps are utilized to relax the tight interaction between power integrity and power efficiency. As shown in Fig. 1.7, global decaps and re-routable decaps provide methods to suppress rush current noise without sacrificing the leakage saving.

Figure 1.7: Proposed design strategies for power-gated PDN designs with a single supply voltage. The oval-shapes indicate the concerns of a PDN design. The edges indicate the strategies to balance design concerns. Black solid edges are the typical strategies. Red dash edges are the strategies proposed in this paper.

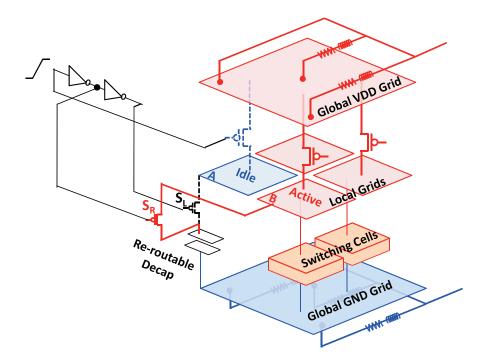

For the power-gated PDN with multiple  $V_{DD}$ , we use diverse decap configurations to adapt to supply voltage as shown in Fig. 1.8. Re-routable decaps can act as local decaps or global decaps through controlling the switches. Hence, we can provide different decap configurations (LDs/GDs/RDs) for each  $V_{DD}$  level through the utilization of re-routable decaps. In this case, the design concerns (leakage saving and power integrity) at different voltage levels can be optimized separately. Therefore, the optimal design can be achieved for each supply voltage level.

Figure 1.8: Proposed design strategies for power-gated PDN designs with multiple supply voltages. The oval-shapes indicate the concerns of a PDN design. The edges indicate the strategies to balance the design concerns. Black solid edges are the typical strategies. Red dash edges are the strategies proposed in this paper.

#### 1.3.2 Proposed Solutions on DVFS

In this dissertation, we proceed by first analyzing design trade-offs at the circuit level and the system level respectively. Then, the interaction between the DC-DC converter design and the DVFS controller is studied. As an intermediate study, we show that performing system-level policy optimization without considering circuitlevel design can lead to suboptimal power and performance trade-offs. Finally, we demonstrate the benefit of cross-layer co-optimization of online-learning based the DVFS controller and the DC-DC converter and develop a two-step design flow. In the first step, we optimize the design of DC-DC converter for power loss, output voltage transition time, and area overhead. A pareto-optimal surface of the DC-DC converter designs is created for the next step. In the second step, system-level simulation is launched to generates a series of CPU usages based on the given DVFS operative periods. The online learning DVFS controller generates a series of operating points according to the CPU usages. Based on the operating points and the power loss of the DC-DC converter, the total energy and execution time are calculated. The global optimizer updates the results and tunes circuit-level converter designs to find the optimal DVFS policy and the optimal DC-DC converter design. The proposed design strategy is evaluated based on single-core processors, dual-core processors with global DVFS, and power-gated processors with DVFS respectively. Our study shows that the co-optimization of DVFS policies and the DC-DC converter can lead to noticeable additional energy saving without significant performance degradation.

#### 2. DECOUPLING STRATEGIES FOR POWER GATING\*

As stated in the last chapter, special design trade-offs exit in power-gated power delivery networks (PDNs). First, the trade-off between switching noise and rush current noise determines the power integrity. The switching noise is mainly suppressed by local decaps in typical PDN designs. But local decaps are the sources of rush current noise at the same time. These two types of supply noises must be balanced carefully in order to achieve the power integrity. Second, the trade-off between rush current noise and power consumption limits the application of power gating. Rush current noise is suppressed through extending turn-on time in typical power-gated PDN designs. At the same time, long turn-on time increases the energy overhead of power gating. Hence, the power gating application is restricted to long idle time. Finally, for a power-gated PDNs with multiple supply voltages, the design concern varies with the voltage levels. In this chapter, we use global decaps and re-routable decaps to balance the trade-offs between supply noises and energy saving of powergated PDNs. Diverse decap configurations are proposed to address the design issues of the PDNs with multiple supply voltages.

#### 2.1 Design of Power-Gated PDNs with Single Supply Voltage

In this section, we consider the design issues associated with power-gated PDNs with single supply voltage. We first discuss the design trade-offs between power integrity and power efficiency. In order to balance the trade-offs, local/global decap

<sup>\*</sup>Part of this chapter is reprinted with permission from "Decoupling for power gating: Sources of power noise and design strategies" by Tong Xu, Peng Li and Boyuan Yan, 2011. In Proceedings of the 48th Design Automation Conf. (DAC), pages 1002–1007, Copyright[2011] by ACM.

Part of this chapter is reprinted with permission from "Design and optimization of power gating for DVFS applications" by Tong Xu and Peng Li, 2012. In 2012 13th International Symposium on Quality Electronic Design, pages 391–397, Copyright[2012] by IEEE.

strategy and local/global/re-routable decap strategy are proposed respectively.

### 2.1.1 Background

The typical structure of power-gated PDN is shown in 1.1. The PDN is composed of an off-chip package and on-chip power grids. The off-chip package includes the models of PCB and C4 bumps. The on-chip part includes a global VDD grid, a global GND grid and multiple local power-gated grids (power domains). Each local power grid is connected to the global VDD grid through switchable sleep transistors. The power gating process is implemented through controlling the sleep transistors.

Fig. 2.1 presents the process of power gating. When the local grid is busy, sleep transistors are turned on to supply the power for the local grid. The sleep transistors are turned off as soon as the idle cycles start at  $t_1$ . The supply voltage of the local grid gradually falls to 0. When the idle cycles end at  $t_2$ , the sleep transistors are turned on. It takes time  $T_{on} = t_3 - t_2$  to wake up the local grid and recharge the local decaps to  $V_{DD}$ . After voltage recovery at  $t_3$ , the local grid starts to work again. The leakage consumption is saved through power gating during the power-off idle cycles  $T_{idle} = t_2 - t_1$ .

During the power process, the net energy saved by power gating is given as

$$E_{save} = E_{leak} - E_{over}, \qquad (2.1)$$

where  $E_{leak}$  is the leakage energy saved by power gating during  $T_{idle}$  and  $E_{over}$  is the energy overhead of the power gating. The time point at which the leakage saving compensates the energy overhead ( $E_{leak} = E_{over}$ ) is the break even point  $t_{BEP}$ . The break even time is defined as  $T_{BE} = t_{BEP} - t_1$ . If  $T_{idle} < T_{BE}$ , the energy overhead overwhelms the leakage saving and thereby the power gating should not be applied to the idle time slot.

Figure 2.1: Schematic of power gating process. The sleep transistor is supposed to be turned off as soon as the idle cycles arrive.  $t_{BEP}$  is the break even point at which the energy saving compensates the energy overhead ( $E_{leak} = E_{over}$ ).

Supply noises suppression is an important design concerns of power-gated PDNs. Switching noise and rush current noise are the two types of supply noises appear during the power gating process.

In typical power-gated PDN designs, local decaps are mainly used to suppress the switching noise [12, 13, 14, 49, 50]. There works improve the efficiency of onchip decaps from the perspective of distribution, material or structure. However, the decaps are mainly allocated on local grids to suppress switching noise. They are not effectively used to reduce rush current noise. In contrast, local decaps are the sources of rush current noise during the process of wake up.

The rush current noise is typically suppressed through extending turn-on time  $T_{on}$ [15, 32, 33, 34, 16, 17]. Stepwise wake-up techniques are proposed in [15, 32]. These techniques turn on the sleep transistor in stepwise manners. The stepwise wake-up process can be implemented in either by dynamically controlling the gate-to-source voltage of a sleep transistor or by turning on only a portion of the sleep transistor at one time. A local grid is slowly turned on until the drain-to-source voltage of sleep transistors are significantly reduced. Then the local grid is turned on completely until the voltage recovers to  $V_{DD}$ . The peak of rush current is controlled in safe range by these techniques. In [33], the rush current is reduced through turning on the local domains at different time. The logic cells are divided into small power domains. The sleep transistors of these domains are driven by a driver tree. The local domains are turned on at different time through slewing the delay of sleep transistor drivers. Multiple wake-up phases are proposed in [34]. The entire turning on process is partitioned into three stages. The turn-on scheme reduces the rush current during its metastable period of operation, while boosting the power supply rail when no short circuit current paths exist in the logic. However, the entire turnon time is extended and thereby the leakage saving is reduced. Multiple sleep modes

with different sleep depths are proposed in [16, 35]. In the detest sleep mode, the local grid is completely turned off during idle time. For the other sleep modes, the voltage of local grid falls to a certain level after power gating. In this case, a local grid in light sleep mode can be waken up quickly with small rush current. Although the rush current of light sleep modes is reduced, the leakage saving of these modes is reduced correspondingly. Generally, these works suppress the rush current noise through extending the turn-on time. However, long turn-on time may reduce the opportunities of power gating and thereby reduce the leakage saving. In addition, the performance delay is increased due to the long turn-on time.

In order to address these drawbacks, we analyze the design concerns and trade-offs systematically in the following section.

# 2.1.2 Design Concerns and Trade-Offs