## DESIGN OF PATTERN MATCHING SYSTEMS: PATTERN, ALGORITHM, AND

## SCANNER

### A Dissertation

by

## HAO WANG

## Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

## DOCTOR OF PHILOSOPHY

| Chair of Committee, | Jyh-Charn Liu     |  |

|---------------------|-------------------|--|

| Committee Members,  | Rabi N. Mahapatra |  |

|                     | Guofei Gu         |  |

|                     | Jiang Hu          |  |

| Head of Department, | Nancy Amato       |  |

December 2013

Major Subject: Computer Engineering

Copyright 2013 Hao Wang

#### ABSTRACT

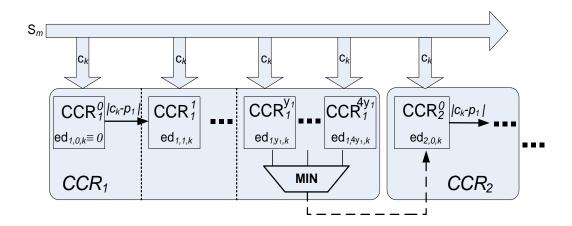

Pattern matching is at the core of many computational problems, e.g., search engine, data mining, network security and information retrieval. In this dissertation, we target at the more complex patterns of regular expression and time series, and proposed a general modular structure, named *character class with constraint repetition* (CCR), as the building block for the pattern matching algorithm. An exact matching algorithm named MIN-MAX is developed to support overlapped matching of CCR based regexps, and an approximate matching algorithm named Elastic Matching Algorithm is designed to support overlapped matching of CCR based time series, i.e., music melody. Both algorithms are parallelized to run on FPGA to achieve high performance, and the FPGAbased scanners are designed as a modular architecture which is parameterizable and can be reconfigured by simple memory writes, achieving a perfect balance between performance and deployment time. DEDICATION

To My Wife and Parents.

#### ACKNOWLEDGEMENTS

I would like to express the deepest gratitude to my advisor, Dr. Jyh-Charn (Steve) Liu, for his guidance and financial support throughout my Ph.D. study. He was patient when I struggled with research challenges, and gradually helped me out by hints and inspirations, rather than directly pointing out the solution. From him, I learned one of the most valuable assets in my life, critical thinking. I would also like to thank Dr. Rabi Mahapatra, Dr. Guofei Gu, and Dr. Jiang Hu for their precious time to serve as my committee members, and their valuable comments and suggestions on improving the quality of my work.

Many thanks to the staff and faculty of Texas A&M University, who made it a warm and enjoyable experience to pursue my graduate study. I would also like to thank my colleagues at the Real Time Distributed System laboratory, for their helpful comments and feedbacks on my research topics.

Finally, I would like to thank my parents, wife and elder brother for their ceaseless support, encouragement and love, without which I would never have been able to finish my Ph.D. study.

# TABLE OF CONTENTS

| ABSTRACT                                                                                                                             | ii       |

|--------------------------------------------------------------------------------------------------------------------------------------|----------|

| DEDICATION                                                                                                                           | iii      |

| ACKNOWLEDGEMENTS                                                                                                                     | iv       |

| TABLE OF CONTENTS                                                                                                                    | V        |

| LIST OF FIGURES                                                                                                                      | vii      |

| LIST OF TABLES                                                                                                                       | ix       |

| 1. INTRODUCTION                                                                                                                      | 1        |

| <ul> <li>1.1 Design Challenges</li> <li>1.1.1 Pattern Expressiveness</li> <li>1.1.2 Tolerance of Noises</li> </ul>                   | 3        |

| <ul> <li>1.1.3 Overlapped Matching</li> <li>1.1.4 Architectures of Scanner</li> <li>1.1.5 Reconfiguration Time of Scanner</li> </ul> | 6        |

| <ol> <li>Research Work and Contribution.</li> <li>Dissertation Outline.</li> </ol>                                                   |          |

| 2. REGEXP MATCHING SYSTEM                                                                                                            | 11       |

| <ul> <li>2.1 Background and Related Works.</li> <li>2.2 CCR Matching Algorithms</li></ul>                                            | 15       |

| <ul><li>2.2.2 MIN-MAX Algorithm</li><li>2.2.3 Matching Collisions and Collision-free Conditions</li></ul>                            | 18<br>30 |

| <ul> <li>2.2.4 Retrospection of Matching Lengths</li> <li>2.3 CES Scanner Design</li> <li>2.3.1 CCR Architecture</li> </ul>          | 38       |

| <ul> <li>2.3.1 CER Architecture</li> <li>2.3.2 CES Architecture</li> <li>2.4 Experiments and Evaluation</li> </ul>                   | 41       |

| <ul><li>2.4.1 Synthesis Results</li><li>2.4.2 Live Experiments</li></ul>                                                             | 45<br>48 |

| <ul><li>2.4.3 Case Study: Snort</li><li>2.5 Summary</li></ul>                                                                        |          |

| 3. MELODY MATCHING SYSTEM               | 55 |

|-----------------------------------------|----|

| 3.1 Background and Related Works        |    |

| 3.2 System Modeling                     |    |

| 3.2.1 String Model for MIDI Files       |    |

| 3.2.2 CCR Model for User Query          |    |

| 3.3 Elastic Matching Algorithm          |    |

| 3.3.1 Sequential Version                |    |

| 3.3.2 Parallelization                   |    |

| 3.4 Melody Matching Engine Design       |    |

| 3.4.1 FPGA End                          |    |

| 3.4.1.1 ACCR                            |    |

| 3.4.1.2 Melody Matching Engine          | 79 |

| 3.4.2 Integration with PC End           |    |

| 3.5 Experiments and Evaluation          |    |

| 3.5.1 Synthesis Results                 |    |

| 3.5.2 Parameter Tuning                  |    |

| 3.5.3 Performance Comparison            | 90 |

| 3.6 Summary                             |    |

| 4. CONCLUSION                           | 94 |

| REFERENCES                              | 97 |

| APPENDIX A. PROOF FOR MIN-MAX ALGORITHM |    |

| APPENDIX B. CONTEXT-DEPENDENT FEATURES  |    |

# LIST OF FIGURES

| Figure 1. Syntax tree for R <sub>1</sub>                                                                                                                                                                                     | 17 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2. State transitions in a CCR                                                                                                                                                                                         | 23 |

| Figure 3. Illustration of matching burst, front, and tail                                                                                                                                                                    | 27 |

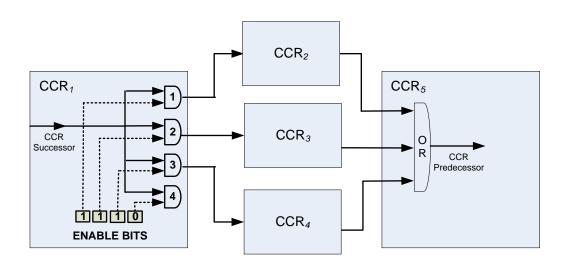

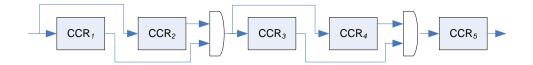

| Figure 4. The architecture of a CCR engine                                                                                                                                                                                   | 39 |

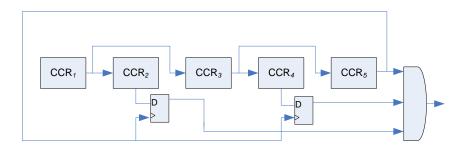

| Figure 5. Interconnection architecture of R <sub>3</sub>                                                                                                                                                                     | 40 |

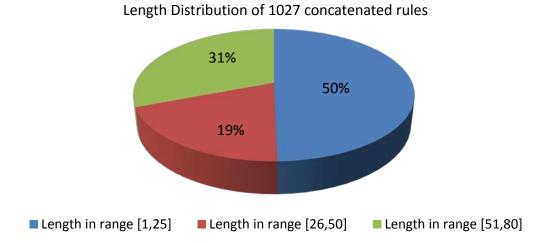

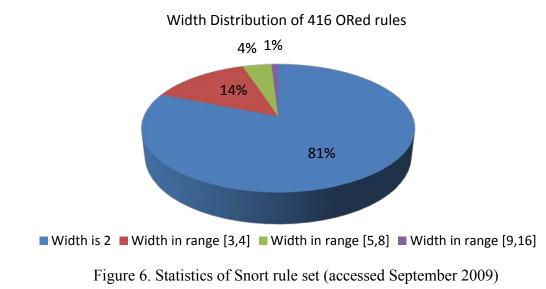

| Figure 6. Statistics of Snort rule set (accessed September 2009)                                                                                                                                                             | 42 |

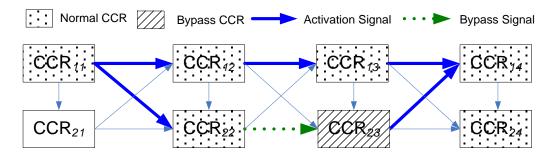

| Figure 7. Implementation of R <sub>7</sub>                                                                                                                                                                                   | 44 |

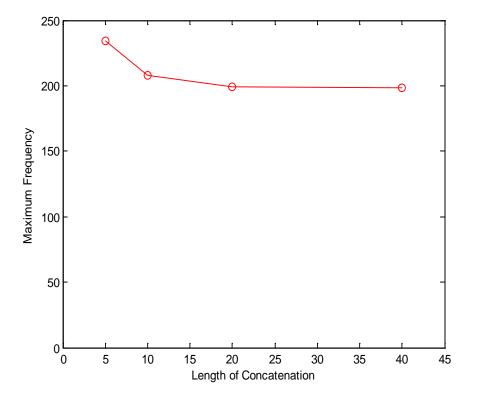

| Figure 8. Maximum frequency vs. length of concatenation                                                                                                                                                                      | 46 |

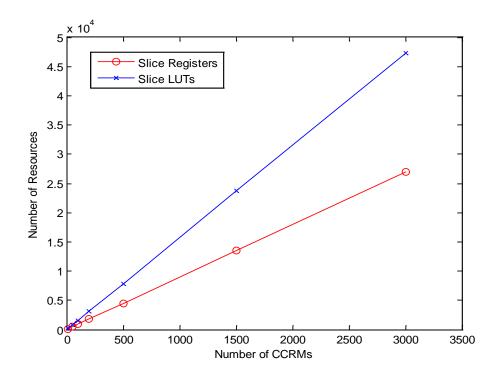

| Figure 9. Resource utilization vs. number of CCRs                                                                                                                                                                            | 47 |

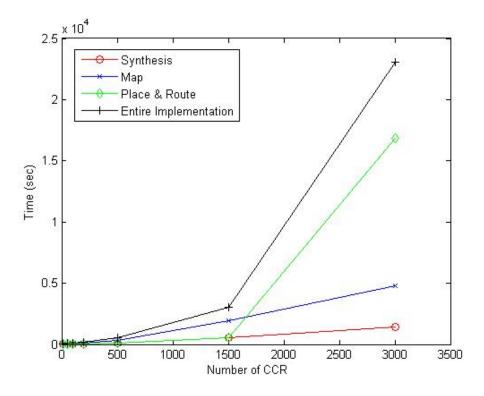

| Figure 10. Implementation time vs. number of CCRs                                                                                                                                                                            | 48 |

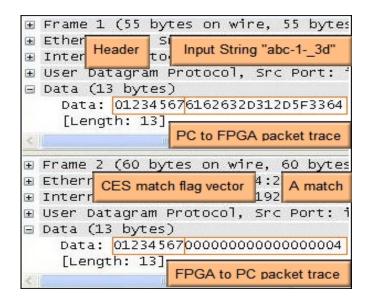

| Figure 11. Input string and output match vector packet                                                                                                                                                                       | 50 |

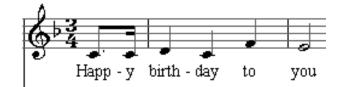

| Figure 12. Musical score of "happy birthday to you"                                                                                                                                                                          | 60 |

| Figure 13. State transition diagram                                                                                                                                                                                          | 69 |

| Figure 14. Pseudo code of elastic matching algorithm                                                                                                                                                                         | 71 |

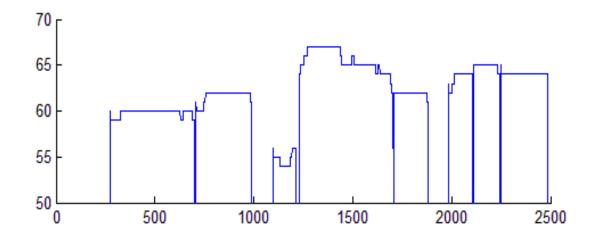

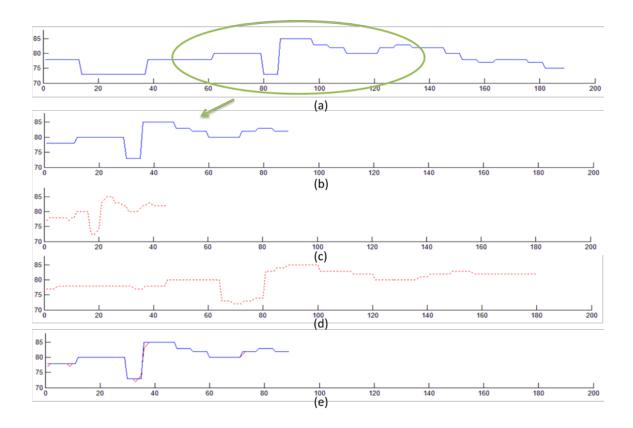

| Figure 15. User query of "my heart will go on"                                                                                                                                                                               | 73 |

| Figure 16. (a) Original MIDI string (b) Matched portion of MIDI string (c) Fastest<br>allowed tempo of user query (d) Slowest allowed tempo of user query (e)<br>Tempo-adaptive alignment between MIDI string and user query | 73 |

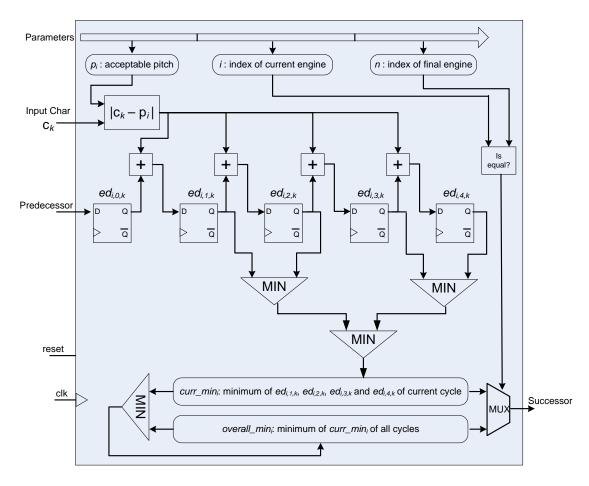

| Figure 17. Architecture of ACCR <sub>i</sub> engine                                                                                                                                                                          |    |

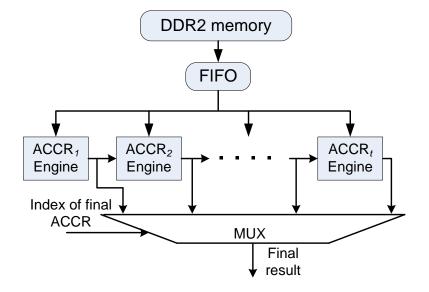

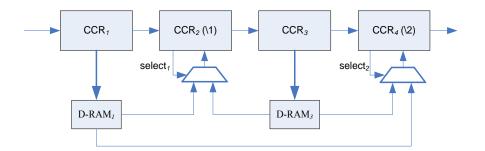

| Figure 18. Architecture of MME                                                                                                                                                                                               | 79 |

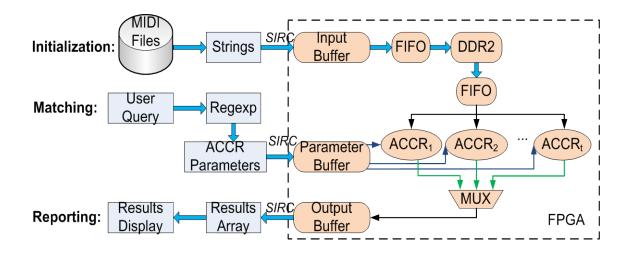

| Figure 19. System flow chart                                                                                                                                                                                                 |    |

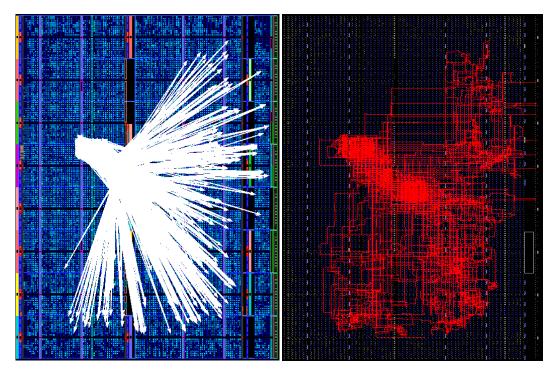

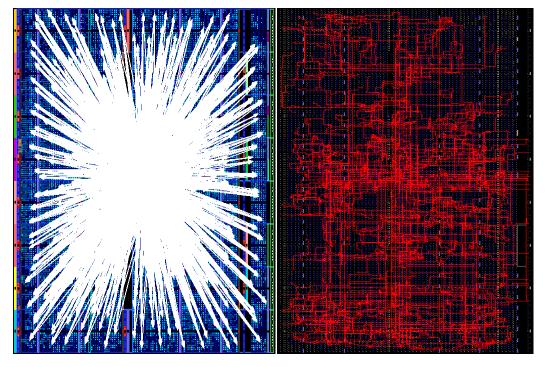

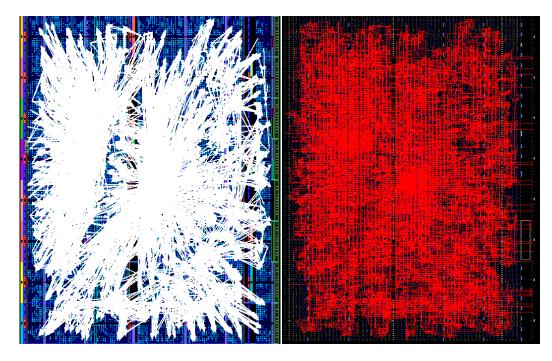

| Figure 20. (left) Interconnections of the MUX (right) Routing of the MUX                                                                                                                                                     | 85 |

| Figure 21. (left) Interconnections for input character from FIFO to ACCRs (right)<br>Routing for input character from FIFO to ACCRs      |     |

|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 22. (left) Interconnections from ACCRs to their successors and the MUX (right) Routing from ACCRs to their successors and the MUX | 86  |

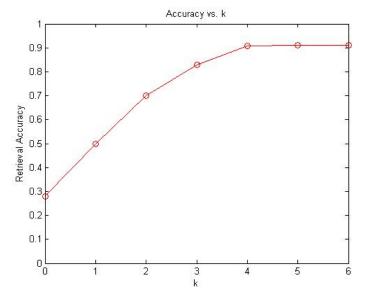

| Figure 23. Average-pitch variation threshold vs. accuracy                                                                                | 88  |

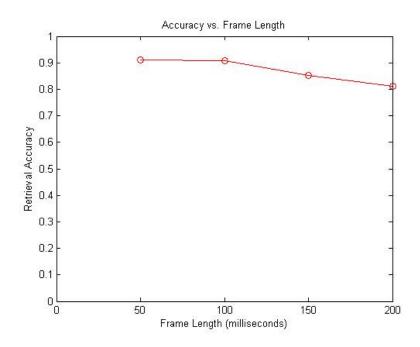

| Figure 24. Frame length vs. accuracy                                                                                                     | 89  |

| Figure 25. Implementation of R <sub>1</sub>                                                                                              | 117 |

| Figure 26. Implementation of R <sub>2</sub>                                                                                              | 118 |

| Figure 27. Implementation of R <sub>3</sub>                                                                                              | 119 |

# LIST OF TABLES

| Table 1. Single counter example                          | 20 |

|----------------------------------------------------------|----|

| Table 2. State transitions of CCRs based on MIN-MAX      |    |

| Table 3. False positive with overlapped matching         |    |

| Table 4. Statistics of regexp rule sets                  |    |

| Table 5. Backtracking procedure                          |    |

| Table 6. Number of context-dependent regexp rules        | 41 |

| Table 7. Regexp and CCR statistics of linear Snort rules | 51 |

| Table 8. CCR type and state distribution                 | 53 |

| Table 9. CSV version of "happy birthday to you"          | 61 |

| Table 10. Implementation time of MME                     |    |

| Table 11. Melody retrieval time                          | 91 |

| Table 12. Performance comparison                         |    |

#### 1. INTRODUCTION

Pattern matching has been a classical problem in the computing society, and it is often found at the heart of many contemporary applications such as data mining, search engine, information retrieval, and bioinformatics. The three major aspects of a pattern matching system are consisted of modeling of *patterns*, *matching algorithms*, and *scanner architectures*. In typical scenarios, the user specified pattern is fed into a scanner which will perform content inspections against the input data stream to determine its presence or absence based on certain matching algorithms.

Patterns are representations of symbols that need to be matched (detected) from an input data stream. Widely used patterns include *fixed string, time series*, and *regular expression* (regexp), and their matching problems may vary in complexity due to their different levels of expressiveness. Matching algorithms are computing logics that accepts an input data stream to be matched with the patterns to detect presence of the patterns in the input data. A matching algorithm is called *exact* if it only generates a matching signal when the input data match the pattern exactly. Alternatively, the matching algorithm may be *approximate* if a certain number of mismatches are allowed in the matching process. A matching algorithm that supports *overlapped matching* can detect patterns embedded anywhere in the input data stream, because it treats any input data as the starting point of a new sub-stream that may potentially match the pattern, and it maintains simultaneous matching algorithm needs to be transformed and configured into the formats most suitable for the scanner to match an input data stream at run time. Design of the scanner architecture needs to take both speed and reconfiguration time into account to achieve the best balance between system performance and deployment time.

Previous works in the literature often focus on a single aspect of the three components of pattern matching systems, e.g., new matching algorithm design without implementation considerations for the proper scanner, or high speed scanner design without consideration of deployment time. Their partial design usually does not translate to a practical and complete pattern matching system. In contrast, in this dissertation we will visit all three components and show a complete view on design of a pattern matching system, which involves design factors such as algorithm design and tailoring for a target scanner architecture, and tradeoffs among various design options.

#### 1.1 Design Challenges

In this dissertation we are mainly interested in complex patterns such as regexp and time series that can be re-represented in structures named *character class with constraint repetition* (CCR), which defines a set of *acceptable* characters and the range of times they can be matched for. CCRs can model complicated behaviors in compact forms, and its behavioral analysis is highly dynamic and recursive. Matching of CCR based patterns will become even more sophisticated in overlapped matching mode, where multiple matching processes for different sub-streams of the input data may coexist in the same CCR state. Therefore the matching algorithm needs to maintain dynamic matching activities of all existing matching processes, including, but not limited to, tracking matching progress, determining acceptance and asserting interaction signals between CCRs. Pattern matching systems usually require fast response time, and we choose FPGA as the scanner architecture for its massive parallelism and outstanding performance. To achieve best performance, we try to exploit the parallelism provided by FPGA architecture as much as possible in design of the matching algorithm, which complicates the modeling and analysis of algorithm because it needs to handle concurrent executions of all CCRs. In addition to performance considerations, we note that many pattern matching systems need to update their patterns to deal with emerging situations and therefore the time required to update patterns on the scanner is critical, yet often not accounted for in the literatures. It is a major design challenge to achieve fast deployment, as FPGA is notorious for its time-consuming synthesis, placing and routing process.

Next we will discuss the requirements and technical challenges in detail for modeling of patterns, matching algorithms, and scanner architectures in the following subsections.

#### 1.1.1 Pattern Expressiveness

The application of pattern matching dates back to 1960s when it is first used in text editors, and at that time the patterns involved are fixed strings of characters. These fixed-string patterns are easy to describe and understand, and their behaviors in the matching process can be easily modeled and captured, at the cost of a very limited level of expressiveness.

Since then, there had been an increasing demand on the ability to describe more flexible patterns, and regular expressions [1] are developed to accomplish this goal.

Regular expressions (regexps) are a sequence of characters with certain syntax and grammar specifications such that they can be used to describe a set of fixed strings conforming to certain criteria. Two most popular features are character class which defines a set of characters that are acceptable, and constraint repetition which is a quantifier defining the number of repetitions that a pattern can be matched. These two structures significantly expand the expressiveness in both dimensions of acceptable characters and their matching lengths. Their rich expressiveness has been widely applied to applications such as spam filters and network intrusion detection systems (NIDS) where a single regexp pattern can represent many variants of a fixed string pattern.

The aforementioned two types of patterns have been mainly used in computer related problems where signals are discrete and well defined. More recently, as sensor technologies advance, more and more data are sampled from real-world analog signals as time series which are a sequence of data points sampled consecutively in time with certain frequency, and there is a demanding need for mining of time series [2] patterns. Although they share the same general form as fixed strings, they are different from fixed string and regexp patterns because they have timing information embedded into the pattern itself, and the embedded tempos may vary from the ones of the input data stream. Time series patterns have a large domain of applications such as motion detection, handwriting recognition and melody matching.

### 1.1.2 Tolerance of Noises

In their early stages, most matching algorithms focus on exact matching of patterns, where any mismatches/errors will terminate the matching process and report a

mismatch. However, nowadays more and more systems are requiring the capability of approximate matching of patterns allowing certain amount of errors such as typos, signal noises, or mutations of DNA. As a result, new algorithms are developed to match patterns in an approximate manner with the capability to evaluate the similarity between patterns and input data streams under certain distance measure. These algorithms constitute the core of many scoring systems such as music retrieval and DNA sequencing.

Because exact matching algorithms do not need to maintain similarity information for the pattern during the matching process and all they need is a Yes or No match information, they usually have simper models and implantations than approximate matching algorithms. In the contrast, approximate matching algorithms have to keep track of the similarity measurements between the pattern and input data, and therefore they usually take more space to implement. Moreover, due to their early-termination policy, exact matching algorithms tend to have better performance than approximate matching algorithms because the later one needs to continue running even on a mismatch.

### 1.1.3 Overlapped Matching

Intrinsically, the pattern to be searched may appear at any position of the input data stream, and therefore all sub-streams of the input need to be inspected against the pattern to guarantee correct detections. This is referred to as overlapped matching, which means that every input data needs not only inspected as part of previous sub-streams, but also as the beginning of a brand new sub-stream, so that all possible sub-streams are inspected and the complete search space is explored.

Many different ways have been developed to support overlapped matching, among which the simplest one is to initiate a new matching process at every position of the input data stream. This straightforward method will restart matching at position i+1 if the sub-streaming starting at position i is determined to be a mismatch, leading to a significantly longer runtime that is n (the length of pattern) times slower, because in the worst case every matching process proceeds to the second to last position of the pattern and then fails and restarts. There are smarter algorithms that can re-use the information gathered from the previously failed matching process to avoid unnecessary work when starting the new matching process, such as the Knuth-Morris-Pratt algorithm [3] for fixed string patterns.

Similar algorithms exist for the more complex regexp patterns, where they are converted to non-deterministic finite automata (NFA) [4] that store the information of all on-going matching processes in their states. Due to the rich expressiveness and flexibility of regexp patterns, it is possible that multiple matching processes stay at the same state, and it is the NFA based matching algorithm's responsibility to resolve the ambiguities of all these concurrent matching processes started from different positions of the input data stream.

#### 1.1.4 Architectures of Scanner

As silicon technologies evolve, more computing platforms have been developed to meet the needs of various problems. Von Neumann [5] based CPU architecture has been the traditional choice for most pattern matching algorithms, where the programs are executed sequentially, and few, if not none, dependence issues need to be taken care of.

More recently, the community has seen a considerably growing trend of parallel computing, based on the massive parallelism offered by modern Graphic Processing Unit (GPU) [6] and Field Programmable Gates Array (FPGA) [7] devices. GPUs are based on the Single Instruction Multiple Thread (SIMT) [8] architecture where each core is responsible for execution of one thread and many cores run in parallel. The behaviors of cores are defined by the vendors, and they need to be programmed following the CUDA [9] or OpenCL [10] language specifications. The GPU cores are much more lightweight than traditional CPUs and the context switch time is significantly reduced such that many threads can be swapped in or out of the core and other threads can run when one is waiting for slow-to-access resources such as the global memory, i.e., hiding the latency. Although each GPU core is less powerful than a CPU, their parallel execution leads to a much higher processing throughput. The SIMT architecture implies that peak performance can be achieved only if all threads agree on the same execution path, otherwise multiple instructions must be issued for divergent execution paths and they are executed sequentially on different cores. This must be taken account into the design of the pattern matching algorithm.

Among the three, FPGA has the finest-grain of granularity where the scanner can be configured in the gate-level, and it is highly customizable which means that the designer has full control of every implementation detail. Programs executing on FPGA run on the bare hardware with minimum overhead caused by operation systems, drivers, and other abstraction layers. The designer is responsible for developing everything from scratch including the circuitry of each function, as well as the interfaces and pipelines between function units to ensure correct timing. This is usually a much more tedious process than GPU and CPU based scanners because the later two have well-established and documented driver and application programming interface to handle the scheduling and communication of processes. However, FPGA usually achieves the best performance gain even if their operation frequency is slower than that of GPU and CPU, because the instructions are issued and executed in real-time single cycles.

#### 1.1.5 Reconfiguration Time of Scanner

It is not uncommon to update the patterns after they have been fed into the scanner, such as the rule set update for network intrusion detection systems and the user query update for music retrieval systems. This implies implementing the new model as well as matching algorithm tailored for the new pattern onto the scanner architecture. For CPU and GPU based scanners, this is a simple matter of re-compilation of the source code which can usually be done in seconds. However, for FPGAs, the contents and routings of the hardware need to be reconfigured in the physical level, which translates to a reconfiguration time of hours.

Although CPUs and GPUs are easier and faster to reprogram, they may not be able to meet the performance requirement enforced by the applications. As for FPGAs, their time-consuming reconfiguration leads to long turnaround time which is unacceptable for online pattern matching engines such as NIDS or user-centric applications such as music melody matching system. Therefore, the reconfiguration time is of great concern in design of FPGA based scanner.

### 1.2 Research Work and Contribution

In this dissertation, we target at complex patterns such as regexps and time series and developed the corresponding matching algorithm for both exact and approximate matching. The models and algorithms for exact and approximate matching are illustrated using network intrusion detection system Snort and music melody matching system as examples, respectively. The matching algorithms are developed based on NFA to support overlapped matching, and FPGA is selected as the scanner architecture to exploit the intrinsic parallelism of the algorithm and achieve best performance. The scanner is designed into a modular architecture such that its parameters are stored in on-chip memories and therefore can be rapidly updated by simple memory writes.

Our research work and contributions regarding each component of the pattern matching system, i.e., pattern, matching algorithm and scanner architecture, are summarized as follows.

Pattern:

- General, uniform CCR module for regexp

- General, uniform ACCR module for time series

- Ease of parallelization

Matching algorithm:

- MIN-MAX algorithm for exact matching of regexp

- Support of overlapped matching

- Resolution of matching ambiguity

- Parallel execution

- Elastic algorithm for approximate matching of time series

- Evaluates similarity of pattern

- > Parallel execution

- Proof of correctness

Scanner architecture:

- FPGA based modular architecture

- Memory parameterizable

- Rapid reconfiguration in milliseconds

In addition to the abovementioned contribution, we also resolved other open problems encountered in the development of the matching algorithms, which will be detailed in their corresponding sections.

### 1.3 Dissertation Outline

The rest of this dissertation is organized as follows. In section 2 we visit the problem of exact matching for regexp patterns, targeting at the network intrusion detection system Snort. In section 3 we explore the problem of music melody matching, which can be modeled as approximate matching of regxp patterns. The dissertation is concluded in section 4.

### 2. REGEXP MATCHING SYSTEM\*

In this section we discuss the design of a regexp pattern matching system. Regexps have been a popular way to extract the features of malicious behaviors of network intrusions, and in these applications they are often required to be matched exactly to claim detection of an attack. Also, the emerging large volume of internet traffic puts a high demand on the speed and throughput of the scanner. As such, we choose FPGA as the scanner architecture to meet the performance requirements, which imposes an extra design challenge to reduce the time-consuming reconfiguration process.

The following of this section is organized as follows. In subsection 2.1 we introduce some background information and related works in the domain of regexp matching system. We then propose our CCR model as the general modular building block to re-write regexps, and develop its corresponding matching algorithms in subsection 2.2. Design of the FPGA-based scanner is covered in subsection 2.3, and experiments and evaluations are conducted in subsection 2.4. Finally, subsection 2.5 summarizes the design of the regexp matching system.

### 2.1 Background and Related Works

Regular expression (regexp) matching is a pattern matching technique, where a set of patterns are represented in regular expressions, so that they can be used to check if the input string contains the target patterns. Various regexp matching engines have been

<sup>\*©2013</sup> IEEE. Reprinted, with permission, from H. Wang, S. Pu, G. Knezek and J.-C. Liu, "MIN-MAX: A Counter-Based Algorithm for Regular Expression Matching", *IEEE Transactions on Parallel and Distributed Systems*, Volume 24, Issue 1, pp. 92-103, 2013

designed to achieve one or more specific objectives, e.g., speed, storage sizes, and complexity of patterns, etc. They are used for a wide range of applications: compilers, bioinformatics, and most recently Network Intrusion Detection Systems (NIDS) such as Snort [11], Bro [12], L7 [13] and spam filters such as SpamAssassin [14], etc. Rapid escalation of network security problems has led to explosive growth of the number and complexities of regexp based rules in these and other similar systems. For instance, the number of regexp rules in Snort has increased from 509 (Apr. 2006) [15] to 1667 (May. 2011), and over 60% of rules in SpamAssassin are involved with regexp matching [16]. Regular expressions have significantly expanded from their classical form [4] to support character class, which is a set of characters that are acceptable to a matching state, and constraint repetition, which is a quantifier defining the number of repetitions that a state can be matched. For example, both character classes (in 1253 regexps) and constraint repetitions including wild cards (in 1600 regexps) are heavily used in the latest version of Snort, and a similar conclusion can be made for SpamAssassin. When the two constructs are used together as a regexp term, it is called a Character Class with Constraint Repetition (CCR).

Regexp matching engines mainly fall into Deterministic Finite Automata (DFA) or Non-deterministic Finite Automata (NFA). Both NFA and DFA [4] have been widely studied for string matching. Memory efficiency is critical for conversion of an NFA to its equivalent DFA [17]. Rewriting and grouping of regexps were proposed to alleviate the state explosion problem of DFA [18].

DFA is a preferred choice for high-performance applications. It was used for content scanning of firewall [19] and spam filtering (conversion of SpamAssassin (SA) regexp rules into DFAs by JLex [20]). Ternary CAM was proposed for fast table lookup [21]. The notion of path ambiguity is the main cause of state explosion in DFA [22]. Modified CAM (m-CAM), memory banks, and data packing techniques were proposed to compact the DFA size [23]. Another table compression technique proposed in [24] can handle variable length inputs. The D<sup>2</sup>FA explored states that share the same transition trigger input to reduce redundancy [25]. The  $\delta$ FA architecture stores only the differences between adjacent states to reduce the number of states and transitions [26]. S. Kumar et al. [27] used auxiliary variables to hold previous transition information. Merging non-equivalent DFA states by adding extra labels on those merged states' transitions was proposed in [28]. Other optimization techniques are also proposed, with the time complexity ranging from  $O(n^2)$  in [25], [18],  $O(n^3)$  in [22], to  $O(n^3 \log n)$  in [28]. All these methods need to traverse the entire DFA state transition table to determine which transitions or states are qualified for optimization.

Overlapped matching requires the automata's starting state to be always *active*, i.e., checking for matching of every input character, so that each incoming character will be regarded as the starting of a new string. DFA architecture cannot support overlapped matching because it allows only one single active state. In contrast, NFA allows multiple active states to exist simultaneously, and therefore is better suited for matching of complex, dynamic patterns.

As regexp based matching algorithms are being used for advanced applications, parallel processing architectures, especially FPGAs, are being used for their implementation. Code generation proved to be an effective technique, e.g., translation of PCRE op-codes into VHDL codes [29]. A Python-based compiler was proposed to translate regexps into instructions for a VLIW architecture on FPGA [30]. Selection of basic building blocks is an important design issue for code generation. The four building blocks *single character*, *OR*, *concatenation*, and *kleene star* proposed in [31] have been widely used in different studies [15],[32].

A shift register based architecture was proposed in [15] for  $\{n, \}$  (constraint repetition for matching at least *n* times),  $\{m,n\}$  (constraint repetition for matching no less than *m* times and no more than *n* times), and  $\{n\}$  (constraint repetition for matching exactly *n* times) to count the matching repetitions of regexps with memory size of O(log *n*) for  $\{n, \}$  and O(n) for  $\{m,n\}$  and  $\{n\}$ . A counter based design proposed in [33] reduced the memory cost to O(log *n*), but this design does not support resolution of character class ambiguity, which refers to the condition that when an incoming character can be matched by (accepted to) two adjacent CCRs, the assignment choice may lead to different matching outcomes.. To the best of our knowledge, CES is the first scanner architecture to resolve character class ambiguity in overlapped matching mode, at the memory cost of O(log *n*) for constraint repetitions.

Resource minimization is important for design of FPGA based regexp scanners. Main techniques include sharing of logic (for sub-prefixes, -infixes, and –suffixes) [34], reduction of memory size [35], mitigation of resource explosion for large regexp rule sets [36], and multi-character NFA decoder [37], etc. The authors of [38] explored several recently developed algorithms and techniques such as edge-minimization, alphabet- reduction and stride-increasing, and evaluated their joint application on FPGAs and memory-based ASICs.

#### 2.2 CCR Matching Algorithms

In this section we first propose the CCR model as a general modular representation for regexp patterns in subsection 2.2.1, and then develop the MIN-MAX matching algorithm in subsection 2.2.2 based on the matching burst model. A further study on the dynamic behaviors of matching bursts reveals the fact that CCRs may suffer from matching collisions and lead to incorrect matching results, and in subsection 2.2.3 we develop several heuristic rules to analyze the regexp pattern and guarantee that matching collisions will never occur to regexps conforming to these rules. The formal proof of the MIN-MAX matching algorithm and the collision-free rules are detailed in Appendix A, and based on the rigorous proof process we developed several retrospection rules in subsection 2.2.4 to track back matching lengths after a match is claimed.

#### 2.2.1 CCR Model

In this section, we propose a new structure, named *character class with constraint repetition* (CCR) to combine the two complex features of regular expressions and represent complex patterns in a compact format. To ease the discussion, we consider regexps consisting of only CCRs in our discussion. Consider a CCR based regexp  $R_n=CCR_1 \cdot ... \cdot CCR_n$  and an input string  $I_m=\{c_1, ..., c_m\}$ , where CCR<sub>i</sub> has the general format of a character class CC<sub>i</sub> followed by the constraint repetition { $b_i^L, b_i^U$ }, and  $c_j$  is

the  $j^{th}$  input character of I<sub>m</sub>. We use the term *cycle* to denote the duration for processing of one character by a matching system, i.e.,  $c_j$  is processed at cycle j. The concept of cycle will also facilitate the subsequent discussion in temporal domain. Real world Perl/POSIX [39][40] regexps are usually not in pure CCR format. However, according to the grammar of *regular language* [39][40], they can always be rewritten as a sequence of CCR terms interconnected by '•' (CONCATENATION) or '|' (OR) operators. *Parentheses* (also known as *groups*) are not actual operators, but only used to force certain precedence orders.

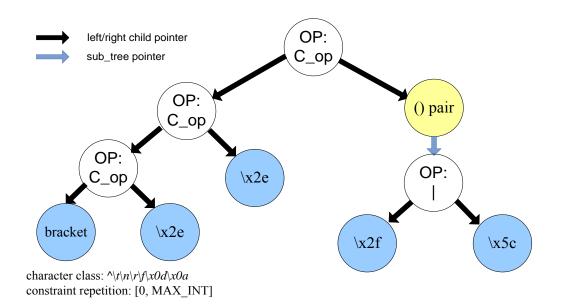

We developed a syntax tree parsing tool to extract CCR terms and their operators from a Perl/POSIX regexp, where the syntax tree is optimized for easy mapping to the scanner architecture. *Tokenization* is the first step to translate a Perl/POSIX regexp to its equivalent CCR based representation. To start, the implicit concatenation operators are represented explicitly as '•''. For example, a Perl regexp based Snort rule,

$R_1: [^x x 0d x 0a] * x 2e x 2e (x 2f x 5c),$

is represented as the expression "[ $\lambda d x0a$ ]\*  $x2e \cdot x2e \cdot (x2f / x5c)$ ". After tokenization, the syntax tree can be generated by backward parsing the token set. Succinctly put, the syntax tree structure has the following characteristics.

- (1) Internal nodes represent logic operators ('•' or '|'), and leaf nodes represent CCRs.

- (2) A sub-tree is constructed when a sub-regexp is surrounded within a pair of parentheses. The sub-root node represents the pair of parentheses.

- (3) Internal nodes have two children nodes. If both of them are leaf nodes, then the left (right) child represents its parent logic operator's left (right) operand. Otherwise, the

left (right) child must be an internal (leaf) node which represents its parent logic operator's preceding operator (right operand).

After the syntax tree is generated, different types of constraint repetitions are translated into the "*Between*" format  $\{m,n\}$ , where *m* and *n* represent the lower and upper bounds of the constraint repetition, respectively. Using MAX\_INT to denote the largest integer supported by the scanner, "*Exactly*" ( $\{m\}$ ) is translated to  $\{m,m\}$ , "*AtLeast*" ( $\{m,\}$ ) to  $\{m, MAX_INT\}$ , '\*' to  $\{0, MAX_INT\}$ , '+' to  $\{1, MAX_INT\}$ , and '?' to  $\{0, 1\}$ .

As an illustration, Figure 1 depicts the syntax tree for the following Perl regexp based Snort rule

$R_I: [^x x0d x0a] x2e x2e (x2f x5c)$

Figure 1. Syntax tree for R<sub>1</sub>

#### 2.2.2 MIN-MAX Algorithm

Matching of  $R_n$  against  $I_m$  is combination of an ordered matching problem (in which the tail of string cannot be matched before the head has been accepted), and a combinatorial search problem (where at each matched CCR location, one will need to decide to stay on the same CCR or move forward to the next one when both of them can accept the input symbol).

Succinctly put, we need to determine whether or not  $I_m$  can be split into substrings  $S_n = \{s_1, ..., s_n\}$ , such that for all  $s_i$  in  $S_n$ , where  $l \le i \le n$ ,  $s_i$  is *acceptable* to CCR<sub>i</sub>. This means that element characters of  $s_i$  are all in CC<sub>i</sub> and the length of  $s_i$ , denoted by  $L_i$ , falls in the range of  $[b_i^L, b_i^U]$ . Enumeration is the only way to get all feasible length assignments of  $L_i$ , and each feasible assignment is referred to as a *matching path*. We develop a combination of *interaction rules* between CCRs, and also *counting rules* for the number of matches made in a CCR for regexp matching. We further develop a *retrospection rule* to store useful information in the forward scanning direction, which can then be used by *matching length calculation rules* to calculate  $L_i$  in a backward fashion after a matching is declared at the last stage of the CCRs (i.e., retrospection of matching path).

While one or more matching paths may be found when a regexp is matched, it is cost prohibitive to find all feasible splits of  $I_m$  (i.e., retrospection of all possible matching paths). Instead, our design aims to generate one single matching signal at cycle *m* if  $I_m$  can match  $R_n$ , and this usually suffices for practical applications.

There has been research efforts [33] to use counters to check whether or not it satisfies the repetition constraint, which however may suffer from false negatives because it only searches part of the search space. In their design, the matching count of an active state CCR<sub>*i*</sub>, denoted by counter<sub>*i*</sub>, is incremented by 1 when an acceptable character arrives. CCR<sub>*i*</sub> activates CCR<sub>*i*+1</sub> to start evaluating subsequent characters when counter<sub>*i*</sub> reaches  $b_i^L$ . CCR<sub>*i*</sub> becomes inactive when counter<sub>*i*</sub> reaches  $b_i^U$  or the input character is unacceptable. This scheme works fine when adjacent CCRs do not have any common acceptable characters, otherwise the design cannot resolve character class ambiguity. This is because after CCR<sub>*i*</sub> matches a character c<sub>*i*</sub>, and its repetition count has exceeded  $b_i^L$  but not  $b_i^U$ , it could continue to check for the next character c<sub>*i*+1</sub>, or alternatively activate CCR<sub>*i*+1</sub> to start checking from c<sub>*i*+1</sub>. With only one single counter, there is no way to keep track of both possibilities, and therefore it is subject to false negatives.

This problem can be illustrated by the following example taken from the tracker ID rule of the SpamAssassin regexp rule set, where the three CCR terms have overlapped character class subset [a-z0-9]:

body TRACKER\_ID

$$/^[a-z0-9]{6,24}[-a-z0-9]{12,36}[a-z0-9]{6,24}\s^{z/is}$$

Let  $R_2 = CCR_1CCR_2CCR_3$  denote the three CCR terms in this example, and we reduce their constraint repetitions to "{2,4}, {3,4}, and {2,5}" respectively for ease of discussion. That is, we use

$R_2$ :  $[a-z0-9]{2,4}[-a-z0-9]{3,4}[a-z0-9]{2,5}$

as the example throughout this section.

Table 1 gives an example to illustrate the false detection when character class ambiguity is present, where  $R_2$  is used to match against the input string "*abc-1-\_3d*". When the scanner processes character '*c*' which is acceptable to both CCR<sub>1</sub> and CCR<sub>2</sub>, two possibilities exist: 1) '*c*' is matched by CCR<sub>2</sub> and counter<sub>2</sub> increments to one, and 2) '*c*' is matched by CCR<sub>1</sub> and counter<sub>2</sub> remains zero. Based on the lazy matching model, the matching engine in [33] will pick up option (1) and follow the searching path of {"*ab*", "*c*-1", "-\_3*d*"}, which leads to the incorrect conclusion that the example string cannot match  $R_2$  because "-\_3*d*" is not acceptable to CCR<sub>3</sub>. However, choice (2) will get the feasible searching path of {"*abc*", "-1-\_", "3*d*"}.

Table 1. Single counter example

| abc-13d | CCR <sub>1</sub>                                                                                                                                    | CCR <sub>2</sub>                                                                                                         | CCR <sub>3</sub>                                                                                                    |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Counter | $\begin{array}{c} 1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow 1 \\ \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \end{array}$ | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 4$<br>$\rightarrow 0 \rightarrow 0 \rightarrow 0$ | $0 \rightarrow 0 \rightarrow 0$ |

To solve the character class ambiguity problem, we propose using two counters  $(MIN_i, MAX_i)$  to track the minimum and maximum number of characters that  $CCR_i$  may have matched. In other words, the two counters together define a feasibility zone of all possible counts of matching for  $CCR_i$ . When a new (or old) possible matching count of  $CCR_i$  needs to be added (or deleted), we can adjust the bounds of the feasibility zone by

simple adjustment of the two counters. The counting and interaction rules are designed to implement adjustments of (MIN,MAX) to guarantee correct matching outcome in the forward matching direction. The retrospection rule saves useful counter information which will be later used by matching length calculation rules to compute matching lengths in the backward direction. By relaxing the tighter condition "explicitly track every possible matching count" to "group all possible matching counts into a range", we avoid tracking every possible matching count for each CCR during the matching process, and the space complexity to implement constraint repetition of n is O(log n), as compared to O(n) for conventional NFA based methods [31][15]. As it will become clear shortly, this technique is guaranteed to match a regexp if it exists in the input string.

In addition to resolving character class ambiguity, overlapped matching is another important feature to eliminate subtle false negatives, as the example illustrated in [17] where the regexp of "*telephone* | *phonebook*" is used to match against the string of "*telephonebook*". Without overlapped matching support, only "*telephone*" can be matched. But with overlapped matching enabled, both "*telephone*" and "*phonebook*" can be matched. Overlapped matching is critical for detection of embedded strings such as malicious (executable) contents embedded in digital media packets. In the overlapped matching mode, CCR<sub>1</sub> needs to be permanently active so that it is always ready to match against a new incoming substring.

Modeling, analysis and proof of solutions for character class ambiguity and overlapped matching for CCR based regexps are highly recursive. To eliminate notational ambiguity, next we will first introduce the structure of a CCR engine and its operational rules, i.e., the MIN-MAX algorithm, and then proceed with their modeling and analysis. For simplicity, we illustrate the algorithm using linearly concatenated CCRs, and support for CCRs ORed in parallel will be covered later.

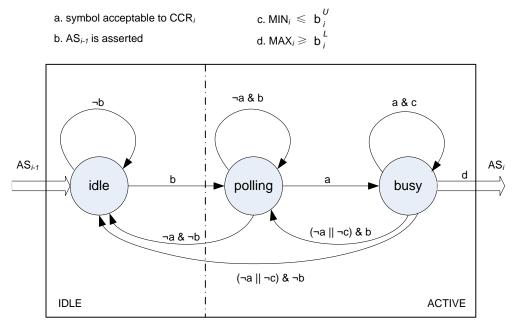

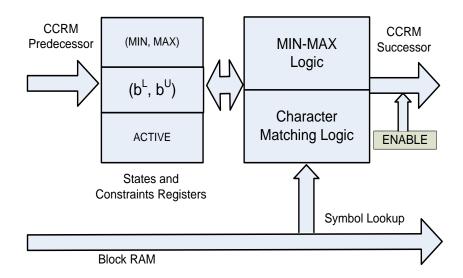

CCR<sub>*i*</sub> consists of two counters (MIN<sub>*i*</sub>, MAX<sub>*i*</sub>), two stored constraint repetition parameters ( $b_i^L$ ,  $b_i^U$ ), a memory-based character class CC<sub>*i*</sub>, and an active-state flag ACTIVE<sub>*i*</sub>. A CCR can be in one of three states: *idle*, *polling* and *busy*, where the latter two are collectively called the *active* state in later discussions. Externally, CCR<sub>*i*</sub> has an input (output) activation signal AS<sub>*i*-1</sub> (AS<sub>*i*</sub>) from (to) CCR<sub>*i*-1</sub> (CCR<sub>*i*+1</sub>). The state transition diagram for a CCR<sub>*i*</sub> is shown in Figure 2, in which CCR<sub>*i*</sub> transits from idle to active when it receives an asserted AS<sub>*i*-1</sub> (condition b). An idle CCR does nothing while an active CCR inspects input characters for matching. An active CCR remains in the polling state and makes no change to any counter, before it makes the first match (condition a). After that, it enters the busy state and updates its (MIN, MAX) counters. It activates its successor if the matching count satisfies the constraint repetition (condition c and d).

Note that there is a one cycle delay between " $AS_{i-1}$  is asserted" and "ACTIVE<sub>i</sub> is set to one". That is, when  $AS_{i-1}$  is asserted after constraint repetition of  $CCR_{i-1}$  is satisfied, ACTIVE<sub>i</sub> will not be updated until the next cycle. Also note that the constraint repetition of  $CCR_{i-1}$  may be satisfied for a burst of consecutive cycles, in which case  $AS_{i-1}$ is fired at each cycle for the duration. Conditions:

Figure 2. State transitions in a CCR

The state transitions in Figure 2 are derived from interaction rules and matches counting rules that run in each CCR. These two sets of rules in the MIN-MAX algorithm are used to control activation signals (AS) between CCRs and track matching counts for each CCR. They are formalized as follows.

- CCR Interaction Rules:

- IR-1 (a) CCR<sub>1</sub> is always set as active, i.e., ACTIVE<sub>1</sub> = 1, and (b) MIN<sub>1</sub> is always 0.

- IR-2 AS<sub>i</sub> is asserted when MAX<sub>i</sub>  $\geq b_i^L$  and MIN<sub>i</sub>  $\leq b_i^U$ .

- IR-3 When  $CCR_i$  asserts  $AS_i$  (activates  $CCR_{i+1}$ ),  $ACTIVE_{i+1}$  is set to 1 and  $MIN_{i+1}$  is reset to 0.

- IR-4 An activated CCR<sub>i</sub> uses three conditions to decide change of its state: (a) the incoming character is not acceptable to  $CC_i$ , (b) MIN<sub>i</sub> has exceeded  $b_i^U$ , and (c) it receives an activation signal from  $CCR_{i-1}$ . When (c) holds,  $CCR_i$  remains active. When none of (a), (b) and (c) holds,  $CCR_i$  remains active. When (c) does not hold, and (a) or (b) holds,  $CCR_i$  changes to inactive state, and (MIN<sub>i</sub>, MAX<sub>i</sub>) counters are reset to 0.

- IR-5 A match is reported when the final CCR asserts its activation signal.

Matches Counting Rules:

- CR-1 When ACTIVE<sub>*i*</sub> = 1, MAX<sub>*i*</sub> is incremented by 1 if the incoming character is acceptable to  $CC_i$ .

- CR-2 When MIN<sub>*i*</sub> is 0, it increments to 1 if (a) (ACTIVE<sub>*i*-1</sub>, ACTIVE<sub>*i*</sub>) = (1, 1) and the incoming character is acceptable to  $CC_i$ , but not  $CC_{i-1}$ , or (b) (ACTIVE<sub>*i*-1</sub>, ACTIVE<sub>*i*</sub>) = (0, 1), and the incoming character is acceptable to  $CC_i$ .

- CR-3 After MIN<sub>*i*</sub> becomes non-zero, it keeps increasing whenever the incoming character is in CC<sub>*i*</sub>.

- CR-4 MAX<sub>i</sub> is reset to  $b_i^L$  when its value increases to MAX\_INT, where MAX\_INT is the highest value of (MIN and MAX) counters that can produce.

After the regexp matching reaches the last CCR, another set of rules is used for retrospection of matching lengths in each CCR. To support retrospection, (MIN<sub>*i*</sub>, MAX<sub>*i*</sub>) counters and current cycle will need to be saved into some memory before they are reset during the forward matching process, and details on that will be discussed in subsection 2.2.4.

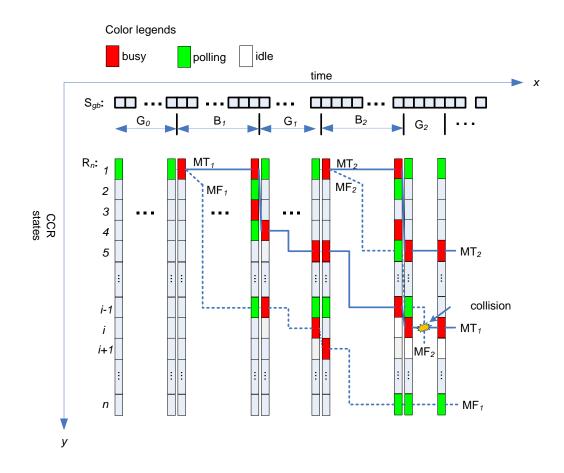

To facilitate analysis of overlapped matching, next we introduce the notion of matching bursts based on structures of the input string. By definition, CCR<sub>1</sub> needs to be set permanently active in the overlapped matching mode (i.e., IR-1.a) to check every input character. When CCR<sub>1</sub> matches a consecutive sequence of acceptable characters, it remains at the busy state and MAX<sub>1</sub> keeps increasing per CR-1, where each increment represents a new (overlapped) matching process. CCR<sub>1</sub> will reset its MAX<sub>1</sub> to 0 when it receives an unacceptable character x. MAX<sub>1</sub> will increase to one again at arrival of its next acceptable character, which also indicates starting of a new matching process. In other words, an input string S can be modeled as *blocks* of characters  $B_i$  acceptable to CCR<sub>1</sub>, segmented by gaps of characters  $G_i$  that are not acceptable to CCR<sub>1</sub>, i.e.,  $S_{gb} :=$  $G_0$ ,  $B_1$ ,  $G_1$ ,  $B_2$ ,  $G_2$ , ...,  $B_i$  is associated with a burst of matching processes, matching *burst* MB<sub>i</sub>, where each of these processes is started at a different input character location. These matching processes can correctly advance in parallel only when they do not cause incorrect changes of the configuration (locations, states of CCRs) of any other matching process.

A matching burst MB<sub>i</sub> is *started* at the first character of B<sub>i</sub>, and it is *terminated* when its matching front and tail become idle, where *matching front* MF<sub>i</sub> denotes the active CCR in MB<sub>i</sub> that is located most close to the final state, and *matching tail* MT<sub>i</sub> denotes the busy CCR in MB<sub>i</sub> that is located most close to CCR<sub>1</sub>. After the birth of MB<sub>i</sub>, MT<sub>i</sub> stays at CCR<sub>1</sub> throughout the cycles of B<sub>i</sub>. Its location "advances" to CCR<sub>k</sub> at the beginning of G<sub>i</sub>, where CCR<sub>k</sub> becomes busy and there is no active CCR between CCR<sub>1</sub>

and  $CCR_k$ . In the meantime  $MF_i$  continuously checks input characters to advance as far as possible.

Figure 3 illustrates state transitions of CCRs with respect to two hypothetical matching bursts. In this figure, the input character sequence is read from left to right (the *x* axis on the top row) and the CCR regexp  $R_n$  is matched from top to down (the *y* axis on the left column). The (busy/idle/polling) states of CCRs corresponding to input characters are marked in different colors, column by column with respect to each input character. The input characters are divided into blocks and gaps based on their acceptance to CCR<sub>1</sub>, and each block of  $S_{gb}$  represents an input character. Each block of regexp  $R_n$  represents a CCR term. The matching tails are denoted by solid lines, and matching fronts are denoted by dotted lines in the CCR state diagram. The color of CCR<sub>1</sub> changes to red (green) at the first character of each block (gap).

Figure 3. Illustration of matching burst, front, and tail

In general, the location of  $MT_i$  advances monotonically with time, but the location of  $MF_i$  may move forward (at acceptance of input characters) or backward (at rejection of an unacceptable character). Once  $AS_n$  is asserted after  $MF_i$  reaches  $CCR_n$ , a match of the regexp is detected, i.e., IR-5. For the two illustrated matching bursts, a collision is marked at the last column (intersection of  $MT_1$  and  $MF_2$ ), when  $MF_2$  attempts to enter  $CCR_i$  which is still occupied by  $MT_1$ , i.e., a *collision* between  $MB_1$  and  $MB_2$ . Here,  $CCR_i$  is still performing string matching for  $MB_1$  while its predecessor

$CCR_{i-1}$  has reported another matched substring in MB<sub>2</sub>, and wants to reset  $CCR_i$  by asserting  $AS_{i-1}$ . It will become clear in the detailed discussion of next subsection that the burst level model significantly simplifies analysis of collisions and subsequent derivation of collision detection criteria.

Unlike traditional NFA/DFA based designs, which usually assign a unique state to each possible matching count of CCR<sub>*i*</sub>, in the MIN-MAX algorithm we use a pair of counters (MIN<sub>*i*</sub>, MAX<sub>*i*</sub>) to represent the minimum and maximum number of characters that CCR<sub>*i*</sub> can match in all matching processes within a matching burst. This way, when a new (old) possible matching count of CCR<sub>*i*</sub> needs to be added (removed), we do not need to store (delete) it to (from) a dedicated register, but to relax (tighten) the bounds of CCR<sub>*i*</sub> so as to accommodate the new matching count. Satisfaction of the constraint repetition of CCR<sub>*i*</sub> is determined by the semantics of (MIN<sub>*i*</sub>, MAX<sub>*i*</sub>) counters, i.e., the maximum possible matching count has to be no less than b<sup>L</sup><sub>1</sub> and the minimum possible matching count has to be no more than b<sup>U</sup><sub>1</sub> (i.e., IR-2). Otherwise, the substring matched by CCR<sub>*i*</sub> is either too short or too long. This technique reduces the resource requirement from the worst-case complexity O(*n*) (for traditional NFA) or O(2<sup>*n*</sup>) (for conventional DFA) to O(log *n*), where *n* is the upper bound of a constraint repetition.

Regarding matches counting rules,  $MAX_i$  can begin to increase when  $CCR_i$  becomes active and the input character is acceptable (i.e., CR-1). This means that at least one matching process in the current matching burst has advanced to  $CCR_i$ , so that its state changes to busy. By IR-3,  $MIN_i$  remains 0 when  $AS_{i-1}$  is asserted, which implies that the matching tail has not reached  $CCR_i$  and some matching process of the current

matching burst might be still staying at an earlier CCR. It increases to 1 only when  $CCR_{i-1}$  gets a mismatch or MIN<sub>*i*-1</sub> reaches  $b_{i-1}^{U}$  (i.e., IR-4 or CR-2), which means that the matching tail must advance to  $CCR_i$  and no matching processes of the current matching burst can stay at an earlier CCR any longer. Thereafter, the matching tail cannot move backward and has to remain in  $CCR_i$  or its successors, which leads to CR-3 that a non-zero MIN<sub>*i*</sub> needs to be incremented by 1 for each input character acceptable to  $CC_i$ . To support the semantics of unbounded wildcard such as "\*", "+", and " $\{b_{i}^{L},\}$ " with a limited upper bound MAX\_INT, MAX<sub>*i*</sub> is reset to  $b_i^{L}$  whenever it reaches MAX\_INT (i.e., CR-4), so that CCR<sub>*i*</sub> can match as many characters as possible and will always be activating CCR<sub>*i*+1</sub> once MAX<sub>*i*</sub> reaches  $b_i^{L}$ .

As an example, when  $R_2$  is used to match against the example string of "*abc-1*-\_*3d*" using the MIN-MAX algorithm, state transitions and (MIN<sub>*i*</sub>, MAX<sub>*i*</sub>) counter values are illustrated in Table 2. After processing the whole string, MAX<sub>3</sub> is 2 which is equal to  $b_3^L$ , indicating a successful match according to IR-2 and IR-5.

|         |                                                             | -                                                                       |                                                             |

|---------|-------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------|

| abc-13d | $CCR_1$                                                     | $CCR_2$                                                                 | $CCR_3$                                                     |

|         |                                                             |                                                                         |                                                             |

| ACTIVE  | $1 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 1$ | $0 \rightarrow 0 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow$ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0$ |

|         | $\rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 1$   | $1 \rightarrow 1 \rightarrow 0 \rightarrow 0$                           | $\rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 1$   |

|         |                                                             |                                                                         |                                                             |

| MIN     | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0$ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow$ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0$ |

|         | $\rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0$   | $3 \rightarrow 4 \rightarrow 0 \rightarrow 0$                           | $\rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 2$   |

|         |                                                             |                                                                         |                                                             |

| MAX     | $1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow 1$ | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow$ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0$ |

|         | $\rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 2$   | $4 \rightarrow 5 \rightarrow 0 \rightarrow 0$                           | $\rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 2$   |

|         |                                                             |                                                                         |                                                             |

Table 2. State transitions of CCRs based on MIN-MAX

#### 2.2.3 Matching Collisions and Collision-free Conditions

An analysis of IR-3 and CR-3 reveals that resource contention may occur when a matching process wants to increment  $MIN_i$  while another one attempts to reset it. This contention may arise between matching processes of different matching bursts, or within the same one. We will discuss collisions between adjacent matching bursts, and then those within the same matching burst.

Two matching bursts have a *collision* when the front of a new matching burst runs into the tail of an earlier matching burst, as the example illustrated in Figure 3, where the collision occurs at CCR<sub>i</sub> at certain point in G<sub>2</sub>. At collisions, the "minimum number of matching counts" of a matching burst is lost, which may lead to false detections. It is easy to verify that a false positive will occur when R<sub>2</sub> scans a (nonmatching) string "*ab\_def\_44*", as shown in Table 3. This is because when MB<sub>1</sub> (starting from '*a*') goes past "*ab\_de*", MIN<sub>2</sub> is reset from 3 to 0 as CCR<sub>1</sub> detects an overlapped matching of substring "*de*" in MB<sub>2</sub> (starting from '*d*'). As a result, MIN<sub>2</sub> fails to observe that substring "*\_def\_*", which is considered to match CCR<sub>2</sub>, has the length of 5, exceeding its upper bound.

| ab_def_44 | CCR <sub>1</sub>                                                                                                                                    | CCR <sub>2</sub>                                                                                                                               | CCR3                                                                                                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| ACTIVE    | $1 \rightarrow 1 \rightarrow$       | $0 \rightarrow 0 \rightarrow 1 \rightarrow $ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 1$             |

| MIN       | $\begin{array}{c} 0 \rightarrow 0 $ | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3$                            | $0 \rightarrow 0 \rightarrow$ |

| MAX       | $1 \rightarrow 2 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow 1 \rightarrow 2$                                 | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 4 \rightarrow 5 \rightarrow 6 \rightarrow 7$                            | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow 0 \rightarrow 1 \rightarrow 2$                           |

Table 3. False positive with overlapped matching

In [41] we proposed using a pair of checkpoint registers to save the contents of (MIN, MAX) counters in order to support two contending matching bursts. One may add more checkpoint registers to handle multi-collisions in a CCR as needed. That being said, we observe that MIN-MAX can be used to directly support overlapped matching without additional checkpoint registers if the regexp is inherently free of collisions. Our case study on two major network security systems Snort and SpamAssassin suggest that indeed most of their rules are free of collision, and therefore MIN-MAX can work in the overlapped matching mode for most of their regexp rules. Next, we will discuss novel techniques that can prove absence of collisions in regexps.

On the basis of the matching burst model, we conduct some sufficient condition based analyses and derive two heuristic lemmas for identification of collision-free CCRs. A third lemma is derived to identify CCRs that will not suffer from resource contention between any two matching bursts, even if collisions are present. CCRs conforming to these three lemmas are called *safe*, because they will not generate false detections in the overlapped matching mode. These three lemmas can cover over 99.8% of regexp rules for Snort and SpamAssassin in our evaluation.

In the following descriptions, the abbreviations PR and CN stand for *premise* and *conclusion*, respectively. Detailed meanings of each condition are listed as follows:

$PR_{i.}(a)$ : None of  $CCR_{i}$ 's predecessors has a collision.

PR<sub>*i*</sub>.(b) : CCR<sub>*i*</sub> has a predecessor CCR<sub>*x*</sub> ( $l \le x < i$ ) whose character class has no intersection with CCR<sub>*x*+1</sub>, CCR<sub>*x*+2</sub>, ..., and CCR<sub>*i*</sub>, and b<sup>L</sup><sub>*x*</sub>  $\ne$  0.

PR<sub>*i*</sub>.(c) : Any of the following conditions is satisfied: (1)  $b_i^U = 1$ , (2)  $b_i^L = b_i^U$ , or (3)  $b_{i-1}^L \ge b_i^U$ .

$\mathrm{PR}_{i\cdot}(\mathrm{d}): b_i^U = \infty.$

$CN_i$  :  $CCR_i$  is collision free.

$CN_i$ ':  $CCR_i$  is safe and will never suffer from false detections.

**Lemma 1.**  $CN_1$  always holds. For  $1 \le i \le n$ , when premises  $PR_{i}(a)$  and  $PR_{i}(b)$  hold,  $CN_i$  holds.

**Lemma 2.** For  $1 \le i \le n$ , when  $PR_{i}(a)$  holds and  $PR_{i}(c)$  holds,  $CN_{i}$  holds.

**Lemma 3.** For  $1 < i \le n$ , when PRi.(d) holds,  $CN_i$ ' holds even if  $CN_i$  does not hold.

Formal proofs for these three lemmas are given in Appendix A.(1,2,3).

In summary, Lemmas 1 and 2 separate collision-free CCRs from those subject to collisions by analyzing character classes (i.e., PR<sub>i</sub>.(b)) and constraint repetitions (i.e.,

$PR_{i.}(c)$ ) of CCR terms, respectively. Then, for these collision-prone CCRs, Lemma 3 determines whether or not they will lose useful state information at actual collisions.

The above discussion covers collisions between adjacent matching bursts, and next we will consider collisions between matching processes within the same matching burst. Note that in the burst level view, there is only one actual matching front and tail, but in between there may be multiple active CCRs that are segmented by idle CCRs. As such, an intermediate active CCR<sub>*i*</sub> with non-zero MIN<sub>*i*</sub> may receive an activation signal from CCR<sub>*i*-1</sub>, which leads to a resource contention to MIN<sub>*i*</sub>. A common feature of matching tails is that if it is not located in CCR<sub>1</sub>, its MIN register must be non-zero. Therefore, we can regard CCR<sub>*i*</sub> as a *pseudo* matching tail and apply the same analysis as conducted above to determine whether CCR<sub>*i*</sub> is safe or not. If one of the criteria is satisfied, no false detections will occur.

A regexp is collision free if all of its CCRs are collision free. The testing process to determine absence of matching collisions for a regexp is summarized as follows. Note that  $CN_i$  implies  $PR_{i+1}$ .(a), and Lemma 1 and 2 shows an inductive relationship:

$$PR_{i}(a) \xrightarrow{PR_{i}(b|c)} CN_{i+1} \rightarrow PR_{i+1}(a),$$

where the symbol " $\rightarrow$ " denotes that the derivation holds, and " $\stackrel{PR_{i}.(b|c)}{\longrightarrow}$ " denotes that the derivation holds if PR<sub>i</sub>.(b) or PR<sub>i</sub>.(c) holds. Thus, by testing PR<sub>1</sub>.(b|c), PR<sub>2</sub>.(b|c), ..., PR<sub>n</sub>. 1.(b|c), we can obtain true/false results for CN<sub>2</sub>, CN<sub>3</sub>, ..., CN<sub>n</sub>. Knowing that CN<sub>1</sub> always holds, when CN<sub>i</sub> holds for  $1 < i \le n$ , one can conclude that the regexp is collision free, regardless of the input string. For regexps that failed the above collision check, Lemma 3 can be further applied to check their violating CCR terms and determine if the safety property is preserved.

We applied the above tests to linear concatenated regexp rules of Snort 2.9.5 and SpamAssassin 3.3.1, and the results are listed in Table 4. Remaining regexp rules including ORed sub-regexps and context-dependent features (i.e., zero-width patterns and back-references), which will be discussed in later sections and Appendix B, respectively.

| Counts of                               | Snort | SpamAssassin |

|-----------------------------------------|-------|--------------|

| All regexp rules                        | 1667  | 1917         |

| Linear regexp rules                     | 1027  | 1344         |

| Regexp rules subject to collisions      |       |              |

| (by Lemmas 1&2)                         | 30    | 33           |

| Regexp rules subject to false detection |       |              |

| at collision                            | 2     | 3            |

| (by Lemma 3)                            |       |              |

Table 4. Statistics of regexp rule sets

The results show that Lemmas 1 and 2 can identify 997 collision free rules from a total of 1027 linear regexp rules in Snort, and also 1311 collision free rules of 1344 linear regexp rules in SpamAssassin. For the 30 (33) linear regexp rules subject to collision, only 2 (3) of them are not guaranteed to be false-detection free in Snort (SpamAssassin), and would need either checkpoint register [41] or shift register [15] type of scanner support. 1025 (1341) of the 1027 (1344) linear regexp rules in Snort (SpamAssassin) can be directly support by MIN-MAX for overlapped matching.

## 2.2.4 Retrospection of Matching Lengths

At this point, we have discussed regex *matching* in the forward scanning direction. Now we focus on *retrospection* of one matching path after the matching signal is triggered at the last stage of CCRs. As stated earlier, we only aim at finding one feasible matching path, rather than enumerating all possible ones.

Let  $S_n = \{s_1, s_2, ..., s_n\}$  denote a set of consecutive string segments acceptable to  $R_n = CCR_1 \cdot CCR_2 \cdot ... \cdot CCR_n$ , where  $s_i$  is acceptable to  $CCR_i$  and the length of  $s_i$  is denoted as  $L_i$ ,  $1 \le i \le n$ . A string  $s_i$  is acceptable to  $CCR_i$  if and only if each character of  $s_i$  is acceptable to  $CC_i$ , and  $L_i$  falls in the range of  $[b_i^L, b_i^U]$ . Next, we will give two theorems which guarantee correctness of the MIN-MAX algorithm.

**Theorem 1.** If  $R_n$  is collision-free and  $S_n$  is acceptable to  $R_n$ , MIN-MAX will report a match. (Sufficient condition)

**Theorem 2.** If  $R_n$  is collision-free and MIN-MAX reports a match, there must have been a string  $S_n$  that has been matched by  $R_n$ . (Necessary condition)

Theorem 1 and 2 guarantee that MIN-MAX algorithm will report a match if and only if  $S_n$  is acceptable to  $R_n$ , and thus MIN-MAX is free of false negatives and false positives. Formal proofs of these two theorems are given in Appendix A.4. A byproduct of the proof process of Theorem 2 is for MIN-MAX to retrospect one feasible matching length configuration (matching path) when a matching burst triggered the matching signal. To enable this feature, a memory stack  $B_i$  is needed for  $CCR_i$  to store 2-tuple *B-code*: (current cycle value, MAX<sub>i</sub>) when  $CCR_i$  has been matched and AS<sub>i</sub> is asserted. MIN registers are not included because they are not used for matching length calculation. The choices of L<sub>i</sub> values can be summarized into the following rules based on the value of MAX<sub>i</sub> when AS<sub>i</sub> is asserted.

Matching Length Calculation Rules:

LR-1  $L_i = MAX_i$  if  $b_i^L \le MAX_i \le b_i^U$  at assertion of AS<sub>i</sub>.

LR-2  $L_i = b_i^U$  if MAX<sub>i</sub> >  $b_i^U$  at assertion of AS<sub>i</sub>.

When retrospection is needed, it is necessary for  $CCR_i$  to store B-codes at each assertion of  $AS_i$  in a stack  $B_i$  so that they can be used in later length calculations. That is, the following retrospection rule needs to be added in the forward matching stage.

Retrospection Rule:

RR-1 When  $AS_i$  is asserted, push the B-code of  $CCR_i$  into the  $B_i$  stack.

One can retrospect ( $L_n$ ,  $L_{n-1}$ , ...,  $L_1$ ) along the backward direction of CCRs, starting from the last stage CCR<sub>n</sub>. We will use R<sub>2</sub> of subsection 2.2.2 to illustrate the process. Even though R<sub>2</sub> does not conform to the tests of Lemmas 1-3, it does not produce false detection for the example input string in Table 2, because no collision would occur to this case. B-codes and other state information generated from the matching process along the forward direction of CCRs are given in Table 5. RR-1 is applied at the cycles when activation signals are asserted, and a new entry is pushed into

the B-code stack for every such cycle. For example,  $CCR_1$  asserts  $AS_1$  to  $CCR_2$  at cycle 2, 3, and 9, according to IR-2, and the MAX counter values at each corresponding cycle are 2, 3 and 2, respectively. Therefore by RR-1, we got a B-code stack  $B_1$  of (9,2), (3,3) and (2,2) from top to down.  $B_2$  and  $B_3$  are generated in a similar manner.

| abc-13d           | CCR <sub>1</sub>                                                                      | CCR <sub>2</sub>                                                        | $CCR_3$                                                                             |

|-------------------|---------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|                   |                                                                                       |                                                                         |                                                                                     |

| ACTIVE            | $1 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow$ | $0 \rightarrow 0 \rightarrow 1 \rightarrow 1 \rightarrow 1 \rightarrow$ | $0 {\rightarrow} 0 {\rightarrow} 0 {\rightarrow} 0 {\rightarrow} 0 {\rightarrow} 0$ |

|                   | $1 \rightarrow 1 \rightarrow 1 \rightarrow 1$                                         | $1 \rightarrow 1 \rightarrow 0 \rightarrow 0$                           | $1 \rightarrow 1 \rightarrow 1 \rightarrow 1$                                       |

| MAX               | $1 \rightarrow 2 \rightarrow 3 \rightarrow 0 \rightarrow 1 \rightarrow$               | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow$ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow$             |

|                   | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2$                                         | $4 \rightarrow 5 \rightarrow 0 \rightarrow 0$                           | $0 \rightarrow 0 \rightarrow 1 \rightarrow 2$                                       |

| Activation        | $0 \rightarrow 1 \rightarrow 1 \rightarrow 0 \rightarrow 0 \rightarrow$               | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 1 \rightarrow$ | $0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow 0 \rightarrow$             |

| Signal            | $0 \rightarrow 0 \rightarrow 0 \rightarrow 1$                                         | $1 \rightarrow 1 \rightarrow 0 \rightarrow 0$                           | $0 \rightarrow 0 \rightarrow 0 \rightarrow 1$                                       |