# LOW-POWER WIRELESS MEDICAL SYSTEMS AND CIRCUITS FOR INVASIVE AND NON-INVASIVE APPLICATIONS

## A Dissertation

by

## JESUS EFRAIN GAXIOLA-SOSA

Submitted to the Office of Graduate and Professional Studies of Texas A&M University in partial fulfillment of the requirements for the degree of

# DOCTOR OF PHILOSOPHY

Chair of Committee, Kamran Entesari

Committee Members, Edgar Sanchez-Sinencio

Arum Han James Moore

Head of Department, Chanan Singh

May 2014

Major Subject: Electrical Engineering

Copyright 2014 Jesus Efrain Gaxiola-Sosa

#### **ABSTRACT**

Approximately 75% of the health care yearly budget of public health systems around the world is spent on the treatment of patients with chronic diseases. This, along with advances on the medical and technological fields has given rise to the use of preventive medicine, resulting on a high demand of wireless medical systems (WMS) for patient monitoring and drug safety research.

In this dissertation, the main design challenges and solutions for designing a WMS are addressed from system-level, using off-the-shell components, to circuit implementation. Two low-power oriented WMS aiming to monitor blood pressure of small laboratory animals (implantable) and cardiac-activity (12-lead electrocardiogram) of patients with chronic diseases (wearable) are presented. A power consumption vs. lifetime analysis to estimate the monitoring unit lifetime for each application is included. For the invasive/non-invasive WMS, *in-vitro* test benches are used to verify their functionality showing successful communication up to 2.1 m/35 m with the monitoring unit consuming 0.572 mA/33 mA from a 3 V/4.5 V power supply, allowing a two-year/88-hour lifetime in periodic/continuous operation. This results in an improvement of more than 50% compared with the lifetime commercial products.

Additionally, this dissertation proposes transistor-level implementations of an ultra-low-noise/low-power biopotential amplifier and the baseband section of a wireless receiver, consisting of a channel selection filter (CSF) and a variable gain amplifier (VGA). The proposed biopotential amplifier is intended for electrocardiogram (ECG)/

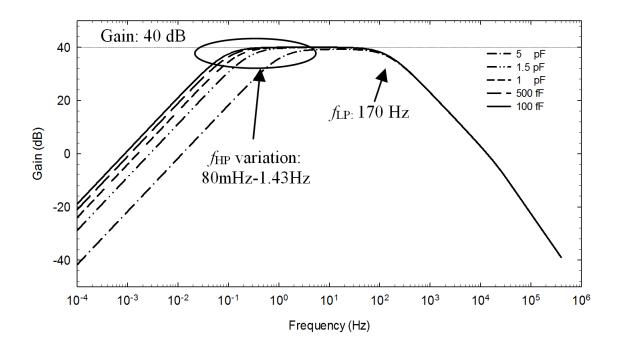

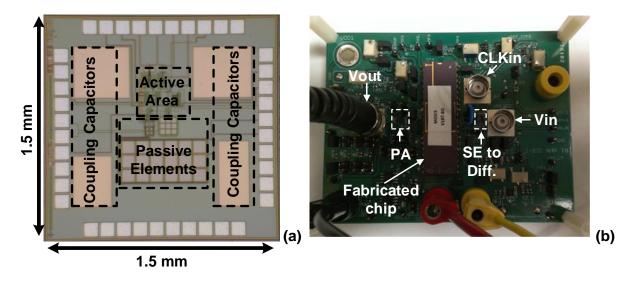

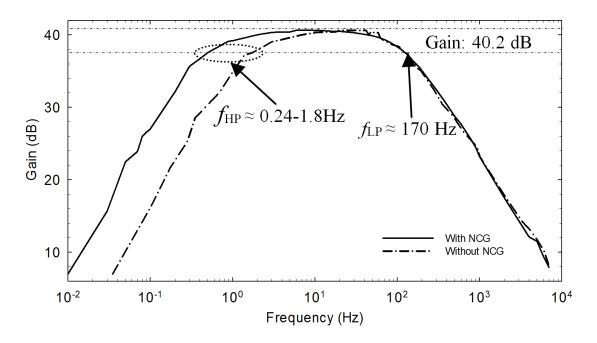

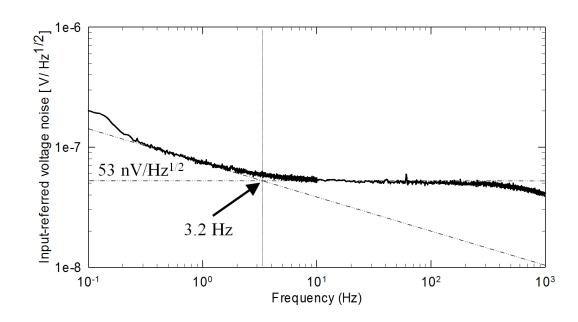

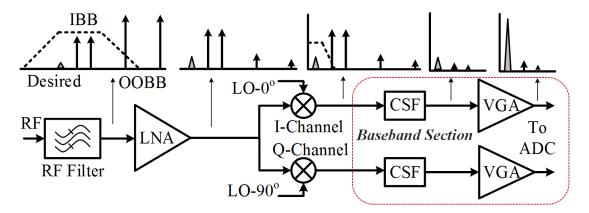

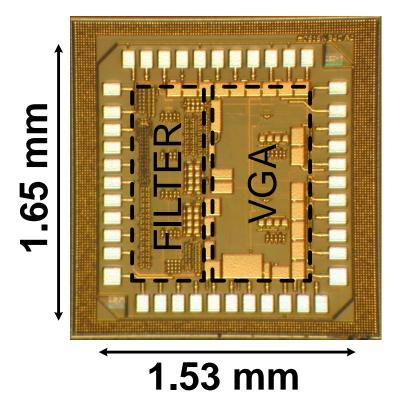

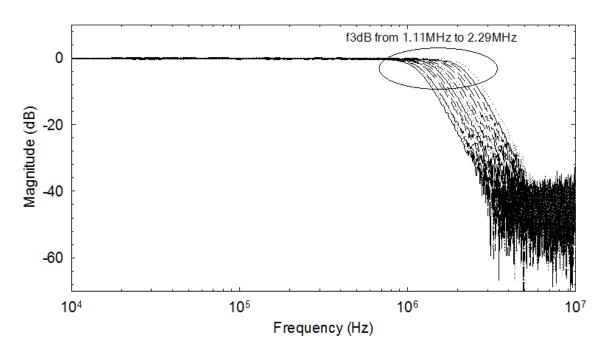

electroencephalogram (EEG)/ electromyogram (EMG) monitoring applications and its architecture was designed focused on improving its noise/power efficiency. It was implemented using the ON-SEMI 0.5 μm standard process with an effective area of 360 μm². Experimental results show a pass-band gain of 40.2 dB (240 mHz - 170 Hz), input referred noise of 0.47 μVrms, minimum CMRR of 84.3 dBm, NEF of 1.88 and a power dissipation of 3.5 μW. The CSF was implemented using an active-RC 4<sup>th</sup> order inverse-chebyshev topology. The VGA provides 30 gain steps and includes a DC-cancellation loop to avoid saturation on the sub-sequent analog-to-digital converter block. Measurement results show a power consumption of 18.75 mW, IIP3 of 27.1 dBm, channel rejection better than 50 dB, gain variation of 0-60dB, cut-off frequency tuning of 1.1-2.29 MHz and noise figure of 33.25 dB. The circuit was implemented in the standard IBM 0.18 μm CMOS process with a total area of 1.45 x 1.4 mm².

The presented WMS can integrate the proposed biopotential amplifier and baseband section with small modifications depending on the target signal while using the low-power-oriented algorithm to obtain further power optimization.

# **DEDICATION**

To my parents: Lupita and Efrain, siblings: Sac-Nicte, Jose Luis, Diego and Rodrigo; grandparents: Nide and Jose, the rest of my family, all my friends, and to Cynthia.

#### ACKNOWLEDGEMENTS

I would like to thank my advisor, Dr. Kamran Entesari, for his support through all these years. His constant advice and guidance helped me grow not only as student but as a person. I am deeply grateful for the way he always challenged me and made me put that little extra effort that ended up making a big difference.

I also want to thank Dr. Edgar Sanchez-Sinencio for inviting me to become part of the Analog and Mixed-Signal Center (AMSC), for his professional and academic advice, and for his friendship. I want to express my appreciation to Dr. Arum Han and Dr. James Moore for being part of my graduation committee, for their comments and suggestions to improve the quality of this research.

My deepest gratitude to my parents, siblings and all the members of my family: grandparents, uncles, aunts and cousins. Their constant support, prayers and unconditional love were always a permanent source of inspiration.

Special thanks to my friends and colleagues at the AMSC for fruitful discussions and long periods of team work. Thanks to Salvador, Carlos, Alfredo, Felix, Jesse, Hajir, Jiayi, Adrian, Jorge, Joselyn, Reza, Marcos, Chengliang, Javier, Moises and Fernando. I also want to thank William, Renan, Alex, Luis Miguel, Jorge B., Ana Karen, Alvaro and all my childhood and college friends, for their friendship and support.

Many thanks to Ella, Tammy, the ECE department staff members and the Sponsored Student Programs Office staff for all their help and support.

I would like to thank my professors from Instituto Tecnologico de Merida, Professor Johan Estrada Lopez, Professor Ramon Atoche Enseñat and Professor Victor Sandoval Curmina for all their patience, support and encouragement.

I am deeply indebted to the Mexican National Council for Science and Technology (CONACYT) for providing me with economic support during most of the doctoral program.

Finally, I want to thank Cynthia for her unconditional love, kindness, enduring support and for being a continuous source of inspiration for my academic and personal life.

## NOMENCLATURE

ADC Analog-to-Digital Converter

AFE Analog Front-End

ASIC Application Specific Integrated Circuit

BS Base Station

CMRR Common-Mode Rejection Ration

CPU Central Processing Unit

DMA Direct Memory Access

ED End Device

FCC Federal Communications Commission

FSK Frequency Shift Keying

GUI Graphical User Interface

IA Instrumentation Amplifier

IC Integrated Circuit

IMD Implantable Medical Device

ISM Industrial Scientific and Medical

ISR Interrupt Service Routine

LNA Low Noise Amplifier

LO Local Oscillator

MAC Media Access Controller

MCU Microcontroller

MICS Medical Implant Communication Service

OOK On/Off Key

OSR Oversampling Ratio

PA Power Amplifier

PSoC Programmable System on Chip

RAM Random Access Memory

SAR Successive Approximation Register

SPI Serial Peripheral Interface

USB Universal Serial Bus

WMS Wireless Medical System

# TABLE OF CONTENTS

|                                                                                                                   | Page   |

|-------------------------------------------------------------------------------------------------------------------|--------|

| ABSTRACT                                                                                                          | ii     |

| DEDICATION                                                                                                        | iv     |

| ACKNOWLEDGEMENTS                                                                                                  | v      |

| NOMENCLATURE                                                                                                      | Vii    |

| TABLE OF CONTENTS                                                                                                 | ix     |

| LIST OF FIGURES                                                                                                   | xiii   |

| LIST OF TABLES                                                                                                    | xviii  |

| CHAPTER I INTRODUCTION                                                                                            | 1      |

| Motivation Wireless Medical Systems Overview Dissertation Organization Research Contribution of this Dissertation | 2<br>4 |

| CHAPTER II A WIRELESS MEDICAL SYSTEM PROTOTYPE FOR IMPLANTABLE APPLICATIONS                                       | 9      |

| Introduction                                                                                                      | 9      |

| System Design and Implementation                                                                                  | 11     |

| Implantable Medical Device                                                                                        |        |

| Signal Acquisition and Analog-to-Digital Conversion                                                               | 12     |

| Digital Communication and RAM Organization                                                                        |        |

| Wireless Transceiver and Matching Network                                                                         |        |

| Base Station and Graphical User Interface                                                                         | 19     |

| System Design and Implementation                                                                                  | 20     |

| Basic Considerations for MCU-based Low Power Operation                                                            | 20     |

| Proposed Low-Power-Oriented Control Algorithm                                                                     | 21     |

| Power Analysis                                                                                                    | 24     |

| Continuous Sampling Mode                                                                                          | 24     |

| Periodic Sampling Mode                                                                                            | 26     |

| In-vitro Measurements and Results                                                                                 | 28     |

| IMD Prototype Implementation                                                                                      | 28     |

| Debug and Testing for In-vitro Measurements                                                                       | 28     |

| Board Optimization                                                                                                | 29     |

| т: 1                                                                            | (r. Amalausia                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                 | k Analysisasurement Setup and Experimental Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                 | nary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                 | ER III A PORTABLE 12-LEAD ECG WIRELESS MEDICAL SYSTEM ONTINOUS CARDIAC-ACTIVITY MONITORING                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Introd                                                                          | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Systen                                                                          | n Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| End                                                                             | Device                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Base                                                                            | e Station                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ED                                                                              | Control Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Graph                                                                           | ical User Interface and Detection Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Result                                                                          | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                 | Device Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Dete                                                                            | ection Algorithm Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                 | pitro Measurements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Summ                                                                            | ary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| BIOPOT                                                                          | ENTIAL AMPLIFIER FOR ECG APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BIOPOT                                                                          | ENTIAL AMPLIFIER FOR ECG APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| BIOPOT<br>Introd                                                                | ENTIAL AMPLIFIER FOR ECG APPLICATIONSuction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIOPOT  Introde  System                                                         | ENTIAL AMPLIFIER FOR ECG APPLICATIONSuctionn-Level Analysis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| BIOPOT  Introde System Bios                                                     | ENTIAL AMPLIFIER FOR ECG APPLICATIONS  uction  n-Level Analysis  amp Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Introde<br>System<br>Bios<br>Con                                                | ER IV A FULLY INTEGRATED ULTRA-LOW-NOISE/LOW-POWER ENTIAL AMPLIFIER FOR ECG APPLICATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

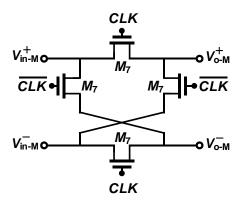

| Introde<br>System<br>Bios<br>Con                                                | ENTIAL AMPLIFIER FOR ECG APPLICATIONS  uction  n-Level Analysis  amp Architecture  atrol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts                                                                                                                                                                                                                                                                                                                                                     |

| BIOPOT  Introde System Bios Com Com E                                           | TENTIAL AMPLIFIER FOR ECG APPLICATIONS  uction  n-Level Analysis  amp Architecture  utrol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts                                                                                                                                                                                                                                                                                                                                                    |

| Introde<br>System<br>Bios<br>Con<br>C                                           | rential Amplifier for ECG Applications  uction  n-Level Analysis  amp Architecture  trol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Effects of Chopper Stabilization in the Proposed Bioamp  Noise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the                                                                                                                                                                                                            |

| BIOPOT  Introde System Bios Con C E                                             | rential Amplifier for ECG Applications  uction  n-Level Analysis  amp Architecture  utrol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Effects of Chopper Stabilization in the Proposed Bioamp  Joise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub>                                                                                                                                                            |

| BIOPOT  Introde System Bios Com C E N A                                         | rential Amplifier For ECG Applications  m-Level Analysis  amp Architecture  atrol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Effects of Chopper Stabilization in the Proposed Bioamp  Joise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub> at Impedance of the Core Amplifier                                                                                                                                 |

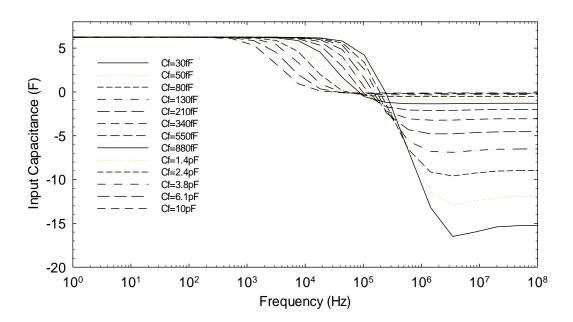

| BIOPOT  Introde System Bios Con C E N A Inpu L L                                | central Amplifier For ECG Applications  m-Level Analysis  amp Architecture  throl System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Cffects of Chopper Stabilization in the Proposed Bioamp  Noise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub> at Impedance of the Core Amplifier  Limitations for Stable Operation  Limitations for Effective Input Impedance Boosting                                           |

| BIOPOT  Introde System Bios Con C E N A Inpu L L                                | central Amplifier For ECG Applications  m-Level Analysis  amp Architecture  throl System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Cffects of Chopper Stabilization in the Proposed Bioamp  Noise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub> at Impedance of the Core Amplifier  Limitations for Stable Operation  Limitations for Effective Input Impedance Boosting                                           |

| BIOPOT  Introde System Bios Com C E N A Inpu L C                                | rential Amplifier for ECG Applications  m-Level Analysis  amp Architecture  throl System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Cffects of Chopper Stabilization in the Proposed Bioamp  Joise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub> at Impedance of the Core Amplifier  Limitations for Stable Operation  Limitations for Effective Input Impedance Boosting  Component Selection                      |

| BIOPOT  Introde System Bios Com C E N A Inpu L L C Des                          | central Amplifier For ECG Applications  m-Level Analysis  amp Architecture  ctrol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Cffects of Chopper Stabilization in the Proposed Bioamp  Noise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub> at Impedance of the Core Amplifier  cimitations for Stable Operation  cimitations for Effective Input Impedance Boosting.  Component Selection  ign Considerations |

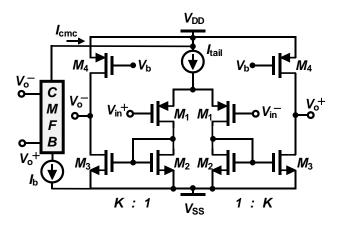

| BIOPOT  Introde System Bios Com C E N A Inpu L C Des Circui Core                | uction  n-Level Analysis  amp Architecture  trol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Effects of Chopper Stabilization in the Proposed Bioamp  Joise-Power Trade-off Between the Chopping Frequency f <sub>chop</sub> and the amplifier's 3dB Frequency f <sub>3dB_AMP</sub> at Impedance of the Core Amplifier  Limitations for Stable Operation  Limitations for Effective Input Impedance Boosting  Component Selection  ign Considerations  t Implementation  e Amplifier    |

| BIOPOT  Introde System Bios Com C E N A Inpu L C Des Circui Cor Hig             | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BIOPOT  Introde System Bios Com C E N A Inpu L C Des Circui Core Higs           | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BIOPOT  Introde System Bios Com C E N A Inpu L C Des Circui Cor High            | uction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| BIOPOT  Introde System Bios Com C E N A Inpu L C Des Circui Cor Hig Cho Neg Nor | TENTIAL AMPLIFIER FOR ECG APPLICATIONS  uction  n-Level Analysis  amp Architecture  trol System Block Diagram and Chopping Modulation  Chopper Stabilization Technique: Basic Concepts  Effects of Chopper Stabilization in the Proposed Bioamp                                                                                                                                                                                                                                                                                            |

|                                                                         | Page |

|-------------------------------------------------------------------------|------|

| Experimental Results and Discussion                                     | 83   |

| Circuit Characterization                                                |      |

| In-vitro Test                                                           | 86   |

| Discussion                                                              | 87   |

| Summary                                                                 | 89   |

| ·                                                                       |      |

| CHAPTER V A VERSATILE AND HIGHLY LINEAR BASEBAND SECTION                |      |

| FOR EXTRAVEHICULAR ACTIVITY (EVA) RADIO RECEIVERS                       | 90   |

| Introduction                                                            | 00   |

| Derivation of CSF/VGA Specifications from EVA Radio Receiver Requiremen |      |

| Chanel Selection Filter                                                 |      |

| Design Approach                                                         |      |

| Active Implementation of the CSF                                        |      |

| •                                                                       |      |

| Operational Amplifier Design and Considerations                         |      |

| Variable Gain Amplifier                                                 |      |

| Design Approach                                                         |      |

| Transistor-level Implementation                                         |      |

| Experimental Results                                                    |      |

| Fabricated Chips                                                        |      |

| PCB and Test-bench.                                                     |      |

| CSF Measurements                                                        |      |

| DC Operation                                                            |      |

| AC Operation                                                            |      |

| Linearity                                                               |      |

| · · · · · · · · · · · · · · · · · · ·                                   |      |

| Noise Figure                                                            |      |

| VGA Measurements                                                        |      |

| DC Operation                                                            |      |

| AC Operation                                                            |      |

| Linearity                                                               |      |

| Noise Figure                                                            |      |

| Summary of Results                                                      |      |

| Complete Baseband Section (CSF+VGA) Measurements                        |      |

| DC Operation                                                            |      |

| AC Operation                                                            |      |

| Linearity                                                               |      |

| Noise Figure                                                            |      |

| Summary of Results                                                      |      |

| Summary                                                                 |      |

| Duilliai y                                                              | 14J  |

|                       | Page |

|-----------------------|------|

| CHAPTER VI CONCLUSION | 126  |

| REFERENCES            | 127  |

# LIST OF FIGURES

|          | Page                                                                                                                                                                           |

|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 1.  | Block diagram of a typical wireless medical system.                                                                                                                            |

| Fig. 2.  | Simplified block diagram of typical ED showing the interaction between a biological parameter and the sensor used to translate the <i>measurand</i> into an electrical signal. |

| Fig. 3.  | Simplified block diagram of a typical BS with the GUI implemented in a personal computer.                                                                                      |

| Fig. 4.  | Block diagram of the WMS.                                                                                                                                                      |

| Fig. 5.  | Detailed block diagram of the IMD unit                                                                                                                                         |

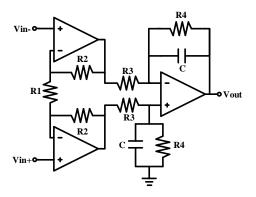

| Fig. 6.  | A three op amp IA with embedded anti-aliasing filter                                                                                                                           |

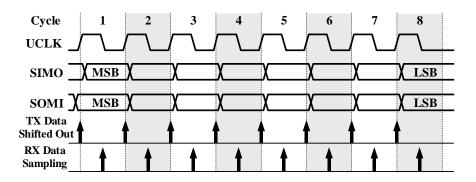

| Fig. 7.  | Timing diagram of the SPI link between the MCU and the transceiver15                                                                                                           |

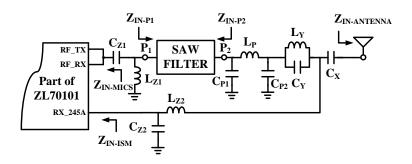

| Fig. 8.  | Dual-band matching network of the IMD                                                                                                                                          |

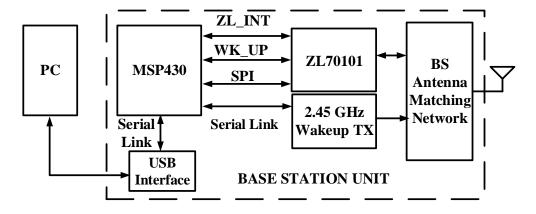

| Fig. 9.  | Block diagram of the base station unit                                                                                                                                         |

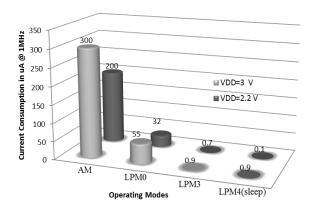

| Fig. 10. | Different operating modes of the MCU [26]                                                                                                                                      |

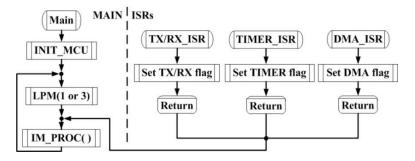

| Fig. 11. | Basic flow chart of the implemented algorithm                                                                                                                                  |

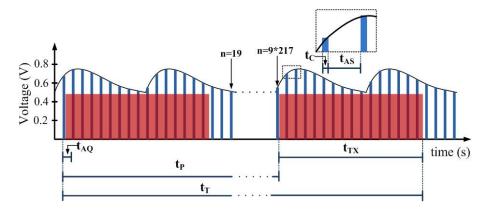

| Fig. 12. | Timming diagram of the IMD sampling a biological signal in CSM24                                                                                                               |

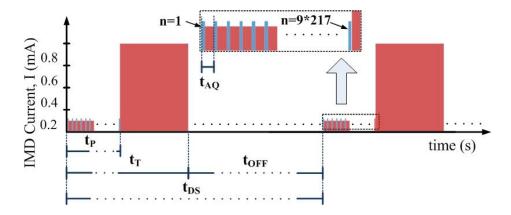

| Fig. 13. | Timing diagram of the IMD operating in periodid sampling mode (PSM)27                                                                                                          |

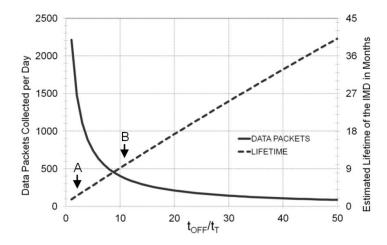

| Fig. 14. | Lifetime and data packets per day vs. $t_{OFF}$ / $t_{T}$ for a 350 mAh battery27                                                                                              |

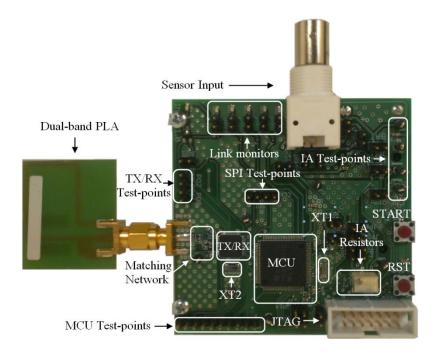

| Fig. 15. | Fabricated implantable medical device prototype board                                                                                                                          |

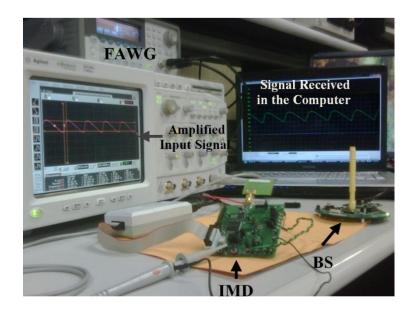

| Fig. 16. | Measurement setup for <i>in-vitro</i> measurements                                                                                                                             |

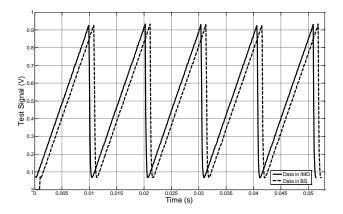

| Fig. 17. | Signal at the ADC input vs data received at the BS, d=2.1 m35                                                                                                                  |

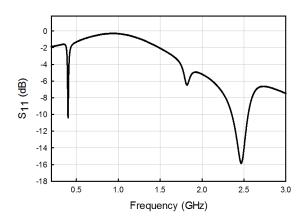

| Fig. 18. | S11 of the dual-band PLA used in the IMD.                                                                                                                                      |

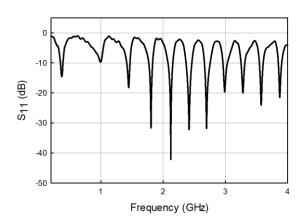

| Fig. 19. | S11 of the multi-band helical antenna used in the BS                                                                                                                           |

| Fig. 20. | Block diagram of the wireless medical system                                                                                                                                   |

|          | F                                                                                                                                                        | Page |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. 21. | Block diagram of the end device.                                                                                                                         | 40   |

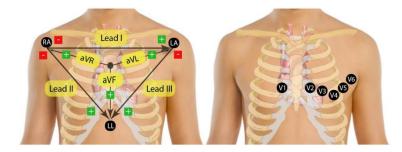

| Fig. 22. | Typical electrode placement on 12-lead ECG systems. (RL not shown)                                                                                       | 41   |

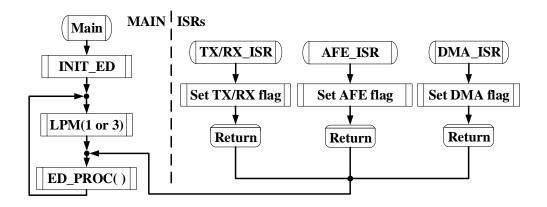

| Fig. 23. | Basic flow chart of the implemented algorithm                                                                                                            | 44   |

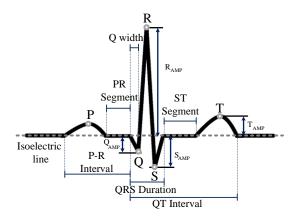

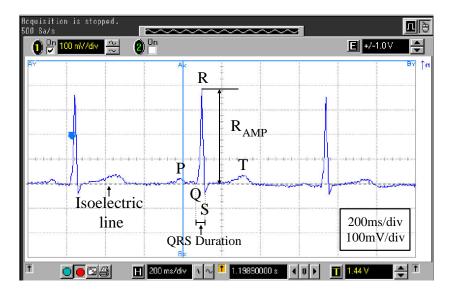

| Fig. 24. | ECG points of interest and clinical measurements.                                                                                                        | 45   |

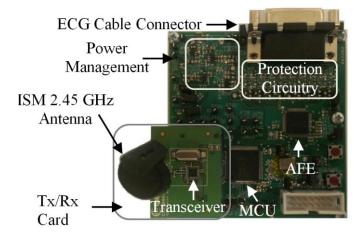

| Fig. 25. | End device PCB and ISM Tx/Rx daughter card.                                                                                                              | 46   |

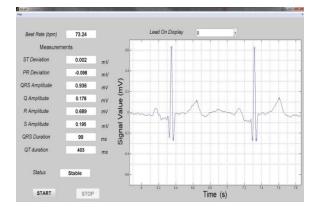

| Fig. 26. | GUI screenshot presenting the detected ECG signal (lead II).                                                                                             | 47   |

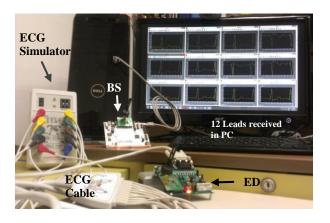

| Fig. 27. | Measurement setup of the 12-lead ECG WMS                                                                                                                 | 49   |

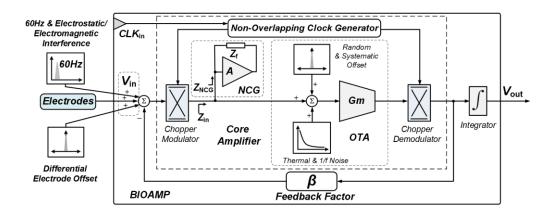

| Fig. 28. | Block diagram of the biopotential amplifier.                                                                                                             | 53   |

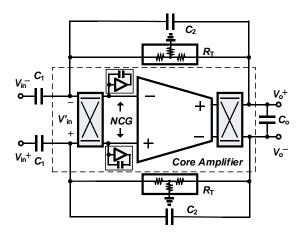

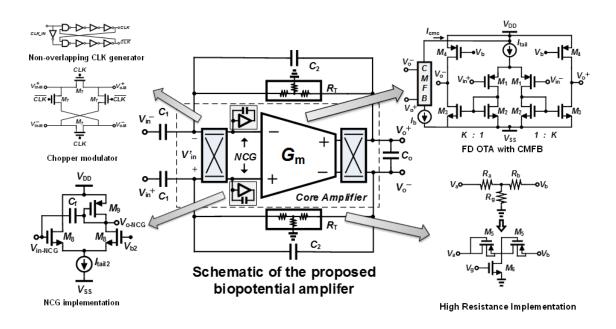

| Fig. 29. | Schematic diagram of the biopotential amplifier                                                                                                          | 55   |

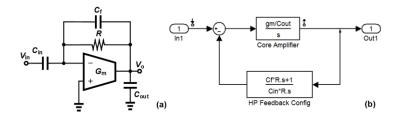

| Fig. 30. | Single-ended bioamp: a) schematic diagram and b) control system block diagram.                                                                           | 55   |

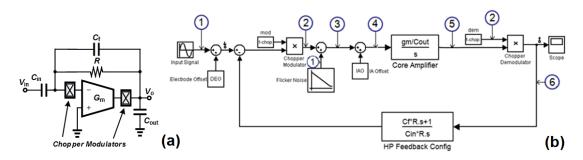

| Fig. 31. | Single-ended bioamp with choppers: a) schematic diagram and b) control system block diagram including signal and transconductance offset and noise.      | 56   |

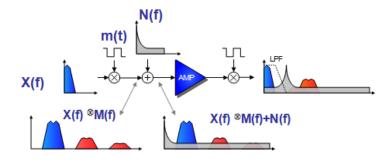

| Fig. 32. | Operation principle of the chopper modulation technique.                                                                                                 | 57   |

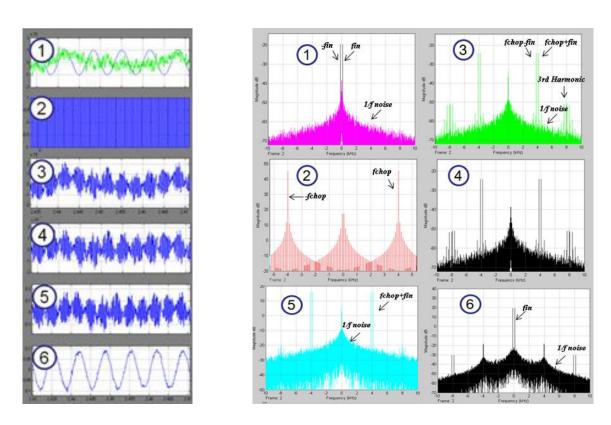

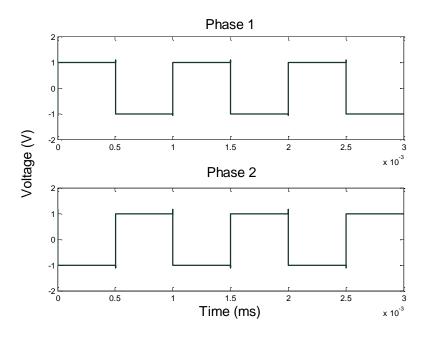

| Fig. 33. | Transient and frequency response of the block diagram from Fig. 31b                                                                                      | 58   |

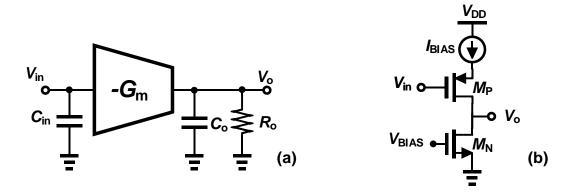

| Fig. 34. | Schematic diagram of a general transconductance stage: a) block diagram of including equivalent input and output impedances, b) transistor-level diagram | 60   |

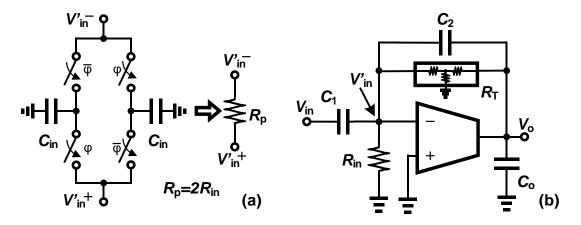

| Fig. 35. | a) SC circuit generating $R_p$ , b) SE representation of the bioamp including the parasitig input resistance $R_{in}$ .                                  |      |

| Fig. 36. | Frequency response of the SE bioamp for different values of $C_{in}$                                                                                     | 63   |

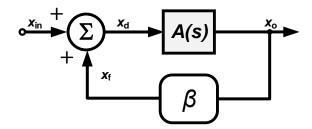

| Fig. 37. | Block diagram of a system connected in positive feedback.                                                                                                | 64   |

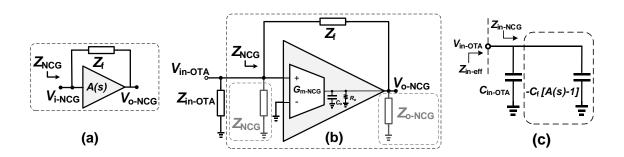

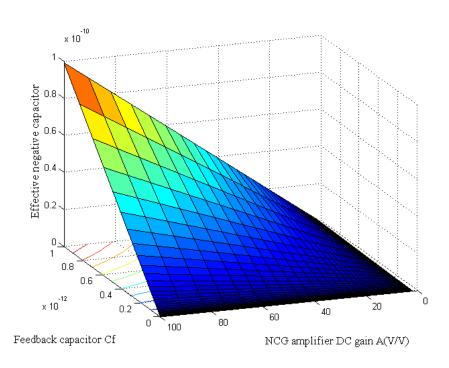

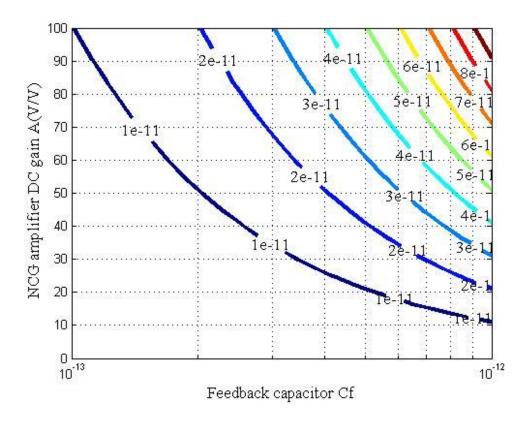

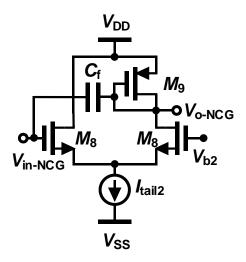

| Fig. 38. | NCG block: a) simple representation, b) detailed schematic diagram                                                                                       | 65   |

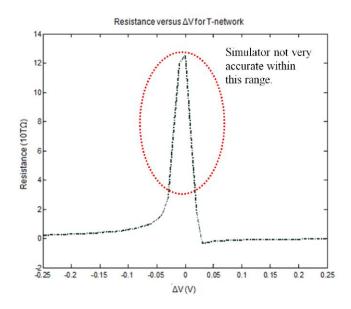

| Fig. 39. | Design trade-off for NCG amplifier gain, feedback capacitor Cf and effective negative capacitance                                                        | 68   |

Page

|          |                                                                                                                              | Page |

|----------|------------------------------------------------------------------------------------------------------------------------------|------|

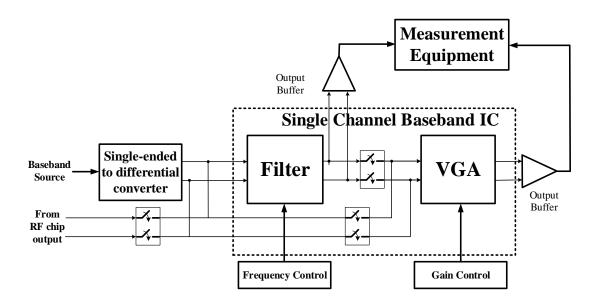

| Fig. 61. | Frequency planning of the EVA radio                                                                                          | 94   |

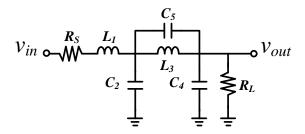

| Fig. 62. | Doubly terminated LC ladder structure.                                                                                       | 96   |

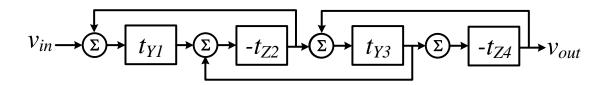

| Fig. 63. | Leapfrog signal flow graph of the LC prototype from Fig. 62.                                                                 | 97   |

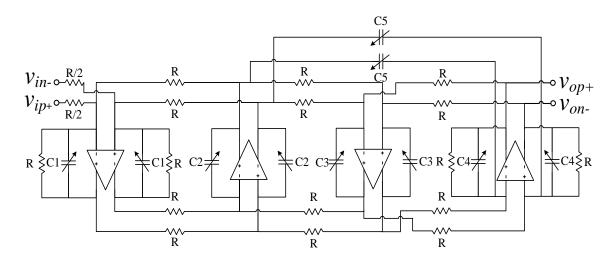

| Fig. 64. | Active-RC implementation of the signal flow graph from Fig. 63                                                               | 99   |

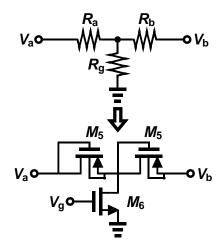

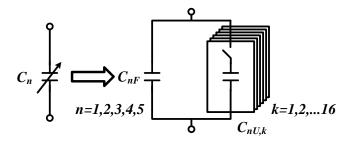

| Fig. 65. | Schematic diagram of the variable capacitors used for frequency tuning                                                       | 99   |

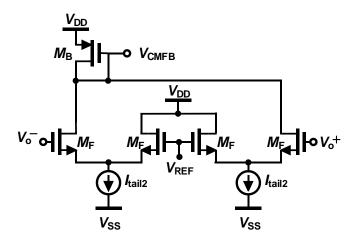

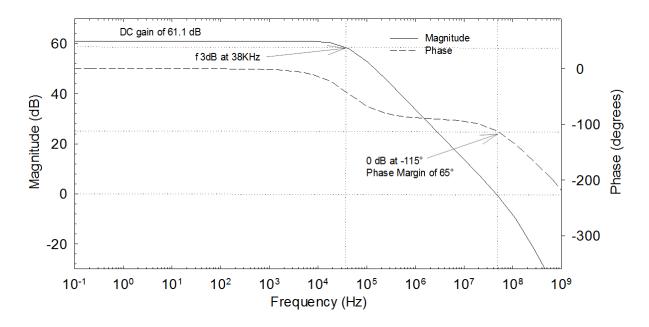

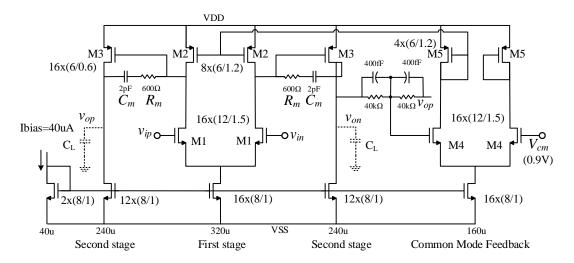

| Fig. 66. | Schematic diagram of the two-stage miller-compensated operational amplifier used for the active-RC implementation of the CSF | .100 |

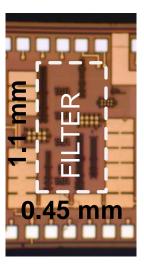

| Fig. 67. | Microphotograph of the fabricated CSF.                                                                                       | .101 |

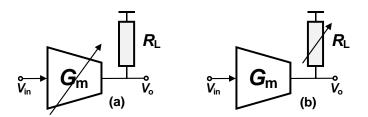

| Fig. 68. | Basic concept of variable gain based on a) transconductance and b) load variations.                                          | .102 |

| Fig. 69. | Block diagram of the proposed VGA.                                                                                           | .103 |

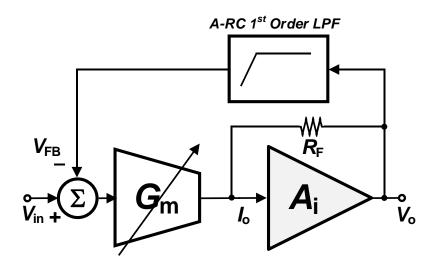

| Fig. 70. | Low-pass filter implementation using an operational amplifier to multiply the value of the feedback capacitor.               | .104 |

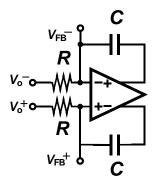

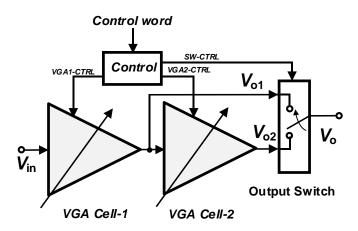

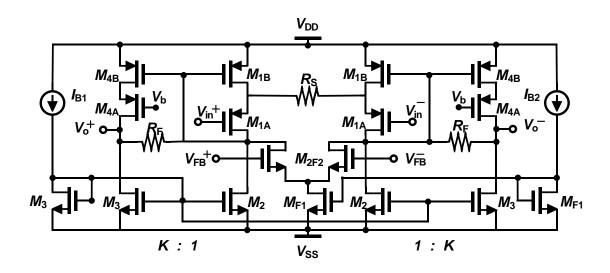

| Fig. 71. | Block diagram of the complete VGA including two VGA cells and a control block for gain variation.                            | .105 |

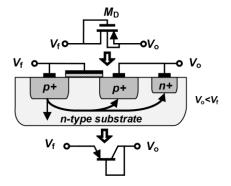

| Fig. 72. | Transistor-level implementation of the VGA cell.                                                                             | .106 |

| Fig. 73. | Micrograph of the fabricated baseband chip                                                                                   | .109 |

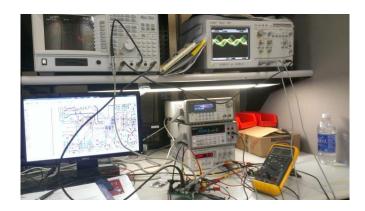

| Fig. 74. | PCB used to characterize the baseband chip                                                                                   | .109 |

| Fig. 75. | Baseband chip characterization setup.                                                                                        | .110 |

| Fig. 76. | Test bench used for the characterization of the baseband chip                                                                | .111 |

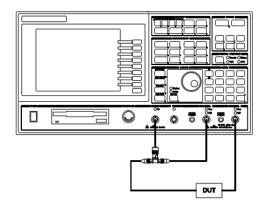

| Fig. 77. | AC response measurement configuration with the HP89410A vector signal analyzer.                                              | .113 |

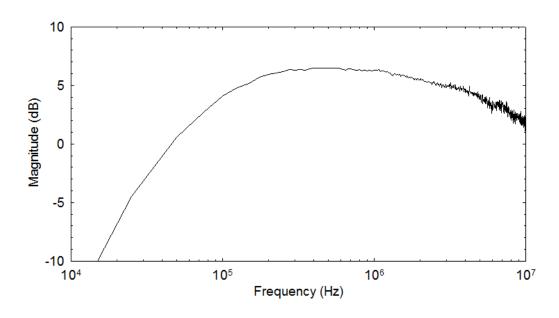

| Fig. 78. | Frequency response of the CSF for different control words                                                                    | .114 |

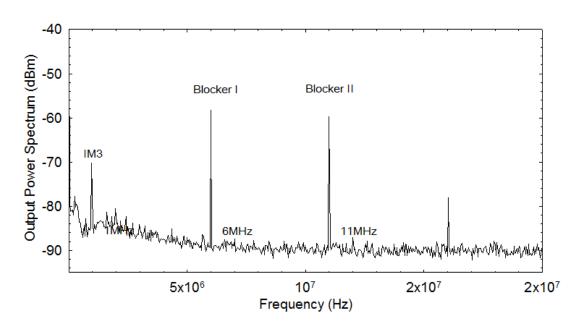

| Fig. 79. | Output power spectrum of the CSF.                                                                                            | .116 |

| Fig. 80. | Frequency response of the VGA for the '1111'control word                                                                     | .120 |

|          |                                                                                   | Page |

|----------|-----------------------------------------------------------------------------------|------|

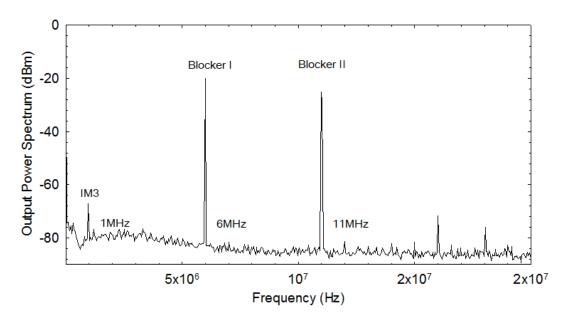

| Fig. 81. | Output power spectrum of the VGA.                                                 | 121  |

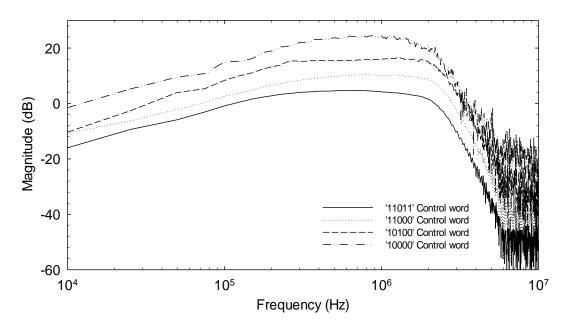

| Fig. 82. | Frequency response of the baseband section (CSF+VGA) for different control words. | 123  |

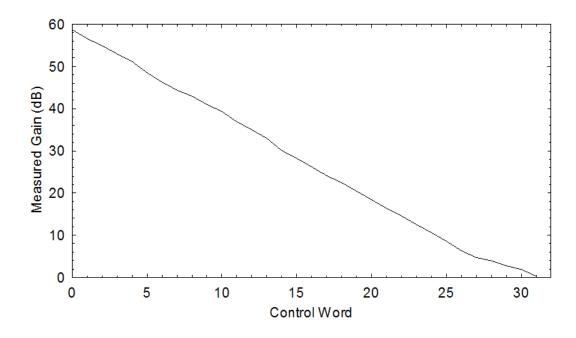

| Fig. 83. | Gain control word vs measured gain of the baseband section                        | 123  |

# LIST OF TABLES

|             |                                                                                    | Page |

|-------------|------------------------------------------------------------------------------------|------|

| Table I.    | Values of the matching network components.                                         | 18   |

| Table II.   | Summary of the time and current values for different IMD tasks                     | 26   |

| Table III.  | Link budget parameters with d=2.1m.                                                | 34   |

| Table IV.   | Lead derivations of the 12-lead ECG WMS.                                           | 42   |

| Table V.    | Summary of measurement results for the presented ECG WMS                           | 49   |

| Table VI.   | Transistor sizing ratios and operating conditions                                  | 73   |

| Table VII.  | Comparison between the proposed bioamp and other state-of-the art works.           | 88   |

| Table VIII. | Summary of EVA tadio Receiver, CSF and VGA specifications                          | 95   |

| Table IX.   | Filter coefficients and capacitor values after frequency/impedance scaling.        | 99   |

| Table X.    | Transistor sizing ratios.                                                          | .107 |

| Table XI.   | DC bias voltages and current measurements, simulated vs measured results.          | .113 |

| Table XII.  | Simulated and measured cut-off frequencies of the CSF for different control words. | .115 |

| Table XIII. | Summary of results (CSF).                                                          | .118 |

| Table XIV.  | DC bias voltages and current measurements. simulated vs measured results.          | .119 |

| Table XV.   | Summary of results (VGA).                                                          | .122 |

| Table XVI.  | Summary of results (CSF+VGA).                                                      | .124 |

#### CHAPTER I

#### INTRODUCTION

#### Motivation

Public health systems of developed countries spend around 75% of their healthcare yearly budget on resources used to treat patients with chronic conditions such as heart/respiratory/oral related diseases, cancer, diabetes, arthritis and obesity among others [1-3]. Only in the U.S., these conditions lead the causes of death and disability, thus becoming a major concern and challenge within the medical community [4]. At the same time, recent advances in physiological research and complementary metal-oxide-semiconductor (CMOS) technology have resulted in significant progress on the medical, analog circuit design and wireless communications fields.

The imminent impact of chronic diseases along with the aforementioned boost on the medical and technological disciplines has given rise to the use of preventive medicine, embracing early detection efforts [4] and ambulatory monitoring for patients with existing conditions as their secondary and tertiary illness prevention stages [5]. Therefore, a major emphasis has been placed on prevention rather than on treatment, resulting in a high demand of wireless medical systems (WMS) able to provide reliable monitoring along with high accuracy diagnosis [6] for home care and short stays in health centers. Furthermore, the use of WMS is expected to lead patients and health care costumers to enhance rehabilitation, information and involvement in their own treatment[7]. Similarly, the use of WMS on preclinical studies aimed to determine

physiological and pharmacological issues has helped to reach key milestones on these fields.

## **Wireless Medical Systems Overview**

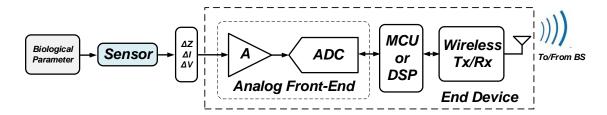

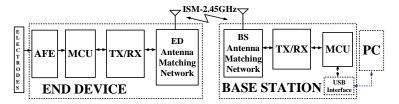

The simplified block diagram of a typical WMS is shown in Fig. 1. The system includes an end device (ED) in charge of collect, digitize and wirelessly transmit the desired signal, a base station (BS) that receives the digital information and sends it to a graphical user interface (GUI) implemented in a personal computer (PC).

Fig. 1. Block diagram of a typical wireless medical system.

The sensor translates a specific physiological or biochemical parameter into an equivalent signal of another type of quantity, for example, an electrical or optical signal, acting as a transducer that converts the *measurand* (a quantity or a parameter) into a signal carrying the desired information [8]. The sensor enables the detection of biologic events through variations of the sensing element properties, thus becoming the interface between a biological system and the WMS.

Depending of the type of sensor, different interfaces are required to successfully acquire the signal of interest. For electrical sensors, a change on the *measurand* is reflected in a variation of a voltage, current or impedance. This variation is detected by an analog front-end (AFE) composed of an amplifier and an analog-to-digital converter (ADC) which in turn transfers the collected data to a microcontroller (MCU) or to a

digital signal processing (DSP) unit. This is illustrated in Fig. 2 where the last block consists of a wireless transceiver in charge of transmitting the information to the BS through a wireless communication channel. Depending on the application, the ED can be implantable (invasive) or wearable (non-invasive). In both cases, the main design concerns are size, power, cost and lifetime. Key aspects to deal with these challenges will be presented on this dissertation for invasive and non-invasive applications.

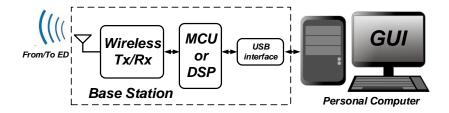

The BS acts as a gateway between the ED and the GUI. Fig. 3 presents a simplified block diagram of a typical BS and GUI. The BS consists of a wireless transceiver that handles the communication with the ED, an MCU or DSP and an interface, in this case universal serial bus (USB) channel, to communicate with the GUI.

Fig. 2. Simplified block diagram of typical ED showing the interaction between a biological parameter and the sensor used to translate the *measurand* into an electrical signal.

Fig. 3. Simplified block diagram of a typical BS with the GUI implemented in a personal computer.

The GUI is implemented in a personal computer and is in charge of storing the received data or sending it to a health care center or physician's office, depending on the application. In some cases, the user can modify the operation of the ED through the GUI, changing settings such as period of operation ( for non-continuous monitoring systems) or signal resolution.

# **Dissertation Organization**

The first and major part of this dissertation will present the design, implementation and testing of two low-power oriented WMS for invasive and non-invasive applications along with a fully integrated ultra-low-power low-noise biopotential amplifier for electrocardiogram (ECG)/ electroencephalogram (EEG)/ electromyogram (EMG) monitoring applications.

Chapter II presents a WMS to monitor the blood pressure of laboratory animals for drug safety research using an implantable medical device (IMD) as the ED unit. The implementation of the IMD provides general picture of design issues faced while implementing a WMS for implantable applications. The IMD and BS units are designed using on off-the-shelf integrated circuits. A low-power-oriented control algorithm aimed to optimize the current consumption of the IMD is introduced as the strategy to increase its lifetime. The main details regarding the analog front-end used for signal acquisition, the aforementioned low-power-oriented algorithm and an analysis of power consumption vs. lifetime are explained. Similarly, the main considerations for link budget calculations in implantable applications using the medical implant communication service (MICS) and are explained. Finally, the *in-vitro* test bench used to characterize the WMS

application and the obtained results are discussed.

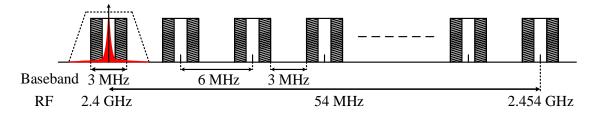

In Chapter III, a wearable WMS intended for continuous cardiac-activity monitoring is presented. The WMS is proposed as mean to provide early detection and diagnosis of cardiac diseases, allowing physicians to identify abnormalities likely to progress and cause permanent damage. This WMS includes a more complex analog front-end consisting of 8-channels dedicated to the extraction of a standard 12-lead ECG. The system is also implemented using off-the-shelf components and although the size/power specs are relaxed, the required range of operation is more demanding (about 30 to 35 m). The WMS uses an RF link that operates in the industrial, scientific and medical (ISM) band at 2.45 GHz. The main design considerations, implementation challenges, the *in-vitro* test bench and measured results are discussed.

Chapter IV presents a fully integrated integrated ultra-low-noise/low-power biopotential amplifier for electrocardiogram ECG/EEG/EMG applications. First, the main design concerns for biopotential acquisition are presented. Then, a literature review summarizing the existing solutions provides an overview of the current trends and challenges on biopotential amplifier's design. The architecture of the bioamp is then presented, including a fully-differential OTA with chopper modulators at its input and output in order to reduce the effect of the OTA's 1/f noise/systematic offset. Also, a feedback network consisting of capacitors and a high resistance implemented by a T-network composed of MOS-bipolar pseudo resistors and a triode-region transistor is used to obtain a high-pass cut-off frequency in the mHz range without the need of external components. Finally, a negative capacitance is introduced to boost the OTA's

input impedance and preserve the negative feedback properties of the bioamp. The measured results of the bioamp fabricated using 0.5 µm CMOS technology and the test bench designed for the circuit characterization, including the considerations for noise performance measurements, are discussed.

Chapter V is dedicated to the system-level design and transistor-level implementation of the baseband section of an extravehichular activity (EVA) radio receiver. EVA is commonly known as spacewalk and allows astronauts to conduct experiments in the space shuttle's payload bay, to test new equipment in space and to repair satellites in orbit. These tasks demand versatile radio systems with high levels of integration, low power consumption, light weight and small volume, characteristics shared with RF transceivers used by WMS. In both applications, EVA and WMS, the radios transmit/receive information (audio/video and physiological signals respectively) through frequency bands (S-band and ISM/MICS band) used by other services, resulting in a crowded spectrum that includes undesired spectral content (blockers) that may limit the dynamic range of the receiver. This chapter starts discussing the specifications for the EVA radio receiver. The architecture used to implement the baseband section, consisting of a channel selection filter and a variable gain amplifier designed to reduce the effect of blockers on the EVA radio receiver, effectively increasing its overall linearity. The circuits were implemented in 180 nm CMOS technology and the measurement results including frequency response, noise and linearity are presented. Due to the similarities between the two applications, the presented topology can be used to implement the baseband section for an ISM/ MICS band receiver.

Finally, Chapter VI concludes the discussion about the proposed WMS, the implemented biopotential amplifier and the baseband circuit for EVA radio presented in this dissertation.

#### **Research Contribution of this Dissertation**

This dissertation provides insight for the design and implementation of WMS starting from the system level point of view and concluding with the transistor-level implementation of blocks relevant specifically to the signal acquisition and radio frequency signal reception. A design methodology aimed to optimize the design time and power consumption of wireless medical systems for implantable [9] and non-implantable [10] [11] is presented. The proposed biopotential amplifier architecture [12] improves the noise power efficiency of the first element on the analog acquisition stage of a WMS while the implemented channel selection [13] and VGA topologies effectively increase the linearity of the radio receiver they are part of.

The presented low-power-oriented algorithm and life-time vs. power analysis complement each other providing an accurate estimation of the ED power performance along with a fast design and debugging process. The *in-vitro* measurements reported in this dissertation demonstrate that the proposed methodology can be used for the implementation of wearable or implantable WMS, allowing the designer to experiment/debug the main issues that would be found by the final version of the ED.

The architecture of the presented ultra-low-noise/low-power biopotential amplifier can be used to implement analog front-ends for other low frequency signals sensitive to flicker noise with reduced power consumption thus improving the power

performance of the required application without compromising the quality of the acquired signal.

Finally, the results for the implemented channel selection filter and variable gain amplifier demonstrate strong rejection to in-band blockers present on the band of interest for the giving receiver, resulting in an increase of the sensitivity of the system. Although the circuit was designed for an EVA radio receiver, the same architecture can be applied for an ISM band radio, currently used by a diverse set of radio systems and therefore very sensitive to the presence of in-band blockers.

The results obtained from the different techniques presented on this work invokes interest from the industry/academia as a way for fast prototyping/defining educational projects based on the proposed WMS design methodology. Additionally, this work demonstrates the feasibility of using long-channel silicon-based technologies for implementing biopotential acquisition circuitry keeping low power consumption while optimizing the integrity of the amplified signal.

#### CHAPTER II

# A WIRELESS MEDICAL SYSTEM PROTOTYPE FOR IMPLANTABLE APPLICATIONS\*

## Introduction

Advances in medical technology have allowed physicians to improve the patients' quality of life through the use of wireless medical systems (WMS) aimed to provide reliable monitoring and high accuracy diagnostics [6]. A typical WMS includes an end device (ED) and a base station (BS) complemented by a graphical user interface (GUI) implemented in a computer [10]. The ED is in charge of collecting information about a specific physiological or biochemical parameter while the BS acts as a gateway between the ED and the GUI. Depending on the application, the ED can be wearable (non-invasive) or implantable (invasive) and the WMS can be targeted to complement the patient's treatment or as part of a research study.

The main issues related with the implementation of such systems are size, cost and lifetime, especially when the monitoring unit is an implantable medical device (IMD) [14]. Key solutions to these issues are the selection of the right hardware along with the use of a smart software control algorithm to optimize the power consumption. In terms of hardware, designers have three main options to choose from: application specific integrated circuits (ASICs), programmable systems on chip (PSoCs) and off-the-

<sup>\*©[2013]</sup> IEEE. Reprinted, with permission, from "A wireless medical system prototype for implantable applications," by J. E. Gaxiola-Sosa and K. Entesari, in 2013 *IEEE Fourth Latin American Symposium on Circuits and Systems (LASCAS)*, 2013, pp. 1-4.

shelf components. ASICs offer the highest level of innovation, small size and the best power performance. However, their design implies high cost and long development periods. Programmable SoCs provide some design flexibility, modest cost and relatively fast implementation. Nevertheless, system optimization is limited to the performance of each individual block. Finally, the use of commercial ICs allows fast prototyping while keeping a low price, but the size and power consumption of the system become restricted by the characteristics of the chosen components. Regarding the software, power optimization can be achieved by using only a microprocessor core in ASICs and PSoCs instead of a complete microcontroller (MCU), as in the off-the-shelf case. Taking this into consideration, careful analysis of the application, available resources and time restrictions should be done in order to determine the optimum way to implement the WMS.

This chapter presents a WMS prototype intended for implantable applications. The implantable unit design takes advantage of the qualities of the three hardware options mentioned before while minimizing the cons that come along with each of them, resulting in a fully programmable system-on-board. The presented BS allows power optimization of the IMD radio through the use of two different radio bands for wake-up and data transmission.

The aim of the system is to monitor the blood pressure of laboratory animals for drug safety research. However, the approach employed in this study can be used to implement an IMD targeted to monitor other physiological or biochemical parameters such as pH, temperature, phosphorus-based blood gases, etc. Moreover, the WMS

includes the option of modifying the signal resolution and frequency of data collection according to the specific needs of the user.

This chapter starts with a discussion of the design and implementation of the WMS. Then, the IMD low-power-oriented control algorithm and the IMD power vs. lifetime analysis are explained. Finally, the obtained results are presented.

# **System Design and Implementation**

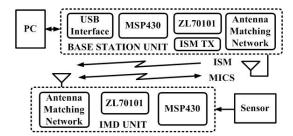

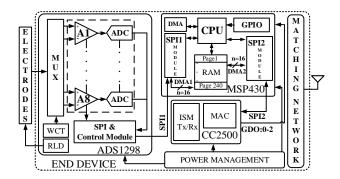

A block diagram of the WMS, including simplified versions of the IMD and the BS, is presented in Fig. 4. Both units are based on two off-the-shelf integrated circuits (ICs) intended for ultra-low-power applications: the Texas Instruments MSP430FG4618 [15], a mixed-signal MCU; and the Microsemi (formerly Zarlink) ZL70101 [16], a medical implantable radio transceiver. The MCU enables the design of a low-power-oriented control algorithm through its capability of shutting down peripherals that are not used at know time intervals. This provides PSoC characteristics to the IMD in the sense of power performance. The transceiver is an ASIC that operates at the medical implant communication service (MICS) band at 402 MHz-405 MHz to send/receive biological information/instruction-commands to/from the BS unit and includes an on-chip ultra-low power wake-up mechanism operating in the industrial, scientific and medical (ISM)

Fig. 4. Block diagram of the WMS.

band at 2.45 GHz to listen for a wake-up signal from the BS unit. The media access controller (MAC) of the transmitter allows it to operate as an extra MCU peripheral, enabling the integration of a system-on-board capable of supporting a software control algorithm to optimize the overall power consumption of the IMD.

The basic operation principle of the WMS can be summarized as follows: the BS transmits a wake-up signal to the IMD using the ISM band and the IMD replies with an acknowledge message using the MICS band. Once the link is established, further communications are handled using the MICS band. This frequency band is regulated by the Federal Communications Commission (FCC) for implantable biotelemetry applications [17]. After a given number of physiological measurements is stored in the IMD, the collected data is sent to the BS which in turn, will transmit it to the PC via universal serial bus (USB) connection. Once in the computer, the GUI allows the user to view the information in real-time and stores the samples in text files available for future analysis. In the next subsections the IMD and the BS unit are described in more detail.

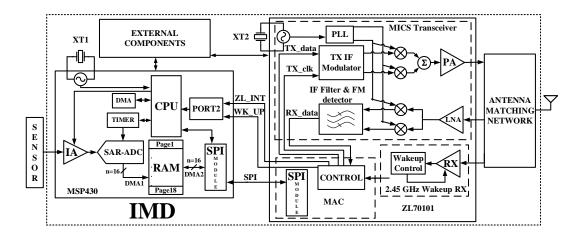

# Implantable Medical Device

The most critical section of the presented WMS is the IMD. A detailed block diagram describing its main components is presented in Fig. 4, including a MCU, a wireless transceiver, a dual-band matching network and a few external components such as bypass capacitors, crystal oscillators and resistors as part of the analog front-end (AFE).

# Signal Acquisition and Analog-to-Digital Conversion

A sensor translates the physiological parameter into an electrical signal. The signal is injected into instrumentation amplifier (IA) built using the MCU's on-chip op amps and

Fig. 5. Detailed block diagram of the IMD unit.

external passive components. The MCU has the ability to turn the op amps off when they are not being used, in order to reduce the power consumption of the IMD. A three op amp IA topology including an antialiasing filter is selected as the IMD's analog frontend and its schematic diagram is presented in Fig. 5. This IA implementation rejects electromagnetic and electrostatic interferences with a common-mode rejection ratio (CMRR) better than 80 dB [18-20]. The first stage of the IA is composed of two op amps in non-inverting configuration in order to provide high input impedance to the incoming differential signal. The second stage is configured as a difference amplifier [21] and includes an antialiasing filter to remove out of band interferences whose folding after the analog to digital conversion would corrupt the signal band [22]. The gain and cut-off frequency of the IA are given by eqs. (2.1) and (2.2). The external passive components used on the IA are: R1 (variable) = 0-250K $\Omega$ , R2 = 1M $\Omega$ , R3 = 200K $\Omega$ , R4 = 10M $\Omega$  and C = 1nF.

The output of the IA is connected to a 12-bit successive approximation register

Fig. 6. A three op amp IA with embedded anti-aliasing filter.

$$V_{OUT} = (V_{IN+} - V_{IN-}) \left( 1 + \frac{2 \cdot R2}{R1} \right) \left( \frac{R4}{R3} \right)$$

(2.1)

$$f_{3dB} = \frac{1}{2\pi \cdot R4 \cdot C} \tag{2.2}$$

analog-to-digital converter (SAR-ADC), also included as part of the MCU. This module can be shut down after a conversion is completed and includes a buffer where the samples are stored before being sent to the random access memory (RAM) [15]. Since most physiological signals have similar bandwidths (from DC up to 250 Hz) [23, 24] and because of the low power features of the SAR-ADC topology [22], it is possible to modify the ADC's oversampling ratio (OSR) up to 30 in order to increase the accuracy of the conversion without compromising the power consumption. Having this relatively high OSR relaxes the specifications of the anti-aliasing filter and allows its integration by just adding external capacitors to the IA's second stage as showed in Fig. 6. The gains of the 1<sup>st</sup> and 2<sup>nd</sup> stages of the IA are 8 V/V and 50 V/V respectively, resulting in a total gain of 400V/V with a cut-off frequency of 15Hz. The cut-off frequency was

selected based on the bandwidth of the signal that will be monitored in this application, blood pressure of small animals.

## **Digital Communication and RAM Organization**

Since the MCU has a 16-bit central processing unit (CPU) and the SAR-ADC has a 12-bit resolution, the 4 most significant bits of each stored sample are kept as reserved bits. The MCU's direct memory access (DMA) module uses a transfer channel (DMA1) to send the data from the ADC's buffer to the 8KB RAM with no CPU intervention [15]. The RAM is organized in 18 pages. Each page includes 217 words of 16 bits, and a data packet consists of 9 of these pages. When a data packet is ready to be transmitted, a second transfer channel of the DMA module (DMA2) sends the data to the serial peripheral interface (SPI) module. Again, no CPU intervention is needed to transport the information from the RAM to the SPI module, thus allowing reduction of the power consumption. Using the SPI module, the sampled data and control commands are transferred from the MCU and to the transceiver. The transceiver has its own SPI module and receives the 8-bit words sent by the MCU with a data rate of 2 mega

Fig. 7. Timing diagram of the SPI link between the MCU and the transceiver.

samples per second using a shared clock provided by the MCU. Fig. 7 shows a timing diagram of the master device (MCU) while it transmits and receives data. The SPI module uses three pins to operate, a clock (CLK), the slave-input master-output (SIMO) and the slave-output master-input (SOMI). Depending on the clock polarity, SIMO will start transmitting at the rising or falling edge of CLK and SOMI will sample the incoming data at the opposite clock edge [15].

# **Wireless Transceiver and Matching Network**

Once in the transceiver, the data is codified and encrypted in the MAC. Then, an intermediate frequency (IF) modulator receives the digital data and a clock stream from the MAC, and converts the data into in-phase and quadrature (I&Q) signals at IF = 450 KHz [16]. The resulting scheme is a four-level frequency shift keying (4FSK) modulation with a maximum effective data rate larger than 200 Kbps [16]. The modulated signals pass through a pair of balanced mixers, fed by I&Q pairs of both IF and local oscillator (LO) signals, for up-conversion to the selected channel in the MICS band. The outputs of the mixers are added and result in a single-sideband signal with suppression on the unwanted opposite sideband. This signal passes through a power amplifier (PA) stage which provides a maximum output signal of -3dBm. Finally, the signal goes into an external matching network and is radiated by the antenna.

When the IMD receives information using the MICS band, the signal from the antenna passes through the matching network and then is injected to the on-chip Low Noise Amplifier (LNA). Then, the signal passes over a pair of balanced mixers similar to the ones used in the transmitter. The mixers produce a pair of I&Q signals at

IF = 450 KHz [16]. This is followed by an IF Filter and a FM detector which translates the frequency deviations to a time-varying voltage level. The resulting baseband signal is converted to the digital domain by a 2-bit quantizer [16]. The digitized data is sent to the MAC for correlation and clock recovery. Finally, the recovered data is transferred to the MCU using the SPI link described before.

Fig. 8 shows the external matching network needed to operate the transceiver in the ISM and MICS bands while using a dual-band antenna. The RF signal received by the antenna goes through a capacitor  $(C_X)$  for AC coupling and is followed by an LC tank  $(C_Y)$  and  $(C_Y)$  that acts as notch to filter out signals centered at the ISM band. A surface acoustic wave (SAW) filter is used to limit the incoming information to content centered at the MICS band. The SAW filter used in this work is a customized design from Kyocera with a center frequency of 403.5 MHz and bandwidth of 3 MHz [25]. A pi-network  $(C_{P1}, C_{P2})$  and  $(C_{P1})$  is used to match the impedance of the SAW filter at port 2  $(C_{P2})$  to the impedance of the antenna while a high-pass LC network  $(C_{P1})$  and  $(C_{P1})$  and the RX/TX MICS band pin of the transceiver. When a wake-up signal (ISM band) is received by the antenna, it is

Fig. 8. Dual-band matching network of the IMD.

rejected by the notch filter mentioned above and passes through a low-pass LC network  $(C_{Z2} \text{ and } L_{Z2})$  that conducts impedance transformation between the wake-up pin of the transceiver and the antenna. The values of the matching network components are presented in Table I.

Table I. Values of the matching network components.

| Component       | Value | Component                 | Uplink |

|-----------------|-------|---------------------------|--------|

| $C_{Z1}$        | 120pF | $C_{Y}$                   | 1.2pF  |

| L <sub>Z1</sub> | 19nH  | $\mathbf{L}_{\mathbf{Y}}$ | 2.7nH  |

| $C_{P1}$        | 5.6pF | $C_{X}$                   | 30pF   |

| C <sub>P2</sub> | 5.6pF | L <sub>Z2</sub>           | 3.3nH  |

| L <sub>P</sub>  | 18nH  | C <sub>Z2</sub>           | 0.75pF |

As mentioned before, the wireless link using the MICS band can be used for data and commands transmission, and it can even work to start communication between the IMD and BS. Nevertheless, using it to periodically listen for the BS's wake-up signals would result in excessive power consumption since the receiver is composed by several power hungry blocks. In order to provide an ultra-low-power wake-up mechanism, a receiver using an On/Off Key (OOK) modulation employing a dedicated frequency band with modest power consumption for the start-up process was implemented in the transceiver IC. By using the OOK scheme there is no need for a local oscillator while the use of a predefined frequency (a channel within the ISM band) for the wireless transmission reduces the complexity of the receiver [16]. On this way the on-chip ultra-

low-power receiver is being used instead of the MICS receiver in order to start the IMD operations.

# Base Station and Graphical User Interface

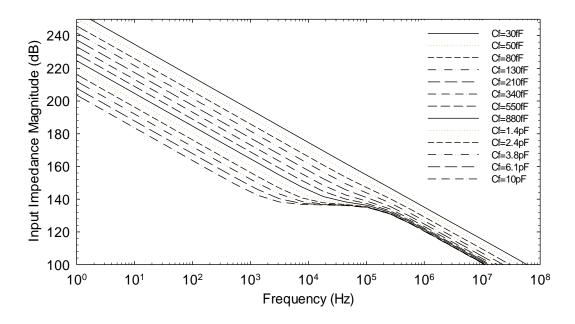

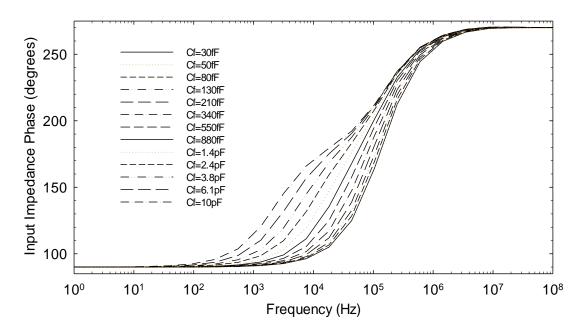

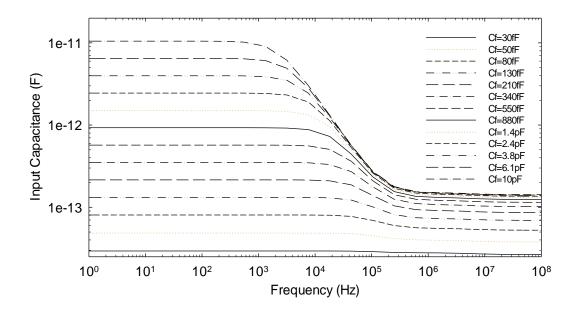

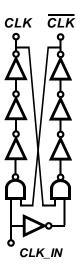

The base station of the ZL70101 application development kit from Microsemi is employed as BS unit in this work. Its design is similar to the IMD in the sense that it is based on the same transceiver and that the employed MCU belongs to the MSP430 family. A block diagram of the BS is presented in Fig. 9. The signal from the IMD is received by a multi-band helical antenna and passes through the matching network and transceiver similarly as explained in the previous subsection. The transceiver receives the data and sends it to the MCU through the SPI module. The MCU then transfers the data to a USB interface chip through a serial non-synchronous link and the aforementioned IC handles the communication with the computer. In the computer, the GUI performs the data processing and stores the received data. Using the GUI, the user can modify the link features such as modulation, data rate and frequency of data collection.